Page 1

MF297-07

CMOS 4-BIT SINGLE CHIP MICROCOMPUTER

S1C6200/6200A

Core CPU Manual

Page 2

NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko

Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any

liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or

circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such

as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there

is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright

infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic

products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from

the Ministry of International Trade and Industry or other approval from another government agency.

© SEIKO EPSON CORPORATION 2001 All rights reserved.

Page 3

The information of the product number change

Starting April 1, 2001, the product number will be changed as listed below. To order from April 1,

2001 please use the new product number. For further information, please contact Epson sales

representative.

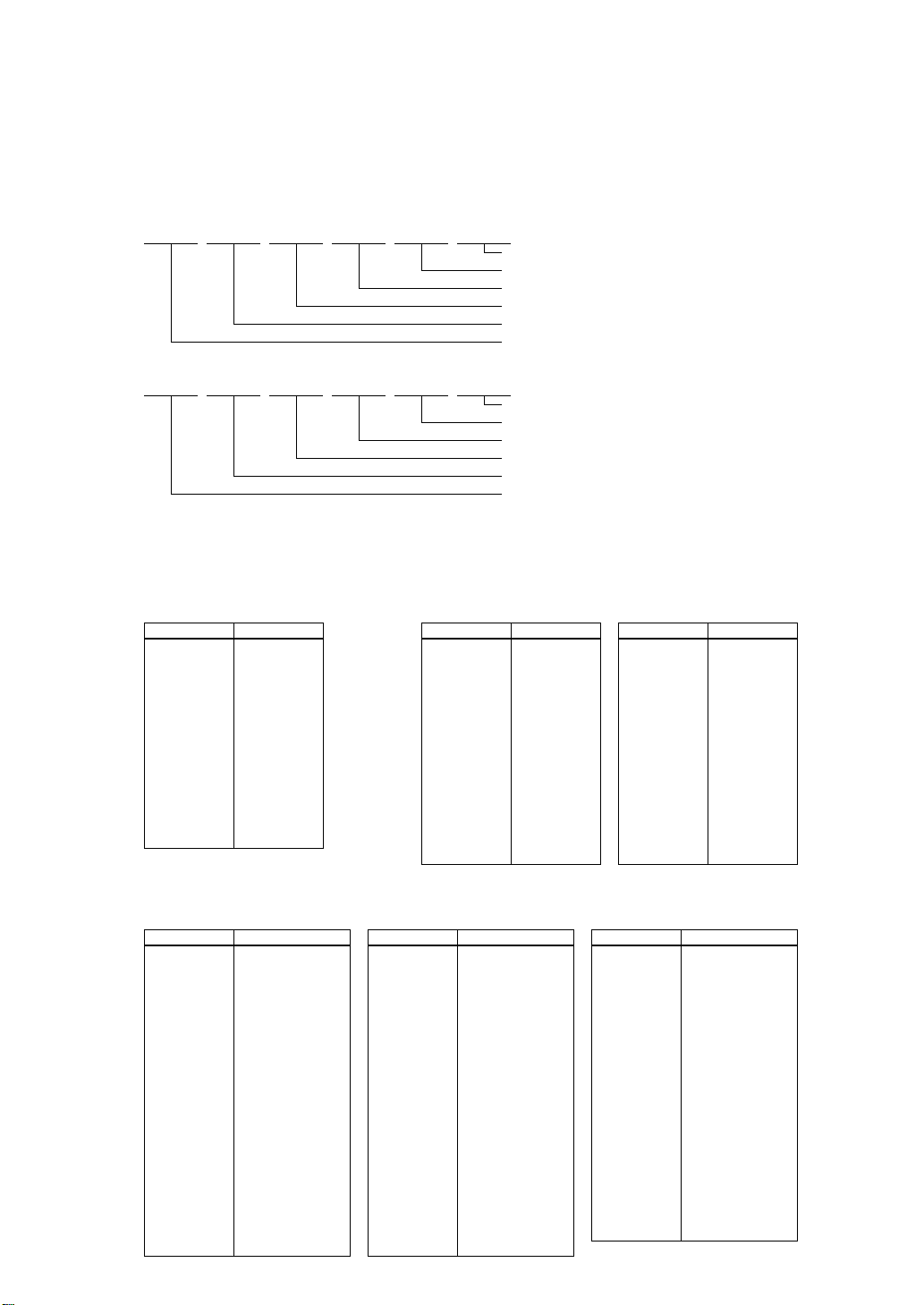

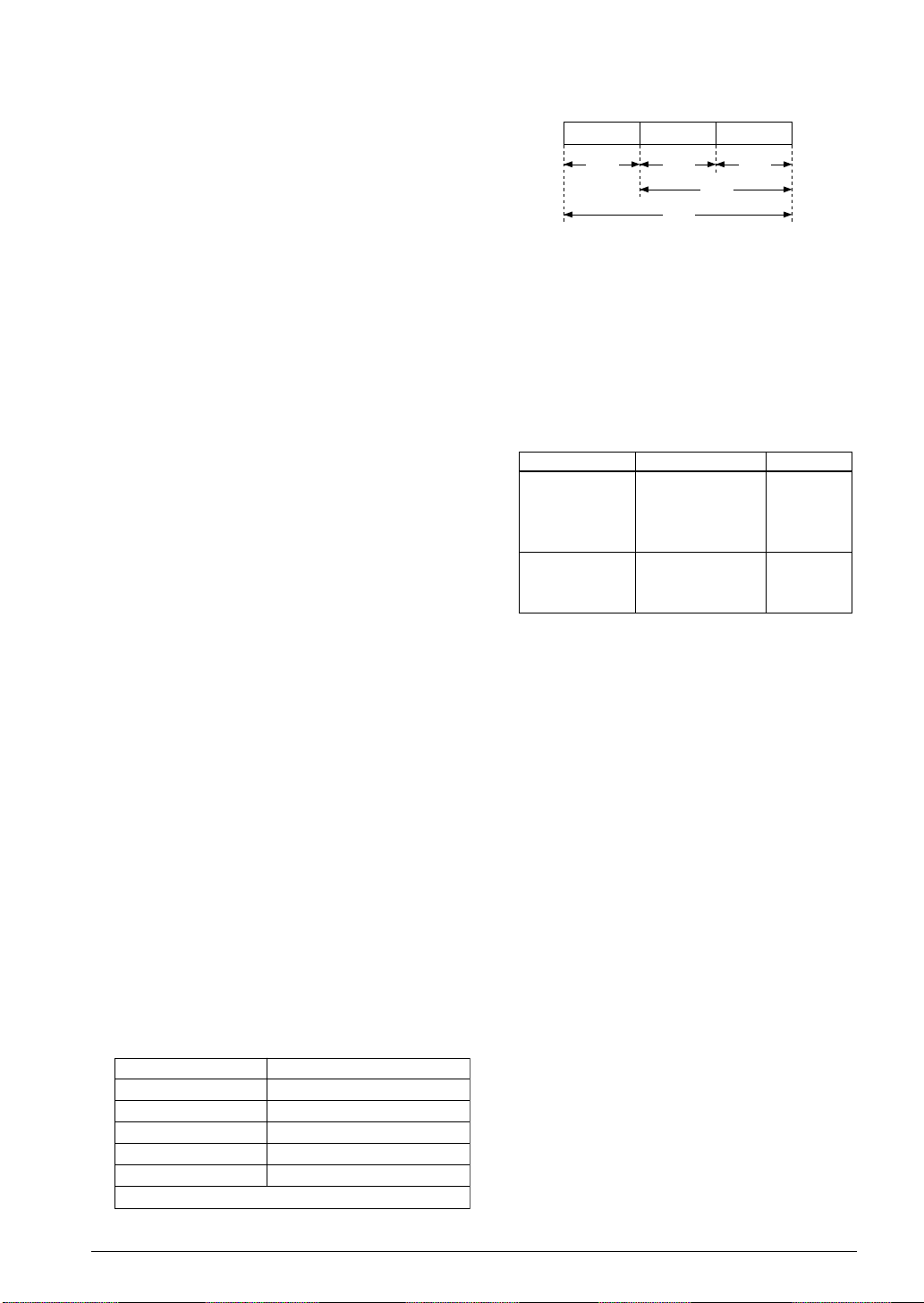

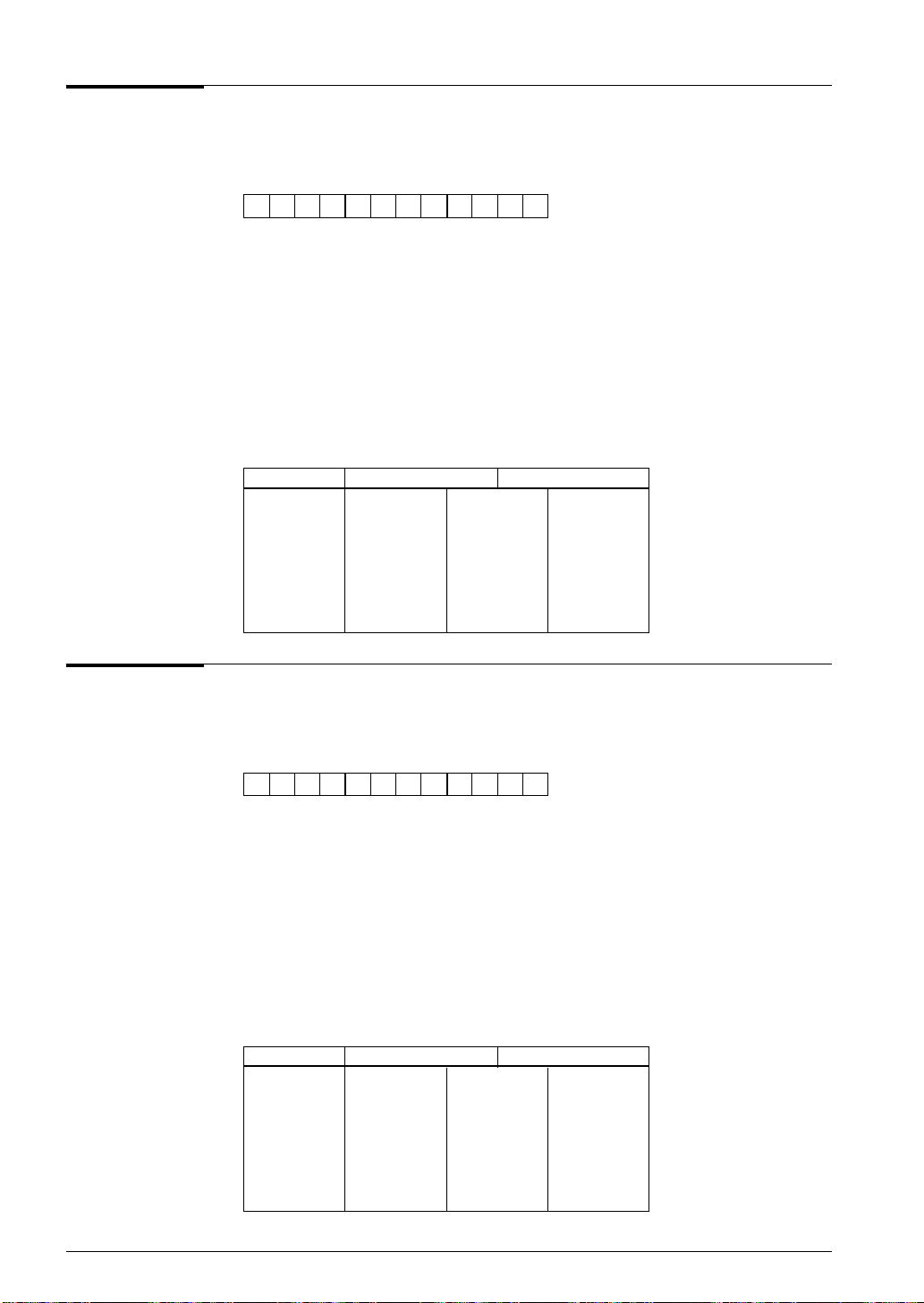

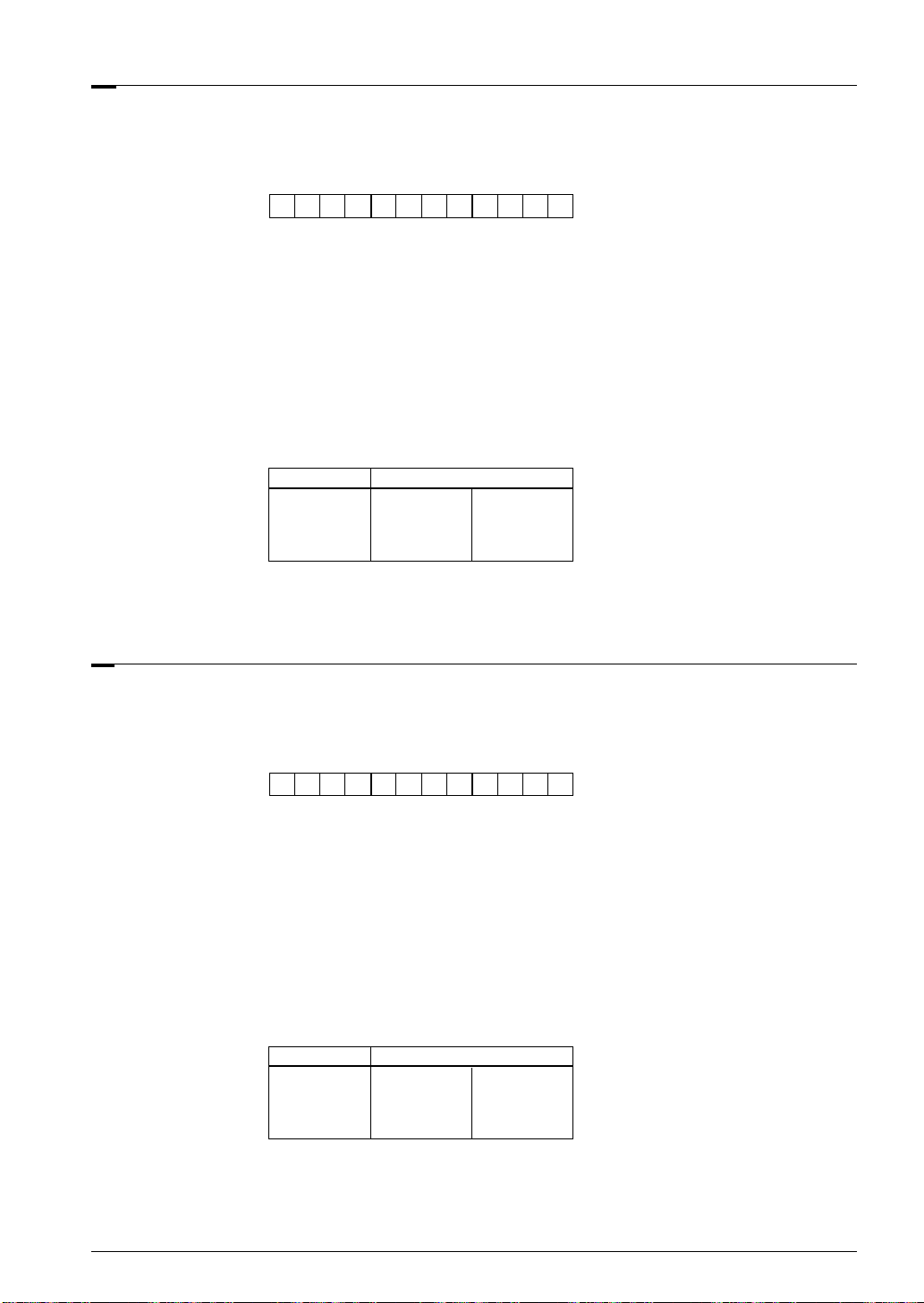

Configuration of product number

Devices

S1 C 60N01 F 0A01

Development tools

S5U1

∗1: For details about tool types, see the tables below. (In some manuals, tool types are represented by one digit.)

∗2: Actual versions are not written in the manuals.

C 60R08 D1 1

00

Packing specification

Specification

Package (D: die form; F: QFP)

Model number

Model name (C: microcomputer, digital products)

Product classification (S1: semiconductor)

00

Packing specification

Version (1: Version 1 ∗2)

Tool type (D1: Development Tool ∗1)

Corresponding model number (60R08: for S1C60R08)

Tool classification (C: microcomputer use)

Product classification

(S5U1: development tool for semiconductor products)

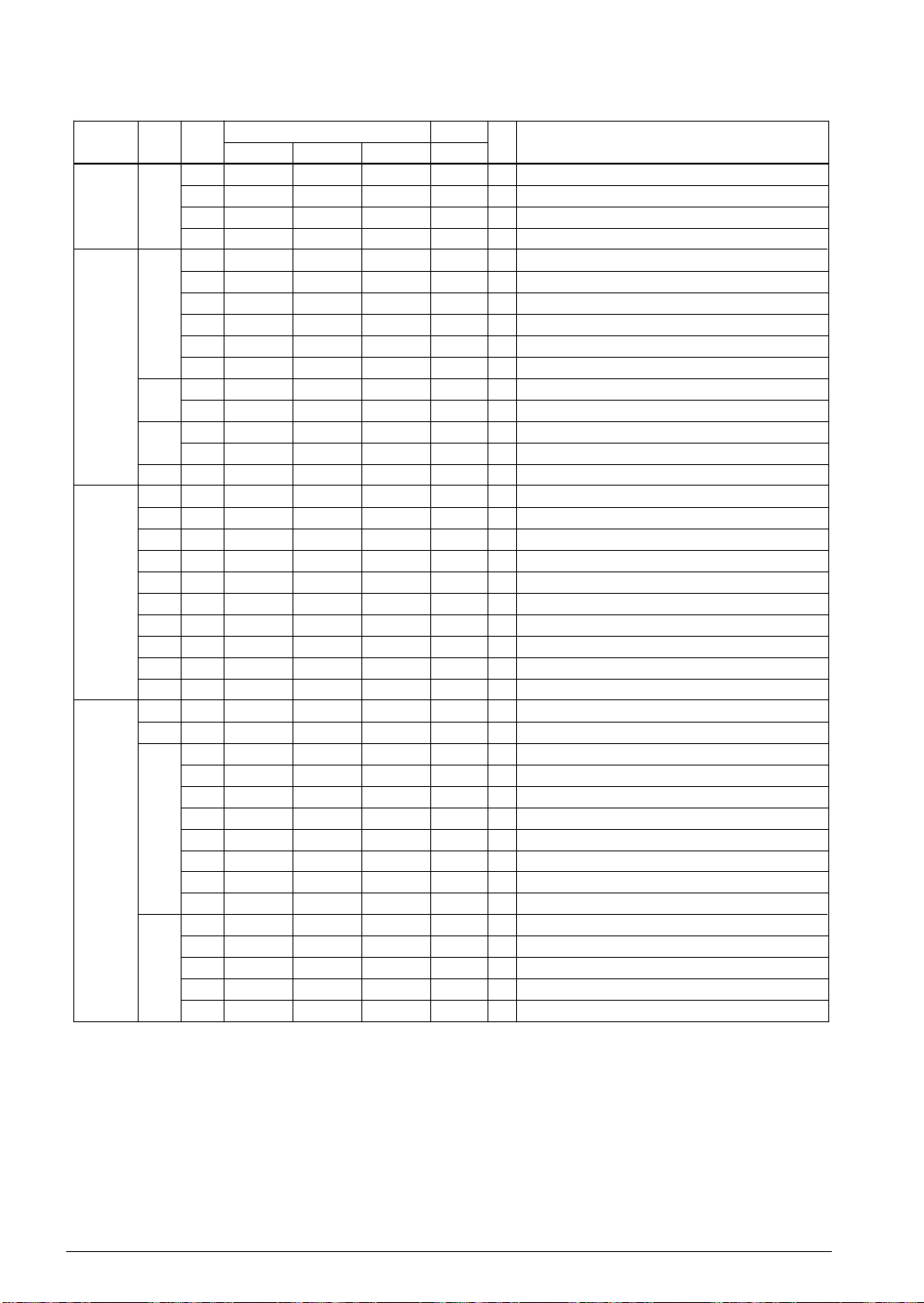

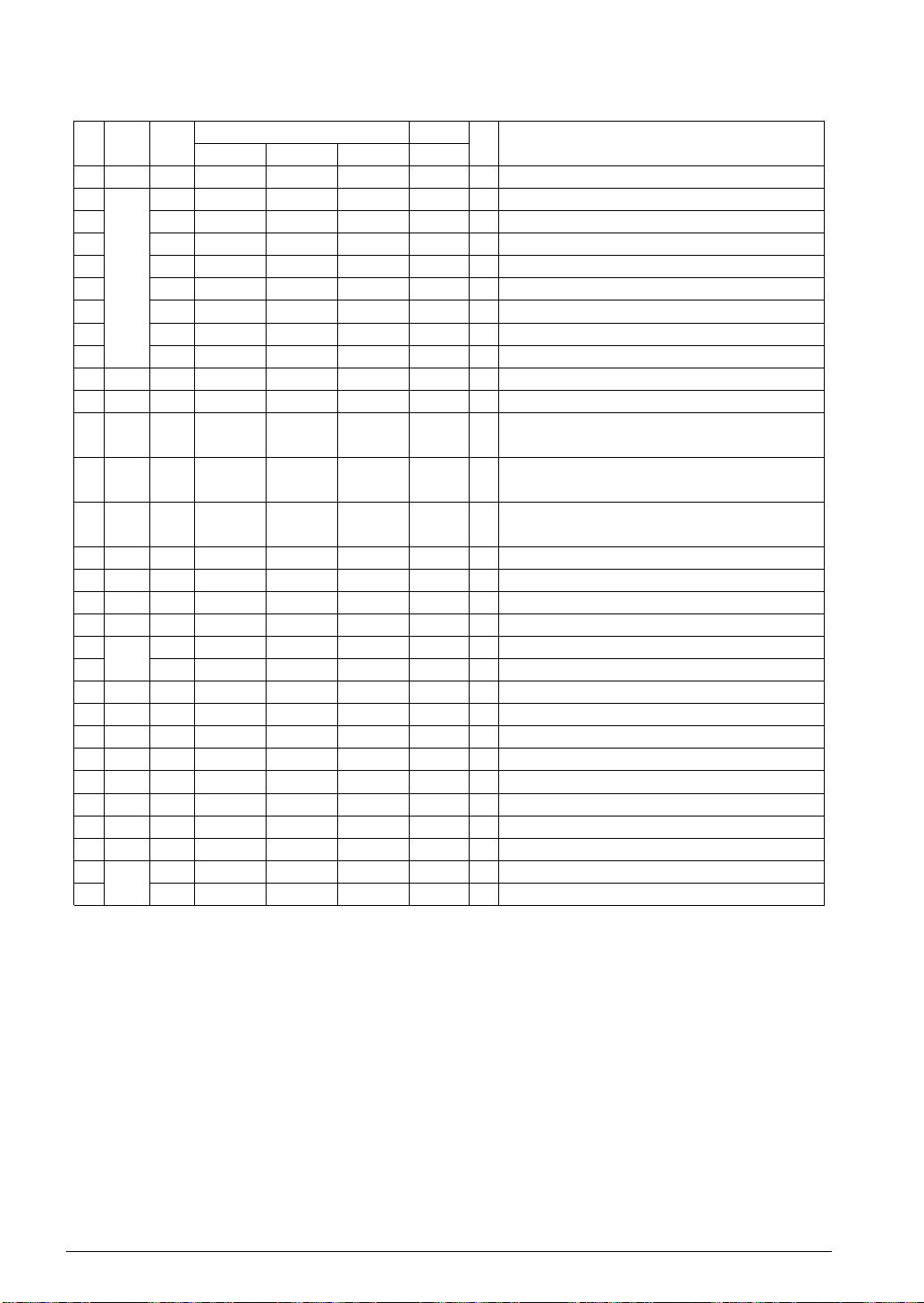

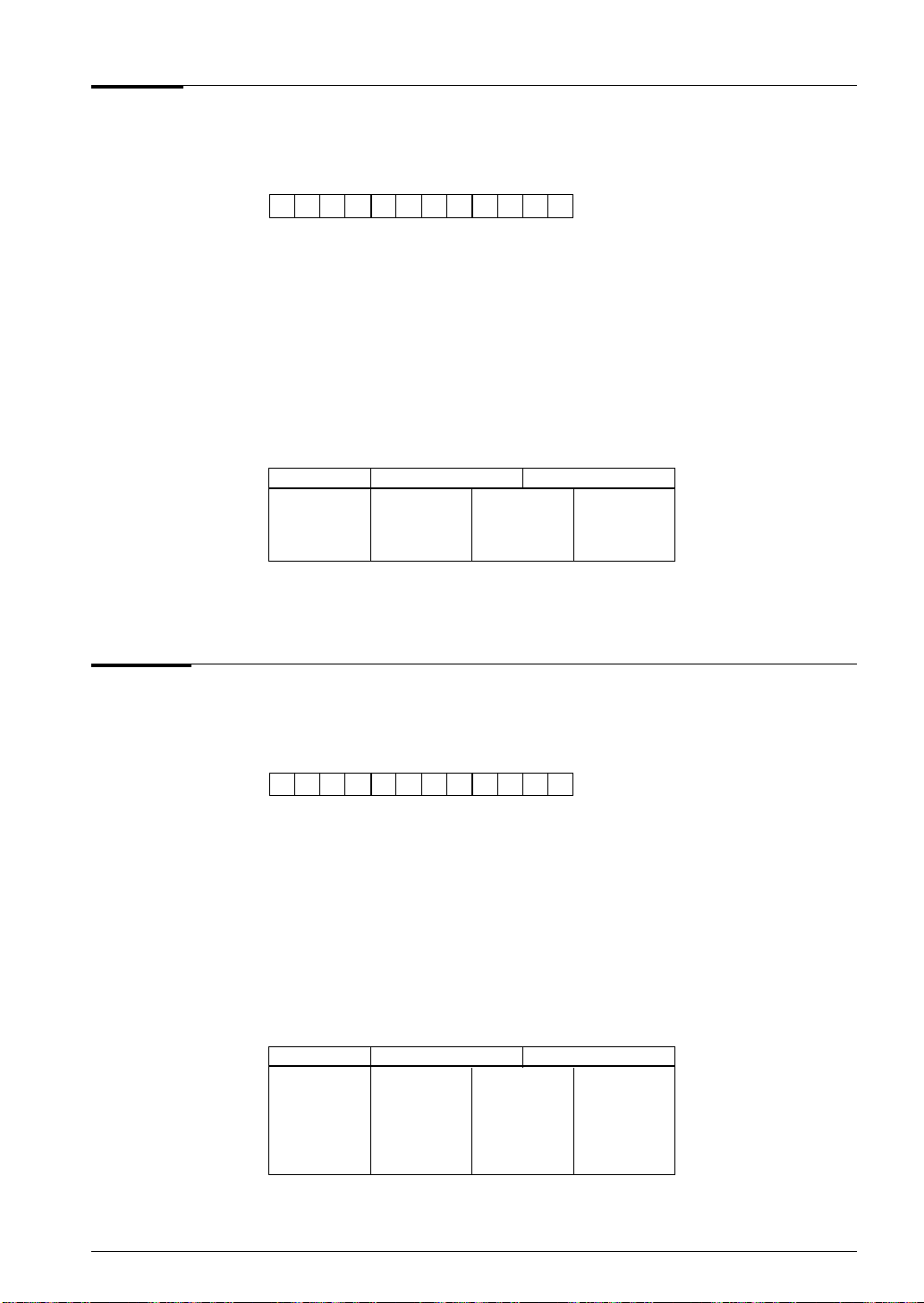

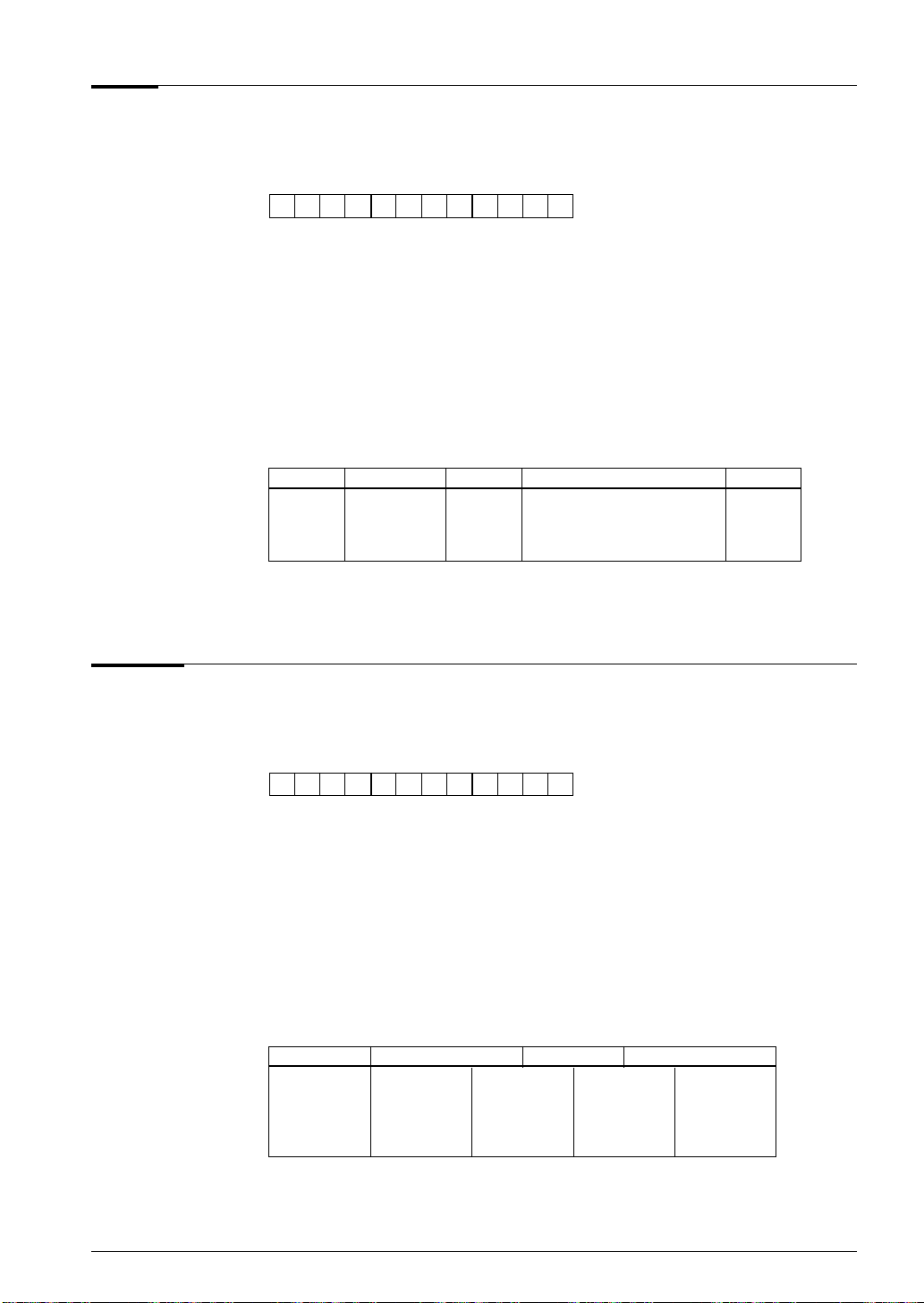

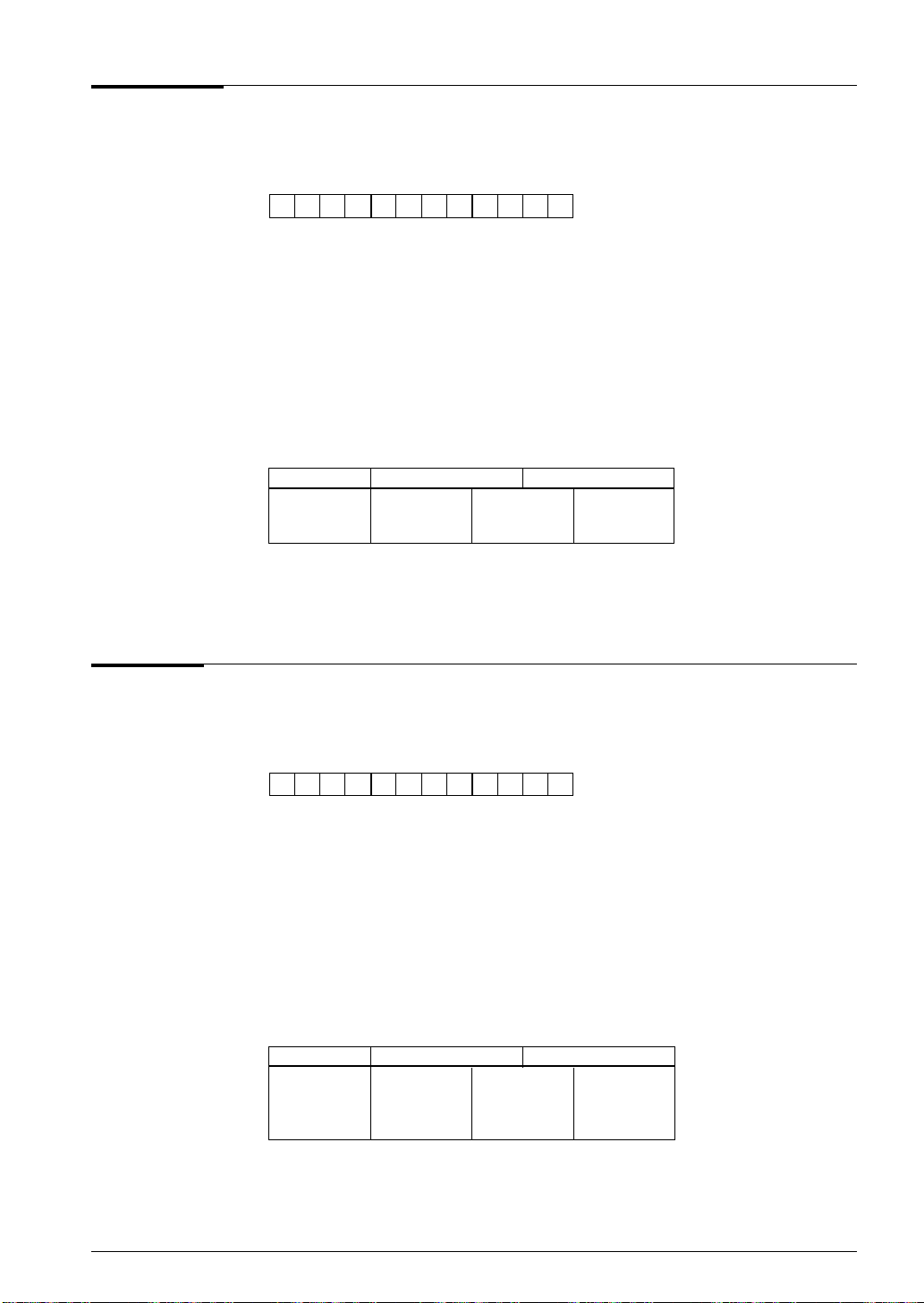

Comparison table between new and previous number

S1C60 Family processors

Previous No.

E0C6001

E0C6002

E0C6003

E0C6004

E0C6005

E0C6006

E0C6007

E0C6008

E0C6009

E0C6011

E0C6013

E0C6014

E0C60R08

New No.

S1C60N01

S1C60N02

S1C60N03

S1C60N04

S1C60N05

S1C60N06

S1C60N07

S1C60N08

S1C60N09

S1C60N11

S1C60N13

S1C60140

S1C60R08

S1C62 Family processors

Previous No.

E0C621A

E0C6215

E0C621C

E0C6S27

E0C6S37

E0C623A

E0C623E

E0C6S32

E0C6233

E0C6235

E0C623B

E0C6244

E0C624A

E0C6S46

New No.

S1C621A0

S1C62150

S1C621C0

S1C6S2N7

S1C6S3N7

S1C6N3A0

S1C6N3E0

S1C6S3N2

S1C62N33

S1C62N35

S1C6N3B0

S1C62440

S1C624A0

S1C6S460

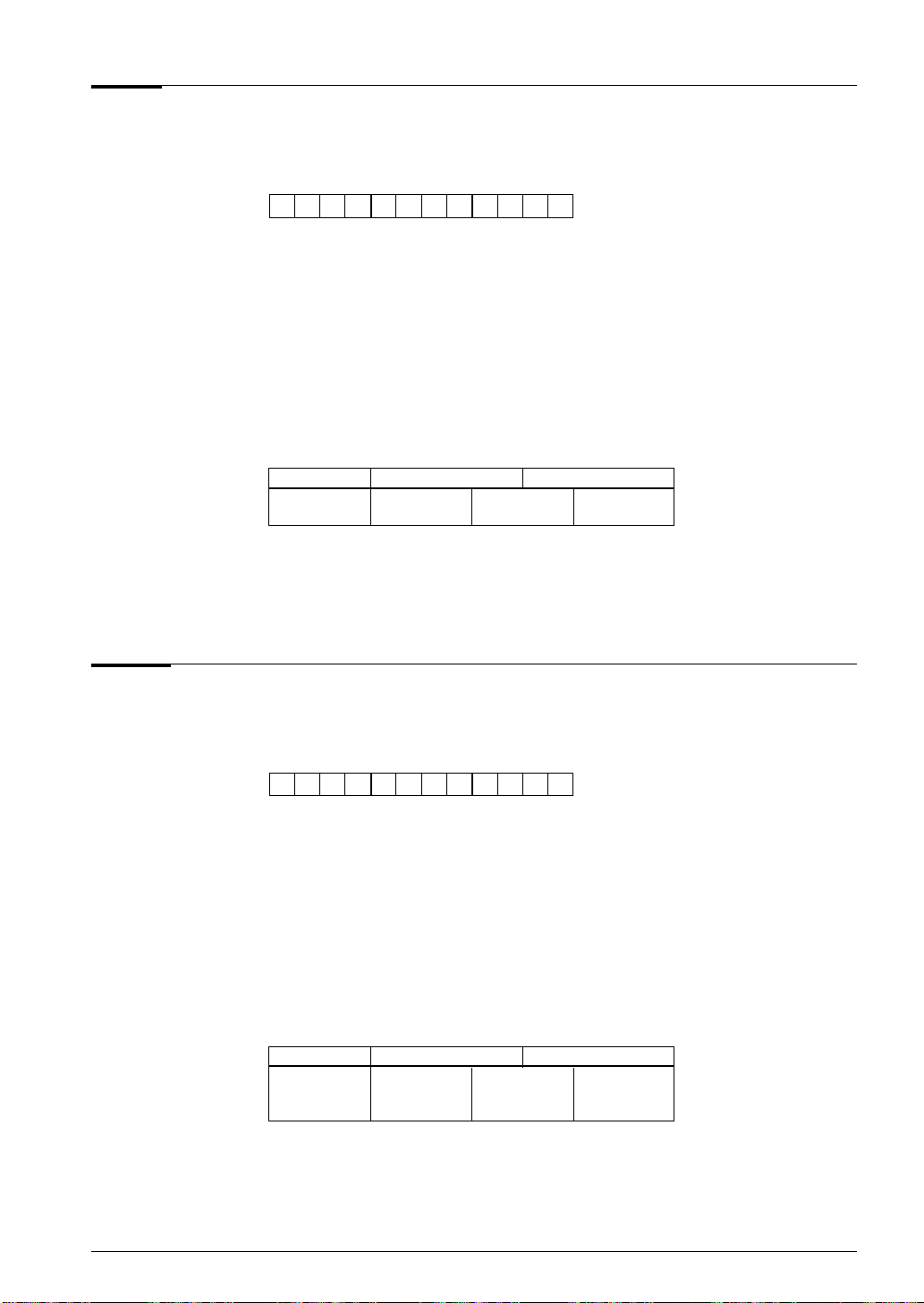

Previous No.

E0C6247

E0C6248

E0C6S48

E0C624C

E0C6251

E0C6256

E0C6292

E0C6262

E0C6266

E0C6274

E0C6281

E0C6282

E0C62M2

E0C62T3

New No.

S1C62470

S1C62480

S1C6S480

S1C624C0

S1C62N51

S1C62560

S1C62920

S1C62N62

S1C62660

S1C62740

S1C62N81

S1C62N82

S1C62M20

S1C62T30

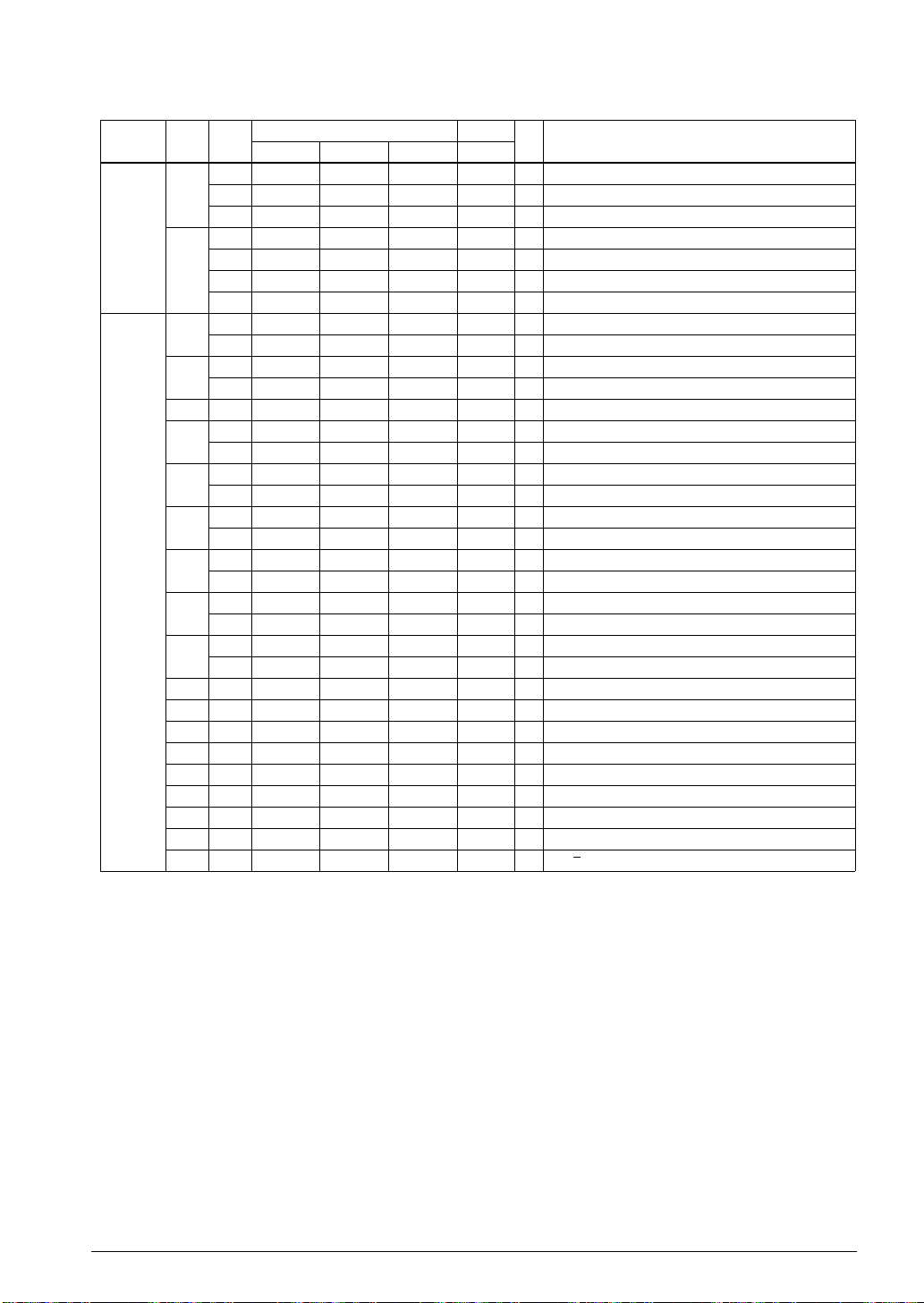

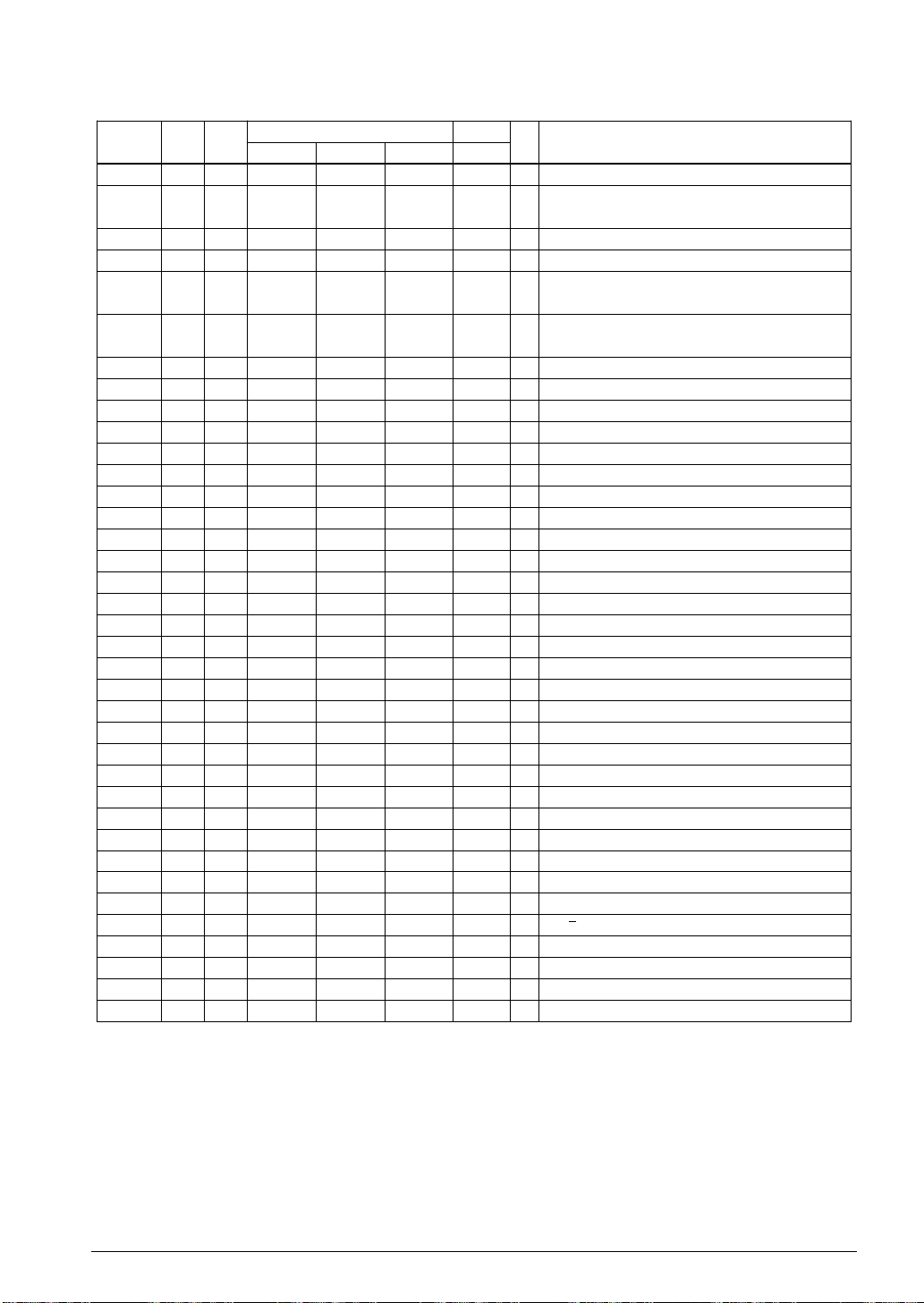

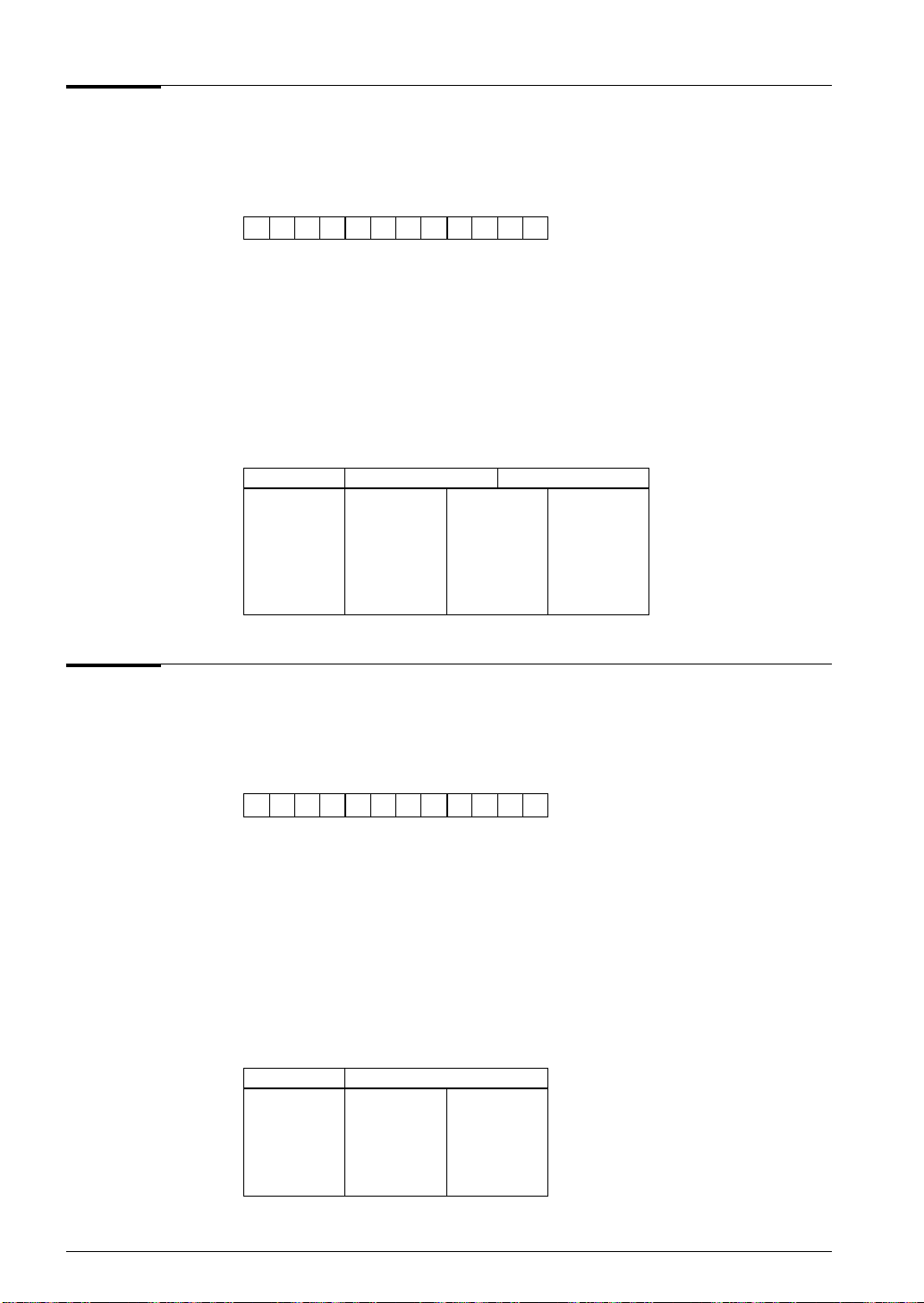

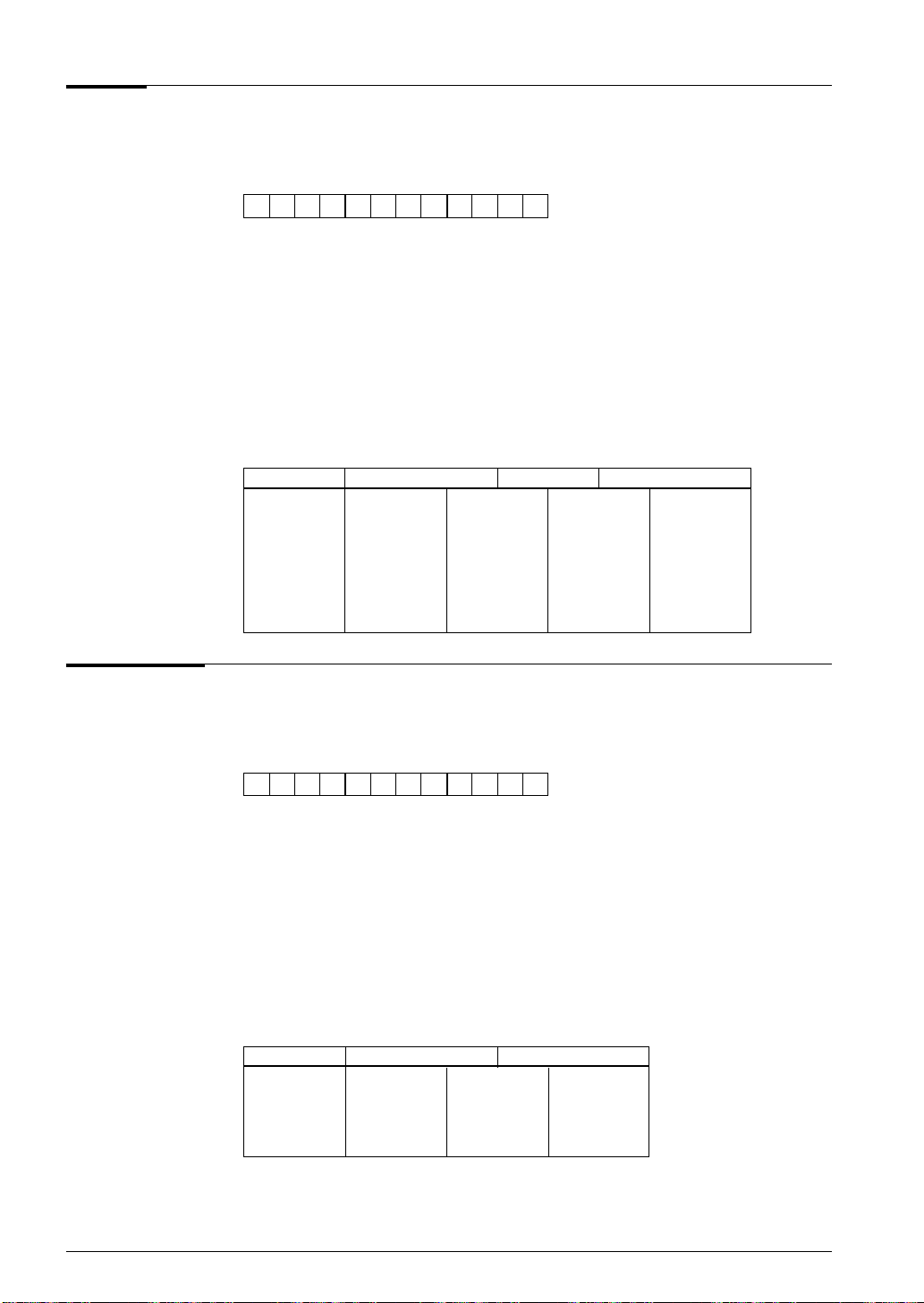

Comparison table between new and previous number of development tools

Development tools for the S1C60/62 Family

Previous No.

ASM62

DEV6001

DEV6002

DEV6003

DEV6004

DEV6005

DEV6006

DEV6007

DEV6008

DEV6009

DEV6011

DEV60R08

DEV621A

DEV621C

DEV623B

DEV6244

DEV624A

DEV624C

DEV6248

DEV6247

New No.

S5U1C62000A

S5U1C60N01D

S5U1C60N02D

S5U1C60N03D

S5U1C60N04D

S5U1C60N05D

S5U1C60N06D

S5U1C60N07D

S5U1C60N08D

S5U1C60N09D

S5U1C60N11D

S5U1C60R08D

S5U1C621A0D

S5U1C621C0D

S5U1C623B0D

S5U1C62440D

S5U1C624A0D

S5U1C624C0D

S5U1C62480D

S5U1C62470D

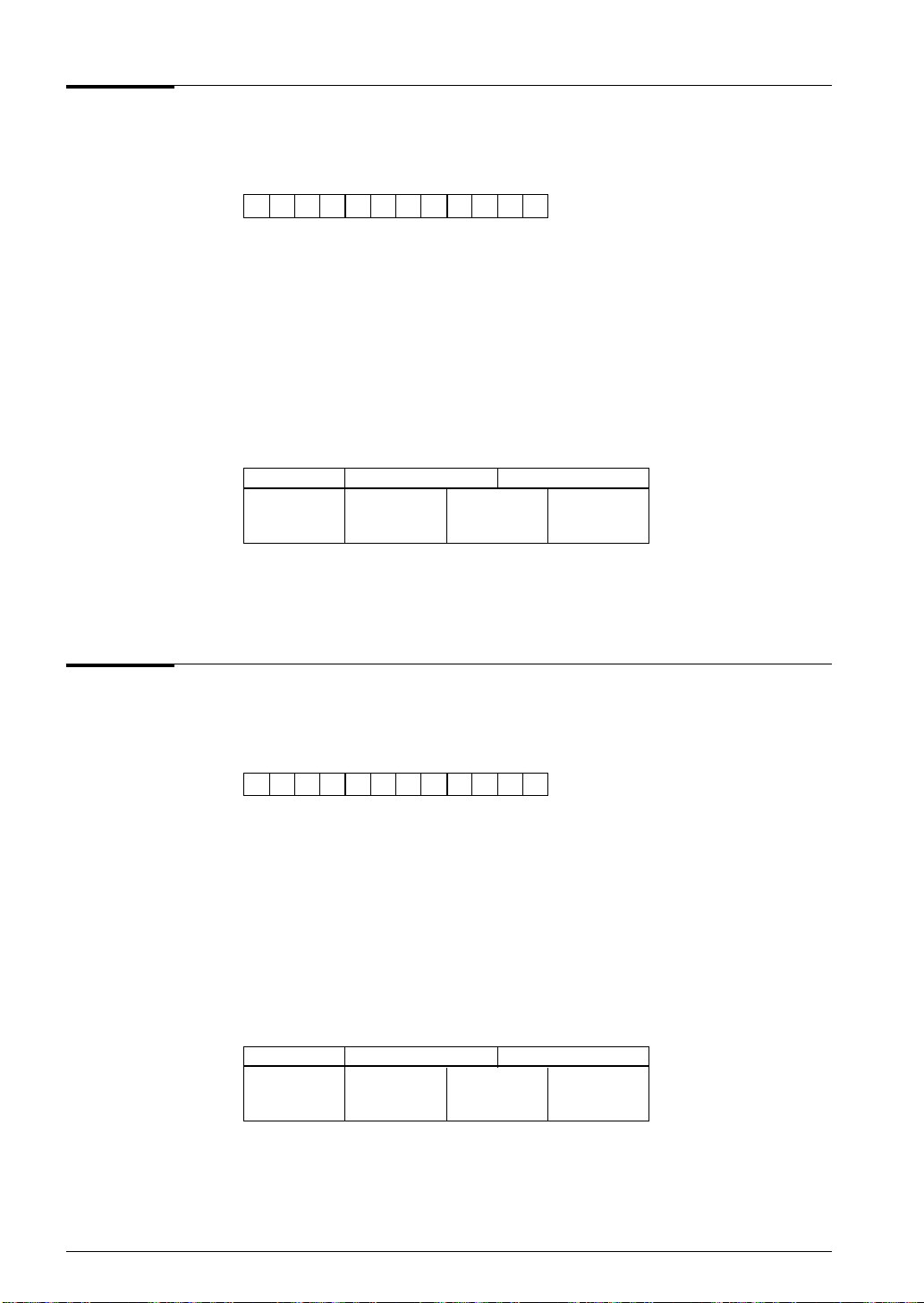

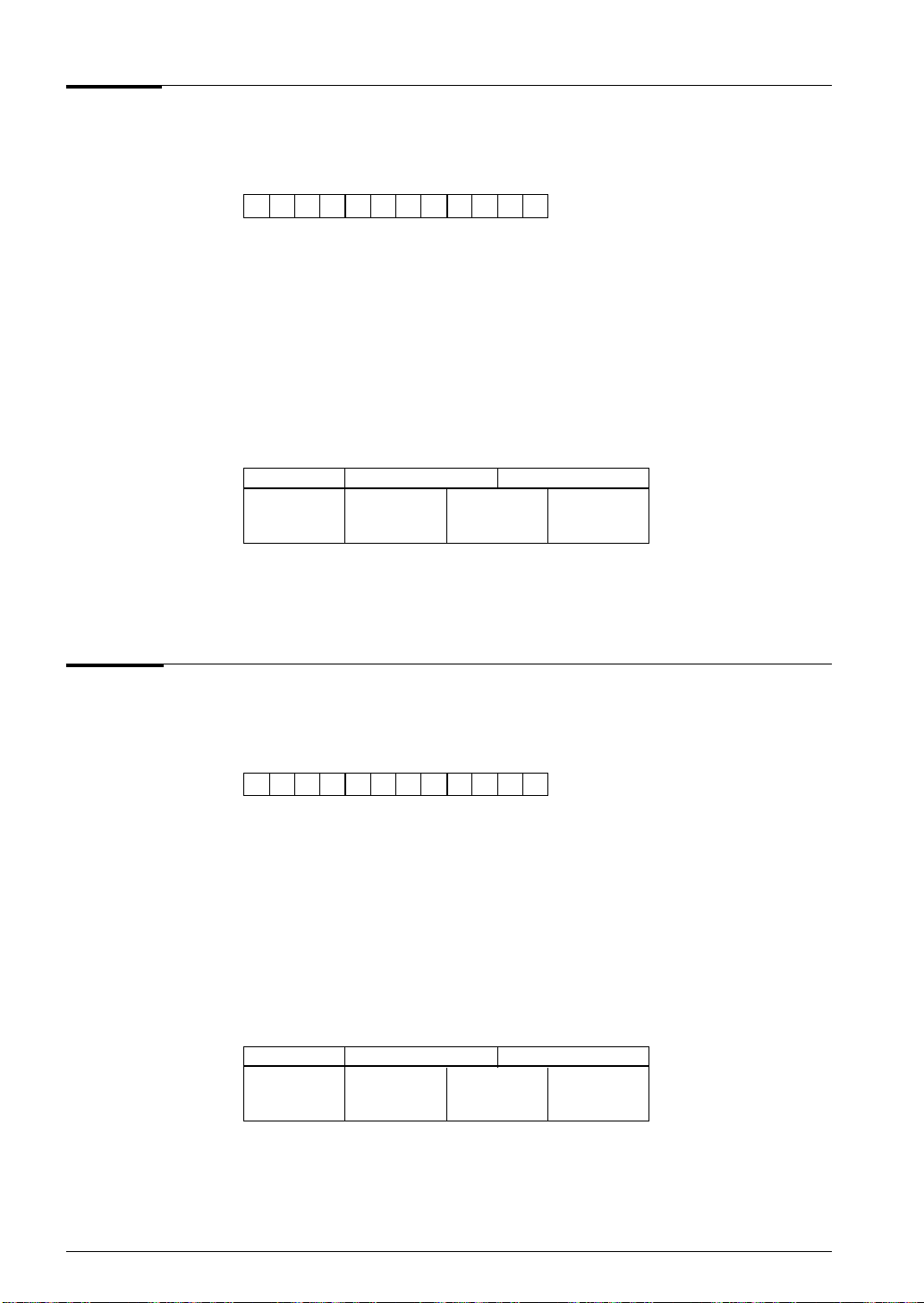

Previous No.

DEV6262

DEV6266

DEV6274

DEV6292

DEV62M2

DEV6233

DEV6235

DEV6251

DEV6256

DEV6281

DEV6282

DEV6S27

DEV6S32

DEV6S37

EVA6008

EVA6011

EVA621AR

EVA621C

EVA6237

EVA623A

New No.

S5U1C62620D

S5U1C62660D

S5U1C62740D

S5U1C62920D

S5U1C62M20D

S5U1C62N33D

S5U1C62N35D

S5U1C62N51D

S5U1C62560D

S5U1C62N81D

S5U1C62N82D

S5U1C6S2N7D

S5U1C6S3N2D

S5U1C6S3N7D

S5U1C60N08E

S5U1C60N11E

S5U1C621A0E2

S5U1C621C0E

S5U1C62N37E

S5U1C623A0E

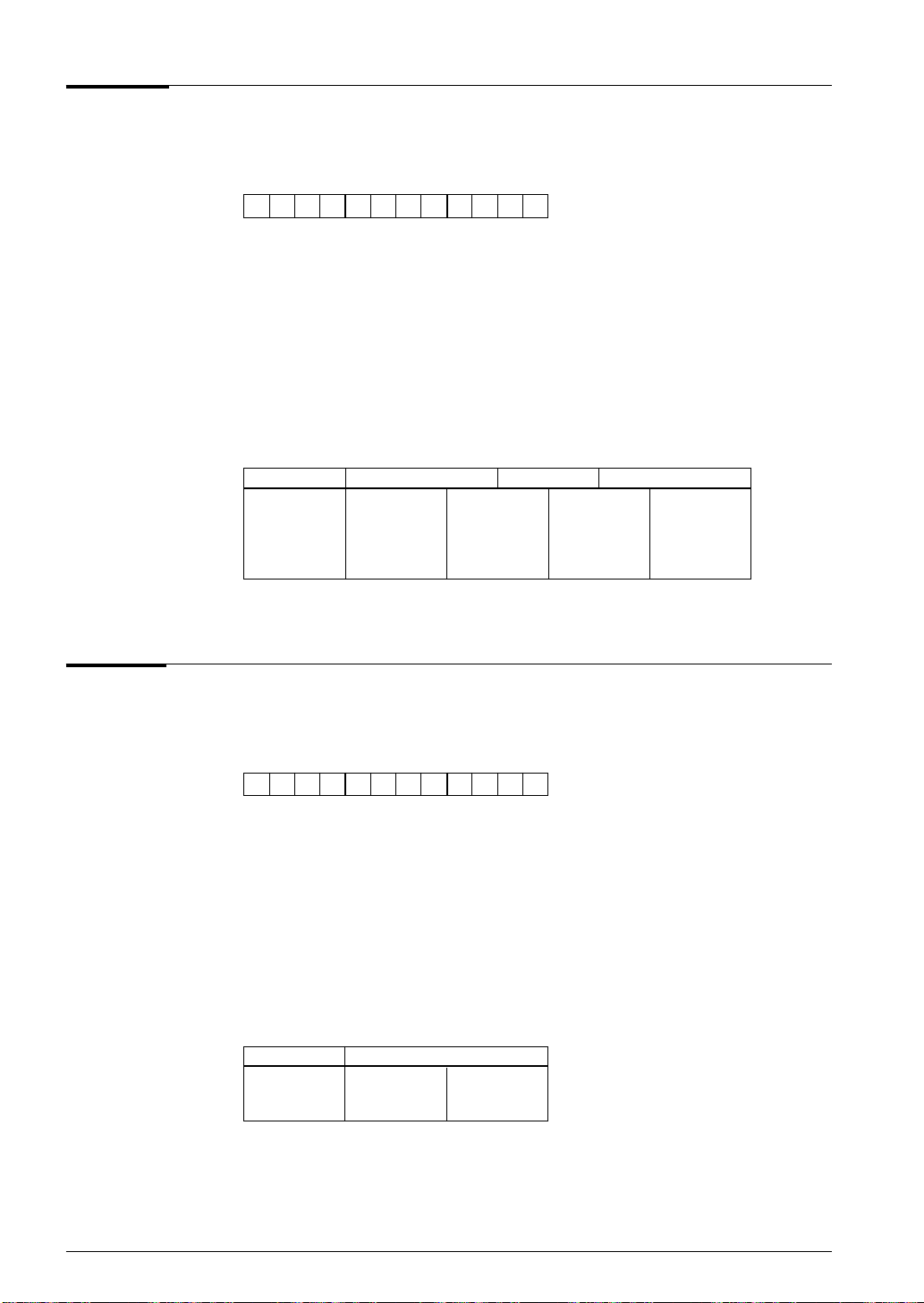

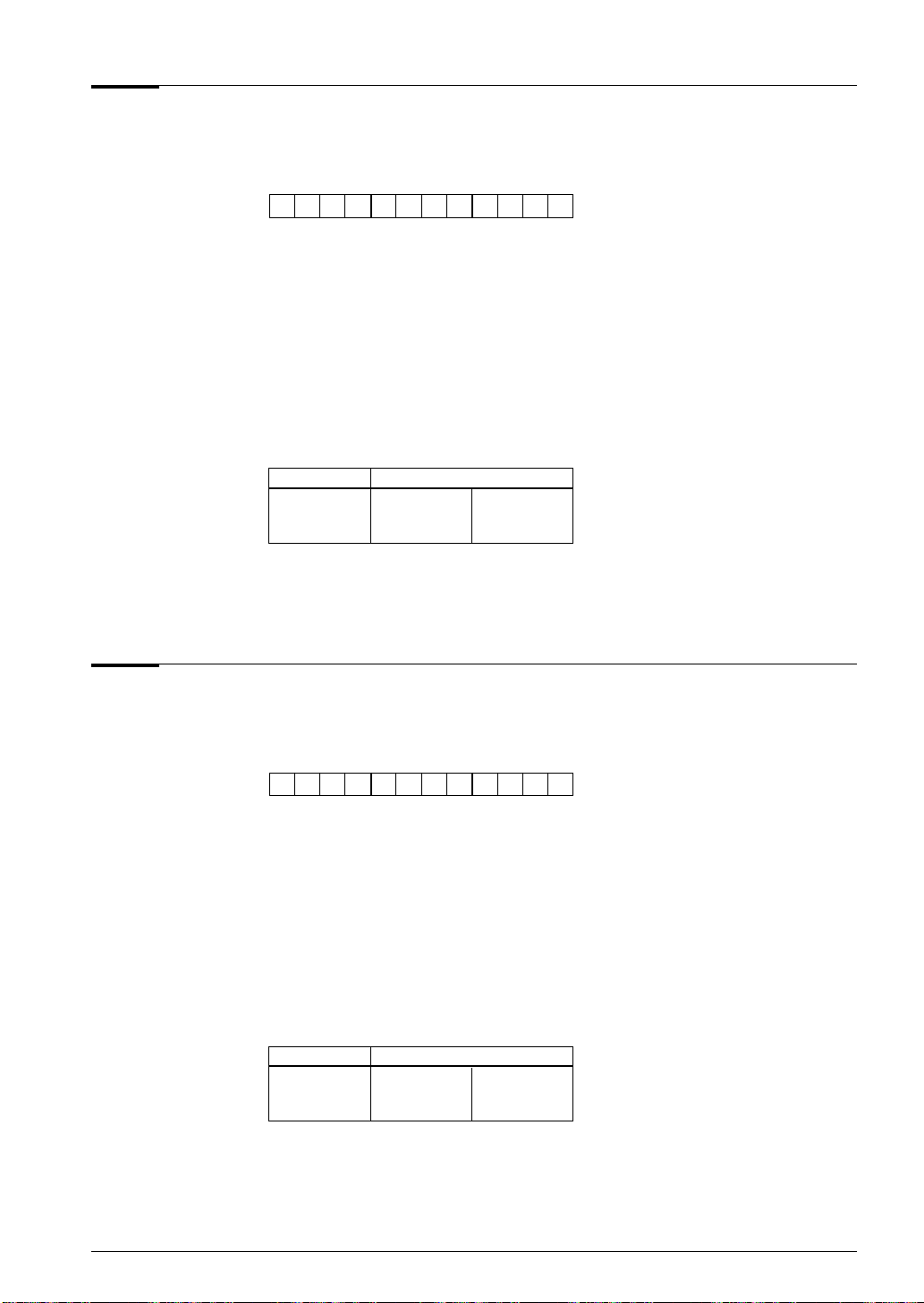

Previous No.

EVA623B

EVA623E

EVA6247

EVA6248

EVA6251R

EVA6256

EVA6262

EVA6266

EVA6274

EVA6281

EVA6282

EVA62M1

EVA62T3

EVA6S27

EVA6S32R

ICE62R

KIT6003

KIT6004

KIT6007

New No.

S5U1C623B0E

S5U1C623E0E

S5U1C62470E

S5U1C62480E

S5U1C62N51E1

S5U1C62N56E

S5U1C62620E

S5U1C62660E

S5U1C62740E

S5U1C62N81E

S5U1C62N82E

S5U1C62M10E

S5U1C62T30E

S5U1C6S2N7E

S5U1C6S3N2E2

S5U1C62000H

S5U1C60N03K

S5U1C60N04K

S5U1C60N07K

Page 4

Page 5

CONTENTS

S1C6200/6200A Core CPU Manual

CONTENTS

1DESCRIPTION ____________________________________________________ 1

1.1 System Features........................................................................................................1

1.2 Instruction Set Features ........................................................................................... 1

1.3 Differences between S1C6200 and S1C6200A.........................................................1

2MEMORY AND OPERATIONS __________________________________________ 3

2.1 Program Memory (ROM) ......................................................................................... 3

2.1.1 Program counter block............................................................................................ 4

2.1.2 Flags ........................................................................................................................ 4

2.1.3 Jump instructions..................................................................................................... 5

2.1.4 PSET with jump instructions ................................................................................... 5

2.1.5 Call instructions ...................................................................................................... 5

2.1.6 PSET instruction...................................................................................................... 6

2.1.7 CALZ instruction ..................................................................................................... 6

2.1.8 RET and RETS instructions ..................................................................................... 7

2.1.9 Stack considerations for call instructions ............................................................... 7

2.2 Data Memory............................................................................................................8

2.2.1 Data memory addressing......................................................................................... 8

2.3 ALU (Arithmetic Logic Unit) and Registers............................................................ 10

2.3.1 D (decimal) flag and decimal operations ............................................................... 10

2.3.2 A and B registers .................................................................................................... 11

2.4 Timing Generator .................................................................................................... 11

2.4.1 HALT and SLP (sleep) modes................................................................................. 11

2.5 Interrupts ................................................................................................................. 12

2.5.1 Interrupt vectors ..................................................................................................... 12

2.5.2 I (interrupt) flag...................................................................................................... 12

2.5.3 Operation during interrupt generation .................................................................. 12

2.5.4 Initial reset.............................................................................................................. 15

3INSTRUCTION SET_________________________________________________ 16

3.1 Instruction Indices ................................................................................................... 16

3.1.1 By function.............................................................................................................. 17

3.1.2 In alphabetical order .............................................................................................. 20

3.1.3 By operation code................................................................................................... 23

3.2 Operands .................................................................................................................26

3.3 Flags ........................................................................................................................26

3.4 Instruction Types ..................................................................................................... 27

3.5 Instruction Descriptions .......................................................................................... 27

APPENDIX A. S1C6200A (ADVANCED S1C6200) CORE CPU _________________ 84

B. INSTRUCTION INDEX ______________________________________ 87

S1C6200/6200A CORE CPU MANUAL EPSON i

Page 6

Page 7

1 DESCRIPTION

1DESCRIPTION

The S1C6200/6200A is the Core CPU of the S1C62 Family of CMOS 4-bit single-chip microcomputers. The CPU features a highly-integrated architecture. Memory-mapped peripheral circuits can include

RAM, ROM, I/O ports, interrupt controllers, timers and LCD drivers, depending upon the application.

The memory address space is divided into program and data memory, each with data and address lines.

Program memory consists of on-chip ROM, containing instructions to be executed by the CPU. Data

memory consists of RAM and memory-mapped I/O, as determined by the design of the peripheral circuitry.

A large memory as well as instructions capable of 8-bit data manipulation enhance the functionality of the

S1C62 Family. Implementation of a common Core CPU ensures that a wide range of application-specific

devices can be designed and fabricated with the minimum turnaround time.

1.1 System Features

• Common Core CPU for all S1C62 Family microcomputers

• UP to 8,192 12-bit words of program memory (ROM)

• UP to 4,096 4-bit words of data memory (RAM/peripheral circuits)

• Memory-mapped I/O

• 5, 7 or 12 clock cycle instructions

• 109 instructions

• Up to 85 levels of subroutine nesting

• 8-bit stack pointer

• Up to 15 interrupt vectors

• Two standby modes

• Low-power CMOS process

1.2 Instruction Set Features

• Four addressing modes: one direct, two indirect, and one stack pointer

• Direct addressing transfers data to and from data memory with a single instruction, resulting in more

efficient code

• 8-bit load instructions and table look-up instructions

• Arithmetic operations in either hexadecimal or decimal

• Arithmetic and logical instructions: addition, subtraction, logical AND, OR, exclusive-OR, comparison

and rotation

1.3 Differences between S1C6200 and S1C6200A

There are some differences in the following operation/circuit between the S1C6200 and the S1C6200A.

For the detailes of each difference, refer to the section enclosed with parentheses.

• Initial setting of D (decimal) flag (refer to Section 2.5.5, "Initial reset".)

• Interrupt circuit

– Interrupt timing (refer to Section 2.5.3, "Operation during interrupt generation".)

– Writing to interrupt mask registers and reading of interrupt flags (refer to Appendix A, "S1C6200A

(Advanced S1C6200) Core CPU".)

S1C6200/6200A CORE CPU MANUAL EPSON 1

Page 8

1 DESCRIPTION

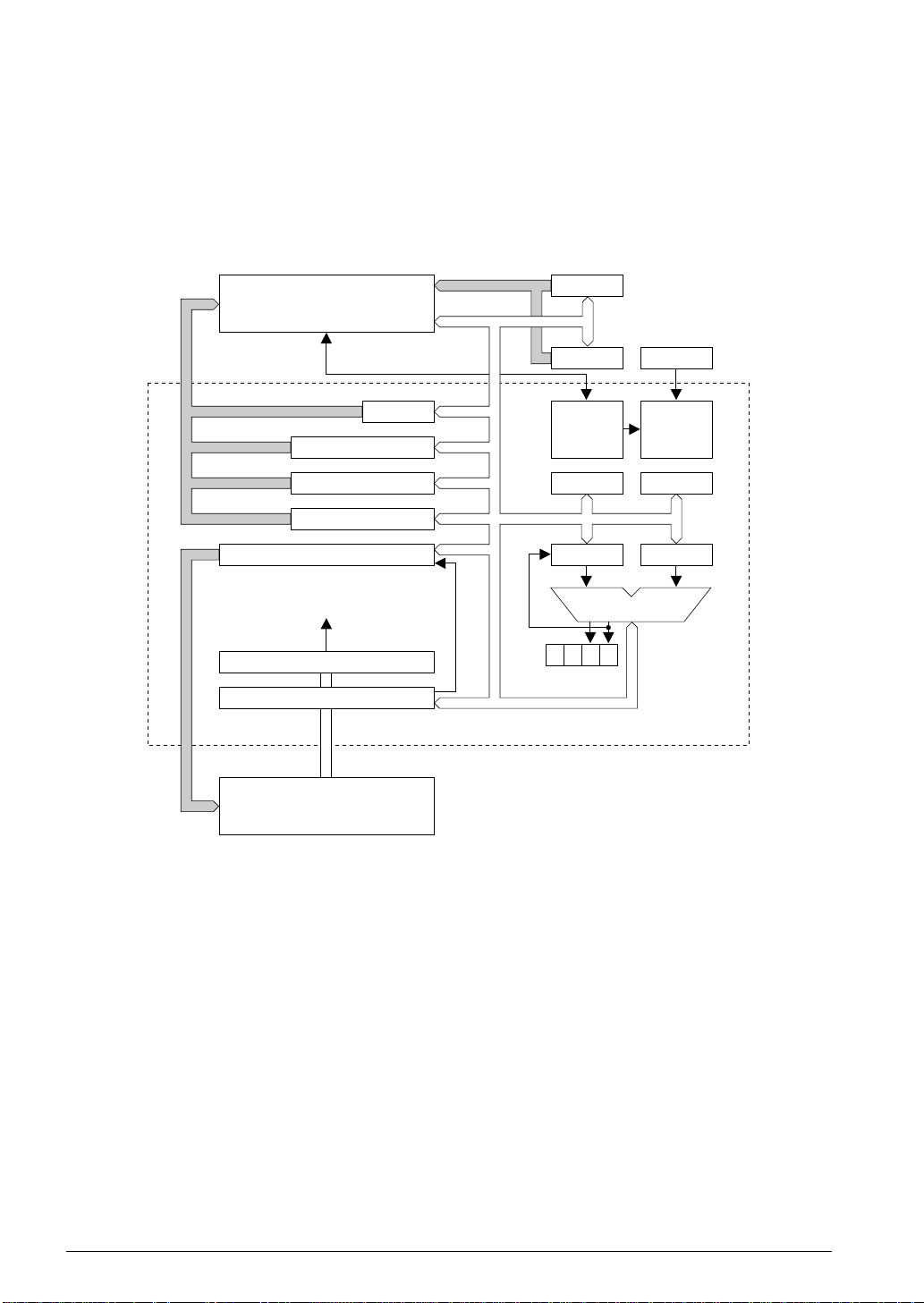

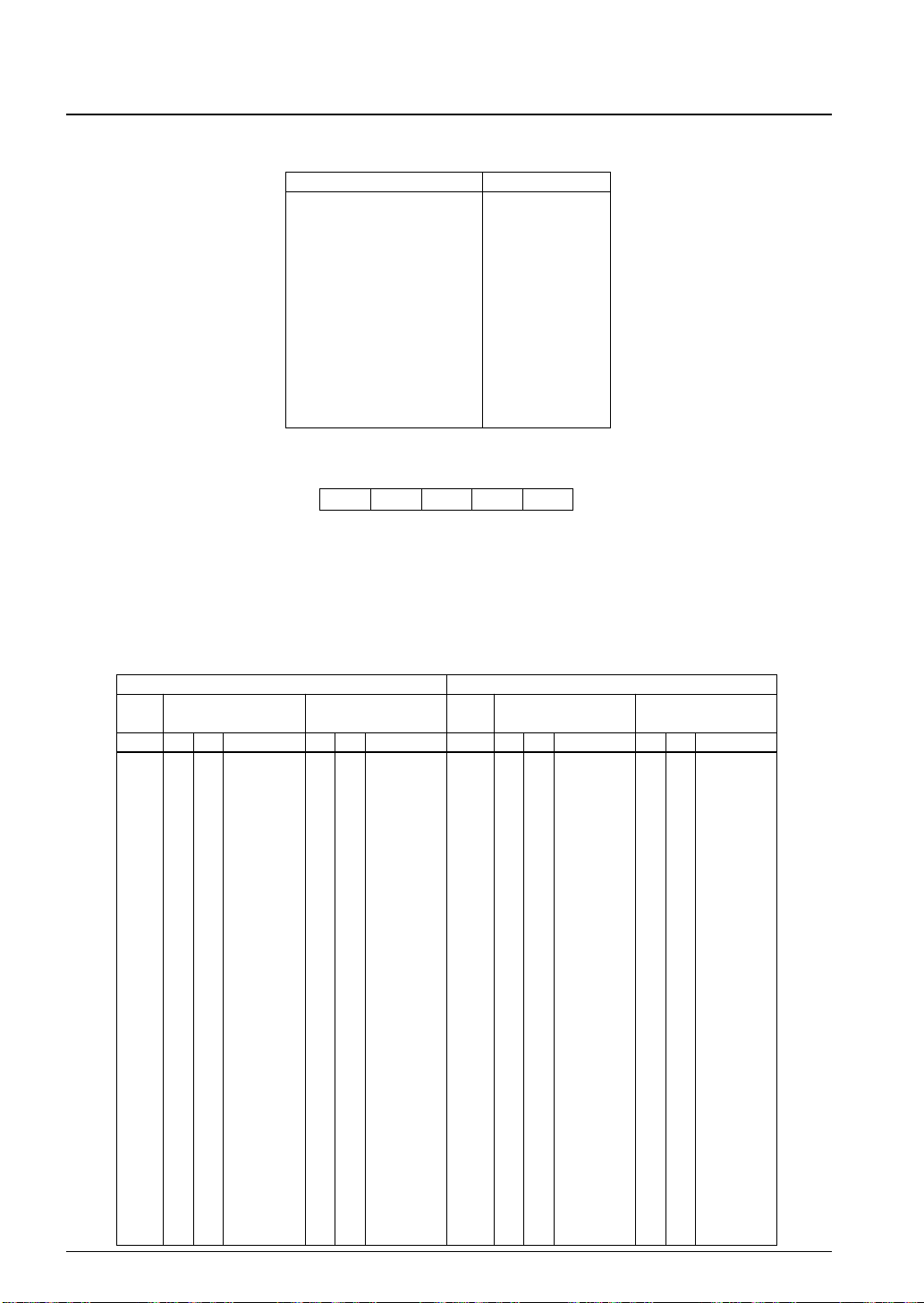

RAM, Peripheral I/O

(4,096 4-bit words max.)

8-bit address bus13-bit address bus

Program Counter Block

Micro-Instructions

Instruction Decorder

Instruction Register (12)

Program Memory

(8,192 12-bit words max.)

Data Memory

YHL (8)

XHL (8)

Stack Pointer (8)

12-bit data bus

ROM

RP (4)

4-bit address bus

4-bit data bus

XP (4)

YP (4)

Interrupt

Controller

A (4)

TEMPB (5)

I DZC

Oscillator

Timing

Generator

B (4)

TEMPA (5)

ALU

S1C6200 CORE CPU

Fig. 1.1 Block diagram

2 EPSON S1C6200/6200A CORE CPU MANUAL

Page 9

2 MEMORY AND OPERATIONS

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;;;;;;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;;;;;;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;;;

2MEMORY AND OPERATIONS

A single-chip microcomputer using the S1C6200/6200A Core CPU has four major blocks: the

program memory (ROM), the data memory (RAM and I/O), the arithmetic logic unit (ALU) and the timing

generator circuit. This section describes each of these blocks in detail.

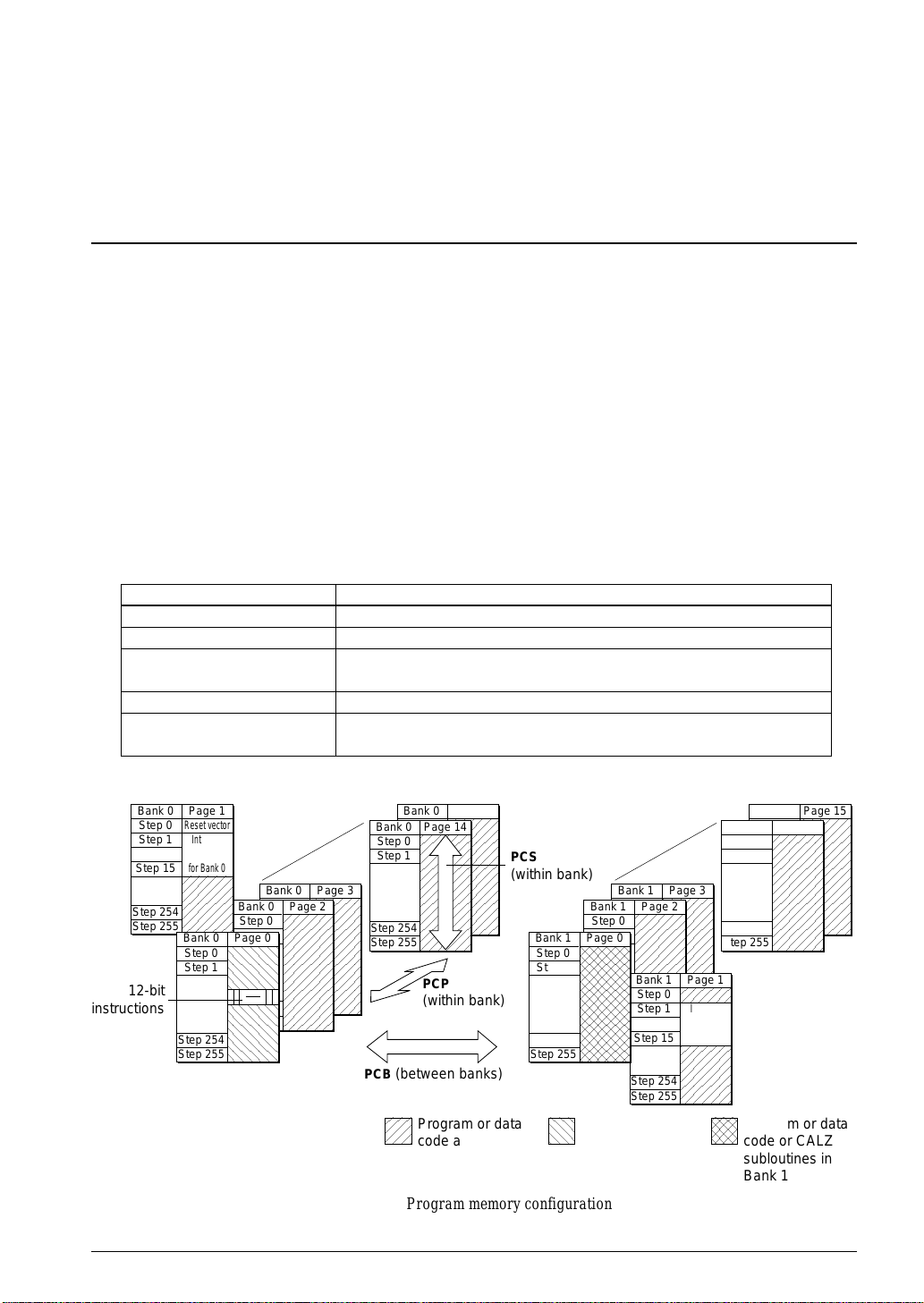

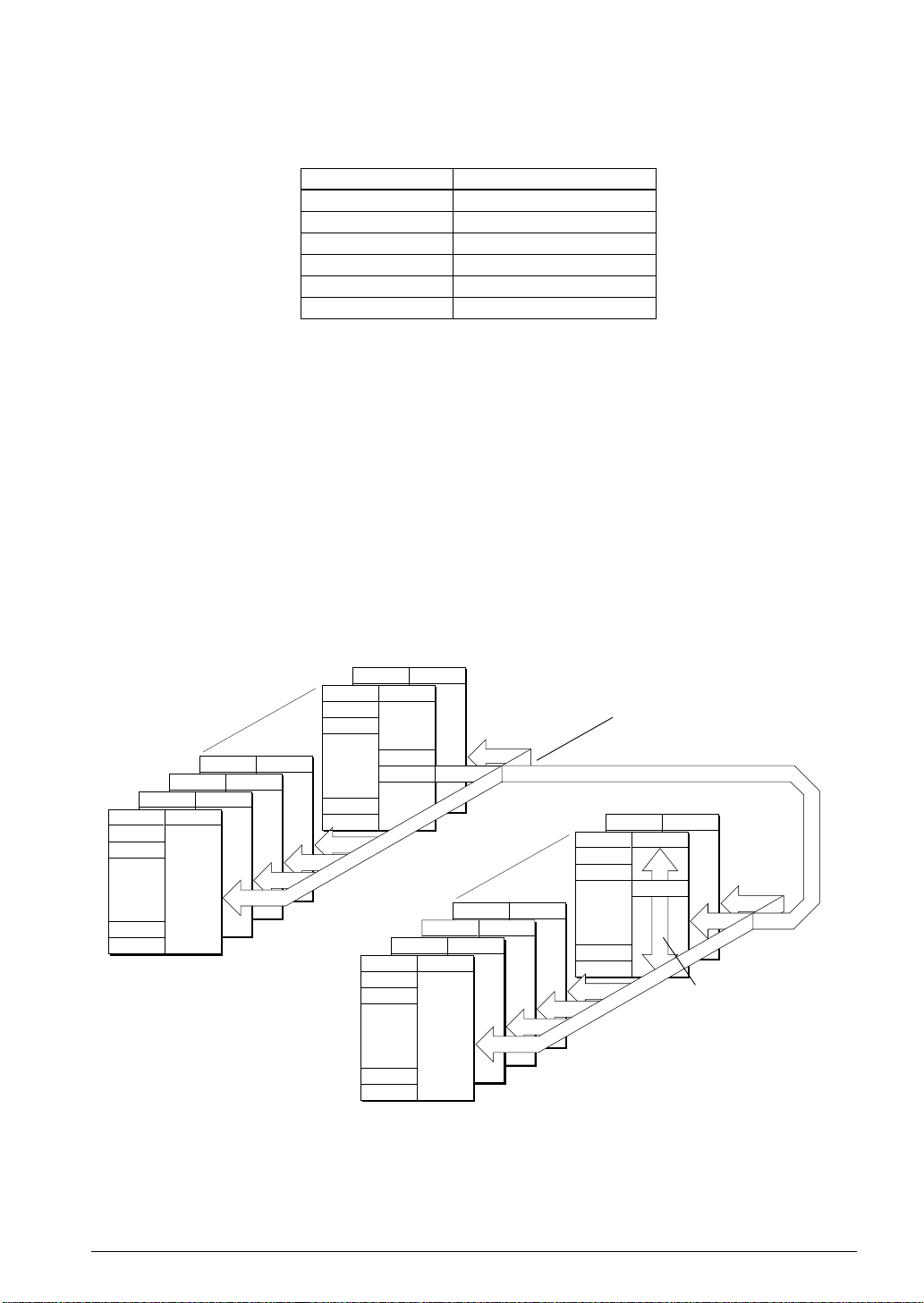

2.1 Program Memory (ROM)

Program memory contains the instructions that the CPU executes. Figure 2.1.1 shows the configuration of

the program memory.

Each instruction is a 12-bit word. Program memory can also be used for data tables for the table look-up

instructions.

There are two banks of program memory. Each bank is subdivided into 16 pages of 256 words (or steps).

That is:

Program memory = 2 banks

= 8,192 steps

1 bank = 4,096 steps

= 16 pages

1 page = 256 steps

1 step = 1 word

= 12 bits

Certain addresses in ROM have specific functions, as shown in Table 2.1.1.

Table 2.1.1 Allocated program memory

Address Function

Bank 0, Page 1, Step 0

Bank 0, Page 1, Step 1 to 15

Bank 0, Page 0, Step 0 to 255

Bank 1, Page 1, Step 1 to 15

Bank 1, Page 0, Step 0 to 255

Reset vector

Interrupt vectors used while a program is running in bank 0

Bank 0, page 0 area

Direct call subroutines for use by CALZ while a program is running in bank 0

Interrupt vectors used while a program is running in bank 1

Bank 1, page 0 area

Direct call subroutines for use by CALZ while a program is running in bank 1

Page 1

Bank 0

Step 0

Step 1

Step 15

Step 254

Step 255

12-bit

instructions

Reset vector

Interrupt

vectors

for Bank 0

;;;;

;;;;

;;;;

;;;;

;;;;

;;;;

Bank 0

Step 0

Step 1

Step 254

Step 255

Page 0

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

Bank 0 Bank 1

Bank 0

Step 0

Step 1

Page 3

Bank 0

Page 2

Bank 0

Step 0

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

Step 254

Step 255

PCB (between banks)

;;

;;

S1C6200/6200A CORE CPU MANUAL EPSON 3

Fig. 2.1.1 Program memory configuration

Page 15

Bank 0

Page 14

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

PCP

(within bank)

Program or data

code area

PCS

(within bank)

Bank 1

Step 0

Step 1

Step 254

Step 255

;;

;;

Bank 1

Step 0

Page 0

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;

;;;;

;;;;

;;;;

;;;;

;;;;

;;;;

Bank 1

;;;;

Step 0

;;;;

;;;;

Step 1

;;;;

;;;;

Step 15

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

Page 3

Bank 1

Page 2

Step 254

Step 255

Program or data

code or CALZ

subloutines in

Bank 0

Page 1

;;;;;

;;;;;

Interrupt

;;;;;

;;;;;

vectors

;;;;;

for Bank 1

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;

;;

Bank 1

Step 0

Step 1

Step 254

Step 255

Program or data

code or CALZ

subloutines in

Bank 1

Bank 1

Page 14

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

Page 15

;;;;

;;;;

;;;;

;;;;

;;;;

;;;;

;;;;

;;;;

;;;;

;;;;

;;;;

;;;;

Page 10

2 MEMORY AND OPERATIONS

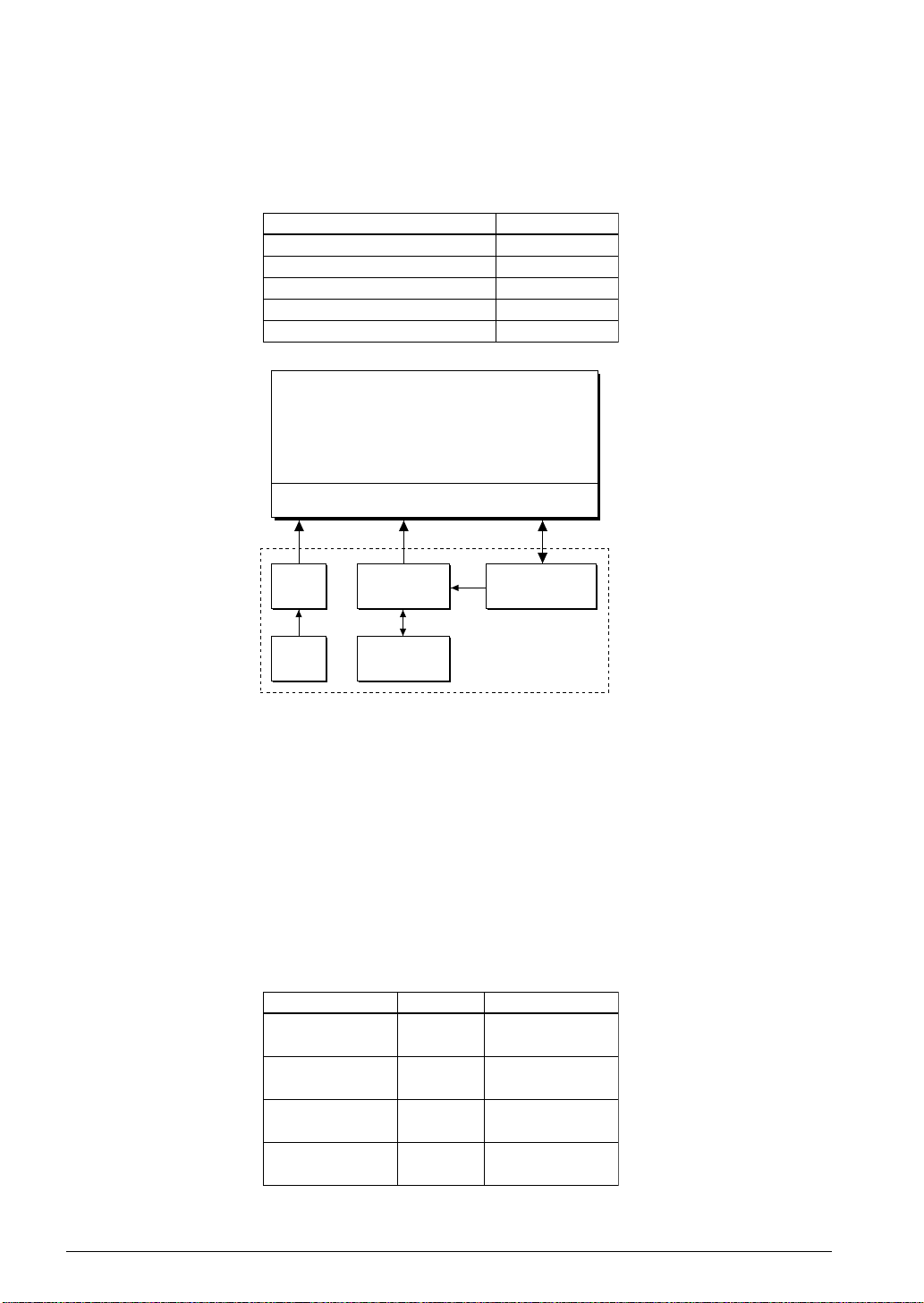

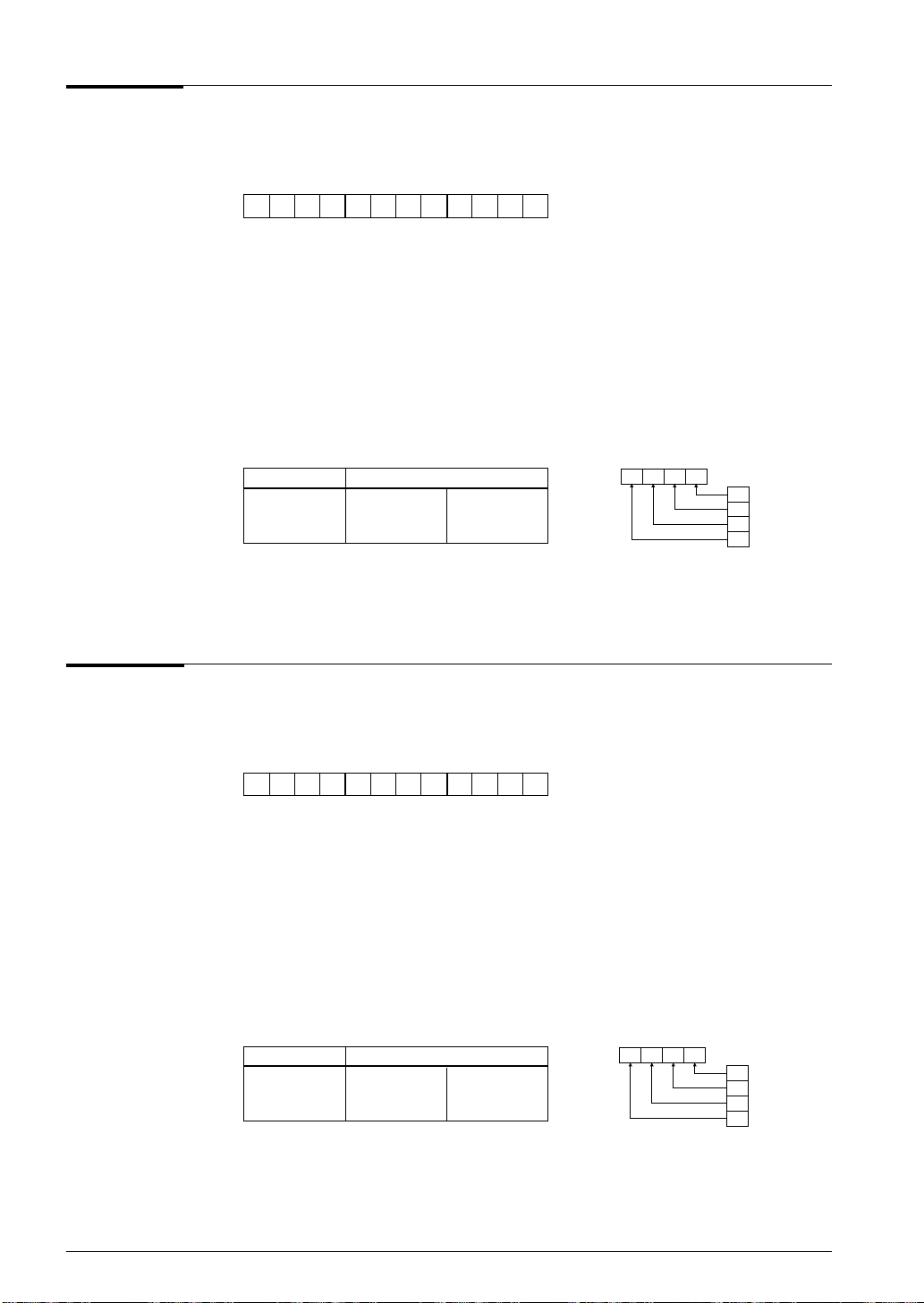

2.1.1 Program counter block

The program counter is used to point to the next instruction step to be executed by the CPU. See Figure

2.1.1.1.

The program counter has the following registers.

Table 2.1.1.1 Program counter registers

Register Size

PCB (Program Counter-Bank)

PCP (Program Counter-Page)

PCS (Program Counter-Step)

NBP (New Bank Pointer)

NPP (New Page Pointer)

Program memory

(8,192 12-bit words max.)

Address decoder

1-bit register

4-bit counter

8-bit counter

1-bit register

4-bit register

PCB

(1)

NBP

(1)

PCP

(4)

NPP

(4)

PCS

(8)

Program counter block

Fig. 2.1.1.1 Program counter configuration

PCB, PCP and PCS together from a 13-bit counter which can address any location in program memory.

PCP and PCS together from a 12-bit counter which can address any location within a given bank of pro-

gram memory. Each time an instruction other than a jump is executed, this counter increments by one.

Thus, a jump instruction does not need to be executed between the last step of one page and the first step of

the next.

The contents of NBP and NPP are loaded into PCB and PCP each time an instruction is executed. On reset,

NBP and NPP are loaded with the same values as PCB and PCP.

2.1.2 Flags

The following flags are provided.

Table 2.1.2.1 Flags

Flag Size

Interrupt

Decimal mode

Zero

Carry

Menus

I

D

Z

C

1: Enabled

0: Disabled

1: Decimal

0: Hexadecimal

1: Set

0: Ignored

1: Set

0: Ignored

4 EPSON S1C6200/6200A CORE CPU MANUAL

Page 11

2 MEMORY AND OPERATIONS

2.1.3 Jump instructions

A jump can be made using the instructions in Table 2.1.3.1.

Table 2.1.3.1 Jump instructions

Type of jump Instruction

Unconditional

Conditional

Subroutine call

Return

Page set

Indirect

JP

JP C, JP NC, JP Z, JP NZ

CALL, CALZ

RET, RETS, RETD

PSET

JPBA

The differences between jumps within the same page and jumps from one page to another is as follows.

• Jumps within the same page

A jump can be made within the same page using any of the following instructions:

JP, JP C, JP Z, JP NZ, JPBA or CALL

The destination address is specified by the 8-bit operand. A label can be used to specify a destination

address with the S1C62 Family cross assembler.

• Jumps from one page to another

The destination bank and page should be set using PSET before executing a JP instruction.

2.1.4 PSET with jump instructions

PSET loads the four low-order bits (page part) of its 5-bit operand to NPP (new page pointer) and loads the

high-order bit (bank part) to NBP (new bank pointer). Executing a JP instruction immediately after PSET

causes a jump to the bank specified by NBP, the page specified by NPP and the step specified by the JP

instruction operand. See Figure 2.1.4.1.

Page 14

PSET

JUMP

Step 0

Step 1

Page 15Bank 0

Jump with PSET can go anywhere

within the program memory

Jump can go between banks

Bank 1

Page 3Bank 1

Page 2Bank 1

Page 1Bank 1

Page 0Bank 1

Bank 1

Step 0

Step 1

Step 254

Step 255

Page 15Bank 1

Page 14

JUMP

Jump without PSET

can go anywhere

Step 0

Step 1

Step 254

Step 255

Bank 0

Page 3Bank 0

Page 2Bank 0

Page 1Bank 0

Page 0Bank 0

Bank 0

Step 0

Step 1

Step 254

Step 255

within one page

Step 254

Step 255

Fig. 2.1.4.1 The PSET and jump instructions

2.1.5 Call instructions

As only the page data specified by NPP is loaded to PCP when a call instruction is executed, subroutine

calls between banks are not possible. Jumps between banks can only be made using JP instructions.

S1C6200/6200A CORE CPU MANUAL EPSON 5

Page 12

2 MEMORY AND OPERATIONS

2.1.6 PSET instruction

Jump or call instructions must follow PSET immediately in order for PSET to affect the destination address.

When a jump or call is not immediately preceded by PSET, the destination address is within the current

page.

Some examples using PSET are shown in Table 2.1.6.1.

Table 2.1.6.1 PSET examples

Bank Page Stap Instruction

PSET

JP

PSET

NOP5

JP

SCF

PSET

JP

RFC

PSET

JP

JP

13H

08H

•

•

15H

09H

•

•

14H

C, 07H

•

•

05H

C, 08H

09H

•

•

0

01H

10H

0

01H

11H

•

•

•

•

•

•

0

01H

21H

0

01H

22H

0

01H

23H

•

•

•

•

•

•

0

01H

55H

0

01H

56H

0

01H

57H

•

•

•

•

•

•

0

01H

60H

0

01H

61H

0

01H

62H

0

01H

63H

•

•

•

•

•

•

The program jumps to bank 1, page 3, step 8.

The data set by PSET is canceled.

The program jumps to bank 0, page 1, step 9.

C flag is set.

The program jumps to bank 1, page 4, step 7 because C flag = 1.

C flag is reset.

No jump occurs because C flag = 0.

The data set by PSET is canceled, and the program jumps to bank 0, page 1, step 9.

Operation

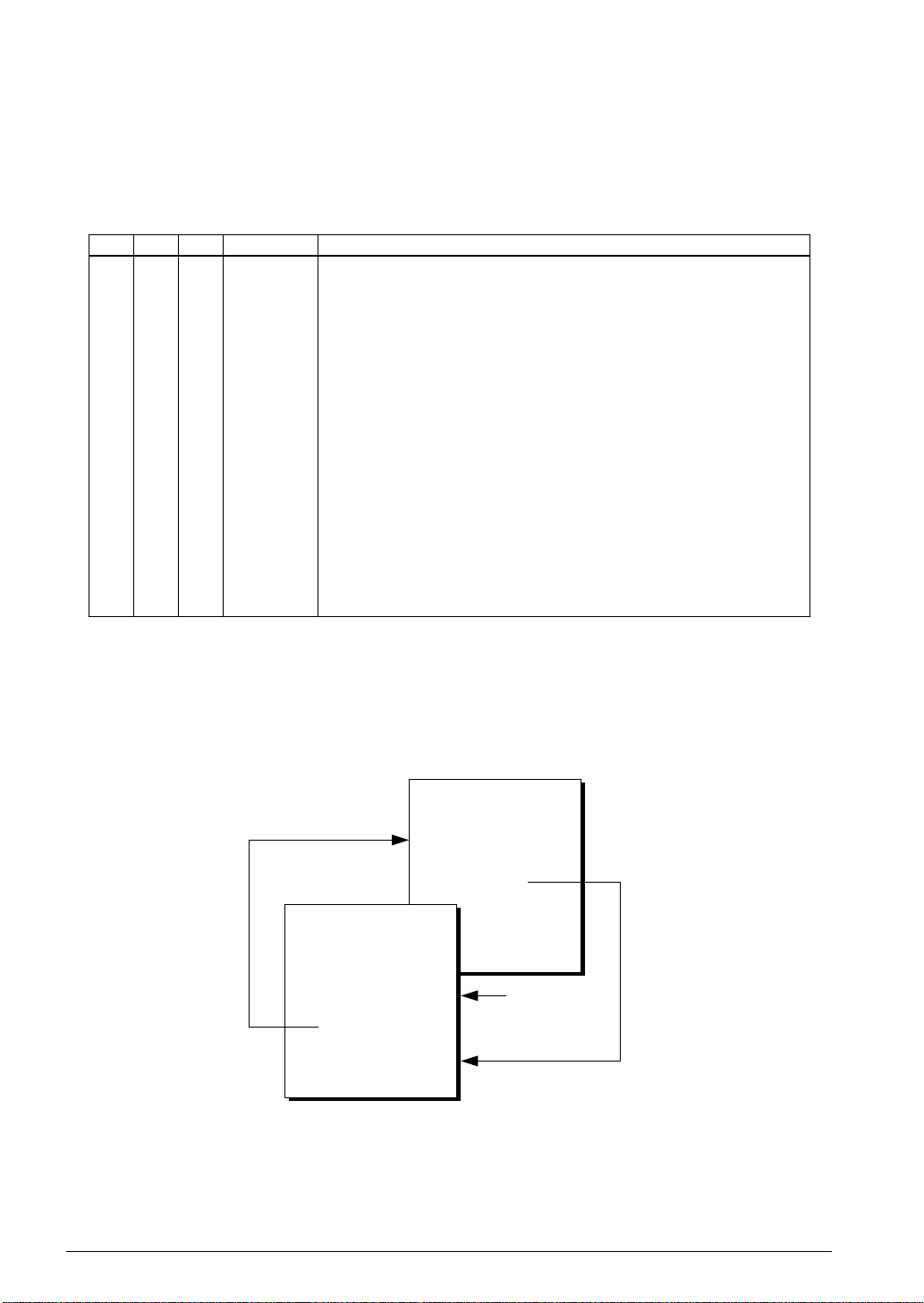

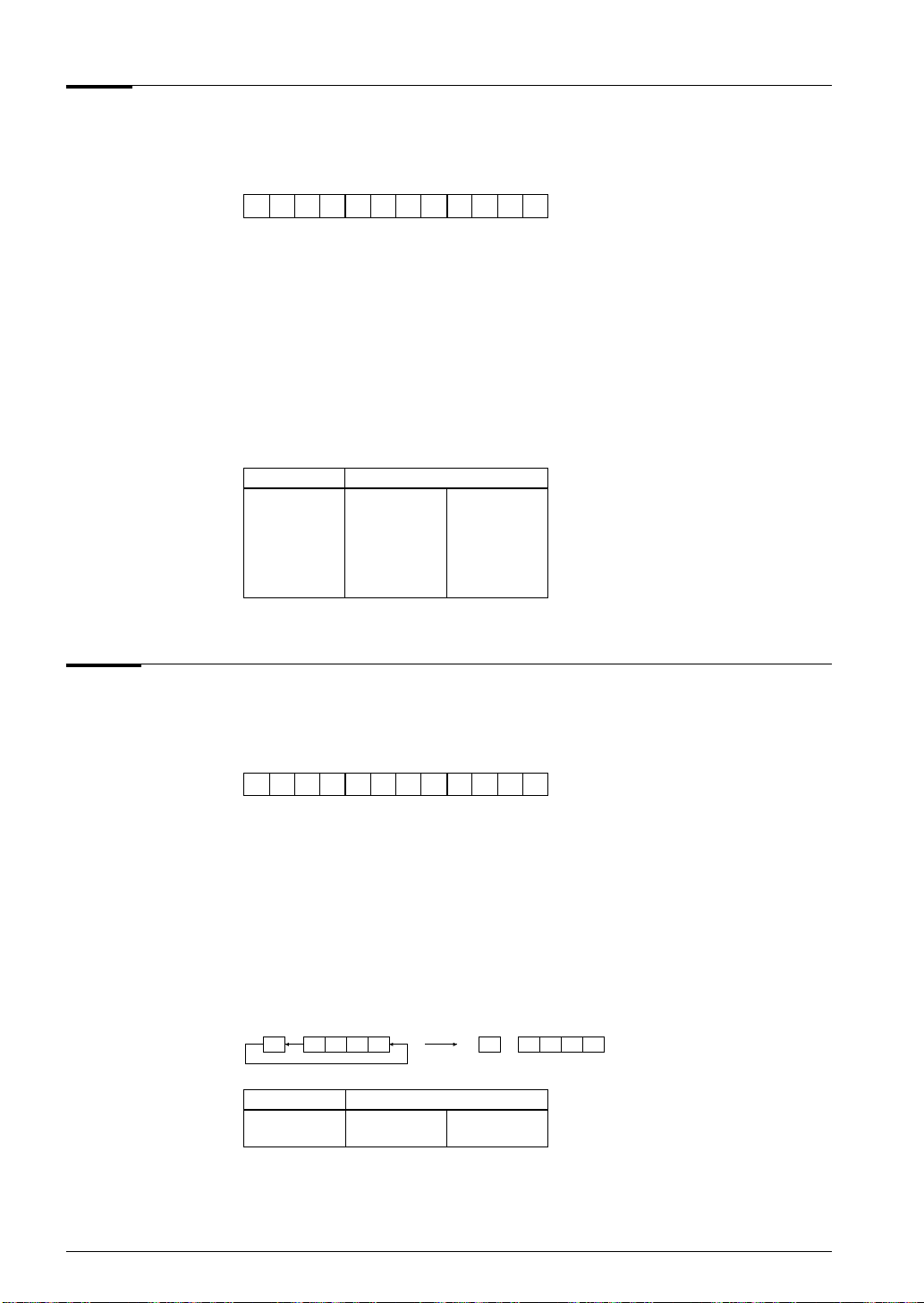

2.1.7 CALZ instruction

CALZ is a direct subroutine call instruction. It calls a subroutine, in page 0 of the current bank, from any

page without requiring the use of PSET.

If CALZ is executed immediately after PSET, the bank and page set by PSET is canceled. This allows direct

subroutine calls to page 0, minimizing repeated code and unnecessary use of PSET. See Figure 2.1.7.1.

Bank 0 Page 0

EEE....................

RET

Bank 0 Page 2

PSET

CALZ

LD

0AH

EEE

A,0

Fig. 2.1.7.1 The use of the CALZ instruction

Not effect

on destination

of CALZ

6 EPSON S1C6200/6200A CORE CPU MANUAL

Page 13

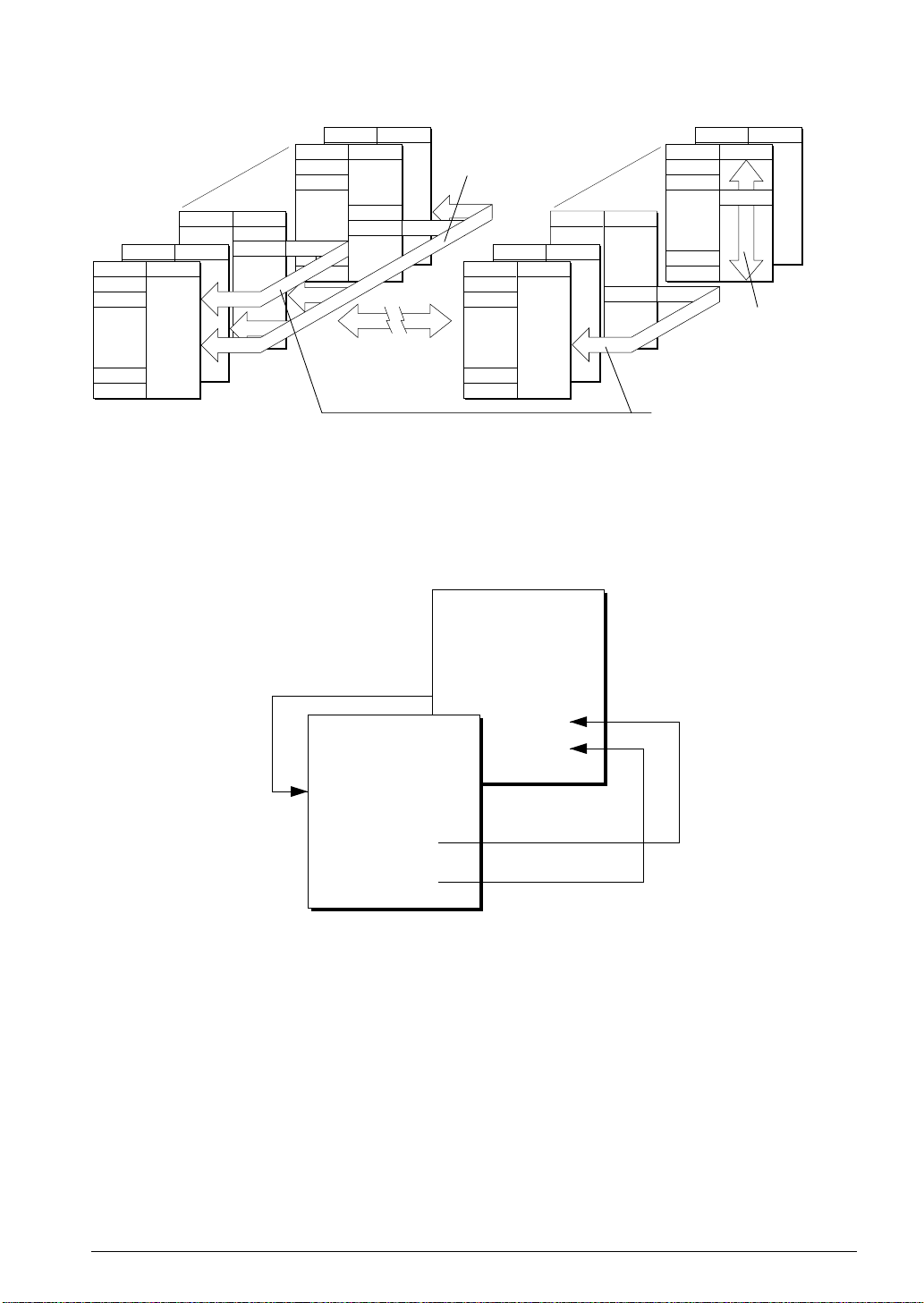

The difference between CALL and CALZ is shown in Figure 2.1.7.2.

2 MEMORY AND OPERATIONS

CALL with PSET

can go anywhere

within a bank

Bank 1

Page 1Bank 1

Page 0Bank 1

Step 0

Step 1

Page 3

CALZ

Bank 1

Step 0

Step 1

Step 254

Step 255

Page 15Bank 1

Page 14

CALL

Step 0

Step 1

Bank 0 Bank 1

Bank 0

Page 3

Page 1Bank 0

Page 0Bank 0

CALZ

Bank 0

Step 0

Step 1

Step 254

Step 255

Page 15Bank 0

Page 14

PSET

CALL

CALL without PSET

can go anywhere

in a page

Step 254

Step 255

CALL and CALZ

cannot go

between banks

Step 254

Step 255

CALZ can only go to page 0

of the current bank

Fig. 2.1.7.2 The difference between CALL and CALZ instructions

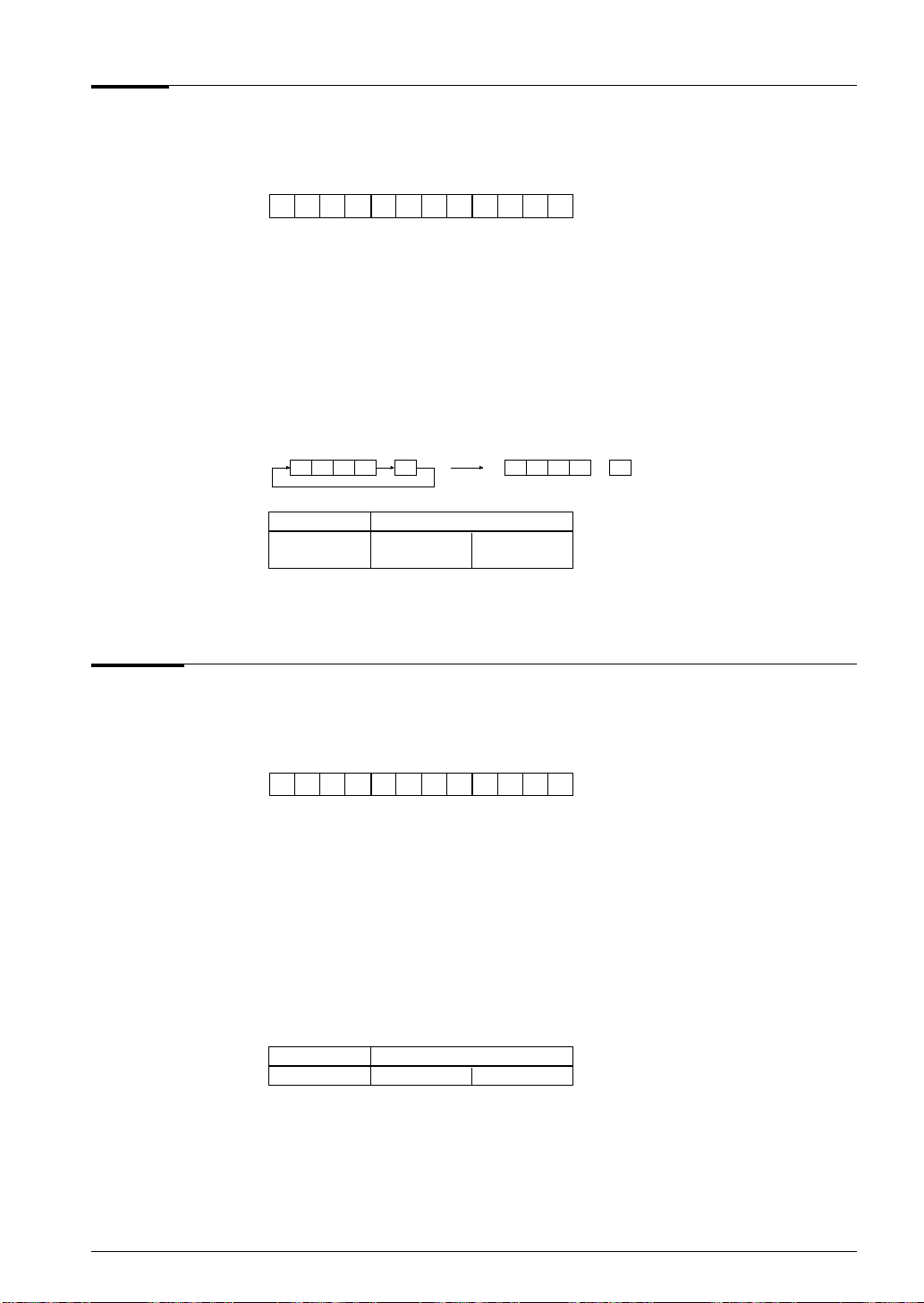

2.1.8 RET and RETS instructions

The RET instruction causes a return from a subroutine to the address immediately following the address

from where that subroutine was called. The RETS instruction causes a return to the address following this

address. Proper use of RET and RETS allows simple conditional exits subroutines back to the main routine.

See Figure 2.1.8.1.

Bank 0 Page 0

Program memory

PSET

0AH

CALL

DDD

LD

Bank 0 Page 10

Program memory

LD

A,0

B,0

DDD....................

RET

RETS

Fig. 2.1.8.1 Difference between RET and RETS instructions

2.1.9 Stack considerations for call instructions

When a subroutine is called, the return address is loaded into the stack and retrieved when control is

returned to the calling program. Nesting allows efficient usage of the stack area.

As the stack area resides in the data memory, care should be taken to ensure that the stack area is not

corrupted by other data.

S1C6200/6200A CORE CPU MANUAL EPSON 7

Page 14

2 MEMORY AND OPERATIONS

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

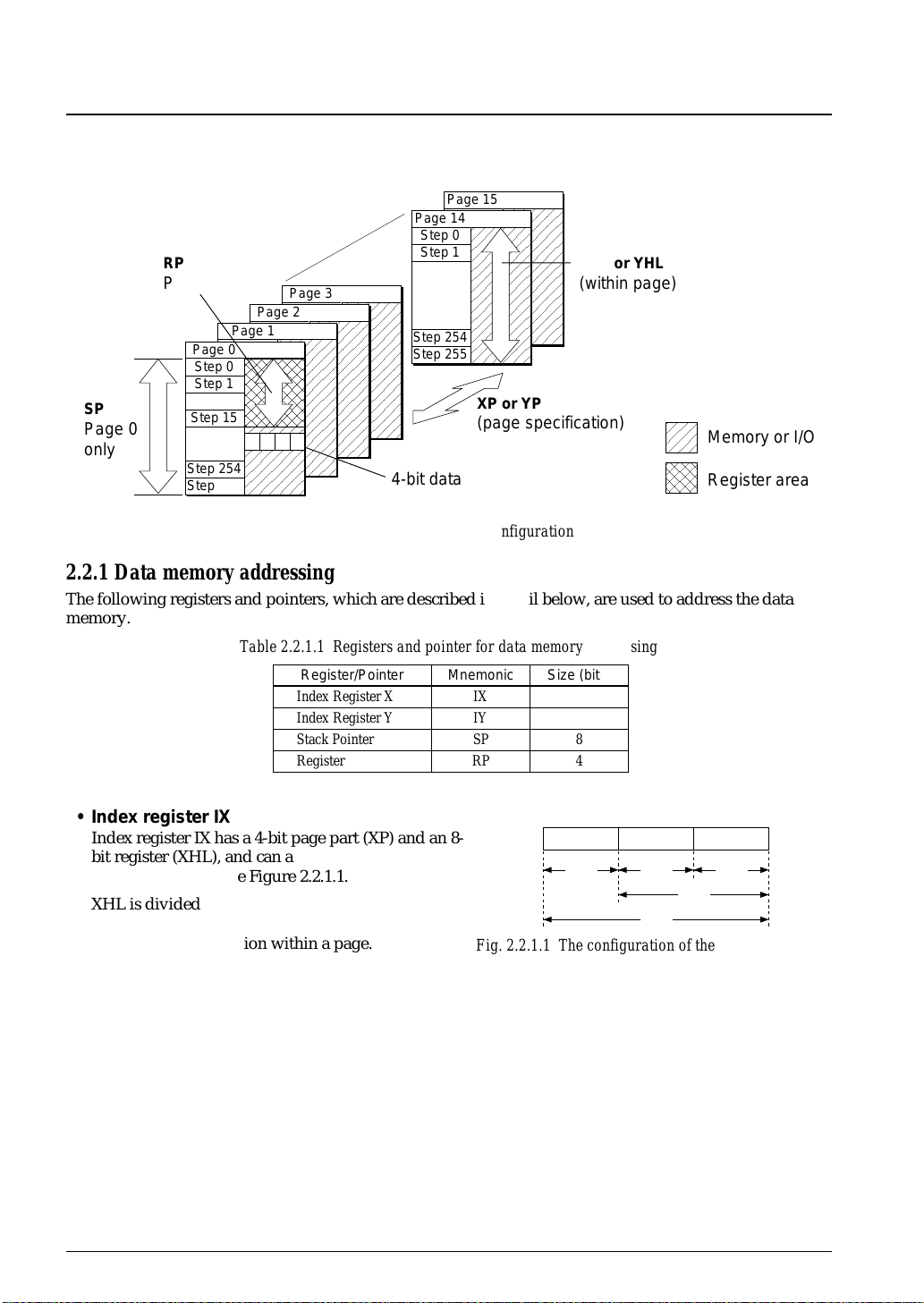

2.2 Data Memory

The data memory area comprises 4,096 4-bit words. The RAM, timer, I/O and other peripheral circuits are

mapped into this memory according to the designer's specifications. Figure 2.2.1 shows the data memory

configuration.

Page 15

SP

Page 0

only

RP

Page 0

only

Page 0

Step 0

Step 1

Step 15

Step 254

Step 255

Page 2

Page 1

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

Page 14

Step 0

Step 1

Page 3

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

Step 254

Step 255

4-bit data

Fig. 2.2.1 Data memory configuration

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

;;;;;

XHL or YHL

(within page)

XP or YP

(page specification)

;;

Memory or I/O

;;

;;

Register area

;;

2.2.1 Data memory addressing

The following registers and pointers, which are described in detail below, are used to address the data

memory.

Table 2.2.1.1 Registers and pointer for data memory addressing

Register/Pointer

Index Register X

Index Register Y

Stack Pointer

Register

• Index register IX

Index register IX has a 4-bit page part (XP) and an 8bit register (XHL), and can address any location in

the data memory. See Figure 2.2.1.1.

XHL is divided into two 4-bit groups: the four highorder bits (XH) and the four low-order bits (XL), and

can address any location within a page.

– MX is the data memory location whose address is specified by IX.

– M(X) refers to the contents of the data memory location whose address is specified by IX.

– XHL can be incremented by 1 or 2 using a post-increment instruction (LDPX, ACPX, SCPX, LBPX or

RETD). An overflow occurring in XHL does not affect the flags.

Mnemonic

IX

IY

SP

RP

Size (bits)

12

12

8

4

MSB

4

XP

44

XH XL

XHL

IX

Fig. 2.2.1.1 The configuration of the index register IX

LSB

8 EPSON S1C6200/6200A CORE CPU MANUAL

Page 15

2 MEMORY AND OPERATIONS

Push-down

(SP is decremented)

Pop-up

(SP is incremented)

Operation Instruction

Stack usage

-3

-3

-1

-1

+3

+1

+1

Interrupt

CALL or CALZ

PUSH

DEC SP

RET, RETS or RETD

POP

INC SP

• Index register IY

Index register IY is like the index register IX: it has a

4-bit page part (YP), an 8-bit register (YHL), and can

address any location in the data memory. See Figure

2.2.1.2.

YHL is divided into two 4-bit groups: the four high-

order bits (YH) and the four low-order bits (YL), and

can address any location within a page.

MSB

4

YP

44

YH YL

YHL

IY

Fig. 2.2.1.2 The configuration of the index register IY

– MY is the data memory location whose address is specified by IY.

– M(Y) refers to the contents of the data memory location whose address is specified by IY.

– YHL can be incremented by 1 using a post-increment instruction (LDPY, ACPY or SCPY). An

overflow occurring in YHL does not affect the flags.

LSB

• Stack pointer SP

The stack area resides in the data memory. The 8-bit, push-down/pop-up stack pointer (SP) is used to

address an element within the stack.

Since it is an 8-bit pointer, SP can only address 256

words out of the total 4,096 words of data memory.

When SP is used, the high-order 4 bits (page part) of

the data memory address are 0, giving a stack area of

256 words in the address range 000H to 0FFH.

In systems with a RAM area of less than 256 words,

the entire RAM area can be used as the stack area.

Stack area usage is shown in Table 2.2.1.2.

The PUSH instruction can be used to store registers and flags in the stack in single-word (4-bit) units.

The POP instruction is used to retrieve this data.

When an interrupt occurs or a call instruction is executed, the return address from the program counter

is pushed onto the stack. When a return instruction is executed, the return address is retrieved from the

stack and loaded into the program counter.

On an interrupt, only the program counter is saved on the stack; flag and register data are not saved.

Programs should be designed so that flag and register data are pushed onto the stack by the interrupt

service routines.

Following a system reset, SP should be initialized using the LD SPH,r or LD SPL,r instructions, where

r represents A, B, MX or MY (4 bits).

Stack pointer data can be read using LD r,SPH or LD r,SPL.

Table 2.2.1.2 Stack usage

• Register pointer RP

The register pointer (RP) is a 4-bit register used to address the first 16 words of data memory, or the

register area. Direct addressing can be used to read from, write to, increment or decrement any location

within this area efficiently, using a single instruction.

Programs cannot directly access RP. It uses the

operand of direct addressing instructions. The

instructions that can access the register area of data

memory are:

LD

LD

LD

S1C6200/6200A CORE CPU MANUAL EPSON 9

LD

INC

DEC

A,Mn

B,Mn

Mn,A

Mn,B

Mn

Mn

A ← M(n)

B ← M(n)

M(n) ← A

M(n) ← B

M(n) ← M(n) + 1

M(n) ← M(n)

n: 0 to F

where M(n) is the contents of a data memory

location within the register area.

As the register area can also be indirectly accessed

–

1

using IX, IY or SP, the stack area should not grow

to address 000H to 00FH when RP is used.

Page 16

2 MEMORY AND OPERATIONS

2.3 ALU (Arithmetic Logic Unit) and Registers

Table 2.3.1 shows ALU operations between the 4-bit registers, TEMPA and TEMPB.

Table 2.3.1 ALU register operation

Operation Instruction

Add, without carry

Add, with carry

Subtract, without borrow

Subtract, with borrow

Logical-AND

Logical-OR

Exclusive-OR

Comparison

Flag bit test

Rotate right, with carry

Rotate left, with carry

Invert

The Z (zero) flag is set when the result of ALU operation is

C3210

X 0000 X: Don't care.

The C (carry) flag is set when an add operation causes a carry or when a subtract operation causes a

borrow.

ADD

ADC

SUB

SBC

AND

OR

XOR

CP

FAN

RRC

RLC

NOT

2.3.1 D (decimal) flag and decimal operations

Setting the D (decimal) flag activates the decimal mode, allowing decimal addition and subtraction. Table

2.3.1.1 shows the relations of actual (decimal) results, ALU outputs, and the values of the C and Z flags.

Table 2.3.1.1 Results of hexadecimal and decimal operations

SubtractionAddition

Actual

result

D = 0 : Result of

hexadecimal operation

Z

1

0

0

1

0

2

0

3

0

4

0

5

0

6

0

7

0

8

0

9

0

10

0

11

0

12

0

13

0

14

0

15

1

16

0

17

0

18

0

19

0

20

0

21

0

22

0

23

0

24

0

25

0

26

0

27

0

28

0

29

0

30

0

31

C

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

ALU output

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

D = 1 : Result of

decimal operation

C

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

ALU output

Z

1

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

Actual

result

0

1

2

3

4

5

6

7

8

9

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

0

1

2

3

4

5

-16

-15

-14

-13

-12

-11

-10

D = 0 : Result of

hexadecimal operation

Z

C

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

-9

-8

-7

-6

-5

-4

-3

-2

-1

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

ALU output

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

D = 1 : Result of

decimal operation

C

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

ALU output

Z

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

A

B

C

D

E

F

0

1

2

3

4

5

6

7

8

9

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

10 EPSON S1C6200/6200A CORE CPU MANUAL

Page 17

2 MEMORY AND OPERATIONS

Hexadecimal operations will not always produce the correct result if performed in decimal mode.

Note that:

• An add instruction with carry (for example, ADC XH,i) which uses index registers XH, XL, YH and YL,

does not involve decimal correction even if it is performed in the decimal mode. This is because it uses

an 8-bit field for 4-bit data.

• The results of the compare instruction (CP) is not decimal-corrected, because the carry flag is ignored.

• The result of the register memory increment instruction (INC Mn) and decrement instruction (DEC Mn)

are not decimal-corrected.

2.3.2 A and B registers

The A and B registers are 4-bit general-purpose registers used as accumulators. They transfer data and

perform ALU operations with other registers, data memory and immediate data.

The data in A can be paired with that in B for use as an indirect jump address by the JPBA instruction.

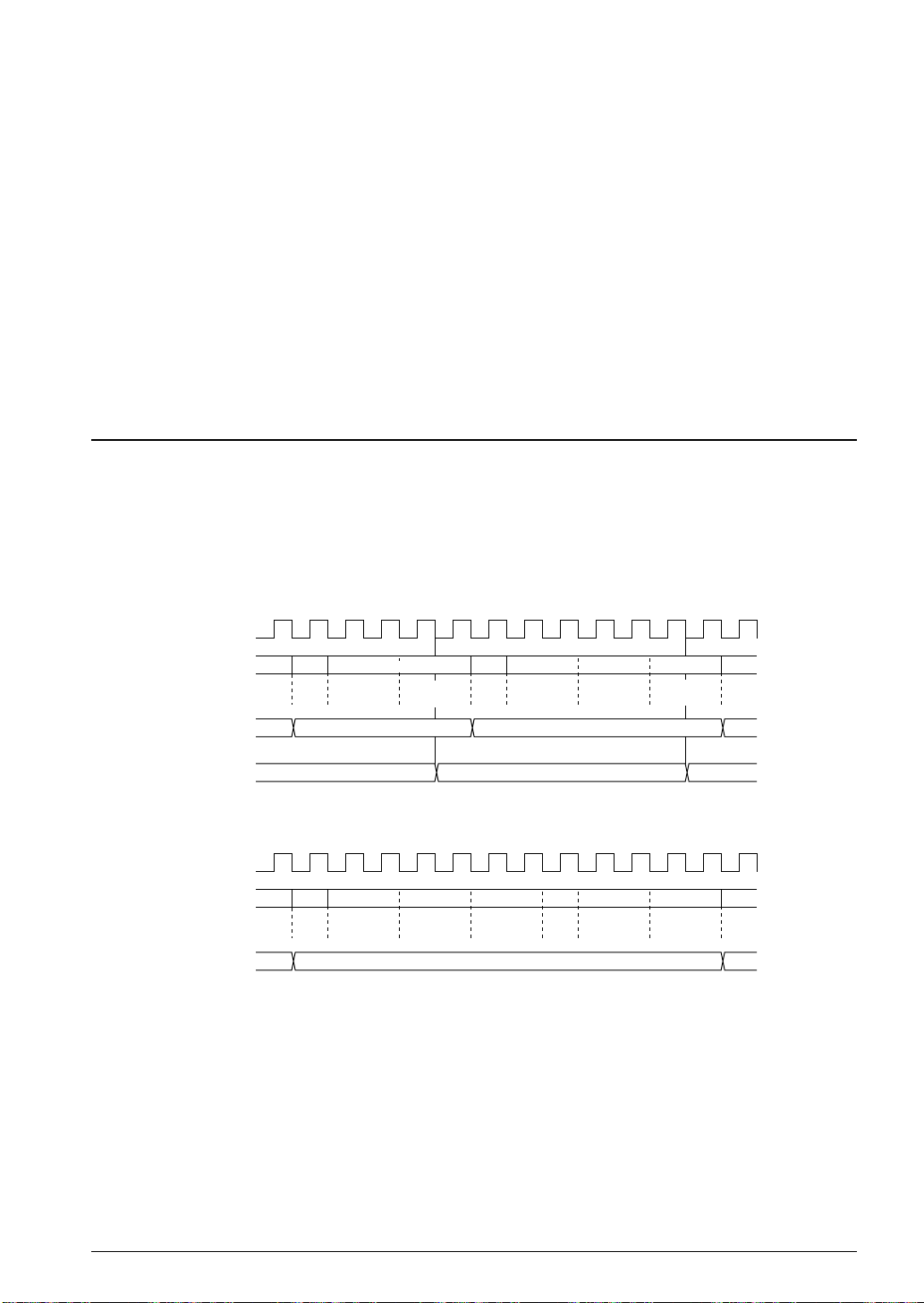

2.4 Timing Generator

S1C6200/6200A instructions can be divided into three different types depending on the number of clock

cycles per instruction: 5, 7 or 12 clock cycles. The more complex the instruction, the more cycles it requires.

Note that the number of clock cycles determines the duration of instructions which, in turn, will affect any

timing performed in software.

As shown in Figure 2.4.1, the first state of all instructions is a fetch cycle. This is followed by a number of

execute cycles.

5-clock/7-clock instructions

Clock

Status

Instruction

register

Date

memory

Fetch ExecuteFetch

State

0

State

1

Execute

State2State0State

1

State

2

State

3

12-clock instructions

Clock

Status

Instruction

register

Fetch

State

0

State

1

State

2

Execute

State3State4State

5

State

6

Fig. 2.4.1 Instruction execution timing

2.4.1 HALT and SLP (sleep) modes

HALT and SLP cause the CPU to store the return address on the stack and then stop. HALT will only stop

the CPU; the system clock will continue to run. SLP also stops the system clock, resulting in reduced power

consumption. The CPU can be restarted by an interrupt.

As interrupts are not automatically enabled by the execution of HALT or SLP, programs should always

enable interrupts before executing HALT or SLP, otherwise they will hang waiting for an interrupt.

S1C6200/6200A CORE CPU MANUAL EPSON 11

Page 18

2 MEMORY AND OPERATIONS

2.5 Interrupts

The S1C6200/6200A can have up to 15 interrupt vectors. When used with peripheral circuits, these allow

internal and external interrupts to be processed easily. See Figure 2.5.3.1 through 2.5.3.4.

2.5.1 Interrupt vectors

The interrupt vectors are assigned to steps 1 to 15 in page 1 of each bank of the program memory. When an

interrupt occurs, the program jumps to the appropriate interrupt vector in the current bank.

The priority and linking of these vectors to actual outside events depends on the configuration of the

peripheral circuits and therefore is device-specific. This information can be found in the technical manuals

for the specific device.

2.5.2 I (interrupt) flag

The I (interrupt) flag enables or disables all interrupts.

When DI or RST F is used to reset the I flag, interrupts are disabled with that instruction step. When EI or

SET F is used to set the I flag, interrupts are enabled after the following instruction step. For example, to

return control from the interrupt subroutine to the main routine, the sequence EI, RET, does not enable

interrupts until after RET has been executed.

The I flag is reset to 0 (DI) on reset.

2.5.3 Operation during interrupt generation

When an interrupt is generated, the program is halted, the program counter (PCP and PCS) is stored on the

stack, the I flag is reset to DI mode and NPP is set to 1. The program then branches to the interrupt vector

corresponding to the interrupt request. Registers and flags are unaffected by an interrupt.

Register and flag data must be saved by the program since they are not automatically stored on the stack.

The I flag can be set to 1 (EI) within the interrupt subroutine, because nesting of multiple interrupts is

available.

If an interrupt is generated while the CPU is in HALT or SLP mode, the CPU is restarted and the interrupt

serviced. When the interrupt service routine is completed, the program resumes from the instruction

following the HALT or SLP.

<Differences between S1C6200 and S1C6200A>

In the S1C6200 and the S1C6200A, the time it takes to complete interrupt processing by hardware after the

Core CPU receives the interrupt request is different as follows:

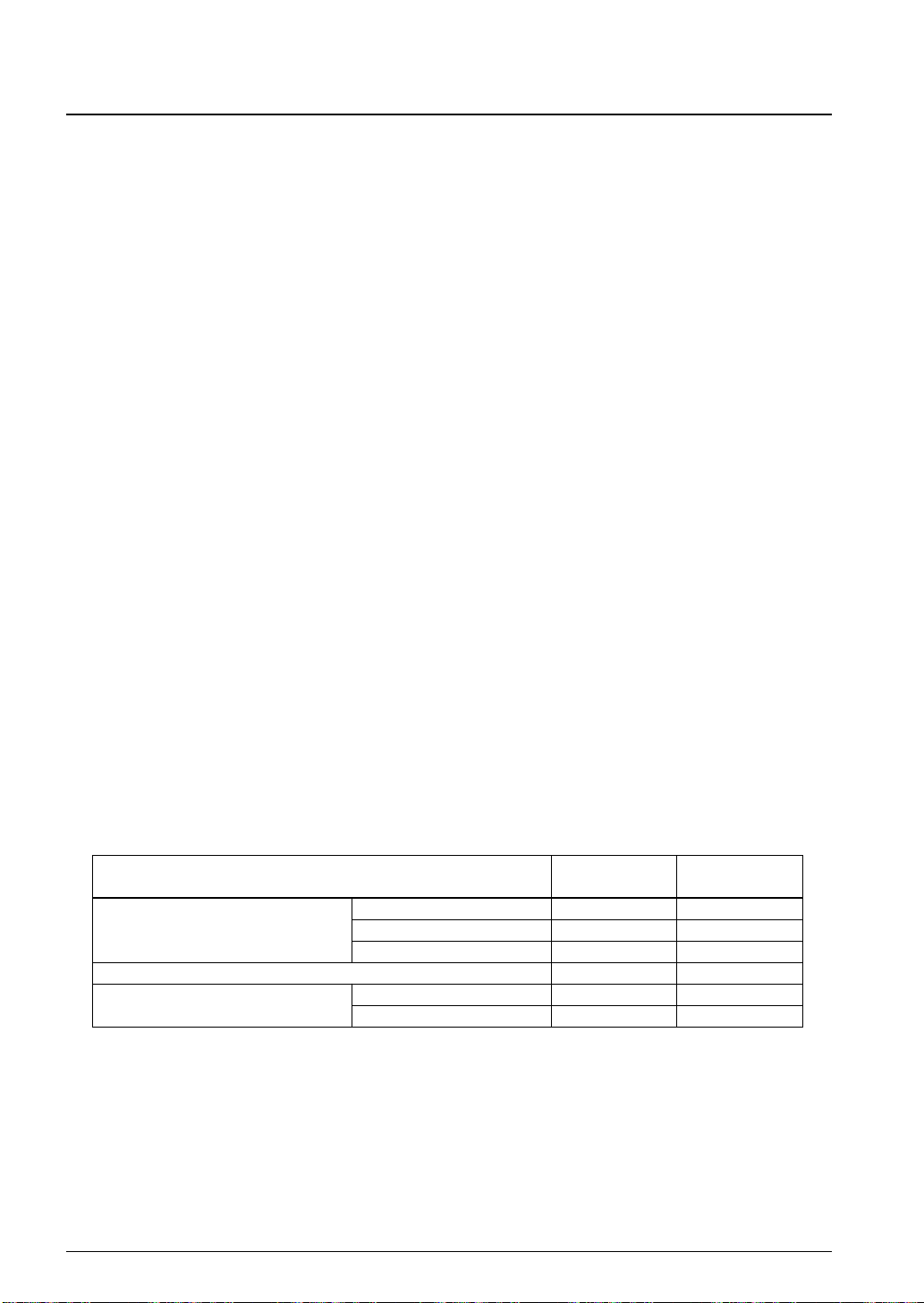

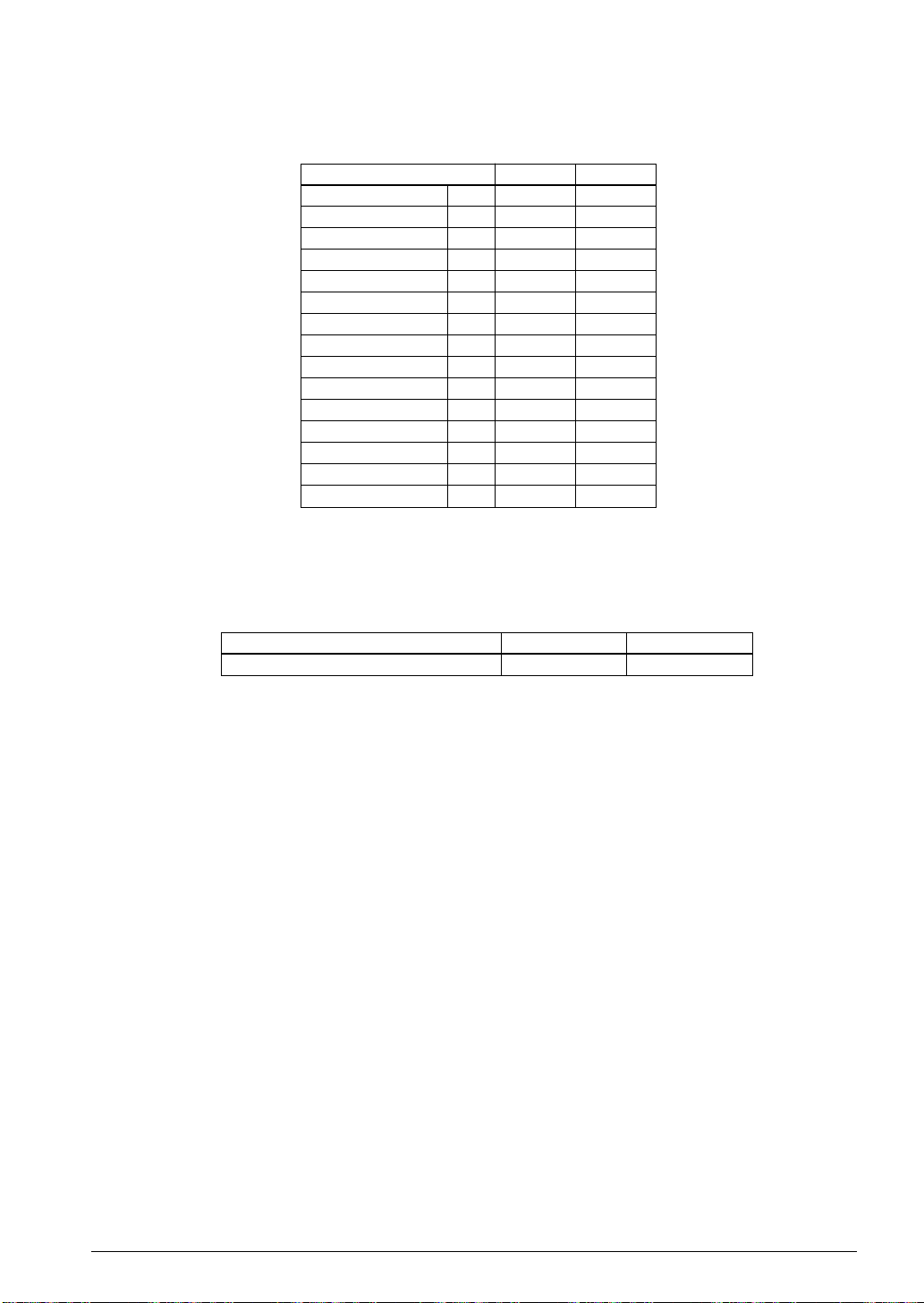

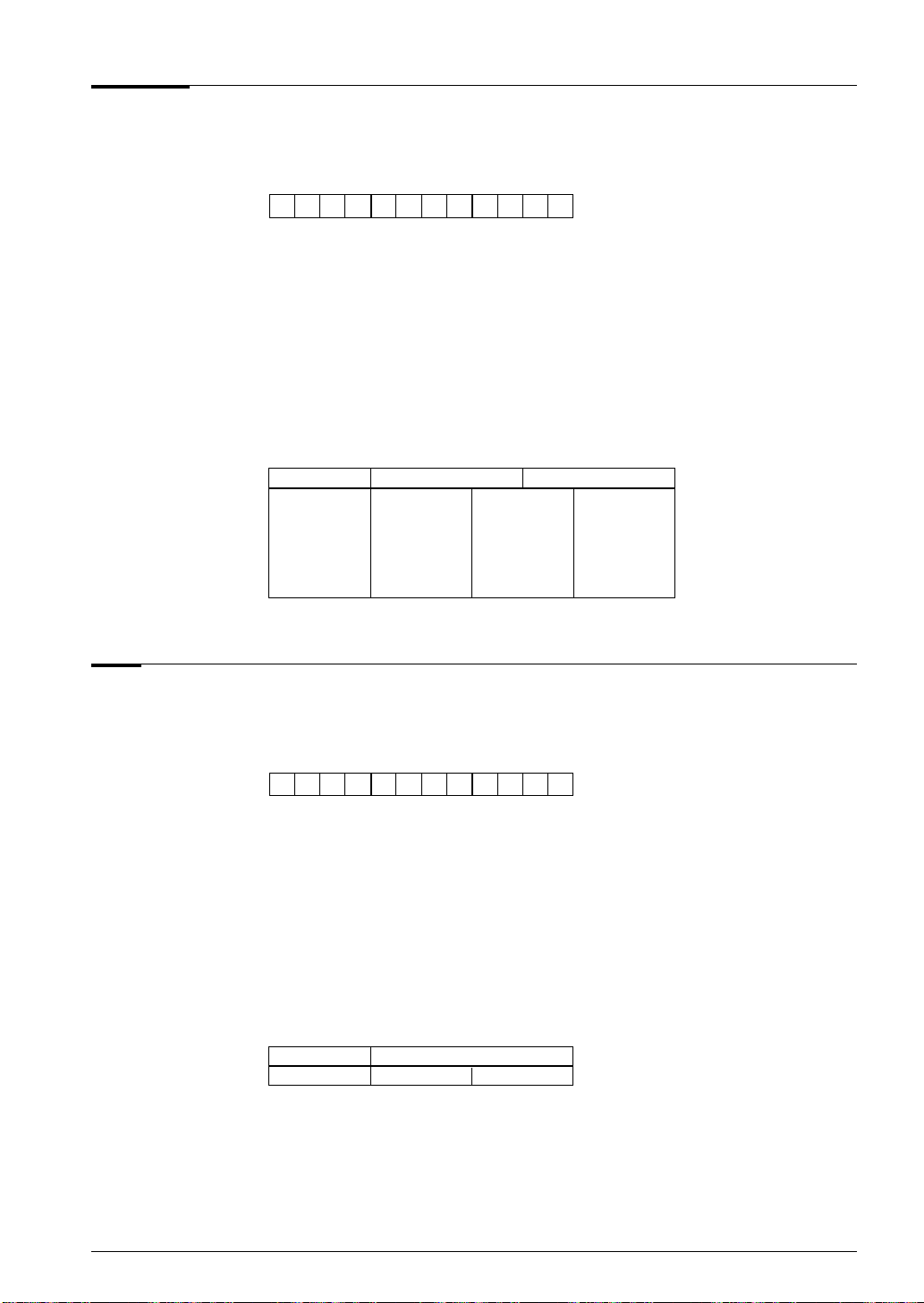

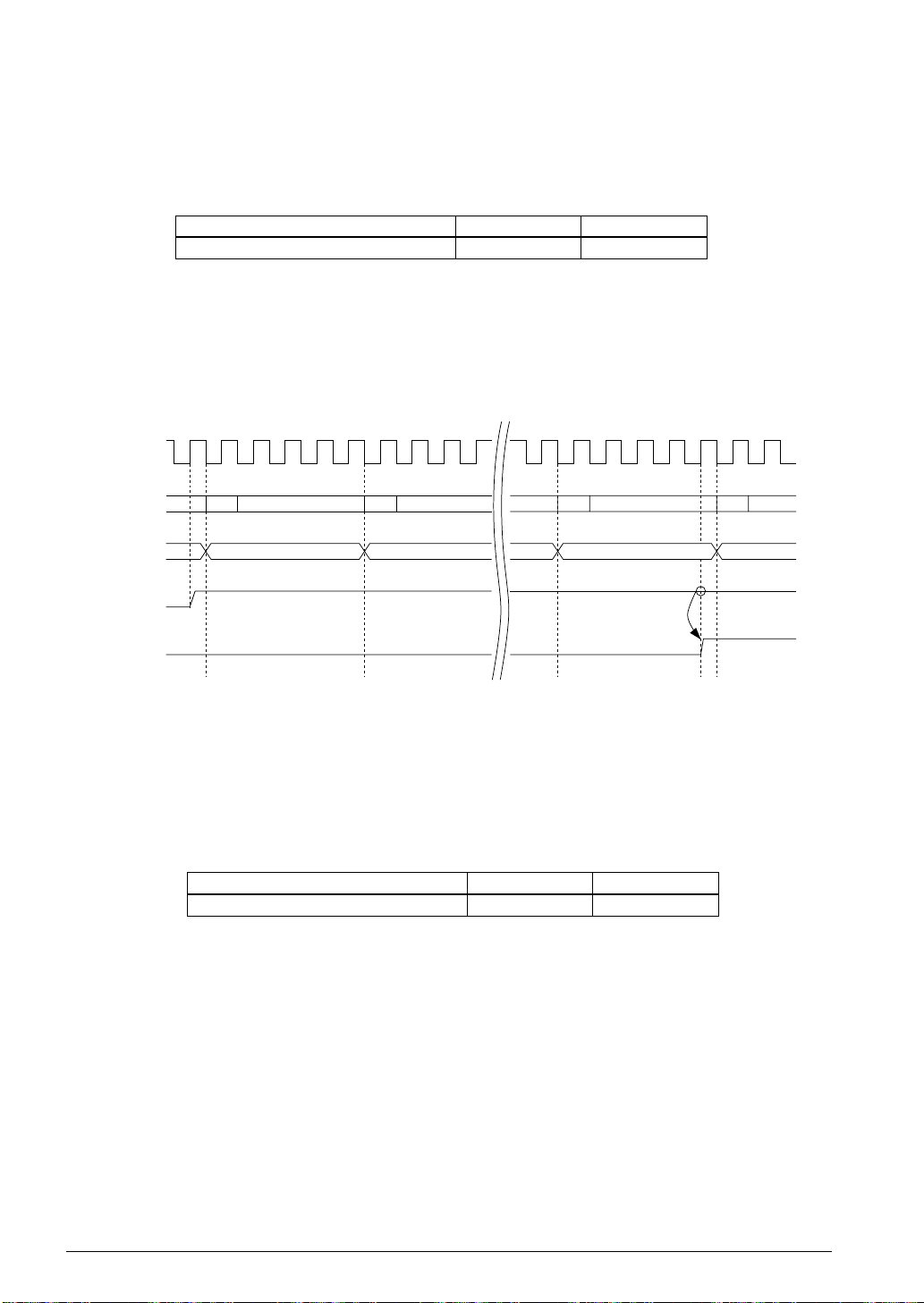

Table 2.5.3.1 Required interrupt processing time

Item

a) During instruction execution

b) At HALT mode

c) During PSET instruction execution

12 EPSON S1C6200/6200A CORE CPU MANUAL

12-cycle instruction execution

7-cycle instruction execution

5-cycle instruction execution

PSET + CALL

PSET + JP

S1C6200A

(clock cycles)

12.5 to 24.5

12.5 to 19.5

12.5 to 17.5

14 to 15

12.5 to 24.5

12.5 to 22.5

S1C6200

(clock cycles)

13 to 25

13 to 20

13 to 18

14 to 15

13 to 25

13 to 23

Page 19

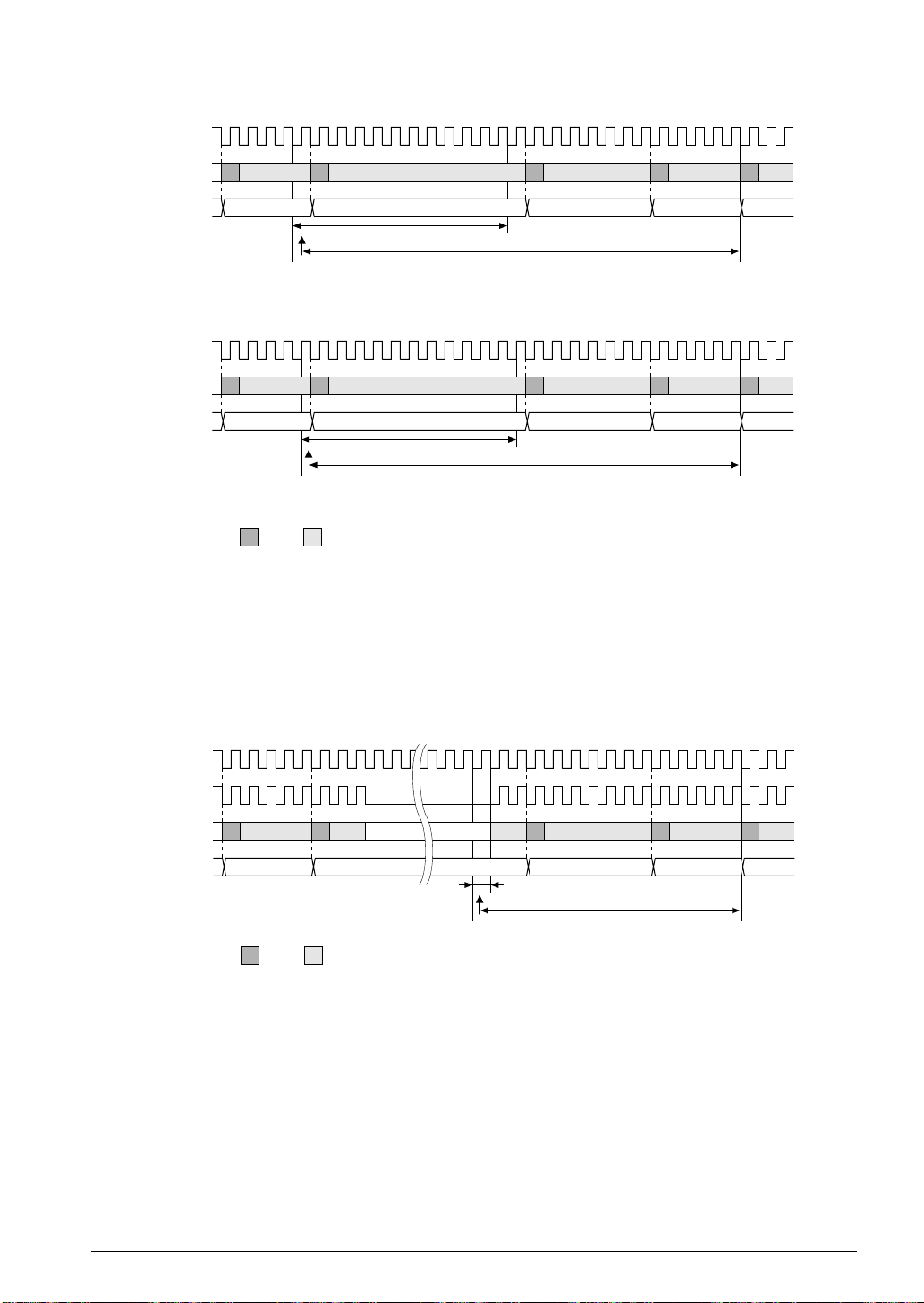

S1C6200

Clock

Status

2 MEMORY AND OPERATIONS

Instruction

S1C6200A

Clock

Status

Instruction

5-clock Instrruction

5-clock Instrruction

Status:

Fetch

12-clock Instrruction

Interrupt

Interrupt processing:

12-clock Instrruction

Interrupt

Interrupt processing:

Execute Note: (*1)

12-clock instruction

7-clock instruction

5-clock instruction

12-clock instruction

7-clock instruction

5-clock instruction

(*2)

INT1 and INT2 are dummy instructions

Branches to the top of the interrupt service routine

INT1 (*1) INT2 (*1) JP (*2)

... 13 to 25 clock cycles

... 13 to 20 clock cycles

... 13 to 18 clock cycles

INT1 (*1) INT2 (*1) JP (*2)

... 12.5 to 24.5 clock cycles

... 12.5 to 19.5 clock cycles

... 12.5 to 17.5 clock cycles

Fig. 2.5.3.1 Interrupt timing during execution

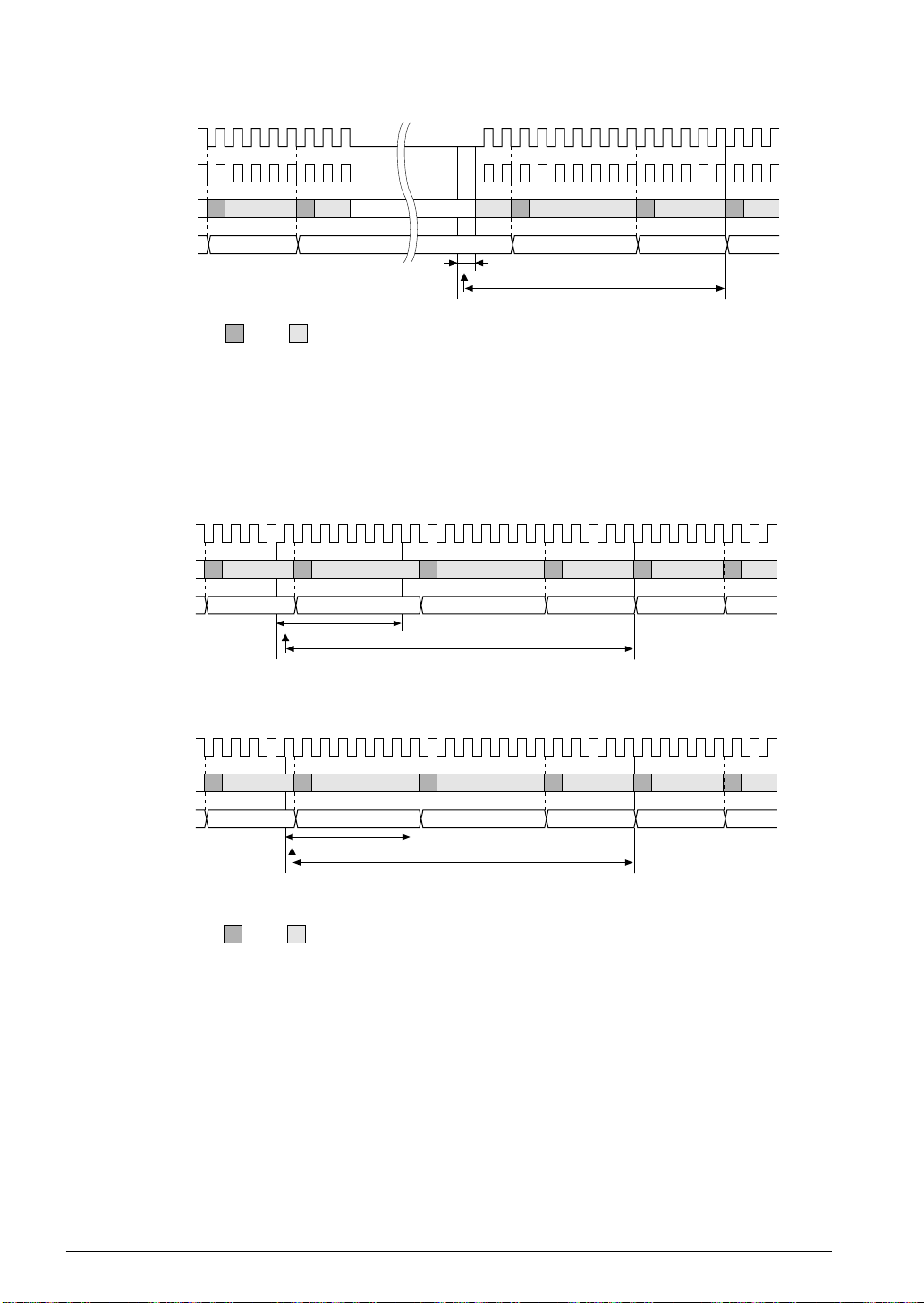

S1C6200/6200A

System clock

CPU clock

Status

Instruction

Status:

5-clock Instrruction

Fetch

HALT

Execute Note: (*1)

(*2)

Interrupt

Interrupt processing: 14 to 15 clock cycles

INT1 and INT2 are dummy instructions

Branches to the top of the interrupt service routine

INT1 (*1) INT2 (*1) JP (*2)

Fig. 2.5.3.2 Interrupt timing in the HALT mode

S1C6200/6200A CORE CPU MANUAL EPSON 13

Page 20

2 MEMORY AND OPERATIONS

S1C6200/6200A

System clock

CPU clock

Status

Instruction

S1C6200

Clock

Status

Instruction

S1C6200A

Clock

5-clock Instrruction

Status:

PSET

SLEEP

Fetch

Execute Note: (*1)

(*2)

Fig. 2.5.3.3 Interrupt timing in SLEEP mode

CALL

Interrupt

Interrupt processing:

INT1 (*1) INT2 (*1) JP (*2)

PSET + CALL

PSET + JP

INT1 (*1) INT2 (*1) JP (*2)

Interrupt

Interrupt processing: 14 to 15 clock cycles

INT1 and INT2 are dummy instructions

Branches to the top of the interrupt service routine

... 13 to 25 clock cycles

... 13 to 23 clock cycles

Status

Instruction

Status:

PSET

Fetch

CALL

Interrupt

Interrupt processing:

Execute Note: (*1)

PSET + CALL

PSET + JP

INT1 (*1) INT2 (*1) JP (*2)

... 12.5 to 24.5 clock cycles

... 12.5 to 22.5 clock cycles

INT1 and INT2 are dummy instructions

(*2)

Branches to the top of the interrupt service routine

Fig. 2.5.3.4 Interrupt timing with PSET

14 EPSON S1C6200/6200A CORE CPU MANUAL

Page 21

2 MEMORY AND OPERATIONS

2.5.4 Initial reset

On reset, the registers and flags are set as shown in Table 2.5.4.1.

Table 2.5.4.1 Reset value

0

Value

00H

01H

00H

01H

Undefined

Undefined

Undefined

Undefined

Undefined

Undefined

Undefined

0H

*

Undefined

Undefined

* S1C6200 ...Undefined

S1C6200A ...0

S1C6200

Undefined

Bit length

Program Counter Step

Program Counter Page

Program Counter Bank

New Page Pointer

New Bank Pointer

Stack Pointer

Index Register

Index Register

Register Pointer

General Register

General Register

Interrupt Flag

Decimal Flag

Zero Flag

Carry Flag

PCS

PCP

PCB

NPP

NBP

SP

IX

IY

RP

A

B

I

D

Z

C

8

4

1

4

1

8

12

12

4

4

4

1

1

1

1

<Difference between S1C6200 and S1C6200A>

There is a difference in the setting value of the D (decimal) flag at initial reset between the S1C6200 and the

S1C6200A.

Table 2.5.4.2 D (decimal) flag initial setting

CPU Core

D (decimal) flag setting

S1C6200A

When using the model loaded with the S1C6200 Core CPU, set or reset the D flag in the user's initial

routine before using an arithmetic instruction. (refer to the SDF and RDF instructions.)

S1C6200/6200A CORE CPU MANUAL EPSON 15

Page 22

3 INSTRUCTION SET

3INSTRUCTION SET

This chapter describes the entire instruction set of the S1C6200/6200A Core CPU.

A subset is allocated to each device within the S1C62 Family according to the configuration of the device.

Therefore not all instructions are available in every device. The relevant information is in the technical

manual for each device.

The source format and a description of the assembler is in the series-specific cross assembler manuals.

The instruction set contains 109 instructions. Each instruction comprises of one 12-bit word.

3.1 Instruction Indices

Three index tables are used for easy reference instructions.

a. Index by function

The instructions are arranged by function.

1. Branch

2. System control

3. Flag operation

4. Stack operation

5. Index operation

6. Data transfer

7. Arithmetic and logical operation

b. Index in alphabetical order

The instructions are arranged in alphabetical order. Page number references are provided.

c. Index by operation code

The instructions are arranged in numerical order by operation code.

16 EPSON S1C6200/6200A CORE CPU MANUAL

Page 23

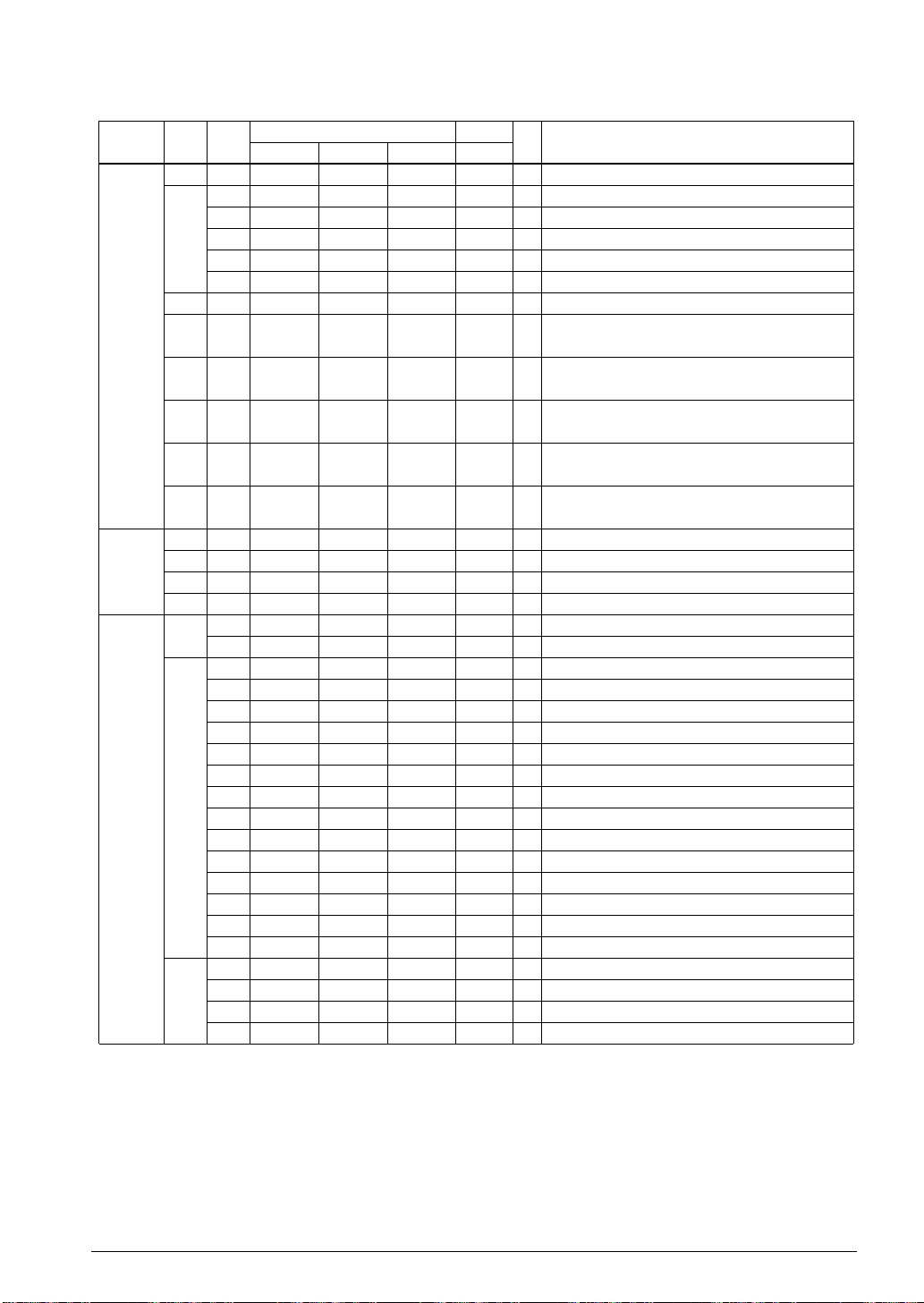

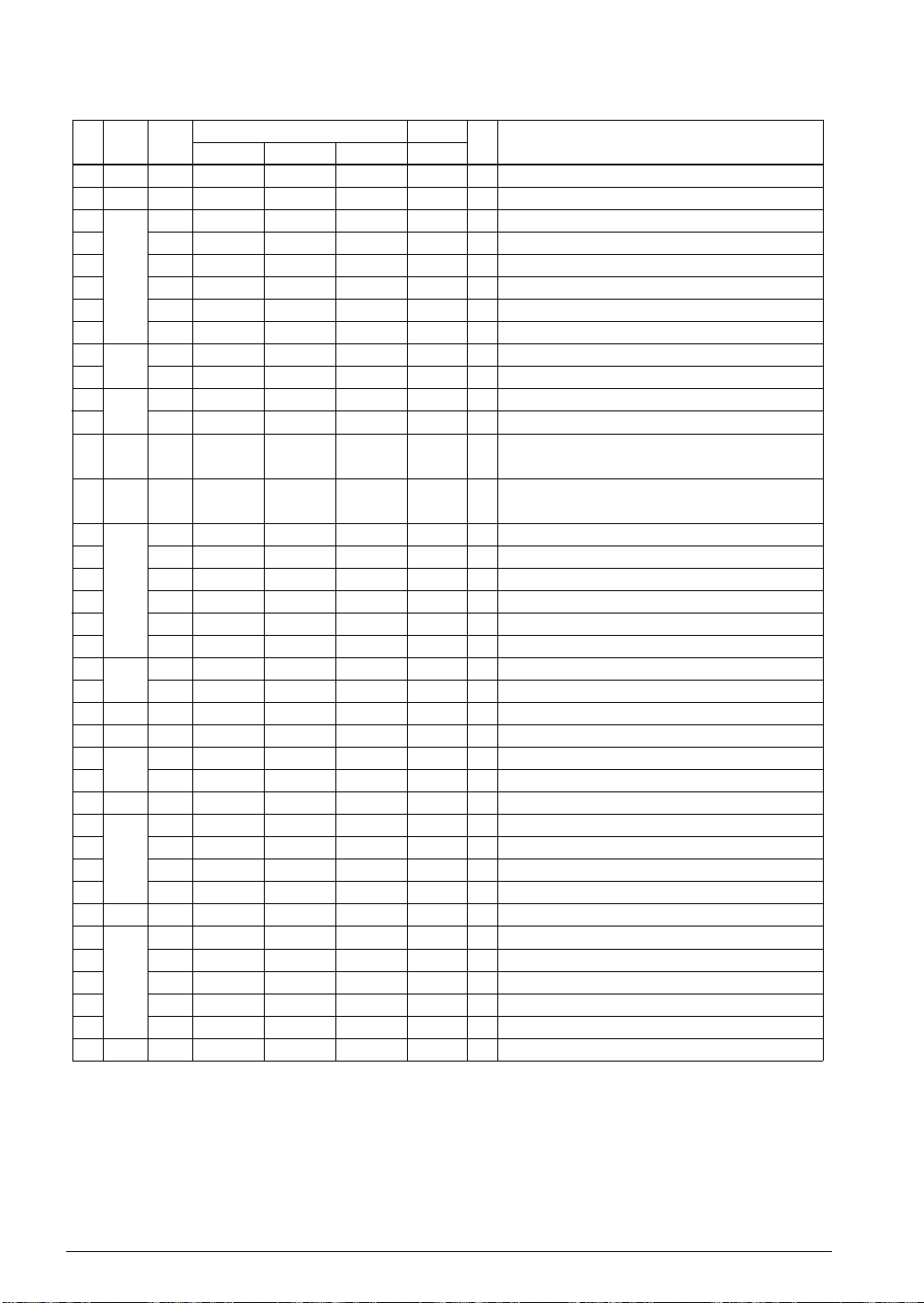

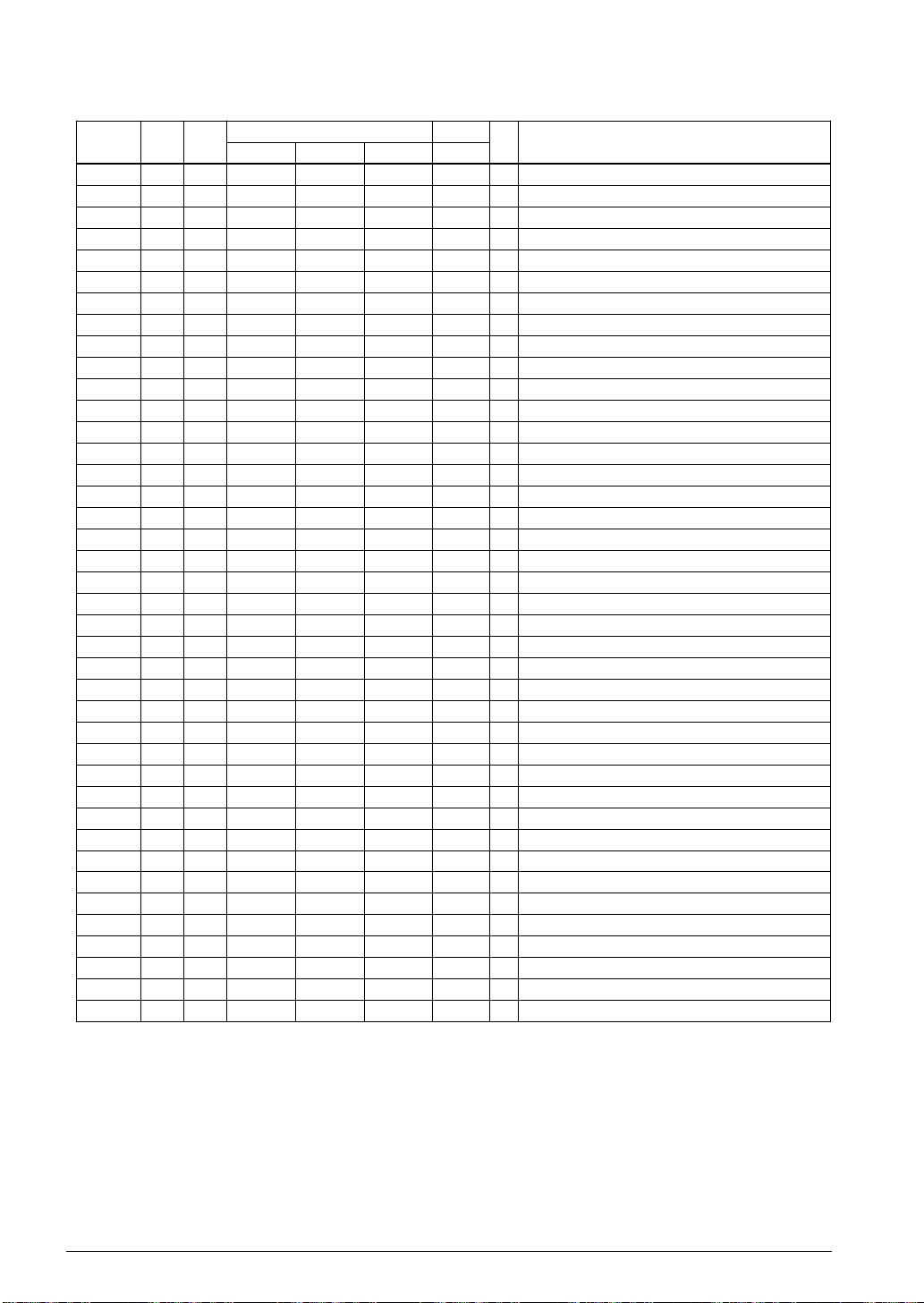

3.1.1 By function

3 INSTRUCTION SET

Classification Operand Clock

Branch

instructions

System

control

instructions

Index

operation

instructions

Mne-

monic

PSET

JP

JPBA

CALL

CALZ

RET

RETS

RETD

NOP5

NOP7

HALT

SLP

INC

LD

ADC

p

s

C, s

NC, s

Z, s

NZ, s

s

s

e

X

Y

X, e

Y, e

XP, r

XH, r

XL, r

YP, r

YH, r

YL, r

r, XP

r, XH

r, XL

r, YP

r, YH

r, YL

XH, i

XL, i

YH, i

YL, i

B

1

0

0

0

0

0

1

0

0

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Operation Code Flag

A

9

8

7

6

5

4

1

1

0

0

1

0

p4

p3

0

0

0

s7

s6

s5

s4

s3

0

1

0

s7

s6

s5

s4

s3

0

1

1

s7

s6

s5

s4

s3

1

1

0

s7

s6

s5

s4

s3

1

1

1

s7

s6

s5

s4

s3

1

1

1

1

1

1

0

1

0

0

s7

s6

s5

s4

s3

1

0

1

s7

s6

s5

s4

s3

1

1

1

1

1

0

1

1

1

1

1

1

0

1

0

0

1

e7

e6

e5

e4

e3

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1

1

1

0

1

1

0

1

1

1

1

0

1

1

e7

e6

e5

e4

e3

0

0

0

e7

e6

e5

e4

e3

1

1

0

1

0

0

0

1

1

0

1

0

0

0

1

1

0

1

0

0

0

1

1

0

1

0

0

1

1

1

0

1

0

0

1

1

1

0

1

0

0

1

1

1

0

1

0

1

0

1

1

0

1

0

1

0

1

1

0

1

0

1

0

1

1

0

1

0

1

1

1

1

0

1

0

1

1

1

1

0

1

0

1

1

0

1

0

0

0

0

0

0

1

0

0

0

0

1

0

1

0

0

0

1

0

0

1

0

0

0

1

1

3

2

1

0

IDZC

p2

p1

p0

s2

s1

s0

s2

s1

s0

s2

s1

s0

s2

s1

s0

s2

s1

s0

1

0

0

0

s2

s1

s0

s2

s1

s0

1

1

1

1

1

1

1

0

e2

e1

e0

1

0

1

1

1

1

1

1

1

0

0

0

1

0

0

1

0

0

0

0

0

0

0

0

e2

e1

e0

e2

e1

e0

0

0

r1

r0

0

1

r1

r0

1

0

r1

r0

0

0

r1

r0

0

1

r1

r0

1

0

r1

r0

0

0

r1

r0

0

1

r1

r0

1

0

r1

r0

0

0

r1

r0

0

1

r1

r0

1

0

r1

r0

i3

i2

i1

i0

i3

i2

i1

i0

i3

i2

i1

i0

i3

i2

i1

i0

5

5

5

5

5

5

5

7

7

7

12

12

5

7

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

↑

↑

7

↓

↓

↑

↑

7

↓

↓

↑

↑

7

↓

↓

↑

↑

7

↓

↓

Operation

←

p4, NPP ← p3~p0

NBP

←

NBP, PCP ← NPP, PCS ← s7~s0

PCB

←

NBP, PCP ← NPP, PCS ← s7~s0 if C=1

PCB

←

NBP, PCP ← NPP, PCS ← s7~s0 if C=0

PCB

←

NBP, PCP ← NPP, PCS ← s7~s0 if Z=1

PCB

←

NBP, PCP ← NPP, PCS ← s7~s0 if Z=0

PCB

←

NBP, PCP ← NPP, PCSH ← B, PCSL ← A

PCB

←

M(SP-1)

SP

M(SP-1)

SP

PCSL

SP

PCSL

SP

PCSL

SP

PCP, M(SP-2) ← PCSH, M(SP-3) ← PCSL+1

←

SP-3, PCP ← NPP, PCS ← s7~s0

←

PCP, M(SP-2) ← PCSH, M(SP-3) ← PCSL+1

←

SP-3, PCP ← 0, PCS ← s7~s0

←

M(SP), PCSH ← M(SP+1), PCP ← M(SP+2)

←

SP+3

←

M(SP), PCSH ← M(SP+1), PCP ← M(SP+2)

←

SP+3, PC ← PC+1

←

M(SP), PCSH ← M(SP+1), PCP ← M(SP+2)

←

SP+3, M(X) ← e3~e0, M(X+1) ← e7~e4, X ← X+2

No operation (5 clock cycles)

No operation (7 clock cycles)

Halt (stop clock)

SLEEP (stop oscillation)

←

X+1

X

←

Y+1

Y

←

e7~e4, XL ← e3~e0

XH

←

e7~e4, YL ← e3~e0

YH

←

r

XP

←

r

XH

←

r

XL

←

r

YP

←

r

YH

←

r

YL

←

XP

r

←

XH

r

←

XL

r

←

YP

r

← Y

H

r

←

YL

r

←

XH+i3~i0+C

XH

←

XL+i3~i0+C

XL

←

YH+i3~i0+C

YH

←

YL+i3~i0+C

YL

S1C6200/6200A CORE CPU MANUAL EPSON 17

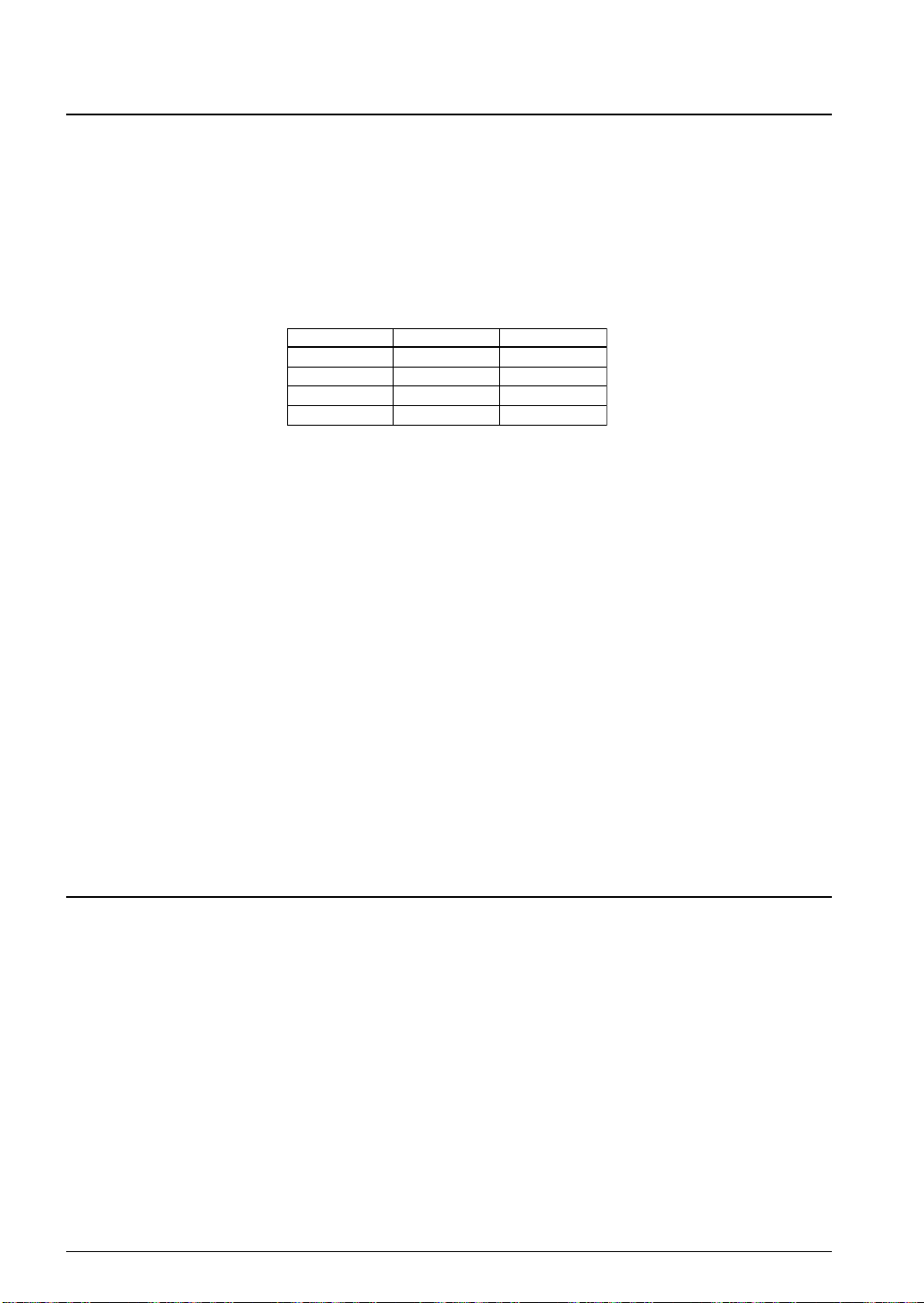

Page 24

3 INSTRUCTION SET

Classification Operand

Index

operation

instructions

Mne-

monic

CP

XH, i

XL, i

YH, i

YL, i

Data

transfer

instructions

LD

r, i

r, q

A, Mn

B, Mn

Mn, A

Mn, B

MX, i

LDPX

r, q

MY, i

LDPY

r, q

MX, e

LBPX

Flag

operation

instructions

SET

RST

SCF

F, i

F, i

RCF

SZF

RZF

SDF

RDF

EI

DI

Stack

operation

instructions

INC

DEC

PUSH

SP

SP

r

XP

XH

XL

YP

YH

YL

F

r

POP

XP

XH

XL

YP

Operation Code Flag

B

A

9

8

7

6

5

4

3

2

1

0

IDZC

1

0

1

0

0

1

0

0

i3

i2

i1

i0

1

0

1

0

0

1

0

1

i3

i2

i1

i0

1

0

1

0

0

1

1

0

i3

i2

i1

i0

1

0

1

0

0

1

1

1

i3

i2

i1

i0

1

1

1

0

0

0

r1

r0

i3

i2

i1

i0

1

1

1

0

1

1

0

0

r1

r0

q1

q0

1

1

1

1

1

0

1

0

n3

n2

n1

n0

1

1

1

1

1

0

1

1

n3

n2

n1

n0

1

1

1

1

1

0

0

0

n3

n2

n1

n0

1

1

1

1

1

0

0

1

n3

n2

n1

n0

1

1

1

0

0

1

1

0

i3

i2

i1

i0

1

1

1

0

1

1

1

0

r1

r0

q1

q0

1

1

1

0

0

1

1

1

i3

i2

i1

i0

1

1

1

0

1

1

1

1

r1

r0

q1

q0

1

0

0

1

e7

e6

e5

e4

e3

e2

e1

e0

1

1

1

1

0

1

0

0

i3

1

1

1

1

0

1

0

1

i3

1

1

1

1

0

1

0

0

0

1

1

1

1

0

1

0

1

1

1

1

1

1

0

1

0

0

0

1

1

1

1

0

1

0

1

1

1

1

1

1

0

1

0

0

0

1

1

1

1

0

1

0

1

1

1

1

1

1

0

1

0

0

1

1

1

1

1

0

1

0

1

0

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

0

0

1

1

1

1

1

1

1

0

0

0

1

1

1

1

1

1

0

0

0

1

1

1

1

1

1

0

0

0

1

1

1

1

1

1

0

0

0

1

1

1

1

1

1

0

0

0

1

1

1

1

1

1

0

0

1

1

1

1

1

1

1

0

0

1

1

1

1

1

1

1

0

0

1

1

1

1

1

1

1

0

1

0

1

1

1

1

1

1

0

1

0

1

1

1

1

1

1

0

1

0

1

1

1

1

1

1

0

1

0

1

1

1

1

1

1

0

1

0

↑

i2

i1

i0

↓

i2

i1

i0

0

0

1

1

1

0

0

1

0

1

0

1

1

0

0

0

1

1

↑

0

0

0

↓

1

1

1

0

1

1

0

1

1

0

r1

r0

1

0

0

1

0

1

1

1

0

1

1

1

0

0

0

0

0

1

0

1

0

0

r1

r0

1

0

0

1

0

1

1

1

0

1

1

1

Clock

↑

↓

↑

↓

↑

↓

↑

↓

↑

↑

↓

↓

↑

↓

↑

↓

XH-i3~i0

↑

7

↓

XL-i3~i0

↑

7

↓

YH-i3~i0

↑

7

↓

YL-i3~i0

↑

7

↓

←

i3~i0

r

5

←

q

r

5

←

M(n3~n0)

A

5

←

M(n3~n0)

B

5

←

M(n3~n0)

5

←

M(n3~n0)

5

←

i3~i0, X ← X+1

M(X)

5

←

q, X ← X+1

r

5

←

i3~i0, Y ← Y+1

M(Y)

5

←

q, Y ← Y+1

r

5

←

e3~e0, M(X+1) ← e7~e4, X ← X+2

M(X)

5

←

FVi3~i0

F

↑

7

←

FΛi3~i0

F

↓

7

←

1

C

↑

7

←

0

C

↓

7

←

1

Z

7

←

0

Z

7

←

1 (Decimal Adjuster ON)

D

7

←

0 (Decimal Adjuster OFF)

D

7

←

1 (Enables Interrupt)

I

7

←

0 (Disables Interrupt)

I

7

←

SP+1

SP

5

←

SP-1

SP

5

←

SP-1, M(SP) ← r

SP

5

←

SP-1, M(SP) ← XP

SP

5

←

SP-1, M(SP) ← XH

SP

5

←

SP-1, M(SP) ← XL

SP

5

←

SP-1, M(SP) ← YP

SP

5

←

SP-1, M(SP) ← YH

SP

5

←

SP-1, M(SP) ← YL

SP

5

←

SP-1, M(SP) ← F

SP

5

←

M(SP), SP ← SP+1

r

5

←

M(SP), SP ← SP+1

XP

5

←

M(SP), SP ← SP+1

XH

5

←

M(SP), SP ← SP+1

XL

5

←

M(SP), SP ← SP+1

YP

5

Operation

A

B

18 EPSON S1C6200/6200A CORE CPU MANUAL

Page 25

3 INSTRUCTION SET

Classification Operand

Stack

operation

instructions

Mne-

monic

POP

LD

YH

YL

F

SPH, r

SPL, r

r, SPH

r, SPL

Arithmetic

instructions

ADD

ADC

r, i

r, q

r, i

r, q

r, q

SUB

r, i

SBC

r, q

r, i

AND

r, q

r, i

OR

r, q

r, i

XOR

r, q

r, i

CP

r, q

r, i

FAN

r, q

r

RLC

r

RRC

Mn

INC

Mn

DEC

MX, r

ACPX

MY, r

ACPY

MX, r

SCPX

MY, r

SCPY

r

NOT

Operation Code Flag

B

A

9

8

7

6

5

4

3

2

1

0

IDZC

1

1

1

1

1

1

0

1

1

0

0

0

1

1

1

1

1

1

0

1

1

0

0

1

1

1

1

1

1

1

0

1

1

0

1

0

↑

1

1

1

1

1

1

1

0

0

0

r1

r0

1

1

1

1

1

1

1

1

0

0

r1

r0

1

1

1

1

1

1

1

0

0

1

r1

r0

1

1

1

1

1

1

1

1

0

1

r1

r0

1

1

0

0

0

0

r1

r0

i3

i2

i1

i0

1

0

1

0

1

0

0

0

r1

r0

q1

q0

1

1

0

0

0

1

r1

r0

i3

i2

i1

i0

1

0

1

0

1

0

0

1

r1

r0

q1

q0

1

0

1

0

1

0

1

0

r1

r0

q1

q0

1

1

0

1

0

1

r1

r0

i3

i2

i1

i0

1

0

1

0

1

0

1

1

r1

r0

q1

q0

1

1

0

0

1

0

r1

r0

i3

i2

i1

i0

1

0

1

0

1

1

0

0

r1

r0

q1

q0

1

1

0

0

1

1

r1

r0

i3

i2

i1

i0

1

0

1

0

1

1

0

1

r1

r0

q1

q0

1

1

0

1

0

0

r1

r0

i3

i2

i1

i0

1

0

1

0

1

1

1

0

r1

r0

q1

q0

1

1

0

1

1

1

r1

r0

i3

i2

i1

i0

1

1

1

1

0

0

0

0

r1

r0

q1

q0

1

1

0

1

1

0

r1

r0

i3

i2

i1

i0

1

1

1

1

0

0

0

1

r1

r0

q1

q0

1

0

1

0

1

1

1

1

r1

r0

r1

r0

1

1

1

0

1

0

0

0

1

1

r1

r0

1

1

1

1

0

1

1

0

n3

n2

n1

n0

1

1

1

1

0

1

1

1

n3

n2

n1

n0

1

1

1

1

0

0

1

0

1

0

r1

r0

1

1

1

1

0

0

1

0

1

1

r1

r0

1

1

1

1

0

0

1

1

1

0

r1

r0

1

1

1

1

0

0

1

1

1

1

r1

r0

1

1

0

1

0

0

r1

r0

1

1

1

1

↑↑

↓↓

★

★

★

★

★

★

★

★

★

★

★

Clock

YH ← M(SP), SP ← SP+1

5

←

M(SP), SP ← SP+1

YL

5

←

M(SP), SP ← SP+1

F

↑

5

↓

↓

←

r

SPH

5

←

r

SPL

5

r

←

SPH

5

←

SPL

r

5

←

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

5

7

7

7

7

7

7

7

r+i3~i0

r

←

r+q

r

←

r+i3~i0+C

r

←

r+q+C

r

←

r-q

r

←

r-i3~i0-C

r

←

r-q-C

r

←

rΛi3~i0

r

←

rΛq

r

←

rVi3~i0

r

←

rVq

r

←

r∀i3~i0

r

←

r∀q

r

r-i3~i0

r-q

rΛi3~i0

rΛq

←

d2, d2 ← d1, d1 ← d0, d0 ← C, C ← d3

d3

←

C, d2 ← d3, d1 ← d2, d0 ← d1, C ← d0

d3

M(n3~n0)

M(n3~n0)

M(X)

M(Y)

M(X)

M(Y)

r

←

←

←

M(X)+r+C, X ← X+1

←

M(Y)+r+C, Y ← Y+1

←

M(X)-r-C, X ← X+1

←

M(Y)-r-C, Y ← Y+1

←

r

↑

↑

↓

↓

↑

↑

↓

↓

↑

↑

↓

↓

↑

↑

↓

↓

↑

↑

↓

↓

↑

↑

↓

↓

↑

↑

↓

↓

↑

↓

↑

↓

↑

↓

↑

↓

↑

↓

↑

↓

↑

↑

↓

↓

↑

↑

↓

↓

↑

↓

↑

↓

↑

↑

↓

↓

↑

↑

↓

↓

↑

↑

↓

↓

↑

↑

↓

↓

↑

↑

↓

↓

↑

↑

↓

↓

↑

↑

↓

↓

↑

↑

↓

↓

↑

↓

Operation

M(n3~n0)+1

M(n3~n0)-1

S1C6200/6200A CORE CPU MANUAL EPSON 19

Page 26

3 INSTRUCTION SET

3.1.2 In alphabetical order

Mne-

Page Operand Clock

monic

28

ACPX

28

ACPY

29

ADC

29

30

30

31

31

32

ADD

32

AND

33

33

CALL

34

CALZ

34

CP

35

35

36

36

37

37

DEC

38

38

DI

39

EI

39

FAN

40

40

HALT

41

INC

41

42

42

43

JPBA

43

JP

44

44

45

45

46

LBPX

46

MX, r

MY, r

r, i

r, q

XH, i

XL, i

YH, i

YL, i

r, i

r, q

r, i

r, q

s

s

r, i

r, q

XH, i

XL, i

YH, i

YL, i

Mn

SP

r, i

r, q

Mn

SP

X

Y

C, s

NC, s

NZ, s

s

Z, s

MX, e

B

1

1

1

1

1

1

1

1

1

1

1

1

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

1

Operation Code Flag

A

9

8

7

6

5

4

1

1

1

0

0

1

0

1

1

1

0

0

1

0

1

0

0

0

1

r1

r0

0

1

0

1

0

0

1

0

1

0

0

0

0

0

0

1

0

0

0

0

1

0

1

0

0

0

1

0

0

1

0

0

0

1

1

1

0

0

0

0

r1

r0

0

1

0

1

0

0

0

1

0

0

1

0

r1

r0

0

1

0

1

1

0

0

1

0

0

s7

s6

s5

s4

1

0

1

s7

s6

s5

s4

1

0

1

1

1

r1

r0

1

1

1

0

0

0

0

0

1

0

0

1

0

0

0

1

0

0

1

0

1

0

1

0

0

1

1

0

0

1

0

0

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

0

0

1

1

1

0

1

0

1

1

1

1

0

1

0

0

1

0

1

1

0

r1

r0

1

1

1

0

0

0

1

1

1

1

1

1

1

1

1

1

1

0

1

1

0

1

1

1

1

1

0

1

1

1

0

1

1

1

0

1

1

0

1

1

1

1

1

1

1

1

1

1

0

0

1

0

s7

s6

s5

s4

0

1

1

s7

s6

s5

s4

1

1

1

s7

s6

s5

s4

0

0

0

s7

s6

s5

s4

1

1

0

s7

s6

s5

s4

0

0

1

e7

e6

e5

e4

3

2

1

0

IDZC

1

0

r1

r0

↑

↑

★

1

1

r1

r0

★

i3

i2

i1

i0

★

r1