Page 1

MF1517-01

CMOS 32-BIT SINGLE CHIP MICROCOMPUTER

S1C33210

Technical Manual

S1C33210 PRODUCT PART

S1C33210 FUNCTION PART

Page 2

NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written

permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice.

Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material

or due to its application or use in any product or circuit and, further, there is no representation that this material

is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any

intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that

anything made in accordance with this material will be free from any patent or copyright infringement of a third

party. This material or portions thereof may contain technology or the subject relating to strategic products under

the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from

the Ministry of International Trade and Industry or other approval from another government agency.

2002 All rights reserved.

Page 3

S1C33210 Technical Manual

This manual describes the hardware specifications of the Seiko Epson original 32-bit microcomputer S1C33210.

S1C33210 PRODUCT PART

Describes the hardware specifications of the S1C33210 except for details of the peripheral circuits.

S1C33210 FUNCTION PART

Describes details of all the peripheral circuit blocks for the S1C33 Family microcomputers.

R e f e r t o t he " S 1C 33 000 C or e C P U M a nua l " f or de t a i l s of t he S 1C 330 00 32- bi t R I S C C P U .

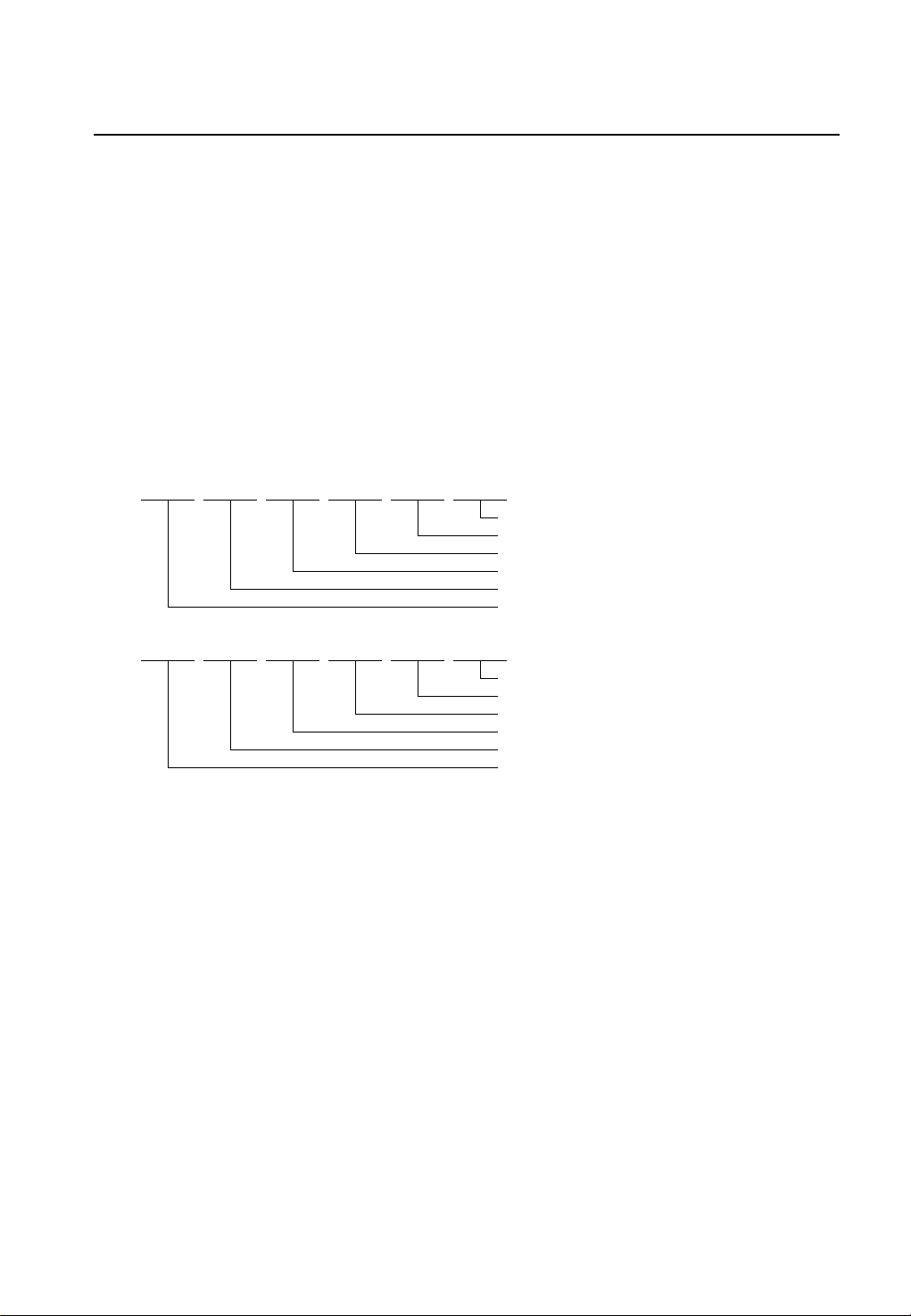

New configuration of product number

Starting April 1, 2001, the configuration of product number descriptions will be changed as listed

below. To order from April 1, 2001 please use these product numbers. For further information, please

contact Epson sales representative.

Devices

S1

C 33104 F 0A01

Development tools

S5U1

C 33L01 D1 1

00

Packing specification

Specification

Package (D: die form; F: QFP)

Model number

Model name (C: microcomputer, digital products)

Product classification (S1: semiconductor)

00

Packing specification

Version (1: Version 1)

Tool type (D1: Development Tool)

Corresponding model number (33L01: for S1C33L01)

Tool classification (C: microcomputer use)

Product classification

(S5U1: development tool for semiconductor products)

Page 4

Page 5

TABLE OF CONTENTS

S1C33210 PRODUCT PART

Table of Contents

1 Outline.....................................................................................................................A-1

1.1 Features...............................................................................................................................................................A-1

1. 2 Bl o c k D iag r a m ...................................................................................................................................................A-3

1.3 Pin Description ..................................................................................................................................................A-4

1.3.1 Pin Layout Diagram (plastic package)...................................................................................A-4

1. 3 . 2 P i n F u nct i o n s ...................................................................................................................................A-5

2 Power Supply ........................................................................................................ A-11

2.1 Power Supply Pins.........................................................................................................................................A-11

2.2 Operating Voltage (V

2.3 Power Supply for Analog Circuits (AV

3 Internal Memory....................................................................................................A-13

3.1 ROM and Boot Address...............................................................................................................................A-13

3.2 RAM.....................................................................................................................................................................A-13

4 Peripheral Circuits................................................................................................A-14

4.1 List of Peripheral Circuits............................................................................................................................A-14

4.2 I/O Memory Map.............................................................................................................................................A-15

DD, VSS)....................................................................................................................A-11

DD)..............................................................................................A-12

5 Po we r -D o w n C o n tr o l.............................................................................................A-62

6 Ba si c E xt er na l Wi ri ng Diagr am..............................................................................A-65

7 Precautions on Mounting......................................................................................A-66

8 El ec t r i c a l C h a r a c t e r i s t i c s......................................................................................A-6 8

8.1 Absolute Maximum Rating..........................................................................................................................A-68

8.2 Recommended Operating Conditions ....................................................................................................A-69

8.3 DC Characteristics..........................................................................................................................................A-70

8.4 Current Consumption....................................................................................................................................A-71

8.5 A/D Converter Characteristics...................................................................................................................A-72

8.6 AC Characteristics..........................................................................................................................................A-74

8.6.1 Symbol Description.....................................................................................................................A-74

8.6.2 AC Characteristics Measurement Condition......................................................................A-74

8.6.3 C3 3 Block AC Characteristic Tables....................................................................................A-75

8.6.4 C33 Block AC Characteristic Timing Charts.......................................................................A-78

8.7 Oscillation Characteristics...........................................................................................................................A-85

8.8 PLL Characteristics........................................................................................................................................A-86

9 Package ................................................................................................................ A-87

9.1 Plastic Package...............................................................................................................................................A-87

10 Pad Layout............................................................................................................A-88

10.1 Pad Layout Diagram.....................................................................................................................................A-88

10.2 Pad Co ordinate ...............................................................................................................................................A-89

EPSON i

Page 6

TABLE OF CONTENTS

Appendix A <Reference> External Device Interface Timings......................................A-92

A.1 DRAM (70ns)....................................................................................................................................................A-93

A.2 DRAM (60ns)....................................................................................................................................................A-96

A.3 ROM and Burst ROM.................................................................................................................................A-100

A.4 SRAM (55ns).................................................................................................................................................A-102

A.5 SRAM (70ns).................................................................................................................................................A-104

A.6 8255A...............................................................................................................................................................A-106

Appendix B Pin Characteristics................................................................................A-107

ii EPSON

Page 7

TABLE OF CONTENTS

S1C33210 FUNCTION PART

Table of Contents

I OUTLINE

I-1 INTRODUCTION............................................................................................... B-I-1-1

I-2 BLOCK DIAGRAM............................................................................................ B-I-2-1

I-3 LIST O F PINS................................................................................................... B-I-3-1

List of External I/O Pins.....................................................................................................................................B-I-3-1

II CORE BLOCK

II-1 INTRODUCTION.............................................................................................. B-II-1-1

II-2 CPU AND OPERATING MODE......................................................................... B-II-2-1

CPU.........................................................................................................................................................................B-II-2-1

Standby Mode.....................................................................................................................................................B-II-2-2

HALT Mode............................................................................................................................................B-II-2-2

SLEEP Mode.........................................................................................................................................B-II-2-2

Notes on Standby Mode...................................................................................................................B-II-2-3

Test Mode.............................................................................................................................................................B-II-2-3

Debug Mode.........................................................................................................................................................B-II-2-3

Trap Table.............................................................................................................................................................B-II-2-4

II-3 INITIAL RESET ................................................................................................ B-II-3-1

Pins for Initial Reset...........................................................................................................................................B-II-3-1

Cold Start and Hot Start..................................................................................................................................B-II-3-1

Power-on Reset..................................................................................................................................................B-II-3-2

Reset Pulse ..........................................................................................................................................................B-II-3-2

Boot Address........................................................................................................................................................B-II-3-3

Notes Related to Initial Reset........................................................................................................................B-II-3-3

II-4 BCU (BUS CONTROL UNIT) ............................................................................B-II-4-1

Pin Assignment for External System Interface.......................................................................................B-II-4-1

I/ O P i n L i s t ..............................................................................................................................................B-II-4-1

Combination of System Bus Control Signals............................................................................B-II-4-3

Memory Area........................................................................................................................................................B-II-4-4

Memory Map..........................................................................................................................................B-II-4-4

External Memory Map and Chip Enable .....................................................................................B-II-4-5

Using Internal Memory on External Memory Area..................................................................B-II-4-7

Exclusive Signals for Areas .............................................................................................................B-II-4-7

Ar e a 1 0 ....................................................................................................................................................B-II-4-8

Ar e a 3 ......................................................................................................................................................B-II-4-8

Setting External Bus Conditions...................................................................................................................B-II-4-9

Setting Device Type and Size ........................................................................................................B-II-4-9

Setting SRAM Timing Conditions.................................................................................................B-II-4-10

Setting Timing Conditions of Burst ROM ..................................................................................B-II-4-11

Bus Operation....................................................................................................................................................B-II-4-12

Data Arrangement in Memory.......................................................................................................B-II-4-12

Bus Operation of External Memory.............................................................................................B-II-4-12

Bus Clock.............................................................................................................................................................B-II-4-16

EPSON iii

Page 8

TABLE OF CONTENTS

Bus Speed Mode ...............................................................................................................................B-II-4-17

Bus Clock Output...............................................................................................................................B-II-4-17

Bus Cycles in External System Interface................................................................................................B-II-4-18

SRAM Read Cycles...........................................................................................................................B-II-4-18

Bus Timing............................................................................................................................................B-II-4-19

SRAM Write Cycles...........................................................................................................................B-II-4-20

Burst ROM Read Cycles .................................................................................................................B-II-4-22

DRAM Direct Interface....................................................................................................................................B-II-4-23

Outline of DRAM Interface .............................................................................................................B-II-4-23

DRAM Setting Conditions...............................................................................................................B-II-4-24

DRAM Read/Write Cycles...............................................................................................................B-II-4-27

DRAM Refresh Cycles.....................................................................................................................B-II-4-30

Re l e a s ing E x t ern a l Bus .................................................................................................................................B-II-4-31

Power-down Control by External Device ................................................................................................B-II-4-32

I/O Memory of BCU.........................................................................................................................................B-II-4-33

II-5 ITC (Interrupt Controller).................................................................................B-II-5-1

Outline of Interrupt Functions.........................................................................................................................B-II-5-1

Maskable Interrupts.............................................................................................................................B-II-5-1

Interrupt Factors and Intelligent DMA...........................................................................................B-II-5-3

Nonmaskable Interrupt (NMI)..........................................................................................................B-II-5-3

Interrupt Processing by the CPU....................................................................................................B-II-5-3

Clearing Standby Mode by Interrupts...........................................................................................B-II-5-3

Trap Table.............................................................................................................................................................B-II-5-4

Control of Maskable Interrupts......................................................................................................................B-II-5-5

Structure of the Interrupt Controller...............................................................................................B-II-5-5

Processor Status Register (PSR)...................................................................................................B-II-5-5

Interrupt Factor Flag and Interrupt Enable Register...............................................................B-II-5-6

Interrupt Priority Register and Interrupt Levels.........................................................................B-II-5-8

IDMA Invocation..................................................................................................................................................B-II-5-9

HSDMA Invocation...........................................................................................................................................B-II-5-11

I/O Memory of Interrupt Controller .............................................................................................................B-II-5-12

Programming Notes.........................................................................................................................................B-II-5-25

II-6 CLG (Clock Generator)....................................................................................B-II-6-1

Configuration of Clock Generator.................................................................................................................B-II-6-1

I/O Pins of Clock Generator...........................................................................................................................B-II-6-2

High-Speed (OSC3) Oscillation Circuit.......................................................................................................B-II-6-2

PLL .........................................................................................................................................................................B-II-6-3

Controlling Oscillation.......................................................................................................................................B-II-6-3

Setting and Switching Over the CPU Operating Clock.........................................................................B-II-6-4

Power-Control Register Protection Flag....................................................................................................B-II-6-5

Operation in Standby Mode...........................................................................................................................B-II-6-5

I/O Memory of Clock Generator....................................................................................................................B-II-6-6

Programming Notes...........................................................................................................................................B-II-6-9

II-7 DBG (Debug Unit)............................................................................................B-II-7-1

Debug Circuit........................................................................................................................................................B-II-7-1

I/O Pins of Debug Circuit.................................................................................................................................B-II-7-1

iv EPSON

Page 9

TABLE OF CONTENTS

III PERIPHERAL BLOCK

III-1 INTRODUCTION ............................................................................................ B-III-1-1

III-2 PRESCALER.................................................................................................B-III-2-1

Configuration of Prescaler..............................................................................................................................B-III-2-1

Source Clock.......................................................................................................................................................B-III-2-1

Selecting Division Ratio and Output Control for Prescaler...............................................................B-III-2-2

Source Clock Output to 8-Bit Programmable Timer.............................................................................B-III-2-2

I/O Memory of Prescaler.................................................................................................................................B-III-2-3

Programming Notes..........................................................................................................................................B-III-2-7

III-3 8-BIT PROGRAMMABLE TIMERS .................................................................B-III-3-1

Configuration of 8-Bit Programmable Timer............................................................................................B-III-3-1

Output Pins of 8-Bit Programmable Timers.............................................................................................B-III-3-1

Uses of 8-Bit Programmable Timers...........................................................................................................B-III-3-2

Control and Operation of 8-Bit Programmable Timer ..........................................................................B-III-3-4

Co n t r o l o f Clo c k Ou tpu t ...................................................................................................................................B-III-3-7

8-Bit Programmable Timer Interrupts and DMA.....................................................................................B-III-3-8

I/O Memory of 8-Bit Programmable Timers...........................................................................................B-III-3-10

Programming Notes........................................................................................................................................B-III-3-17

III-4 16-BIT PROGRAMMABLE TIMERS................................................................ B-III-4-1

Configuration of 16-Bit Programmable Timer..........................................................................................B-III-4-1

I/O Pins of 16-Bit Programmable Timers..................................................................................................B-III-4-2

Uses of 16-Bit Programmable Timers........................................................................................................B-III-4-3

Control and Operation of 16-Bit Programmable Timer........................................................................B-III-4-4

Co n t r o lli n g C loc k Ou tpu t .................................................................................................................................B-III-4-7

16-Bit Programmable Timer Interrupts and DMA..................................................................................B-III-4-9

I/O Memory of 16-Bit Programmable Timers.........................................................................................B-III-4-12

Programming Notes........................................................................................................................................B-III-4-25

III-5 WATCHDOG TIMER ...................................................................................... B-III-5-1

Configuration of Watchdog Timer................................................................................................................B-III-5-1

Control of Watchdog Timer............................................................................................................................B-III-5-1

Operation in Standby Modes........................................................................................................................B-III-5-2

I/O Memory of Watchdog Timer...................................................................................................................B-III-5-3

Programming Notes..........................................................................................................................................B-III-5-3

III-6 LOW-SPEED (OSC1) OSCILLATION CIRCUIT...............................................B-III-6-1

Configuration of Low-Speed (OSC1) Oscillation Circuit......................................................................B-III-6-1

I/O Pins of Low-Speed (OSC1) Oscillation Circuit................................................................................B-III-6-1

Oscillator Types.................................................................................................................................................B-III-6-2

Controlling Oscillation......................................................................................................................................B-III-6-3

Switching Over the CPU Operating Clock................................................................................................B-III-6-3

Power-Control Register Protection Flag...................................................................................................B-III-6-4

Operation in Standby Mode..........................................................................................................................B-III-6-4

OSC1 Clock Output to External Devices..................................................................................................B-III-6-4

I/O Memory of Clock Generator...................................................................................................................B-III-6-5

Programming Notes..........................................................................................................................................B-III-6-8

EPSON v

Page 10

TABLE OF CONTENTS

III-7 CLOCK TIMER ...............................................................................................B-III-7-1

Configuration of Clock Timer.........................................................................................................................B-III-7-1

Control and Operation of the Clock Timer...............................................................................................B-III-7-2

Interrupt Function..............................................................................................................................................B-III-7-4

Examples of Use of Clock Timer.................................................................................................................B-III-7-6

I/O Memory of Clock Timer............................................................................................................................B-III-7-7

Programming Notes........................................................................................................................................B-III-7-12

III-8 SERIAL INTERFACE......................................................................................B-III-8-1

Configuration of Serial Interfaces ................................................................................................................B-III-8-1

Features of Serial Interfaces...........................................................................................................B-III-8-1

I/ O P i n s of Se r i al Int e r f a c e .............................................................................................................................B-III-8-2

Setting Transfer Mode ......................................................................................................................B-III-8-3

Clock-Synchronized Interface.......................................................................................................................B-III-8-4

Outline of Clock-Synchronized Interface....................................................................................B-III-8-4

Setting Clock-Synchronized Interface.........................................................................................B-III-8-5

Control and Operation of Clock-Synchronized Transfer ......................................................B-III-8-7

Asynchronous Interface ................................................................................................................................B-III-8-12

Outline of Asynchronous Interface.............................................................................................B-III-8-12

Setting Asynchronous Interface ..................................................................................................B-III-8-13

Control and Operation of Asynchronous Transfer................................................................B-III-8-16

IrDA Interface ....................................................................................................................................................B-III-8-21

Outline of IrDA Interface.................................................................................................................B-III-8-21

Se t t i n g Ir D A In t e r f a c e......................................................................................................................B-III-8-21

Control and Operation of IrDA Interface...................................................................................B-III-8-23

Serial Interface Interrupts and DMA.........................................................................................................B-III-8-24

I/O Memory of Serial Interface....................................................................................................................B-III-8-28

Programming Notes........................................................................................................................................B-III-8-46

III-9 INPUT/OUTPUT PORTS .................................................................................B-III-9-1

Input Ports (K Ports).........................................................................................................................................B-III-9-1

Structure of Input Port.......................................................................................................................B-III-9-1

Input-Port Pins.....................................................................................................................................B-III-9-2

Notes on Use........................................................................................................................................B-III-9-2

I/O Memory of Input Ports...............................................................................................................B-III-9-3

I/O Ports (P Ports).............................................................................................................................................B-III-9-4

Structure of I/O Port...........................................................................................................................B-III-9-4

I/ O P o r t Pi n s .........................................................................................................................................B-III-9-4

I/O Control Register and I/O Modes............................................................................................B-III-9-5

I/O Memory of I/O Ports...................................................................................................................B-III-9-6

Input Interrupt...................................................................................................................................................B-III-9-11

Port Input Interrupt ...........................................................................................................................B-III-9-11

Key Input Interrupt............................................................................................................................B-III-9-13

Control Registers of the Interrupt Controller..........................................................................B-III-9-15

I/O Memory for Input Interrupts...................................................................................................B-III-9-17

Programming Notes.........................................................................................................................B-III-9-23

III-10 Mobile Access Interfaces ............................................................................B-III-10-1

Configuration of Mobile Access Interfaces............................................................................................B-III-10-1

I/ O P i n s fo r M o b i l e Ac c e s s I n t e r f a c e s.......................................................................................B - I II-10-2

Basic Settings for Mobile Access Interfaces..........................................................................B-III-10-4

UART Communications Mode....................................................................................................................B-III-10-7

Overview...............................................................................................................................................B-III-10-7

PDC Communications Mode.......................................................................................................................B-III-10-8

vi EPSON

Page 11

TABLE OF CONTENTS

Overview...............................................................................................................................................B-III-10-8

PDC Communications Control and Operation....................................................................B-III-10-10

PHS Communications Mode....................................................................................................................B-III-10-11

PHS Communications Control and Operation....................................................................B-III-10-13

HDLC Communications Mode.................................................................................................................B-III-10-14

Overview............................................................................................................................................B-III-10-14

HDLC Communications Control and Operation.................................................................B-III-10-15

Mobile Access Interface Interrupts ........................................................................................................B-III-10-18

Overview............................................................................................................................................B-III-10-18

Mobile Access Interface Interrupt Outputs...........................................................................B-III-10-20

I/O Memory for Mobile Access Interfaces...........................................................................................B-III-10-21

Important Notes on Debugging...............................................................................................................B-III-10-42

EPSON vii

Page 12

TABLE OF CONTENTS

IV ANALOG BLOCK

IV-1 INTRODUCTION............................................................................................B-IV-1-1

IV-2 A/D CONVERTER.......................................................................................... B-IV-2-1

Features and Structure of A/D Converter................................................................................................B-IV-2-1

I/O Pins of A/D Converter ..............................................................................................................................B-IV-2-2

Setting A/D Converter.....................................................................................................................................B-IV-2-3

Control and Operation of A/D Conversion ...............................................................................................B-IV-2-5

A/D Converter Interrupt and DMA...............................................................................................................B-IV-2-7

I/O Memory of A/D Converter .......................................................................................................................B-IV-2-9

Programming Notes.......................................................................................................................................B-IV-2-15

V DMA BLOCK

V-1 INTRODUCTION............................................................................................. B-V-1-1

V-2 HSDMA (HIGH-SPEED DMA).......................................................................... B-V-2-1

Functional Outline of HSDMA........................................................................................................................B-V-2-1

I/O Pins of HSDMA ............................................................................................................................................B-V-2-2

Programming Control Information................................................................................................................B-V-2-3

Setting the Registers in Dual-Address Mode ............................................................................B-V-2-3

Setting the Registers in Single-Address Mode ........................................................................B-V-2-6

Enabling/Disabling DMA Transfer.................................................................................................................B-V-2-7

Trigger Factor.......................................................................................................................................................B-V-2-8

Operation of HSDMA.........................................................................................................................................B-V-2-9

Operation in Dual-Address Mode ..................................................................................................B-V-2-9

Operation in Single-Address Mode............................................................................................B-V-2-12

Timing Chart........................................................................................................................................B-V-2-13

Interrupt Function of HSDMA......................................................................................................................B-V-2-15

I/O Memory of HSDMA..................................................................................................................................B-V-2-17

Programming Notes........................................................................................................................................B-V-2-36

V-3 IDMA (Intelligent DMA) .................................................................................. B-V-3-1

Functional Outline of IDMA.............................................................................................................................B-V-3-1

Programming Control Information................................................................................................................B-V-3-1

IDMA Invocation..................................................................................................................................................B-V-3-5

Operation of IDMA..............................................................................................................................................B-V-3-8

Linking.................................................................................................................................................................B-V-3-12

Interrupt Function of Intelligent DMA........................................................................................................B-V-3-13

I/O Memory of Intelligent DMA ...................................................................................................................B-V-3-14

Programming Notes........................................................................................................................................B-V-3-17

APPENDIX I/O MAP................................................................................... B-Appendix-1

viii EPSON

Page 13

S1C33210

PRODUCT PART

Page 14

Page 15

1 OUTLINE

1 Outline

The S1C33210 is a Seiko Epson original 32-bit microcomputer. It features high speed, low power consumption,

and low-voltage operation, and is ideal for portable products that require high-speed data processing.

The S1C33210 consists of an S1C33000 32-bit RISC type CPU as its core, peripheral circuits including a bus control

unit, DMA controller, interrupt controller, timers, serial interface, and A/D converter, and also mobile access

interface and RAM. A high-speed oscillation circuit and PLL, and a low-speed clock input circuit, are also included,

supporting advanced operation, power-saving operation, and high-speed realtime clock functions. Use of the internal

MAC (multiplication and accumulation) function in combination with the A/D converter also facilitates the design of

systems requiring DSP functions, such as speech recognition and synthesis applications.

Table 1.1 shows the various models. The package and data bus interface vary according to the model.

Table 1.1 Model Lineup

Package Internal RAM Internal ROM Data bus I/F

QFP15-128pin 8K bytes None CMOS/LVTTL

Notes: • The end of the S1C33210 subcode is not related to model identification.

1.1 Features

Core CPU

Seiko Epson original 32-bit RISC CPU S1C33000 built-in

• Basic instruction set: 105 instructions (16-bit fixed size)

• Sixteen 32-bit general-purpose register

• 32-bit ALU and 8-bit shifter

• Multiplication/division instructions and MAC (multiplication and accumulation) instruction are available

• 20.0 ns of minimum instruction execution time at 50 MHz operation

Internal memory

ROM: None

RAM: 8K bytes

Internal peripheral circuits

Oscillation circuit: High-speed (OSC3) oscillation circuit 33 MHz max.

Crystal/ceramic oscillator or external clock input

Low-speed (OSC1) oscillation circuit 32.768 kHz typ.

Crystal oscillator or external clock input

Timers: 8-bit timer 6 channels

16-bit timer 6 channels

Watchdog timer (16-bit timer 0's function)

Clock timer 1 channel (with alarm function)

Serial interface: 4 channels (clock-synchronous system, asynchronous system and IrDA

interface are selectable. Interfaces 1 and 3 support only asynchronous

operation.)

A/D converter: 10 bits × 4 channels

DMA controller: High-speed DMA 4 channels (Only two channels support external

requests.)

Intelligent DMA 128 channels

Interrupt controller: Possible to invoke DMA

Input interrupt 10 types (programmable)

DMA controller interrupt 5 types

16-bit programmable timer interrupt 12 types

8-bit programmable timer interrupt 4 types

Serial interface interrupt 6 types

A/D converter interrupt 1 type

Clock timer interrupt 1 type

S1C33210 PRODUCT PART EPSON A-1

Page 16

1 OUTLINE

General-purpose input Shared with the I/O pins for internal peripheral circuits

and output ports: Input port 7 bits

I/O port 27 bits

Mobile access interfaces One PHS, PDC, and HDLC channel each

External bus interface

BCU (bus control unit) built-in

• 24-bit address bus (internal 28-bit processing)

• 16-bit data bus

Data size is selectable from 8 bits and 16 bits in each area.

• Little-endian memory access; big-endian may be set in each area.

• Memory mapped I/O

• Chip enable and wait control circuits built-in

• DRAM direct interface function built-in

Supports fast page mode and EDO page mode.

Supports self-refresh and CAS-before RAS refresh.

• Supports burst ROM.

Operating conditions and power consumption

Operating voltage: VDD 2.7 V to 3.6 V

Operating clock frequency: CPU

50 MHz max.

25 MHz max. (Mobile access interfaces)

Operating temperature: -40 to 85°C

Power consumption: During SLEEP 4 µW typ.

During HALT 122 mW typ.

(3.3 V, 50 MHz)

During execution 238 mW typ.

(3.3 V, 50 MHz)

Supply form

QFP15-128 pin plastic package.

Note: • The values of power consumption during execution were measured when a test

program that consisted of 55% load instructions, 23% arithmetic operation

instructions, 1% mac instruction, 12% branch instructions and 9% ext

instruction was being continuously executed.

A-2 EPSON S1C33210 PRODUCT PART

Page 17

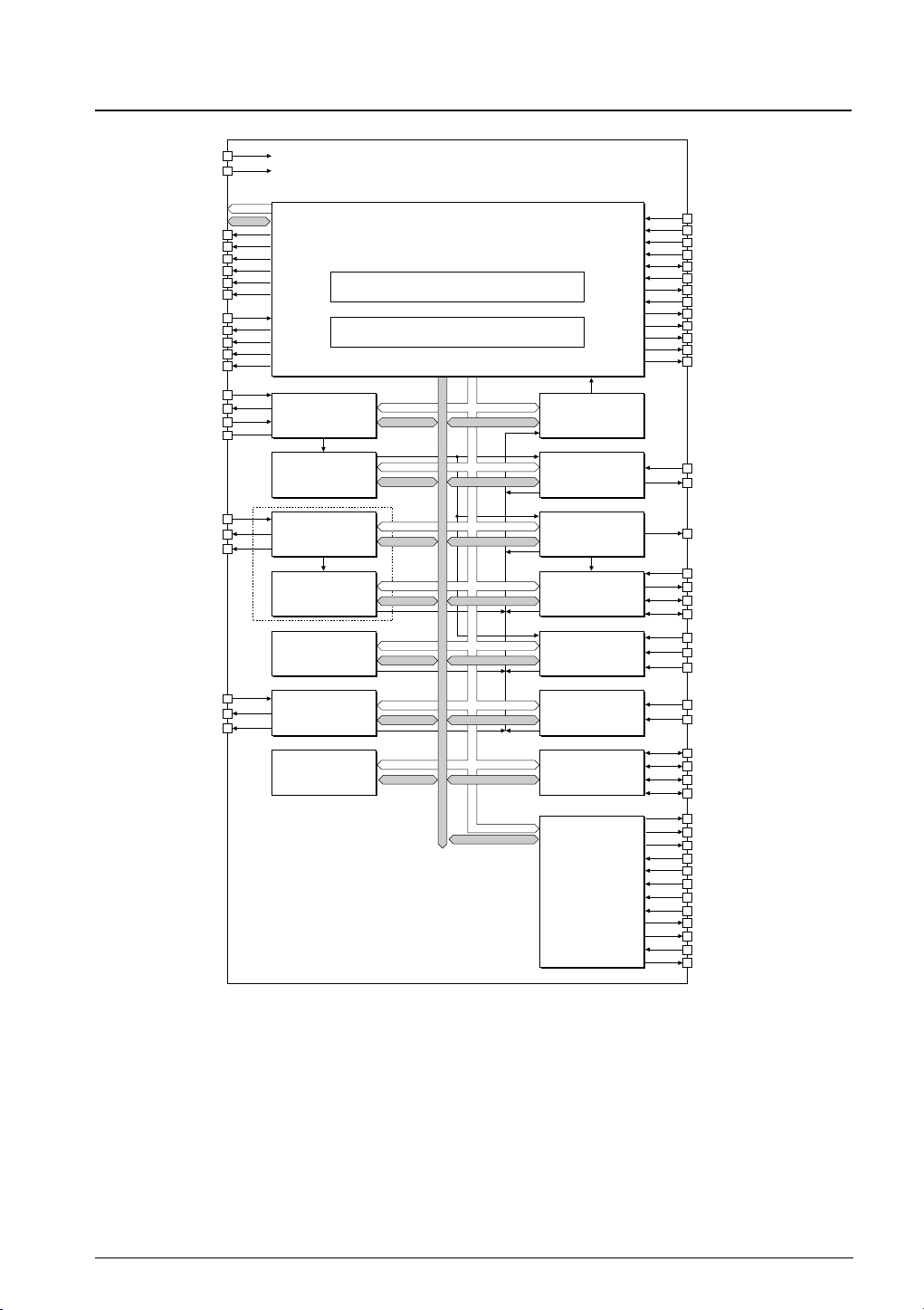

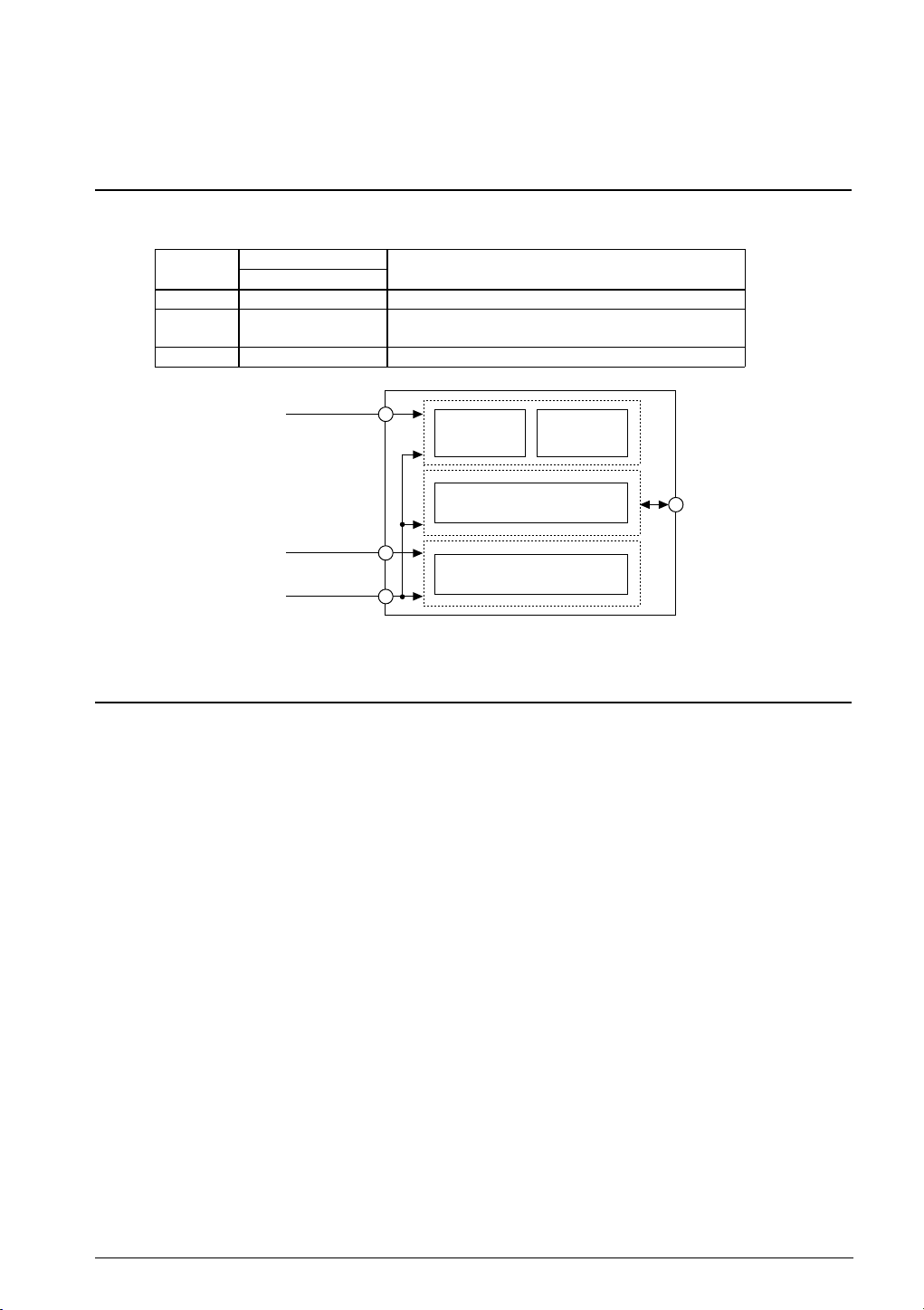

1.2 Block Diagram

VDD

VSS

1 OUTLINE

S1C33210

A[23:0]

D[15:0]

#WRL/#WR/#WE

#CE10EX #CE[9:4]

#DMAREQx(K50, K51)

#DMAACKx(P32, P33)

#DMAENDx(P15, P16)

#RD

#WRH/#BSH

#HCAS

#LCAS

#WAIT(P30)

#DRD(P20)

#DWE(P21)

#GAAS(P21)

#GARD(P31)

OSC3

OSC4

PLLS[1:0]

PLLC

OSC1

OSC2

FOSC1(P14)

OSC3/PLL

Prescaler

OSC1

Clock

Timer

Intelligent

DMA (128 ch.)

High-speed

DMA (4 ch.)

RAM

8KB

S1C33000

CPU Core

Bus Control Unit

Interrupt

Controller

16-bit

Programmable

Timer (6 ch.)

8-bit

Programmable

Timer (6 ch.)

Serial Interface

(4 ch.)

A/D Converter

(4 ch.)

Input Port

I/O Port

Mobile Access

Interface

#RESET

#NMI

#X2SPD

TST

DSIO

EA10MD[1:0]

BCLK

#BUSREQ(P34)

#BUSACK(P35)

#BUSGET(P31)

DST[2:0](P10–12)

DPCO(P13)

DCLK(P14)

EXCLx(P10–13, P15, P16)

TMx(P22–27)

T8UFx(P10–13)

SINx(P00, P04, P27, RXD)

SOUTx(P01, P05, P26, TXD)

#SCLKx(P02, P25)

#SRDYx(P03, P24)

AD0–3(K60–63)

#ADTRG(K52)

DD

AV

K50–52

K60–63

P00–05

P10–16

P20–27

P30–35

DTR

RTS

TXD

RI

CTS

DCD

DSR

RXD

CNT1

CNT2

MSEL

GOUT

Figure 1.2.1 S1C33210 Block Diagram

S1C33210 PRODUCT PART EPSON A-3

Page 18

1 OUTLINE

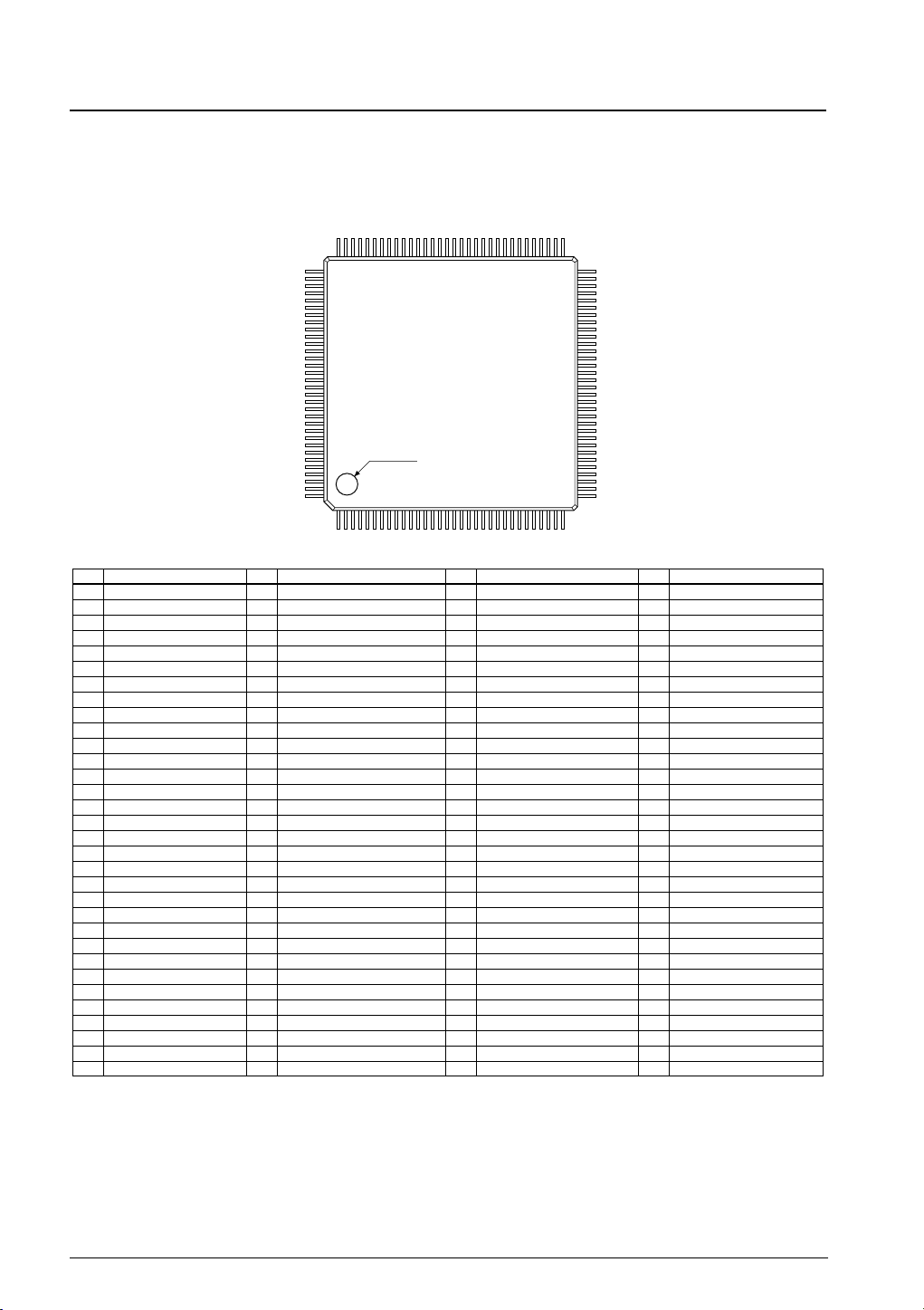

1.3 Pin Description

1.3.1 Pin Layout Diagram (plastic package)

QFP15-128pin

6596

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

Pin name

P26/TM4/SOUT2

P27/TM5/SIN2

SS

V

BCLK

P00/SIN0

P01/SOUT0

D15

DD

V

P03/#SRDY0

D14

P31/#BUSGET/#GARD

D13

P32/#DMAACK0

D12

P33/#DMAACK1

D11

P02/#SCLK0

D10

K50/#DMAREQ0

#WRL/#WR/#WE

#WRH/#BSH

VSS

K51/#DMAREQ1

#RD

D9

D8

DD

V

K63/AD3

K62/AD2

AVDD

K61/AD1

K60/AD0

97

INDEX

128

No.

33

K52/#ADTRG

34

#CE10EX/#CE9&10EX

35

#CE4/#CE11/#CE11&12

36

D7

37

D6

38

D5

39

V

D4

40

D3

41

D2

42

#RESET

43

#NMI

44

D1

45

D0

46

V

47

#CE9/#CE17/#CE17&18

48

#CE7/#RAS0/#CE13/#RAS2

49

OSC2

50

OSC1

51

#CE6/#CE7&8

52

#CE8/#RAS1/#CE14/#RAS3

53

V

54

A0/#BSL

55

A1

56

A2

57

A3

58

P35/#BUSACK

59

#HCAS

60

#LCAS

61

P34/#BUSREQ/#CE6

62

A4

63

A5

64

Pin name

SS

DD

SS

No.

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

Pin name

A6

A7

SS

V

P30/#WAIT/#CE4&5

A8

A9

#CE5/#CE15/#CE15&16

A10

A20

DD

V

A11

A21

P16/EXCL5/#DMAEND1

A12

A22

TST

A13

A23

P04/SIN1

A14

A15

P05/SOUT1

A16

A17

A18

SS

V

A19

P20/#DRD

DD

V

RTS

DTR

DSR

Figure 1.3.1 Pin Layout Diagram (QFP15-128pin)

64

33

321

No.

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

Pin name

RI

CNT2

CNT1

TXD/SOUT3

CTS

SS

V

PLLC

V

SS

PLLS1

PLLS0

RXD/SIN3

DCD

MSEL

GOUT

DD

V

OSC3

OSC4

EA10MD0

EA10MD1

#X2SPD

P21/#DWE/#GAAS

P22/TM0

P23/TM1

DSIO

P10/EXCL0/T8UF0/DST0

P11/EXCL1/T8UF1/DST1

P12/EXCL2/T8UF2/DST2

P13/EXCL3/T8UF3/DPC0

P14/FOSC1/DCLK

P24/TM2/#SRDY2

P25/TM3/#SCLK2

P15/EXCL4/#DMAEND0

A-4 EPSON S1C33210 PRODUCT PART

Page 19

1.3.2 Pin Functions

Table 1.3.1 List of Pins for Power Supply System

Pin name Pin No. I/O Pull-up Function

QFP15-128

VDD 8, 27, 47, 74, 93, 111 ––Power supply (+)

VSS 3, 22, 39, 54, 67, 90,

102, 104

AVDD 30 ––Analog system power supply (+); AVDD = VDD

Table 1.3.2 List of Pins for External Bus Interface Signals

Pin name Pin No. I/O Pull-up Function

QFP15-128

A0

#BSL

A[23:1] 56-58, 63-66, 69, 70, 72,

75, 78, 81, 84, 85, 87-89,

D[15:0] 7, 10, 12, 14, 16, 18, 25, 26,

#CE10EX

#CE9&10EX

#CE9

#CE17

#CE17&18

#CE8

#RAS1

#CE14

#RAS3

#CE7

#RAS0

#CE13

#RAS2

#CE6

#CE7&8

#CE5

#CE15

#CE15&16

55 O – A0: Address bus (A0) when SBUSST(D3/0x4812E) = "0" (default)

91, 73, 76, 79, 82

36-38, 40-42, 45, 46

34 O – Area 10 chip enable for external memory

48 O – #CE9: Area 9 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00"

53 O – #CE8: Area 8 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00"

49 O – #CE7: Area 7 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00"

52 O – Area 6 chip enable

71 O – #CE5: Area 5 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00"

– (104

O – Address bus (A1 to A23)

I/O – Data bus (D0 to D15)

Power supply (-); GND

Pull-

down)

#BSL: Bus strobe (low byte) signal when SBUSST(D3/0x4812E) = "1"

* When CEFUNC[1:0] = "1x", this pin outputs #CE9+#CE10EX signal.

(default)

#CE17: Area 17 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01"

* When CEFUNC[1:0] = "1x", this pin outputs #CE17+#CE18 signal.

and A8DRA(D8/0x48128) = "0" (default)

#RAS1: Area 8 DRAM row strobe when CEFUNC[1:0](D[A:9])/0x48130) =

"00" and A8DRA(D8/0x48128) = "1"

#CE14: Area 14 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01"

or "1x" and A14DRA(D8/0x48122) = "0"

#RAS3: Area 14 DRAM row strobe when CEFUNC[1:0](D[A:9])/0x48130)

= "01"or "1x" and A14DRA(D8/0x48122) = "1"

and A7DRA(D7/0x48128) = "0" (default)

#RAS0: Area 7 DRAM row strobe when CEFUNC[1:0](D[A:9])/0x48130) =

"00" and A7DRA(D7/0x48128) = "1"

#CE13: Area 13 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01"

or "1x" and A13DRA(D7/0x48122) = "0"

#RAS2: Area 13 DRAM row strobe when CEFUNC[1:0](D[A:9])/0x48130)

= "01" or "1x" and A13DRA(D7/0x48122) = "1"

* When CEFUNC[1:0] = "1x", this pin outputs #CE7+#CE8 signal.

(default)

#CE15: Area 15 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01"

* When CEFUNC[1:0] = "1x", this pin outputs #CE15+#CE16 signal.

1 OUTLINE

S1C33210 PRODUCT PART EPSON A-5

Page 20

1 OUTLINE

Pin name Pin No. I/O Pull-up Function

QFP15-128

#CE4

#CE11

#CE11&12

#RD 24 O – Read signal

#WRL

#WR

#WE

#WRH

#BSH

#HCAS 60 O – #HCAS: DRAM column address strobe (high byte) signal

#LCAS 61 O – #LCAS: DRAM column address strobe (low byte) signal

BCLK 4 O – Bus clock output

P34

#BUSREQ

#CE6

P35

#BUSACK

P30

#WAIT

#CE4&5

P20

#DRD

P21

#DWE

#GAAS

P31

#BUSGET

#GARD

EA10MD1 115 I Pull-up Area 10 boot mode selection

EA10MD0 114 I – 10–

35 O – #CE4: Area 4 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00"

(default)

#CE11: Area 11 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01"

* When CEFUNC[1:0] = "1x", this pin outputs #CE11+#CE12 signal.

20 O – #WRL: Write (low byte) signal when SBUSST(D3/0x4812E) = "0" (default)

#WR: Write signal when SBUSST(D3/0x4812E) = "1"

#WE: DRAM write signal

21 O – #WRH: Write (high byte) signal when SBUSST(D3/0x4812E) = "0"

(default)

#BSH: Bus strobe (high byte) signal when SBUSST(D3/0x4812E) = "1"

62 I/O – P34: I/O port when CFP34(D4/0x402DC) = "0" (default)

#BUSREQ: Bus release request input when CFP34(D4/0x402DC) = "1"

#CE6: Area 6 chip enable when CFP34(D4/0x402DC) = "1" and

IOC34(D4/0x402DE) = "1"

59 I/O – P35: I/O port when CFP35(D5/0x402DC) = "0" (default)

#BUSACK: Bus acknowledge output when CFP35(D5/0x402DC) = "1"

68 I/O – P30: I/O port when CFP30(D0/0x402DC) = "0" (default)

#WAIT: Wait cycle request input when CFP30(D0/0x402DC) = "1"

#CE4&5: Areas 4&5 chip enable when CFP30(D0/0x402DC) = "1" and

IOC30(D0/0x402DE) = "1"

92 I/O – P20: I/O port when CFP20(D0/0x402D8) = "0" (default)

#DRD: DRAM read signal output for successive RAS mode when

CFP20(D0/0x402D8) = "1"

117 I/O – P21: I/O port when CFP21(D1/0x402D8) = "0" and

CFEX2(D2/0x402DF) = "0" (default)

#DWE: DRAM read signal output for successive RAS mode when

CFP21(D1/0x402D8) = "1" and CFEX2(D2/0x402DF) = "0"

#GAAS: Area address strobe for GA when CFEX2(D2/0x402DF) = "1"

11 I/O – P31: I/O port when CFP31(D1/0x402DC) = "0" and

CFEX3(D3/0x402DF) = "0" (default)

#BUSGET: Bus status monitor signal output when CFP31(D1/0x402DC) = "1"

and CFEX3(D3/0x402DF) = "0"

#GARD: Area read signal output for GA when CFEX3(D3/0x402DF) = "1"

EA10MD1 EA10MD0 Mode

1 1 External ROM mode

01–

00–

A-6 EPSON S1C33210 PRODUCT PART

Page 21

Table 1.3.3 List of Pins for HSDMA Control Signals

Pin name Pin No. I/O Pull-up Function

QFP15-128

K50

#DMAREQ0

K51

#DMAREQ1

P32

#DMAACK0

P33

#DMAACK1

P04

SIN1

P15

EXCL4

#DMAEND0

P16

EXCL5

#DMAEND1

P05

SOUT1

19 I Pull-up K50: Input port when CFK50(D0/0x402C0) = "0" (default)

#DMAREQ0: HSDMA Ch. 0 request input when CFK50(D0/0x402C0) = "1"

23 I Pull-up K51: Input port when CFK51(D1/0x402C0) = "0" (default)

#DMAREQ1: HSDMA Ch. 1 request input when CFK51(D1/0x402C0) = "1"

13 I/O – P32: I/O port when CFP32(D2/0x402DC) = "0" (default)

#DMAACK0: HSDMA Ch. 0 acknowledge output when CFP32(D2/0x402DC)

= "1"

15 I/O – P33: I/O port when CFP33(D3/0x402DC) = "0" (default)

#DMAACK1: HSDMA Ch. 1 acknowledge output when CFP33(D3/0x402DC)

= "1"

83 I/O – P04: I/O port when CFP04(D4/0x402D0) = "0" and

CFEX4(D4/0x402DF) = "0" (default)

SIN1: S erial I/F Ch. 1 data input when CFP04(D4/0x402D0) = "1" and

CFEX4(D4/0x402DF) = "0"

128 I/O – P15: I/O port when CFP15(D5/0x402D4) = "0" (default)

EXCL4: 16-bit timer 4 event counter input when CFP15(D5/0x402D4) =

"1" and IOC15(D5/0x402D6) = "0"

#DMAEND0: HSDMA Ch. 0 end-of-transfer signal output when

CFP15(D5/0x402D4) = "1" and IOC15(D5/0x402D6) = "1"

77 I/O – P16: I/O port when CFP16(D6/0x402D4) = "0" (default)

EXCL5: 16-bit timer 5 event counter input when CFP16(D6/0x402D4) =

"1" and IOC16(D6/0x402D6) = "0"

#DMAEND1: HSDMA Ch. 1 end-of-transfer signal output when

CFP16(D6/0x402D4) = "1" and IOC16(D6/0x402D6) = "1"

86 I/O – P05: I/O port when CFP05(D5/0x402D0) = "0" and

CFEX5(D5/0x402DF) = "0" (default)

SOUT1: Serial I/F Ch. 1 data output when CFP05(D5/0x402D0) = "1" and

CFEX5(D5/0x402DF) = "0"

1 OUTLINE

S1C33210 PRODUCT PART EPSON A-7

Page 22

1 OUTLINE

Table 1.3.4 List of Pins for Internal Peripheral Circuits

Pin name Pin No. I/O Pull-up Function

QFP15-128

K52

#ADTRG

K60

AD0

K61

AD1

K62

AD2

K63

AD3

P00

SIN0

P01

SOUT0

P02

#SCLK0

P03

#SRDY0

P04

SIN1

P05

SOUT1

P10

EXCL0

T8UF0

DST0

P11

EXCL1

T8UF1

DST1

P12

EXCL2

T8UF2

DST2

33 I Pull-up K52: Input port when CFK52(D2/0x402C0) = "0" (default)

#ADTRG: A/D converter trigger input when CFK52(D2/0x402C0) = "1"

32 I – K60: Input port when CFK60(D0/0x402C3) = "0" (default)

AD0: A/D converter Ch. 0 input when CFK60(D0/0x402C3) = "1"

31 I – K61: Input port when CFK61(D1/0x402C3) = "0" (default)

AD1: A/D converter Ch. 1 input when CFK61(D1/0x402C3) = "1"

29 I – K62: Input port when CFK62(D2/0x402C3) = "0" (default)

AD2: A/D converter Ch. 2 input when CFK62(D2/0x402C3) = "1"

28 I – K63: Input port when CFK63(D3/0x402C3) = "0" (default)

AD3: A/D converter Ch. 3 input when CFK63(D3/0x402C3) = "1"

5 I/O – P00: I/O port when CFP00(D0/0x402D0) = "0" (default)

SIN0: Serial I/F Ch. 0 data input when CFP00(D0/0x402D0) = "1"

6 I/O – P01: I/O port when CFP01(D1/0x402D0) = "0" (default)

SOUT0: Serial I/F Ch. 0 data output when CFP01(D1/0x402D0) = "1"

17 I/O – P02: I/O port when CFP02(D2/0x402D0) = "0" (default)

#SCLK0: Serial I/F Ch. 0 clock input/output when CFP02(D2/0x402D0) =

"1"

9 I/O – P03: I/O port when CFP03(D3/0x402D0) = "0" (default)

#SRDY0: Serial I/F Ch. 0 ready signal input/output when

CFP03(D3/0x402D0) = "1"

83 I/O – P04: I/O port when CFP04(D4/0x402D0) = "0" and

CFEX4(D4/0x402DF) = "0" (default)

SIN1: S erial I/F Ch. 1 data input when CFP04(D4/0x402D0) = "1" and

CFEX4(D4/0x402DF) = "0"

86 I/O – P05: I/O port when CFP05(D5/0x402D0) = "0" and

CFEX5(D5/0x402DF) = "0"(default)

SOUT1: Serial I/F Ch. 1 data output when CFP05(D5/0x402D0) = "1" and

CFEX5(D5/0x402DF) = "0"

121 I/O – P10: I/O port when CFP10(D0/0x402D4) = "0" and

CFEX1(D1/0x402DF) = "0"

EXCL0: 16-bit timer 0 event counter input when CFP10(D0/0x402D4) =

"1", IOC10(D0/0x402D6) = "0" and CFEX1(D1/0x402DF) = "0"

T8UF0: 8-bit timer 0 output when CFP10(D0/0x402D4) = "1",

IOC10(D0/0x402D6) = "1" and CFEX1(D1/0x402DF) = "0"

DST0: DST0 signal output when CFEX1(D1/0x402DF) = "1" (default)

122 I/O – P11: I/O port when CFP11(D1/0x402D4) = "0" and

CFEX1(D1/0x402DF) = "0"

EXCL1: 16-bit timer 1 event counter input when CFP11(D1/0x402D4) =

"1", IOC11(D1/0x402D6) = "0" and CFEX1(D1/0x402DF) = "0"

T8UF1: 8-bit timer 1 output when CFP11(D1/0x402D4) = "1",

IOC11(D1/0x402D6) = "1" and CFEX1(D1/0x402DF) = "0"

DST1: DST1 signal output when CFEX1(D1/0x402DF) = "1" (default)

123 I/O – P12: I/O port when CFP12(D2/0x402D4) = "0" and

CFEX0(D0/0x402DF) = "0"

EXCL2: 16-bit timer 2 event counter input when CFP12(D2/0x402D4) =

"1", IOC12(D2/0x402D6) = "0" and CFEX0(D0/0x402DF) = "0"

T8UF2: 8-bit timer 2 output when CFP12(D2/0x402D4) = "1",

IOC12(D2/0x402D6) = "1" and CFEX0(D0/0x402DF) = "0"

DST2: DST2 signal output when CFEX0(D0/0x402DF) = "1" (default)

A-8 EPSON S1C33210 PRODUCT PART

Page 23

Pin name Pin No. I/O Pull-up Function

QFP15-128

P13

EXCL3

T8UF3

DPCO

P14

FOSC1

DCLK

P15

EXCL4

#DMAEND0

P16

EXCL5

#DMAEND1

P20

#DRD

P21

#DWE

#GAAS

P22

TM0

P23

TM1

P24

TM2

#SRDY2

P25

TM3

#SCLK2

P26

TM4

SOUT2

P27

TM5

SIN2

124 I/O – P13: I/O port when CFP13(D3/0x402D4) = "0" and

CFEX1(D1/0x402DF) = "0"

EXCL3: 16-bit timer 3 event counter input when CFP13(D3/0x402D4) =

"1", IOC13(D3/0x402D6) = "0" and CFEX1(D1/0x402DF) = "0"

T8UF3: 8-bit timer 3 output when CFP13(D3/0x402D4) = "1",

IOC13(D3/0x402D6) = "1" and CFEX1(D1/0x402DF) = "0"

DPCO: DPCO signal output when CFEX1(D1/0x402DF) = "1" (default)

125 I/O – P14: I/O port when CFP14(D4/0x402D4) = "0" and

CFEX0(D0/0x402DF) = "0"

FOSC1: OSC1 clock output when CFP14(D4/0x402D4) = "1" and

CFEX0(D0/0x402DF) = "0"

DCLK: DCLK signal output when CFEX0(D0/0x402DF) = "1" (default)

128 I/O – P15: I/O port when CFP15(D5/0x402D4) = "0" (default)

EXCL4: 16-bit timer 4 event counter input when CFP15(D5/0x402D4) =

"1" and IOC15(D5/0x402D6) = "0"

#DMAEND0: HSDMA Ch. 0 end-of-transfer signal output when

CFP15(D5/0x402D4) = "1" and IOC15(D5/0x402D6) = "1"

77 I/O – P16: I/O port when CFP16(D6/0x402D4) = "0" (default)

EXCL5: 16-bit timer 5 event counter input when CFP16(D6/0x402D4) =

"1" and IOC16(D6/0x402D6) = "0"

#DMAEND1: HSDMA Ch. 1 end-of-transfer signal output when

CFP16(D6/0x402D4) = "1" and IOC16(D6/0x402D6) = "1"

92 I/O – P20: I/O port when CFP20(D0/0x402D8) = "0" (default)

#DRD: DRAM read signal output for successive RAS mode when

CFP20(D0/0x402D8) = "1"

117 I/O – P21: I/O port when CFP21(D1/0x402D8) = "0" and

CFEX2(D2/0x402DF) = "0" (default)

#DWE: DRAM read signal output for successive RAS mode when

CFP21(D1/0x402D8) = "1" and CFEX2(D2/0x402DF) = "0"

#GAAS: Area address strobe for GA when CFEX2(D2/0x402DF) = "1"

118 I/O – P22: I/O port when CFP22(D2/0x402D8) = "0" (default)

TM0: 16-bit timer 0 output when CFP22(D2/0x402D8) = "1"

119 I/O – P23: I/O port when CFP23(D3/0x402D8) = "0" (default)

TM1: 16-bit timer 1 output when CFP23(D3/0x402D8) = "1"

126 I/O – P24: I/O port when CFP24(D4/0x402D8) = "0" (default)

TM2: 16-bit timer 2 output when CFP24(D4/0x402D8) = "1"

#SRDY2: Serial I/F Ch.2 ready signal input/output when

SSRDY2(D3/0x402DB) = "1" and CFP24 (D4/0x402D8) = "0"

127 I/O – P25: I/O port when CFP25(D5/0x402D8) = "0" (default)

TM3: 16-bit timer 3 output when CFP25(D5/0x402D8) = "1"

#SCLK2: Serial I/F Ch.2 clock input/output when SSCLK2(D2/0x402DB) =

"1" and CFP25(D5/0x402D8) = "0"

1I/O– P26: I/O port when CFP26(D6/0x402D8) = "0" (default)

TM4: 16-bit timer 4 output when CFP26(D6/0x402D8) = "1"

SOUT2: Serial I/F Ch.2 data output when SSOUT2(D1/0x402DB) = "1"

and CFP26(D6/0x402D8) = "0"

2I/O– P27: I/O port when CFP27(D7/0x402D8) = "0" (default)

TM5: 16-bit timer 5 output when CFP27(D7/0x402D8) = "1"

SIN2: S erial I/F Ch.2 data input when SSIN2(D0/0x402DB) = "1" and

CFP27(D7/0x402D8) = "0"

1 OUTLINE

S1C33210 PRODUCT PART EPSON A-9

Page 24

1 OUTLINE

Pin name Pin No. I/O Pull-up Function

QFP15-128

DTR 95 O – DTR output *1

RTS 94 O – RTS output*1

TXD

SOUT3

RI 97 I – RI input *1

CTS 101 I – CTS input *1

DCD 108 I – DCD input *1

DSR 96 I – DSR input *1

RXD

SIN3

CNT1 99 O – Mobile access control output #1

CNT2 98 O – Mobile access control output #2

MSEL 109 I Pull-up Serial I/O interface Ch. 3 configuration input. Normally drive this at High level.

GOUT 110 O – NMI interrupt request output

100 O – TXD: TXD output*1 when MSEL pin input is at High level

SOUT3: SOUT3 output when MSEL pin input is at Low level

107 I – RXD: RXD input when MSEL pin input is at High level

SIN3: SIN3 input when MSEL pin input is at Low level

Note: *1 The communications macro select (MCRS) register (D[1:0]/0x200000) configures the I/O

signals to match the target mobile device.

Table 1.3.5 List of Pins for Clock Generator

Pin name Pin No. I/O Pull-up Function

QFP15-128

OSC1 51 I – Low-speed (OSC1) oscillation input (32 kHz crystal oscillator or external clock

input)

OSC2 50 O – Low-speed (OSC1) oscillation output

OSC3 112 I – High-speed (OSC3) oscillation input (crystal/ceramic oscillator or external clock

input)

OSC4 113 O – High-speed (OSC3) oscillation output

PLLS[1:0] 105,106 I – PLL set-up pins

PLLS1 PLLS0 fin (f OSC3) fout (fPSCIN)

1110–25MHz 20–50MHz

0110–12.5MHz 40–50MHz

0 0 PLL is not

used

L

PLLC 103 ––Capasitor connecting pin for PLL

Table 1.3.6 List of Other Pins

Pin name Pin No. I/O Pull-up Function

QFP15-128 /down

TST 80 I Pull-

DSIO 120 I/O Pull-up Serial I/O pin for debugging

#X2SPD 116 I – Clock doubling mode set-up pin1: CPU clock = bus clock × 1, 0: CPU clock = bus

#NMI 44 I Pull-up NMI request input pin

#RESET 43 I Pull-up Initial reset input pin

Test mode input. This pin is used for testing this chip. For further details, refer

down

to the S1C33 ASIC Design Guide.

This pin is used to communicate with the debugging tool S5U1C33000H.

clock × 2

Note:"#" in the pin names indicates that the signal is low active.

A-10 EPSON S1C33210 PRODUCT PART

Page 25

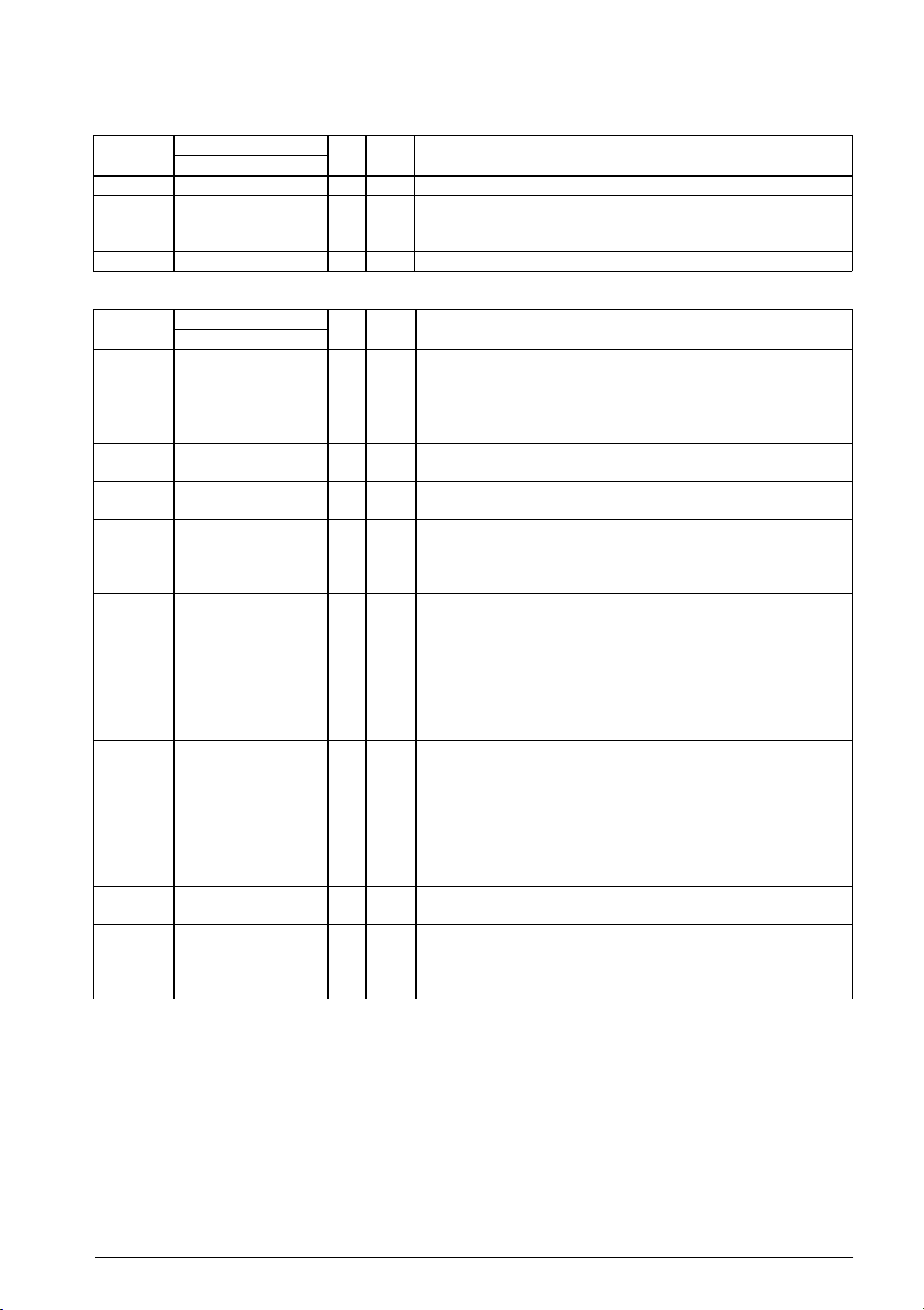

2 Power Supply

This chapter explains the operating voltage of the S1C33210.

2.1 Power Supply Pins

The S1C33210 has the power supply pins shown in Table 2.1.1.

Table 2.1.1 Power Supply Pins

Pin name Pin No. Function

QFP15-128

VDD 8, 27, 47, 74, 93, 111 Power supply (+)

VSS 3, 22, 39, 54, 67, 90,

102, 104

AVDD 30 Analog system power supply (+); AVDD = VDD

Power supply (-); GND

2 POWER SUPPLY

2.7 to 3.6 V

2.7 to 3.6 V

GND

VDD

CPU core

I/O

interface circuit

AVDD

Analog circuits

(A/D converter)

VSS

Figure 2.1.1 Power Supply System

Internal

peripheral

circuit

I/O pins

2.2 Operating Voltage (VDD, VSS)

The core CPU, internal peripheral circuits, and external signal interfaces operate on the voltage difference between

the V

DD and VSS pins. The following operating voltage can be used:

DD = 2.7 V to 3.6 V (VSS = GND)

V

Note: The S1C33210 has 6 V

pins. Do not open any of them.

The operating clock frequency range (OSC3) is 5 MHz to 50 MHz with this voltage.

DD pins and 8 VSS pins. Be sure to supply the operating voltage to all the

S1C33210 PRODUCT PART EPSON A-11

Page 26

2 POWER SUPPLY

2.3 Power Supply for Analog Circuits (AVDD)

The analog power supply pin (AVDD) is provided separately from the V DD and VDD pins in order that the digital

circuits do not affect the analog circuit (A/D converter). The AV

the V

SS pin is used as the analog ground.

Supply the same voltage level as the V

DD = V DD, V SS = GND

AV

Note: Be sure to supply V

DD to the AVDD pin even if the analog circuit is not used.

DD to the AVDD pin.

Noise on the analog power lines decrease the A/D converting precision, so use a stabilized power supply and make

the board pattern with consideration given to that.

DD pin is used to supply an analog power voltage and

A-12 EPSON S1C33210 PRODUCT PART

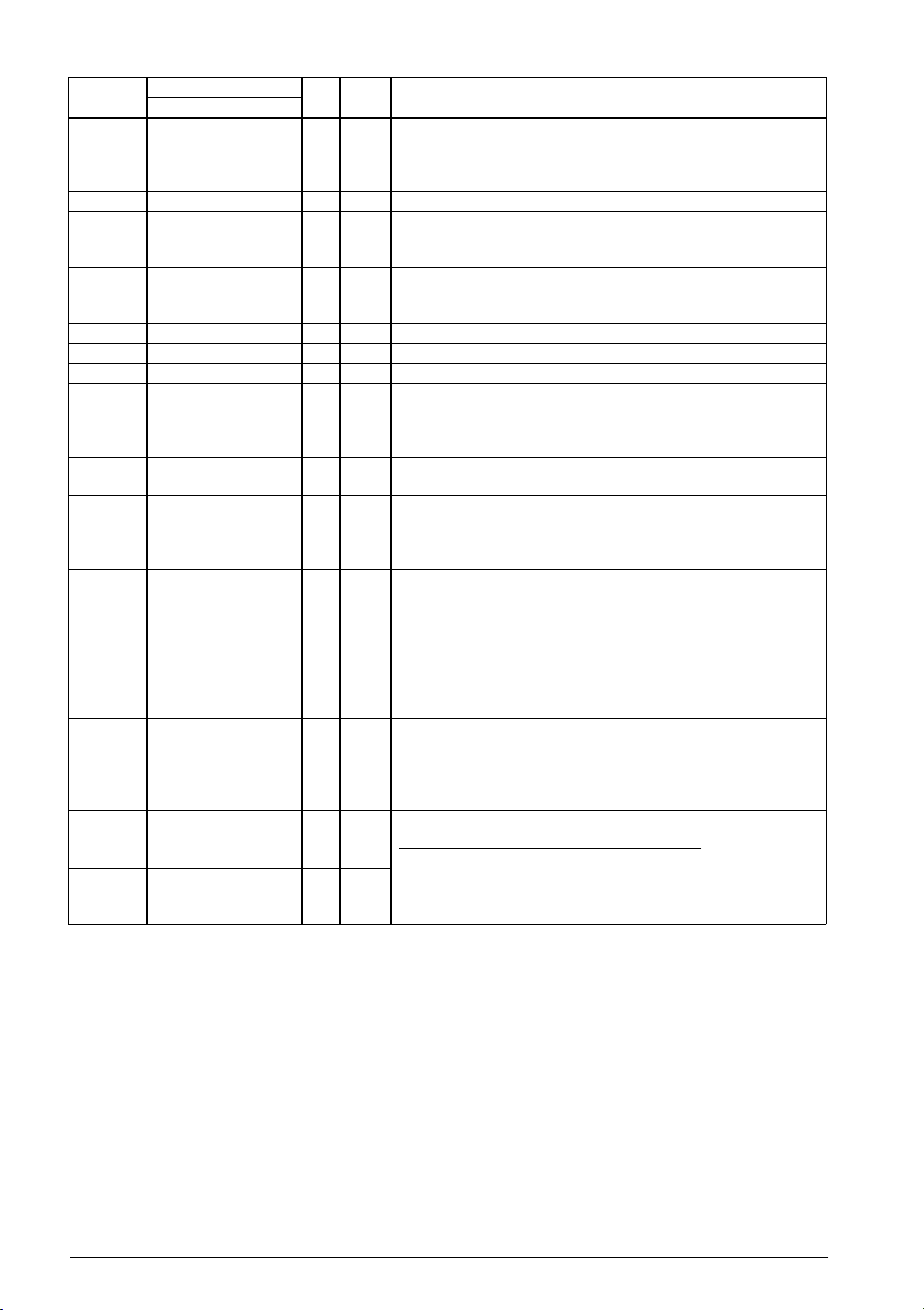

Page 27

3 INTERNAL MEMORY

3 Internal Memory

This chapter explains the internal memory configuration.

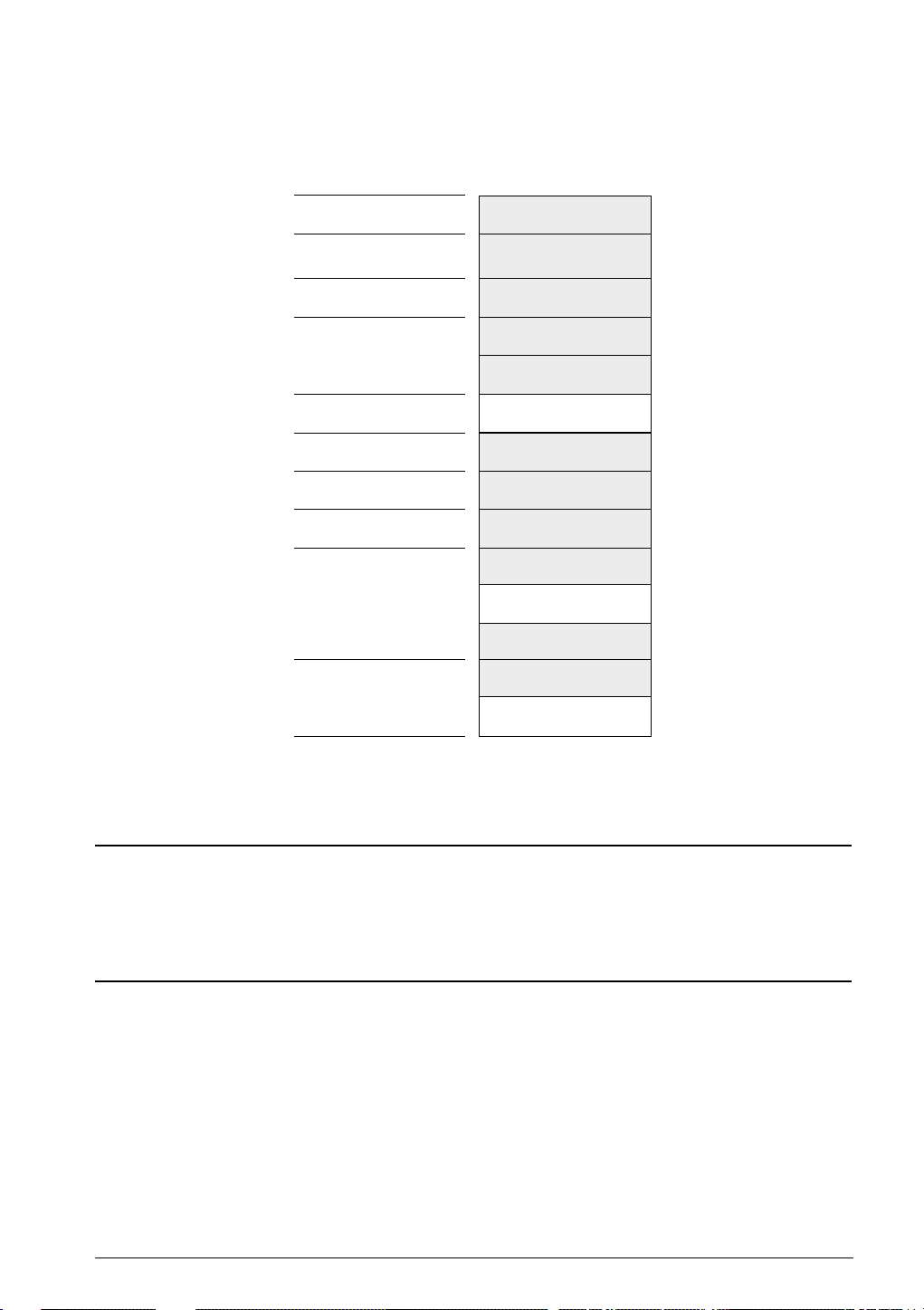

Figure 3.1 shows the S1C33210 memory map.

Area Address

Areas 18–11

Area 10

Areas 9

Area 6

Area 5

Area 4 0x01FFFFF

Area 3

Area 2

Area 1

Area 0

–7

0xFFFFFFF

0x1000000

0x0FFFFFF

0x0C00000

0x0BFFFFF

0x0400000

0x03FFFFF

0x0380000

0x037FFFF

0x0300000

0x02FFFFF

0x0200000

0x0100000

0x00FFFFF

0x0080000

0x007FFFF

0x0060000

0x005FFFF

0x0050000

0x004FFFF

0x0040000

0x003FFFF

0x0030000

0x002FFFF

0x0002000

0x0001FFF

0x0000000

Figure 3.1 Memory Map

Area 2 is used in debug mode only and it cannot be accessed in user mode (normal program execution status).

S1C33210

External Memory

External Memory

External Memory

External I/O (16-bit device)

External I/O (8-bit device)

Internal peripheral circuits

External Memory

(Reserved)

For middleware use

(Reserved)

For CPU, debug mode

(Mirror of internal

peripheral circuits)

Internal peripheral circuits

(Mirror of internal

peripheral circuits)

(Mirror of internal RAM)

Internal RAM (8KB)

3.1 ROM and Boot Address

The S1C33210 does not have a built-in ROM. The boot address is fixed at 0x0C00000, and so external ROM/Flash

should be used in Area 10.

For setting up Area 10, refer to the "BCU (Bus Controller Unit)" in "S1C33210 FUNCTION PART" in this manual.

3.2 RAM

The S1C33210 has a built-in 8KB RAM. The RAM is allocated to Area 0, address 0x0000000 to address

0x0001FFF.

The internal RAM is a 32-bit sized device and data can be read/written in 1 cycle regardless of data size (byte, halfword or word).

S1C33210 PRODUCT PART EPSON A-13

Page 28

4 PERIPHERAL CIRCUITS

4 Peripheral Circuits

This chapter lists the built-in peripheral circuits and the I/O memory map. For details of the circuits, refer to the

"S1C33210 FUNCTION PART".

4.1 List of Peripheral Circuits

The S1C33210 consists of the C33 Core Block, C33 Peripheral Block, C33 DMA Block and C33 Analog Block.

C33 Core Block

CPU S1C33000 32-bit RISC type CPU

BCU (Bus Control Unit) 24-bit external address bus and 16-bit data bus

All the BCU functions can be used.

ITC (Interrupt Controller) 39 types of interrupts are available.

CLG (Clock Generator) OSC3 oscillation circuit (33 MHz Max.), PLL and OSC1 oscillation circuit

(32.768 kHz Typ.) built-in

DBG (Debug Unit) Functional block for debugging with the S5U1C33000H (In-Circuit Debugger

for S1C33 Family)

C33 Peripheral Block

Prescaler Programmable clock generator for peripheral circuits

8-bit programmable timer 6 channels with clock output function

16-bit programmable timer 6 channels with event counter, clock output and watchdog timer functions

Serial interface 4 channels (asynchronous mode, clock synchronous mode and IrDA are

selectable. Interfaces 1 and 3 support only asynchronous operation.)

Input and I/O ports 7 bits of input ports and 27 bits of I/O ports (used for peripheral I/O)

Clock timer 1 channel with alarm function

Mobile access interfaces One PHS, PDC, and HDLC interface each

C33 DMA Block

HSDMA (High-Speed DMA) 4 channels (Only two interfaces support external requests.)

IDMA (Intelligent DMA) 128 channels

C33 Analog Block

A/D converter 10-bit A/D converter with 4 input channels

A-14 EPSON S1C33210 PRODUCT PART

Page 29

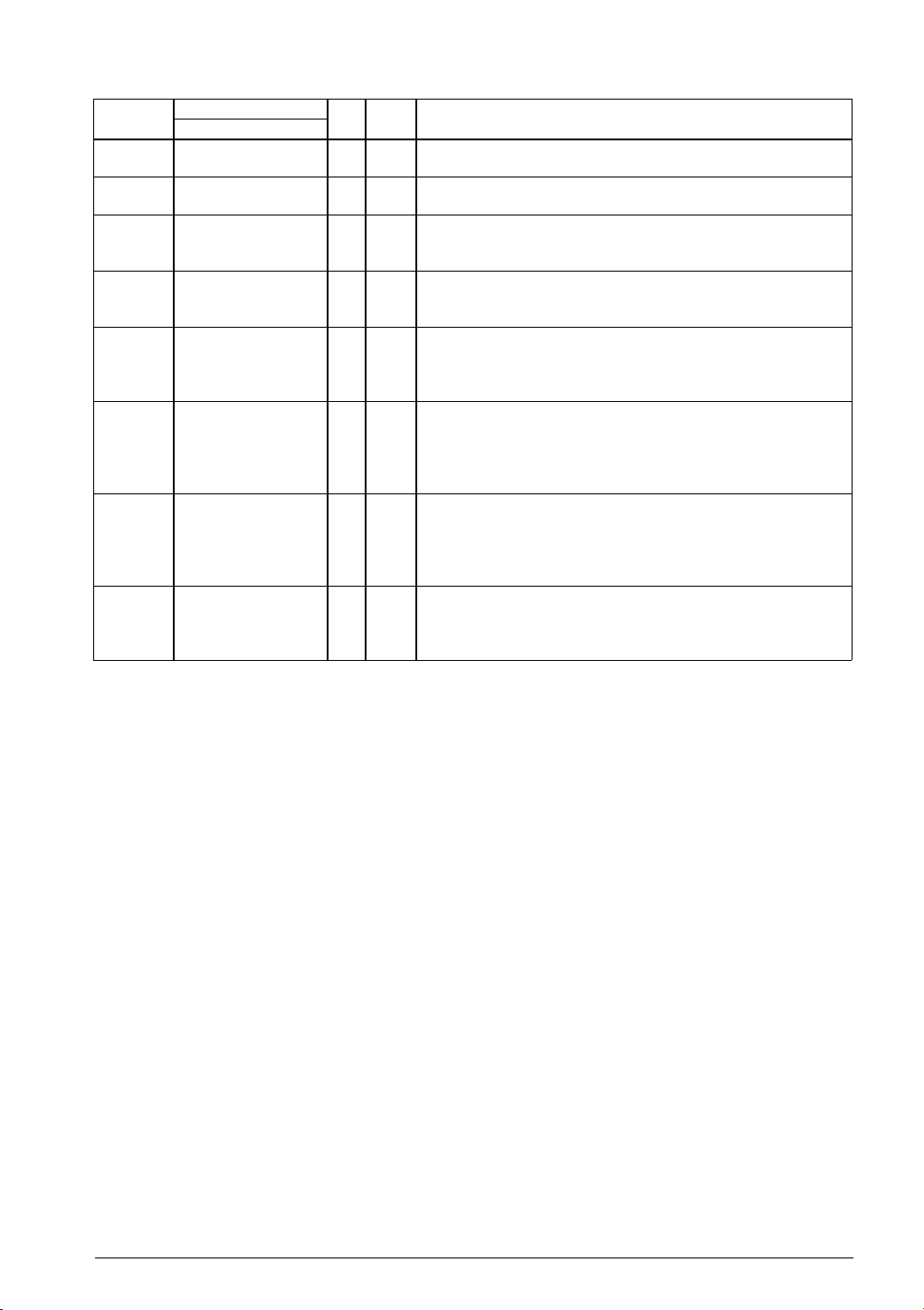

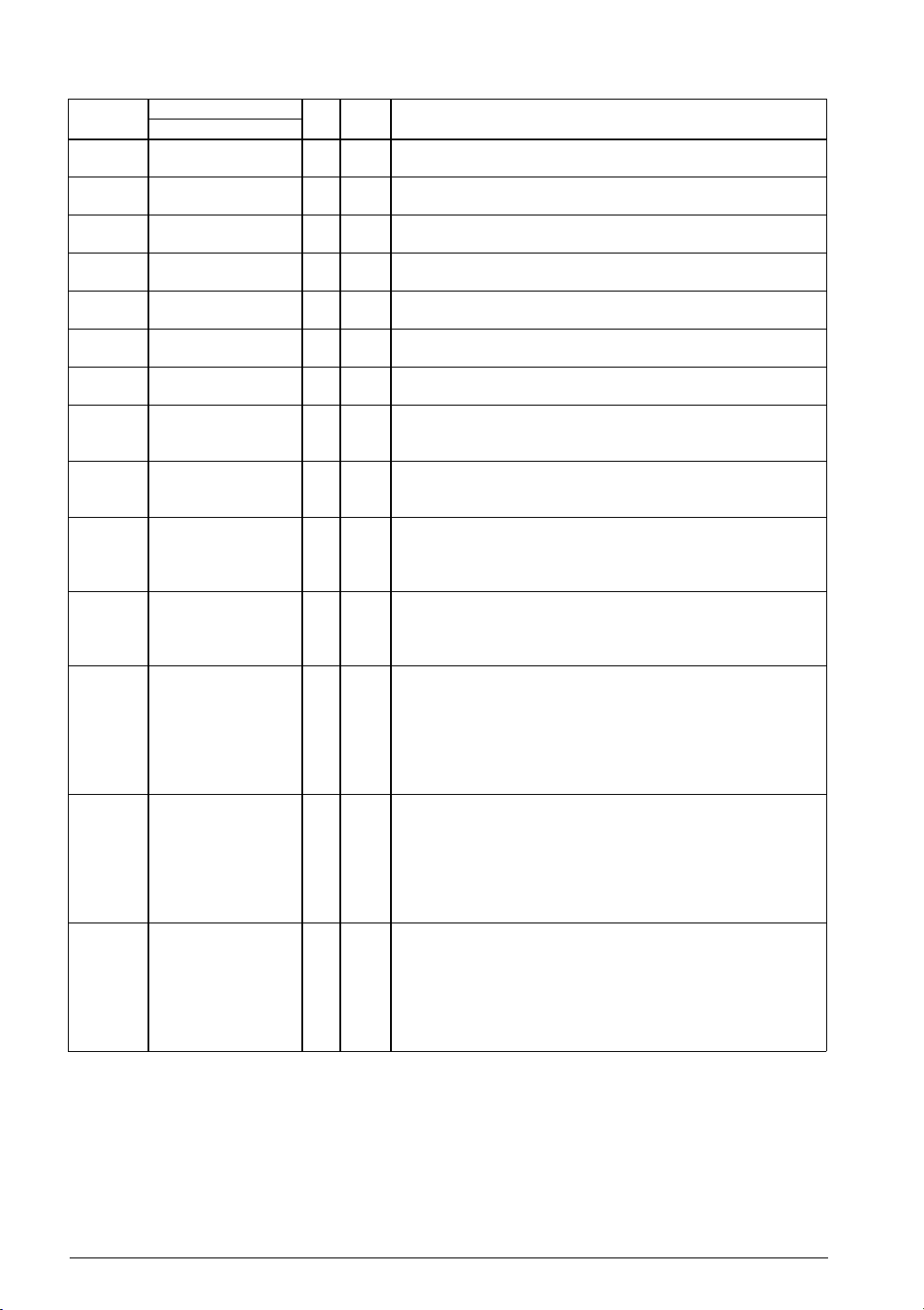

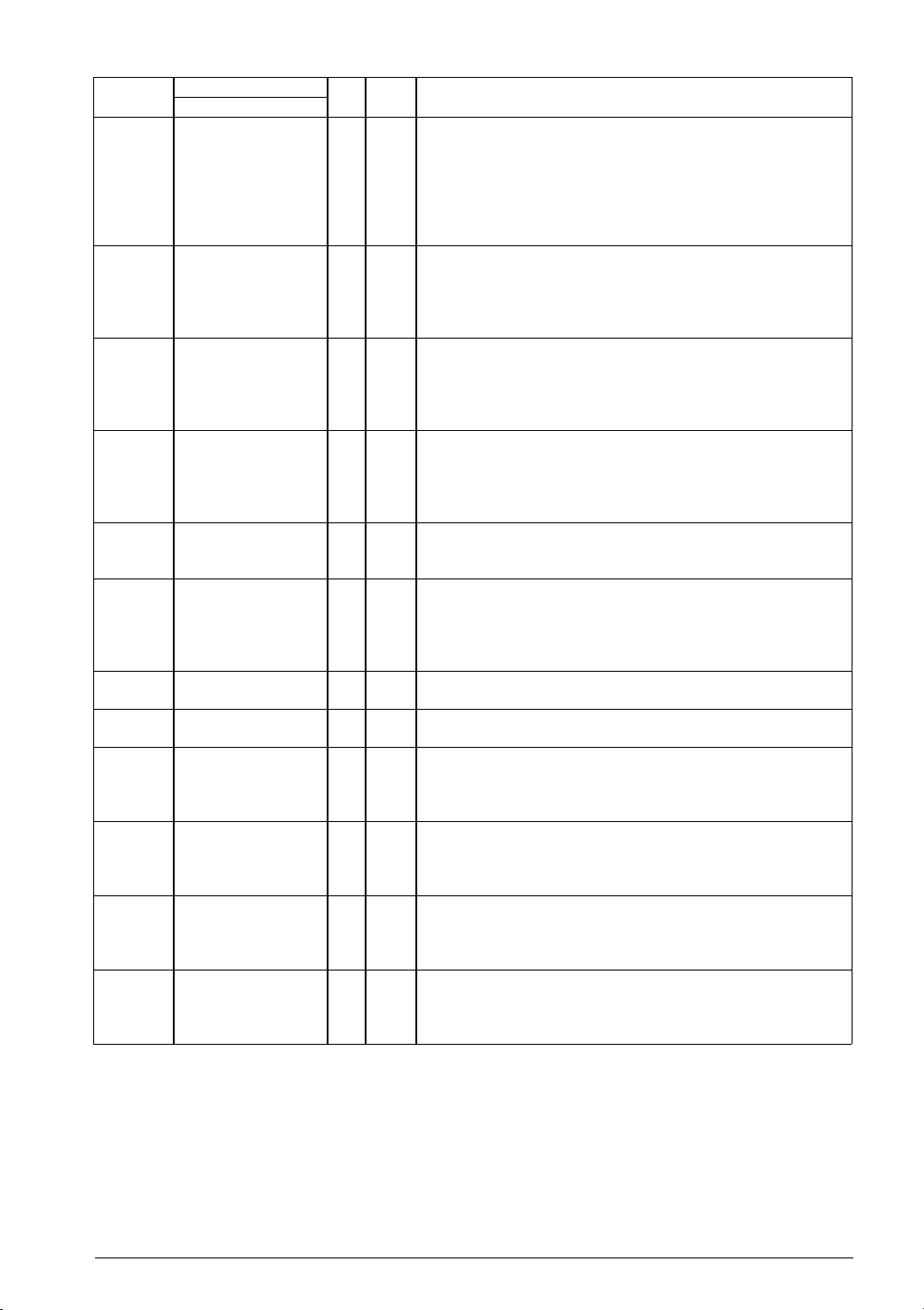

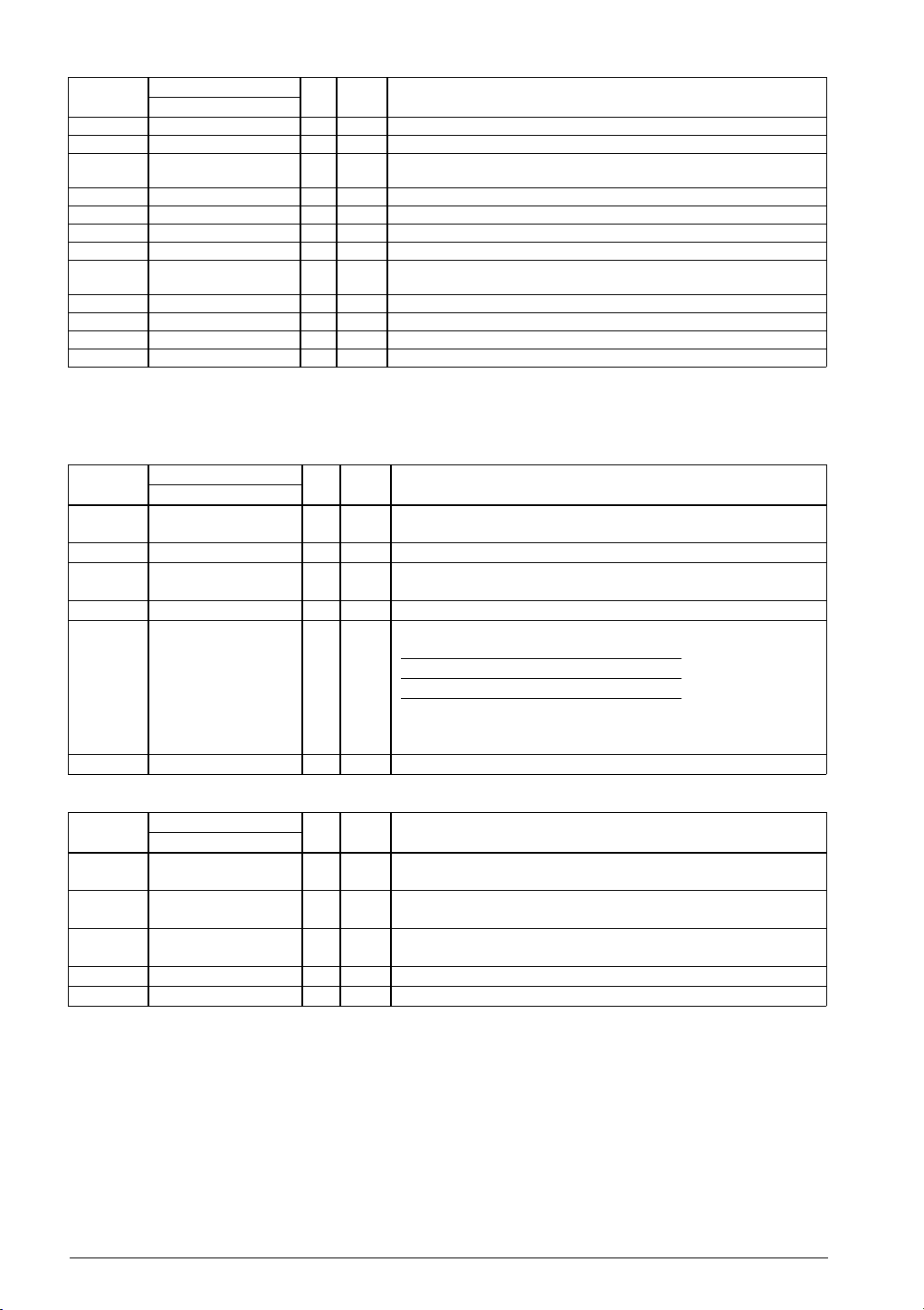

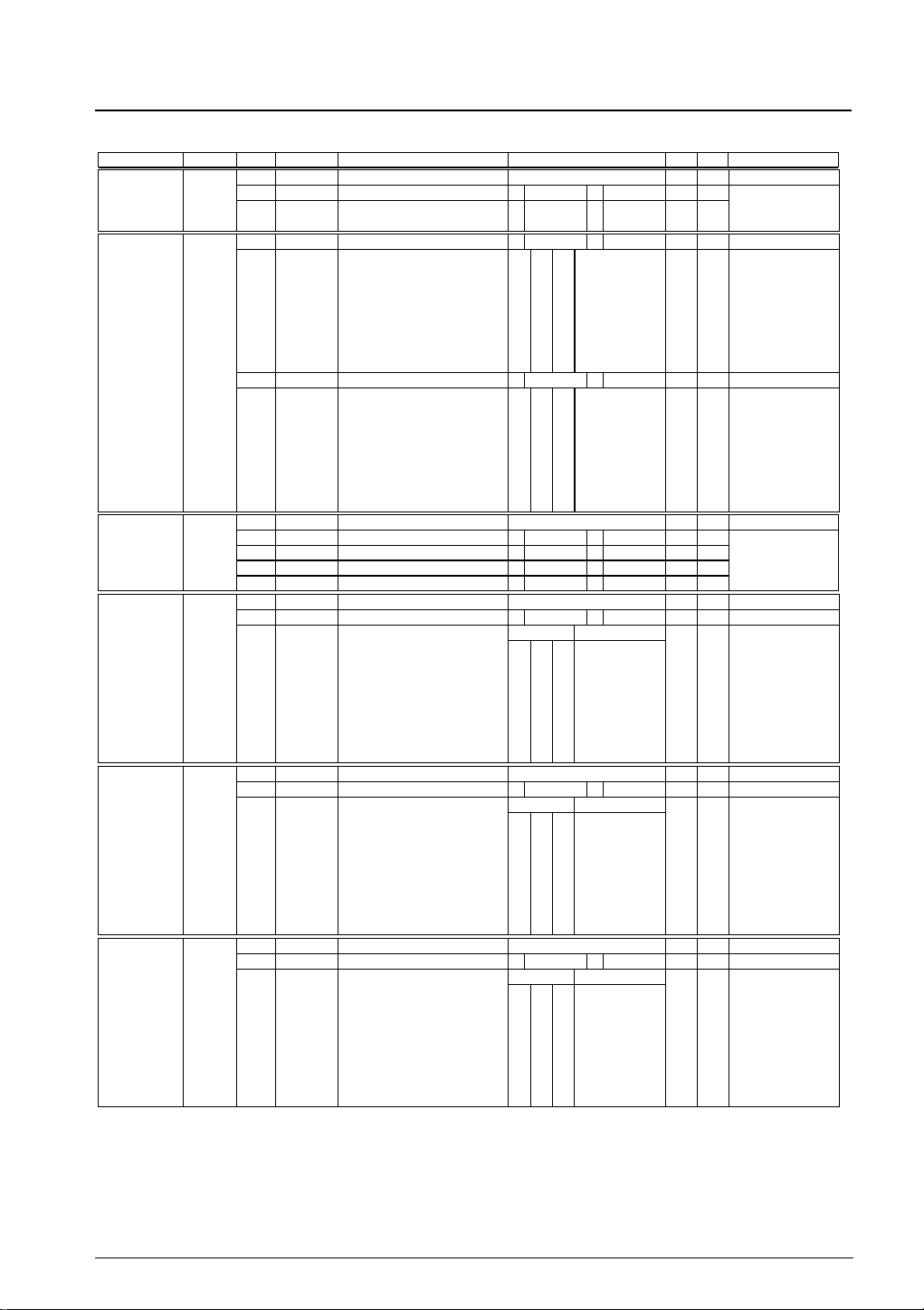

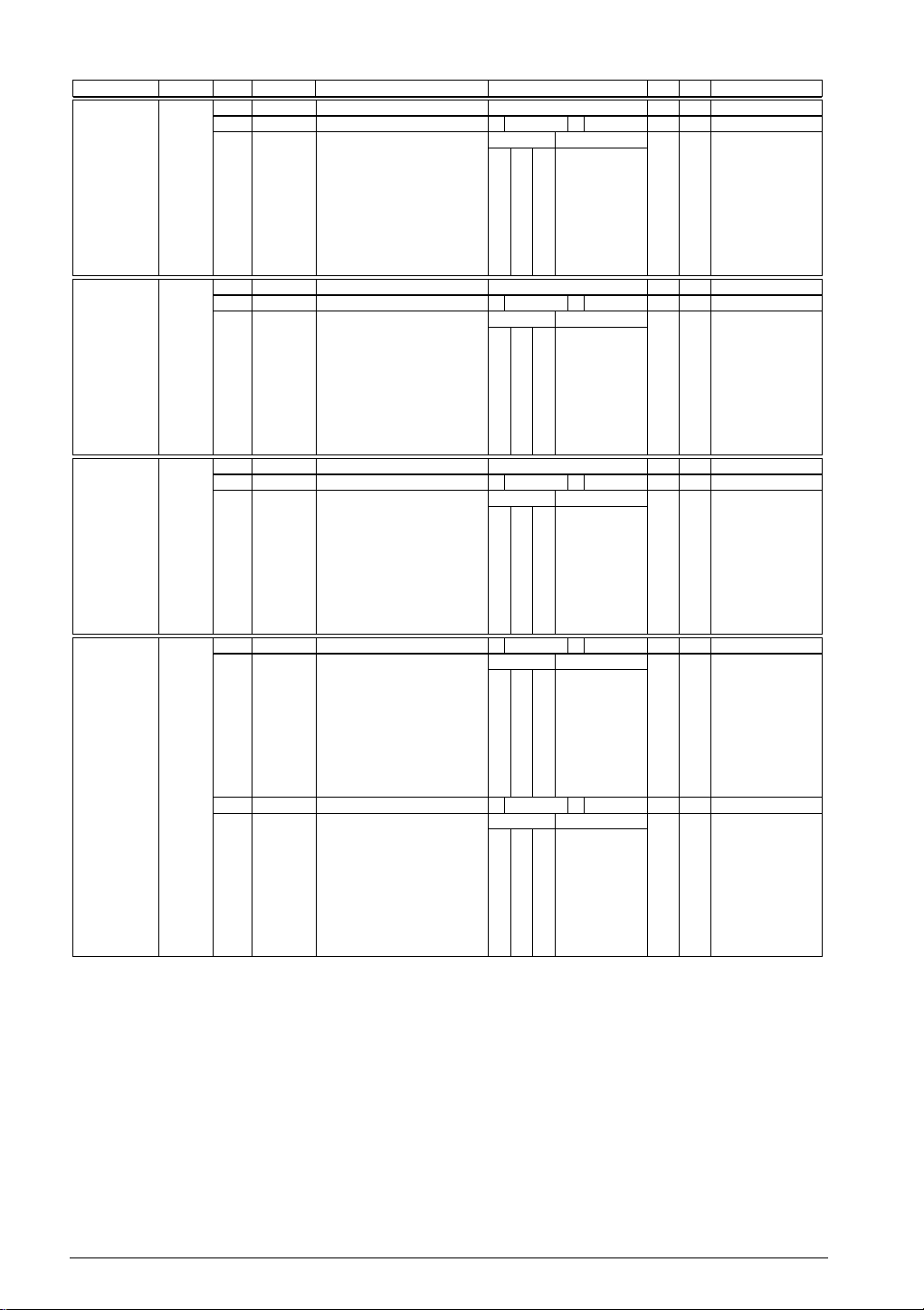

4.2 I/O Memory Map

NameAddressRegister name Bit Function Setting Init. R/W Remarks

–

8-bit timer 4/5

clock select

register

8-bit timer 4/5

clock control

register

8-bit timer

clock select

register

16-bit timer 0

clock control

register

16-bit timer 1

clock control

register

16-bit timer 2

clock control

register

0040140

0040145

0040146

0040147

0040148

0040149

(B)

(B)

(B)

(B)

(B)

(B)

D7–2

D1

D0

D7

D6

D5

D4

D3

D2

D1

D0

D7–4

D3

D2

D1

D0

D7–4

D3

D2

D1

D0

D7–4

D3

D2

D1

D0

D7–4

D3

D2

D1

D0

P8TPCK5

P8TPCK4

P8TS52

P8TS51

P8TS50

P8TON4

P8TS42

P8TS41

P8TS40

P8TPCK3

P8TPCK2

P8TPCK1

P8TPCK0

P16TON0

P16TS02

P16TS01

P16TS00

P16TON1

P16TS12

P16TS11

P16TS10

P16TON2

P16TS22

P16TS21

P16TS20

Table 4.2.1 I/O Memory Map

reserved

8-bit timer 5 clock selection

8-bit timer 4 clock selection

8-bit timer 5 clock control

8-bit timer 5

clock division ratio selection

8-bit timer 4 clock control

8-bit timer 4

clock division ratio selection

reserved