DYNEX NMAQ31750FS, NMAR31750AE, NMAR31750FB, NMAR31750FE, NMAR31750FD Datasheet

...

MA31750

1/42

The Dynex Semiconductor MA31750 is a single-chip

microprocessor that implements the full MIL-STD-1750A

instruction set architecture, or Option 2 of Draft MIL-STD1750B. The processor executes all mandatory instructions and

many optional features are also included. Interrupts, fault

handling, memory expansion, Console, timers A and B, and

their related optional instructions are also supported in full

accordance with MIL-STD-1750.

The MA31750 offers a considerable performance increase

over the existing MAS281. This is achieved by using a 32-bit

internal bus structure with a 24 x 24 bit multiplier and 32-bit

ALU. Other performance-enhancing features include a 32-bit

shift network, a multi-port register file and a dedicated address

calculation unit.

The MA31750 has on-chip parity generation and checking

to enhance system integrity. A comprehensive built-in self-test

has also been incorporated, allowing processor functionality to

be verified at any time.

Console operation is supported through a parallel interface

using command/data registers in l/O space. Several discrete

output signals are produced to minimise external logic.

Control signals are also provided to allow inclusion of the

MA31750 into a multiprocessor or DMA system.

The processor can directly access 64KWords of memory in

full accordance with MIL-STD-1750A. This increases to

1MWord when used with the optional MA31751 memory

management unit (MMU). 1750B mode allows the system to

be expanded to 8MWord with the MMU.

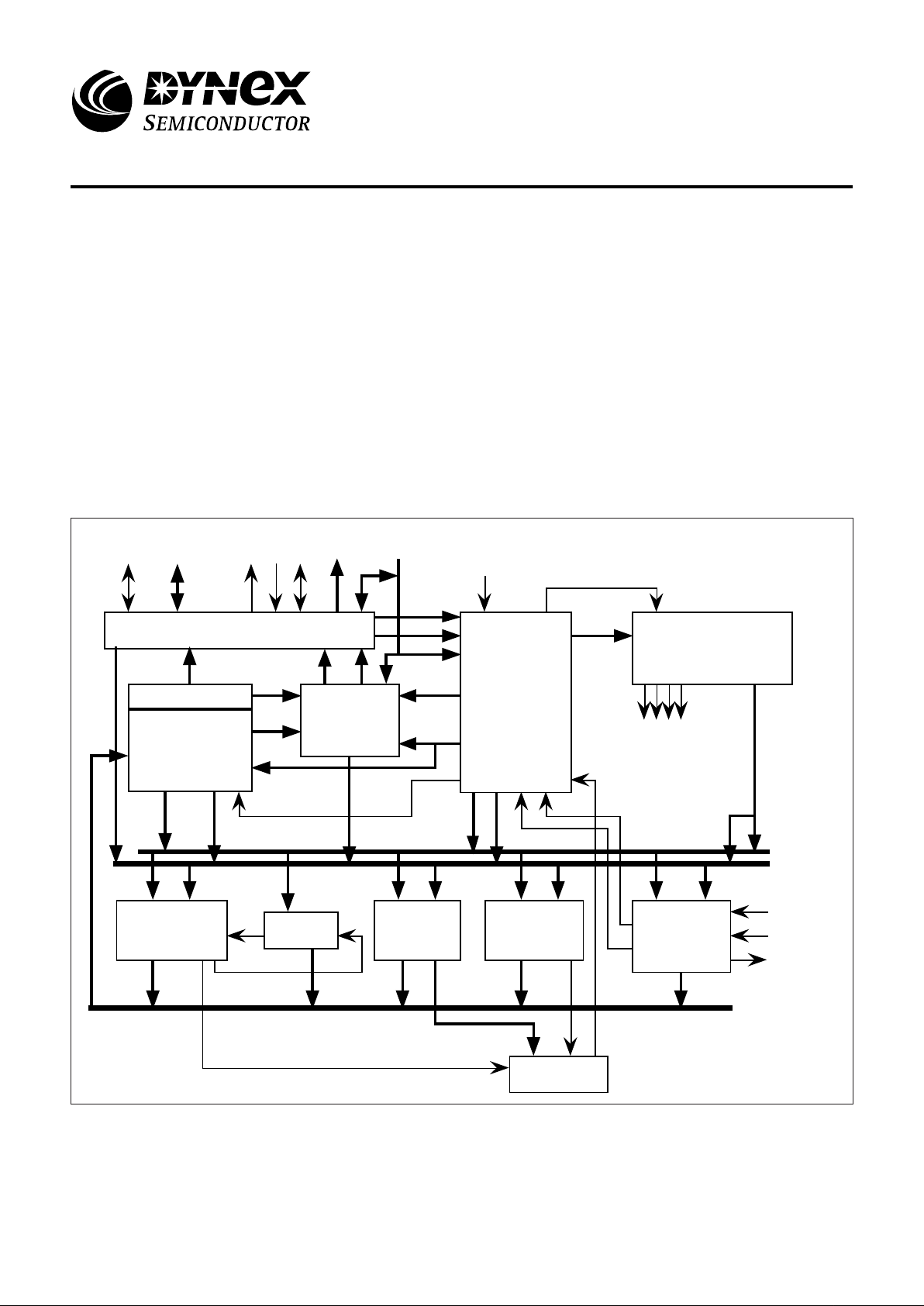

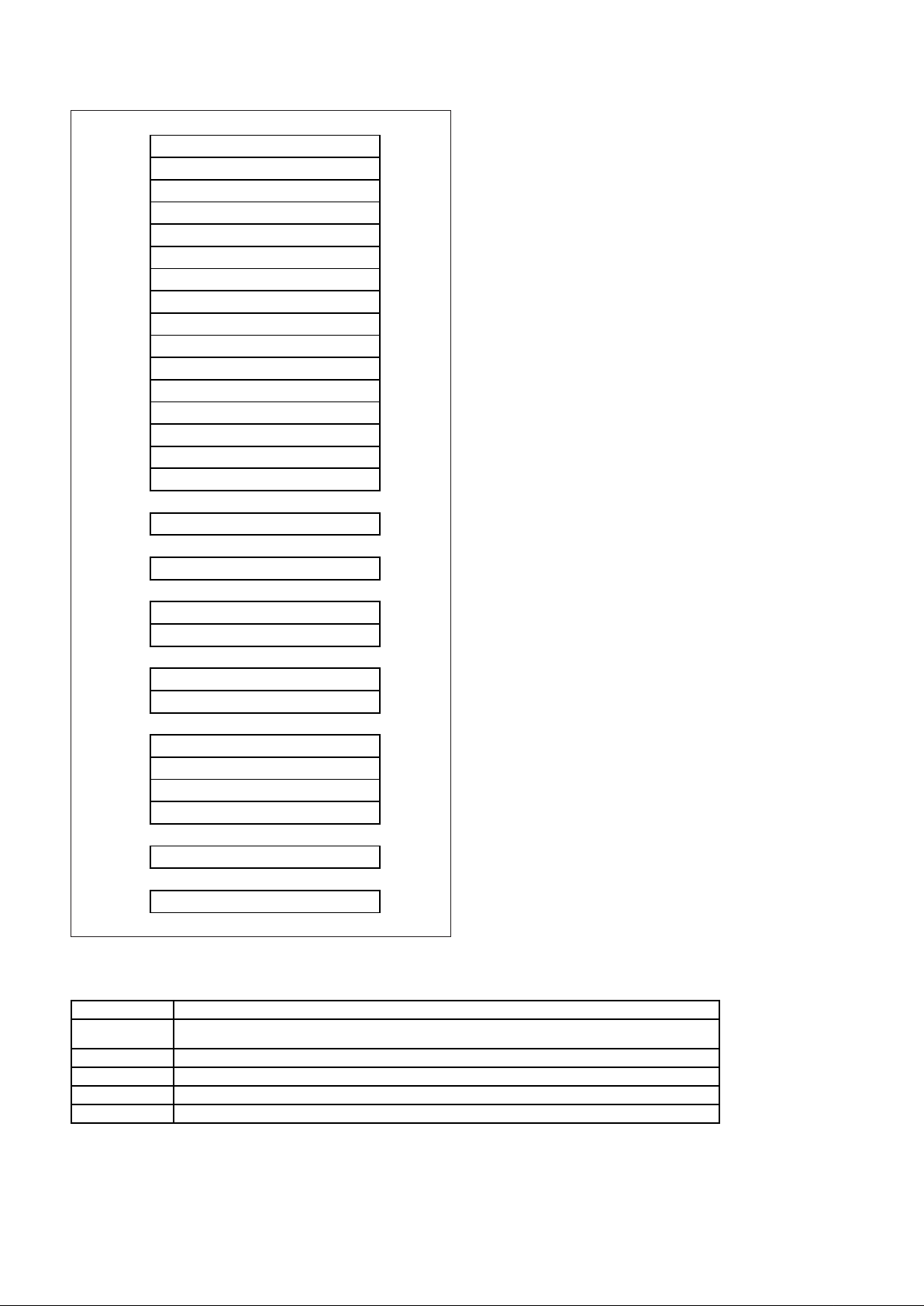

IO control

DOUT

Register

file

Address

generator

Sequencer

Microcode ROM

ALU Qshift

Multiplier Shift network

Interrupt

controller

Flags

Bus

Control

Parity

Bus

arb. Address Data

CLK

ebf

Microcode control

words to other blocks

Y bus

R bus

S bus

Ints

Faults

uAddr

C0

C1

IB

IA

X

BR

rap

sc

mov

ir

abort

uData

bf

IC A

aluv

INTAKN

BUSFAULTN

Figure 1: Architecture

MA31750

High Performance MIL-STD-1750 Microprocessor

Replaces July 1999 version, DS3748-7.0 DS3748-8.0 January 2000

MA31750

2/42

1. ARCHITECTURE

The Dynex Semiconducor MA31750 Microprocessor is a

high performance implementation of the MIL-STD-1750A

(Notice 1) Instruction Set Architecture. Figure 1 depicts the

architectural details of the chip. Two key features of this

architecture which contribute to the overall high performance

of the MA31750 are a 32-bit shift network and a 24-bit parallel

multiplier. These sub-systems allow the MA31750 to perform

multi-bit shifts, multiplications,divisions and normalisations in a

fraction of the clock cycles required on machines not having

such resources. This is especially true of floating-point

operations, in which the MA31750 excels. Such operations

constitute a large proportion of the Digital Avionics Instruction

Set (DAIS) mix and generally a high percentage of many signal

processing algorithms, therefore having a significant impact on

system performance.

Key features include:

1) A three-bus (R, S, and Y) datapath consisting of an

arithmetic/logic unit (ALU), three-port register file, shift

network, parallel multiplier and flags block;

2) Four instruction fetch registers C0,C1, IA, and IB;

3) Two operand transfer registers DI, and DO;

4) Two address registers IC and A;

5) A state sequencer;

6) Micro-instruction decode logic.

The relationship between these functional blocks is shown

in Figure 1.

2. ADDITIONAL FEATURES

The MA31750 may be operated in one of two basic user

selectable modes. 1750A mode follows the requirements of

MIL-STD-1750A (Notice 1) and implements all of the

mandatory features of this standard. In addition, many of the

optional features such as interval timers A and B, a watchdog

timer and parity checking are included. 1750B mode, when

selected, allows the user access to a range of new instructions

and features as described in the Draft MIL-STD-1750B, Option

2. These include a range of unsigned arithmetic operations

and expanded addressing support instructions.

2.1. MIL-STD-1750 OPTIONAL FEATURES

In addition to implementing all of the required features of

MIL-STD-1750A and the Draft standard MIL-STD-1750B, the

MA31750 also incorporates a number of optional features.

Interval timers A and B as well as a trigger-go counter are

provided. Most specified XIO commands are decoded directly

on the chip and an additional set of commands, associated

with MMU and BPU operations, are also decoded on chip.

2.2. BUS ARBITRATION

The MA31750 has a number of extra control lines to allow

its use in a system utilising multiple processors. A bus request

and grant system coupled with external arbitration logic allows

common data and address buses to be used between devices.

A lock request pin is also provided to allow the processor to

maintain control of the buses when modifying areas of shared

memory.

2.3. MEMORY BLOCK PROTECTION

The basic MMU function allows write or execute protection

to be applied on 4KWord block boundaries. This may be

further resolved to 1kWord blocks by the inclusion of a Block

Protect Unit (BPU). The MA31751 can act as both an MMU

and a BPU in 1750A mode, operating with the full compliment

of 1MWord of memory. It will also support expansion to

8MWord in accordance with Draft MIL-STD-1750B.

MA31750

3/42

3. MODES OF OPERATION

MA31750 operating modes include: (1) initialisation, (2)

instruction execution, (3) interrupt servicing, (4) fault servicing,

(5) timer operations and (6) console operation.

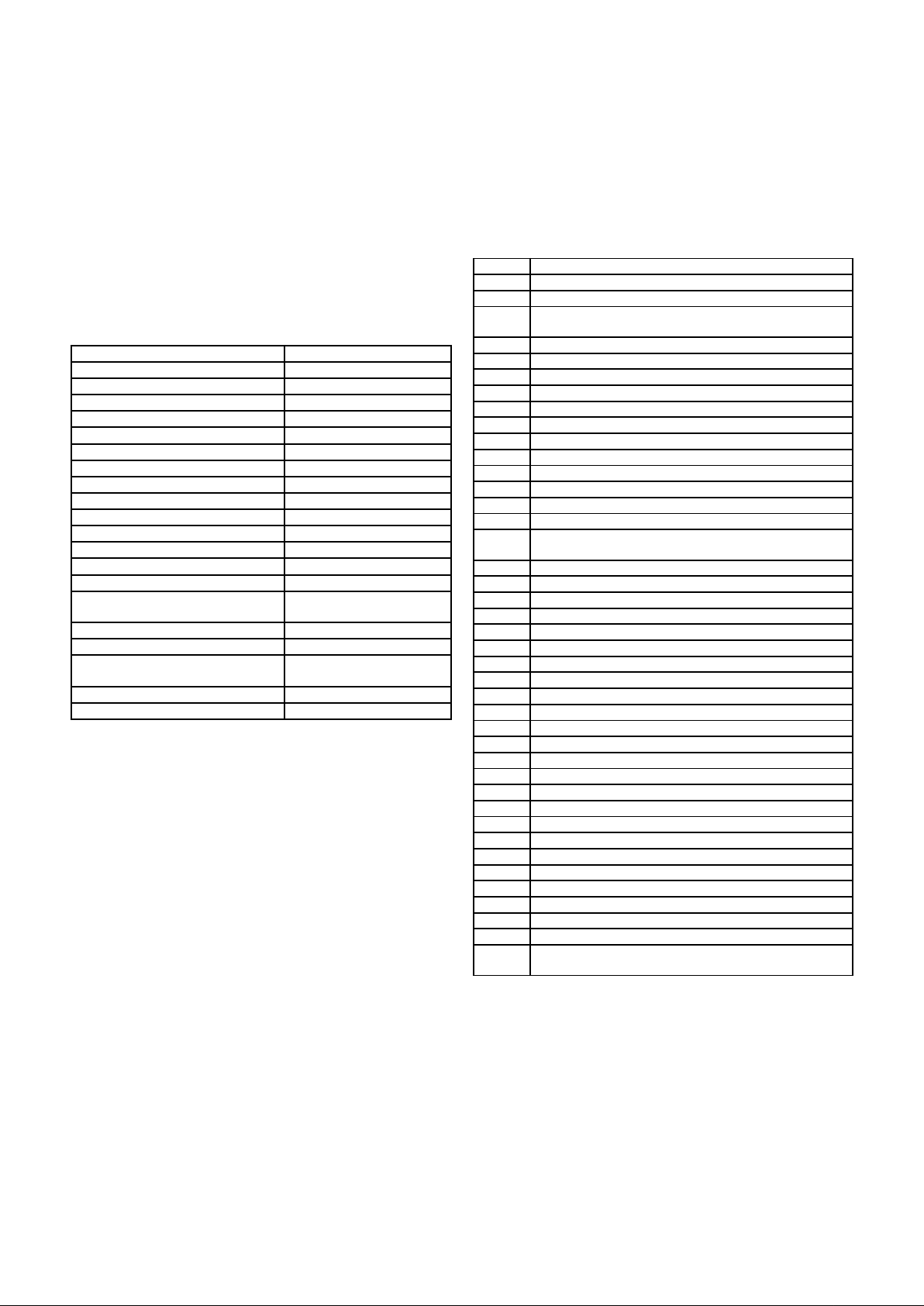

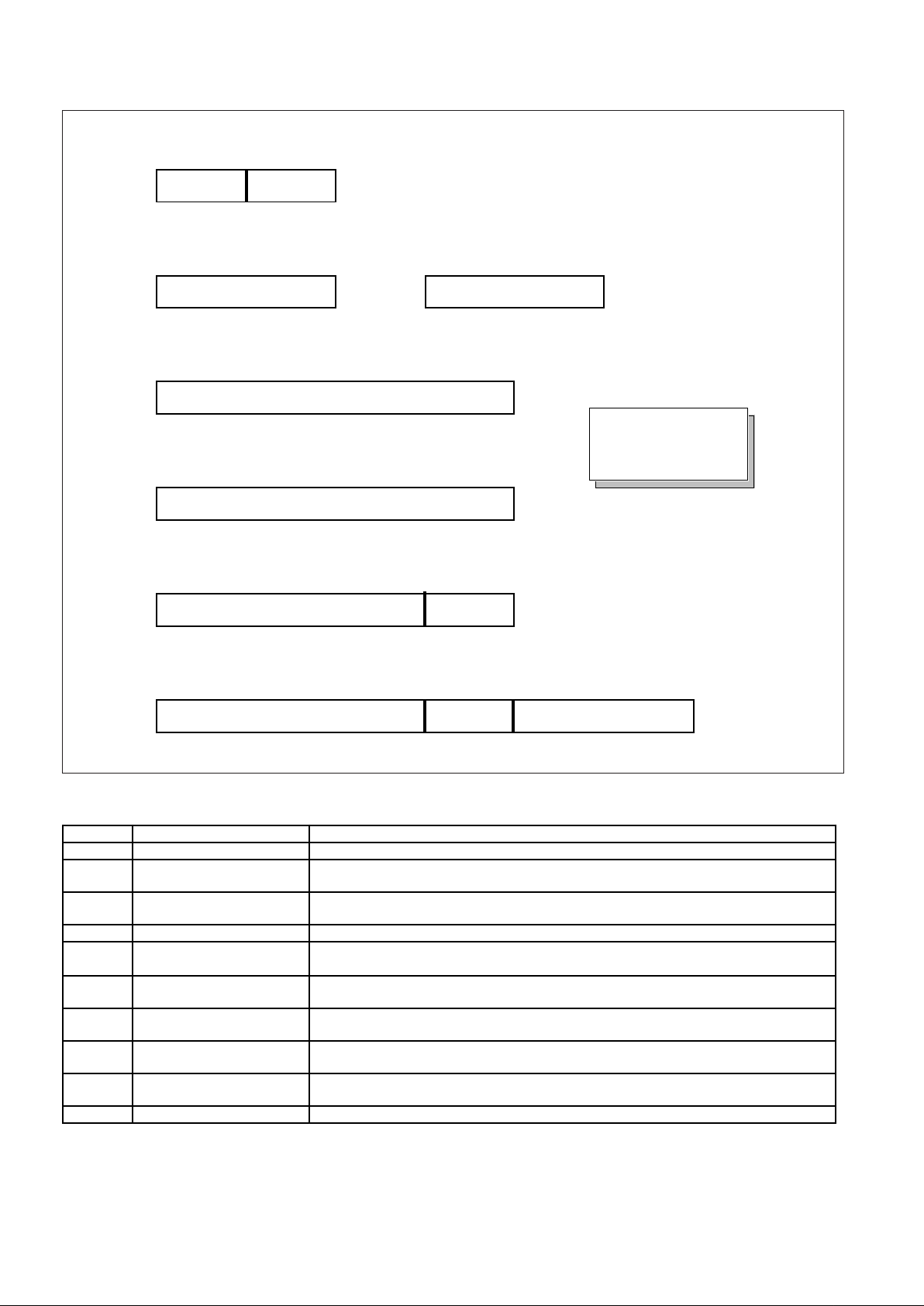

3.1. INITIALISATION

The MA31750 executes a microcoded initialisation routine

in response to a hardware reset or power-up. Figure 3 shows

a cycle-by-cycle breakdown of this routine. The operations

performed are dependent on the system configuration read by

the processor during startup. Figure 2 summarises the

resulting initialisation state.

The last action performed by the initialisation routine is to

load the instruction pipeline. Instruction fetches start at

memory location zero with AS = 0, PS = 0 and PB = 0 and will

be from the Start-Up ROM (SUR) if implemented. Whether

BIT passes or not, the processor will begin instruction

execution at this point. The system start-up code may include

a routine to enable and unmask interrupts in order to detect

and respond to a BIT failure if required.

Addr Operation

0 PIC initialised

1 A<-- 0x8410

*2 Read external configuration register from 8410H

(CONFWN asserted low)

31F 20 If BPU, N<-- 128 else N<-- 0

21 Decrement N; branch to 21 if N >= 0

4 Write internal configuration register

56 If no MMU, br to 7

13 14 15 N <-- 256

16 Decrement N

*17 Write MMU Instruction Page Register N

*18 Write MMU Operand Page Register N; branch to 16 if

N > 0

19 A <-- 0400H

1A N <-- 16

1B PBSR <-- N

1C *1D Write Memory control register to MMU with PB = N

1E Decrement N; branch if N >= 0 to 1B

7 A <-- 0

8 IC <-- A

9 Br to BIT if required

AB Br if no SUR to 00D

CD Re-init PIC

E*F Zero SW

10 32 33 Br to 011 if BIT passed (or not run)

34

35

36 Set FT bit 13

11 Init DMAE, SUREN, NPU

12

*3F8 Fetch first word from 0

*3F9 Fetch second word from 1

First instruction first cycle

* Indicates an external cycle

Figure 3: Initialization Sequence

Figure 2: Initialization State

MA31750

Instruction Counter Zero

Status Word Zero

Fault Register Zero Zero

Fault Mask Register (1750B) All ones

Pending Interrupt Register Zero

Interrupt Mask Register Zero

General Registers Undefined

Interrupts Disabled

Timers A and B Zeroed and started

Timer Reset Registers (1750B) Zero

Trigger-Go Counter Reset and started

TGON Line High

Start-Up ROM Enabled

DMA Disabled

MMU

Page Registers AL/W/E fields Zero

Page Register PPA field Logical to physical

BPU

Memory Protect RAM Zero (disabled)

Global Memory Protect Enabled

MA31750

4/42

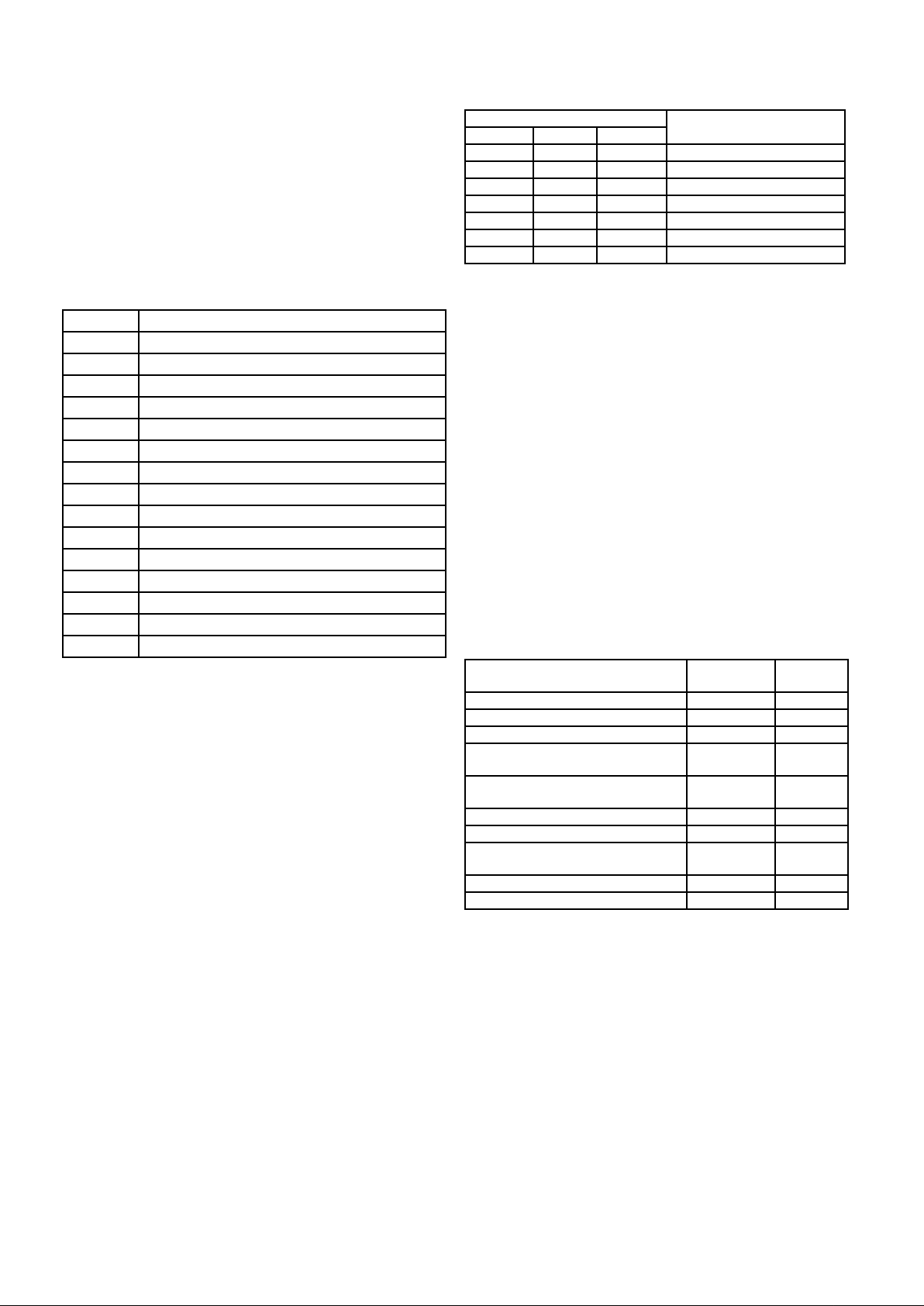

3.1.1. CONFIGURATION REGISTER

The system configuration register allows the MA31750 to

function with a variety of different system designs.

Implemented features such as a BPU should be indicated as

present by setting bits in an externally-implemented 16-bit

latch - see figure 4 for bit assignments. The latch must be

placed in IO space at the address defined by XIO RCW (8410)

shown in the table of XIO commands, Figure 20c. The

processor decodes this command internally and produces a

discrete output signal CONFWN which may be used as the

external register Output Enable control.

3.1.2. BUILT-IN TEST (BIT)

BIT consists of ten subroutines, as outlined in Figure 6. If

all ten subroutines execute successfully, or no BIT is selected

in the configuration word, a BIT pass is flagged (seen

externally as NPU raised high by the initialization routine). If

any part of BIT fails, a corresponding bit identifying the failed

subroutine is set in General Register R0, Fault Bit 13 is set in

the Fault register (FT) and NPU is left in the low state. Figure 6

defines the coding of BIT results in R0. In the event of such a

failure, the resulting processor reset state will be dependent on

where in BIT the error occurred and may not be the same as

that shown in figure 2. A BIT failure indication in FT will set the

level 1 interrupt request bit of the Pending Interrupt (Pl)

register. Since initialisation disables and masks interrupts, this

interrupt request will not be asserted. Any external interrupts or

faults occurring during BIT will be cleared before program

execution begins and will not be serviced.

The processor maintains an internal configuration register

which is updated from the external register during initialisation

and during the execution of a NOP/BPT (No-op/Breakpoint)

instruction. The internal configuration register is used to

control the CPU. Note that although the external register can

be read using XIO RCW, this does not affect the internal

configuration. Note: if the interrupt level/edge trigger select bit

- (bit 4) is changed in the internal register during normal

operation of the device, one or more spurious interrupts may

occur.

When in 1750B mode, the processor needs to know how

many Page Banks are implemented in the external system so

that Status Word changes can be protected properly. MILSTD-1750B allows the options 0,1,2,4,8 or 16. The actual

selection should be coded into the three configuration register

bits MMU0, MMU1 and MMU2 as shown in figure 5.

In 1750A mode, setting any of the MMU select bits

indicates the presence of an MMU, the actual code is

unimportant in this mode.

BPU selects bits 2:0 should be set to indicate how much

BPU-protected memory exists on the system. If no BPU is

present, all three bits should be zero.

Bit Function

0 MMU Select 0

1 BPU Select 0

2 1 = Console operation enabled

3 MMU Select 1

4 Interrupt sensitivity (1 = level, 0 = edge)

5 MMU Select 2

6 Parity sense (1 = odd, 0 = even)

7 1= BIT on power-up

8 1 = Start-Up ROM present

9 1 = DMA device present

10 1=1750A mode, 0=1750B mode

11 1=Instruction set expansion enabled

12 BPU Select 1

13 BPU Select 2

14-15 Reserved for future expansion

Figure 4: Configuration Word Bits

Selected bit Function

MMU2 MMU1 MMU0

0 0 0 No MMU in system

0 0 1 1 Page Bank (PB0)

0 1 0 2 Page Banks (PB0-1)

0 1 1 4 Page Banks (PB0-3)

1 0 0 8 Page Banks (PB0-7)

1 0 1 16 Page Banks (PB0-15)

1 1 X 16 Page Banks (PB0-15)

Note: In 1750A mode, setting any or all of the MMU

select bits indicates the presence of an MMU.

Figure 5: MMU Selection Bits

Test Coverage Machine

Cycles

Bit set

on fail

Temporary Registers (T0-T11) 47 7

General Registers (R0-R15) 79 7

Flags Block 18 8

Sequencer Operation and ROM

checksum

5632 9

Divide routine Quotient Shift

Network

12 10

Multiplier and ALU 13 11

Barrel shift Network 13 12

Interrupts and fault handling and

detection

17 13

Address generator block 13 14

Instruction pipeline 15 15

Note: BIT pass is indicated by all zeros

in FT bits 13,14, and 15

Figure 6: Built-In Test Coverage

MA31750

5/42

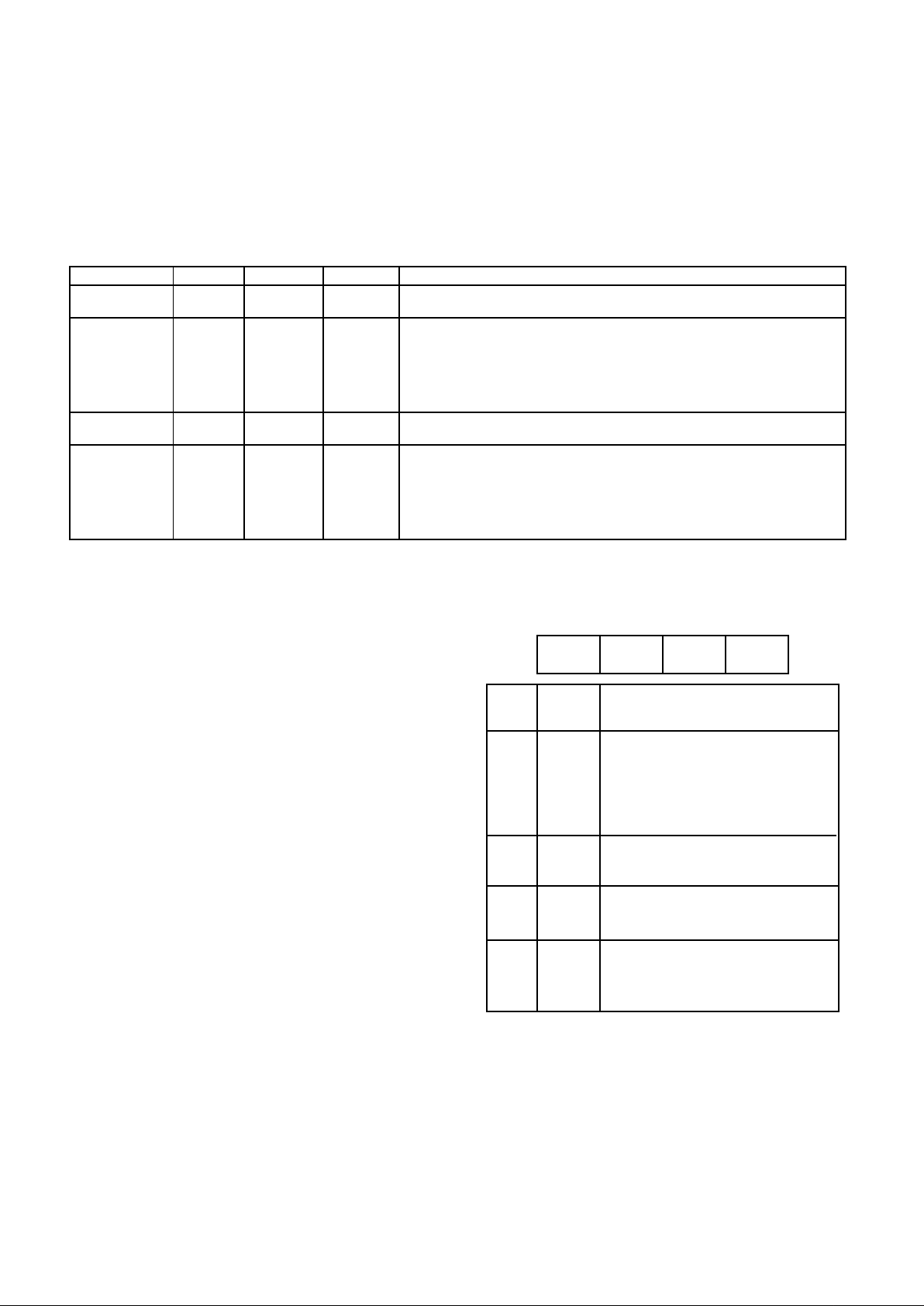

3.2. INSTRUCTION EXECUTION

Once initialisation has been completed, the processor will

begin instruction execution. Instruction execution is

characterised by a variety of operations, each is one machine

cycle in duration (two or more system CLK periods).

Depending on the instruction being executed at the time, these

operations include: (1) internal CPU cycles, (2) instruction

fetches, (3) operand transfers, and (4) input/output transfers.

Instruction execution may be interrupted at the end of any

individual machine cycle by an interrupt or Console request.

Internal cycles are always two CLK periods long, whilst the

other cycle types are a minimum of two CLK periods extendable by inserting waitstates. In all cycles except internal

cycles, RDN, WRN, DSN and AS strobes are produced to

control the transfer and latching of data and address around

the system.

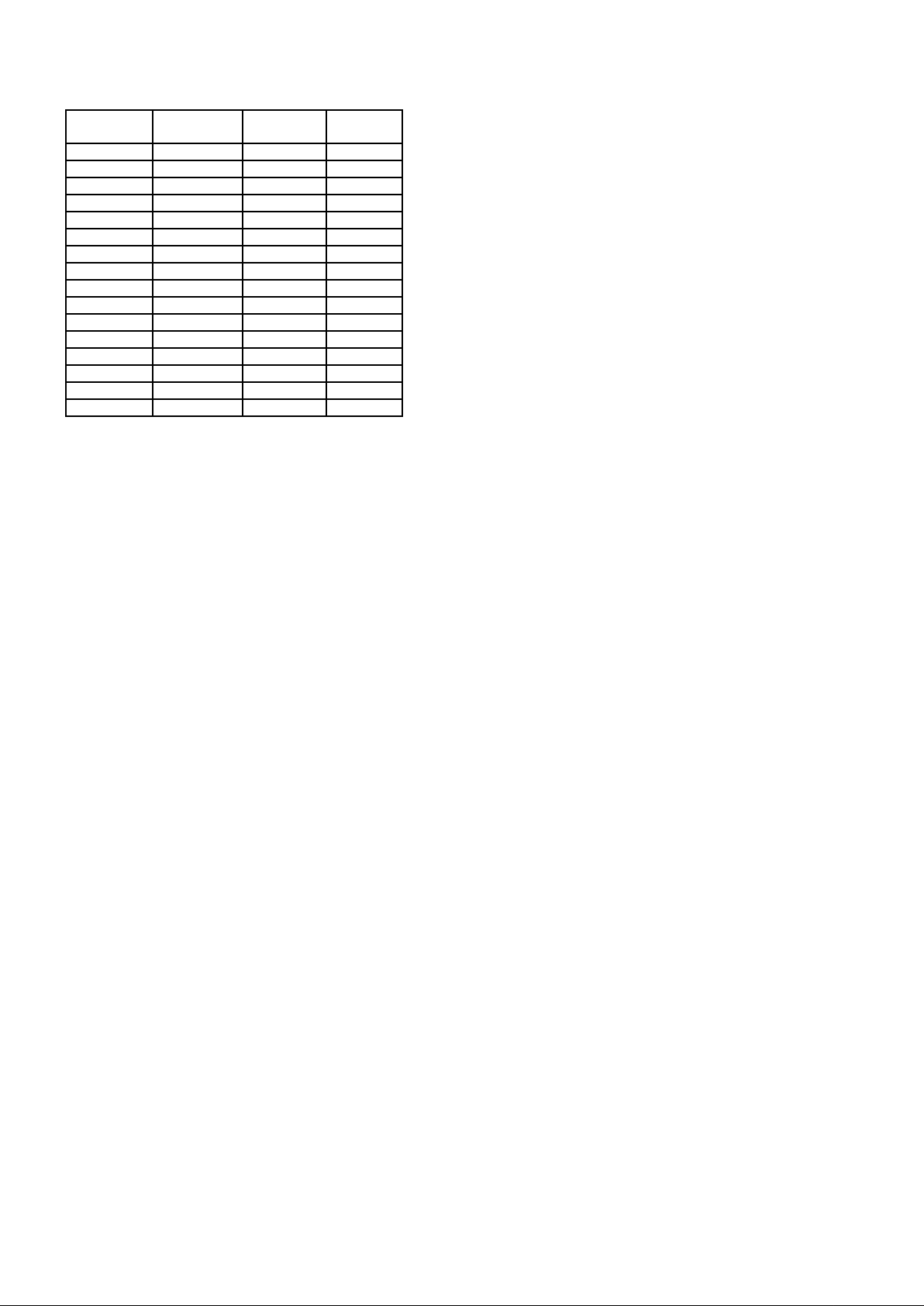

Cycle Type RD/WRN O/IN M/ION Description

Internal Cycle H L H Used to perform all CPU data manipulation operations where bus

activity is not required.

Instruction

Fetch

H L H Used to keep the instruction pipeline full with instructions and/or their

postwords. At least one instruction is always ready for execution when

the preceding instruction is completed. During jump and branch

instruction execution the pipeline is refilled by two consecutive

instruction fetches starting at the new instruction location. It is also

refilled as part of interrupt request processing.

Operand Read

Operand WriteHL

H

H

H

H

Used to read in data from the external system and to write results to the

system.

IO Read

IO Write

H

L

H

H

L

L

Input/Output transfers utilize the MIL-STD-1750 XIO and VIO

instructions. RD/WN defines the direction of the transfer. IO transfers

may be divided into three groups; those commands which are

implemented internally by the CPU, those commands which are

implemented by external system hardware and those commands

defined as illegal by MIL-STD-1750A and B.

Figure 7: External Cycle Types

3.3. IO OPERATION

The MA31750 supports a 64KWord addressing space

dedicated to IO control and communication in accordance with

MIL-STD-1750. The control line MION is asserted low when

accessing IO space (see figure 7 above for other strobe

states). One of the two commands XIO or VIO is used to

specify both data for the transfer and the port address (referred

to as an XIO Command in 1750). The CPU contains logic

which decodes all internally supported XIO commands and

generates the control signals necessary to carry out the

commanded action. In addition, the validity of a command not

implemented internally is verified. Figure 20c identifies the XIO

commands which are internally supported by the MA31750.

3.4. INTERRUPT AND FAULT HANDLING

3.4.1. STATUS WORD (SW)

Figure 8 depicts the status register format. This 16-bit word

is divided into four, 4-bit sections. Three of these sections [AS,

PS and, (1750B mode) PB] are control bits for implementing

expanded memory with an external MMU. The fourth section,

CS, is used to hold the carry, positive, zero and negative

condition flags set by the result of the previous arithmetic

operation.

CS R (PB) PS AS

0 3 4 7 8 11 12 15

Field Bits Description

CS

0

1

2

3

CONDITION STATUS

C- Carry from an addition or no

borrow from a subtraction.

P- Result > 0

Z- Result = 0

N- Result < 0

R

PB

4-7 RESERVED (=0) in 1750A mode

Page Bank Select in 1750B mode

PS 8-11 PROCESSOR STATE:

(a)- Memory access to key code

(b)- Priviledged instruction enable

AS 12-15 ADDRESS STATE:

Page register sets for expanded

memory addressing.

Figure 8: Status Word Format

MA31750

6/42

The AS field is used during expanded memory access to

define the page register set to be used for instruction and

operand memory references. The PS field is used during

memory protect operations to define the access key used for

memory accesses. The PS field is also used during execution

of privileged Instructions - PS must be zero for such operations

to be legal. See Section 4.3 for further information on the use

of this field. The PB field is used in conjunction with the AS

field in 1750B mode to expand the number of page registers

available. Note that attempting to set AS or PB to a non-zero

value with no MMU, or setting PB to a non-zero value in 1750A

mode is illegal. This will be aborted and a fault 11 will be

generated (SW will remain unchanged).

3.4.2. PENDING INTERRUPT REGISTER (PI)

This 16-bit register is used to capture and hold interrupts

until they can be processed by microcode and user software. A

logic 1 is used to represent an active pending interrupt. The Pl

register supports three dedicated external, six user-definable

external, and seven dedicated internal interrupts. Levelsensitive interrupts are sampled on each rising CLK edge,

whilst edge sensitive interrupts are captured immediately.

Figure 10: Fault Register Bit Assignments

Figure 9: Pending Interrupt Bit Assignments

System Internal

Interrupts Interrupts

PWRD 0 (Cannot be disabled or masked)

1 Machine Error (Cannot be

disabled)

INT02 2

3 Floating-Point Overflow

4 Fixed-Point Overflow

5 Executive call (Cannot be

disabled or masked)

6 Floating-Point Underflow

7 Timer A Overflow

INT08 8

9 Timer B Overflow

INT10 10

INT11 11

IOI1 12

INT13 13

IOI2 14

INT15 15

System Internal

Faults Faults

MPROE (CPU) 0

MPROE (DMA) 1

PE (CPU memory) 2

PE (CPU IO) 3

PE (DMA) 4

EXADE or Bus 5

Timeout (CPU IO)

6 Parallel IO Transfer Error

FLT7 7

EXADE or Bus

Timeout (CPU 8

memory)

9 Illegal Instruction Opcode

10 Priviledged Instruction

11 Unimplemented Address State

Reserved 12

SYSF 13 MA31750 BIT Fail

EXADE (DMA) 14

SYSF 15

MA31750

7/42

3.4.3. MASK REGISTER (MK)

This 16-bit register is used to store the interrupt mask.

Interrupts are masked by ANDing each mask bit with its

corresponding Pl register bit. ie. A logic zero in a given bit

position indicates that the corresponding bit in the Pl register

will be masked. Interrupts which are masked will be captured

in the Pl register but will not be acted on until unmasked.

Interrupt level zero can not be masked.

3.4.4. PRIORITY ENCODER

This encoder generates an interrupt request to the

sequencer block whenever one or more unmasked interrupts

are pending and enabled in the Pl. The highest priority

unmasked pending interrupt is encoded as a 4-bit vector. This

vector is used during interrupt servicing in order to create the

interrupt linkage and service pointers.

3.4.5. FAULT REGISTER (FT)

This 16-bit register is used to capture and hold both internal

and user implemented external faults using positive logic, i.e.,

a logic one represents a fault. Bus cycle faults are captured at

the end of each machine cycle whilst the two general purpose

faults SYSFN and FLT7N are set when the low time exceeds

the minimum pulse width. Setting any one or more faults in FT

will cause a level 1 (machine error) interrupt request. Once a

fault is set in FT, it may only be cleared via an XIO command.

In 1750B mode, a fault mask register is provided to allow

selective masking of fault conditions. Section 4 (Software

Considerations) contains further information. Figure 27 shows

the fault register assignments.

3.4.6. MEMORY FAULT PAGE AND ADDRESS REGISTERS

These registers capture the page and address information

at the end of each external cycle until a memory fault occurs.

Faults setting bits 0, 1, 2 and 8 in the fault register cause the

registers to stop latching new address information, so retaining

information about the address at which the fault occured. The

registers can be read (using the GPS defined XIOs RMFP and

RMPA). The fault register must be cleared and both memory

fault registers read before latching can restart.

The information stored in the memory fault registers is as

follows:

MFPR[0:3] MFPR[4:7] MFPR[8:10] MFPR[11]

A[0:3] PB[0:3](ASOB) Res ION

MFPR[12:15] MFAR[0:15] Note: MFPR[11] is the

AS[0:3] A[0:15] inverse of OIN.

These registers are only available if there is an MMU in the

system. If there is no MMU present, then the RMFP and RMFA

XIO commands become illegal.

The address information held in these registers can be

used to restart code after a memory fault has occurred. Bits

[6:7] of the OAS register store information on the type of

instruction which was being executed when the fault occured:

00 → branch that was taken

01 → single word instruction

10 → double word instruction

(Subtracting this value from the saved address will give the

address of the failed instruction unless it was a branch that

was taken).

3.4.7. INTERRUPT SERVICING

Nine user interrupt request inputs are provided for

programmed response to asynchronous system events. A low

on any of these inputs will be detected at the rising edge of

CLK (level sensitive interrupts only) and latched into the

Pending Interrupt (Pl) register on the falling edge of CLK at the

end of the current CPU cycle. This sequence occurs whether

interrupts are enabled or disabled or whether the specific

interrupt is masked or unmasked. More details of interrupt

operations are available in Applications Note 4.

All of the user interrupts PWRDN, INT02N - INT15N may

be programmed to be either level or edge sensitive by setting

or clearing the appropriate bit in the system configuration

register. If edge sensitivity is selected then an interrupt request

input must return to the high state before a subsequent request

on that input will be detected. If level sensitivity is selected then

holding an interrupt input low will cause a new interrupt to be

latched following each service. Note that interrupts IOI1N and

IOI2N are level sensitive only.

In order that the system may recognise when a service has

been started, an interrupt acknowledge pin is provided. During

the microcoded interrupt service routine execution, the

processor will read the Linkage Pointer address in memory.

During this operand read cycle, the processor will also assert

INTAKN low, which may be used in conjunction with AS and

address bus bits A[11:14] to reveal the priority level of the

interrupt being serviced. (A[11:14] = 0 indicates level 0

interrupt, A[11:14] = 1 indicates level 1 interrupt, and so on).

INTAKN should also be used to remove level-sensitive

interrupt requests to ensure that repeated requests are not

generated.

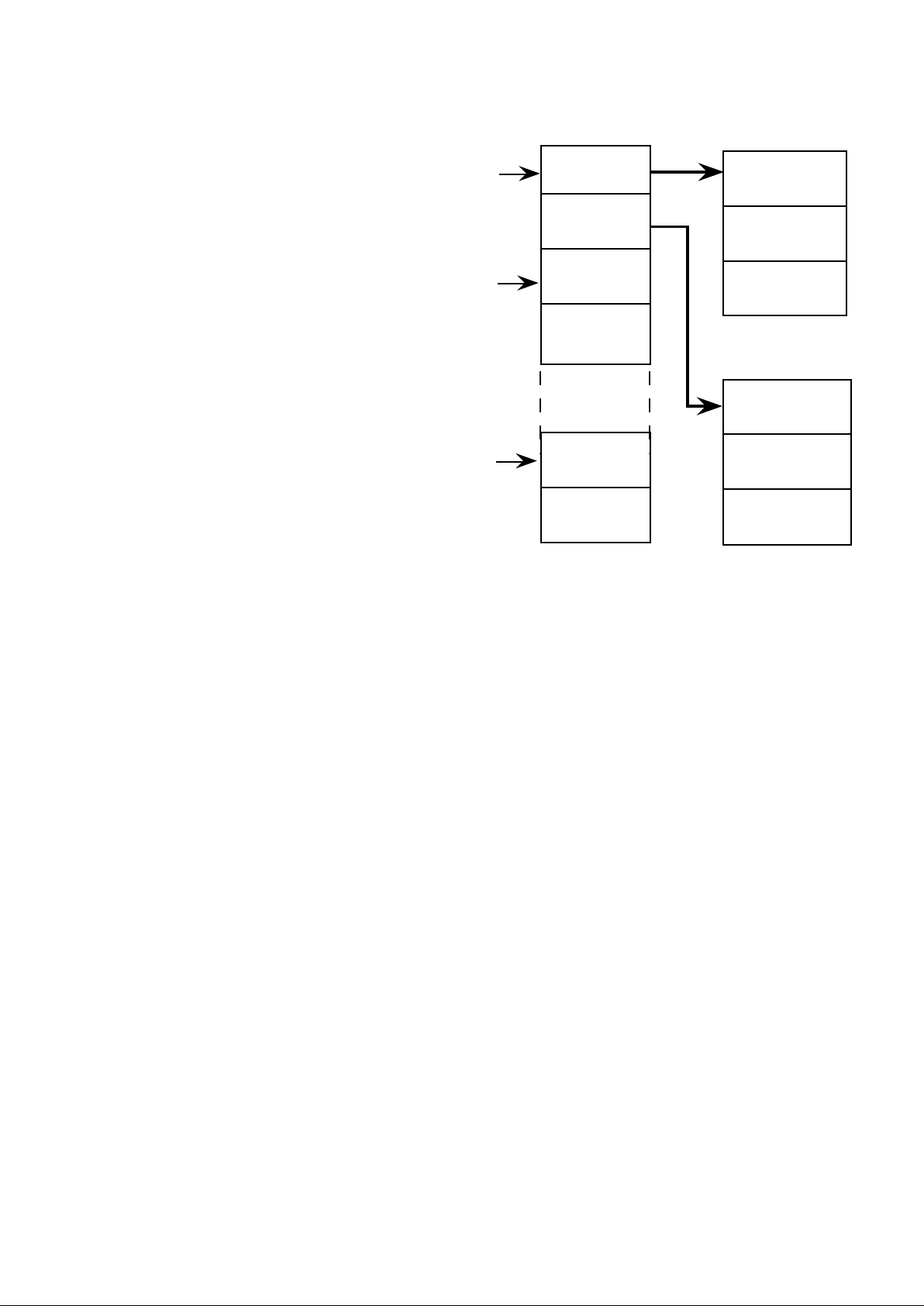

Linkage

Pointer 0

Service

Pointer 0

Linkage

Pointer 1

Service

Pointer 1

Linkage

Pointer 15

Service

Pointer 15

Interrupt 0

Interrupt 1

Interrupt 15

Old Interrupt

Mask

Old Status

Word

Old Instruction

Counter

CPU status at time

of interrupt

New Interrupt

Mask

New Status

Word

New Instruction

Counter

Status at start of

Service Routine

Figure 11: Interrupt Vectoring

MA31750

8/42

When an interrupt request is latched into Pl, it is ANDed

with its corresponding mask bit in the mask register (MK).

NOTE: Interrupt level 0 is non-maskable. Any unmasked

pending interrupts are output to the priority encoder where the

highest priority is encoded as a 4-bit vector. If interrupts are

enabled and an unmasked interrupt is pending, the priority

encoder will assert an interrupt request to the sequencer. 1 or

2 extra CLKs will be inserted into the machine cycle on which

the interrupt request is asserted.

Upon completing execution of each MIL-STD-1750A or B

instruction, the sequencer checks the state of the priority

encoder interrupt request. If a request is asserted, the

sequencer branches to the microcode interrupt service

routine. This routine reads the 4-bit pending interrupt vector

and then uses this value to calculate the appropriate interrupt

linkage (old processor context save area) and service (new

context load area) pointers. Figure 11 depicts this relationship.

Figure 12 defines the pointer values.

Using the linkage and service pointers, the microcode

interrupt service routine performs the following: (1) the current

contents of the status word, mask register, and instruction

counter are saved; (2) a write status word (WSW) I/O

command is executed with an all zero data word; (3) the new

mask is loaded into MK and interrupts are disabled; (4) the

new status word is read and checked for a valid Address State

(AS[0:3]) field - If the address state is non-zero and an MMU is

not present, AS[0:3] is set to zero and fault 11 (address state

error) is set in the fault register FT); (5) a write status word

command using the new status word is performed; and (6) the

new IC value is loaded into IC, the instruction pipeline is

flushed and refilled starting at the new address, and instruction

execution begins.

[NOTE: The steps listed above represent a summary of

actions performed during interrupt servicing and do not

necessarily reflect the actual order in which these events take

place.]

If an address state fault occurs during the service routine,

interrupt level 1 will be set. This interrupt will be serviced when

interrupts are re-enabled unless it is masked by the new value

in MK.

3.4.8. FAULT SERVICING

Five user fault inputs are provided. A low on any of the

three bus-cycle-related fault inputs, EXADEN, MPROEN or

PEN, will be latched into the Fault Register (FT) on the next

falling edge of AS. A low on either of the two general purpose

fault inputs, FLT7N or SYSFN, will be latched immediately and

will be sampled into the appropriate bit of FT on the falling

edge of AS.

Any fault which sets a bit in the FT immediately causes a

level 1 pending interrupt to be entered into the PI register. This

interrupt is maskable but may not be disabled.

This interrupt will be serviced at the end of the currently

executing 1750 instruction if not masked. The microcoded

interrupt service routine reads the interrupt priority vector and

clears the bit relating to the serviced interrupt from the PI.

However, the FT retains the set fault bits until the FT is cleared

using the XIO RCFR command. (A non-destructive read of the

FT is provided by the XIO RFR command.) Anti-repeat logic

between the FT and the PI prevents the same fault being

latched and serviced twice. However, as all FT bits are ORed

together and input to PI bit 1, this also prevents any other faults

being serviced until the fault register has been cleared. It is

imperative, therefore, that the fault service routine executes a

RCFR XIO before exiting. Different types of faults are serviced

slightly differently as follows:

3.4.8.1. MPROEN and EXADEN

If MPROEN and/or EXADEN are low on a falling clock

edge with AS and DSN high (see figure 23a), the processor will

wait in this state. If either fault input remains low during two

falling edges of TCLK, the cycle is forced to complete but RDN/

WRN and DSN are inhibited (see figure 24b). This allows the

processor to prevent erroneous accesses. An access fault will

be registered as AS falls at the end of the cycle.

3.4.8.2. PEN

External parity errors are latched into the FT on the falling

edge of AS. The fault bit set is dependant upon the type of

transfer taking place (memory, IO or DMA).

3.4.8.3. FLT7N and SYSFN

These faults are latched immediately, but are not sampled

into the fault register until the following falling edge of AS.

3.4.9. PARITY GENERATION AND CHECKING

The MA31750 features on-chip parity generation and

checking on all data bus transfers. Data generated by the

processor has a parity bit attached to it to allow external logic

to verify write transfers. On read transfers, the processor will

check the incoming parity (if enabled) and will generate the

appropriate parity error fault if detected. However, the data to

be checked is only available as DSN rises at the end of the

cycle so the error flag is generated and latched in the cycle

following the erroneous cycle. Parity checking may be

Interrupt

No.

LP

AddressSPAddress

PWRD 0 20 21

ME 1 22 23

INT02 2 24 25

FI.P o/f 3 26 27

Fx.P o/f 4 28 29

BEX 5 2A 2B

FI.P u/f 6 2C 2D

Timer A 7 2E 2F

INT08 8 30 31

Timer B 9 32 33

INT10 10 34 35

INT11 11 36 37

IOI1 12 38 39

INT13 13 3A 3B

IOI2 14 3C 3D

INT15 15 3E 3F

Note: Addresses (in hex) are in operand space

Figure 12: Interrupt Pointer Address

MA31750

9/42

disabled when operating with devices which do not support

parity generation by asserting the DPARN (Disable Parity)

input low. The checking polarity (odd or even) is selectable

with Configuration Register bit 6.

3.5. TIMER OPERATIONS

The MA31750 implements interval timers A and B, a

trigger-go counter, and a bus fault timer. A discussion of each

follows:

3.5.1. TIMERS A AND B

Two general-purpose, 16-bit timers are provided in the

processor. Timer A is clocked by the TCLK input; timer B is

clocked by an internally generated TCLK/10. The divider

circuit is reset when Timer B is reset to give deterministic

processor operation. MIL-STD-1750 requires TCLK to be a

100kHz pulse train. If allowed to overflow, timers A and B will

set level 7 and level 9 interrupt requests respectively. Each

timer can be read, loaded, started and stopped by using XIO

commands as identified in figure 20c.

Each timer has associated with it a reset register from

which the timer is automatically loaded following a software

reset or overflow. These registers are initially loaded with zero

but may be reloaded from software (using the XIO instructions

OTA and OTB) to provide greater control over the count

period.

The MA31750 timers A and B will be disabled when the

device enters Console mode, as required by MIL-STD-1750A

Notice 1.

3.5.2. TRIGGER-GO COUNTER

This 16-bit counter is clocked by the TCLK input and is

typically used as a system “watchdog” timer. It is enabled

during system initialisation and may be preset under software

control to give a wide range of timeout intervals. In order that

the count period may be controlled, a reset register is

provided. On reset, this register is loaded with zero, but can be

reloaded under software control to take any value between 0

and FFFF

16

(a value of zero gives the maximum count period).

This allows the timeout period to be varied between 20us and

0.65s. Note that there is no value which disables the timer.

The counter is incremented on each TCLK falling edge.

Whenever the trigger-go counter overflows, TGON drops low

and remains low until the counter is reloaded from the reset

register via the GO internal XIO command. TGON low would

typically be used to initiate a user-defined system recovery

action such as a system reset.

3.5.3. BUS FAULT TIMER

All bus operations are monitored to ensure timely

completion. A hardware timeout circuit is enabled at the start of

each memory and l/O transfer (DSN high-to-low transition) and

is reset upon receipt of the external ready (RDYN) signal. If

this circuit fails to reset within a minimum of one TCLK period

or a maximum of two TCLK periods, either bit 8 (if the

transaction is with memory) or bit 5 (if the transaction is with l/

O) of the Fault Register (FT) is set. This sets Pending Interrupt

level 1 and causes the strobes to be suppressed and the

current bus cycle to be aborted. The MIL-STD-1750 instruction

is aborted, and control passes to the level 1 interrupt service

routine (if the level 1 interrupt is unmasked). The timeout

mechanism is disabled and reset if DTON is asserted low.

3.6. CONSOLE OPERATION

The MA31750 is capable of interfacing directly to an

external console, allowing the developer to: examine and

change the contents of internal registers, memory and IO

devices; single step code and halt the processor. Applications

Note 3 provides a full description of the Console interface, its

implementation and operation.

3.7. MULTIPROCESSOR SUPPORT

Once initialisation has been completed, the processor will

begin instruction execution by executing a sequence of microinstructions, each one machine cycle (two system clock

periods) long. Each machine cycle may perform either an

internal or an external operation; if the operation is purely

internal then the system busses will not be in use and may be

reassigned to another processor.

An external machine cycle (indicated by REQN low during

the second half of the previous cycle) will cause the processor

to stall upon completion of the current microcycle, awaiting

GRANTN asserted low. Whilst GRANTN is high the busses

remain undriven.

In simple, single processor systems which use no DMA

devices the GRANTN line should be tied to GND to allow the

processor to retain control of the busses. The LOCKN and

REQN pins can be left open-circuit in this case. Applications

Note 11 provides further information for designers of systems

with more than one bus master.

4. SOFTWARE CONSIDERATIONS

4.1. OPERATING MODES

The MA31750 is capable of being operated in one of two

basic modes as previously mentioned. These are described in

detail below:

4.1.1 1750A MODE

1750A mode is a full implementation of MIL-STD-1750A

(Notice 1) and includes some of the optional features

mentioned in this standard.

4.1.2 1750B MODE

1750B mode is an implementation of the proposed MILSTD-1750B, Option 2, Draft of 17th July 1988. This mode

extends the basic 1750A mode operation. Note that the

transcendental functions SIN, COS, LN etc. (Option 3 of MILSTD-1750B) are not supported. Features new to MIL-STD1750B which are in violation of MIL-STD-1750A are only

enabled in 1750B mode. The additional instructions available

in 1750B mode are detailed in figure 20b.

4.2. ACCESSING IO USING XIO AND VIO COMMANDS

MIL-STD-1750 defines a 64KWord addressing space

which is available exclusively for accessing IO resources. Two

special commands, XIO and VIO, are provided as part of the

instruction set for accessing this space. Port addresses are

specified as a 16-bit Command word which is supplied as a

parameter to the XIO/VIO instruction. The MSB of the

Command word indicates the direction of data transfer

between the port and the register specified in the XIO

command (a 1 in the MSB indicates that the port is being read,

whilst 0 indicates a write to the port).

MA31750

10/42

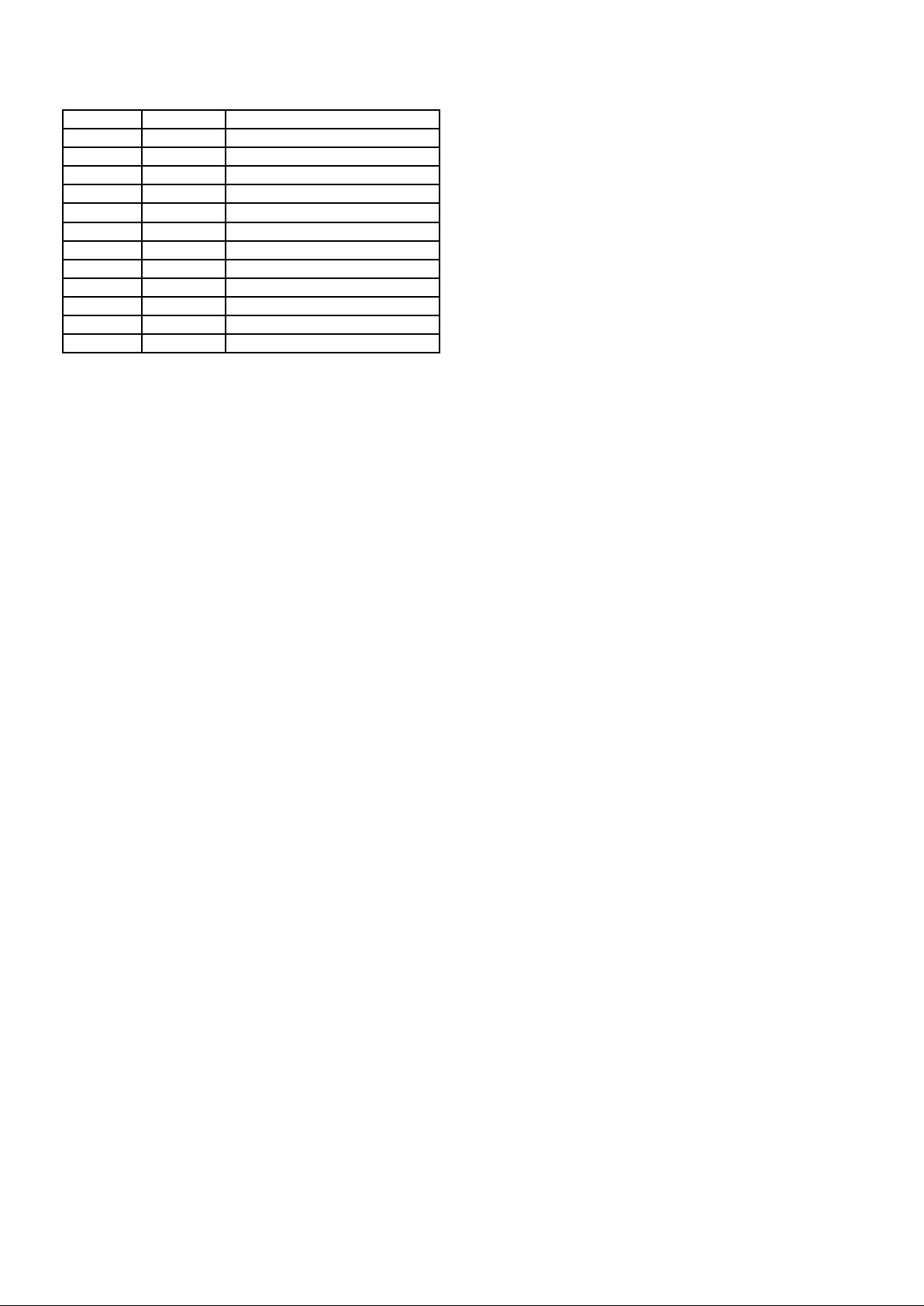

Figure 13: XIO Command Channel Grouping

XIO command addresses are grouped by the Standard

according to function. Certain groups are ‘reserved’ and must

not be implemented. Attempts to read or write these areas will

be prevented by the processor and a fault will be logged in the

fault register. Other groups are designated ‘spare’ and may be

implemented as required by the system designer. Note,

however, that there is a third group which access system

resources such as MMU page registers and interrupt control

registers which are not available to the user to implement. A

summary of the XIO map is provided in figure 13, whilst the

detailed list of implemented command addresses is shown in

Figure 20c.

The VIO (Vectored IO) command allows a number of IO

operations to be executed in a sequence from a table.

Applications Note 8 gives further information on the use of this

command.

Both XIO and VIO are priveleged commands and as such

can only be executed when the Status Word PS field is zero.

4.3. PROCESSOR STATE AND PRIVILEGED

INSTRUCTIONS

The Processor State is defined by a 4-bit value held in the

processor Status Word. If the value is made non-zero then

attempts to execute the commands XIO, VIO or LST will be

aborted and a fault will be raised. This is intended to deny

direct access to the hardware from user applications (running

in PS≠0), whilst allowing the Operating System (operating with

PS=0) access to the system IO and interrupt resources.

If an MMU is present on the system the PS field is used in

conjunction with the page register Access Key field to provide

a further level of protection to the system. When PS=0 access

is granted to all pages, irrespective of their key value. If PS is

non-zero, access is only permitted if the Access Key is equal to

the PS value, or the Access Key is 15. Access Key 15 should

be applied to a shared area of code or data, and is accessable

to all PS values.

Output Input Usage

0000-03FF 8000-83FF PIO

0400-1FFF 8400-9FFF Spare

2000-20FF A000-A0FF CPU and auxiliary register control

2100-2FFF A100-AFFF Reserved

3000-3FFF B000-BFFF Spare

4000-40FF C000-CFFF CPU and auxiliary register control

4100-4CFF C100-CCFF Reserved

4D00-4FFF CD00-CFFF Extended memory protect RAM

5000-50FF D000-D0FF Memory protect RAM

5100-51FF D100-D1FF MMU Instruction Page Registers

5200-52FF D200-D2FF MMU Operand Page Registers

5300-7FFF D300-FFFF Spare

4.4. USING START-UP ROM

The transition between code execution from Start-up ROM

and system RAM must be made with care. If a system overlays

RAM with the Start-Up ROM and the transition is made by

simply executing XIO DSUR from the ROM, then the

instruction pipeline will contain the value stored in the ROM

location immediately following the XIO DSUR command. This

value will be treated as an instruction and the processor will

attempt to execute it. In such cases, it is recommended that

DSUR be followed by an unconditional branch instruction with

offset, i.e. the BR instruction. An alternative approach is simply

to jump to a portion of RAM not overlaid by the Start-Up ROM

and execute DSUR from RAM.

4.5. USING SOFTWARE TIMERS A AND B

The MA31750 implements the two software timers, A and

B as defined in the MIL-STD 1750A specification. These are

general purpose timers which are clocked at 100kHz and

10kHz respectively, giving clock ‘tick’ intervals of 10us and

100us respectively. They may be started using the XIO TAS

and XIO TBS instructions, and stopped using XIO TAH and

XIO TBH. If a timer is allowed to overflow (FFFF

16

- 000016) it

will generate pending interrupt levels 7 (A) or 9 (B).

In 1750B mode each timer has associated with it a reset

register which may be loaded with any 16-bit value from

software. If a timer is allowed to overflow, an automatic reset

will take place which will reload the timer with the value held in

its on-chip reset register, provided that the timer had

previously been loaded using XIO OTA/OTB. If this is not the

case, then the timers will reset to zero on overflow. Each of the

reset registers is initialised to zero but may be changed using

XIO OTAR or XIO OTBR.

4.6. FAULT MASK REGISTER

A fault mask register is accessible in 1750B mode. Its

function is similar to that of the Interrupt Mask register and

allows selective enabling and disabling of all bits in the Fault

Register. All faults are maskable. Setting a bit in this register

allows the corresponding fault bit to be seen by the system.

The mask register is loaded with FFFF

16

on initialisation.

4.7. GENERAL REGISTERS R0-R15

There are 16 general purpose registers defined by MILSTD-1750; each is 16-bits wide. Adjacent registers may be

concatenated to provide storage for the larger data formats

(Double Integer and Float - 32-bit; Extended Float - 48-bit).

The first register in the set stores the most significant data

word and is the register specified when referring to the value.

Wrap-around occurs between R15 and R0.

Although generally all registers are the same, certain

registers are notionally assigned to particular tasks, see figure

15.

MA31750

11/42

4.8. MIL-STD-1750 DATA TYPES

The MA31750 fully supports 16-bit fixed-point singleprecision, 32-bit fixed-point double-precision, 32-bit floatingpoint, and 48-bit extended precision floating- point data types.

Figure 16 depicts the formats of these data types.

All numerical data is represented in two’s complement

form. Floating-point numbers are represented by a fractional

two’s complement mantissa with an 8-bit two’s complement

exponent. All floating-point operands are expected to be

normalised. If not normalised, the results from an instruction

are not defined.

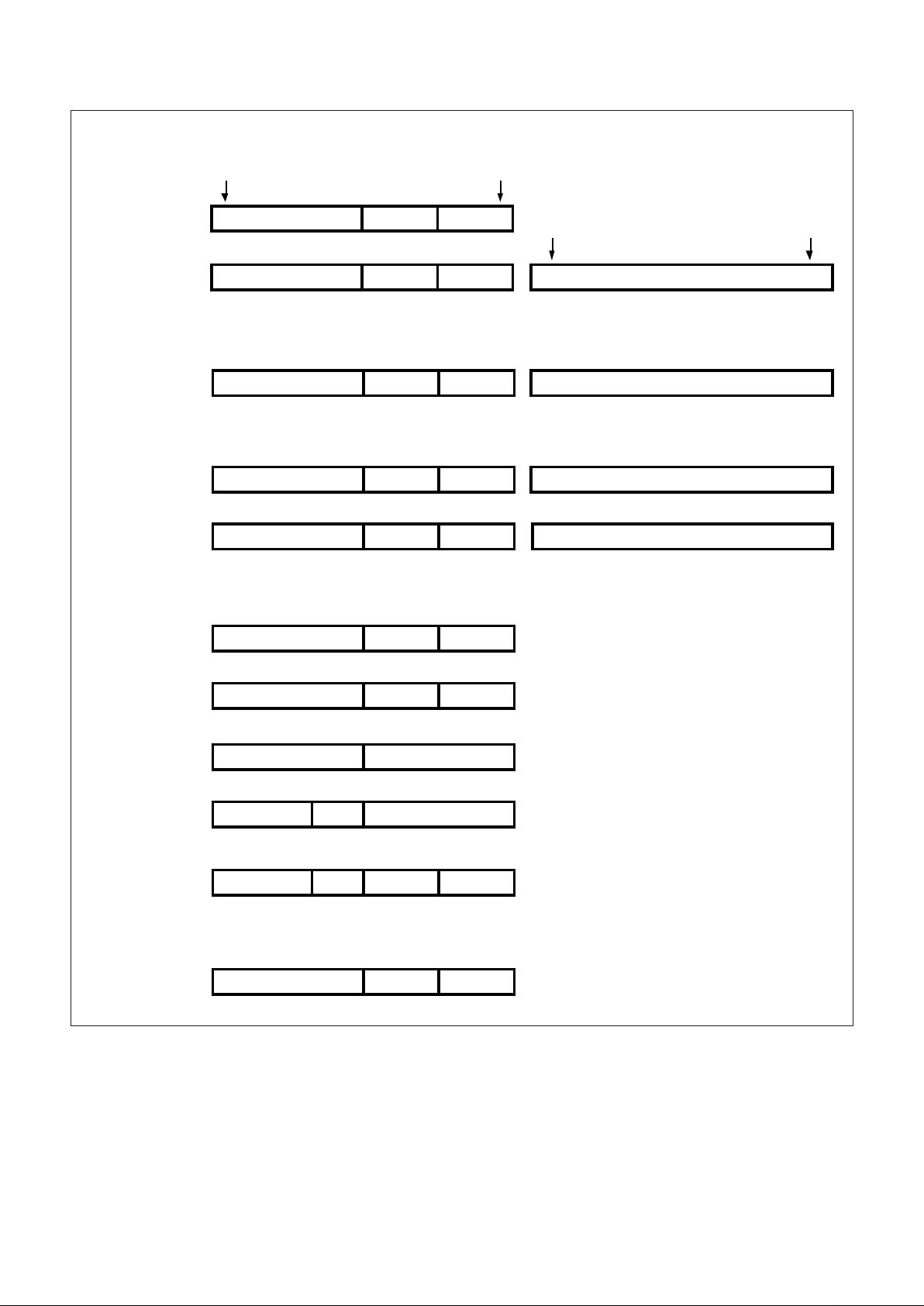

4.9. MIL-STD-1750 ADDRESSING MODES

The MA31750 supports the eight basic addressing modes

specified in MIL-STD-1750A. These addressing modes are

depicted in Figure 18 and are defined below. In binary

operations one operand is assumed to be in a register

(specified as part of the opcode) whilst the second operand

(the Derived Operand, DO) is taken from a source which is

dependent upon the addressing mode, see figure 17. Many

adddressing modes may be specified as indexable: the index

register may be any of the general purpose registers R1-R15

(if 0 is specified then the non-indexable form is used). For

Base Relative addressing modes the first operand is fixed as

part of the instruction (either R0 for Double Integer operations,

or R2 for Single Integer operations).

4.10. MEMORY ADDRESSING CAPABILITY

In accordance with MIL-STD-1750A, the MA31750 can

access a 64KWord address space directly. With the addition of

a single external Dynex Semiconductor MA31751 chip,

configured as a Memory Management Unit (MMU), this

address space may be expanded to 1MWord (1750A mode) or

8MWord (1750B mode). The MA31751 data sheet gives

further information on the MMU/BPU chip and on the memory

management scheme employed. Note that whilst one MMU

can be used to provide the full range of physical addresses to

the system memory, the logical addressing capability may also

be expanded by adding further MMU devices up to a maximum

of 16.

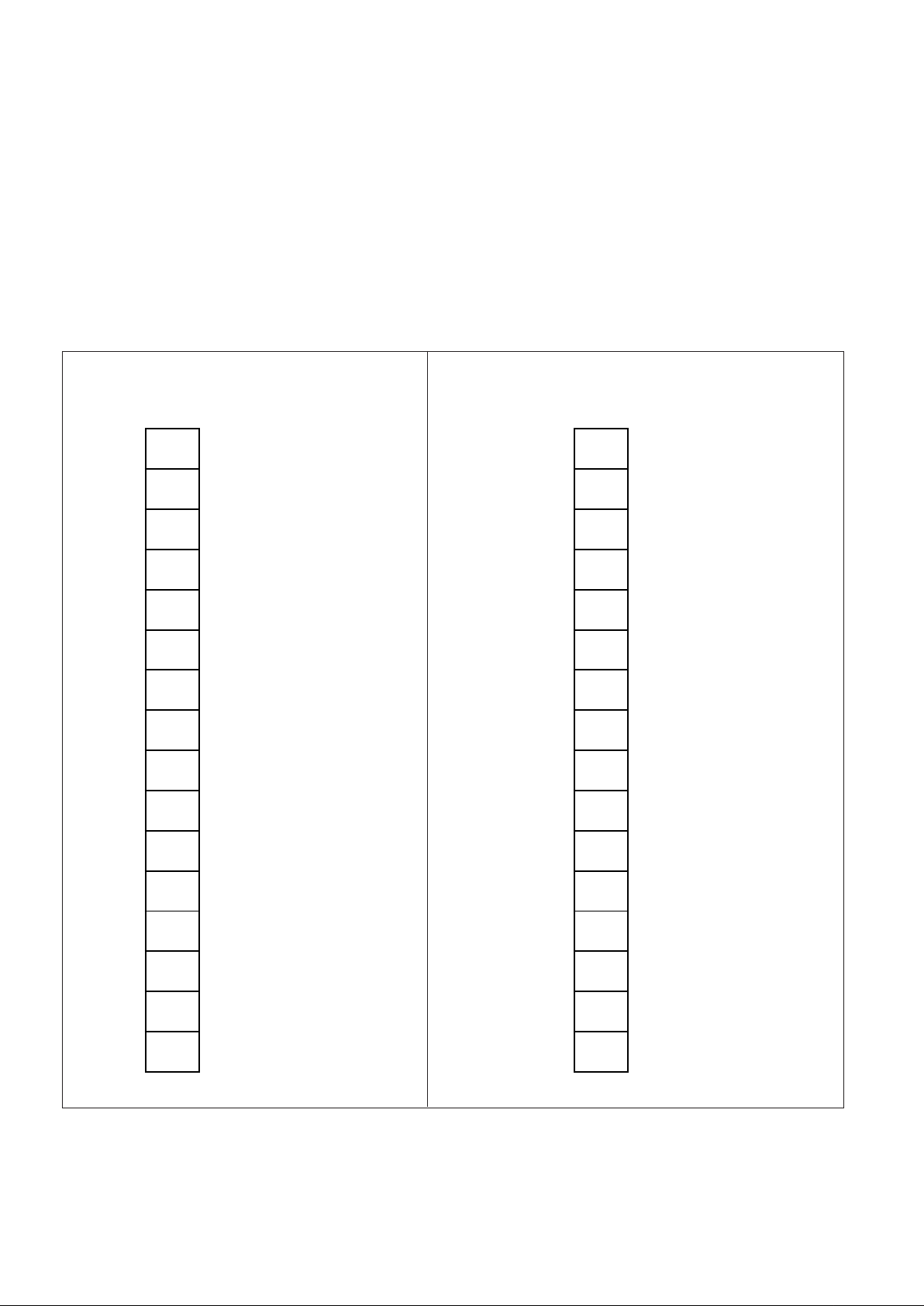

Figure 14: Register Set Model

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

R14

R15

Status Word (SW)

Instruction Counter (IC)

Fault Register (FT)

Fault Mask (1750B only)

Pending Interrupt (PI)

Interrupt Mask (MK)

Timer A

Timer A reset (1750B only)

Timer B

Timer B reset (1750B only)

Trigger-Go Reset Register

Configuration

Register(s) Notional Use or Restriction on Use

R0 Cannot be used as an index register

With R1: Implied register in Double mode Base Relative addressing

R2 Implied register in Single mode Base Relative addressing

R3-R11 General purpose

R12-R15 Base relative registers

R15 Stack pointer in PSHM and POPM operations

Figure 15: General Register Usage

MA31750

12/42

Figure 16: Data Formats

Single Precision Fixed-Point

Byte

Double-Precision Fixed-Point

Floating Point

Extended Precision Floating Point

Value

015

Mantissa (Most significant) Mantissa (Least Sig.)

Exponent

0 2324 3132 47

Mantissa Exponent

02331

Upper byte Lower byte

015

Unsigned value

031

Value

031

Unsigned value

015

Unsigned Double Precision Fixed-Point (1750B)

Unsigned Single Precision Fixed-Point (1750B)

MSB LSB MSB LSB

MSB LSB MSB LSB

MSB LSB

MSB LSB

MSB LSB MSB LSB

MSB LSB MSB LSB MSB LSB

Note: All values are

Signed 2s complement

unless shown as

unsigned.

24

Mode Name Derived Operand

R Register Direct The operand is contained in a regular specified by the instruction.

D, DX Memory Direct The instruction postword (plus RX if RX ≠ 0), contains the memory address of the

operand.

I, IX Memory Indirect The instruction postword (plus RX if RX ≠ 0) contains the address of the address

which holds the operand.

IM, IMX Immediate Long The instruction postword (plus RX if RX ≠ 0) holds the operand.

ISP Immediate Short Positive The operand value is specified as part of the instruction. (ISP specifies values

between 0001H and 0010H, ISN specifies values between FFFFH and FFEFH).

ISN Immediate Short Negative The operand value is specified as part of the instruction. (ISP specifies values

between 0001n and 0010n, ISN specifies values between FFFFn and FFEFn).

ICR Instruction Counter

Relative

A 2s-complement, 8-bit displacement which is sign-extended and added to the

Instruction counter to provide an offset of -128 to +127.

B Base Relative Data at address given by: contents of specified base register (R12-R15, specified

by opcode), plus unsigned 8-bit displacement field from opcode.

BX Base Relative Indexed Data at address given by contents of specified base register (R12-R15, specified

by opcode), plus contents of RX register if RX ≠ R0

S Special See instruction for details.

Figure 17: Address Mode Summary

MA31750

13/42

OC RA

0 7 8 11 12

15

OC RA

0 7 8 11 12 15

RX = 0 (Non-indexed)

RX ≠ 0 (Indexed)

OC RA

0 7 8 11 12 15

RX = 0 (Non-indexed)

RX ≠ 0 (Indexed)

OC RA

0 7 8 11 12 15

OC RA

0 7 8 11 12 15

RX = 0 (Non-indexed)

RX ≠ 0 (Indexed)

OC RA

0 7 8 11 12

15

OC RA

0 7 8 11 12

15

OC

0 7 8

15

OC

0 7 8

15

OC

OCX

0 7 8 11 12

15

RX = 0 (Non-indexed)

RX ≠ 0 (Indexed)

OC S1

0 7 8 11 12

15

RB

RX

RX

OCX

RX

I

I

D

DU

S2

RX

BR'

BR'

BR' = BR - 12

5 6

5 6

A

A

I

I

16 31

31

31

3116

16

16

Legend

OC = Operation Code

RA = Destination Register

RB = Source Register

RX = Index Register

A = Address (logical)

OCX = Extension to Operation Code

I = Immediate Data

D = Displacement

BR' = Base Register Reference

DU = Displacement (positive)

S1, S2 = Special Code

FORMAT

1. Register Direct

"R"

2. Memory Direct

"D"

"DX"

3. Memory Indirect

"I"

"IX"

4. Immediate Long

a. Not indexable

"IM"

b. Indexable

"IM"

"IMX"

5. Immediate Short

a. Positive

"ISP"

b. Negative

"ISN"

6. IC Relative

"ICR"

7. Base Relative

a. Not Indexable

"B"

b. Indexable

"B"

"BX"

8. Special

"S"

MODE MSB

LSB

INSTRUCTION

MSB LSB

POSTWORD

Figure 18: Addressing Modes

Loading...

Loading...