Page 1

SERVICE MANUAL

For U.S.A., Canada

& Japan model

Ver. 2

MODEL

ADV-M71

DVD SURROUND RECEIVER

注 意

サービスをおこなう前に、このサービスマニュアルを

必ずお読みください。本機は、火災、感電、けがなど

に対する安全性を確保するために、さまざまな配慮を

おこなっており、また法的には「電気用品安全法」に

もとづき、所定の許可を得て製造されております。

従ってサービスをおこなう際は、これらの安全性が維

持されるよう、このサービスマニュアルに記載されて

いる注意事項を必ずお守りください。

For purposes of improvement, specifications and

●

design are subject to change without notice.

Please use this service manual with referring to

●

the operating instructions without fail.

●

Some illustrations using in this service manual are

slightly different from the actual set.

16-11, YUSHIMA 3-CHOME, BUNKYO-KU, TOKYO 113-0034 JAPAN

● 本機の仕様は性能改良のため、予告なく変更すること

があります。

● 補修用性能部品の保有期間は、製造打切後

修理の際は、必ず取扱説明書を参照の上、作業を行って,

●

ください。

● 本文中に使用しているイラストは、説明の都合上現物

と多少異なる場合があります。

X0182V.02 DE/CDM 0308

8年です。

Page 2

ADV-M71

SAFETY PRECAUTIONS

Thefollowingcheckshouldbeperformedforthecontinuedprotectionofthecustomerandservicetechnician.

LEAKAGE CURRENT CHECK

Beforereturningtheunittothecustomer,makesureyoumakeeither(1)aleakagecurrentcheckor(2)alinetochassis

resistancecheck.Iftheleakagecurrentexceeds0.5milliamps,oriftheresistancefromchassistoeithersideofthe

powercordislessthan460kohms,theunitisdefective.

LASER RADIATION

Donotstareintobeamorviewdirectlywithopticalinstruments,class3Alaserproduct.

500V

1M

2

(1)

(2)

(1)

(2)

2

Page 3

ADV-M71

3

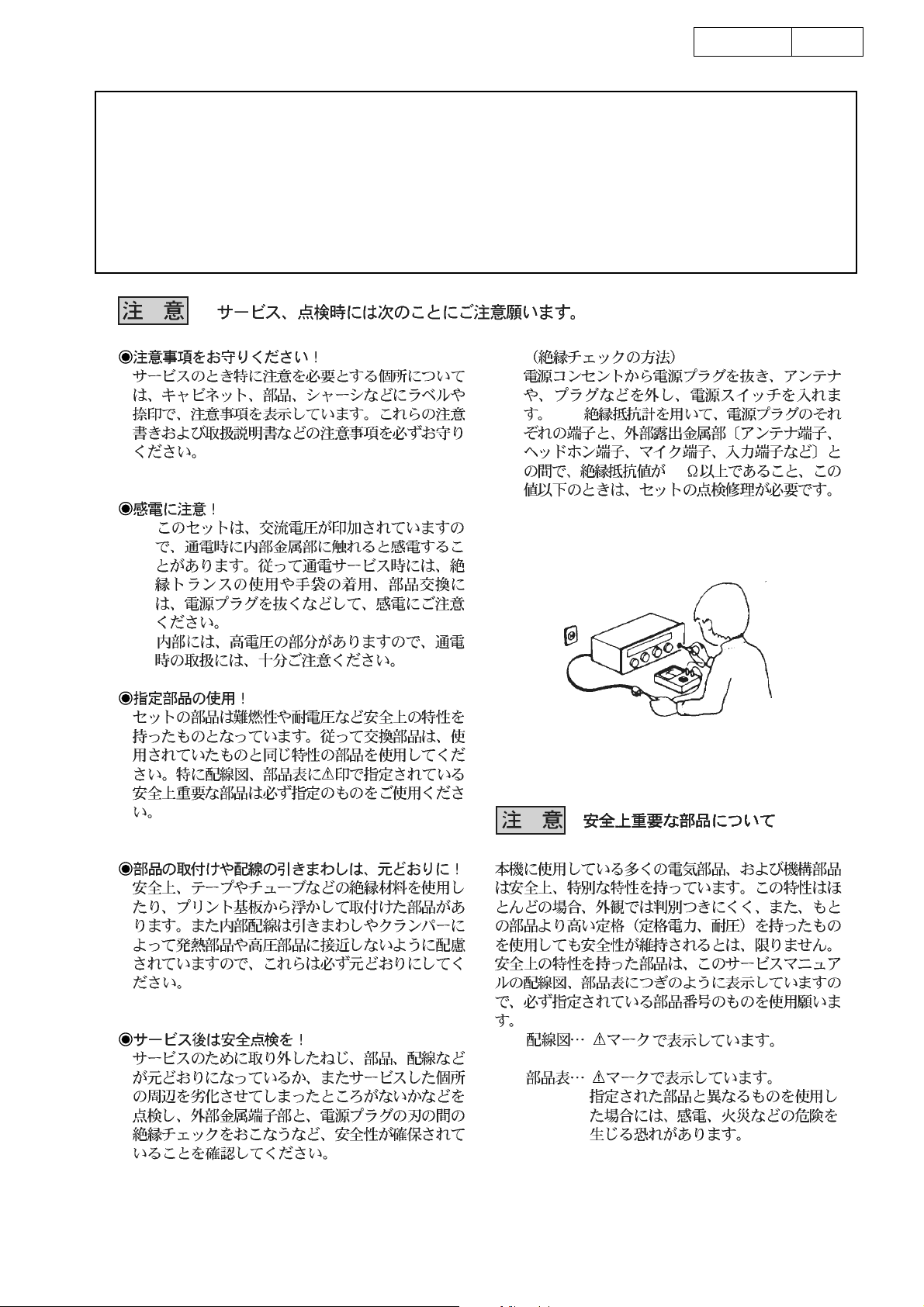

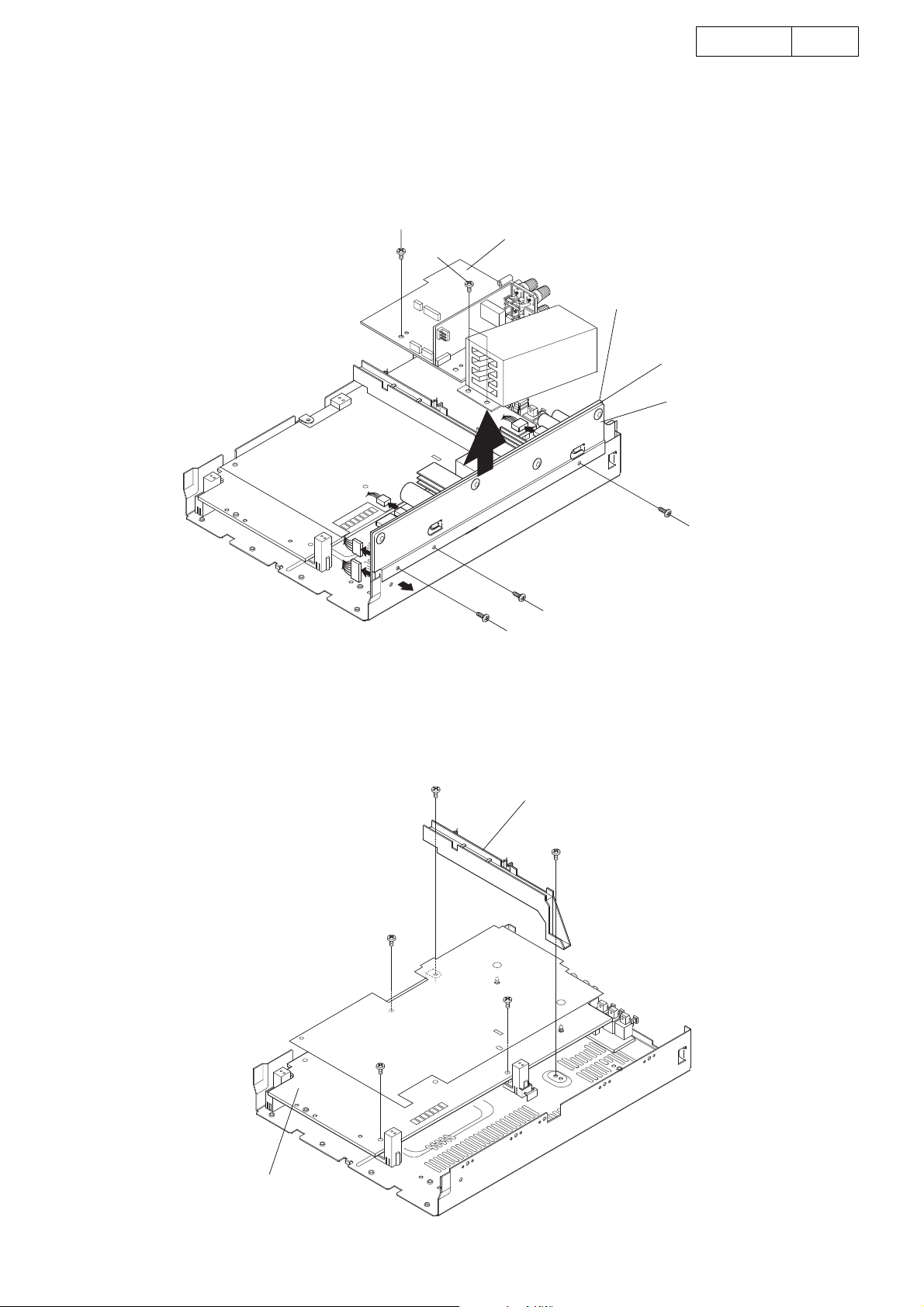

DISASSEMBLY

(Follow the procedure below in reverse order when reassembling)

1. TOP COVER

Remove 2 screws on both sides and 4 screws on the rear,

then detach upward the Top Cover.

2. FRONT PANEL

(1)Disconnect FFC and 3p WIRG on the P.W.B..

(2)Remove 4 lower screws.

(3)Detach the Front Panel with releasing the hook on both

sides.

各部のはずしかた

(組み立てるときは、逆の順序でおこなってください。)

1. トップカバーのはずしかた

両サイドのからねじ 2本、リアパネルからのねじ 4本を

はずし、トップカバーを上にはずします。

2. フロントパネルのはずしかた

(1)基板から、FFC と 3P ワイヤをはずします。

(2)FRONTPANELの下側からねじ 4 本をはずします。

(3)両サイドの HOOK をはずし、FRONTPANEL をはずし

ます。

FRONT PANEL

DVD MECHA

FFC

3P WIRG

HOOK

3

Page 4

ADV-M71

4

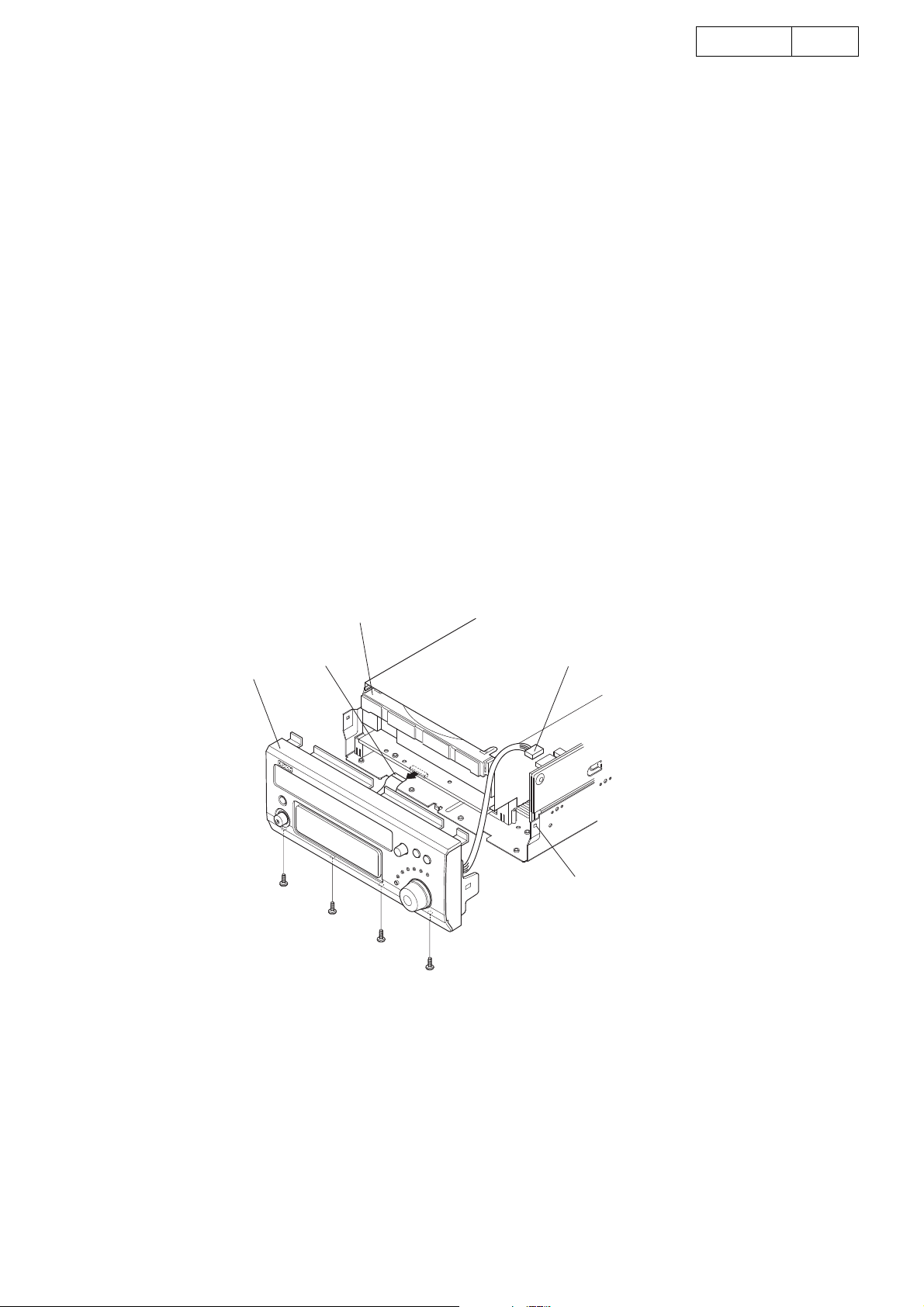

3. DVD MECHANISM UNIT

(1)Remove 5 screws to detach the MECHA COVER and

the DVD Mecha.

(2)Disconnect WIRG from the DVD Mecha.

DVD MECHA

3. DVDメカのはずしかた

(1)ねじ 6 本をはずし、MECHACOVERとDVDMECHA-

EARTHCLIPをはずします。

(2)DVDMECHAからワイヤをはずします。

MECHA COVER

4. REAR PANEL

(1)Pull out the cord bush.

(2) Remove 26 screws.

EARTH CLIP

4. リアパネルのはずしかた

(1)CORDBUSHをはずします。

(2)ねじ 26 本をはずします。

CORD BUSH

4

Page 5

ADV-M71

5

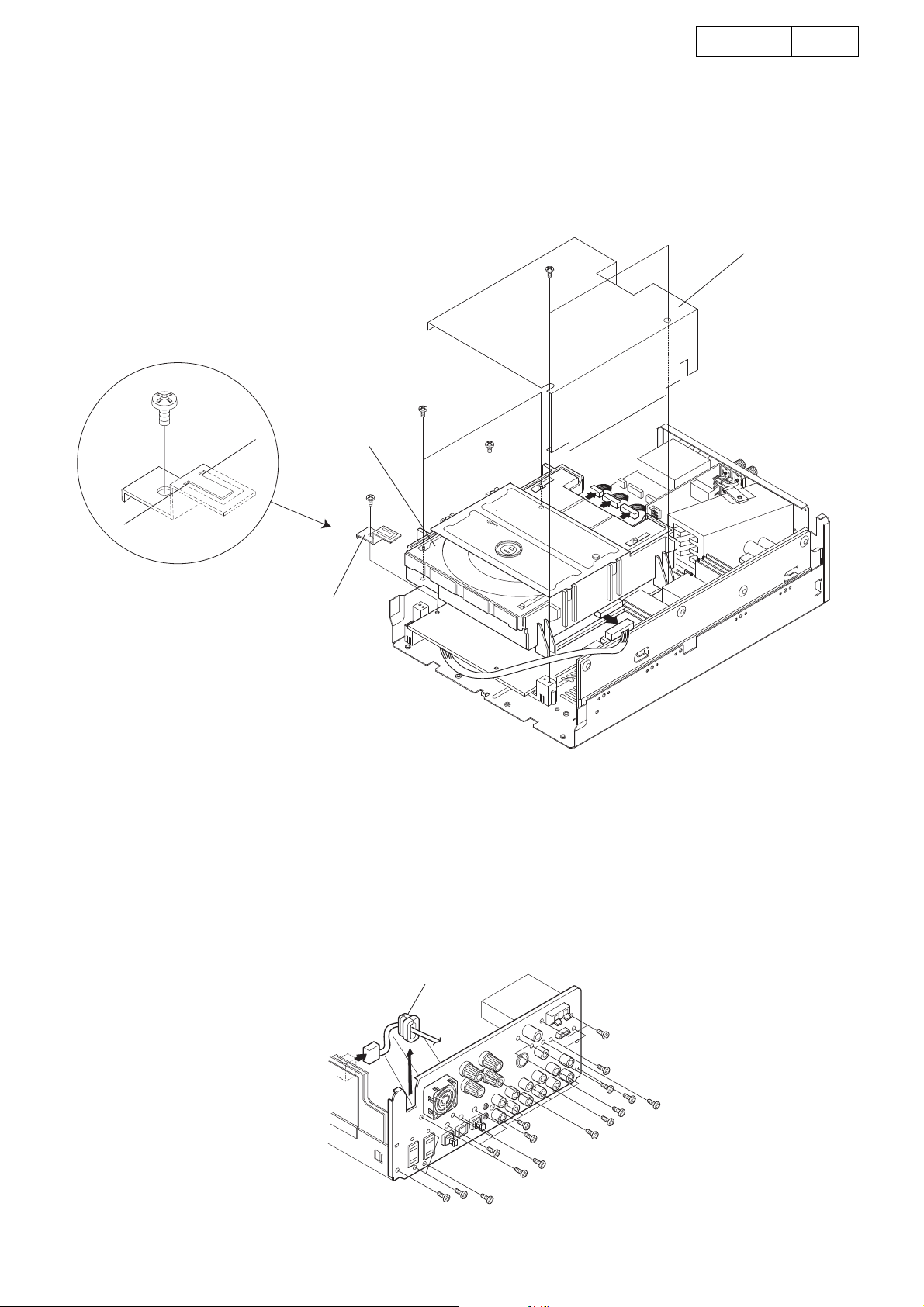

5. POWER P.W.B. / AMP VIDEO P.W.B.

(1)Remove 3 screws to detach the P.W.B. BRACKET

together with the POWER P.W.B..

(2)Unplug 4 connectors on the POWER P.W.B..

(3)Remove 3 screws.

(3)

5. パワー基板/アンプビデオ基板

(1)ねじ 3 本をはずし、POWERP.W.B.といっしょにP.W.B.

BRACKETをはずします。

(2)POWERP.W.B.のコネクタ4か所をはずします。

(3)ねじ3本をはずします。

AMP VIDEO P.W.B.

(3)

POWER P.W.B.

PVC SHEET

P.W.B. BRACKET

6. MAIN P.W.B.

(1)Remove 2 screws fixing the P.W.B. stay.

(2)Remove 3 screws.

(1)

(1)

(1)

メイ

6.

ン基板

(1)P.W.B.STAYを止めているねじ2本をはずします。

(2)ねじ 3 本をはずします。

P.W.B. STAY

MAIN P.W.B.

5

Page 6

ADV-M71

6

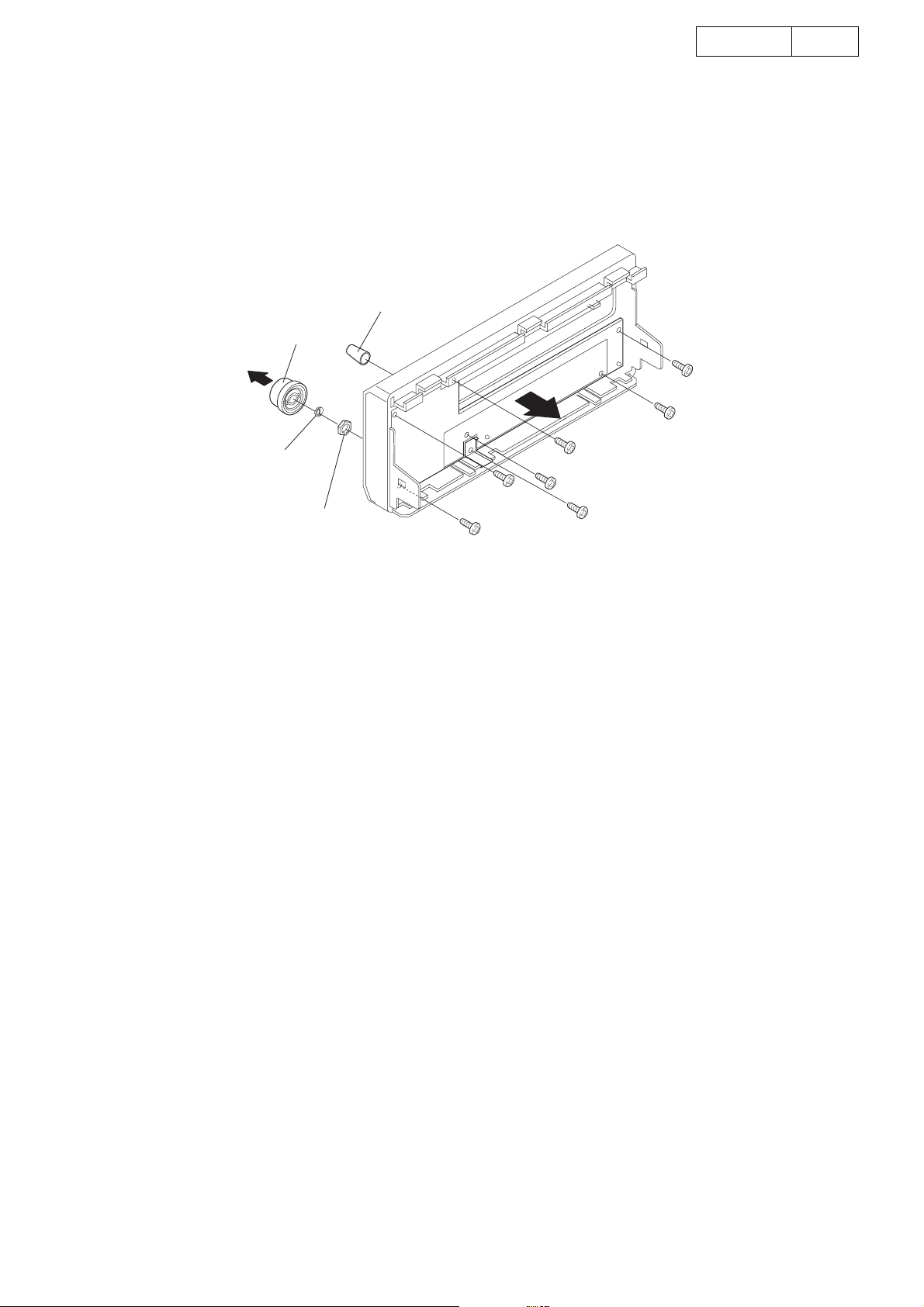

7. DISPLAY P.W.B.

(1)Pull out the VR knob and TUNING knob.

(2)Remove the spacer and the VR nut.

(3)Remove 7 screws.

VR KNOB

SPACER

VR NUT

7. ディスプレイ基板

(1)VRKNOBとTUNINGKNOBをはずします。

(2)SPACERとVRNUTをはずします。

(3)ねじ7本をはずします。

TUNNING KNOB

6

Page 7

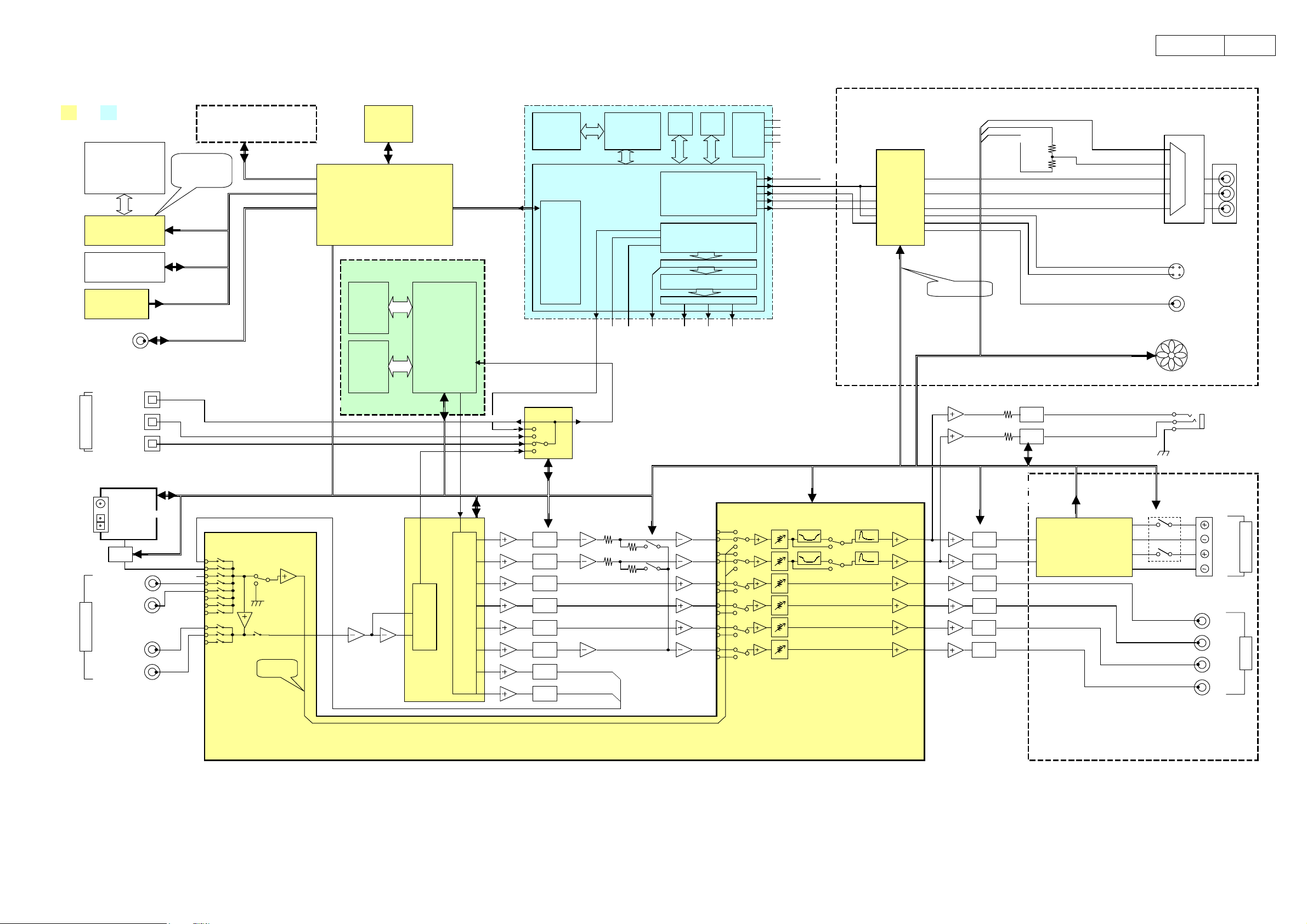

g

RGB_H

p

(

)

50/60

BACK END DSP

YUV[0-7]

C

g

Pr/C

CS

AUDIO DECODER

M66005AFP

RESET

D.D/DTS/PCM/AAC

(

))

VR-JOG

KEY

KEY-0/1

D

V.MUTE 1/2YY/C

ROTARY ENCODER

byMONITOR OUT

16MB

DelayC

CLK

SPDIF OUT

I/O1䌾I/O7

DIR

OPT IN 1

RXOUT

LC89057

DI/DO/CE/CLK

STEREO

DI/DO/CE/CLK/RST

SYR

AUDIO/EMPHA/INT

DATA

VR MUTE

FL/FR

CLK

C

FM ANT

SL/SR

RELAY FR

[+6dB]

[0dB]

FL

PASS

POWER AMP

TU.MUTE

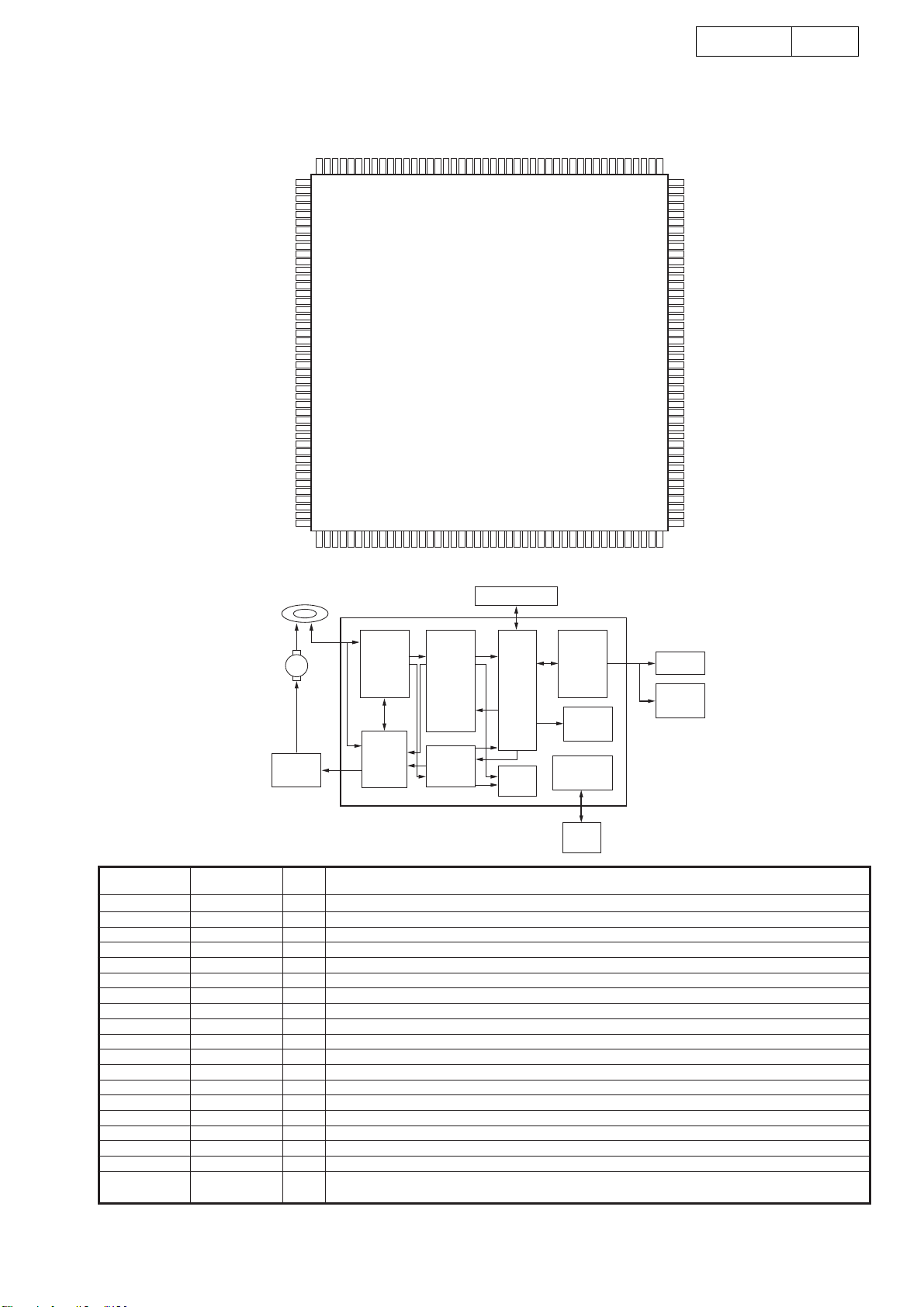

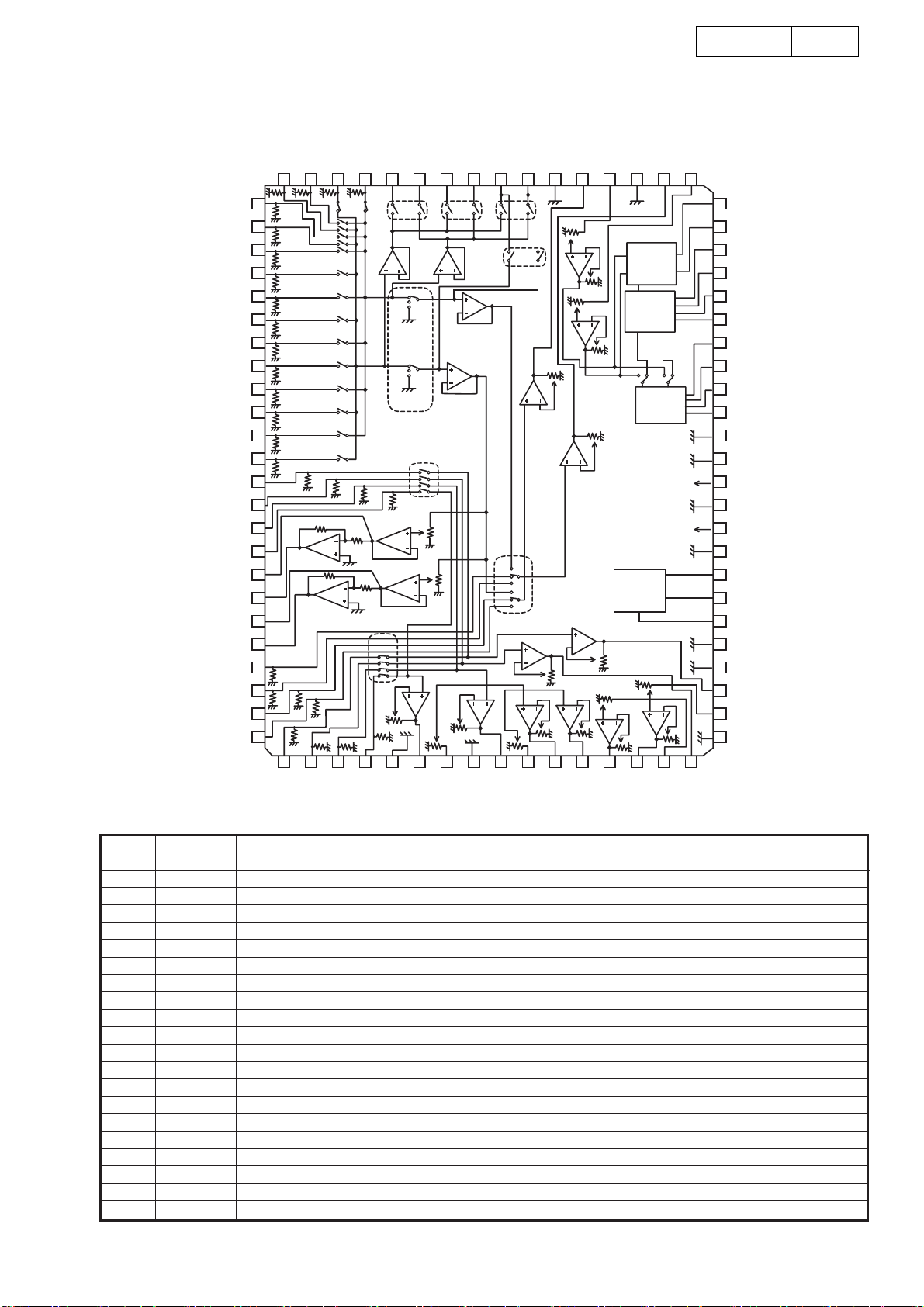

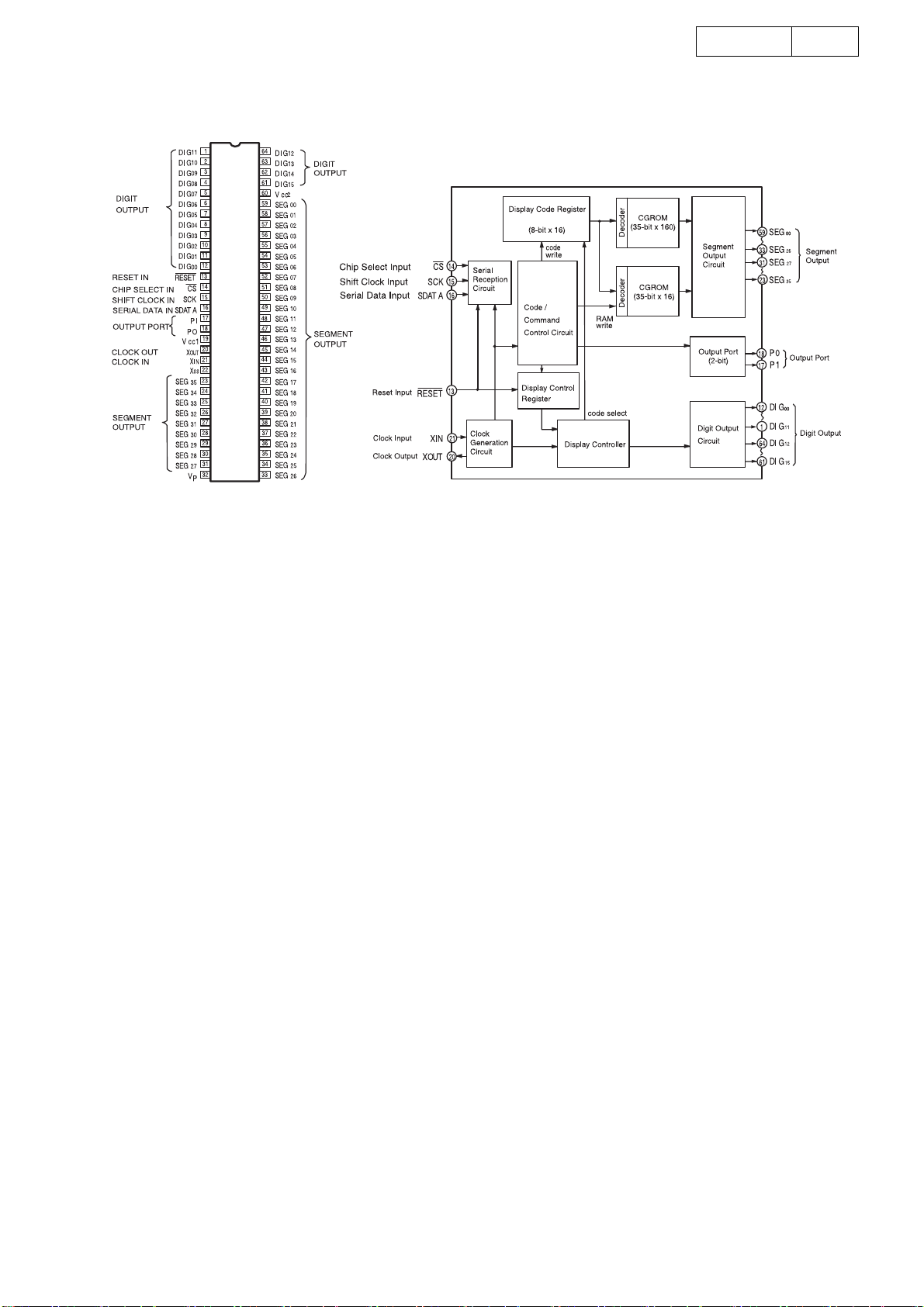

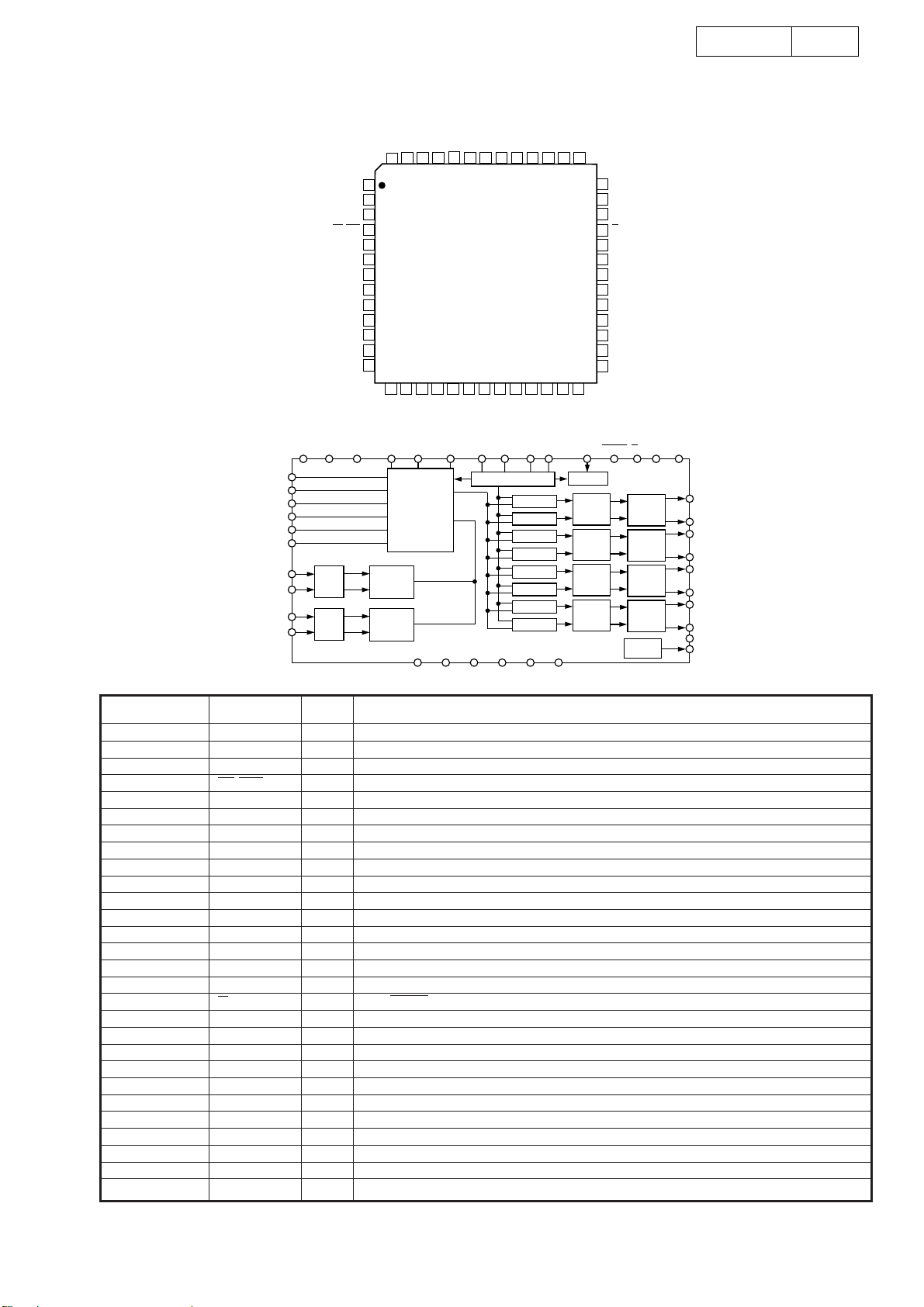

BLOCK DIAGRAMS

ADV-M71

7

:IC :DVD Engine Block

FL TUBE P ON/OFF

HNV-15SS04T SUB ON/OFF

13digit Dot Matrix SYSTEM uCOM ES6028 PY/Y

DISC information is

received from DVD

and it displays it in the

FL tube.

SWITCHING POWER SUPPLY EEPROM PROG/INTE

16k

DVD ON/OFF DI/DO/CS/CK

M30626 FHPGP

CLK

FL DRIVER DA/CK/CE/RST

SDATA I/O

A/B TBCK

LED LED-G DENON BASS Management

REMOCON REMOTE

GP1UE271XK AUDIO DSP MONITOR OUT

DENON BUS

x2

Communicate with DENON-BUS : MD/DECK/CD-R 64MB

OPT OUT RESET/ACK/REQUEST/BUSY NJM4556AD

[GP1Z352TZ] WRIGHT/OSC/IOPOWER/POM_RST

[GP1F352RZ] SPDIF SDATA

OPT IN 2 DIN 0 RBCK

DIGITAL IN/OUTAUDIO IN/OUT

[GP1F352RZ] PCM MCLK H/P MUTE

LED-R

ROM

RXD ADSST-MEL100 SPDIF RSD TSD3 TSD 2 TSD 1 TSD 0

TXD

MELODY 100

SD-RAM FAN ON/OFF COOLING FAN

PCM/AAC/D.D/DTS bitstream SPDIF RWS

DVD ENGINE UNIT RL-871 1U-3528 AMP/POWER UNIT

DVD MECHA ROM RAM

PU/Traverse FRONT END

Loadin

User I/F

Developed

( MCLK)

TWS

VIDEO DAC 4ch

with Pro

ressive scan

PLII/MP3/(WMA)/2chVirtual

PPCM(DVD-Audio

ownMix

Config-1(ON/OFF each CH)

for VDAC ex

UD-M30DVx : no use

Pb/Cb

and VIDEO DRIVER

r

with Filter

PY IN

Pb IN

Pr IN

YIN

CIN

BH7862

MIXOUT

C OUT

PY/Y

Pb/Cb

Pr/Cr

Y

C

V

Mute PY/Pb/Pr or Y/C/V

constantly

PCM/D.D/DTS bitstream H/P AMP

1U-3527 MAIN UNIT

VCNT1/YC_H

VCNT2/WIDE

MUTE

MUTE

LINE_2

LINE_3

J:D-TERMINAL VIDEO OUT

C

omposite

H/P SW

E3:COMPONENT VIDEO OUT

H/P

TUNED [I2S x 3] ERR/CS FLAG/96DET

FM/AM SDATA(AD) DO/CE/CLK/RST ERR MUTE SUB SUM

AM ANT NJM2068 BA15218 BA15218 DSP/EXT/DIRECT BASS/TREBLE SDB

TUNER PACK LRCK/BCK for SP Config-2 SWITCHING

VR

㪤㪬㪫㪜

MUTING

LINE-1 IN C

MUTE

LINE-2 IN SL

LINE-1 OUT LFE

LINE-2 OUT AD1837 DMIXL [0dB] 4.2Vrms

Route of

DIRECT mode

BA15218

A/D CONVERTER

8ch CODEC

㪏㪺㪿㩷㪛㪆㪘㩷㪚㪦㪥㪭㪜㪩㪫㪜㪩

FR

㪤㪬㪫㪜

㪤㪬㪫㪜

㪤㪬㪫㪜

SR

㪤㪬㪫㪜

㪤㪬㪫㪜

㪤㪬㪫㪜

DMIXR FUNCTION/VR/TONE/SDB IC

for RECOUT

㪤㪬㪫㪜

INPUT GAIN AMP

0/+6dB

BD3811K1

OUTPUT GAIN

0䌾+18dB

2dBstep BA15218

Max output

PRE AMP

MUTE

MUTE

MUTE

MUTE

MUTE

MUTE

SW

[STK-402-050]

1U-3528 AMP/POWER UNIT

PROTECT

THERMO

FL

FR

SW

C

SL

SR

SPEAKER OUT

PRE OUT

7

Page 8

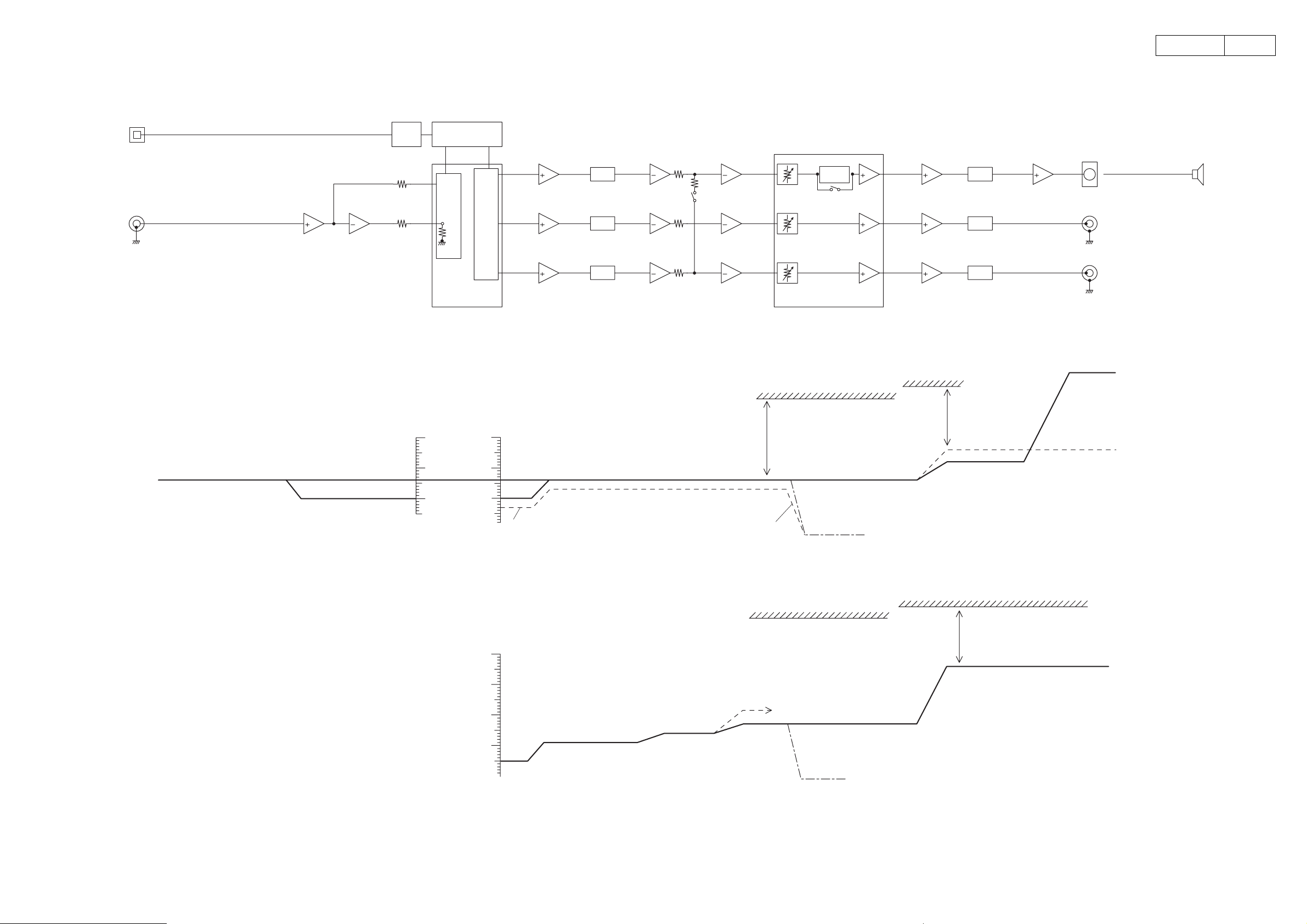

LEVEL DIAGRAMS

DIGITAL

OPT IN

-20dBFs

DIR

DSP

ADV-M71

8

POWER AMPPRE AMP

ANALOG

LINE IN

200mVrms

ANALOG

DIGITAL

L,R

L/R ch

FL/FR ch

SL/SR/C ch

ANALOG ANALOG DIRECT

-6dB

To A/D

470

470

2ch

A/D

AD1837

8ch CODEC

0dBFs

=1Vrms

-10dBFs

-20dBFs

-23dB

8ch

D/A

FL/FR

SL/SR/C

SW

ANALOG DIRECT

Prologic

+6dB

MUTE

MUTE

MUTE

For

Config2

TONE

SDB

BD3811

ELEC. VR

ELEC. VR Head Room (4.2Vrms)

26.4dB

-18dB

-15dB

Prologic

at VR "00"

FL/FR

SL/SR/C

SW

+6dB

+10dB

+19dB

PRE AMP Head Room (7.0Vrms)

21.0dB

SL/SR/C

+10dB

+6dB

FL/FR

MUTE

MUTE

MUTE

30dB

30dB

SL/SR/C

SW

SP OUTFL/FR

VR MAX: 12.6Vrms

VR MAX : 632mVrms

VR " 00 " : 80mVrms

FL/FR

(20W, 8Ω)

SW ch

Input Sens : 200mVrms

SP Output Power : 20W (THD 0.08%,8Ω)

Total GAIN : 36dB

0dBFs

=1Vrms

-10dBFs

-20dBFs

-30dBFs

-35dBFs

+6dB

+2.85dB

PRE AMP Head Room (7.0Vrms)

ELEC. VR Head Room (4.2Vrms)

21.0dB

VR MAX : 632mVrms

VR " 00 " : 80mVrms

Config-1

+7.5dB

+3.31dB

Config-2

To Front ch

-18dB

atVR"00"

8

Page 9

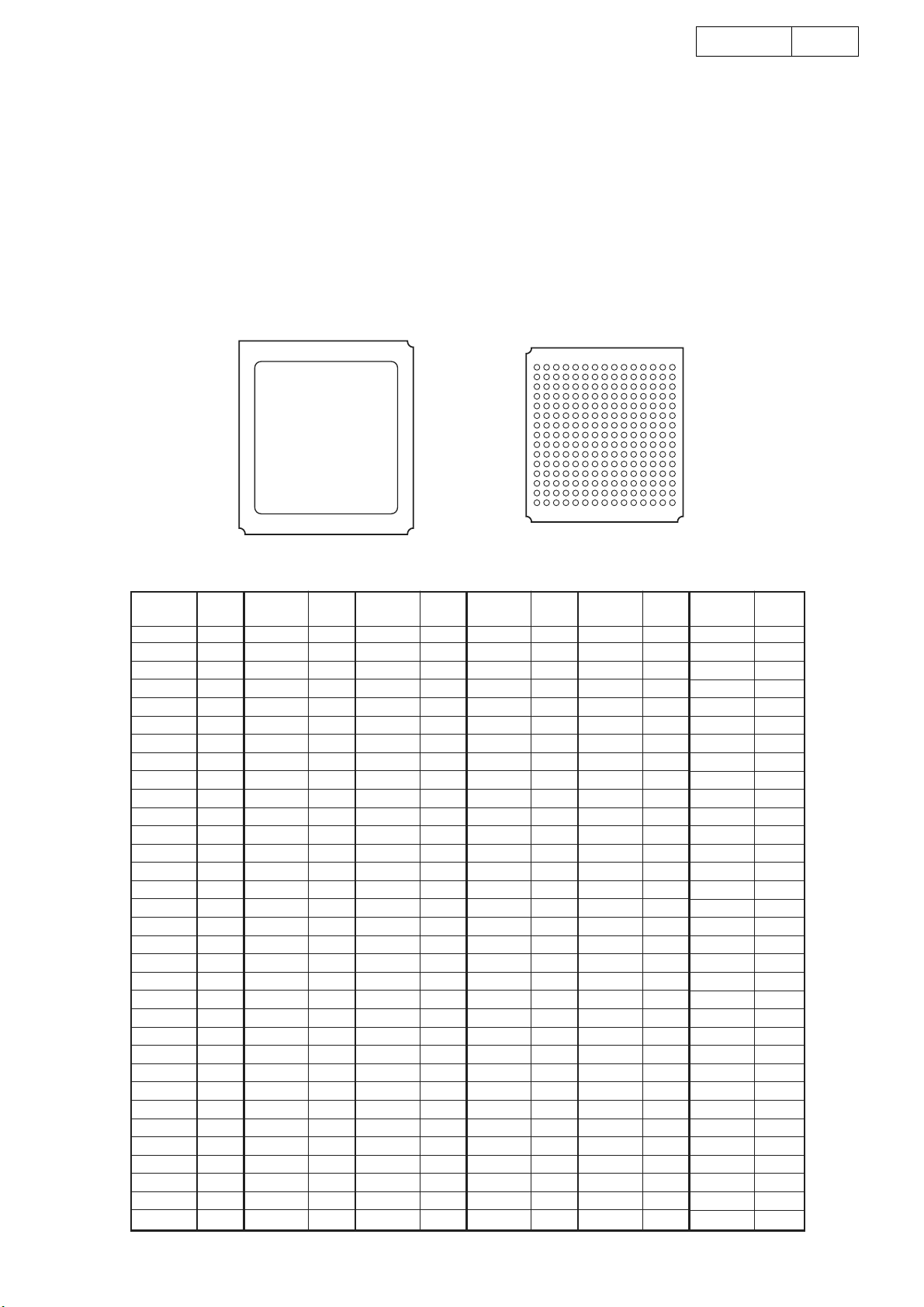

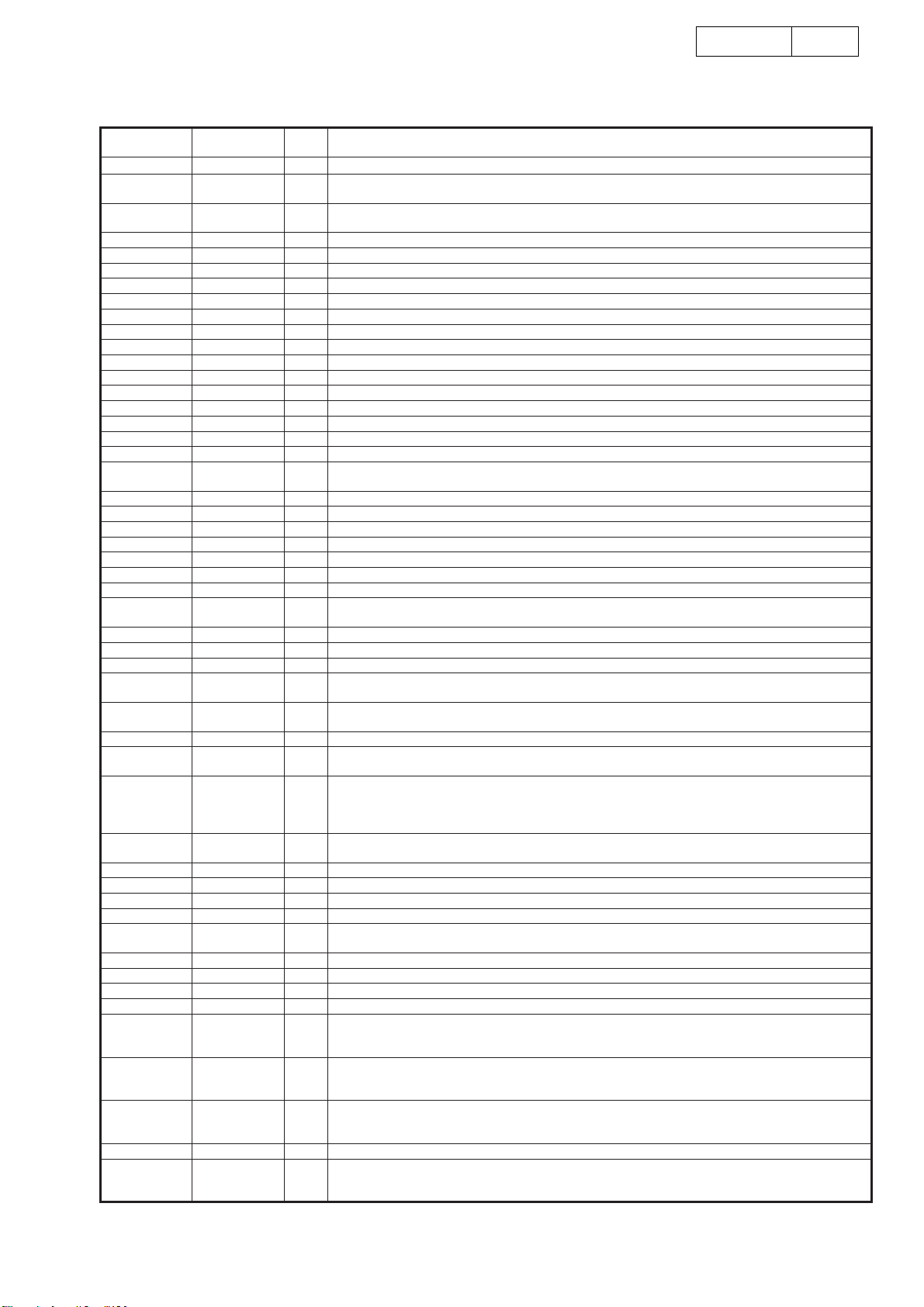

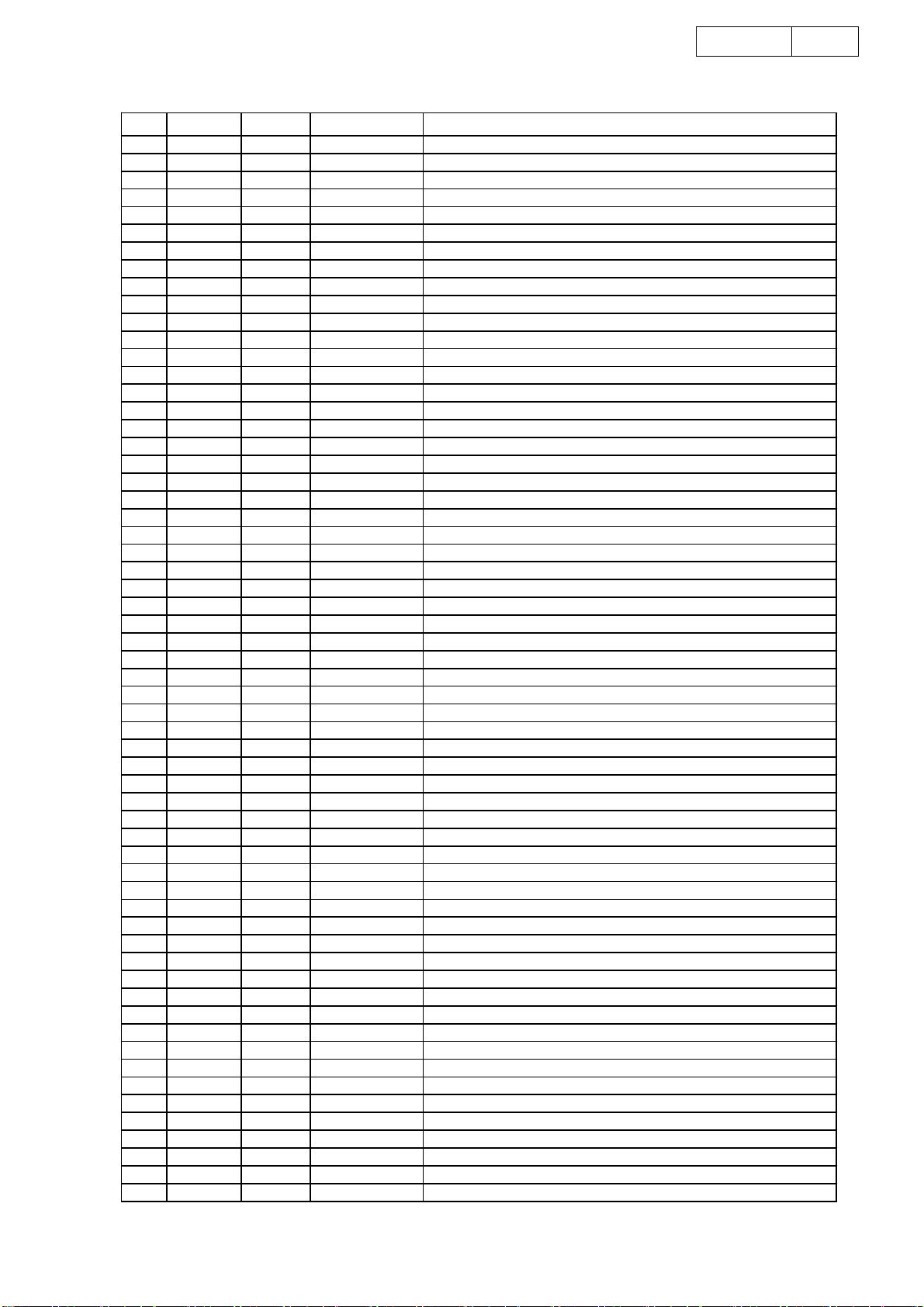

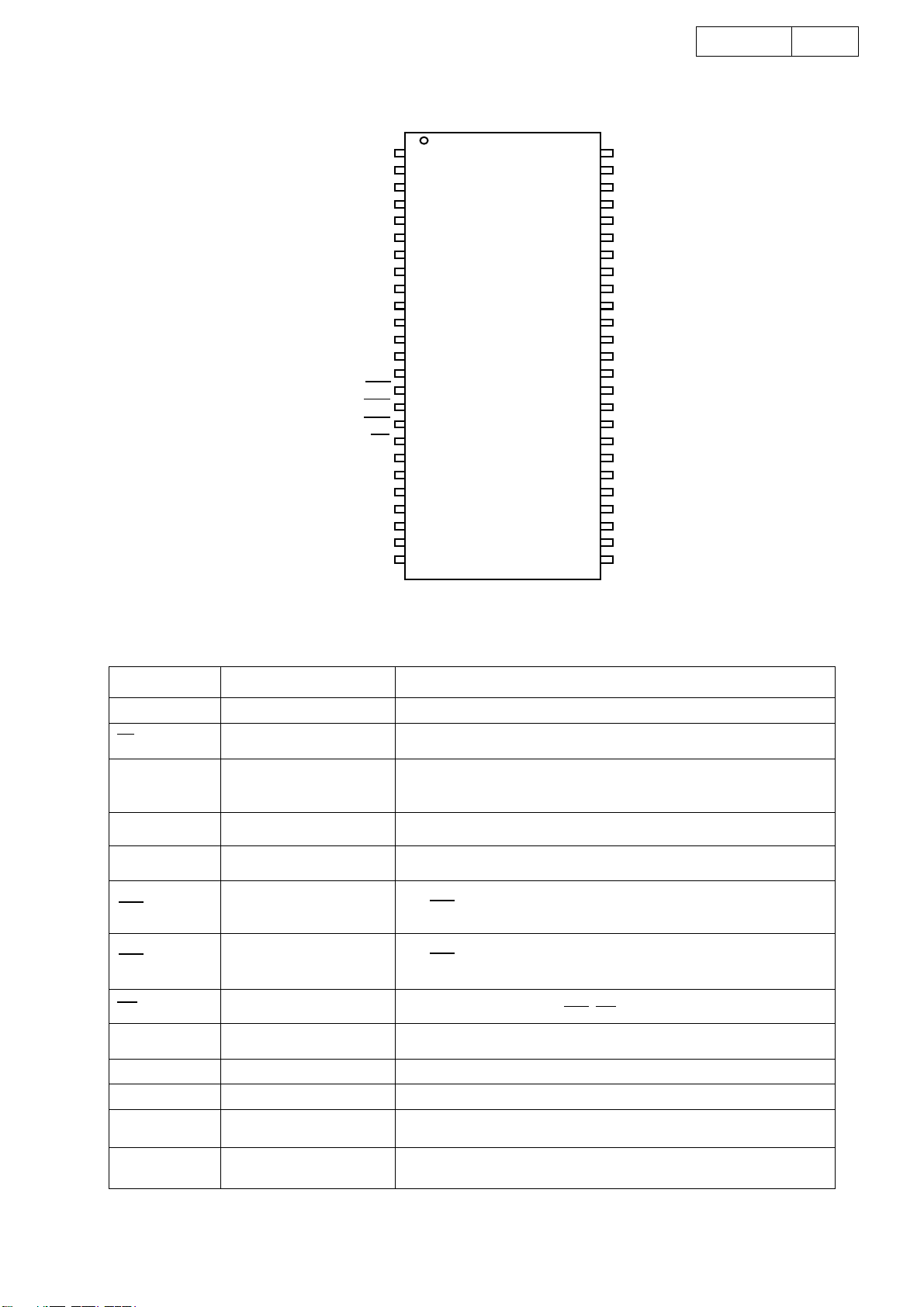

SEMICONDUCTORS

Only major IC's are shown, general IC's etc. are omitted to list.

主な半導体を記載しています。汎用の半導体等は記載を省略しています。

●IC's

Note: Abbreviation ahead of IC No. indicates the name of P.W.B., etc.

注 ) : IC No. の前の記号は、基板の名称を表します。

DS : DSP P.W.B. AP: AMP/POWER P.W.B.

MA: Main P.W.B. ME : MECHA P.W.B.

ADSST-MEL100(DS:IC801)

Note : When this IC is defecitive, replace P.W.B. Unit Ass'y

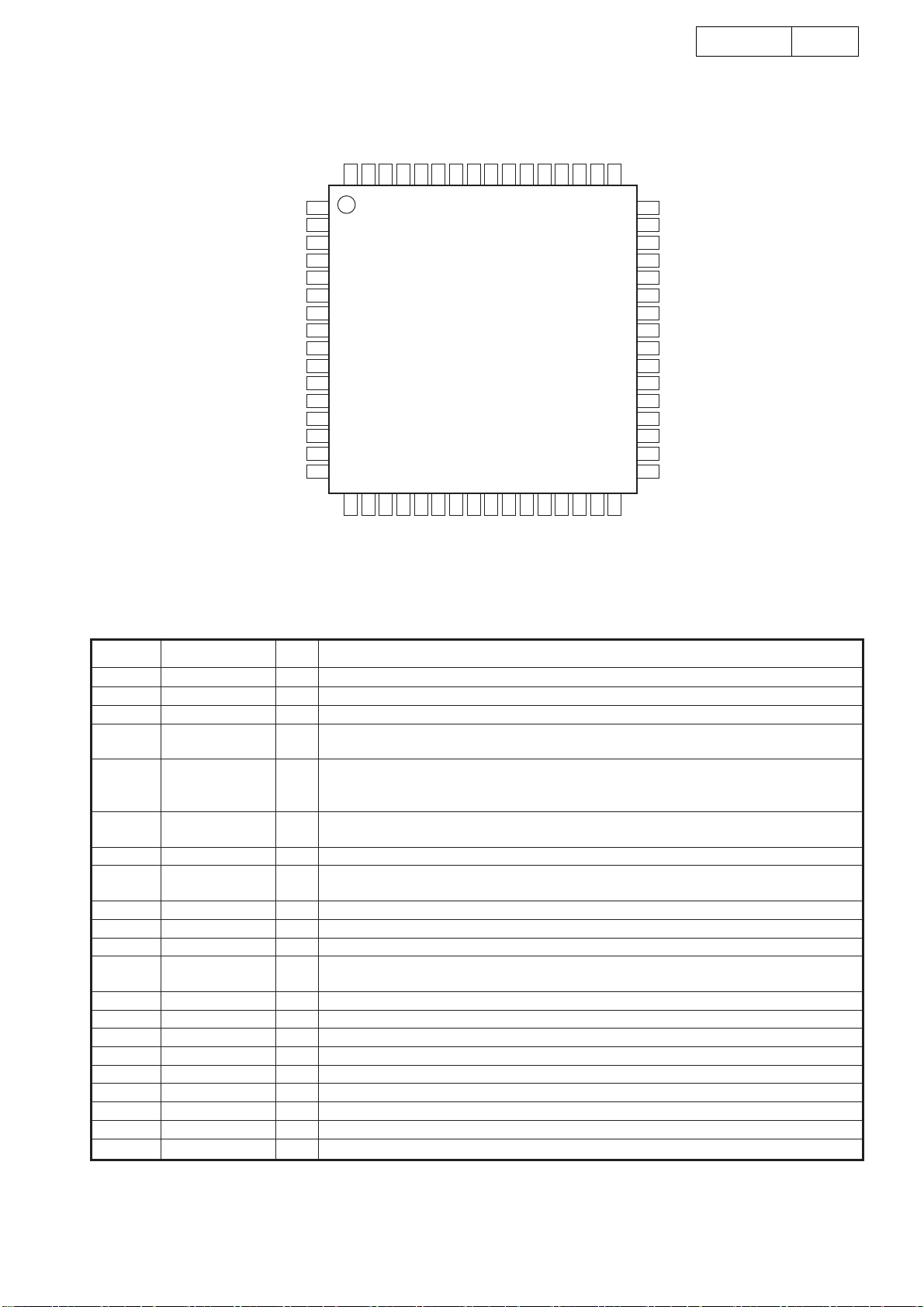

TOP VIEW

ADV-M71

123456789101112131415

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

9

ADSST-MEL100 Terminal Function

Pin Name

NC A01

BMSTR A02

BMS_B A03

SPIDS A04

EBOOT A05

LBOOT A06

SCLK2 A07

SD3B A08

L0DAT[4] A09

L0ACK A10

L0DAT[2] A11

L1DAT[6] A12

L1CLK A13

L1DAT[2] A14

NC A15

FLAG10 E01

RESET_B E02

FLAG8 E03

SD0A E04

VDDEXT E05

VDDINT E06

VDDEXT E07

VDDINT E08

VDDEXT E09

VDDINT E10

VDDEXT E11

L0DAT[0] E12

DATA[39] E13

DATA[43] E14

TRST_B B01

TD1 B02

RPBA B03

MOSI B04

Pin No.

Pin Name

SFS0 B05

SCLK1 B06

SD2B B07

SD3A B08

L0DAT[7] B09

L0CLK B10

L0DAT[1] B11

L1DAT[4] B12

L1ACK B13

L1DAT[0] B14

NC B15

FLAG5 F01

FLAG7 F02

FLAG9 F03

FLAG6 F04

VDDINT F05

GND F06

GND F07

GND F08

GND F09

GND F10

VDDINT F11

DATA[37] F12

DATA[40] F13

DATA[38] F14

TMS C01

EMU_B C02

GND C03

SPICLK C04

SD08 C05

SD1A C06

SD2A C07

SFS2 C08

Pin No.

Pin Name

SFS3 C09

L0DAT[6] C10

L1DAT[7] C11

L1DAT[3] C12

L1DAT[1] C13

DATA[45] C14

DATA[47] C15

FLAG1 G01

FLAG2 G02

FLAG4 G03

FLAG3 G04

VDDEXT G05

GND G06

GND G07

GND G08

GND G09

GND G10

VDDEXT G11

DATA[34] G12

DATA[35] G13

DATA[33] G14

DATA[41] E15

IRQ2_B J01

ID1 J02

ID2 J03

ID0 J04

VDDEXT J05

GND J06

GND J07

GND J08

GND J09

GND J10

VDDEXT J11

Pin No.

Pin Name

DATA[26] J12

DATA[24] J13

DATA[25] J14

DATA[27] J15

ADDR[14] N01

ADDR[15] N02

ADDR[10] N03

ADDR[5] N04

ADDR[1] N05

MS0_B N06

BR5_B N07

BR2_B N08

BRST N09

SDCKE N10

CS_B N11

CLK_CFG1 N12

CLK_CFG0 N13

AVDD N14

DMARI1_B N15

DATA[36] F15

TIMEXP K01

ADDR[22] K02

ADDR[20] K03

ADDR[23] K04

VDDINT K05

GND K06

GND K07

GND K08

GND K09

GND K10

VDDINT K11

DATA[22] K12

DATA[19] K13

Pin No.

BOTTOM VIEW

Pin Name

DATA[21] K14

DATA[23] K15

ADDR[13] P01

ADDR[9] P02

ADDR[8] P03

ADDR[4] P04

MS2_B P05

SBTS_B P06

BR4_B P07

BR1_B P08

SDCLK1 P09

SDCLK0 P10

REDY P11

CLKIN P12

DQM P13

AVSS P14

DMAR2_B P15

DATA[32] G15

ADDR[19] L01

ADDR[17] L02

ADDR[21] L03

ADDR[2] L04

VDDEXT L05

VDDINT L06

VDDEXT L07

VDDINT L08

VDDEXT L09

VDDINT L10

VDDEXT L11

CAS_B L12

DATA[20] L13

DATA[16] L14

DATA[18] L15

Pin No.

Pin Name

NC R01

ADDR[11] R02

ADDR[7] R03

ADDR[3] R04

MS3_B R05

PA_B R06

BR3_B R07

RDL_B R08

CLKOUT R09

HBR_B R10

HBG_B R11

CLKDBL R12

XTAL R13

SDWE_B R14

NC R15

DATA[31] H15

ADDR[16] M01

ADDR[12] M02

ADDR[18] M03

ADDR[6] M04

ADDR[0] M05

MS1_B M06

BR6_B M07

VDDEXT M08

WRL_B M09

SDA10 M10

RAS_B M11

ACK M12

DATA[17] M13

DMAG2_B M14

DMAG1_B M15

Pin No.

9

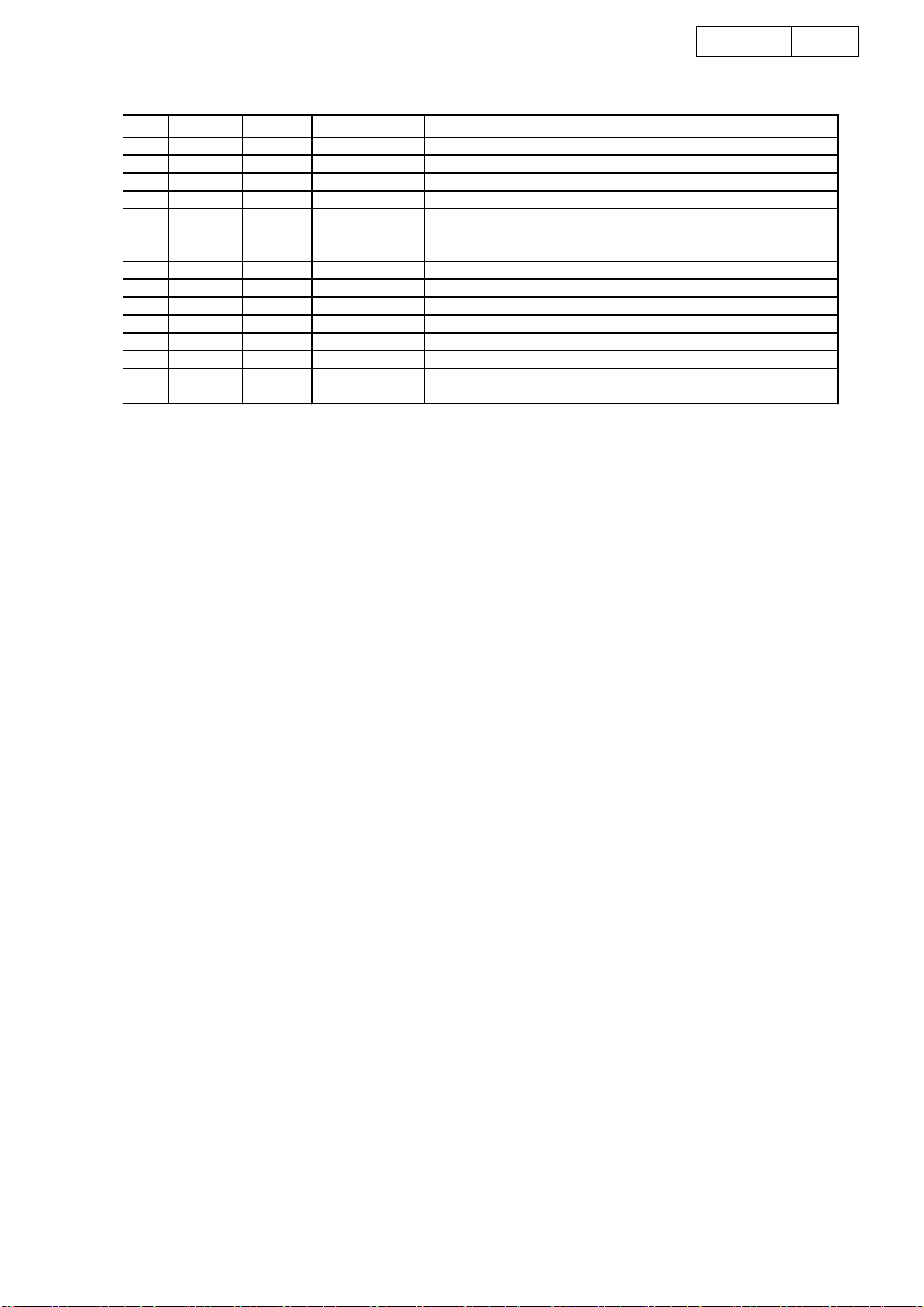

Page 10

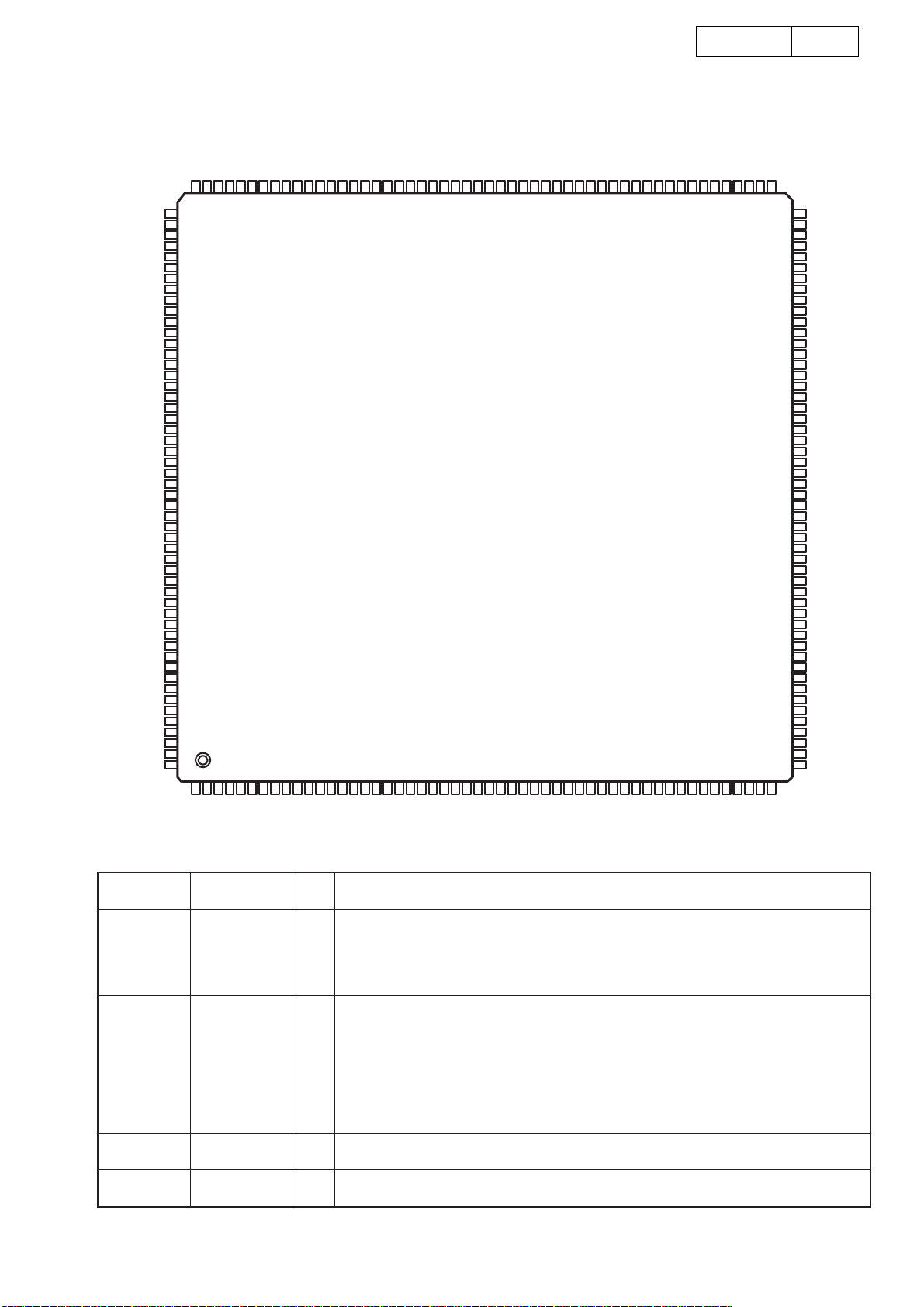

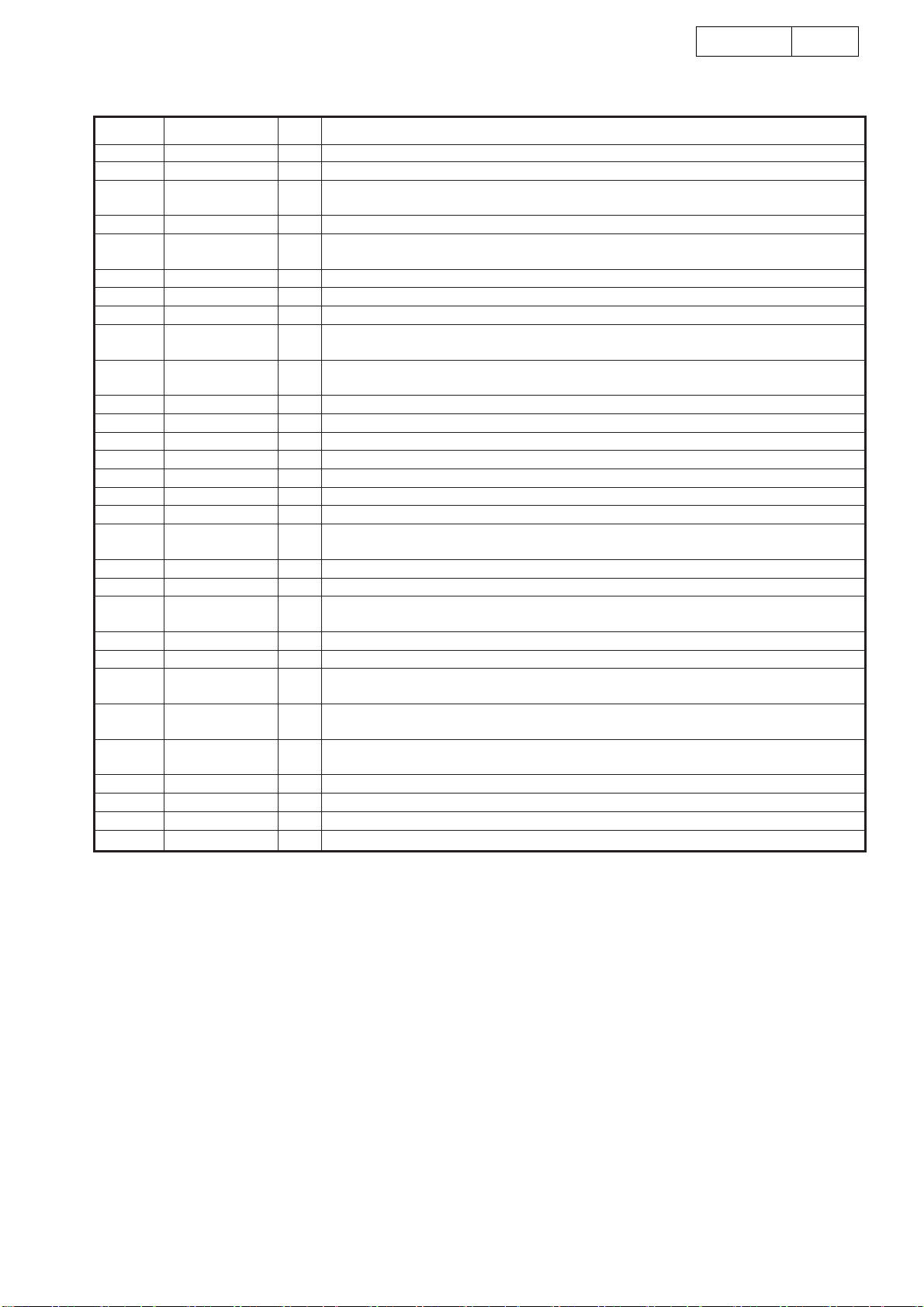

ES6028 (ME: U9)

VSS

HA1

156

VEE

HA2

VEE

AUX[0]

AUX[1]

AUX[2]

VSS

VEE

AUX[3]

AUX[4]

AUX[5]

AUX[6]

AUX[7]

LOE#

VSS

VCC

LCS0#

LCS1#

LCS2#

LCS3#

VSS

VEE

VSS

LD10

LD11

VSS

VEE

LD12

LD13

LD14

LD15

LWRLL#

LWRHL#

VSS

VEE

CAMIN0

CAMIN1

VSS

LD0

LD1

LD2

LD3

LD4

LD5

LD6

LD7

LD8

LD9

LA0

LA1

LA2

LA3

155

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

123456789101112131415161718192021222324252627282930313233343536373839404142434445464748495051

HA0

154

HCS3FX#

HCS1FX#

153

152

VEE

VSS

DSCK

DQM

DCS0#

VEE

VSS

DCS1#

DB15

DB14

DB13

DB12

VEE

VSS

DB11

DB10

DB9

DB8

DB7

DB6

VSS

VCC

DB5

DB4

DB3

DB2

DB1

DB0

VSS

VEE

DMBS1

DMBS0

DRAS#

DWE#

DSCK_EN

DCAS#

VEE

VSS

DMA11

DMA10

DMA9

DMA8

DMA7

DMA6

VSS

VEE

DMA5

DMA4

DMA3

DMA2

DMA1

DMA0

10

ADV-M71

HIOCS16#

HRD#

HWR#

VEE

VSS

HIORDY

HRST#

HIRQ

HRDQ#

HWRQ#

HD15

HD14

VCC

VSS

HD13

HD12

HD11

HD10

HD9

HD8

HD7

VEE

VSS

HD6

HD5

HD4

HD3

HD2

HD1

HD0

VCC

VSS

HSYNC#

VSYNC#

PCLKQSCN

PCLK2XSCN

YUV7

YUV6

YUV5

VSS

ADVEE

YUV4

YUV3

YUV2

YUV1

YUV0

DCLK

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

LA4

LA5

LA6

LA7

LA8

VEE

LA9

VSS

VCC

VSS

LA10

LA11

LA12

LA13

VEE

LA14

LA15

LA16

LA17

ES6038 Terminal Function

1, 18, 27, 59,

68, 75, 92, 99,

104, 130, 148, VEE I I/O power supply.

157, 159, 164,

183, 193, 201

8, 17, 26, 34,

43, 52, 60, 67,

76, 84, 91, 98,

103, 112, 120, VSS I Ground.

129, 138, 147,

156, 163, 171,

177, 184, 192,

200, 208

23:19, 16:10,

7:2, 207:204

9, 35, 44, 83,

121, 139, 172

LA[21:0] O Device address output.

VCC I Core power supply.

TDMFS

TDMTSC#

VSS

VCC

TSD2

TWS/SEL_PLL2

TSD0/SEL_PLL0

TSD1/SEL_PLL1

VSS

LA18

LA19

LA20

VEE

LA21

TDMDX

TDMDR

RESET#

TDMCLK

NC

TSD3

VSS

TBCK

MCLK

SPDIF/PLL3

VCC

RSD

RWS

RBCK

NC

XIN

VSS

AVEE

XOUT

FunctionI/OPin No. Pin Name

10

Page 11

ADV-M71

11

Pin No. Pin Name

24 RESET# I Reset input, active low.

25 TDMDX O TDM transmit data.

28 TDMDR I TDM receive data.

29 TDMCLK I TDM clock input.

30 TDMFS I TDM frame sync.

31 TDMTSC# O TDM output enable.

TWS O Audio transmit frame sync.

SEL_PLL2 I System and DSCK output clock frequency selection is made at the rising edge of RESET#.

The matrix below lists the available clock frequencies and their respective PLL bit settings.

SEL_PLL2 SEL_PLL1 SEL_PLL0 Clock Type

0 0 0 VCO off.

0 0 1 DCLK

32 0 1 0 Bypass mode

0 1 1 DCLK x 2

1 0 0 DCLK x 4.5

1 0 1 DCLK x 3

1 1 0 DCLK x 3.5z

1 1 1 DCLK x 4

33

36

37 TSD[2] O Audio transmit serial data output 2.

38 TSD[3] O Audio transmit serial data output 3.

39 MCLK I/O Audio master clock for audio DAC.

40 TBCK O Audio transmit bit clock.

41 SEL_PLL3 Clock Source

42,48 NC No connect pins. Leave open.

45 RSD I Audio receive serial data.

46 RWS I Audio receive frame sync.

47 RBCK I Audio receive bit clock.

49 XIN I Crystal input.

50 XOUT O Crystal output.

51 AVEE I Analog power for PLL.

66:61, 58:53 DMA[11:0] O DRAM address bus [11:0]

69 DCAS# O DRAM column address strobe,

70 DSCK_EN O DRAM clock enable.

71 DWE# O DRAM write enable.

72 DRAS# O DRAM row address strobe.

73 DMBS0 O SDRAM bank select 0.

74 DMBS1 O SDRAM bank select 1.

96:93, 90:85,

82:77

97, 100 DCS[1:0]# O SDRAM chip select [1:0]

101 DQM O Data input/output mask.

102 DSCK O Output clock to SDRAM.

105 DCLK I 27 MHz clock input to PLL.

106 UDAC O Video UDAC output.

107 VREF I Internal voltage to video DAC.

108 CDAC O Video CDAC output.

109 COMP I Compensation input.

110 RSET I DAC current adjustment resistor input.

111 ADVEE I Analog power for video DAC.

113 YDAC O Video YDAC output.

TSD0 O Audio transmit serial data port 0.

SEL_PLL0 I Refer to the description and matrix for SEL_PLL2 pin 32.

TSD1 O Audio transmit serial data port 1.

SEL_PLL1 I Refer to the description and matrix for SEL_PLL2 pin 32.

SPDIF O S/PDIF output.

SEL_PLL3 I Clock source select.

0 Crystal oscillator

1 DCLK input

DB[15:0] I/O DRAM data bus [15:0]

FunctionI/O

11

Page 12

ADV-M71

12

Pin No. Pin Name

114 VDAC O Video VDAC output.

115 YUV7 O YUV7 pixel output data.

116 PCLK2XSCN I/O 27 MHz video output pixel clock.

117 PCLKQSCN O 13.5 MHz video output pixel clock.

118 VSYNC# I/O Ver tical sync, active low.

119 HSYNC# I/O Horizontal sync, active low.

127:122 HD[5:0] I/O Host data I/O [5:0].

128 HD[6] I/O Host data I/O [6].

131 HD[7] I/O Host data I/O [7].

132 HD[8] I/O Host data bus 8.

133 HD[9] I/O Host data bus line 9.

134 HD[10] I/O Host data bus line 10.

135 HD[11] I/O Host data bus line 11.

136 HD[12] I/O Host data bus line 12.

137 HD[13] I/O Host data bus line 13.

140 HD[14] I/O Host data bus line 14.

141 HD[15] I/O Host data bus line 15.

142 HWRQ# O Host write request.

143 HRRQ# O Host read request.

144 HIRQ I/O Host interrupt.

145 HRST# O Host reset.

146 HIORDY I Host I/O ready.

149 HWR# I/O Host write.

150 HRD# O Host read.

151 HIOCS16# I Device16-bit data transfer.

152 HCS1FX# O Host select 1.

153 HCS3FX# O Host select 3.

158, 155:154 HA[2:0] I/O Host address bus.

160 AUX[0] O I2C DATA.

162 AUX[2] I/O Auxiliary ports 2.

165 AUX[3] I/O Auxiliary ports 3.

169:166 AUX[7:3] I/O Auxiliary ports 7:3.

170 LOE# O Device output enable.

176:173 LCS[3:0]# O Chip select [3:0].

197:194,

191:185, LD[15:0] I/O EPROM device data bus.

182:178

198 LWRLL# O Device low-byte write enable.

199 LWRHL# O Device high-byte write enable.

202 CAMIN0 I Camera YUV 0.

203 CAMIN1 I Camera YUV 1.

161 AUX[1]OI2C CLK.

FunctionI/O

12

Page 13

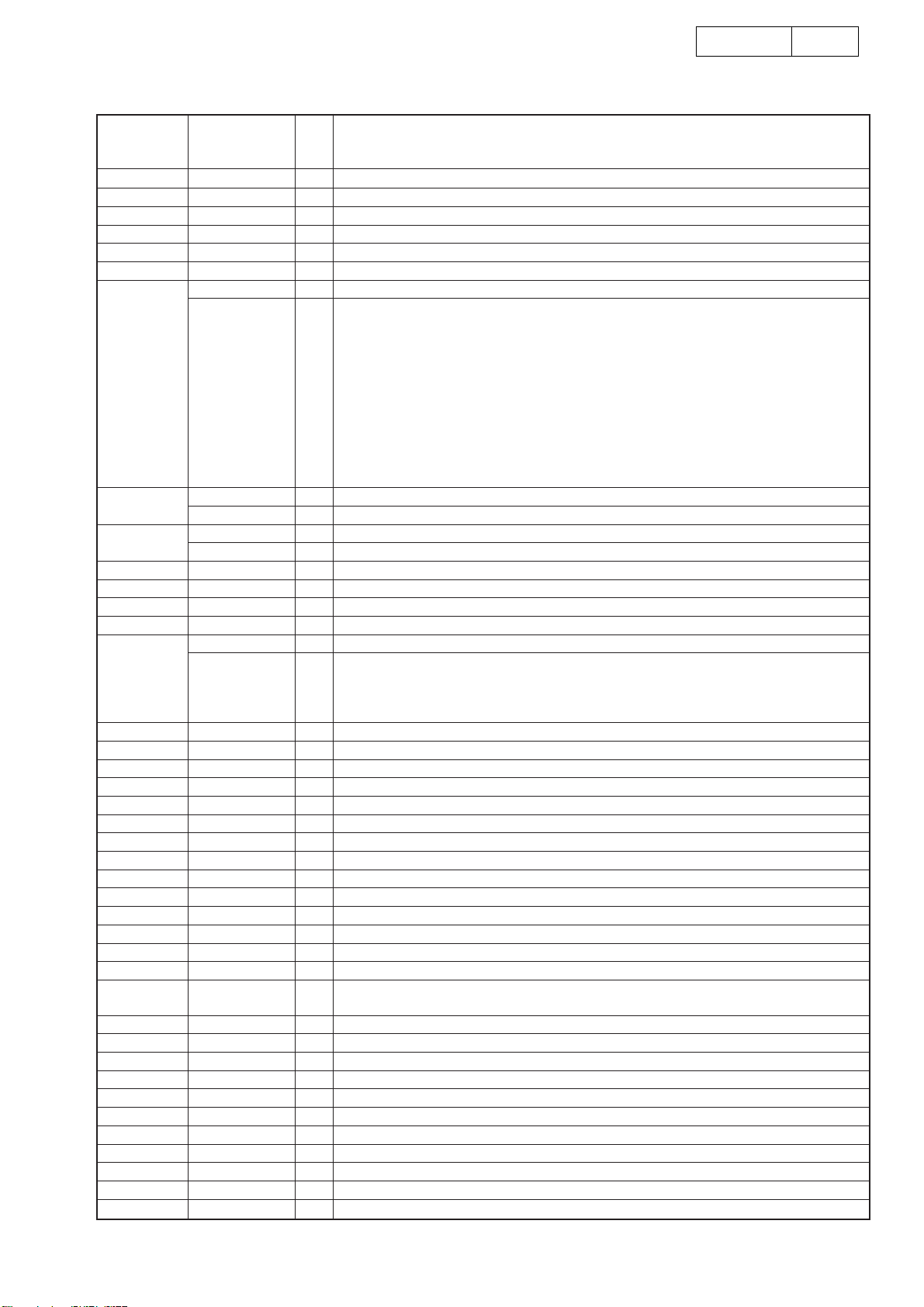

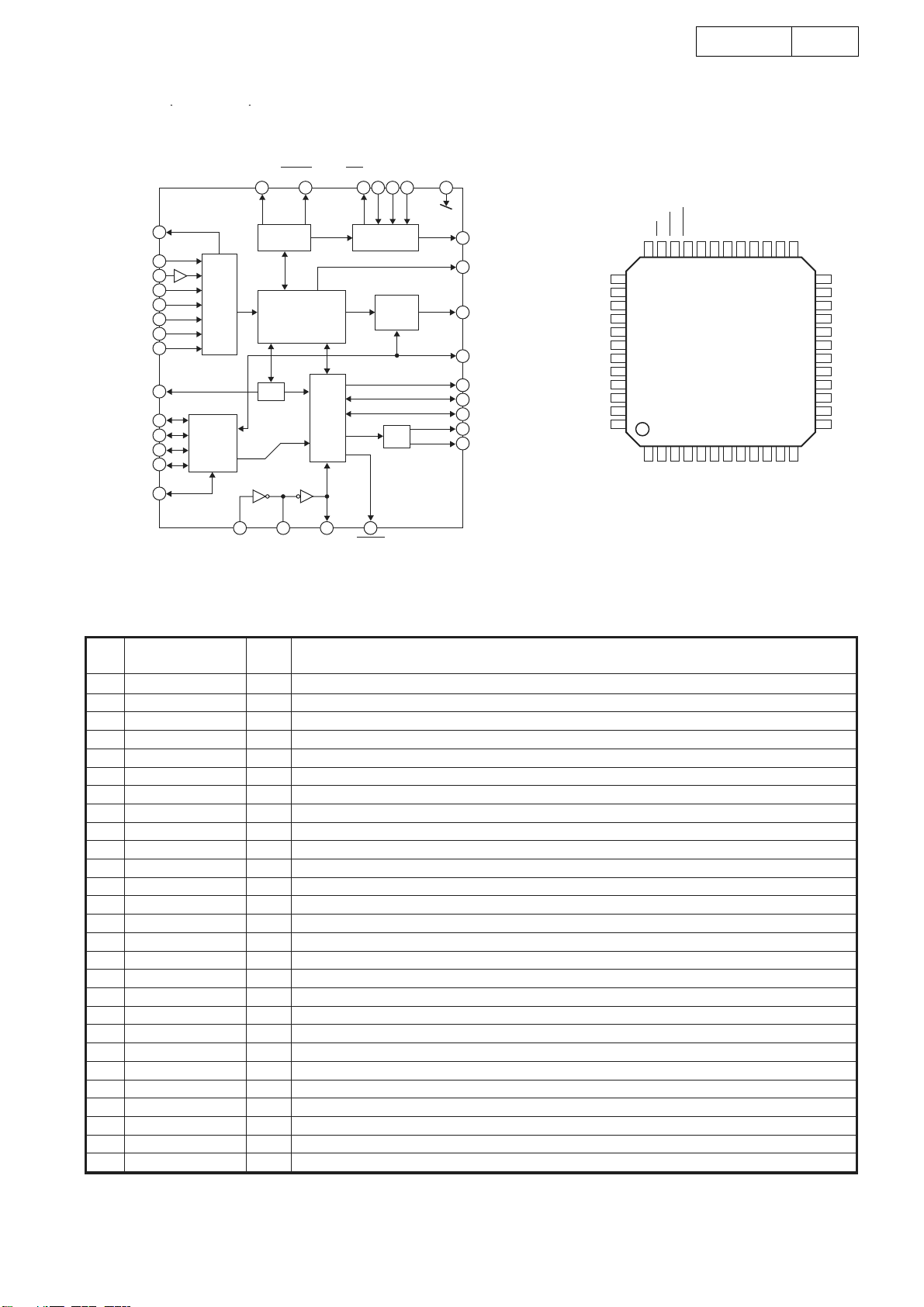

M5705 (ME: U1)

AVSS-DS

XSRFIN

XSIPIN

AVDD5-DS

XSDSSLV

XSRSLINT

XSAWRC

XSRFGC

XSEFGC

XSFOCUS

XSTRACK

XSSLEG

AVDD5-DA

XSMOTOR

AVSS-DA

XSRFRPLP

XSTELP

XSVREF2

XSRFRP

XSTEXI

AVSS-AD

XSTEI

XSFEI

XSAEI

AVDD5-AD

XSSBAD

GND

XSDFCT

XSCSJ

XSCLK

XSDATA

XSLDC

XSFGIN

XSSPDON

XSFLAG(3)

XSFLAG(2)

XSFLAG(1)

XSFLAG(0)

XMP1_7

XMP1_6

GND

XMP1_4

XSAWRCVCO

XSVREFO

XSPDOFTR2

XSVR_PLL

XSFTROPI

XSFDO

AVSS_PL

XSPLLFTR2

AVDD5_PL

XSFDIREF

XSPDIREF

GND

XTSLRF

XTPLCK

VDD

XRA(3)

XRA(2)

XRA(1)

XRA(0)

XRA(4)

XRA(5)

XRA(6)

GND

XRA(7)

XRA(10)

XRA(11)

VDD

XRA(8)

XRA(9)

XROEJ

VDD

176

175

174

173

172

171

170

169

168

167

166

165

164

163

162

161

160

159

158

157

156

155

154

153

152

151

150

149

148

147

1

2

3

4

5

6

VDD

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

NC

43

44

45464748495051525354555657585960616263646566676869707172737475767778798081828384858687

VDD

VDD

GND

XOSC1

XOSC2

XMALE

XMD(0)

XMD(1)

XMD(2)

XMD(3)

XMD(4)

XMD(5)

XMD(6)

XMP1_3

XMFSCSJ

XMP1_2

XGPIO(2)

XMP1_1

XMRSTJ

XGPO(1)

XGPO(0)

XCRSTJ

XMPSENJ

XMP1_0

XMD(7)

146

XMCSJ

XMRDJ

XMWRJ

XMA(11)

XMA(10)

XMINT1J

4M DRAM

M5705

XRCASJ

XRRASJ

145

144

VDD

XMA(9)

XRSDCLK

XRWEJ

143

142

XMA(8)

XMA(7)

XRD(7)

141

XMA(6)

XRD(8)

140

XMA(5)

XRD(6)

139

XMA(4)

GND

138

XMA(3)

XRD(9)

137

XMA(2)

XRD(5)

136

XMA(1)

XRD(10)

XRD(4)

135

134

XMA(0)

XMA(12)

XRD(11)

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

88

GND

99

98

97

96

95

94

93

92

91

90

89

XRD(3)

XRD(12)

GND

XRD(2)

XRD(13)

XRD(1)

XRD(14)

XRD(0)

XRD(15)

XHD(7)

XHD(8)

XHD(6)

XHD(9)

XHD(5)

XHD(10)

XHD(4)

XHD(11)

VDD

XHD(3)

XHD(12)

XHD(2)

XHD(13)

GND

XHD(1)

XHD(14)

XHD(0)

XHD(15)

XHDRQ

XHIOWJ

XHIORJ

XHIORDY

XHDACKJ

XHINT

XHCS16J

XHA(1)

XHPDIAGJ

XHA(0)

XHA(2)

XHCS1J

XHCS3J

XHDASPJ

XMA(15)

XMA(14)

XMA(13)

ADV-M71

13

ATAPI

M

Motor

Driver

Data

Separator

Digital

Servo

DVD-DSP

CD-DSP

RAM

Arbiter

Target

Search

&

MPEG

I/F

C3 ECC

EDC

MCU

ROM

M5705 Terminal Function

Pin Name

Type

2 XSRFIN I/A Analog RF signal input after passing through the equalizer

3 XSIPIN I/A Inverting input pin of data slicer

5 XSDSSLV O/A Slice level output pin

6 XSRSLINT I/A Reference current setting pin for analog data slicer

8 XSAWRC O/A Output for enlarge VCO range. Analog output from DAC buffer

9 XSRFGC O/A RF gain control output

10 XSEFGC O/A E,F gain control output

11 XSFOCUS O/A Output voltage level for focusing buffer IC

12 XSTRACK O/A Output voltage level for tracking buffer IC

13 XSSLEG O/A Output voltage level for sledge buffer IC

15 XSMOTOR O/A Output voltage level for spindle motor buffer IC

17 XSRFRPLP I/A High bandwidth low pass filter input for RFRP

18 XSTELP I/A High bandwidth low pass filter input for TE

19 XSVREF2 I/A 2.1V reference voltage input

20 XSRFRP I/A RF ripple/envelope signal input

21 XSTEXI I/A Tracking zero crossing input signal

23 XSTEI I/A Tracking error input signal

24 XSFEI I/A Focus error input signal

25 XSCEI I/A

1. Center error input signal

2. Photo Interrupt input

DescriptionPin No.

PC

MPEG

DEC.

13

Page 14

ADV-M71

14

Pin Name

27 XSSBAD I/A Sub-beam addition signal input

166 XSPDIREF I/A

167 XSFDIREF I/A

169 XSPLLFTR2 I/A Data PLL loop filter pin#2

171 XSFDO O/A Output node of frequency detector charge pump circuit

172 XSFTROPI I/A Input node of loop filter OP circuit

173 XSVR_PLL I/A PLL reference voltage input

174 XSPDOFTR2 I/A Phase detector filter pin#1

175 XSVREFO O/A Reference voltage output

176 XSAWRCVCO I/A Auto Wide Range Control of VCO input pin. For enlarge VCO range in CAV mode

29 XSDFCT I Detect detection signal input

30 XSCSJ O Chip select signal for accessing control registers

31 XSCLK O Clock output for accessing control registers

32 XSDATA I/O Registers data input/output pin

33 XSLDC O Laser diode on/off control output for both CD/DVD

34 XSFGIN I Motor Hall sensor input

35 XSSPDON O Spindle motor on output

36, 37, 38, 39 XSFLAG[3:0] O These pins are used to monitor some status of servo control block

48, 51, 52 XGPIO[2:0] I/O

40 XMP1_7 I/O Internal microcontroller programmable I/O port 1.7.

41 XMP1_6 I/O Internal microcontroller programmable I/O port 1.6.

43 XMP1_5 I/O This pin is now changed to be NC.

44 XMP1_4 I/O Internal microcontroller programmable I/O port 1.4.

45 XMP1_3 I/O Internal microcontroller programmable I/O port 1.3.

47 XMP1_2 I/O Internal microcontroller programmable I/O port 1.2.

49 XMP1_1 I/O Internal microcontroller programmable I/O port 1.1.

57 XMP1_0 I/O

46 XMFSCSJ I/O Output chip select connected to external flash ROM chip enable pin

54 XMPSENJ I/O Output program store enable connected to external ROM PSENJ pin.

56 XMALE I/O This signal is used as address latch signal in address/data mux mode

70 XMCSJ I/O

71 XMRDJ I/O

72 XMWRJ I/O This signal is used as the Wire Strobe signal

73 XMINT1J I/O

74, 75, 77, 78,

79, 80, 81, 82,

83, 84, 85, 86,

87, 89, 90, 91

62, 63, 64, 65,

66, 67, 68, 69 bus for the 8-bit processor mode.

163 XTPLCK I/O PLCK test pin

164 XTSLRF I/O SLRF test pin

59 XOSC1 I Crystal input/System clock. The input frequency from outside crystal or oscillator is 33.8688MHz

60 XOSC2 O Crystal output

53 XCRSTJ I

94 XHCS1J I This pin is used to select the command block task file registers

93 XHCS3J I This pin is used to select the control block task file registers

103 XHIORJ I Asserted by the host during a host I/O read operation

104 XHIOWJ I Asser ted by the host during a host I/O write operation

105 XHDRQ O

101 XHDACKJ I

99 XHCS16J O

50 XHRSTJ I Host Reset. The reset of ATA bus

100 XHINT O

XMA[15:0] I/O These pins are used as address bus

XMD[7:0] I/O

Type

Phase detector reference current generator. Connect a resistor between this pin and

ground to set reference current

Frequency detector reference current generator. Connect a resistor between this pin and

ground to set reference current

1. These pins are used as general purpose I/O bus

2. When use internal microcontroller, XGPIO[2] can be used as programmable I/O port 3.6.

Internal microcontroller programmable I/O port 1.0.

This pin is default used as the A16 (microcontroller address line 16)

1. This signal must be asserted for all microcontroller accesses to the register of this chip

2. When use internal microcontroller, this signal can be used as programmable I/O port 3.1

1. This signal is used as the Read Strobe signal

2. When use internal microcontroller, this signal can be used as programmable I/O port 3.0

1. This signal is an interrupt line to the microcontroller

2. When use internal microcontroller, this signal can be used as programmable I/O port 3.7

These pins are used as data bus for the 16-bit processor mode, or the address/data mux

Chip Reset. As asserted low input generates a component reset that stops all operations within

the chip and deasserts all output signals. All input/output signals are set to input.

1.

DMA request. This pin is configured as the DMA request signal, and is used during DMA transfer

between the host and the controller. This pin is tri-stated when DMA transfers are not enabled.

2.

MPEG acknowledge. This pin is used as the ACKJ signal when MPEG interface mode is selected.

1. DMA acknowledge. This pin is configured as DACKJ, and is used as the DMA acknowledge

signal during DMA data transfers.

2. MPEG request. This pin is used as the REQ signal when MPEG interface mode is selected

1. 16-bit data select. This signal indicates that a 16-bit data transfer is active on the host data

bus. This pin is open-drain tri-state output.

2. MPEG clock. This pin is used as the CLOCK signal when MPEG interface mode is selected.

1. Host interface request. This tri-state pin is the host interrupt request, and is asserted to

indicate to the host that the controller needs attention.

2. MPEG begin. This pin is used as the BEGIN signal when MPEG interface mode is selected

DescriptionPin No.

14

Page 15

ADV-M71

15

Pin Name

97 XHPDIAGJ I/O This pin is used as the Passed Diagnostics signal, and may be an input or an open-drain output

92 XHDASPJ I/O

102 XHIORDY I/O

95, 96, 98 XHA[2:0] I

106, 107, 108, 2.

109, 111, 112, 3. VCD I/F. Bit3-0 are used as VCD I/F signal when VCD function is enabled. The relationship of

113, 114, 116, bit3-0 and VCD I/F is as follow

117, 118, 119, HD0—CD-DATA

120, 121, 122, HD1—CD-LRCK

123 HD2—CD-BCK

143 XRSDCLK O This signal is the clock output for SDRAM

147 XROEJ O

142 XRWEJ O This signal is asserted low when a buffer memory write operation is active

144 XRRASJ O

145 XRCASJ O

148, 149, 151,

152, 153, 155,

156, 157, 158,

159, 160, 161

124, 125, 126,

127, 128, 129,

131, 132, 134,

135, 136, 137,

138, 139, 140,

141

4 AVDD5_DS Analog Power +5V for Data Slicer part

14 AVDD5_DA Analog Power +5V for DAC part

26 AVDD5_AD Analog Power +5V for ADC part

168 AVDD5_PL Analog Power +5V for Data PLL part

7, 55, 58, 76,

115, 146,

150, 162

1 AVSS_DS Analog Ground for Data Slicer part

16 AVSS_DA Analog Ground for DAC part

22 AVSS_AD Analog Ground for ADC part

170 AVSS_PL Analog Ground for Data PLL part

28, 42, 61,

88, 110, 130,

138, 154, 165

XHD[15.0] I/O

XRA[11:0] O 1: Normal operation

XRD[15:0] I/O These signals are the 8-bit parallel data lines to/from the buffer memory.

VDD Power +3.3V for digital core logic and pad

GND Digital Ground core logic and pad.

Type

This pin is used as the Drive Active/Slave Present signal, and is an input or an open-drain

output. This pin is used for Master/Slave drive communication and/or for driving an LED

1. I/O channel ready. This signal is driven low to extend host transfer cycles when the controller

is not ready to respond. This pin will be tri-stated when a read or write is not in progress.

2. MPEG error. This pin is used as the ERROR signal when MPEG interface mode is selected

Host address lines. The host address lines A[2:0] are used to access the various host control,

status, and data registers

1. Host data bus. This bus is used to transfer data and status between the host and the controller.

MPEG data bus 7-8. The HD[7:0] are used as the DATA [7:0] when MPEG interface mode is selected.

HD3—CD-C2PO

This signal is used as the memory output enable for external DRAM buffers. After RSTJ is

asserted, this signal will be low

This signal is used as Row address output to external DRAM buffer. After RSTJ is asserted, this

signal will be high

This signal is used as column address output to external DRAM. After RSTJ is asserted, this

signal will be high

1. RAM address lines. These are bits11-0 for addressing the buffer memory.

2. Hardware setting. The bits6-0 are used as hardware setting for some functions.

RA[9] : FLASH size is 64K/128K

1: FLASH size is 64K

0: FLASH size is 128K

RA[8] : External CPU is 8032/H8

1: 8032

0: H8

RA[7] : Microcontroller programmable I/O port 1 pin control

1: By internal microcontroller

0: By registers to decide input/output

RA[6] : System test pin output

0: System test pin output

RA[5] : For testing purpose, don’t need to set

RA[4] : IDE master/slave

1: Slave

0: Master

RA[3] : For testing purpose, don’t need to set

RA[2] : For testing purpose, don’t need to set

RA[1-0] : MCU Mode selection

11: Normal Mode (internal uP, internal address latch)

10: Outside uP Mode (ICE Mode)

01: Test mode for internal uP testing

00: Internal uP mode with external address latch

DescriptionPin No.

15

Page 16

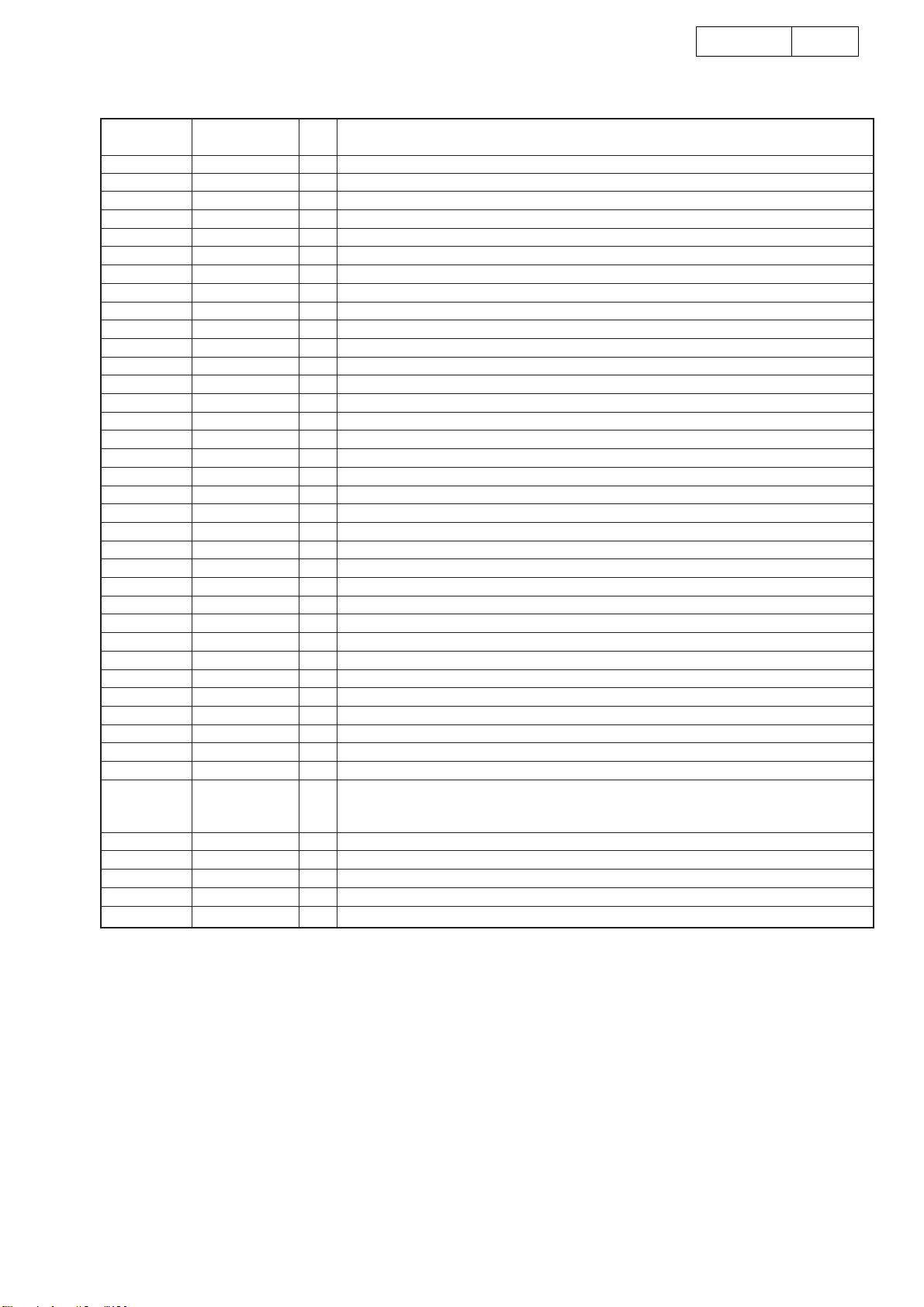

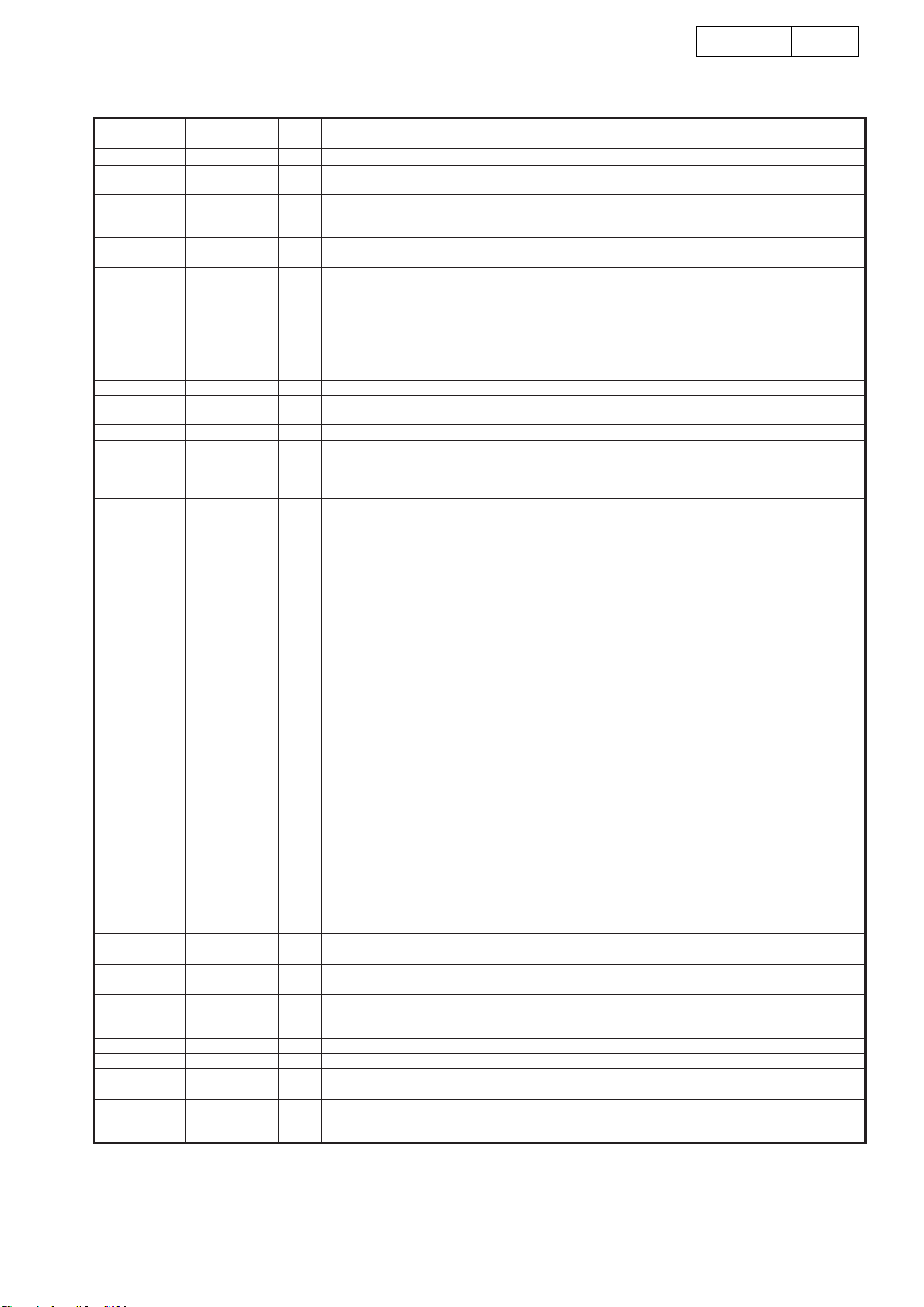

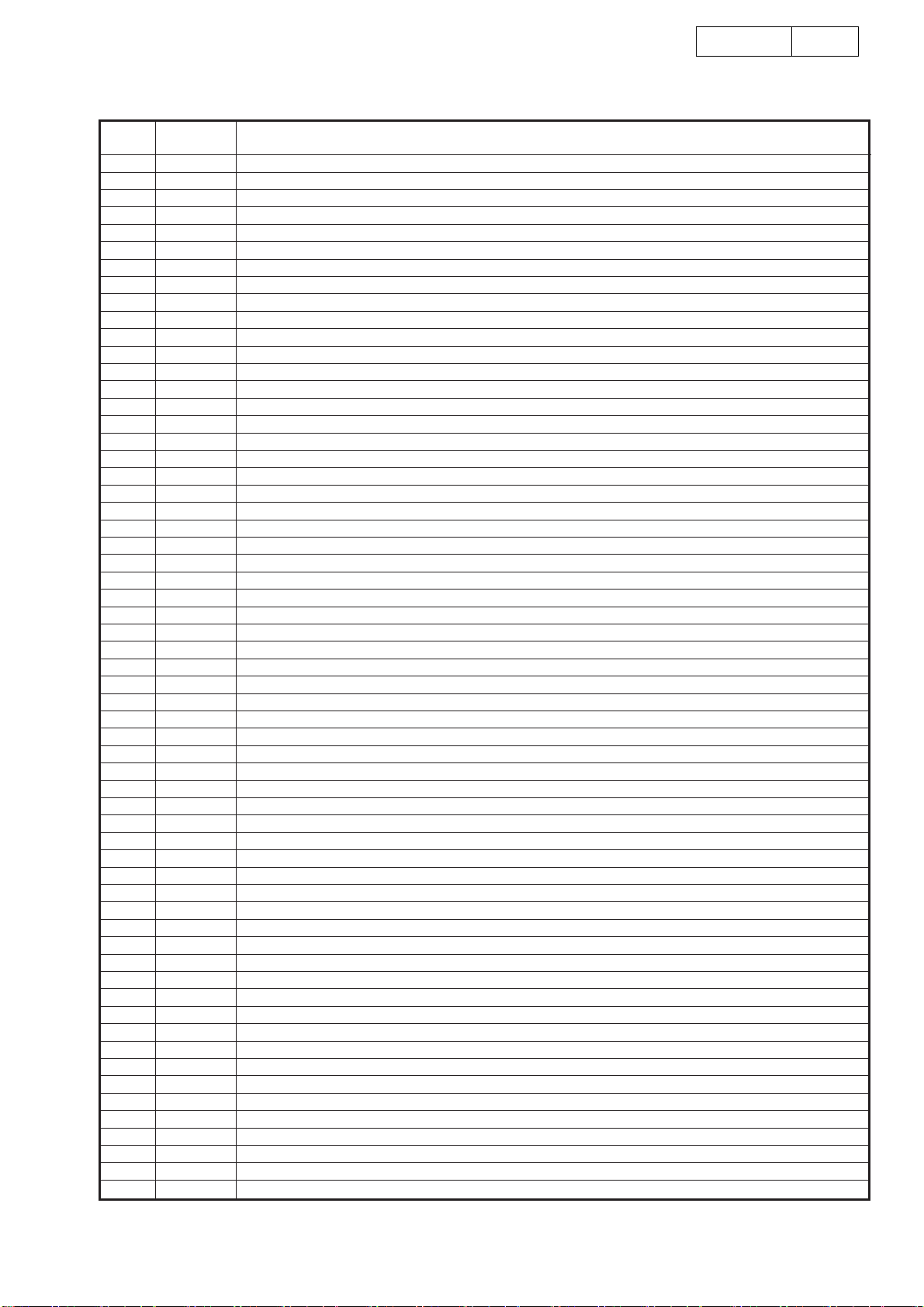

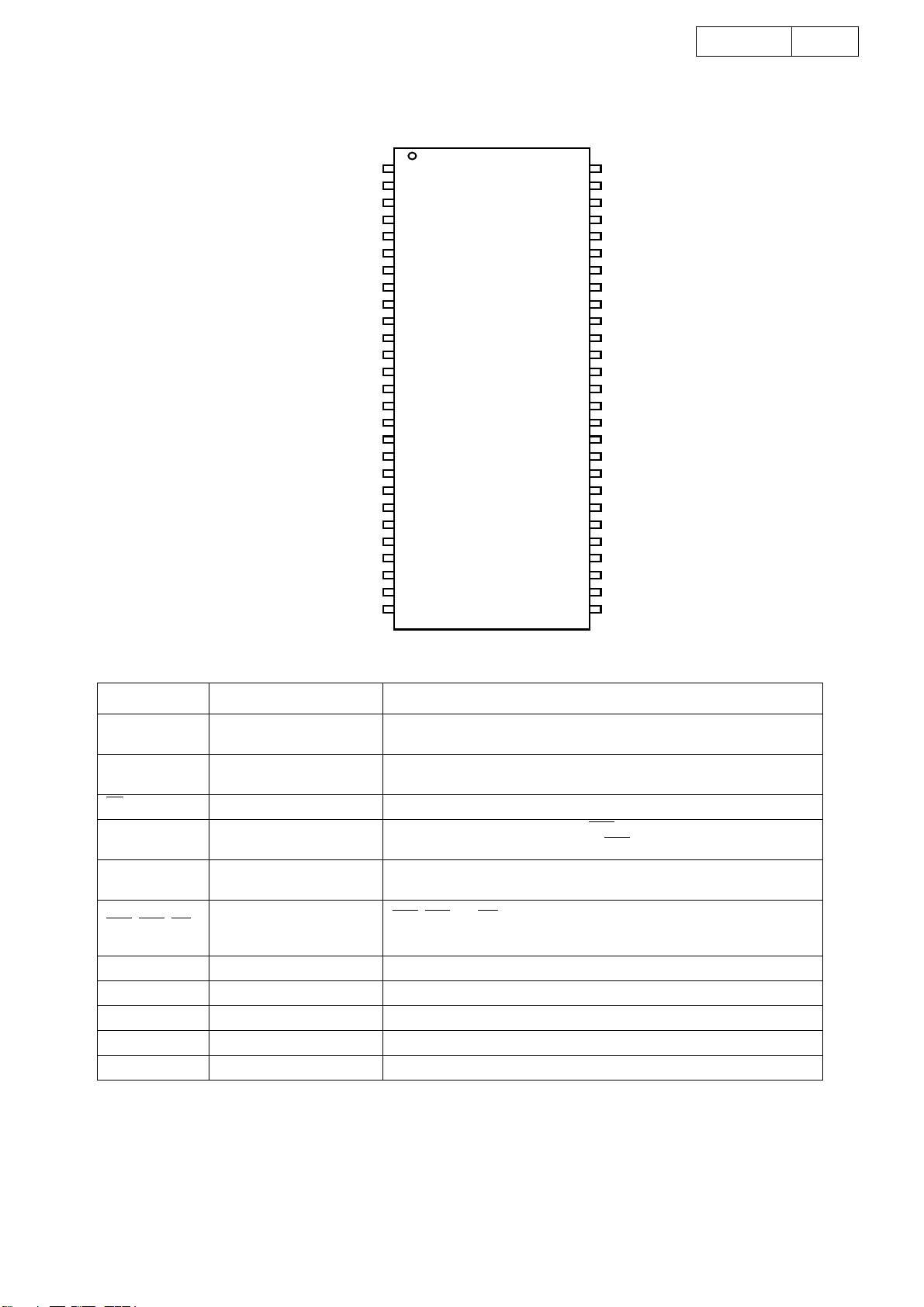

M30626FHPGP (MA: IC302)

ADV-M71

16

M30626FHPGP PORT

Pin No. port function Port setting Port name Explanation

1P94

2P93

3P92

4P91

5P90

6 BYTE - Gnd

7 CNVSS - don't use

8P87

9P86

10 RESET RESET Reset input

11 XOUT XOUT Xtal output

12 VSS VSS Gnd

13 XIN XIN Xtal input

14 VCC VCC Vcc

15 NMI - don't use

16 INT2

17 INT1

18 INT0 INT DE RXD Serial data input from DENON BUS

19 TA4IN

20 P80

21 P77

22 P76

23 P75

24 P74

25 P73

OE2P CS

O 3811 DATA

SO E2P DI

SI E2P DO

SO E2P CK

O 3811 CLK

OVMUTE

INT PROTECT

INT ESS CS

I50/60

O PROG/INTE

IVR JOG-B

IVR JOG-A

IFN JOG-B

IFN JOG-A

OFLCS

Chip select output to EEPROM

Serial data output to elec.VR

Serial data output to EEPROM

Serial data input from EEPROM

Serial clock output to EEPROM

Serial clock output to elec.VR

Mute output to video driver

Protect signal input L:Protect detect

Chip select input from ESS

Line pulse input(50/60Hz)

Progressive/Interlace switching signal output

VR encoder pulse-B input

VR encoder pulse-A input

Function encoder pulse-B input

Function encoder pulse-A input

Chip select output to FLD driver

16

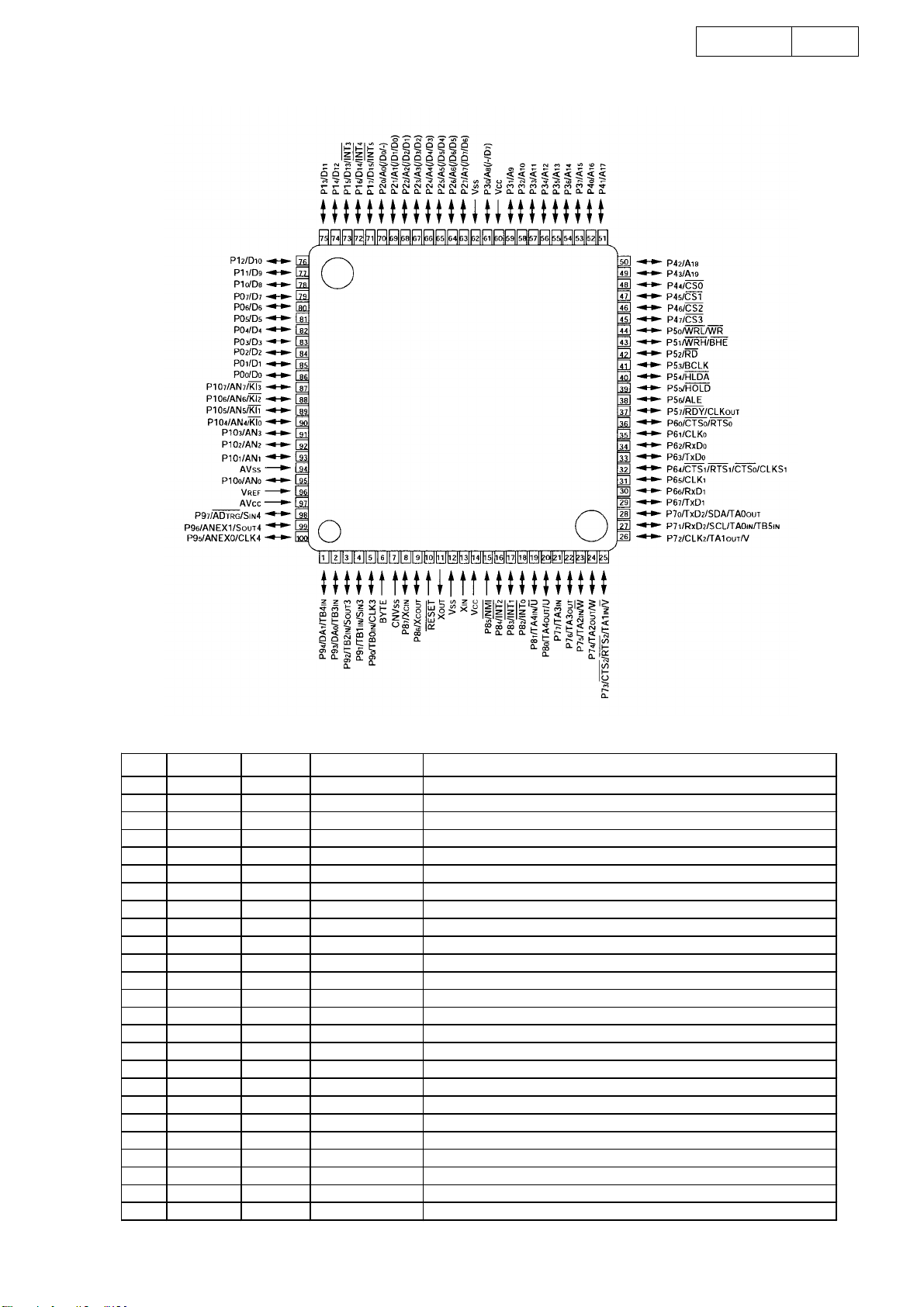

Page 17

Pin No. port function Port setting Port name Explanation

26 CLK2

27 RXD2

28 TXD2

29 TXD1

30 P66 O DSPCOREPOW DSP(Mel100) core power ON/OFF switching H:P-ON

31 CLK1

32 P64

33 TXD0

34 RXD0

35 CLK0

36 P60

37 P57

38 P56

39 P55 O - don't use

40 P54

41 P53

42 P52 O RGB H Conposite/S/RGB switching

43 P51

44 P50 O - don't use

45 P47

46 P46

47 P45

48 P44

49 P43

50 P42

51 P41

52 P40

53 P37

54 P36

55 P35

56 P34

57 P33 O EXP OE for port expand

58 P32 O EXP STB for port expand

59 P31 O EXP DA for port expand

60 VCC VCC Vcc

61 P30 O EXP CLK for port expand

62 VSS VSS Gnd

63 P27

64 P26

65 P25

66 P24

67 P23

68 P22

69 P21

70 P20

71 INT5

72 INT4

73 INT3

74 P14

75 P13

76 P12

77 P11

78 P10

79 P07

80 P06

81 P05

82 P04

83 P03

84 P02

85 P01

SO DE CK

SI DE RXD

SO DE TXD

SO FLDA

SO FLCK

OFLRST

SO ESS DO

SI ESS DI

SI ESS CK

I ESS ON

ODVD RST

I HP SW

O

REQ1

O DVD ON/OFF

O VCONT1

O VCONT2

OCODEC RST

O SEL CLK

O BSE

OERR MUTE

ODIR CE

ODIR RST

OCLATCH

OP.ON/OFF

OSCART MUTE

OSUB ON

O FR-RELAY

I TEMP FAN

ISTEREO

ITUNED

OTMUTE

OTU CE

OTU DI

OTU CK

ITU DO

DFRES Ext reset signal from ESS

I

I DIR INT1

IREMOTE

O SYR

O DSP1-RST

OROM RST1

O DSPOSCON

O DSPIOPOWER

IO IO8

IO IO7

IO IO6

IO IO5

IO IO4

IO IO3

IO IO2

Serial clock output to DENON BUS

Serial data input from DENON BUS

Serial data output to DENON BUS

Serial data output to FLD driver

Serial clock output to FLD driver

RESET output to FLD driver

Serial data output to ESS

Serial data input from ESS

Serial clock input from ESS

ESS"Active" signal input H:Active

Forced reset output to DVD drive

H/P insert detect signal input H:insert

Control signal input from DSP(Mel100)

DVD drive power supply ON/OFF switching H:P-ON

Aspect ratio switching-1

Aspect ratio switching-2

Reset output to CODEC(AD1837)

DSP clock switching

DSP mute output

Mute output at DSP error

Chip select output to DIR(LC89057)

Reset output to DIR(LC89057)

Latch output to DIR(LC89057)

Main power ON/OFF switching H:ON

Mute output to SCART audio output H:mute-on

Standby power ON/OFF switching H:OFF

Front SP relay ON/OFF switching H:ON

Temp detect input for fan L: fan-on

"STEREO"indicator input from tuner

Tuned detect input from tuner

Mute output to tuner audio signal L:mute-on

Chip enable output to tuner

Serial data output to tuner

Serial clock output to tuner

Serial data input from tuner

Interrupt request from DIR

Remote controler signal input

Reset output to RDS IC

Reset output to DSP

Reset output to DSP ROM

OSC(for DSP) ON/OFF switching

DSP(Mel100) I/O power ON/OFF switching H:P-ON

I/O interface port to DSP

I/O interface port to DSP

I/O interface port to DSP

I/O interface port to DSP

I/O interface port to DSP

I/O interface port to DSP

I/O interface port to DSP

ADV-M71

17

17

Page 18

Pin No. port function Port setting Port name Explanation

86 P00

87 P107

88 P106

89 P105

90 P104

91 AN3 AD MODE2 Mode select-2

92 AN2 AD MODE1 Mode select-1

93 AN1

94 AVSS AVSS Gnd

95 AN0

96 VREF VREF Ref voltage of A/D port

97 AVCC AVCC Avcc

98 P96

99 P97

100 P95

INT:Interrupt Input

IO IO1

OR/W

IACK1

I BUSY1

IFLAG3A

AD KEY-0

AD KEY-1

SI DIR DOUT

SO DIR/CODEC DIN

SO DIR/CODEC CLK

I:Input

O:Output

SI:Serial Input

SO:Serial Output

I/O interface port to DSP

Write/Read switching output to ROM for DSP

Control signal input from DSP(Mel100)

Control signal input from DSP(Mel100)

Control signal input from DSP(Mel100)

KEY A/D input-0

KEY A/D input-1

Serial data input from DIR

Serial data output to DIR/CODEC

Serial clock output to DIR/CODEC

ADV-M71

18

18

Page 19

BD3811K1 (MA: IC504)

()

IN31

1

IN32

2

IN41

3

IN42

4

IN51

5

IN52

6

IN61

7

IN62

8

IN71

9

IN72

10

IN81

11

IN82

12

INDVDSR

13

INDVDSL

14

INDVDC

15

INDVDSW

16

OUT2(+)

17

OUT2(-)

18

OUT1(+)

19

OUT1(-)

20

IN1DSP

21

IN1MIX

22

IN2DSP

23

IN2MIX

24

BD3811K1 Pin Description

IN22

IN21

IN12

IN11

ROUT32

ROUT31

ROUT22

ROUT21

ROUT12

ROUT11

AGND10

GOUT2

VIN2

AGND9

TREBLE

LOGIC

BASS

BASS

BOOST

OUTSR

GOUT1

VINSL

80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65

47k

47k

47k

47k

47k

47k

47k

47k

47k

47k

47k

47k

47k

47k

47k

47k

47k

25 26

INDSPSR

47k

47k

GOUTSW

RECSW

23

VINSW

RECSW

1

2

3

1

2

3

Input mute SW

5.1ch Mode SW2 DVD

47k

47k

47k

47k

5.1ch Mode SW2 DSP

47k

47k

47k

47k

47k

27 28 29 30 31 32 33 34 35 36 37 38 39 40

INDSPSL

INDSPC

INDSPSW

AGND1

AGND2

REC

SW1

REC

INSW

LINE

R/L

MIX

LINE

R/L

MIX

5.1ch Mode SW1

GOUTC

VINC

OUTSW

OUTC

OUTSL

VCC

VEE

ADV-M71

VIN1

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

GOUTSL

19

TNF2

TNF1

BNF11

BNF21

BNF12

BNF22

BBNF2

OUT2

BBNF1

OUT1

AGND8

AGND7

VCC

AGND6

VEE

AGND5

MUTE

CL

DA

DGND

AGND4

GOUTSR

VINSR

AGND3

Pin No. DescriptionPin Name

1 IN31 1ch input terminal 3

2 IN32 2ch input terminal 3

3 IN41 1ch input terminal 4

4 IN42 2ch input terminal 4

5 IN51 1ch input terminal 5

6 IN52 2ch input terminal 5

7 IN61 1ch input terminal 6

8 IN62 2ch input terminal 6

9 IN71 1ch input terminal 7

10 IN72 2ch input terminal 7

11 IN81 1ch input terminal 8

12 IN82 2ch input terminal 8

13 INDVDSR DVD surround Rch input terminal

14 INDVDSL DVD surround Lch input terminal

15 INDVDC DVD center speaker input terminal

16 INDVDSW DVD sub woofer input terminal

17 OUT2(+) 2ch (+) A/D output terminal

18 OUT2(-) 2ch (-) A/D output terminal

19 OUT1(+) 1ch (+) A/D output terminal

20 OUT1(-) 1ch (-) A/D output terminal

19

Page 20

Pin No. DescriptionPin Name

21 IN1DSP 1ch DSP input terminal

22 IN1MIX 1ch DSP MIX input terminal

23 IN2DSP 2ch DSP input terminal

24 IN2MIX 2ch DSP MIX input terminal

25 INDSPSR DSP surround Rch input terminal

26 INDSPSL DSP surround Lch input terminal

27 INDSPC DVD center speaker input terminal

28 INDSPSW DSP sub woofer input terminal

29 AGND1 Analog ground terminal

30 GOUTSW Sub woofer input gain output terminal

31 VINSW Sub woofer volume input terminal

32 AGND2 Analog ground terminal

33 GOUTC Center speaker input gain output terminal

34 VINC Center speaker volume input terminal

35 OUTSW Sub woofer output terminal

36 OUTC Center speaker output terminal

37 OUTSL Surround Lch output terminal

38 OUTSR Surround Rch output terminal

39 VINSL Surround Lch volume inut terminal

40 GOUTSL Surround Lch input gain output terminal

41 AGND3 Analog ground terminal

42 VINSR Surround Rch volume input terminal

43 GOUTSR Surround Rch input gain output terminal

44 AGND4 Analog ground terminal

45 DGND Ground terminal for comparator.

46 DA Serial data and latch input terminal

47 CL Serial clock input terminal

48 MUTE Mute terminal

49 AGND5 Analog ground terminal

50 VEE (-) Power supply terminal

51 AGND6 Analog ground terminal

52 VCC (+) Powr supply terminal

53 AGND7 Analog ground terminal

54 AGND8 Analog ground terminal

55 OUT1 1ch output terminal

56 BBNF1 1ch bass boost filter terminal

57 OUT2 2ch output terminal

58 BBNF2 2ch bass boost filter terminal

59 BNF22 2ch bass filter terminal 2

60 BNF12 2ch bass filter terminal 1

61 BNF21 1ch bass filter terminal 2

62 BNF11 1ch bass filter terminal 1

63 TNF1 1ch treble filter terminal

64 TNF2 2ch treble filter terminal

65 VIN1 1ch (Lch) volume input terminal

66 GOUT1 1ch (Lch) input gain output terminal

67 AGND9 Analog ground terminal

68 VIN2 2ch (Rch) volume input terminal

69 GOUT2 2ch (Rch) input gain output terminal

70 AGND10 Analog ground terminal

71 ROUT11 1ch REC input and output terminal 1

72 ROUT12 2ch REC input and output terminal 1

73 ROUT21 1ch REC output terminal 2

74 ROUT22 2ch REC output terminal 2

75 ROUT31 1ch REC output terminal 3

76 ROUT32 2ch REC output terminal 3

77 IN11 1ch input terminal 1

78 IN12 2ch input terminal 1

79 IN21 1ch input terminal 2

80 IN22 2ch input terminal 2

ADV-M71

20

20

Page 21

M66005AFP (MA: IC101)

ADV-M71

21

21

Page 22

SP3721A (ME: U2)

ATOP

CDRF

CDRDDC

ATON

AIN

AIP

ADV-M71

HOLD1

VNA

FNN

FNP

DIP

DIN

RX

BYP

SIGO

VPA

49505152535455565758596061626364

22

DVDRFP

DVDRFN

PD1

PD2

A2

B2

C2

D2

CP

CN

1

2

3

4

5

6

7

8

9

10

11

D

12

C

13

B

14

A

15

F

16

E

NC

VCI2

CDTE

TOP VIEW

VNB

DVDLD

DVDPD

CDLD

CDPD

VC

LDON#

VCI

VPB

VIIRR

VIP

32313029282726252423222120191817

VIB

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

FDCHG#

SDEN

SD ATA

SCLK

LCP

LCN

CE

FE

TE

MEI

MEV

TPH

DFT

PI

MIN

MEVO

MLPF

SP3721A Terminal Function

Pin Name

Type

1, 2 DVDREP, DVDREN I RF Signal Inputs. Differential RF signal attenuator input pins

63 CDRF I RF Signal Inputs. Single-ended RF signal attenuator input pin

59, 60 AIP, AIN I AGC Amplifier Inputs. Differential AGC amplifier input pins

53, 54 DIP, DIN I

Analog inputs for RF Single Buffer. Differential analog inputs to the RF single-ended output buffer

and full wave rectifier

Low Impedance Enable. A TTL compatible input pin that activates the FDCHG switches. A low

32 FDCHG# I

level activates the switches and the falling edge of the internal FDCHG triggers the fast decay for

the MIRR bottom hold circuit. (open high)

49 HOLD1 I

Hold Control. A TLL compatible control pin which, when pulled high, disables the RF AGC charge

pump and holds the RF AGC amplifier gain at its present value. (open high)

11~14 D, C, B, A I Photo Detector Interface Inputs. Inputs from the main beam Photo detector matrix outputs

5~8 A2, B2, C2, D2 I

Photo Detector Interface Inputs. AC coupled inputs for the DPD from the main beam Photo

detector matrix outputs

15~16 F, E I CD tracking Error Inputs. Inputs from the CD photo detector error outputs.

3~4 PD1, PD2 I CD Photo detector Interface Inputs. Inputs from the CD photo detector error outputs

40 MEI I Mirror Envelope Inputs. The SIGO envelope input pin

35 MIN I

RF signal Input for Mirror. AC coupled inputs for the mirror detection circuit from the pull-in signal

output. (PI)

21 DVDPD I APC Input. DVD APC input pin from the monitor photo diode

23 CDPD I APC Input. CD APC input pin from the monitor photo diode

25 LDON# I APC Output On/Off. APC output control pin. A low level activates the LD output. (open high)

61, 62 ATON/ATOP O Differential Attenuator Output. Attenuator outputs

51, 52 FNN, FNP O Differential Normal Output. Filter normal outputs

57 SIGO O Single Ended Normal Output. Single-ended RF output

64 CDRFDC O CD RF Signal Output. Single ended CD RF summing output

42 FE O Focusing Error Signal Output. Focus error output reference to VCI

41 TE O Tracking Error Signal Output. Tracking error output reference to VCI

DescriptionPin No.

22

Page 23

ADV-M71

23

Pin Name

43 CE O Center Error Signal Output. Center error output reference to VCI

34 NEVO O SIGO Bottom Envelope Output. Bottom envelope for mirror detection

37 DFT O

29 MIRR O Mirror Detect Output. Mirror Detect comparator output. Pseudo CMOS output

36 PI O

22 DVDLD O APC output. DVD APC output pin to control the laser power

24 CDLD O APC output. CD APC output pin to control the laser power

56 BYP I/O The RF AGC integration capacitor CBYP, is connected between BYP and VPA

9 CP I/O

10 CN I/O

45 LCP — Center Error LPF pin. An external capacitance is connected between this pin and the LCN pin

44 LCN — Center Error LPF pin. An external capacitance is connected between this pin and the LCP pin

30 MP — MIRR signal Peak hold pin. An external capacitance is connected to between this pin and VPB

31 MB — MIRR signal Bottom hold pin. An external capacitance is connected to between this pin and VPB

39 MEV — Sigo Bottom Envelope pin. An external capacitance is connected to between this pin and VPB

17 CDTE — CD Tracking. E-F Opamp output for feedback

38 TPH — PI Top Hold pin. An external capacitance is connected to between this pin and VPB

26 VC —

27 VCI — Reference Voltage input. DC bias voltage input for the servo input reference

18 VCI2 — Reference Voltage input. DC bias voltage input for the servo input reference

55 RX —

33 MLPF — MIRR signal LPF pin. An external capacitance is connected between this pin and VPB

19 NC — No Connect

48 SDEN I

47 SDATA I/O

46 SCLK I

58 VPA Power. Power supply pin for the RF block and serial port

28 VPB Power. Power supply pin for the servo block

50 VNA Ground. Ground pin for the RF block and serial port

20 VNB Ground. Ground pin for the servo bolck

Type

Defect Output. Pseudo CMOS output. When a defect is detected, the DFT output goes high. Also

the servo AGC output can be monitored at this pin, when CAR bits 7-4 are ‘0011’

Pull-in Signal Output. The summing signal output of A, B, C, D or PD1, PD2 for mirror detection.

Reference to VCI

Differential Phase tracking LPF pin. An external capacitance is connected between this pin and

the CN pin

Differential Phase tracking LPF pin. An external capacitance is connected between this pin and

the CP pin

Reference Voltage output. This pin provides the internal DC bias reference voltage (+2.5V lix).

Output Impedance is less than 50ohms

Reference Resistor Input. An external 8.2kohm, 1% resistor is connected from this pin to ground

to establish a precise PTAT (proportional to absolute temperature) reference current for the filter

Serial Data Enable. Serial Enable CMOS input. A high level input enable the serial port (Not to be

left open)

Serial Data. Serial data bi-directional CMOS pin. NRZ programming data for the internal registers

is applied to this input ( Not to be left open)

Serial Clock. Serial Clock CMOS input. The clock applied to this pin is synchronized with the data

applied to SDATA (Not to be left open)

DescriptionPin No.

23

Page 24

HY57V651620BTC-75 (ME: U11)

ADV-M71

24

DD

V

DQ0

V

DDQ

DQ1

DQ2

SSQ

V

DQ3

DQ4

DDQ

V

DQ5

DQ6

V

SSQ

DQ7

DD

V

LDQM

/WE

/CAS

/RAS

/CS

BA0

BA1

A10/ AP

A0

A1

A2

A3

V

DD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

SS

V

DQ15

V

SSQ

DQ14

DQ13

DDQ

V

DQ12

DQ11

SSQ

V

DQ10

DQ9

V

DDQ

DQ8

SS

V

NC

UDQM

CLK

CKE

NC

A11

A9

A8

A7

A6

A5

A4

V

SS

PIN DESCRIPTION

PIN PIN NAME DESCRIPTION

CLK Clock

CKE Clock Enable

CS

BA0,BA1 Bank Address

A0 ~ A11 Address

RAS

, CAS, WE

LDQM, UDQM Data Input/Output Mask Controls output buffers in read mode and masks input data in write mode

DQ0 ~ DQ15 Data Input/Output Multiplexed data input / output pin

V

DD/VSS Power Supply/Ground Power supply for internal circuits and input buffers

V

DDQ/VSSQ Data Output Power/Ground Power supply for output buffers

NC No Connection No connection

Chip Select Enables or disables all inputs except CLK, CKE and DQM

Row Address Strobe,

Column Address Strobe,

Write Enable

The system clock input. All other inputs are registered to the SDRAM on the

rising edge of CLK

Controls internal clock signal and when deactivated, the SDRAM will be one

of the states among power down, suspend or self refresh

Selects bank to be activated during RAS activity

Selects bank to be read/written during CAS

Row Address : RA0 ~ RA11, Column Address : CA0 ~ CA7

Auto-precharge flag : A10

RAS

, CAS and WE define the operation

Refer function truth table for details

activity

24

Page 25

AD1837A (MA: IC711)

ADV-M71

25

DSDATA2

DSDATA1

NC

AGND

CLOCK

DIGITAL

FILTER

DIGITAL

FILTER

DIGITAL

FILTER

DIGITAL

FILTER

DGND

DVDD

39

38

DBCLK

37

DLRCLK

M/S

36

AGND

35

34

OUTR4

33

NC

32

OUTL4

31

NC

30

AGND

29

AVDD

28

OUTR3

NC

27

OUTL3

MCLKASDATAABCLKALRCLKODVDDDVDD DVDD

PD/RST M/S AVDD AVDD

DescriptionPin No.

V

Σ-∆

DAC

Σ-∆

DAC

Σ-∆

DAC

Σ-∆

DAC

REF

OUTL1

OUTR1

OUTL2

OUTR2

OUTL3

OUTR3

OUTL4

OUTR4

FILTD

FILTR

DLRCLK

DBCLK

DSDATA1

DSDATA2

DSDATA3

DSDATA4

ADCLP

ADCLN

ADCRP

ADCRN

AD1837 Terminal Function

Pin Name

CLATCH

PD/RST

OUTL1

OUTR1

OUTL2

Σ-∆

ADC

Σ-∆

ADC

AD1837

Input/

Output

DVDD

CIN

AGND

NC

NC

AGND

AVDD

NC

DGND

CCLK

COUT

ASDATA

ODVDD

MCLK

ALRCLK

ABCLK

50 494847 46 45 44 43 42 41 40

51

52

1

2

3

4

5

6

7

8

9

10

11

12

13

14 15 16 17 18 19 20 21 22 23 24 25 26

NC

SERIAL DATA

I/O PORT

DIGITAL

FILTER

DIGITAL

FILTER

AGND

OUTR2

TOP VIEW

AVDD

FILTD

FILTR

DGND AGND AGND AGND AGNDDGND

DSDATA4

ADCLP

ADCLN

ADCRN

CONTROL PORT

VOLUME

VOLUME

VOLUME

VOLUME

VOLUME

VOLUME

VOLUME

VOLUME

DSDATA3

ADCRP

CINCLATCHCCLK COUT

1,39 DVDD Digital Power Supply. Connect to digital 5V supply.

2 CLATCH I Latch Input for Control Data

33 CIN I Serial Control Input

4 PD/RST I Power-Down/Reset

5,10,16,24,30,35 AGND Analog Ground

6,12,25,31 NC Not connected

7,13,26,32 OUTLx O DACx Left Channel Output

8,14,27,33 NC Not connected

9,15,28,34 OUTRx O DACx Right Channel Output

11,19,29 AVDD Analog Power Supply. Connect to analog 5V supply.

17 FILTD Filter Capacitor Connection. Recommend 10µF/100nF.

18 FILTR Reference Filter Capacitor Connection. Recommended 10µF/100nF.

20 ADCLN I ADC Left Channel Negative Input

21 ADCLP I ADC Left Channel Positive Input

22 ADCRN I ADC Right Channel Negative Input

23 ADCRP I ADC Right Channel Positive Input

36 M/S I ADC Master/Slave Select

37 DLRCLK I/O DAC LR Clock

38 DBCLK I/O DAC Bit Clock

40,52 DGND Digital Ground

41-44 DSDATAx I DACx Input Data (Left and Right Supply)

45 ABCLK I/O ADC Bit Clock

46 ALRCLK I/O ADC LR Clock

47 MCLK I Master Clock Input

48 ADVDD Digital Output Driver Power Supply

49 ASDATA O ADC Serial Data Output

50 COUT O Output for Control Data

51 CCLK I Control Clock Input for Control Data

25

Page 26

T431616A-8S (ME: U5)

ADV-M71

26

DD

V

DQ0

DQ1

SSQ

V

DQ2

DQ3

DDQ

V

DQ4

DQ5

V

SSQ

DQ6

DQ7

DDQ

V

LDQM

WE

CAS

RAS

CS

BA

A10/ AP

A0

A1

A2

A3

V

DD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

SS

V

DQ15

DQ14

V

SSQ

DQ13

DQ12

DDQ

V

DQ11

DQ10

SSQ

V

DQ9

DQ8

V

DDQ

N . C / RFU

UDQM

CLK

CKE

N . C

A9

A8

A7

A6

A5

A4

V

SS

PIN DESCRIPTION

PIN PIN NAME DESCRIPTION

CLK System Clock

CS

CKE Clock Enable

A0 ~ A10/AP

BA Bank Select Address

RAS

CAS

WE

L(U)DQM Data Input/Output Mask

DQ0 ~ DQ15

DD/VSS Power Supply/Ground

V

VDDQ/VSSQ

N.C/RFU

Chip Select

Address

Row Address Strobe

Column Address Strobe

Write Enable

Data Input/Output

Data Output Power/Ground

No Connection/Reserved

for Future Use

Active on the positive going edge to sample all input.

Disables or enables device operation by masking or enabling all input

except CLK,CKE and L(U)DQM

Masks system clock to freeze operation from the next clock cycle.

CKE should be enabled at least one cycle prior to new command.

Disable input buffers for power down in standby.

Row/column aaddresses are multiplexed on the same pins.

Row address : RA0 ~ RA10,column address : CA0 ~ CA7

Selects bank to activated during row address latch time.

Select bank for read/write during column address latch time.

Latches row addresses on the positive going edge of the CLK

with RAS low.

Enables row access & precharge.

Latches column addresses on the positive going edge of the CLK

with CAS low.

Enables column access.

Enables write operation and row precharge.

Latches data in starting from CAS, WE active.

Makes data output Hi-Z, t

Blocks data input when L(U)DQM active.

Data inputs/outputs are multiplexed on the same pins.

Powe and ground for the input buffers and the core logic.

Isolated power supply and ground for the output buffers to provide

improved noise immunity.

This pin is recommended to be left No Connection on the device.

SHZ after the clock and masks the output.

26

Page 27

LC89057W (MA: IC707)

( )

ADV-M71

27

RXOUT

RX0

RX1

RX2

RX3

RX4

RX5/VI

RX6/UI

LPF

TMCK/PIO0

TBCK/PIO1

TLRCK/PIO2

TDATA/PIO3

TXO/PIOEN

1

2

3

4

5

8

9

10

13

44

45

46

47

48

EMPHA/UO33AUDIO/VO35INT40CL39CE38DI

32

Microcontroller

Clock

27

Input

Selector

Modulation

or

Parallel Port

29

XIN

C bit, U bit

Demodulation

&

Lock Detect

PLL

28

XOUT

Selector

XMCK34CKST

I/F

Data

Selector

I/N

XMODE

41

37

36

21

24

16

17

20

22

23

DO

RERR

RD ATA

SDIN

RMCK

RBCK

RLRCK

SBCK

SLRCK

36 RERR1RXOUT

35 INT2RX0

34 CKST3RX1

TOP VIEW

33 AUDIO/VO4RX2

32 EMPHA/UO5RX3

31 DGND6DGND

30 DVDD7DVDD

29 XIN8RX4

28 XOUT9RX5/VI

27 XMCK10RX6/UI

26 DVDD11DVDD

25 DGND12DGND

24 SDIN37DO

23 SLRCK38DI

22 SBCK39CE

21 RDATA40CL

20 RLRCK41XMODE

19 DVDD42DGND

18 DGND43DVDD

17 RBCK44TMCK/PIO0

16 RMCK45TBCK/PIO1

15 AGND46TLRCK/PIO2

14 AVDD47TDATA/PIO3

13 LPF48TXO/PIOEN

LC89057W Terminal Function

Pin

No.

1 RXOUT O Input bi-phase select data output terminal

2 RX0 I TTL compatible digital data input terminal

3 RX1 I Coaxial compatible amp built-in digital data input terminal

4 RX2 I TTL compatible digital data input terminal

5 RX3 I TTL compatible digital data input terminal

6 DGND — Digital GND

7 DVDD — Digital power

8 RX4 I TTL compatible digital data input terminal

9 RX5/VI I TTL compatible digital data/Validity flag input terminal for modulation

10 RX6/UI I TTL compatible digital data/User data input terminal for modulation

11 DVDD — Digital power for PLL

12 DGND — Digital GND for PLL

13 LPF O PLL loop filter connecting terminal

14 AVDD — Analog power for PLL

15 AGND — Analog GND for PLL

16 RMCK O RMCK clock output terminal (256fs, 512fs, XIN, VCO)

17 RBCK O/I RBCK clock in/output terminal (64fs)

18 DGND — Digital GND

19 DVDD — Digital power

20 RLRCK O/I RLRCK clock in/output terminal (fs)

21 RDATA O Serial audio data output terminal

22 SBCK O SBCK clock output terminal (32fs, 64fs, 128fs)

23 SLRCK O SLRCK clock output terminal (fs/2, fs, 2fs)

24 SDIN I Serial audio data input terminal

25 DGND — Digital GND

26 DVDD — Digital power

27 XMCK O Osc. amp output terminal

Pin Name

I/O

Function

27

Page 28

ADV-M71

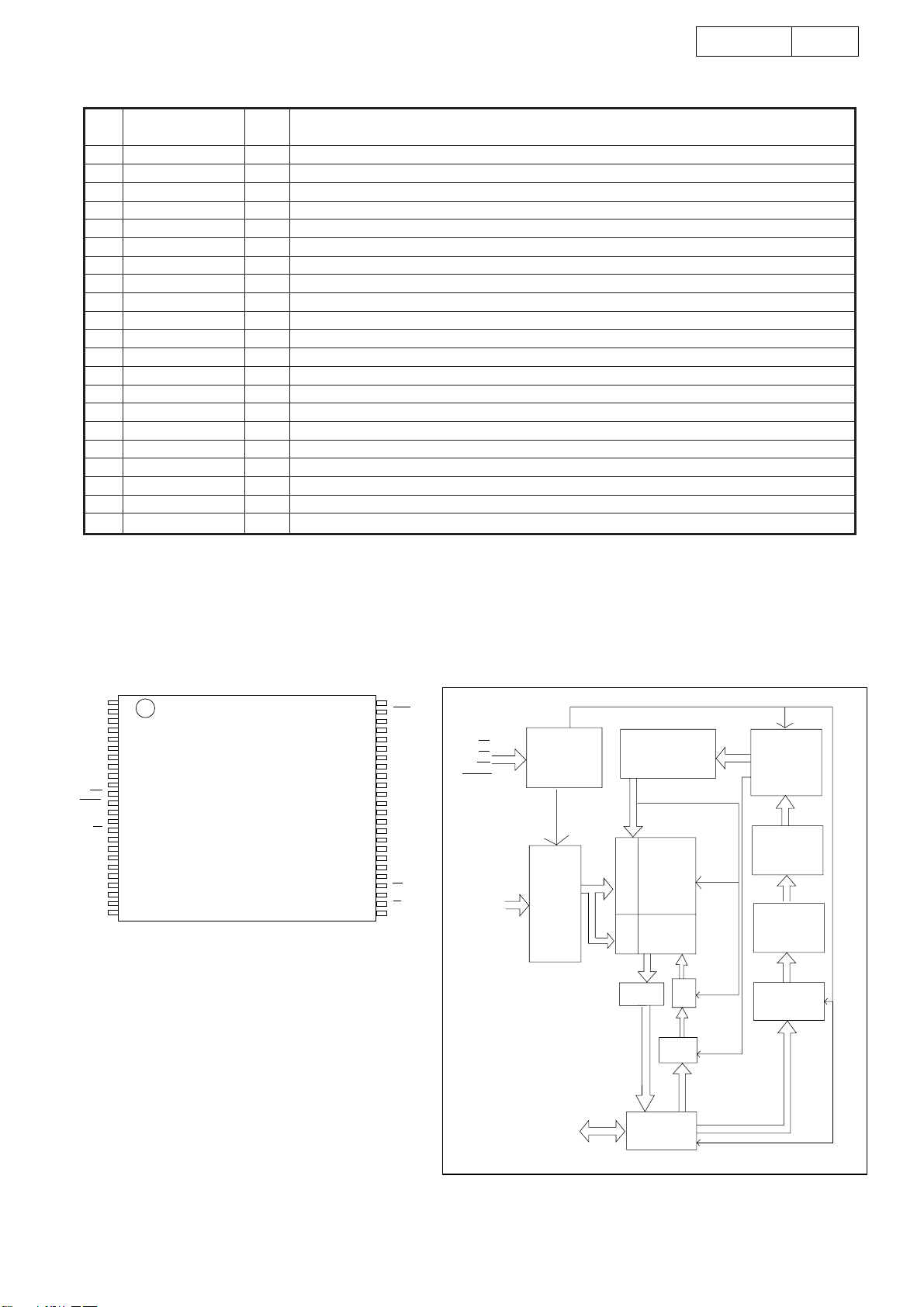

CONTROL

INPUT

LOGIC

PROGRAM/ERASE

HIGH VOLTAGE

WRITE

S TATE

MACHINE

(WSM)

STATE

REGISTER

FLASH

ARRAY

X-DECODER

ADDRESS

LATCH

AND

BUFFER

Y-PASS GATE

Y-DECODER

ARRAY

SOURCE

HV

COMMAND

DATA

DECODER

COMMAND

DATA LATCH

I/O BUFFER

PGM

DATA

HV

PROGRAM

DATA LAT CH

SENSE

AMPLIFIER

Q0-Q15/A-1

A0-A19

CE

OE

WE

RESET

28

Pin

No.

Pin Name I/O

Function

28 XOUT O X’tal osc. connecting output terminal

29 XIN I X’tal osc. connection, external clock input terminal (24.576MHz or 12.288MHz)

30 DVDD — Digital power

31 DGND — Digital GND

32 EMPHA/UO I/O Emphasis information/U-data output/Chip address setting terminal

33 AUDIO/VO I/O Non-PCM detect/V-flag output/ Chip address setting terminal

34 CKST I/O Clock switch transition period output/Demodulation master or slave function switching ter minal

35 INT I/O Interrupt output for ∝com (Interrupt factor selectable)/Modulation or general I/O switching terminal

36 RERR O PLL lock error, data error flag output

37 DO O ∝com I/F, read out data output terminal (3-state)

38 DI I ∝com I/F, write data input terminal

39 CE I ∝com I/F, chip enable input terminal

40 CL I ∝com I/F, clock input terminal

41 XMODE I System reset input terminal

42 DGND — Digital GND

43 DVDD — Digital power

44 TMCK/PIO0 I/O 256fs system clock input for modulation/General I/O in/output terminal

45 TBCK/PIO1 I/O 64fs bit clock input for modulation/General I/O in/output terminal

46 TLRCK/PIO2 I/O fs clock input for modulation/General I/O in/output terminal

47 TDATA/PIO3 I/O Serial audio data input for modulation/General I/O in/output terminal

48 TXO/PIOEN O/I Modulation data output/ General I/O enable input terminal

* For latch-up countermeasure, perform each power supply ON/OFF in the same timing.

MX29LV160ABTC-70 (ME: U10))

1

A15

2

A14

3

A13

4

A12

5

A11

6

A10

7

A9

8

A8

9

A19

10

NC

11

WE

12

RESET

13

NC

14

NC

15

RY/BY

A18

A17

A7

A6

A5

A4

A3

A2

A1

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

A16

BYTE

GND

Q15/A-1

Q7

Q14

Q6

Q13

Q5

Q12

Q4

VCC

Q11

Q3

Q10

Q2

Q9

Q1

Q8

Q0

OE

GND

CE

A0

BLOCK DIAGLAM

28

Page 29

BH7862FS (AP: IC202)

ADV-M71

29

01CTRAP

02MUTE1 MUTE1

CIN

03

04GND

05YIN

06VCC

07GND

08PYIN

09GND

10PYTRAP

11VCC

12PbIN

13GND

14PrIN

15MUTE2

1.5-6M

20k

CLAMP

CLAMP

20k

20k

MUTE2

BPF

12M

LPF

6M

LPF

6M

LPF

6M

LPF

6dB

6dB

6dB

6dB

6dB

75ohm

75ohm

75ohm

75ohm

75ohm

TEST

32

31

30

29

28

27

22

21

20

19

18

COUT

TEST

MIXOUT

MIXFB

GND

YTRAP

GND26

YOUT25

YFB24

GND23

PYOUT

PYFB

GND

PbOUT

N.C.

16PrTRAP

6dB

75ohm

BH7862FS Terminal Function

Pin No.

Port

1 CTRAP

10 PYTRAP

16 PrTRAP

Pin for LC resonation

27 YTRAP

2 MUTE1 Mute control pin, L: C, MIX, Y simultaneous mute

3 CIN

12 PbIN Signal input pin, chroma signal & color-difference signal

14 PrIN

4, 7, 9, 13, 20, 23, 26, 28

GND GND pin

5 YIN Signal input pin, luminance signal

8 PYIN

6

11 Power supply for PY, Pb, Pr

VCC

Power supply for C, MIX, Y

15 MUTE2 Mute control pin, L: PY, Pb, Pr simultaneous mute

17 PrOUT

19 PbOUT

Signal output pin, color-difference signal

18 N.C.

21 PYFB

22 PYOUT

24 YFB

25 YOUT

29 MIXFB

30 MIXOUT

Signal output pin, luminance signal (progressive)

Signal output pin, luminance signal (interlace)

Signal output pin, Y/C MIX signal

31 TEST TEST pin

32 COUT Signal output pin, chroma signal

Description

17

PrOUT

29

Page 30

AT49F001N-70JC (ME: U3)

A12

A15

A16

432

5

A7

6

A6

7

A5

8

A4

9

A3

10

A2

11

A1

12

A0

13

I/O0

14151617181920

I/O1

I/O2

GND

*Note: This pin is a DC on the AT49F001N(T).

FAN8024BDTF (ME: U6)

RESET *

VCCWENC

1

323130

I/O3

I/O4

I/O5

29

28

27

26

25

24

23

22

21

I/O6

A14

A13

A8

A9

A11

OE

A10

CE

I/O7

Pin Configurations

Pin Name Function

A0 - A16 Addresses

CE

OE

WE

RESET

I/O0 - I/O7 Data Inputs/Outputs

NC No Connect

DC Don’t Connect

Chip Enable

Output Enable

Write Enable

RESET

ADV-M71

30

STBY

REF

IN4

CAP4.1

CAP4.2

+

7

5

.

-

IN2.2

IN3

K

X

2

67

OUT2

28 27 26 25 24 23 22 21 20 19 18 17 16 15

S

T

D

+

-

+

12345

IN1

K

0

1

K

5

.

-

+

-

K

0

2

K

5

.

7

K

0

1

CAP1.1

7

K

0

2

-

+

7

.

5

K

IN2.1

CAP1.2

VCCGND

FB1

GND

PVCC2

FB4

PGND2

DO3−DO3+

V

P

C

C

2

1

5

K

1

0

K

+

-

2

5

K

C

V

P

V

C

C

89

VCC

-

C

PVCC1

+

1

10 11

PGND1

Loading

Driver

Sled

Driver

−

DO2

V

P

C

V

P

C

V

12

DO2+

X

2

1

0

K

GND

Pin Definitions

Pin Number Pin Name I/O Pin Function Description

1 IN1 I CH1 input

2 CAP1.1 - Connection with capacitor

3 CAP1.2 - for CH1

4 IN2.1 I OP-AMP CH2 input(+)

5 IN2.2 I OP-AMP CH2 input(-)

6 OUT2 O OP-AMP CH2 output

7 FB1 I Feedback for CH1

8 VCC - Signal Vcc

9 PVCC1 - Power Supply 1

10 PGND1 - Power Ground 1

11 D O2

12 DO2+ O Drive2 Output (+)

13 DO1

14 DO1+ O Drive1 Output (+)

15 DO4+ O Drive4 Output (+)

16 DO4

17 DO3+ O Drive3 Output (+)

18 DO3

19 PGND2 - Power Ground 2

20 FB4 - Feedback for CH4

21 PVCC2 - Power Supply 2

22 VCCGND - Vcc ground

23 IN3 I CH3 input

24 CAP4.2 - Connection with capacitor

25 CAP4.1 - for CH4

26 IN4 I CH4 input

27 REF I Bias voltage input

28 STBY I Stand-by input

−

−

−

−

O Drive2 Output (-)

O Drive1 Output (-)

O Drive4 Output (-)

O Drive3 Output (-)

Actuator

Driver

C

1

2

C

C

C

Actuator

Driver

13 14

DO4−DO4+

−

DO1

DO1+

30

Page 31

FAN8423D3TF (ME: U7)

Pin Definitions

Pine Number Pin Name I/O Pin Function Description

1 NC - No connection

2 A3 O Output (A3)

3 NC - No connection

4 A2 O Output (A2)

5 NC - No connection

6 NC - No connection

7 A1 O Output (A1)

8 GND - Ground

9 H1+ I Hall signal (H1+)

10 H1- I Hall signal (H1-)

11 H2+ I Hall signal (H2+)

12 H2- I Hall signal (H2-)

13 H3+ I Hall signal (H3+)

14 H3- I Hall signal (H3-)

15 VH I Hall bias

16 NC - No connection

17 PC1 - Phase compensation capacitor

18 SB I Short brake

19 FG3X O FG waveform (3X)

20 DIR O Rotational direction output

21 ECR I Output current control reference

22 EC I Output current control voltage

23 S/S I Power save (Start/Stop switch)

24 FG1X O FG waveform (1X)

25 VCC - Supply voltage (Signal)

26 NC - No connection

27 VM - Supply voltage (Motor)

28 CS1 - Output current detection

GND

CS1

VM

NC

VCC

28 27 26 25 24 23 22 21 20 19 18 17 16 15

1234567

A3

NC

NC

FG1X

FG1X

A2

NC

EC

S/S

-

Stop

Start

Generator

Current Sense

Amp

A1

NC

GND

+

Absolute

Values

Output

Current Limit

ECR

DIR

FG3X

SB

Short

Brake

FG3X

Generator

tion

Logic

Reverse Rota-

tor

tion

Direc-

Upper

Lower

Distribu-

Distribu-

8

GND

Detec-

Selector

Commutation

91011121314

H1+

Hall Amp

H1-

H2+

PC1

NC

TSD

H2-

H3+

ADV-M71

VH

Hall

H3-

31

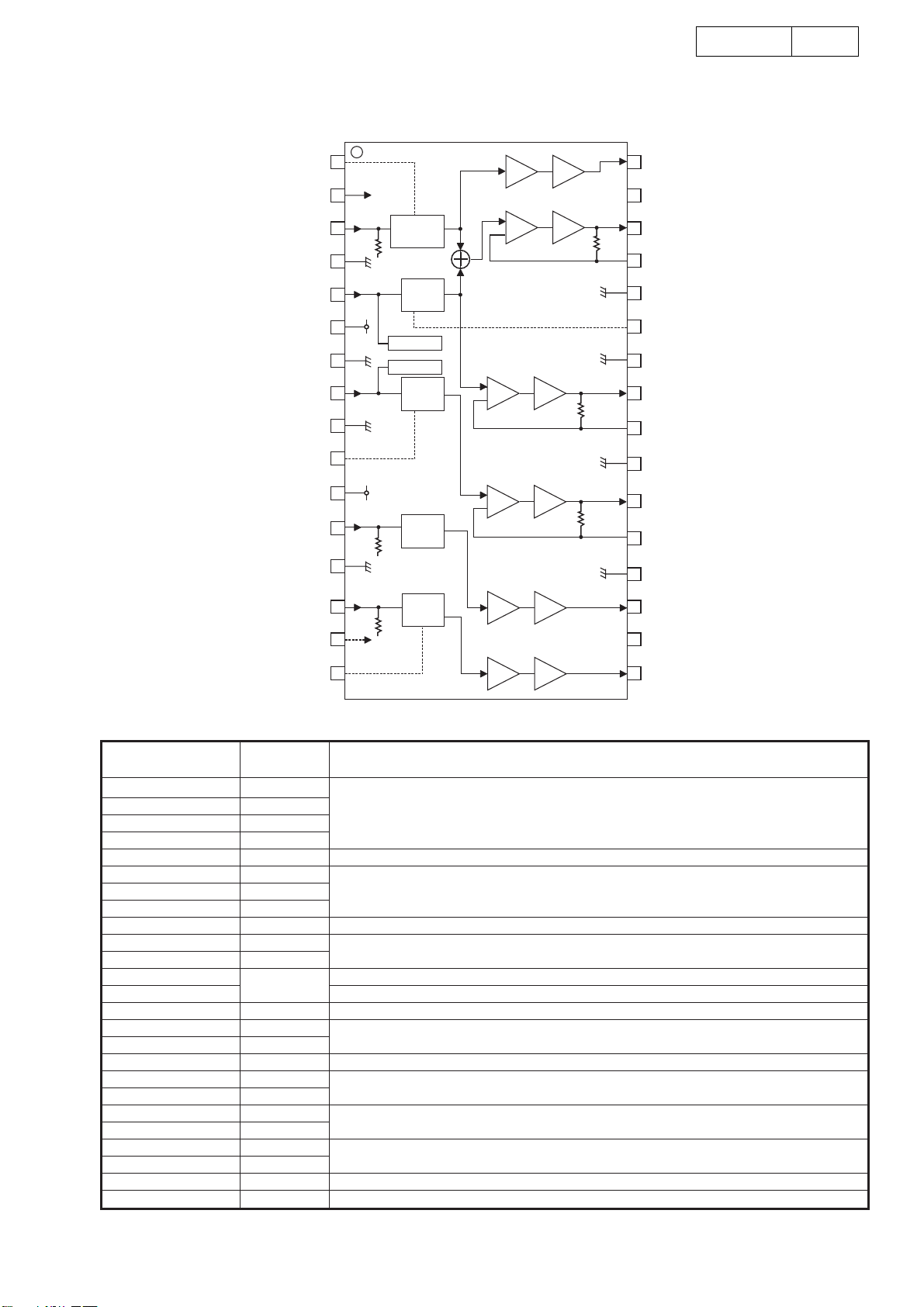

SN74HCT244APW (MA: IC304)

SN74LV244APW (MA: IC708)

logic symbol Function Table

INPUTS OUTPUT

GA Y

LH H

LL L

HX Z

31

Page 32