Page 1

^1 HARDWARE REFERENCE MANUAL

^2 TURBO PMAC2 VME

^3 Programmable Multi-Axis Controller

^4 4Ax-602413-xHxx

^5 May 26, 2004

Single Source Machine Control Power // Flexibility // Ease of Use

21314 Lassen Street Chatsworth, CA 91311 // Tel. (818) 998-2095 Fax. (818) 998-7807 // www.deltatau.com

Page 2

Copyright Information

© 2003 Delta Tau Data Systems, Inc. All rights reserved.

This document is furnished for the customers of Delta Tau Data Systems, Inc. Other uses are

unauthorized without written permission of Delta Tau Data Systems, Inc. Information contained

in this manual may be updated from time-to-time due to product improvements, etc., and may not

conform in every respect to former issues.

To report errors or inconsistencies, call or email:

Delta Tau Data Systems, Inc. Technical Support

Phone: (818) 717-5656

Fax: (818) 998-7807

Email: support@deltatau.com

Website: http://www.deltatau.com

Operating Conditions

All Delta Tau Data Systems, Inc. motion controller products, accessories, and amplifiers contain

static sensitive components that can be damaged by incorrect handling. When installing or

handling Delta Tau Data Systems, Inc. products, avoid contact with highly insulated materials.

Only qualified personnel should be allowed to handle this equipment.

In the case of industrial applications, we expect our products to be protected from hazardous or

conductive materials and/or environments that could cause harm to the controller by damaging

components or causing electrical shorts. When our products are used in an industrial

environment, install them into an industrial electrical cabinet or industrial PC to protect them

from excessive or corrosive moisture, abnormal ambient temperatures, and conductive materials.

If Delta Tau Data Systems, Inc. products are exposed to hazardous or conductive materials and/or

environments, we cannot guarantee their operation.

Page 3

Turbo PMAC2 VME Hardware Reference

Table of Contents

INTRODUCTION.....................................................................................................................................................1

Board Configuration....................................................................................................................................................1

Base Version............................................................................................................................................................1

Option 1: Additional Four Channels Axis Interface Circuitry...............................................................................1

Option 2: Dual-Ported RAM..................................................................................................................................2

Option 5: CPU and Memory Configurations.........................................................................................................2

Option 7: Plate Mounting.......................................................................................................................................2

Option 8: High-Accuracy Clock Crystal ................................................................................................................2

Option 9: Serial Port Configuration ......................................................................................................................2

Option 10: Firmware Version Specification ..........................................................................................................3

Option 12: Analog-to-Digital Converters ..............................................................................................................3

Option 16: Battery-Backed Parameter Memory.....................................................................................................3

Option 18: Identification Number and Real Time Clock/Calendar Module ..........................................................3

CPU BOARD E-POINT DESCRIPTIONS.............................................................................................................5

E1: Watchdog Disable Jumper...................................................................................................................................5

E2-E3: Expansion Port Configure..............................................................................................................................5

E4 – E6: Power-Up/Reset Load Source .....................................................................................................................5

E7: Firmware Reload Enable......................................................................................................................................5

BOTTOM BOARD E-POINT JUMPER DESCRIPTIONS..................................................................................7

E1: Servo and Phase Clock Direction Control ...........................................................................................................7

E2: (Reserved for Future Use)....................................................................................................................................7

E3: Normal/Re-Initializing Power-Up/Reset..............................................................................................................7

E4 – E6: (Reserved for Future Use) ...........................................................................................................................7

E7A-H, E8A-H, E9A-H, E10A-H: P2 Connector B-Row Use Select........................................................................7

E11 – E12: Compare Output Supply Voltage Configure...........................................................................................8

E13 - E14: Encoder Sample Clock Direction Control................................................................................................8

E17 - E18: Serial Connector Select............................................................................................................................8

E20A-I: DPRAM Byte Order Control........................................................................................................................9

E39: Reset-from-Bus Enable......................................................................................................................................9

OPTION 1V PIGGYBACK JUMPER DESCRIPTION......................................................................................11

JP1-1 to JP1-32: P2A Connector B-Row Use Select ...............................................................................................11

E14: SCLK Direction Control..................................................................................................................................11

MATING CONNECTORS.....................................................................................................................................13

CPU Board Connectors .............................................................................................................................................13

J2 (JEXP)/Expansion.............................................................................................................................................13

J4 (JDPRAM)/Dual-Ported RAM..........................................................................................................................13

Base Board Connectors .............................................................................................................................................13

J1 (JANA)/Analog (Option 12)..............................................................................................................................13

J2 (JTHW)/Multiplexer Port..................................................................................................................................13

J3 (JIO)/Digital I/O...............................................................................................................................................13

J4 (JMACRO)/Macro Digital Data.......................................................................................................................13

J5 (JRS232)/RS-232 Serial Communications........................................................................................................13

J5A (JRS422)/RS-422 Serial Communications......................................................................................................13

J6 (JDISP)/Display................................................................................................................................................13

J7 (JHW)/Auxiliary Channel.................................................................................................................................14

J8 (JEQU)/Position Compare ...............................................................................................................................14

J9 (JMACH1)/Machine Port 1 ..............................................................................................................................14

J10 (JMACH2)/Machine Port 2 ............................................................................................................................14

P1 (PVME)/Main VME Bus Connector.................................................................................................................14

P2 (PMACH)/Alternate Machine Port/Extended VME.........................................................................................14

Table of Contents

i

Page 4

Turbo PMAC -VME Hardware Reference

Option 1V Axis Piggyback Connectors.....................................................................................................................14

J11 (JMACH3)/ Machine Port 3 ...........................................................................................................................14

J12 (JMACH4)/ Machine Port 4 ...........................................................................................................................14

P2A (PMACHA)/Alternate Machine Port .............................................................................................................14

BASE BOARD CONNECTOR PINOUTS............................................................................................................15

J1 (JANA) Analog Input Port Connector..................................................................................................................15

J2 (JTHW) Multiplexer Port Connector....................................................................................................................16

J3 (JI/O) General Input/Output Connector................................................................................................................17

J4 (JMACRO) MACRO Network Ring Interface Connector....................................................................................18

J5 (JRS232) Serial Port Connector............................................................................................................................18

J5A: RS422 Serial Port Connector............................................................................................... .............................19

J6 (JDISP) Display Connector...................................................................................................................................20

J7 (JHW) Handwheel Encoder Connector ................................................................................................................20

J8 (JEQU) Position Compare Output Connector.......................................................................................................21

J9 (JMACH1) Machine Connector............................................................................................................................21

J10 (JMACH2) Machine Connector..........................................................................................................................24

P1 (JVME) VME Bus Connector..............................................................................................................................27

P2 (JMACHA) Alternate Machine Connector ..........................................................................................................28

TB1 (2/4-Pin Terminal Block) ..................................................................................................................................29

TB2 (4-Pin Terminal Block)......................................................................................................................................29

AXIS PIGGYBACK BOARD CONNECTOR DESCRIPTIONS.......................................................................31

J11 (JMACH3) Machine Connector..........................................................................................................................31

J12 (JMACH4) Machine Connector..........................................................................................................................34

P2A (JMACHB) Alternate Machine Connector........................................................................................................37

ii Table of Contents

Page 5

Turbo PMAC2 VME Hardware Reference

INTRODUCTION

The Turbo PMAC2 VME is a member of the Turbo PMAC family of boards optimized for interface to

sinewave or direct PWM servo drives and to pulse-and-direction stepper drives. Its software is capable of

32 axes of control. It can have up to eight channels of on-board axis interface circuitry. It can also

support up to 32 channels of off-board axis interface circuitry through its expansion port, connected to

Acc-24P or Acc-24P2 boards.

The Turbo PMAC2 VME is a full-sized ISA-bus expansion card, with a small piggyback board

containing the CPU board. This piggyback board occupies part of the next slot, but ½-sized boards are

permitted in this next slot. While the Turbo PMAC2 VME is capable of ISA bus communications, with

or without the optional on-board dual-ported RAM, it does not need to be inserted into an ISA expansion

slot. Communications can be done through an RS-232 or optional RS-422 serial port; standalone

operation is possible.

Board Configuration

Base Version

The base version of the Turbo PMAC2 VME provides a 2-slot board with:

• 80 MHz DSP56303 CPU (120 MHz PMAC equivalent)

• 128k x 24 SRAM compiled/assembled program memory (5C0)

• 128k x 24 SRAM user data memory (5C0)

• 1M x 8 flash memory for user backup & firmware (5C0)

• Latest released firmware version

• RS-232 serial interface, VME bus interface

• 1 16-node MACRO interface IC

• Four channels axis interface circuitry, each including:

• Three output command signal sets, configurable as either:

Two serial data streams to external DACs, 1 pulse-and-direction

Three PWM top-and-bottom pairs

• 3-channel differential/single-ended encoder input

• Nine input flags, two output flags

• Interface to two external serial ADCs, 8 to 18 bits

• Two channels supplemental interface circuitry, each including:

• 2-channel differential/single-ended encoder input

• One output command signal set, configurable as pulse-and-direction or

PWM top-and-bottom pair

• Display, MACRO, muxed I/O, direct I/O interface ports

• PID/notch/feedforward servo algorithms

• Extended "pole-placement" servo algorithms

• 1-year warranty from date of shipment

• One manual per set of one to four PMACs in shipment

(Cables, mounting plates, mating connectors not included)

Option 1: Additional Four Channels Axis Interface Circuitry

• Option 1V provides an additional four channels of axis interface circuitry on a small piggyback

board, identical to the standard first four channels on the base board.

Introduction 1

Page 6

Turbo PMAC2 VME Hardware Reference

Option 2: Dual-Ported RAM

Dual-ported RAM provides a high speed communications path for bus communications with the host

computer through a bank of shared memory. DPRAM is advised if more than about 100 data items per

second are to be passed between the controller and the host computer in either direction.

Option 2V provides an 8k x 16 bank of dual-ported RAM. The key component on the board is U87.

Option 5: CPU and Memory Configurations

The various versions of Option 5 provide different CPU speeds and main memory sizes on the piggyback

CPU board. Only one Option 5xx may be selected for the board.

The CPU is a DSP5630x IC as component U1. Currently, it is available only as an 80 MHz device (with

computational power equivalent to a 120 MHz non-Turbo PMAC), but higher speed versions will be

available shortly.

The compiled/assembled-program memory SRAM ICs are located in U14, U15, and U16. These ICs

form the active memory for the firmware, compiled PLCs, and user-written phase/servo algorithms.

These can be 128k x 8 ICs (for a 128k x 24 bank), fitting in the smaller footprint, or they can be the larger

512k x 8 ICs (for a 512k x 24 bank), fitting in the full footprint.

The user-data memory SRAM ICs are located in U11, U12, and U13. These ICs form the active memory

for user motion programs, uncompiled PLC programs, and user tables and buffers. These can be 128k x 8

ICs (for a 128k x 24 bank), fitting in the smaller footprint, or they can be the larger 512k x 8 ICs (for a

512k x 24 bank), fitting in the full footprint.

The flash memory IC is located in U10. This IC forms the non-volatile memory for the board’s firmware,

the user setup variables, and for user programs, tables, and buffers. It can be 1M x 8, 2M x 8, or 4M x 8

in capacity.

• Option 5C0 is the standard CPU and memory configuration. It is provided automatically if no Option

5xx is specified. It provides an 80 MHz CPU (120 MHz PMAC equivalent), 128k x24 of

compiled/assembled program memory, 128k x 24 of user data memory; and a 1M x 8 flash memory.

• Option 5C1 provides an 80 MHz CPU (120 MHz PMAC equivalent), 128k x 24 of

compiled/assembled program memory, an expanded 512k x 24 of user data memory, and a 2M x 8

flash memor y.

• Option 5C2 provides an 80 MHz CPU (120 MHz PMAC equivalent), an expanded 512k x 24 of

compiled/assembled program memory, 128k x 24 of user data memory, and a 2M x 8 flash memory.

• Option 5C3 provides an 80 MHz CPU (120 MHz PMAC equivalent), an expanded 512k x 24 of

compiled/assembled program memory, an expanded 512k x 24 of user data memory, and a 4M x 8

flash memor y.

Option 7: Plate Mounting

• Option 7 provides a mounting plate connected to the PMAC with standoffs. It is used to install the

PMAC in standalone applications.

Option 8: High-Accuracy Clock Crystal

The Turbo PMAC2 VME has a clock crystal (component Y1) of nominal frequency 19.6608 MHz (~20

MHz). The standard crystal’s accuracy specification is +/-100 ppm.

• Option 8A provides a nominal 19.6608 MHz crystal with a +/-15 ppm accuracy specification.

Option 9: Serial Port Configuration

The Turbo PMAC2 VME comes standard with a single serial port, which can be used in either RS-232 or

RS-422 format. Optionally, a second independent serial port may be added.

2 Introduction

Page 7

Turbo PMAC2 VME Hardware Reference

• Option 9T adds an auxiliary RS-232 port on the CPU piggyback board. The key components added

are IC U22 and connector J8 on the CPU board.

Option 10: Firmware Version Specification

Normally, the Turbo PMAC2 VME is provided with the newest released firmware version. A label on

the U10 flash memory IC shows the firmware version loaded at the factory.

• Option 10 provides for a user-specified firmware version.

Option 12: Analog-to-Digital Converters

Option 12 permits the installation of 8 or 16 channels of on-board multiplexed analog-to-digital

converters. One or two of these converters are read every phase interrupt. The analog inputs are not

optically isolated, and each can have a 0 – 5V input range, or a +/-2.5V input range, individually

selectable.

• Option 12 provides an 8-channel 12-bit A/D converter. The key components on the board are U28

and connector J1.

• Option 12A provides an additional 8-channel 12-bit A/D converter. The key component on the board

is U29.

Option 16: Battery-Backed Parameter Memory

The contents of the standard memory are not retained through a power-down or reset unless they have

been saved to flash memory first. Option 16 provides supplemental battery-backed RAM for real-time

parameter storage that is ideal for holding machine state parameters in case of an unexpected powerdown. The battery is located at component BT1.

• Option 16A provides a 32k x 24 bank of battery-backed parameter RAM in components U17, U18,

and U19 on the CPU board, fitting in the smaller footprint for those locations.

• Option 16B provides a 128k x 24 bank of battery-backed parameter RAM in components U17, U18,

and U19 on the CPU board, filling the full footprint for those locations.

Option 18: Identification Number and Real Time Clock/Calendar Module

Option 18 provides a module at location U5 on the CPU board that contains an electronic identification

number and possibly a real-time clock/calendar.

• Option 18A provides an electronic identification number module.

• Option 18B provides an electronic identification number module with a real-time clock and calendar.

The year representation in the calendar is a 4-digit value, so there are no Year 2000 problems.

Introduction 3

Page 8

Turbo PMAC2 VME Hardware Reference

4 Introduction

Page 9

Turbo PMAC2 VME Hardware Reference

CPU BOARD E-POINT DESCRIPTIONS

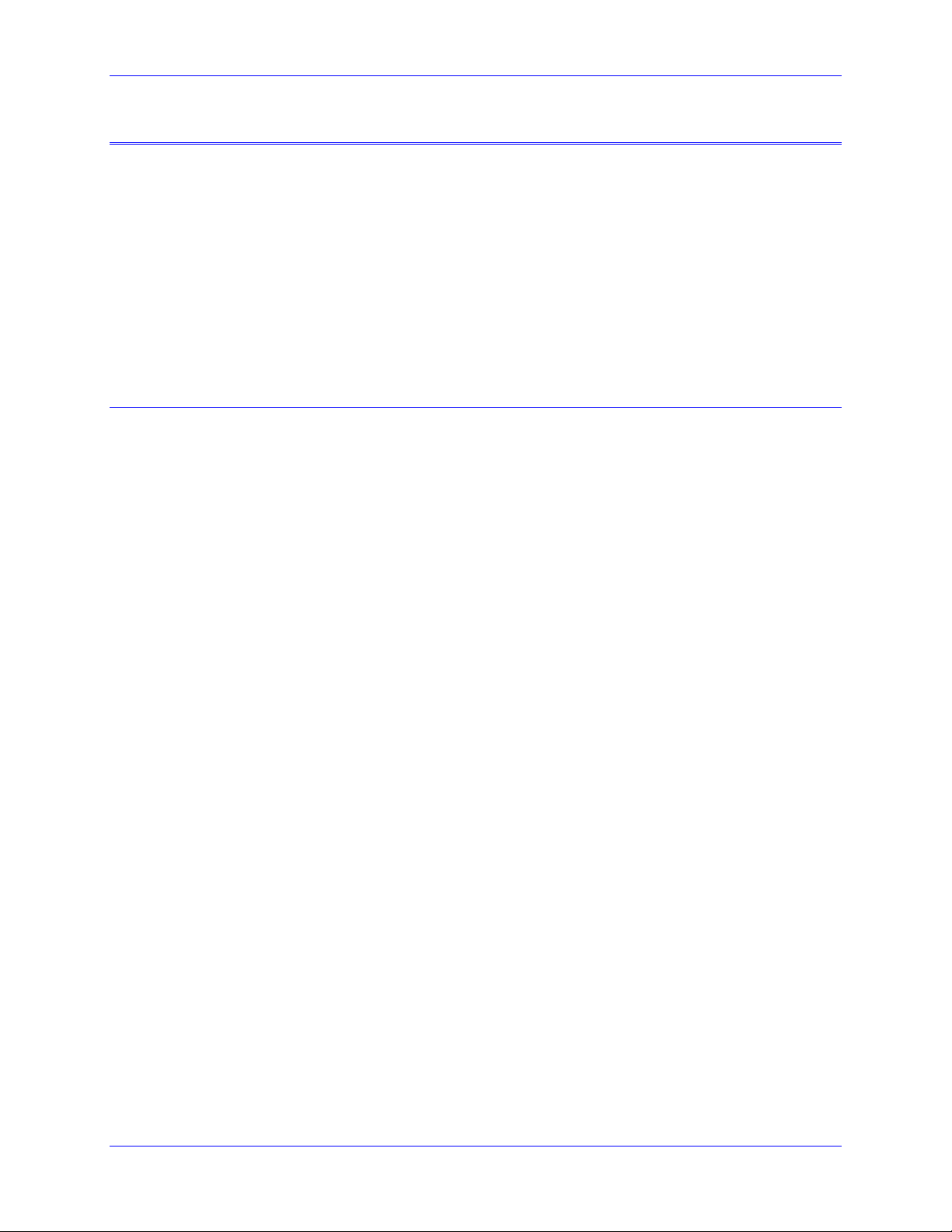

E1: Watchdog Disable Jumper

E Point and

Description Default

Physical Layout

E1

Jump pin 1 to 2 to disable Watchdog timer (for test purposes

only).

Remove jumper to enable Watchdog timer.

No jumper installed

E2-E3: Expansion Port Configure

(Prototype boards {-104 and earlier} only)

E Point and

Description Default

Physical Layout

E2

E3

Note: Production versions of the Turbo CPU board are built with circuit traces providing the equivalent of E2

and E3 ON. To use with an Option 2 DPRAM board, pins 41 and 42 on the 50-pin connector of the Option 2

board must be clipped in order to be able to operate properly. All Option 2 boards built since Turbo PMAC

production began have been built with these pins clipped.

Jump pin 1 to 2 to permit use of Acc-24 expansion boards.

Remove jumper to permit use of unmodified (pin 41 intact)

Option 2 DPRAM board

Jump pin 1 to 2 to permit use of Acc-24 expansion boards.

Remove jumper to permit use of unmodified (pin 42 intact)

Option 2 DPRAM board

Jumper installed

Jumper installed

E4 – E6: Power-Up/Reset Load Source

E Point and

Physical Layout

E4

E6

Remove jumper E4;

jump E5 pin 1 to 2;

jump E6 pin 2 to 3;

to read flash IC on power-up/reset.

Other combinations are for factory use only; the board will not

operate in any other configuration

E7: Firmware Reload Enable

E Point and

Physical Layout

E7

Jump pin 1 to 2 to reload firmware through serial or bus port

Remove jumper for normal operation.

Description Default

No E4 jumper

installed;

E5 and E6 jump pin

1 to 2

Description Default

No jumper installed

CPU Board E-Point Descriptions 5

Page 10

Turbo PMAC2 VME Hardware Reference

6 CPU Board E-Point Descriptions

Page 11

Turbo PMAC2 VME Hardware Reference

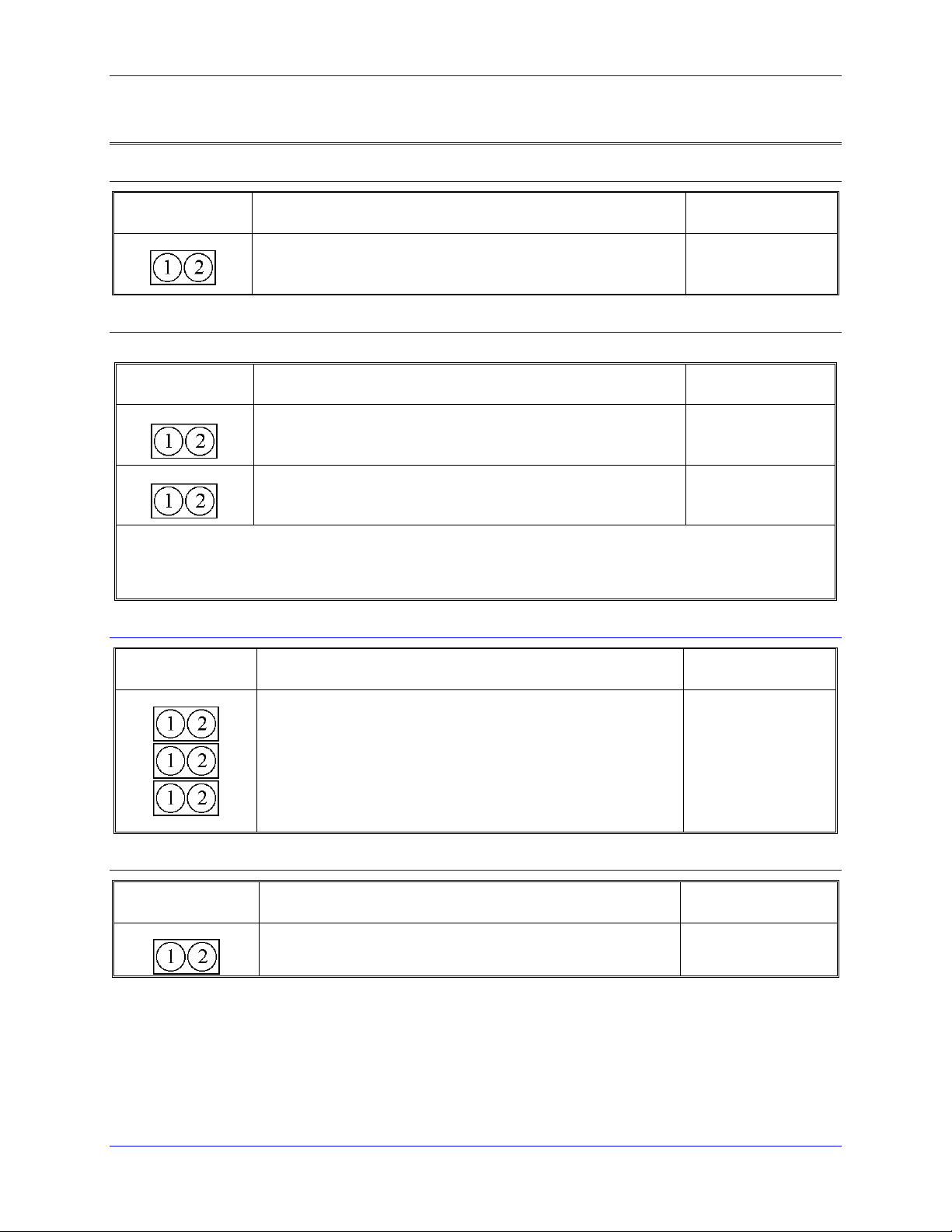

BOTTOM BOARD E-POINT JUMPER DESCRIPTIONS

E1: Servo and Phase Clock Direction Control

E Point and

Description Default

Physical Layout

E1

Note: If the E1 jumper is ON and the servo and phase clocks are not brought in on the J4 serial port, the

watchdog timer will trip immediately.

Remove jumper for Turbo PMAC2 VME to use its internally

generated servo and phase clock signals and to output these

signals on the J5x serial port connector

Jump pins 1 and 2 for Turbo PMAC2 VME to expect to receive its

servo and phase clock signals on the J5x serial port connector.

No jumper

E2: (Reserved for Future Use)

E3: Normal/Re-Initializing Power-Up/Reset

E Point and

Physical Layout

E51

Location Description Default

A2 Jump pin 1 to 2 to re-initialize ON power-up/reset.

Remove jumper for Normal power-up/reset.

No jumper installed

E4 – E6: (Reserved for Future Use)

E7A-H, E8A-H, E9A-H, E10A-H: P2 Connector B-Row Use Select

E Point and

Location Description Default

Physical Layout

E7A-H

E8A-H

E9A-H

E10A-H

Note: All jumpers in the E7 to E10 families must be in the same setting.

Jump pins 1 to 2 to use B-row of P2 connector for

JMACH pins (not compatible with 32-bit VME).

Jump pins 2 to 3 to use B-row of P2 connector for 32-

bit VME bus interface

Jump pins 1 to 2 to use B-row of P2 connector for

JMACH pins (not compatible with 32-bit VME).

Jump pins 2 to 3 to use B-row of P2 connector for 32-

bit VME bus interface.

Jump pins 1 to 2 to use B-row of P2 connector for

JMACH pins (not compatible with 32-bit VME).

Jump pins 2 to 3 to use B-row of P2 connector for 32-

bit VME bus interface.

Jump pins 1 to 2 to use B-row of P2 connector for

JMACH pins (not compatible with 32-bit VME).

Jump pins 2 to 3 to use B-row of P2 connector for 32-

bit VME bus interface.

1-2 Jumpers installed

1-2 Jumpers installed

1-2 Jumpers installed

1-2 Jumpers installed

(32-bit VME)

Bottom Board E-Point Jumper Descriptions 7

Page 12

Turbo PMAC2 VME Hardware Reference

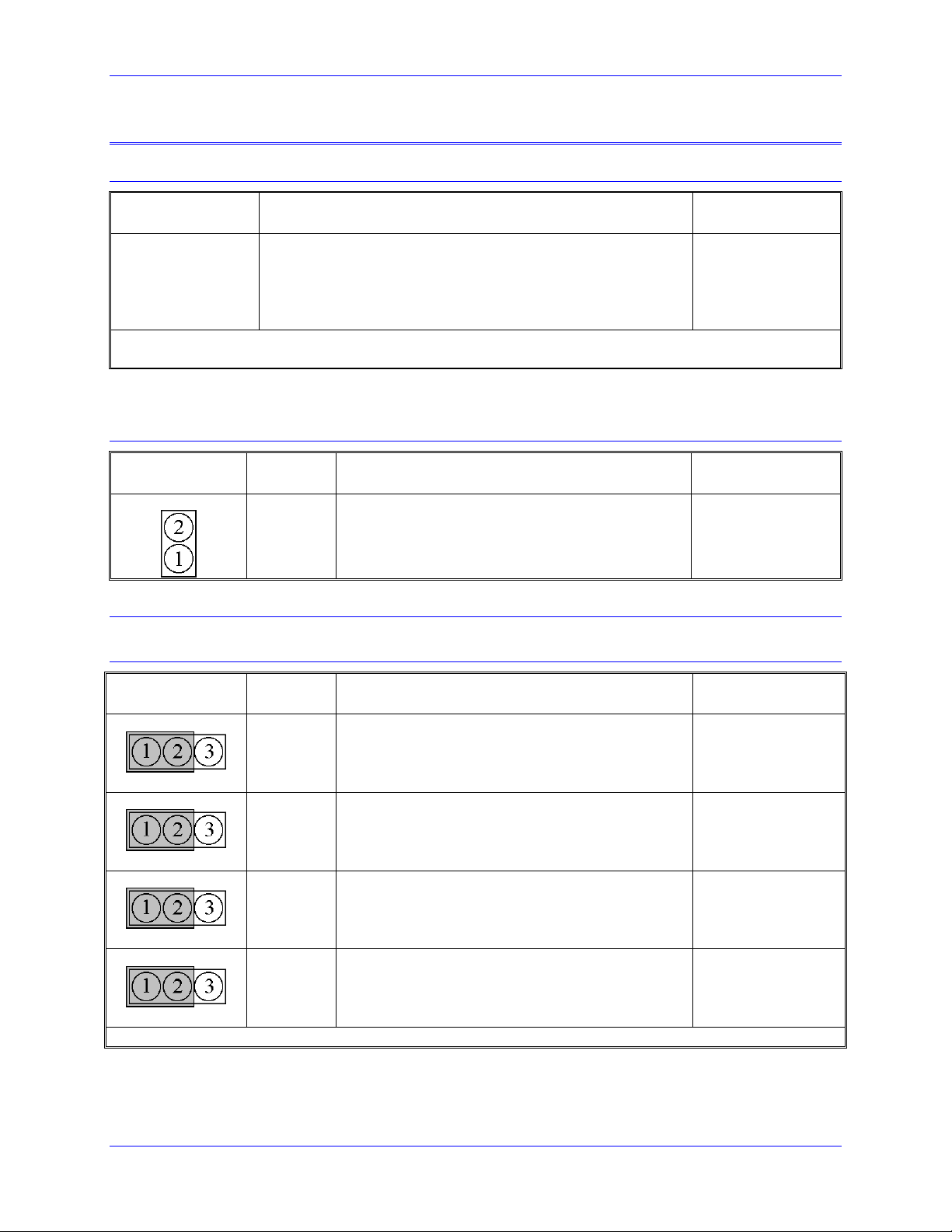

E11 – E12: Compare Output Supply Voltage Configure

E Point and

Location Description Default

Physical Layout

E11

D3 Jump pin 1 to 2 to apply +V (+5V to 24V) to pin 11

of U74 (should be ULN2803A for sink output

configuration) JEQU Compare outputs EQU1-EQU8.

Jump pin 2 to 3 to apply GND to pin 11 of U74

(should be UDN2981A for source output

configuration).

WARNING:

The jumper setting must match the type of driver

IC, or damage to the IC will result.

E12

C3 Jump pin 1 to 2 to apply GND to pin 10 of U74

(should be ULN2803A for sink output configuration).

Jump pin 2 to 3 to apply +V (+5V to 24V) to pin 10

of U74 (should be UDN2981A for source output

configuration).

WARNING:

The jumper setting must match the type of driver

IC, or damage to the IC will result.

E13 - E14: Encoder Sample Clock Direction Control

1-2 Jumper installed

1-2 Jumper installed

E Point and

Location Description Default

Physical Layout

E13

Remove jumper to output SCLK generated in first

ASIC on SCLK_12 and SCLK_34, or to control

direction by software.

Jump pins 1 to 2 to input SCLK signal for first ASIC

on SCLK_34 and output this signal on SCLK_12.

Jump pins 2 to 3 to input SCLK signal for first ASIC

on SCLK_12 and output this signal on SCLK_34.

E17 - E18: Serial Connector Select

E17 and E18 control whether the RS-232 or RS-422 serial port is used.

E Point and

Physical Layout

E17

E18

Location Description Default

Jump pins 1 to 2 to use RS-232 serial interface.

Jump pins 2 to 3 to use RS-422 serial interface.

Jump pins 1 to 2 to use RS-232 serial interface.

Jump pins 2 to 3 to use RS-422 serial interface.

No jumper installed

1-2 Jumper installed

1-2 Jumper installed

8 Bottom Board E-Point Jumper Descriptions

Page 13

Turbo PMAC2 VME Hardware Reference

E20A-I: DPRAM Byte Order Control

E Point and

Location Description Default

Physical Layout

E20A-I

5 (4 3) (2 1)

5 (4 3) (2 1)

5 (4 3) (2 1)

5 (4 3) (2 1)

5 (4 3) (2 1)

5 (4 3) (2 1)

5 (4 3) (2 1)

5 (4 3) (2 1)

5 (4 3) (2 1)

All E20A-I jumpers must be in the same setting for DPRAM communications to work.

Jump pins 1 to 2 and pins 3 to 4, to tie DPRAM data

lines 8-15 to VMEbus data lines 8-15, and DPRAM

data lines 0-7 to VMEbus data lines 0-7 (Motorola

big-endian format).

Jump pins 2 to 3 and pins 4 to 5 to tie DPRAM data

lines 8-15 to VMEbus data lines 0-7, and DPRAM

data lines 0-7 to VMEbus data lines 8-15 (Intel littleendian format).

E39: Reset-from-Bus Enable

E Point and

Physical Layout

E39

Location Description Default

B5 Jump pin 1 to 2 to permit VMEbus reset line to reset

PMAC2.

Remove jumper so VMEbus reset line does not reset

PMAC2.

1-2, 3-4 Jumpers

installed (Motorola

format)

1-2 Jumper installed

Bottom Board E-Point Jumper Descriptions 9

Page 14

Turbo PMAC2 VME Hardware Reference

10 Bottom Board E-Point Jumper Descriptions

Page 15

Turbo PMAC2 VME Hardware Reference

OPTION 1V PIGGYBACK JUMPER DESCRIPTION

JP1-1 to JP1-32: P2A Connector B-Row Use Select

(Option 1V only)

E Point and

Location Description Default

Physical Layout

JP1-1 to JP1-32

• • •

Jump pins 1 to 2 to use B-row of P2A connector for

JMACH pins (not compatible with 32-bit VME).

Remove jumpers to leave B-row of P2A unconnected

to prevent contention with 32-bit VMEbus.

E14: SCLK Direction Control

(Option 1V only)

E Point and

Physical Layout

E14

Location Description Default

Remove jumper to output SCLK generated in second

ASIC on SCLK_56 and SCLK_78, or to control

direction by software.

Jump pins 1 to 2 to input SCLK signal for second

ASIC on SCLK_78 and output this signal on

SCLK_56.

Jump pins 2 to 3 to input SCLK signal for second

ASIC on SCLK_56 and output this signal on

SCLK_78.

1-2 Jumpers

installed

No jumper installed

Option 1V Piggyback Jumper Description 11

Page 16

Turbo PMAC2 VME Hardware Reference

12 Option 1V Piggyback Jumper Description

Page 17

Turbo PMAC2 VME Hardware Reference

MATING CONNECTORS

CPU Board Connectors

J2 (JEXP)/Expansion

1. Two 50-pin female flat cable connector Delta Tau P/N 014-R00F50-0K0 T&B Ansley P/N 609-5041

2. 171-50 T&B Ansley standard flat cable stranded 50-wire

3. Phoenix varioface module type FLKM 50 (male pins) P/N 22 81 08 9 used for daisy chaining Acc14 I/0, -23 A and D connectors -24 expansion

J4 (JDPRAM)/Dual-Ported RAM

1. Two 10-pin female flat cable connector Delta Tau P/N 014-ROOF10-0K0 T&B Ansley P/N 609-1041

2. 171-10 T&B Ansley standard flat cable stranded 10-wire

3. Phoenix varioface module type FLKM 10 (male pins) P/N 22 81 01 8

Base Board Connectors

J1 (JANA)/Analog (Option 12)

1. Two 14-pin female flat cable connector Delta Tau P/N 014-R00F14-0K0 T&B Ansley P/N 609-1441

2. 171-14 T&B Ansley standard flat cable stranded 14-wire

3. Phoenix varioface modules type FLKM14 (male pins) P/N 22 81 02 1

J2 (JTHW)/Multiplexer Port

1. Two 26-pin female flat cable connector Delta Tau P/N 014-R00F26-0K0 T&B Ansley P/N 609-2641

2. 171-26 T&B Ansley standard flat cable stranded 26-wire

3. Phoenix varioface module type FLKM 26 (male pins) P/N 22 81 05 0

J3 (JIO)/Digital I/O

1. Two 40-pin female flat cable connector Delta Tau P/N 014-R00F40-0K0 T&B Ansley P/N 609-4041

2. 171-40 T&B Ansley standard flat cable stranded 40-wire

3. Phoenix varioface module type FLKM 40 (male pins)

J4 (JMACRO)/Macro Digital Data

1. Two 26-pin female flat cable connector Delta Tau P/N 014-R00F26-0K0 T&B Ansley P/N 609-2641

2. 171-26 T&B Ansley standard flat cable stranded 26-wire

3. Phoenix varioface module type FLKM 26 (male pins) P/N 22 81 05 0

J5 (JRS232)/RS-232 Serial Communications

1. Two 10-pin female flat cable connector Delta Tau P/N 014-ROOF10-0K0 T&B Ansley P/N 609-1041

2. 171-10 T&B Ansley standard flat cable stranded 10-wire

3. Phoenix varioface module type FLKM 10 (male pins) P/N 22 81 01 8

J5A (JRS422)/RS-422 Serial Communications

1. Two 26-pin female flat cable connector Delta Tau P/N 014-R00F26-0K0 T&B Ansley P/N 609-2641

2. 171-26 T&B Ansley standard flat cable stranded 26-wire

3. Phoenix varioface module type FLKM 26 (male pins) P/N 22 81 05 0

J6 (JDISP)/Display

1. Two 14-pin female flat cable connector Delta Tau P/N 014-R00F14-0K0 T&B Ansley P/N 609-1441

2. 171-14 T&B Ansley standard flat cable stranded 14-wire

3. Phoenix varioface modules type FLKM14 (male pins) P/N 22 81 02 1

Mating Connectors 13

Page 18

Turbo PMAC2 VME Hardware Reference

J7 (JHW)/Auxiliary Channel

1. Two 20-pin female flat cable connector Delta Tau P/N 014-R00F20-0K0 T&B Ansley P/N 609-2041

2. 171-20 T&B Ansley standard flat cable stranded 20-wire

3. Phoenix varioface modules type FLKM20 (male pins)

J8 (JEQU)/Position Compare

1. Two 10-pin female flat cable connector Delta Tau P/N 014-ROOF10-0K0 T&B Ansley P/N 609-1041

2. 171-10 T&B Ansley standard flat cable stranded 10-wire

3. Phoenix varioface module type FLKM 10 (male pins) P/N 22 81 01 8

J9 (JMACH1)/Machine Port 1

1. Two 100-pin high-density flat-cable connector

2. High-density flat cable stranded 100-wire

J10 (JMACH2)/Machine Port 2

1. Two 100-pin high-density flat-cable connector

2. High-density flat cable stranded 100-wire

P1 (PVME)/Main VME Bus Connector

1. 96-pin VME/DIN connector AMLAN P/N C96F3LA+B+C

P2 (PMACH)/Alternate Machine Port/Extended VME

1. 96-pin VME/DIN connector AMLAN P/N C96F3LA+B+C

Option 1V Axis Piggyback Connectors

J11 (JMACH3)/ Machine Port 3

1. Two 100-pin high-density flat-cable connector

2. High-density flat cable stranded 100-wire

J12 (JMACH4)/ Machine Port 4

1. Two 100-pin high-density flat-cable connector

2. High-density flat cable stranded 100-wire

P2A (PMACHA)/Alternate Machine Port

1. 96-pin VME/DIN connector. AMLAN P/N C96F3LA+B+C

14 Mating Connectors

Page 19

Turbo PMAC2 VME Hardware Reference

BASE BOARD CONNECTOR PINOUTS

J1 (JANA) Analog Input Port Connector

(Present only if Option 12 ordered)

Pin # Symbol Function Description Notes

1 ANAI00 Input Analog Input 0 0-5V or +/-2.5V Range

2 ANAI01 Input Analog Input 1 0-5Vor +/-2.5V Range

3 ANAI02 Input Analog Input 2 0-5V or +/-2.5V Range

4 ANAI03 Input Analog Input 3 0-5V or +/-2.5V Range

5 ANAI04 Input Analog Input 4 0-5V or +/-2.5V Range

6 ANAI05 Input Analog Input 5 0-5V or +/-2.5V Range

7 ANAI06 Input Analog Input 6 0-5V or +/-2.5V Range

8 ANAI07 Input Analog Input 7 0-5V or +/-2.5V Range

9 ANAI08 Input Analog Input 8 0-5V or +/-2.5V Range

10 ANAI09 Input Analog Input 9 0-5V or +/-2.5V Range

11 ANAI10 Input Analog Input 10 0-5V or +/-2.5V Range

12 ANAI11 Input Analog Input 11 0-5V or +/-2.5V Range

13 ANAI12 Input Analog Input 12 0-5V or +/-2.5V Range

14 ANAI13 Input Analog Input 13 0-5V or +/-2.5V Range

15 ANAI14 Input Analog Input 14 0-5V or +/-2.5V Range

16 ANAI15 Input Analog Input 15 0-5V or +/-2.5V Range

17 GND Common PMAC Common Not isolated from digital

18 +12V Output Positive Supply Voltage To power external circuitry

19 GND Common PMAC Common Not isolated from digital

20 -12V Output Negative Supply Voltage To power external circuitry

The JANA connector provides the inputs for the 8 or 16 optional analog inputs on the PMAC2.

Base Board Connector Pinouts 15

Page 20

Turbo PMAC2 VME Hardware Reference

J2 (JTHW) Multiplexer Port Connector

Pin # Symbol Function Description Notes

1 GND Common PMAC Common

2 GND Common PMAC Common

3 DAT0 Input Data-0 Input Data input from MUX port accessories

4 SEL0 Output Select-0 Output Address/data output for MUX port

5 DAT1 Input Data-1 Input Data input from MUX port accessories

6 SEL1 Output Select-1 Output Address/data output for MUX port

7 DAT2 Input Data-2 Input Data input from MUX port accessories

8 SEL2 Output Select-2 Output Address/data output for MUX port

9 DAT3 Input Data-3 Input Data input from MUX port accessories

10 SEL3 Output Select-3 Output Address/data output for MUX port

11 DAT4 Input Data-4 Input Data input from MUX port accessories

12 SEL4 Output Select-4 Output Address/data output for MUX port

13 DAT5 Input Data-5 Input Data input from MUX port accessories

14 SEL5 Output Select-5 Output Address/data output for MUX port

15 DAT6 Input Data-6 Input Data input from MUX port accessories

16 SEL6 Output Select-6 Output Address/data output for MUX port

17 DAT7 Input Data-7 Input Data input from MUX port accessories

18 SEL7 Output Select-7 Output Address/data output for MUX port

19 N.C. N.C. No Connection

20 GND Common PMAC Common

21 BRLD/ Output Buffer Request Low is Buffer Request

22 GND Common PMAC Common

23 IPLD/ Output In Position Low is In Position

24 GND Common PMAC Common

25 +5V Output +5Vdc Supply Power supply out

26 INIT/ Input PMAC Reset Low is Reset

The JTHW connector provides eight inputs and eight outputs at TTL levels; these are dedicated to reading BCD

thumbwheel switches. Two thumbwheels may be read by direct connection to J3, more thumbwheels, up to 512

switches, may be read using the Acc-18 (Thumbwheel Multiplexer). J3’s inputs and outputs may be used as

general purpose multiplexed TTL I/O, if thumbwheels are not used.

accessories

accessories

accessories

accessories

accessories

accessories

accessories

accessories

16 Base Board Connector Pinouts

Page 21

Turbo PMAC2 VME Hardware Reference

J3 (JI/O) General Input/Output Connector

Pin # Symbol Function Description Notes

1 I/O00 In/Out Digital I/O 0 Software direction ctrl.

2 I/O01 In/Out Digital I/O 1 Software direction ctrl.

3 I/O02 In/Out Digital I/O 2 Software direction ctrl.

4 I/O03 In/Out Digital I/O 3 Software direction ctrl.

5 I/O04 In/Out Digital I/O 4 Software direction ctrl.

6 I/O05 In/Out Digital I/O 5 Software direction ctrl.

7 I/O06 In/Out Digital I/O 6 Software direction ctrl.

8 I/O07 In/Out Digital I/O 7 Software direction ctrl.

9 I/O08 In/Out Digital I/O 8 Software direction ctrl.

10 I/O09 In/Out Digital I/O 9 Software direction ctrl.

11 I/O10 In/Out Digital I/O 10 Software direction ctrl.

12 I/O11 In/Out Digital I/O 11 Software direction ctrl.

13 I/O12 In/Out Digital I/O 12 Software direction ctrl.

14 I/O13 In/Out Digital I/O 13 Software direction ctrl.

15 I/O14 In/Out Digital I/O 14 Software direction ctrl.

16 I/O15 In/Out Digital I/O 15 Software direction ctrl.

17 I/O16 In/Out Digital I/O 16 Software direction ctrl.

18 I/O17 In/Out Digital I/O 17 Software direction ctrl.

19 I/O18 In/Out Digital I/O 18 Software direction ctrl.

20 I/O19 In/Out Digital I/O 19 Software direction ctrl.

21 I/O20 In/Out Digital I/O 20 Software direction ctrl.

22 I/O21 In/Out Digital I/O 21 Software direction ctrl.

23 I/O22 In/Out Digital I/O 22 Software direction ctrl.

24 I/O23 In/Out Digital I/O 23 Software direction ctrl.

25 I/O24 In/Out Digital I/O 24 Software direction ctrl.

26 I/O25 In/Out Digital I/O 25 Software direction ctrl.

27 I/O26 In/Out Digital I/O 26 Software direction ctrl.

28 I/O27 In/Out Digital I/O 27 Software direction ctrl.

29 I/O28 In/Out Digital I/O 28 Software direction ctrl.

30 I/O29 In/Out Digital I/O 29 Software direction ctrl.

31 I/O30 In/Out Digital I/O 30 Software direction ctrl.

32 I/O31 In/Out Digital I/O 31 Software direction ctrl.

33 GND Common Reference Voltage

34 GND Common Reference Voltage

35 PHASE/ Output Phase Clock For latching data

36 SERVO/ Output Servo Clock For latching data

37 GND Common Reference Voltage

38 GND Common Reference Voltage

39 +5V Output Supply Voltage To power external circuitry

40 +5V Output Supply Voltage To power external circuitry

The JI/O connector provides 32 input/output pins at TTL levels. Direction can be controlled in byte-wide groups.

Base Board Connector Pinouts 17

Page 22

Turbo PMAC2 VME Hardware Reference

J4 (JMACRO) MACRO Network Ring Interface Connector

Pin # Symbol Function Description Notes

1 DOUT7 Output Ring Out Bit 7 Macro ring command

2 DOUT6 Output Ring Out Bit 6 Macro ring transmit

3 DOUT5 Output Ring Out Bit 5 Macro ring transmit

4 DOUT4 Output Ring Out Bit 4 Macro ring transmit

5 DOUT3 Output Ring Out Bit 3 Macro ring transmit

6 DOUT2 Output Ring Out Bit 2 Macro ring transmit

7 DOUT1 Output Ring Out Bit 1 Macro ring transmit

8 DOUT0 Output Ring Out Bit 0 Macro ring transmit

9 CMD_IN Input

10 DIN7 Input Ring In Bit 7 Macro ring receive

11 DIN6 Input Ring In Bit 6 Macro ring receive

12 DIN5 Input Ring In Bit 5 Macro ring receive

13 DIN4 Input Ring In Bit 4 Macro ring receive

14 DIN3 Input Ring In Bit 3 Macro ring receive

15 DIN2 Input Ring In Bit 2 Macro ring receive

16 DIN1 Input Ring In Bit 1 Macro ring receive

17 DIN0 Input Ring In Bit 0 Macro ring receive

18 CMD_OUT Output

19 TCLK Output Ring Clock 10mHz

20 GND Common Reference Voltage

21 STB_OUT Output Byte Strobe

22 GND Common Reference Voltage

23 DAT_STB Input Data Byte Strobe

24 GND Common Reference Voltage

25 CMD_STB Input CMD Byte Strobe

26 VLTN Input Violation Flag Taxi chip receive error

The JMACRO connector provides the interface to the MACRO driver/receiver accessory board.

J5 (JRS232) Serial Port Connector

Pin # Symbol Function Description Notes

1 PHASE Output Phasing Clock

2 DTR Bidirect Data Term Ready Tied to DSR

3 TXD/ Input Receive Data Host transmit data

4 CTS Input Clear to Send Host ready bit

5 RXD/ Output Send Data Host receive data

6 RTS Output Request to Send PMAC ready bit

7 DSR Bidirect Data Set Ready Tied to DTR

8 SERVO Output Servo Clock

9 GND Common PMAC Common

10 +5V Output +5Vdc Supply Power supply out

The JRS232 connector provides the Turbo PMAC2 VME with the ability to communicate serially with an RS232

port. Jumpers E17 and E18 must both connect pins 1 and 2 to use this port. This connector cannot be used for

daisy chain interconnection of multiple PMACs. The J5A RS-422 port is required for daisy chaining.

18 Base Board Connector Pinouts

Page 23

Turbo PMAC2 VME Hardware Reference

J5A: RS422 Serial Port Connector

JRS422 (26-Pin Connector)

Front View

Pin # Symbol Function Description Notes

1 CHASSI Common PMAC Common

2 S+5V Output +5Vdc Supply Deactivated by E8

3 RD- Input Receive Data Diff. I/O low true **

4 RD+ Input Receive Data Diff. I/O high true *

5 SD- Output Send Data Diff. I/O low true **

6 SD+ Output Send Data Diff. I/O high true *

7 CS+ Input Clear to Send Diff. I/O high true **

8 CS- Input Clear to Send Diff. I/O low true *

9 RS+ Output Request to Send Diff. I/O high true **

10 RS- Output Request to Send Diff. I/O low true *

11 DTR Bidirect Data Term Read Tied to DSR

12 INIT/ Input PMAC Reset Low is Reset

13 GND Common PMAC Common **

14 DSR Bidirect Data Set Ready Tied to DTR

15 SDIO- Bidirect Special Data Diff. I/O low true

16 SDIO+ Bidirect Special Data Diff. I/O high true

17 SCIO- Bidirect Special Ctrl. Diff. I/O low true

18 SCIO+ Bidirect Special Ctrl. Diff. I/O high true

19 SCK- Bidirect Special Clock Diff. I/O low true

20 SCK+ Bidirect Special Clock Diff. I/O high true

21 SERVO- Bidirect Servo Clock Diff. I/O low true ***

22 SERVO+ Bidirect Servo Clock Diff. I/O high true ***

23 PHASE- Bidirect Phase Clock Diff. I/O low true ***

24 PHASE+ Bidirect Phase Clock Diff. I/O high true ***

25 GND Common PMAC Common

26 +5V Output +5Vdc Supply Power supply out

The JRS422 connector provides the PMAC with the ability to communicate both in RS422 and RS232. In addition,

this connector is used to daisy chain interconnect multiple PMACs for synchronized operation. Jumpers E17 and

E18 must both connect pins 2 and 3 to use this port.

Base Board Connector Pinouts 19

Page 24

Turbo PMAC2 VME Hardware Reference

J6 (JDISP) Display Connector

Pin # Symbol Function Description Notes

1 Vdd Output +5V Power Power supply out

2 Vss Common PMAC Common

3 Rs Output Read Strobe TTL signal out

4 Vee Output Contrast Adjust Vee 0 to +5Vdc *

5 E Output Display Enable High is enable

6 R/W Output Read or Write TTL signal out

7 DB1 Output Display Data1

8 DB0 Output Display Data0

9 DB3 Output Display Data3

10 DB2 Output Display Data2

11 DB5 Output Display Data5

12 DB4 Output Display Data4

13 DB7 Output Display Data7

14 DB6 Output Display Data6

The JDISP connector is used to drive the 2-line x 24-character (Acc-12), 2 x 40 (Acc-12A) LCD, or the 2 x 40

vacuum fluorescent (Acc 12C) display unit. The DISPLAY command may be used to send messages and values to

the display.

J7 (JHW) Handwheel Encoder Connector

Pin # Symbol Function Description Notes

1 GND Common Reference Voltage

2 +5V Output Supply Voltage To power external circuitry

3 HWA1+ Input HW Pos A Chan. Also pulse input

4 HWA1- Input HW Neg A Chan. Also pulse input

5 HWB1+ Input HW Pos B Chan. Also direction input

6 HWB1- Input HW Neg B Chan. Also direction input

7 HWA2+ Input HW Pos A Chan. Also pulse input

8 HWA2- Input HW Neg A Chan. Also pulse input

9 HWB2+ Input HW Pos B Chan. Also direction input

10 HWB2- Input HW Neg B Chan. Also direction input

11 PUL1+ Output PFM Pos Pulse Also PWM output

12 PUL1- Output PFM Neg Pulse Also PWM output

13 DIR1+ Output PFM Pos Dir. Out Also PWM output

14 DIR1- Output PFM Neg Dir Out Also PWM output

15 PUL2+ Output PFM Pos Pulse Also PWM output

16 PUL2- Output PFM Neg Pulse Also PWM output

17 DIR2+ Output PFM Pos Dir. Out Also PWM output

18 DIR2- Output PFM Neg Dir Out Also PWM output

19 GND Common Reference Voltage

20 +5V Output Supply Voltage To power external circuitry

20 Base Board Connector Pinouts

Page 25

Turbo PMAC2 VME Hardware Reference

J8 (JEQU) Position Compare Output Connector

Pin # Symbol Function Description Notes

1 EQU1/ Output Enc. 1 Comp-Eq Low is true

2 EQU2/ Output Enc. 2 Comp-Eq Low is true

3 EQU3/ Output Enc. 3 Comp-Eq Low is true

4 EQU4/ Output Enc. 4 Comp-Eq Low is true

5 EQU5/ Output Enc. 5 Comp-Eq Low is true

6 EQU6/ Output Enc. 6 Comp-Eq Low is true

7 EQU7/ Output Enc. 7 Comp-Eq Low is true

8 EQU8/ Output Enc. 8 Comp-Eq Low is true

9 +V Supply Positive Supply +5V to +24V

10 GND Common Digital Ground

This connector provides the position-compare outputs for the eight encoder channels.

J9 (JMACH1) Machine Connector

J9 (JMACH1) Machine Connector

____________ __________

99 | ooooooooooo … oooooooooo | 1

100 | ooooooooooo … oooooooooo

| 2

Pin # Symbol Function Description Notes

1 +5V Output / Input +5V Power For external circuit or from external

supply

2 +5V Output / Input +5V Power "

3 GND Common Reference Voltage

4 GND Common Reference Voltage

5 CHA1+ Input Enc 1 Positive A Chan. Also pulse input

6 CHA1- Input Enc 1 Negative A Chan. "

7 CHB1+ Input Enc 1 Positive B Chan. Also direction input

8 CHB1- Input Enc 1 Negative B Chan. "

9 CHC1+ Input Enc 1 Positive C Chan. Index channel

10 CHC1- Input Enc 1 Negative C Chan. "

11 CHU1 Input Chan 1 U Flag Hall effect, fault code, or sub-count

12 CHV1 Input Chan 1 V Flag Hall effect, fault code, or sub-count

13 CHW1 Input Chan 1 W Flag Hall effect, fault code, or sub-count

14 CHT1 Input Chan 1 T Flag Fault code, or sub-count

15 USER1 Input General Purpose User Flag Hardware capture flag, or sub-count

16 PLIM1 Input Positive Overtravel Limit Hardware capture flag

17 MLIM1 Input Negative Overtravel Limit Hardware capture flag

18 HOME1 Input Home Switch Input Hardware capture flag

19 ACCFLT1 Input Accessory Fault Flag For loss of acc supply voltage

20 WD0/ Output Watchdog Output Low is PMAC watchdog fault

21 SCLK12+ Input / Output Encoder Sample Clock Direction controlled by PMAC2 jumper

22 SCLK12- Input / Output Encoder Sample Clock Direction controlled by PMAC2 jumper

23 ADC_CLK1+ Output A/D Converter Clock Programmable frequency

24 ADC_CLK1- Output A/D Converter Clock Programmable frequency

25 ADC_STB1+ Output A/D Converter Strobe Programmable sequence

26 ADC_STB1- Output A/D Converter Strobe Programmable sequence

27 ADC_DAA1+ Input Chan A ADC Serial Data MSB first

28 ADC_DAA1- Input Chan A ADC Serial Data MSB first

29 ADC_DAB1+ Input Chan B ADC Serial Data MSB first

30 ADC_DAB1- Input Chan B ADC Serial Data MSB first

Base Board Connector Pinouts 21

Page 26

Turbo PMAC2 VME Hardware Reference

J9 (JMACH1) Machine Connector

(Continued)

____________ __________

99 | ooooooooooo … oooooooooo | 1

100 | ooooooooooo … oooooooooo

| 2

Pin # Symbol Function Description Notes

31 AENA1+ Output Amplifier Enable High is enable

32 AENA1- Output Amplifier Enable Low is enable

33 FAULT1+ Input Amplifier Fault Programmable polarity

34 FAULT1- Input Amplifier Fault Programmable polarity

35 PWMATOP1+

DAC_CLK1+

36 PWMATOP1-

DAC_CLK1-

37 PWMABOT1+

DAC1A+

38 PWMABOT1-

DAC1A-

39 PWMBTOP1+

DAC_STB1+

40 PWMBTOP1-

DAC_STB1-

41 PWMBBOT1+

DAC1B+

42 PWMBBOT1-

DAC1B-

43 PWMCTOP1+

DIR1+

44 PWMCTOP1-

DIR1-

45 PWMCBOT1+

PULSE1+

46 PWMCBOT1-

PULSE147 GND Common Reference Voltage

48 GND Common Reference Voltage

49 +5V Output / Input +5v Power For external circuit or from external

50 +5V Output / Input +5v Power For external circuit or from external

51 +5V Output / Input +5v Power For external circuit or from external

52 +5V Output / Input +5v Power For external circuit or from external

53 GND Common Reference Voltage

54 GND Common Reference Voltage

55 CHA2+ Input Enc 2 Positive A Chan. Also pulse input

56 CHA2- Input Enc 2 Negative A Chan. Also pulse input

57 CHB2+ Input Enc 2 Positive B Chan. Also direction input

58 CHB2- Input Enc 2 Negative B Chan. Also direction input

59 CHC2+ Input Enc 2 Positive C Chan. Index channel

60 CHC2- Input Enc 2 Negative C Chan. Index channel

61 CHU2 Input Chan 2 U Flag Hall effect, fault code, or sub-count

62 CHV2 Input Chan 2 V Flag Hall effect, fault code, or sub-count

Output Phase A Top CMD or DAC

Clock

Output Phase A Top CMD or DAC

Clock

Output Phase A Bottom CMD or

DAC A Serial Data

Output Phase A Bottom CMD or

DAC A Serial Data

Output Phase B Top CMD or DAC

Strobe

Output Phase B Top CMD or DAC

Strobe

Output Phase B Bottom CMD or

DAC B Serial Data

Output Phase B Bottom CMD or

DAC B Serial Data

Output Phase B Top CMD or PFM

Direction

Output Phase B Top CMD or PFM

Direction

Output Phase B Bottom CMD or

PFM Pulse

Output Phase B Bottom CMD or

PFM Pulse

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

supply

supply

supply

supply

22 Base Board Connector Pinouts

Page 27

Turbo PMAC2 VME Hardware Reference

J9 (JMACH1) Machine Connector

(Continued)

____________ __________

99 | ooooooooooo … oooooooooo | 1

100 | ooooooooooo … oooooooooo

| 2

Pin # Symbol Function Description Notes

63 CHW2 Input Chan 2 W Flag Hall effect, fault code, or sub-count

64 CHT2 Input Chan 2 T Flag Fault code, or sub-count

65 USER2 Input General Purpose User Flag Hardware capture flag, or sub-count

66 PLIM2 Input Positive Overtravel Limit Hardware capture flag

67 MLIM2 Input Negative Overtravel Limit Hardware capture flag

68 HOME2 Input Home Switch Input Hardware capture flag

69 ACCFLT2 Input Accessory Fault Flag For loss of ACC supply voltage

70 WD0/ Output Watchdog Output Low is PMAC watchdog fault

71 SCLK12+ Input / Output Encoder Sample Clock Direction controlled by PMAC2 jumper

72 SCLK12- Input / Output Encoder Sample Clock Direction controlled by PMAC2 jumper

73 ADC_CLK2+ Output A/D Converter Clock Programmable frequency

74 ADC_CLK2- Output A/D Converter Clock Programmable frequency

75 ADC_STB2+ Output A/D Converter Strobe Programmable sequence

76 ADC_STB2- Output A/D Converter Strobe Programmable sequence

77 ADC_DAA2+ Input Chan A ADC Serial Data MSB first

78 ADC_DAA2- Input Chan A ADC Serial Data MSB first

79 ADC_DAB2+ Input Chan B ADC Serial Data MSB first

80 ADC_DAB2- Input Chan B ADC Serial Data MSB first

81 AENA2+ Output Amplifier Enable High is enable

82 AENA2- Output Amplifier Enable Low is enable

83 FAULT2+ Input Amplifier Fault Programmable polarity

84 FAULT2- Input Amplifier Fault Programmable polarity

85 PWMATOP2+

DAC_CLK2+

86 PWMATOP2-

DAC_CLK2-

87 PWMABOT2+

DAC2A+

88 PWMABOT2-

DAC2A-

89 PWMBTOP2+

DAC_STB2+

90 PWMBTOP2-

DAC_STB2-

91 PWMBBOT2+

DAC2B+

92 PWMBBOT2-

DAC2B-

93 PWMCTOP2+

DIR2+

94 PWMCTOP2-

DIR2-

95 PWMCBOT2+

PULSE2+

96 PWMCBOT2-

PULSE2-

Output Phase A Top CMD or DAC

Clock

Output Phase A Top CMD or DAC

Clock

Output Phase A Bottom CMD or

DAC A Serial Data

Output Phase A Bottom CMD or

DAC A Serial Data

Output Phase B Top CMD or DAC

Strobe

Output Phase B Top CMD or DAC

Strobe

Output Phase B Bottom CMD or

DAC B Serial Data

Output Phase B Bottom CMD or

DAC B Serial Data

Output Phase B Top CMD or PFM

Direction

Output Phase B Top CMD or PFM

Direction

Output Phase B Bottom CMD or

PFM Pulse

Output Phase B Bottom CMD or

PFM Pulse

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Base Board Connector Pinouts 23

Page 28

Turbo PMAC2 VME Hardware Reference

J9 (JMACH1) Machine Connector

(Continued)

____________ __________

99 | ooooooooooo … oooooooooo | 1

100 | ooooooooooo … oooooooooo

| 2

Pin # Symbol Function Description Notes

97 GND Common Reference Voltage

98 GND Common Reference Voltage

99 +5V Output / Input +5V Power For external circuit or from external

supply

100 +5V Output / Input +5V Power For external circuit or from external

supply

The JMACH1 connector provides the interface pins for channels 1 and 2. Usually, it is connected to a breakout

board, such as one of the Acc-8x family of boards, or an application-specific interface board.

Connector: 100-pin male box header with center key, 0050" pitch. AMP part # 1-04068-7 Delta Tau part # 01400010-FPB.

J10 (JMACH2) Machine Connector

J10 (JMACH2) Machine Connector

____________ __________

99 | ooooooooooo … oooooooooo | 1

100 | ooooooooooo … oooooooooo | 2

Pin # Symbol Function Description Notes

1 +5V Output / Input +5V Power For external circuit or from external

supply

2 +5V Output / Input +5V Power For external circuit or from external

supply

3 GND Common Reference Voltage

4 GND Common Reference Voltage

5 CHA3+ Input Enc 3 Positive A Chan. Also pulse input

6 CHA3- Input Enc 3 Negative A Chan. Also pulse input

7 CHB3+ Input Enc 3 Positive B Chan. Also direction input

8 CHB3- Input Enc 3 Negative B Chan. Also direction input

9 CHC3+ Input Enc 3 Positive C Chan. Index channel

10 CHC3- Input Enc 3 Negative C Chan. Index channel

11 CHU3 Input Chan 3 U Flag Hall effect, fault code, or sub-count

12 CHV3 Input Chan 3 V Flag Hall effect, fault code, or sub-count

13 CHW3 Input Chan 3 W Flag Hall effect, fault code, or sub-count

14 CHT3 Input Chan 3 T Flag Fault code, or sub-count

15 USER3 Input General Purpose User Flag Hardware capture flag, or sub-count

16 PLIM3 Input Positive Overtravel Limit Hardware capture flag

17 MLIM3 Input Negative Overtravel Limit Hardware capture flag

18 HOME3 Input Home Switch Input Hardware capture flag

19 ACCFLT3 Input Accessory Fault Flag For loss of acc supply voltage

20 WD0/ Output Watchdog Output Low is PMAC watchdog fault

21 SCLK34+ Input / Output Encoder Sample Clock Direction controlled by PMAC2

jumper

22 SCLK34- Input / Output Encoder Sample Clock Direction controlled by PMAC2

jumper

23 ADC_CLK3+ Output A/D Converter Clock Programmable frequency

24 ADC_CLK3- Output A/D Converter Clock Programmable frequency

25 ADC_STB3+ Output A/D Converter Strobe Programmable sequence

26 ADC_STB3- Output A/D Converter Strobe Programmable sequence

27 ADC_DAA3+ Input Chan A ADC Serial Data MSB first

24 Base Board Connector Pinouts

Page 29

Turbo PMAC2 VME Hardware Reference

J10 (JMACH2) Machine Connector

(Continued)

____________ __________

99 | ooooooooooo … oooooooooo | 1

100 | ooooooooooo … oooooooooo

| 2

Pin # Symbol Function Description Notes

28 ADC_DAA3- Input Chan A ADC Serial Data MSB first

29 ADC_DAB3+ Input Chan B ADC Serial Data MSB first

30 ADC_DAB3- Input Chan B ADC Serial Data MSB first

31 AENA3+ Output Amplifier Enable High is enable

32 AENA3- Output Amplifier Enable Low is enable

33 FAULT3+ Input Amplifier Fault Programmable polarity

34 FAULT3- Input Amplifier Fault Programmable polarity

35 PWMATOP3+

DAC_CLK3+

36 PWMATOP3-

DAC_CLK3-

37 PWMABOT3+

DAC3A+

38 PWMABOT3-

DAC3A-

39 PWMBTOP3+

DAC_STB3+

40 PWMBTOP3-

DAC_STB3-

41 PWMBBOT3+

DAC3B+

42 PWMBBOT3-

DAC3B-

43 PWMCTOP3+

DIR3+

44 PWMCTOP3-

DIR3-

45 PWMCBOT3+

PULSE3+

46 PWMCBOT3-

PULSE347 GND Common Reference Voltage

48 GND Common Reference Voltage

49 +5V Output / Input +5V Power For external circuit or from external

50 +5V Output / Input +5V Power For external circuit or from external

51 +5V Output / Input +5V Power For external circuit or from external

52 +5V Output / Input +5V Power For external circuit or from external

53 GND Common Reference Voltage

54 GND Common Reference Voltage

55 CHA4+ Input Enc 4 Positive A Chan. Also pulse input

56 CHA4- Input Enc 4 Negative A Chan. Also pulse input

57 CHB4+ Input Enc 4 Positive B Chan. Also direction input

58 CHB4- Input Enc 4 Negative B Chan. Also direction input

59 CHC4+ Input Enc 4 Positive C Chan. Index channel

Output Phase A Top CMD or DAC

Clock

Output Phase A Top CMD or DAC

Clock

Output Phase A Bottom CMD or

DAC A Serial Data

Output Phase A Bottom CMD or

DAC A Serial Data

Output Phase B Top CMD or DAC

Strobe

Output Phase B Top CMD or DAC

Strobe

Output Phase B Bottom CMD or

DAC B Serial Data

Output Phase B Bottom CMD or

DAC B Serial Data

Output Phase B Top CMD or PFM

Direction

Output Phase B Top CMD or PFM

Direction

Output Phase B Bottom CMD or

PFM Pulse

Output Phase B Bottom CMD or

PFM Pulse

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

supply

supply

supply

supply

Base Board Connector Pinouts 25

Page 30

Turbo PMAC2 VME Hardware Reference

J10 (JMACH2) Machine Connector

(Continued)

____________ __________

99 | ooooooooooo … oooooooooo | 1

100 | ooooooooooo … oooooooooo

| 2

Pin # Symbol Function Description Notes

60 CHC4- Input Enc 4 Negative C Chan. Index channel

61 CHU4 Input Chan 4 U Flag Hall effect, fault code, or sub-count

62 CHV4 Input Chan 4 V Flag Hall effect, fault code, or sub-count

63 CHW4 Input Chan 4 W Flag Hall effect, fault code, or sub-count

64 CHT4 Input Chan 4 T Flag Fault code, or sub-count

65 USER4 Input General Purpose User Flag Hardware capture flag, or sub-count

66 PLIM4 Input Positive Overtravel Limit Hardware capture flag

67 MLIM4 Input Negative Overtravel Limit Hardware capture flag

68 HOME4 Input Home Switch Input Hardware capture flag

69 ACCFLT4 Input Accessory Fault Flag For loss of acc supply voltage

70 WD0/ Output Watchdog Output Low is PMAC watchdog fault

71 SCLK34+ Input / Output Encoder Sample Clock Direction controlled by PMAC2

jumper

72 SCLK34- Input / Output Encoder Sample Clock Direction controlled by PMAC2

jumper

73 ADC_CLK4+ Output A/D Converter Clock Programmable frequency

74 ADC_CLK4- Output A/D Converter Clock Programmable frequency

75 ADC_STB4+ Output A/D Converter Strobe Programmable sequence

76 ADC_STB4- Output A/D Converter Strobe Programmable sequence

77 ADC_DAA4+ Input Chan A ADC Serial Data MSB first

78 ADC_DAA4- Input Chan A ADC Serial Data MSB first

79 ADC_DAB4+ Input Chan B ADC Serial Data MSB first

80 ADC_DAB4- Input Chan B ADC Serial Data MSB first

81 AENA4+ Output Amplifier Enable High is enable

82 AENA4- Output Amplifier Enable Low is enable

83 FAULT4+ Input Amplifier Fault Programmable polarity

84 FAULT4- Input Amplifier Fault Programmable polarity

85 PWMATOP4+

DAC_CLK4+

86 PWMATOP4-

DAC_CLK4-

87 PWMABOT4+

DAC4A+

88 PWMABOT4-

DAC4A-

89 PWMBTOP4+

DAC_STB4+

90 PWMBTOP4-

DAC_STB4-

91 PWMBBOT4+

DAC4B+

92 PWMBBOT4-

DAC4B-

93 PWMCTOP4+

DIR4+

94 PWMCTOP4-

DIR4-

Output Phase A Top CMD or DAC

Clock

Output Phase A Top CMD or DAC

Clock

Output Phase A Bottom CMD or

DAC A Serial Data

Output Phase A Bottom CMD or

DAC A Serial Data

Output Phase B Top CMD or DAC

Strobe

Output Phase B Top CMD or DAC

Strobe

Output Phase B Bottom CMD or

DAC B Serial Data

Output Phase B Bottom CMD or

DAC B Serial Data

Output Phase B Top CMD or PFM

Direction

Output Phase B Top CMD or PFM

Direction

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

Programmable function control

26 Base Board Connector Pinouts

Page 31

Turbo PMAC2 VME Hardware Reference

J10 (JMACH2) Machine Connector

(Continued)

____________ __________

99 | ooooooooooo … oooooooooo | 1

100 | ooooooooooo … oooooooooo

| 2

Pin # Symbol Function Description Notes

95 PWMCBOT4+

PULSE4+

96 PWMCBOT4-

PULSE497 GND Common Reference Voltage

98 GND Common Reference Voltage

99 +5V Output / Input +5V Power For external circuit or from external

100 +5V Output / Input +5V Power For external circuit or from external

The JMACH2 connector provides the interface pins for channels 3 and 4. Usually, it is connected to a breakout

board, such as one of the Acc-8x family of boards, or an application-specific interface board.

Connector: 100-pin male box header with center key, 0050" pitch. AMP part # 1-04068-7 Delta Tau part # 01400010-FPB.

Output Phase B Bottom CMD or

PFM Pulse

Output Phase B Bottom CMD or

PFM Pulse

Programmable function control

Programmable function control

supply

supply

P1 (JVME) VME Bus Connector

P1 JVME (96-Pin Header)

Front View

Pin # Row A Row B Row C

01 D00 BBSY/ D08

02 D01 BCLR/ D09

03 D02 ACFAIL/ D10

04 D03 B0IN/ D11

05 D04 BG0OUT/ D12

06 D05 BG1IN/ D13

07 D06 BG1OUT/ D14

08 D07 BG2IN/ D15

09 GND BG2OUT/ GND

10 SYSCLK BG3IN/ SYSFAIL/

11 GND BG3OUT/ BERR/

12 DS1/ BR0/ SYSRESET/

13 DS0/ BR1/ LWORD/

14 WRITE/ BR2/ AM5

15 GND BR3/ A23

16 DTACK/ AM0 A22

17 GND AM1 A21

18 AS/ AM2 A20

19 GND AM3 A19

20 IACK/ GND A18

21 IACKIN/ SERCLK A17

22 IACKOUT/ SERDAT/ A16

23 AM4 GND A15

24 A07 IRQ7/ A14

25 A06 IRQ6/ A13

26 A05 IRQ5/ A12

27 A04 IRQ4/ A11

Base Board Connector Pinouts 27

Page 32

Turbo PMAC2 VME Hardware Reference

P1 JVME (96-Pin Header)

Continued

Front View

Pin # Row A Row B Row C

28 A03 IRQ3/ A10

29 A02 IRQ2/ A09

30 A01 IRQ1/ A08

31 -12V +5V STDBY +12V

32 +5V +5V +5V

This is the standard VME connector. It is sufficient for 16-bit or 24-bit addressing, and for 8-bit or 16-bit data. For

32-bit addressing the B-row of P2 must be used as well. PMAC does not support 32-bit data transfers over the bus,

even with the B-row of P2.

If P1 is connected to the VME backplane, PMAC is connected to the +5V supply and GND automatically. In this

case, no other +5V supply should be connected.

P2 (JMACHA) Alternate Machine Connector

The P2 connector provides an alternate path to J9 and J10 for the machine interface connections for

Channels 1-4. Only the positive signals of complementary pairs are brought out on this connector. For

the inputs, the complementary lines are tied to 2.5V on PMAC2. Refer to the J9 and J10 pin descriptions

for more detailed information on each pin.

P2/JMACHA (96-Pin

Header) Continued

Front View

Pin# Row A Row B

(Format A)

01 +5V +5V CHU1 +5V

02 GND GND CHU3 GND

03 CHA1 (Reserved) CHV1 CHA3

04 CHB1 VA24 CHV3 CHB3

05 CHC1 VA25 CHW1 CHC3

06 PLIM1 VA26 CHW3 PLIM3

07 MLIM1 VA27 CHT1 MLIM3

08 HOME1 VA28 CHT3 HOME3

09 AENA1 VA29 USER1 AENA3

10 FAULT1 VA30 USER3 FAULT3

11 PWMATOP1/ DAC_CLK1 VA31 ADC_DAA1 PWMATOP3/ DAC_CLK3

12 PWMABOT1/ DAC1A GND ADC_DAA3 PWMABOT3/ DAC3A

13 PWMBTOP1/ DAC_STB1 +5V ADC_DAB1 PWMBTOP3/ DAC_STB3

14 PWMBBOT1/ DAC1B VD16* ADC_DAB3 PWMBBOT3/ DAC3B

15 PWMCTOP1/ DIR1 VD17* ADC_CLK1234 PWMCTOP3/ DIR3

16 PWMCBOT1/ PULSE1 VD18* ADC_STB1234 PWMCBOT3/ PULSE3

17 CHA2 VD19* SCLK1234 CHA4

18 CHB2 VD20* WD0/ CHB4

19 CHC2 VD21* CHU2 CHC4

20 PLIM2 VD22* CHU4 PLIM4

21 MLIM2 VD23* CHV2 MLIM4

22 HOME2 GND CHV4 HOME4

23 AENA2 VD24* CHW2 AENA4

24 FAULT2 VD25* CHW4 FAULT4

25 PWMATOP2/ DAC_CLK2 VD26* CHT2 PWMATOP4/ DAC_CLK4

Row B

(Format B)

Row C

28 Base Board Connector Pinouts

Page 33

Turbo PMAC2 VME Hardware Reference

P2/JMACHA (96-Pin

Header) Continued

Front View

Pin# Row A Row B

(Format A)

26 PWMABOT2/ DAC2A VD27* CHT4 PWMABOT4/ DAC4A

27 PWMBTOP2/ DAC_STB2 VD28* USER2 PWMBTOP4/ DAC_STB4

28 PWMBBOT2/ DAC2B VD29* USER4 PWMBBOT4/ DAC4B

29 PWMCTOP2/ DIR2 VD30* ADC_DAA2 PWMCTOP4/ DIR4

30 PWMCBOT2/ PULSE2 VD31* ADC_DAA4 PWMCBOT4/ PULSE4

31 GND GND ADC_DAB2 GND

32 +5V +5V ADC_DAB4 +5V

Note: Format A for the B-row will be used if E7A-H, E8A-H, E9A-H, and E10A-H connect pins 2 and 3. This

format must be used for a 32-bit VME system. Format B for the B-row will be used if these jumpers connect pins 1

and 2. This format is not compatible with 32-bit VME systems.

* Not used

Row B

(Format B)

Row C

TB1 (2/4-Pin Terminal Block)

This terminal block can be used to provide the input for the power supply for the circuits on the PMAC2

board when it is not in a bus configuration. When the PMAC2 is in a bus configuration, these supplies

automatically come through the bus connector from the bus power supply; in this case, this terminal block

should not be used.

Pin# Symbol Function Description Notes

1 GND Common Reference Voltage

2 +5V Input Positive Supply Voltage Supplies all PMAC digital circuits

3 +12V Input Positive Supply Voltage +12V to +15V; not required on-board;

used on j1 to supply analog inputs

4 -12V Input Negative Supply Voltage -12V to –15V; required for opt-12 ADCs;

used on J1 to supply analog inputs

Note: Unless Option 12 (Analog-to-Digital Converters) is included on the board, only pins 1 and 2 may be provided

on this terminal block.

TB2 (4-Pin Terminal Block)

This terminal block provides the output for PMAC2’s watchdog timer relay, both normally open and

normally closed contacts.

Pin# Symbol Function Description Notes

1 WD_NC Output Watchdog Relay Out Normally closed

2 COM Input Watchdog Return +V or 0V

3 WD_NO Output Watchdog Relay Out Normally open

4 COM Input Watchdog Return +V or 0V

Note: The normally closed relay contact is open while PMAC2 is operating properly – it has power and the

watchdog timer is not tripped – and closed when the PMAC2 is not operating properly – either it has lost power or

the watchdog timer has tripped. The normally open relay contact is closed while PMAC2 is operating properly and

open when PMAC2 is not operating properly.

Base Board Connector Pinouts 29

Page 34

Turbo PMAC2 VME Hardware Reference

30 Base Board Connector Pinouts

Page 35

Turbo PMAC2 VME Hardware Reference

AXIS PIGGYBACK BOARD CONNECTOR DESCRIPTIONS

J11 (JMACH3) Machine Connector

(Only present if Option 1V ordered)

J11 (JMACH3) Machine Connector

____________ __________

99 | ooooooooooo … oooooooooo | 1

100 | ooooooooooo … oooooooooo

| 2

Pin# Symbol Function Description Notes

1 +5V Output / Input +5V Power For external circuit or from external

supply

2 +5V Output / Input +5V Power For external circuit or from external

supply

3 GND Common Reference Voltage

4 GND Common Reference Voltage

5 CHA5+ Input Enc 5 Pos. A Chan. Also pulse input

6 CHA5- Input Enc 5 Neg. A Chan. Also pulse input

7 CHB5+ Input Enc 5 Pos. B Chan. Also direction input

8 CHB5- Input Enc 5 Neg. B Chan. Also direction input

9 CHC5+ Input Enc 5 Pos. C Chan. Index channel

10 CHC5- Input Enc 5 Neg. C Chan. Index channel

11 CHU5 Input Chan 5 U Flag Hall effect, fault code, or sub-count

12 CHV5 Input Chan 5 V Flag Hall effect, fault code, or sub-count

13 CHW5 Input Chan 5 W Flag Hall effect, fault code, or sub-count

14 CHT5 Input Chan 5 T Flag Fault code, or sub-count

15 USER5 Input General Purpose User Flag Hardware capture flag, or sub-count

16 PLIM5 Input Positive Overtravel Limit Hardware capture flag

17 MLIM5 Input Negative Overtravel Limit Hardware capture flag

18 HOME5 Input Home Switch Input Hardware capture flag

19 ACCFLT5 Input Accessory Fault Flag For loss of ACC supply voltage

20 WD0/ Output Watchdog Output Low is PMAC watchdog fault

21 SCLK56+ Input / Output Encoder Sample Clock Direction controlled by PMAC2 jumper

22 SCLK56- Input / Output Encoder Sample Clock Direction controlled by PMAC2 jumper

23 ADC_CLK5+ Output A/D Converter Clock Programmable frequency

24 ADC_CLK5- Output A/D Converter Clock Programmable frequency

25 ADC_STB5+ Output A/D Converter Strobe Programmable sequence

26 ADC_STB5- Output A/D Converter Strobe Programmable sequence

27 ADC_DAA5+ Input Chan A ADC Serial Data MSB first

28 ADC_DAA5- Input Chan A ADC Serial Data MSB first

29 ADC_DAB5+ Input Chan B ADC Serial Data MSB first

30 ADC_DAB5- Input Chan B ADC Serial Data MSB first

31 AENA5+ Output Amplifier Enable High is enable

32 AENA5- Output Amplifier Enable Low is enable

33 FAULT5+ Input Amplifier Fault Programmable polarity

34 FAULT5- Input Amplifier Fault Programmable polarity

35 PWMATOP5+

DAC_CLK5+

36 PWMATOP5-

DAC_CLK5-

37 PWMABOT5+

DAC5A+

Output Phase A Top CMD or DAC

Clock

Output Phase A Top CMD or DAC

Clock

Output Phase A Bottom CMD or

DAC A Serial Data

Programmable function control

Programmable function control

Programmable function control

Axis Piggyback Board Connector Descriptions 31

Page 36

Turbo PMAC2 VME Hardware Reference

J11 (JMACH3) Machine Connector

(Continued)

____________ __________

99 | ooooooooooo … oooooooooo | 1

100 | ooooooooooo … oooooooooo

| 2

Pin# Symbol Function Description Notes

38 PWMABOT5-

DAC5A-

39 PWMBTOP5+

DAC_STB5+

40 PWMBTOP5-

DAC_STB5-

41 PWMBBOT5+

DAC5B+

42 PWMBBOT5-

DAC5B-

43 PWMCTOP5+

DIR5+

44 PWMCTOP5-

DIR5-

45 PWMCBOT5+

PULSE5+

46 PWMCBOT5-

PULSE547 GND Common Reference Voltage

48 GND Common Reference Voltage

49 +5V Output / Input +5v Power For external circuit or from external

50 +5V Output / Input +5v Power For external circuit or from external

51 +5V Output / Input +5v Power For external circuit or from external

52 +5V Output / Input +5v Power For external circuit or from external

53 GND Common Reference Voltage

54 GND Common Reference Voltage

55 CHA6+ Input Enc 6 Positive A Chan. Also pulse input

56 CHA6- Input Enc 6 Negative A Chan. Also pulse input

57 CHB6+ Input Enc 6 Positive B Chan. Also direction input

58 CHB6- Input Enc 6 Negative B Chan. Also direction input

59 CHC6+ Input Enc 6 Positive C Chan. Index channel

60 CHC6- Input Enc 6 Negative C Chan. Index channel

61 CHU6 Input Chan 6 U Flag Hall effect, fault code, or sub-count

62 CHV6 Input Chan 6 V Flag Hall effect, fault code, or sub-count

63 CHW6 Input Chan 6 W Flag Hall effect, fault code, or sub-count

64 CHT6 Input Chan 6 T Flag Fault code, or sub-count

65 USER6 Input General Purpose User Flag Hardware capture flag, or sub-count

66 PLIM6 Input Positive Overtravel Limit Hardware capture flag

67 MLIM6 Input Negative Overtravel Limit Hardware capture flag

68 HOME6 Input Home Switch Input Hardware capture flag

69 ACCFLT6 Input Accessory Fault Flag For loss of acc supply voltage

70 WD0/ Output Watchdog Output Low is PMAC watchdog fault

Output Phase A Bottom CMD or

DAC A Serial Data

Output Phase B Top CMD or DAC

Strobe

Output Phase B Top CMD or DAC

Strobe

Output Phase B Bottom CMD or

DAC B Serial Data