Page 1

Single Source Machine Control Power // Flexibility // Ease of Use

21314 Lassen Street Chatsworth, CA 91311 // Tel. (818) 998-2095 Fax. (818) 998-7807 // www.deltatau.com

^1 USER MANUAL

^2 Accessory 11E

^3 24 Opto In/24 Opto Out

^4 3AX-603307-XUXX

^5 October 17, 2018

DELTA TAU

Data Systems, Inc.

NEW IDEAS IN MOTION …

Page 2

ACC-11E User Manual

Copyright Information

© 2018 Delta Tau Data Systems, Inc. All rights reserved.

This document is furnished for the customers of Delta Tau Data Systems, Inc. Other uses are

unauthorized without written permission of Delta Tau Data Systems, Inc. Information contained in this

manual may be updated from time-to-time due to product improvements, etc., and may not conform in

every respect to former issues.

To report errors or inconsistencies, call or email:

Delta Tau Data Systems, Inc. Technical Support

Phone: (818) 717-5656

Fax: (818) 998-7807

Email: support@deltatau.com

Website: http://www.deltatau.com

Operating Conditions

All Delta Tau Data Systems, Inc. motion controller products, accessories, and amplifiers contain static

sensitive components that can be damaged by incorrect handling. When installing or handling Delta Tau

Data Systems, Inc. products, avoid contact with highly insulated materials. Only qualified personnel

should be allowed to handle this equipment.

In the case of industrial applications, we expect our products to be protected from hazardous or

conductive materials and/or environments that could cause harm to the controller by damaging

components or causing electrical shorts. When our products are used in an industrial environment, install

them into an industrial electrical cabinet or industrial PC to protect them from excessive or corrosive

moisture, abnormal ambient temperatures, and conductive materials. If Delta Tau Data Systems, Inc.

products are directly exposed to hazardous or conductive materials and/or environments, we cannot

guarantee their operation.

WARNING

A Warning identifies hazards that could result in personal injury

or death. It precedes the discussion of interest.

Caution

A Caution identifies hazards that could result in equipment damage. It

precedes the discussion of interest.

Note

A Note identifies information critical to the user’s understanding or

use of the equipment. It follows the discussion of interest.

Page 3

ACC-11E User Manual

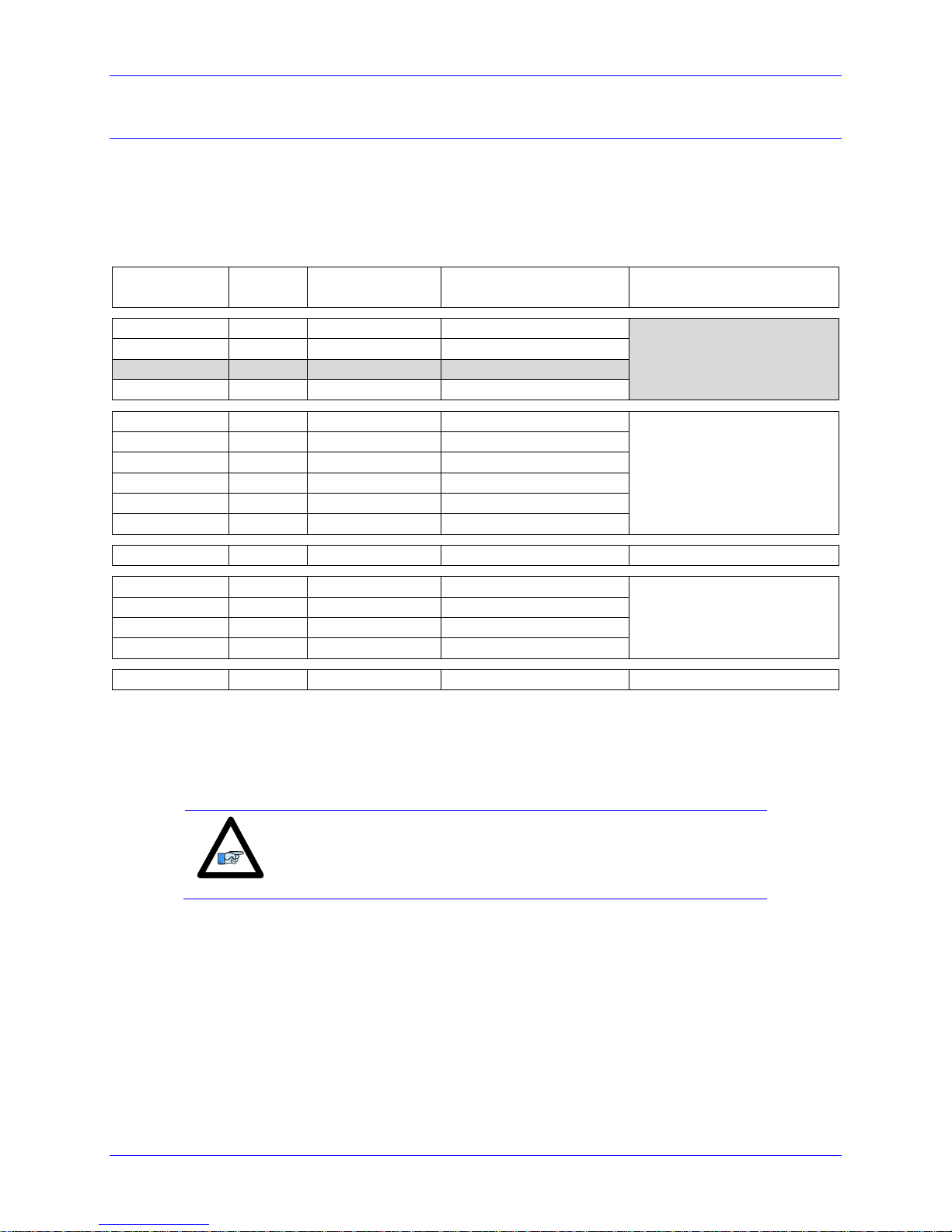

MANUAL REVISION HISTORY

REV.

DESCRIPTION

DATE

CHG.

APPVD

1

ADDED CE DECLARATION

06/07/06

CP

SF

2

REVS. TO J1& J2, PINS 8 & 15, P. 31

05/11/07

CP

AO

3

REVS. TO ELEC. SPECS, P. 3

07/27/07

CP

BP

4

ADDED UL SEAL TO MANUAL COVER

UPDATED AGENCY APPROVAL/SAFETY SECTION

10/01/09

CP

SF

5

REFURBISHED ENTIRE MANUAL

12/17/12

GS

RN

6

ADDED KC CONFORMITY

10/17/18

SM

RN

Page 4

ACC-11E User Manual

Table of Contents 4

Table of Contents

INTRODUCTION......................................................................................................................... 6

SPECIFICATIONS....................................................................................................................... 7

Environmental Specifications ......................................................................................................... 7

Electrical Specifications.................................................................................................................. 7

Physical Specifications ................................................................................................................... 7

Agency Approval and Safety .......................................................................................................... 8

ADDRESSING ACC-11E ............................................................................................................. 9

Turbo/Power UMAC and MACRO Station Jumper Settings ......................................................... 9

Legacy MACRO Station Address Jumper Settings ........................................................................ 9

Sinking or Sourcing Output Select ............................................................................................... 10

I/O Gate Data Clock Select ........................................................................................................... 10

Hardware Address Limitations ..................................................................................................... 11

USING ACC-11E WITH TURBO UMAC ............................................................................... 13

Configuring the Control Word ...................................................................................................... 13

Accessing I/O data points (M-Variables) ..................................................................................... 14

USING ACC-11E WITH POWER UMAC SCRIPT PROGRAMING ................................. 16

Configuring the Control Word ...................................................................................................... 16

Accessing I/O Data Points (Pointers) ........................................................................................... 17

Suggested M-Variables ............................................................................................................ 17

USING ACC-11E WITH POWER UMAC C PROGRAMING ............................................. 18

Setting Up Digital I/O Access....................................................................................................... 18

Function for Setting the Control Word: ACC11E_SetControlWord() ..................................... 18

Function for Reading the State of Inputs: ACC11E_GetInputState() ...................................... 19

Function for Reading the State of Outputs: ACC11E_GetOutputState()................................. 19

Function for Writing to Outputs: ACC11E_SetOutputState() ................................................. 20

Header and Source File ........................................................................................................... 22

User Written Functions ............................................................................................................ 26

Setting Up the Control Word ........................................................................................................ 28

USING ACC-11E WITH UMAC MACRO STATION ........................................................... 30

Quick Review: Nodes and Addressing ......................................................................................... 30

Setting Up The Control Word ....................................................................................................... 33

Transferring Data Points over I/O Nodes ..................................................................................... 35

Preparing for I/O Data Transfer on the MACRO16 Station ................................................... 36

MS{anynode},MI71: 24-Bit Transfer ....................................................................................... 37

Page 5

ACC-11E User Manual

Table of Contents 5

MS{anynode},MI69 and MI70: 16-Bit Transfer ...................................................................... 42

MS{anynode}, MI171, MI172, and MI173: 24-Bit/16-Bit Transfer ........................................ 46

LAYOUTS & PINOUTS ............................................................................................................ 47

Board Layout Diagrams ................................................................................................................ 47

Wiring Considerations .................................................................................................................. 48

Terminal Block Option ................................................................................................................. 49

TB1 Top: Inputs 1 thru 12 ........................................................................................................ 49

TB2 Top: Inputs 13 thru 24 ...................................................................................................... 49

TB3 Top: Reference Voltages................................................................................................... 49

Wiring Input Terminal Blocks .................................................................................................. 50

TB1 Bottom: Outputs 1 thru 12 ................................................................................................ 51

TB2 Bottom: Outputs 13 thru 24 .............................................................................................. 51

TB3 Bottom: Reference Voltages ............................................................................................. 51

Wiring Output Terminal Blocks ............................................................................................... 52

D-Sub Option ................................................................................................................................ 53

J1 Top: Inputs 1 thru 12 ........................................................................................................... 53

J2 Top: Inputs 13 thru 24 ......................................................................................................... 53

Wiring Input DB15 Connectors ............................................................................................... 54

J1 Bottom: Outputs 1 thru 12 ................................................................................................... 55

J2 Bottom: Outputs 13 thru 24 ................................................................................................. 55

Wiring Output DB15 Connectors ............................................................................................. 56

SCHEMATICS ............................................................................................................................ 58

APPENDIX A: USING THE UMAC CONFIG PRO2 TOOL ............................................... 60

APPENDIX B: FULL TURBO UMAC M-VARIABLE MAPPINGS ................................... 66

APPENDIX C: FULL POWER UMAC M-VARIABLE MAPPINGS .................................. 78

APPENDIX D: THE CONTROL WORD ................................................................................ 90

Page 6

ACC-11E User Manual

Introduction 6

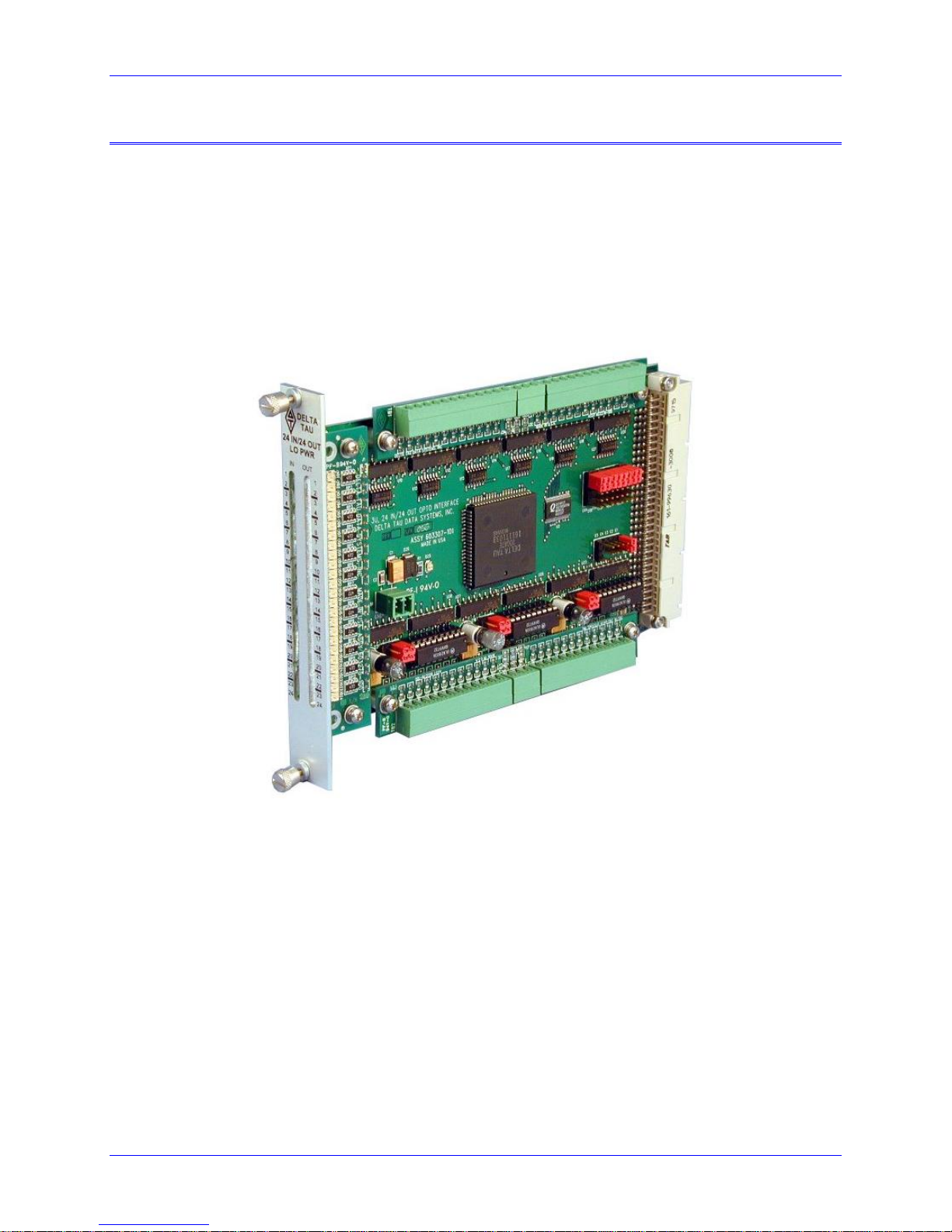

INTRODUCTION

The ACC-11E is a 24 In/24 Out general purpose I/O card. Built in the 3U euro card format, it can be used

in the following products:

- Turbo UMAC

- Power UMAC

- UMAC MACRO Station

All inputs and outputs are 12-24 VDC, optically isolated, and can be configured as sinking or sourcing.

Page 7

ACC-11E User Manual

Specifications 7

SPECIFICATIONS

Environmental Specifications

Description

Specification

Operating Temperature

0°C to 45°C,

Storage Temperature

-25°C to 70°C

Humidity

10% to 95 % non-condensing

Electrical Specifications

Description

Specification

Notes

Power Requirements

5V @ 0.05A (10%)

Output Current (individual)

100 mA

For UDN2981 and ULN2803

V1

12 – 24V

User-supplied voltage

Output Voltage

V1 – 1.1V

ULN2803 (See chip data sheet

for details)

V1 – 1.8V

UDN2981 (See chip data sheet

for details)

Fuse

125V @ 2.0A

Manufacturer: Little Fuse

Physical Specifications

Description

Specification

Notes

Dimensions

Length: 16.256 cm (6.4 in.)

Height: 10 cm (3.94 in.)

Width: 2.03 cm (0.8 in.)

Weight

180 g

Front Plate included

Terminal Block Connectors

FRONT-MC1,5/12-ST3,81

FRONT-MC1,5/5-ST3,81

FRONT-MC1,5/3-ST3,81

Terminal Blocks from Phoenix

Contact. UL-94V0

DB Option Connectors

DB15 Female

UL-94V0

The width is the width of the front plate. The length and height are the dimensions of the PCB.

Page 8

ACC-11E User Manual

Specifications 8

Agency Approval and Safety

Item

Description

CE Mark

EN61326-1

EMC

EN55011 Class A Group 1

EN61000-4-2

EN61000-4-3

EN61000-4-4

EN61000-4-5

EN61000-4-6

UL

UL 61010-1 File E314517

cUL

CAN/CSA C22.2 No. 1010.1-92 File E314517

Flammability Class

UL 94V-0

KC

EMI: KN 11

EMS: KN 61000-6-2

사 용 자 안 내 문

이 기기는 업무용 환경에서 사용할 목적으로 적합성평가를 받은 기기로서 가정

용 환경에서 사용하는 경우 전파간섭의 우려가 있습니다.

한국 EMC적용제품 준수사항

본 제품은 전파법(KC 규정)을 준수합니다. 제품을 사용하려면 다음 사항에 유

의하십시오. 이 기기는 업무용 환경에서 사용할 목적으로 적합성평가를 받은

기기로서 가정용 환경에서 사용하는 경우 전파간섭의 우려가 있습니다.

입력에 EMC 필터, 서지 보호기, 페라이트 코어 또는 1차측의 케이블에 노이즈

필터를 입력으로 사용하십시오.

Page 9

ACC-11E User Manual

Addressing and Jumper Settings 9

ADDRESSING ACC-11E

Several jumpers must be configured on the Accessory 11E in order for it to work properly with other I/O

cards in the UMAC rack. Jumpers E1-E4 select the starting base I/O address, and for within the base

address, jumpers E6A-E6H select whether the low, middle, or high byte will be used.

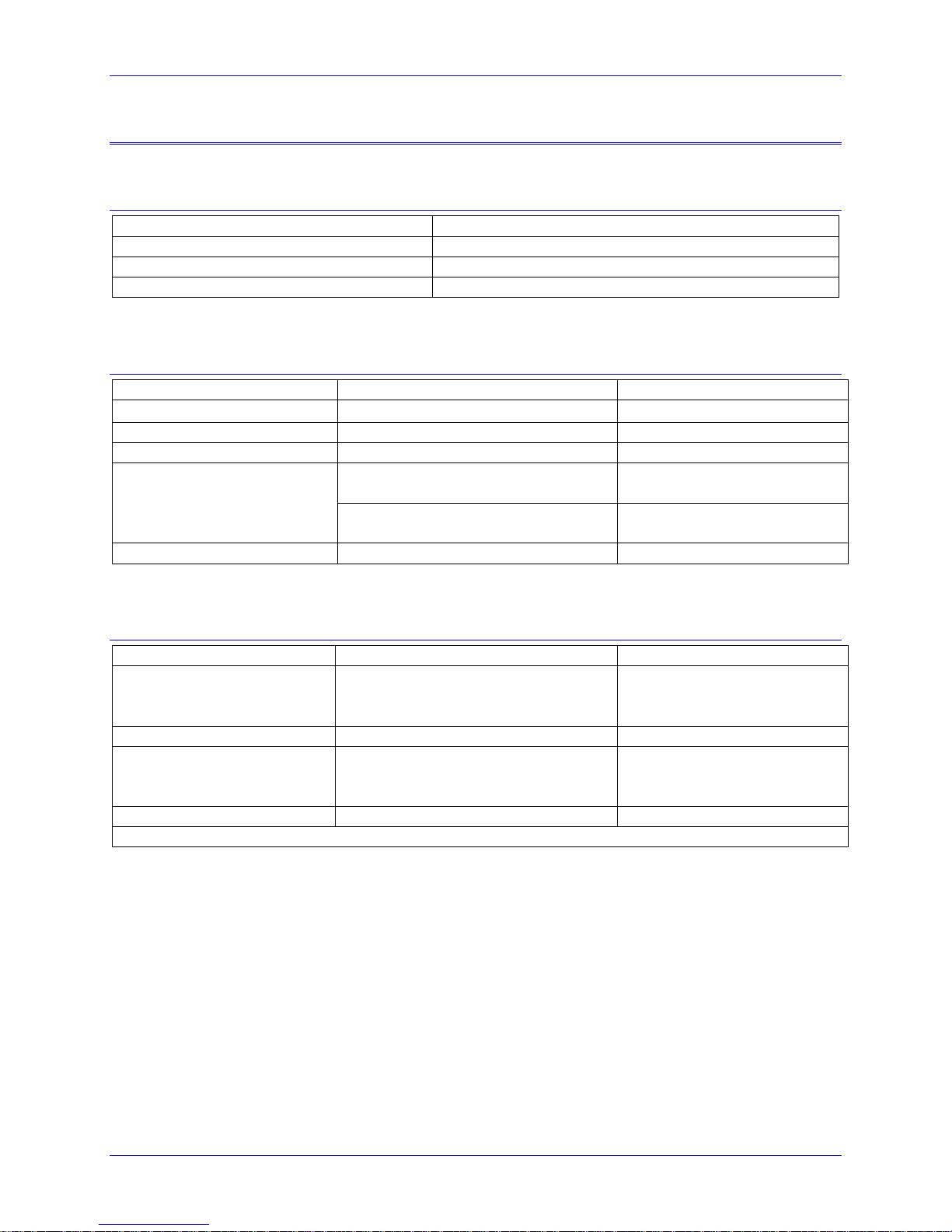

Turbo/Power UMAC and MACRO Station Jumper Settings

Chip

Select

TURBO

MACRO

POWER

Jumpers

Offset

Index

(n)

E1

E2

E3

E4

E6A-E6H

CS10

Y:$78C00,0,8

Y:$8800,0,8

$A00000.8.8

0

ON

OFF

OFF

OFF

1 to 2

CS10

Y:$78C00,8,8

Y:$8800,8,8

$A00000.16.8

0

ON

OFF

OFF

OFF

2 to 3

CS10

Y:$78C00,16,8

Y:$8800,16,8

$A00000.24.8

0

ON

OFF

OFF

OFF

4 to 5

CS12

Y:$78D00,0,8

Y:$8840,0,8

$B00000.8.8

1

OFF

ON

OFF

OFF

1 to 2

CS12

Y:$78D00,8,8

Y:$8840,8,8

$B00000.16.8

1

OFF

ON

OFF

OFF

2 to 3

CS12

Y:$78D00,16,8

Y:$8840,16,8

$B00000.24.8

1

OFF

ON

OFF

OFF

4 to 5

CS14

Y:$78E00,0,8

Y:$8880,0,8

$C00000.8.8

2

OFF

OFF

ON

OFF

1 to 2

CS14

Y:$78E00,8,8

Y:$8880,8,8

$C00000.16.8

2

OFF

OFF

ON

OFF

2 to 3

CS14

Y:$78E00,16,8

Y:$8880,16,8

$C00000.24.8

2

OFF

OFF

ON

OFF

4 to 5

CS16

Y:$78F00,0,8

Y:$88C0,0,8

$D00000.8.8

3

OFF

OFF

OFF

ON

1 to 2

CS16

Y:$78F00,8,8

Y:$88C0,8,8

$D00000.16.8

3

OFF

OFF

OFF

ON

2 to 3

CS16

Y:$78F00,16,8

Y:$88C0,16,8

$D00000.24.8

3

OFF

OFF

OFF

ON

4 to 5

E6A – E6H Layout Diagram

1

2

3

4

5

E6A

E6B

E6C

E6D

E6E

E6F

E6G

E6H

Legacy MACRO Station Address Jumper Settings

Chip Select

MACRO

Jumpers

E1

E2

E3

E4

CS10

$FFE0

ON

OFF

OFF

OFF

CS12

$FFE8

OFF

ON

OFF

OFF

CS14

$FFF0

OFF

OFF

ON

OFF

Page 10

ACC-11E User Manual

Addressing and Jumper Settings 10

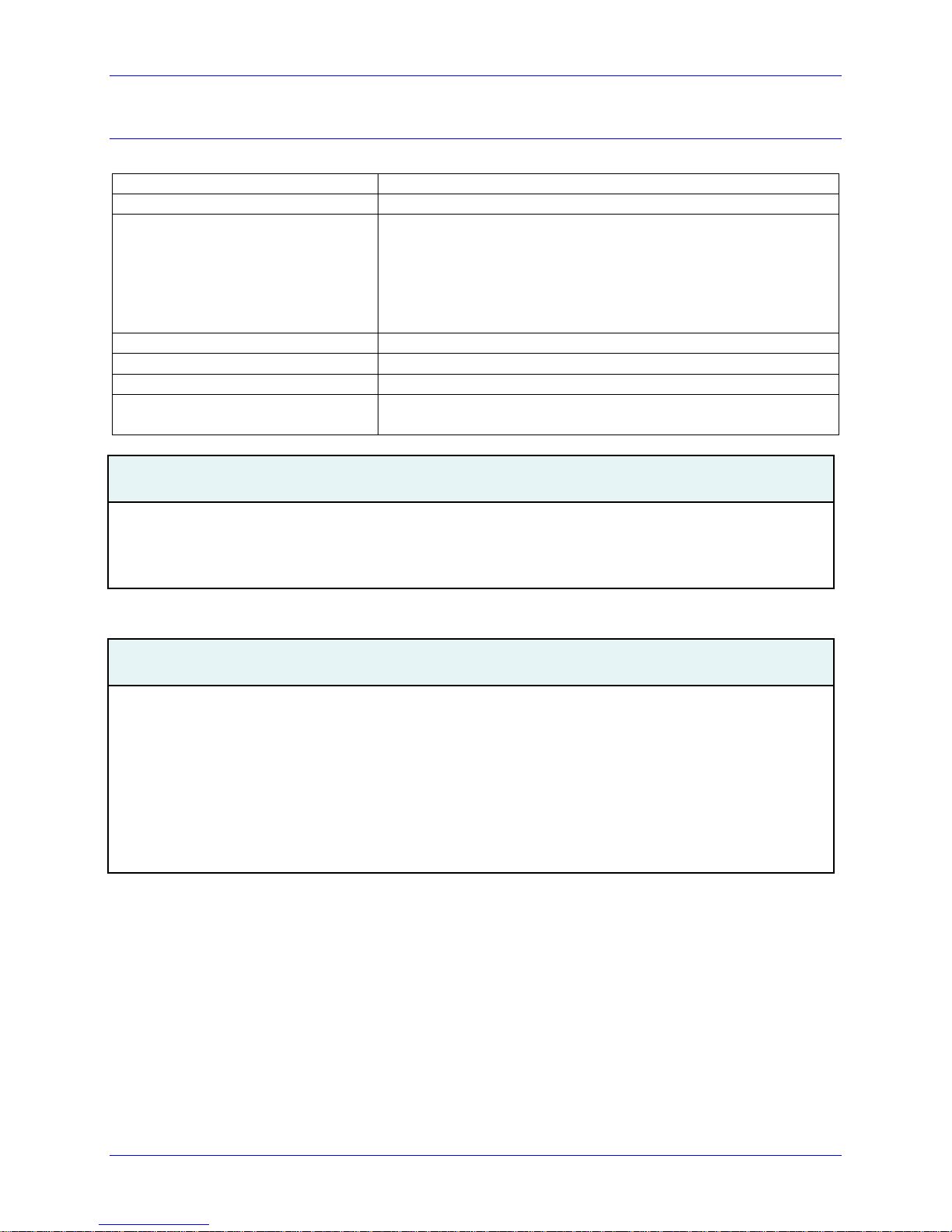

Sinking or Sourcing Output Select

WARNING

Jumpers E16 thru E21 generally should be left at factory defaults.

They must not be changed without also changing their respective

buffer IC, ULN2803A for sinking or UDN2981A for sourcing.

Jumpers

Descriptions

E16 & E17

1-2 = Outputs 1 thru 8 Sinking

2-3 = Outputs 1 thru 8 Sourcing

E18 & E19

1-2 = Outputs 9 thru 16 Sinking

2-3 = Outputs 9 thru 16 Sourcing

E20 & E21

1-2 = Outputs 17 thru 24 Sinking

2-3 = Outputs 17 thru 24 Sourcing

I/O Gate Data Clock Select

Jumper

Function

E5

Servo Clock 2-3 Phase Clock (default)

Page 11

ACC-11E User Manual

Addressing and Jumper Settings 11

Hardware Address Limitations

The ACC-11E has a hardware address limitation relative to the newer type B series of UMAC high-speed

I/O cards. These new I/O cards have four base addresses per chip select (CS10, CS12, CS14, and CS16).

This enables these cards to have up to 16 different addresses. The type A cards have one base address per

chip select but also have the low-byte, middle-byte, and high-byte type of an addressing scheme and thus

allow for a maximum of twelve of these I/O cards.

Name

Type

Category

Possible Number

of Addresses

Maximum Number

of Cards in 1 Rack

ACC-9E

A

General I/O

4

12

ACC-10E

A

General I/O

4

ACC-11E

A

General I/O

4

ACC-12E

A

General I/O

4

ACC-14E

B

General I/O

16

16

ACC-28E

B

Analog I/O

16

ACC-36E

B

Analog I/O

16

ACC-53E

B

Feedback

16

ACC-57E

B

Feedback

16

ACC-58E

B

Feedback

16

ACC-59E

B

Analog I/O

12

12

ACC-65E

B

General I/O

16

16

ACC-66E

B

General I/O

16

ACC-67E

B

General I/O

16

ACC-68E

B

General I/O

16

ACC-84E

B

Feedback

12

12

Addressing Type A and Type B accessory cards requires attention to the following set of rules:

Populating Rack with Type A Cards Only (no conflicts)

In this mode, the card(s) can use any available Address.

Note

Type A cards can have up to 4 different base addresses. Because

each card can be setup to use the lower, middle, or high byte of a

specific base address, it is possible to populate a single rack with a

maximum of 12 Type A accessory cards.

Populating Rack with Type B Cards Only (no conflicts)

In this mode, the card(s) can potentially use any available Address.

Populating Rack with Type A & Type B Cards (possible conflicts)

Typically, Type A and Type B cards should not share the same Chip Select; however, if they do, the

following rules apply:

Type A and Type B Feedback Cards

Type A cards cannot share the same Chip Select as Type B Feedback cards.

Page 12

ACC-11E User Manual

Addressing and Jumper Settings 12

Type A and Type B General I/O Cards

Type A cards can share the same Chip Select as Type B general I/O cards; however, in this mode,

Type B cards naturally use the lower byte (default), and Type A cards must be set to the

middle/high byte of the selected base address.

Type A Cards and Type B Analog Cards

Type A cards can share the same Chip Select as Type B analog I/O cards; however, in this mode,

Type B cards naturally use the middle/high bytes (default), and Type A cards must be set to the

low byte of the selected base address.

Page 13

ACC-11E User Manual

Using ACC-11E with UMAC Turbo 13

USING ACC-11E WITH TURBO UMAC

The procedure for using the ACC-11E with Turbo UMAC has two steps:

1. Configure the Control Word

2. Accessing I/O data points (M-Variables)

Configuring the Control Word

Write a 7 to the control word which is located at {base address + 7}, n, 8 where:

n = 0 if using low byte addressing

n = 8 if using middle byte addressing

n = 16 if using high byte addressing

The control word must be configured every time the UMAC is powered or reset. This can be done in an

initialization (one that disables itself) PLC.

Example 1: Setting up Control Word at Startup for Card at Base Address $78C00, Low Byte Addressing

M3307->Y:$78C07,0,8 // I/O Card 1 control register from suggested M-Variables

Open PLC 1 Clear

M3307=$07

Disable PLC 1

Close

Example 2: Setting up Control Word at Startup for 3 Cards at Base Address $78C00; Low, Middle, and

High Byte Addressing

M3307->Y:$78C07,0,8 // I/O Card 1 control register using low byte

M3317->Y:$78C07,8,8 // I/O Card 2 control register using middle byte

M3327->Y:$78C07,16,8 // I/O Card 3 control register using high byte

Open PLC 1 Clear

M3307=$07

M3317=$07

M3327=$07

Disable PLC 1

Close

Note

See Appendix for control word details and explanations.

Page 14

ACC-11E User Manual

Using ACC-11E with UMAC Turbo 14

Accessing I/O data points (M-Variables)

Every ACC-11E has 48 bits of I/O data, which are comprised of one byte (8 bits) at the base address plus

five more bytes (8 x 6 = 48) at the next five consecutive addresses. Examples:

I/O data bits for card at base address

$78C00 using low bytes

I/O data bits for card at base address

$78C00 using high bytes

Y:$078C00,0,8

Y:$078C01,0,8

Y:$078C02,0,8

Inputs 1-8

Inputs 9-16

Inputs 17-24

Y:$078C00,16,8

Y:$078C01,16,8

Y:$078C02,16,8

Inputs 1-8

Inputs 9-16

Inputs 17-24

Y:$078C03,0,8

Y:$078C04,0,8

Y:$078C05,0,8

Outputs 1-8

Outputs 9-16

Outputs 17-24

Y:$078C03,16,8

Y:$078C04,16,8

Y:$078C05,16,8

Outputs 1-8

Outputs 9-16

Outputs 17-24

Example: Bitwise M-Variable mapping for ACC-11E at base address $78C00 using low bytes:

#define Input1 M7000 Input1->Y:$078C00,0,1

#define Input2 M7001 Input2->Y:$078C00,1,1

#define Input3 M7002 Input3->Y:$078C00,2,1

#define Input4 M7003 Input4->Y:$078C00,3,1

#define Input5 M7004 Input5->Y:$078C00,4,1

#define Input6 M7005 Input6->Y:$078C00,5,1

#define Input7 M7006 Input7->Y:$078C00,6,1

#define Input8 M7007 Input8->Y:$078C00,7,1

#define Input9 M7008 Input9->Y:$078C01,0,1

#define Input10 M7009 Input10->Y:$078C01,1,1

#define Input11 M7010 Input11->Y:$078C01,2,1

#define Input12 M7011 Input12->Y:$078C01,3,1

#define Input13 M7012 Input13->Y:$078C01,4,1

#define Input14 M7013 Input14->Y:$078C01,5,1

#define Input15 M7014 Input15->Y:$078C01,6,1

#define Input16 M7015 Input16->Y:$078C01,7,1

#define Input17 M7016 Input17->Y:$078C02,0,1

#define Input18 M7017 Input18->Y:$078C02,1,1

#define Input19 M7018 Input19->Y:$078C02,2,1

#define Input20 M7019 Input20->Y:$078C02,3,1

#define Input21 M7020 Input21->Y:$078C02,4,1

#define Input22 M7021 Input22->Y:$078C02,5,1

#define Input23 M7022 Input23->Y:$078C02,6,1

#define Input24 M7023 Input24->Y:$078C02,7,1

#define Output1 M7024 Output1->Y:$078C03,0,1

#define Output2 M7025 Output2->Y:$078C03,1,1

#define Output3 M7026 Output3->Y:$078C03,2,1

#define Output4 M7027 Output4->Y:$078C03,3,1

#define Output5 M7028 Output5->Y:$078C03,4,1

#define Output6 M7029 Output6->Y:$078C03,5,1

#define Output7 M7030 Output7->Y:$078C03,6,1

#define Output8 M7031 Output8->Y:$078C03,7,1

#define Output9 M7032 Output9->Y:$078C04,0,1

#define Output10 M7033 Output10->Y:$078C04,1,1

#define Output11 M7034 Output11->Y:$078C04,2,1

#define Output12 M7035 Output12->Y:$078C04,3,1

#define Output13 M7036 Output13->Y:$078C04,4,1

#define Output14 M7037 Output14->Y:$078C04,5,1

#define Output15 M7038 Output15->Y:$078C04,6,1

#define Output16 M7039 Output16->Y:$078C04,7,1

#define Output17 M7040 Output17->Y:$078C05,0,1

#define Output18 M7041 Output18->Y:$078C05,1,1

#define Output19 M7042 Output19->Y:$078C05,2,1

#define Output20 M7043 Output20->Y:$078C05,3,1

#define Output21 M7044 Output21->Y:$078C05,4,1

#define Output22 M7045 Output22->Y:$078C05,5,1

#define Output23 M7046 Output23->Y:$078C05,6,1

#define Output24 M7047 Output24->Y:$078C05,7,1

Page 15

ACC-11E User Manual

Using ACC-11E with UMAC Turbo 15

Note

See Appendix for suggested M-Variables for additional cards.

Note

Suggested M-Variable definitions are also available with the UMAC

Config. Pro2 tool (see Appendix).

Note

Most systems only use low byte addressing

Page 16

ACC-11E User Manual

Using ACC-11E with Power UMAC 16

USING ACC-11E WITH POWER UMAC SCRIPT PROGRAMING

The following section describes two software configuration procedures that are needed when using the

Power PMAC script programming language:

1. Configuring the Control Word

2. Accessing I/O data points (pointers)

Configuring the Control Word

Write a 7 to the control word which is located at {base address + 7}.n.8 where:

n = 8 if using low byte addressing

n = 16 if using middle byte addressing

n = 24 if using high byte addressing

The control word must be configured every time the POWER UMAC is powered or reset. This can be

done in an initialization (one that disables itself) PLC, usually PLC 1.

Example: Setting up Control Word at Startup for Card at $A00000, Low Byte Addressing

ptr IoCard0Reg7->u.io:$A0001C.8.8 // I/O Card 0 control register from suggested M-Variables

open plc 1

IoCard0Reg7=$7;

disable plc 1;

close

Example: Setting up Control Word at Startup for 3 Cards at Base Address $A00000; Low, Middle, and

High Byte Addressing

ptr IoCard0Reg7->u.io:$A0001C.8.8 // I/O Card 0 control register from suggested M-Variables

ptr IoCard1Reg7->u.io:$A0001C.16.8 // I/O Card 1 control register from suggested M-Variables

ptr IoCard2Reg7->u.io:$A0001C.24.8 // I/O Card 2 control register from suggested M-Variables

open plc 1

IoCard0Reg7=$7;

IoCard1Reg7=$7;

IoCard2Reg7=$7;

disable plc 1;

close

Note

See Appendix for control word details and explanations.

Page 17

ACC-11E User Manual

Using ACC-11E with Power UMAC 17

Accessing I/O Data Points (Pointers)

The simplest way to access I/O points on the ACC-11E is to define pointer variables (M-Variables) that

point to each bit on the I/O device.

Suggested M-Variables

Base offset $A00000, low byte addressing

// Single-bit variables used for accessing I/O points

ptr Input1->u.io:$A00000.8.1 // I/O Card 1 Input1

ptr Input2->u.io:$A00000.9.1 // I/O Card 1 Input2

ptr Input3->u.io:$A00000.10.1 // I/O Card 1 Input3

ptr Input4->u.io:$A00000.11.1 // I/O Card 1 Input4

ptr Input5->u.io:$A00000.12.1 // I/O Card 1 Input5

ptr Input6->u.io:$A00000.13.1 // I/O Card 1 Input6

ptr Input7->u.io:$A00000.14.1 // I/O Card 1 Input7

ptr Input8->u.io:$A00000.15.1 // I/O Card 1 Input8

ptr Input9->u.io:$A00004.8.1 // I/O Card 1 Input9

ptr Input10->u.io:$A00004.9.1 // I/O Card 1 Input10

ptr Input11->u.io:$A00004.10.1 // I/O Card 1 Input11

ptr Input12->u.io:$A00004.11.1 // I/O Card 1 Input12

ptr Input13->u.io:$A00004.12.1 // I/O Card 1 Input13

ptr Input14->u.io:$A00004.13.1 // I/O Card 1 Input14

ptr Input15->u.io:$A00004.14.1 // I/O Card 1 Input15

ptr Input16->u.io:$A00004.15.1 // I/O Card 1 Input16

ptr Input17->u.io:$A00008.8.1 // I/O Card 1 Input17

ptr Input18->u.io:$A00008.9.1 // I/O Card 1 Input18

ptr Input19->u.io:$A00008.10.1 // I/O Card 1 Input19

ptr Input20->u.io:$A00008.11.1 // I/O Card 1 Input20

ptr Input21->u.io:$A00008.12.1 // I/O Card 1 Input21

ptr Input22->u.io:$A00008.13.1 // I/O Card 1 Input22

ptr Input23->u.io:$A00008.14.1 // I/O Card 1 Input23

ptr Input24->u.io:$A00008.15.1 // I/O Card 1 Input24

ptr Output1->u.io:$A0000C.8.1 // I/O Card 1 Output1

ptr Output2->u.io:$A0000C.9.1 // I/O Card 1 Output2

ptr Output3->u.io:$A0000C.10.1 // I/O Card 1 Output3

ptr Output4->u.io:$A0000C.11.1 // I/O Card 1 Output4

ptr Output5->u.io:$A0000C.12.1 // I/O Card 1 Output5

ptr Output6->u.io:$A0000C.13.1 // I/O Card 1 Output6

ptr Output7->u.io:$A0000C.14.1 // I/O Card 1 Output7

ptr Output8->u.io:$A0000C.15.1 // I/O Card 1 Output8

ptr Output9->u.io:$A00010.8.1 // I/O Card 1 Output9

ptr Output10->u.io:$A00010.9.1 // I/O Card 1 Output10

ptr Output11->u.io:$A00010.10.1 // I/O Card 1 Output11

ptr Output12->u.io:$A00010.11.1 // I/O Card 1 Output12

ptr Output13->u.io:$A00010.12.1 // I/O Card 1 Output13

ptr Output14->u.io:$A00010.13.1 // I/O Card 1 Output14

ptr Output15->u.io:$A00010.14.1 // I/O Card 1 Output15

ptr Output16->u.io:$A00010.15.1 // I/O Card 1 Output16

ptr Output17->u.io:$A00014.8.1 // I/O Card 1 Output17

ptr Output18->u.io:$A00014.9.1 // I/O Card 1 Output18

ptr Output19->u.io:$A00014.10.1 // I/O Card 1 Output19

ptr Output20->u.io:$A00014.11.1 // I/O Card 1 Output20

ptr Output21->u.io:$A00014.12.1 // I/O Card 1 Output21

ptr Output22->u.io:$A00014.13.1 // I/O Card 1 Output22

ptr Output23->u.io:$A00014.14.1 // I/O Card 1 Output23

ptr Output24->u.io:$A00014.15.1 // I/O Card 1 Output24

// Byte-wide variables used for power-on configuration

ptr IoCard1Reg0->u.io:$A00000.8.8 // I/O Card 1 Inputs 1-8 as byte

ptr IoCard1Reg1->u.io:$A00004.8.8 // I/O Card 1 Inputs 9-16 as byte

ptr IoCard1Reg2->u.io:$A00008.8.8 // I/O Card 1 Inputs 17-24 as byte

ptr IoCard1Reg3->u.io:$A0000C.8.8 // I/O Card 1 Outputs 1-8 as byte

ptr IoCard1Reg4->u.io:$A00010.8.8 // I/O Card 1 Outputs 9-16 as byte

ptr IoCard1Reg5->u.io:$A00014.8.8 // I/O Card 1 Outputs 17-24 as byte

ptr IoCard1Reg6->u.io:$A00018.8.8 // I/O Card 1 latch inputs

ptr IoCard1Reg7->u.io:$A0001C.8.8 // I/O Card 1 control register

See Appendix for suggested M-Variables for additional cards.

Page 18

ACC-11E User Manual

Using ACC-11E with Power UMAC 18

USING ACC-11E WITH POWER UMAC C PROGRAMING

Setting Up Digital I/O Access

Delta Tau has developed the following functions which can be used to setup the ACC-11E using the C

Programming Language. The last entry in the list describes, as an alternative, how to create user written

functions.

Function for Setting the Control Word: ACC11E_SetControlWord()

Function for Reading the State of Inputs: ACC11E_GetInputState()

Function for Reading the State of Outputs: ACC11E_GetOutputState()

Function for Writing to Outputs: ACC11E_SetOutputState()

User Written Functions

Function for Setting the Control Word: ACC11E_SetControlWord()

Two parameters must be passed in the calling function:

BaseAddressOffset: One of the four base addresses (jumper selected) ACC-11E can take

=0xA00000

=0xB00000

=0xC00000

=0xD00000

ByteSelect: The byte used (jumper selected) for the I/O bits on this card

=1 for low byte

=2 for middle byte

=3 for high byte

The function is of type void, so it will not return any values.

void ACC11E_SetControlWord(unsigned int BaseAddressOffset, unsigned int ByteSelect)

/*

Input:

BaseAddressOffset: IO Card Base Address offset

ByteSelect: =1 for lowest 8 bits, =2 for middle 8 bits, =3 for high 8 bits

ControlWord: Control word value to which to set the card's Control Word

*/

{

volatile unsigned int *ioptr; // Create I/O pointer

ioptr = piom + BaseAddressOffset/4 + 7;// Initialize I/O pointer to Control Word register

*ioptr = 7 << (8*ByteSelect); // Write Control Word value to register

return;

}

Note

See Appendix for control word details and explanations.

Page 19

ACC-11E User Manual

Using ACC-11E with Power UMAC 19

Function for Reading the State of Inputs: ACC11E_GetInputState()

Three parameters must be passed in the calling function:

BaseAddressOffset: One of the four base addresses (jumper selected) ACC-11E can take

=0xA00000

=0xB00000

=0xC00000

=0xD00000

ByteSelect: The byte used (jumper selected) for the I/O bits on this card

=1 for low byte

=2 for middle byte

=3 for high byte

InputNumber: The number of the Input pin whose state one desires to read or modify.

Inputs are numbered 1–24 on ACC-11E

The function will return the state of the specified pin as an unsigned int:

=0, pin is low

=1, pin is high

unsigned int ACC11E_GetInputState(unsigned int BaseAddressOffset, unsigned int ByteSelect,

unsigned int InputNumber)

/*

Input:

------BaseAddressOffset: I/O Card Base Address Offset

InputNumber: Input Pin Number (1-24)

ByteSelect: =1 for lowest 8 bits, =2 for middle 8 bits, =3 for high 8 bits

Output:

------State of the I/O pin specified*/

{

volatile unsigned int *ioptr; // Create I/O pointer

// Compute location for high bit

unsigned int HighBitInCorrectLocation=0,ShiftValue;

InputNumber--;

ShiftValue = InputNumber%8 + 8*(ByteSelect-1);

HighBitInCorrectLocation = 1 << ShiftValue; // Shift bit to that location

ioptr = piom + BaseAddressOffset/4; // Initialize pointer

ioptr += InputNumber/8; // Increment to register containing the I/O bit

// Return state of I/O point

return ((*ioptr >> 8) & HighBitInCorrectLocation) >> ShiftValue;

}

Function for Reading the State of Outputs: ACC11E_GetOutputState()

Three parameters must be passed in the calling function:

BaseAddressOffset: One of the four base addresses (jumper selected) ACC-11E can take

=0xA00000

=0xB00000

=0xC00000

=0xD00000

Page 20

ACC-11E User Manual

Using ACC-11E with Power UMAC 20

ByteSelect: The byte used (jumper selected) for the I/O bits on this card

=1 for low byte

=2 for middle byte

=3 for high byte

OutputNumber: The number of the Onput pin whose state one desires to read or modify.

Outputs are numbered 1–24 on ACC-11E

The function will return the state of the specified pin as an unsigned int:

=0, pin is low

=1, pin is high

unsigned int ACC11E_GetOutputState(unsigned int BaseAddressOffset, unsigned int ByteSelect,

unsigned int OutputNumber)

/*

Input:

------BaseAddressOffset: I/O Card Base Address Offset

InputNumber: Input Pin Number (1-24)

ByteSelect: =1 for lowest 8 bits, =2 for middle 8 bits, =3 for high 8 bits

Output:

------State of the I/O pin specified*/

{

volatile unsigned int *ioptr; // Create I/O pointer

// Compute location for high bit

unsigned int HighBitInCorrectLocation=0,ShiftValue;

OutputNumber--;

ShiftValue=OutputNumber%8 + 8*(ByteSelect-1);

HighBitInCorrectLocation = 1 << ShiftValue; // Shift bit to that location

ioptr = piom + BaseAddressOffset/4; // Initialize pointer

ioptr += OutputNumber/8 + 3; // Increment to register containing the I/O bit

// Return state of I/O point

return ((*ioptr >> 8) & HighBitInCorrectLocation) >> ShiftValue;

}

Function for Writing to Outputs: ACC11E_SetOutputState()

Four parameters must be passed in the calling function:

BaseAddressOffset: One of the four base addresses (jumper selected) ACC-11E can take

=0xA00000

=0xB00000

=0xC00000

=0xD00000

ByteSelect: The byte used (jumper selected) for the I/O bits on this card

=1 for low byte

=2 for middle byte

=3 for high byte

OutputNumber: The number of the Output pin whose state one desires to read or modify.

Outputs are numbered 1–24 on ACC-11E

State: The state to which the desires to set the I/O pin.

=0, pin is OFF (low=false)

=1, pin is ON (high=true)

Page 21

ACC-11E User Manual

Using ACC-11E with Power UMAC 21

The function is of type void, so it will not return any values.

void ACC11E_SetOutputState(unsigned int BaseAddressOffset, unsigned int ByteSelect, unsigned int

OutputNumber, unsigned int State)

/*

Input:

BaseAddressOffset: I/O Card Base Address offset

ByteSelect: =1 for lowest 8 bits, =2 for middle 8 bits, =3 for high 8 bits

PinNumber: Output Pin Number (1-24)

State: Desired digital state of pin (0 = OFF, 1 = ON)

*/

{

volatile unsigned int *ioptr; // Create I/O pointer

// Compute location for high bit

unsigned int HighBitInCorrectLocation;

OutputNumber--;

HighBitInCorrectLocation = 1 << (OutputNumber%8 + 8*ByteSelect);

ioptr = piom + BaseAddressOffset/4; // Initialize pointer

ioptr += OutputNumber/8 + 3; // Increment to register containing the I/O bit

if(State==1) // If the user wants the pin to be ON (high true)

{// Logical OR with the bit the user desires to activate

*ioptr |= HighBitInCorrectLocation;

} else {

// Logical AND the register with a 0 in the desired location to bring the pin's state low

// right shift to push out garbage in lowest 8 bits, then shift back up 8 bits to have

// data in the proper location

*ioptr &= (((~0)^HighBitInCorrectLocation) >> 8) << 8;

}

return;

}

Page 22

ACC-11E User Manual

Using ACC-11E with Power UMAC 22

Header and Source File

The code for “acc11e.h” and “acc11e.c”, given below, contains the definitions for using the above

functions, prototypes, and the above listed functions. “acc11.h” should be included whenever using the

above ACC-11E C code. The files, acc11e.h and acc11e.c, must be put into the same folder as the C

program (BGCPLC, RTICPLC, or Background C Program.

#include "acc11e.h"

Below is the full code for both acc11e.h and acc11e.c.

acc11e.h

#include <gplib.h>

#include <RtGpShm.h> // Global Rt/Gp Shared memory pointers

//------------------------------------------------------------// The following is a projpp created file from the User defines

//-------------------------------------------------------------

#include "../../Include/pp_proj.h"

// Corresponds to E1 installed on ACC-11E, Turbo base address of $78C00

#define ACC11E_BaseAddressOffset_E1 0xA00000

// Corresponds to E2 installed on ACC-11E, Turbo base address of $78D00

#define ACC11E_BaseAddressOffset_E2 0xB00000

// Corresponds to E3 installed on ACC-11E, Turbo base address of $78E00

#define ACC11E_BaseAddressOffset_E3 0xC00000

// Corresponds to E4 installed on ACC-11E, Turbo base address of $78F00

#define ACC11E_BaseAddressOffset_E4 0xD00000

#define ON 1 // Assumes that (logic high)=true

#define OFF 0 // Assumes that (logic low)=false

#define ByteSelectLow 1

#define ByteSelectMiddle 2

#define ByteSelectHigh 3

void ACC11E_SetControlWord(unsigned int BaseAddressOffset, unsigned int ByteSelect);

unsigned int ACC11E_GetInputState(unsigned int BaseAddressOffset, unsigned int ByteSelect,

unsigned int InputNumber);

unsigned int ACC11E_GetOutputState(unsigned int BaseAddressOffset, unsigned int ByteSelect,

unsigned int OutputNumber);

void ACC11E_SetOutputState(unsigned int BaseAddressOffset, unsigned int ByteSelect, unsigned int

OutputNumber, unsigned int State);

Page 23

ACC-11E User Manual

Using ACC-11E with Power UMAC 23

acc11e.c

#include <gplib.h>

#include <RtGpShm.h> // Global Rt/Gp Shared memory pointers

//------------------------------------------------------------// The following is a projpp created file from the User defines

//-------------------------------------------------------------

#include "acc11e.h"

void ACC11E_SetControlWord(unsigned int BaseAddressOffset, unsigned int ByteSelect)

/*

Input:

BaseAddressOffset: IO Card Base Address offset

ByteSelect: =1 for lowest 8 bits, =2 for middle 8 bits, =3 for high 8 bits

ControlWord: Control word value to which to set the card's Control Word

*/

{

volatile unsigned int *ioptr; // Create I/O pointer

ioptr = piom + BaseAddressOffset/4 + 7;// Initialize I/O pointer to Control Word register

*ioptr = 7 << (8*ByteSelect); // Write Control Word value to register

return;

}

unsigned int ACC11E_GetInputState(unsigned int BaseAddressOffset, unsigned int ByteSelect,

unsigned int InputNumber)

/*

Input:

------BaseAddressOffset: I/O Card Base Address Offset

InputNumber: Input Pin Number (1-24)

ByteSelect: =1 for lowest 8 bits, =2 for middle 8 bits, =3 for high 8 bits

Output:

------State of the I/O pin specified*/

{

volatile unsigned int *ioptr; // Create I/O pointer

// Compute location for high bit

unsigned int HighBitInCorrectLocation=0,ShiftValue;

InputNumber--;

ShiftValue = InputNumber%8 + 8*(ByteSelect-1);

HighBitInCorrectLocation = 1 << ShiftValue; // Shift bit to that location

ioptr = piom + BaseAddressOffset/4; // Initialize pointer

ioptr += InputNumber/8; // Increment to register containing the I/O bit

// Return state of I/O point

return ((*ioptr >> 8) & HighBitInCorrectLocation) >> ShiftValue;

}

unsigned int ACC11E_GetOutputState(unsigned int BaseAddressOffset, unsigned int ByteSelect,

unsigned int OutputNumber)

/*

Input:

------BaseAddressOffset: I/O Card Base Address Offset

InputNumber: Input Pin Number (1-24)

ByteSelect: =1 for lowest 8 bits, =2 for middle 8 bits, =3 for high 8 bits

Output:

------State of the I/O pin specified*/

{

volatile unsigned int *ioptr; // Create I/O pointer

// Compute location for high bit

unsigned int HighBitInCorrectLocation=0,ShiftValue;

OutputNumber--;

ShiftValue=OutputNumber%8 + 8*(ByteSelect-1);

HighBitInCorrectLocation = 1 << ShiftValue; // Shift bit to that location

ioptr = piom + BaseAddressOffset/4; // Initialize pointer

ioptr += OutputNumber/8 + 3; // Increment to register containing the I/O bit

// Return state of I/O point

return ((*ioptr >> 8) & HighBitInCorrectLocation) >> ShiftValue;

Page 24

ACC-11E User Manual

Using ACC-11E with Power UMAC 24

}

void ACC11E_SetOutputState(unsigned int BaseAddressOffset, unsigned int ByteSelect, unsigned int

OutputNumber, unsigned int State)

/*

Input:

BaseAddressOffset: I/O Card Base Address offset

ByteSelect: =1 for lowest 8 bits, =2 for middle 8 bits, =3 for high 8 bits

PinNumber: Output Pin Number (1-24)

State: Desired digital state of pin (0 = OFF, 1 = ON)

*/

{

volatile unsigned int *ioptr; // Create I/O pointer

// Compute location for high bit

unsigned int HighBitInCorrectLocation;

OutputNumber--;

HighBitInCorrectLocation = 1 << (OutputNumber%8 + 8*ByteSelect);

ioptr = piom + BaseAddressOffset/4; // Initialize pointer

ioptr += OutputNumber/8 + 3; // Increment to register containing the I/O bit

if(State==1) // If the user wants the pin to be ON (high true)

{// Logical OR with the bit the user desires to activate

*ioptr |= HighBitInCorrectLocation;

} else {

// Logical AND the register with a 0 in the desired location to bring the pin's state low

// right shift to push out garbage in lowest 8 bits, then shift back up 8 bits to have

// data in the proper location

*ioptr &= (((~0)^HighBitInCorrectLocation) >> 8) << 8;

}

return;

}

Page 25

ACC-11E User Manual

Using ACC-11E with Power UMAC 25

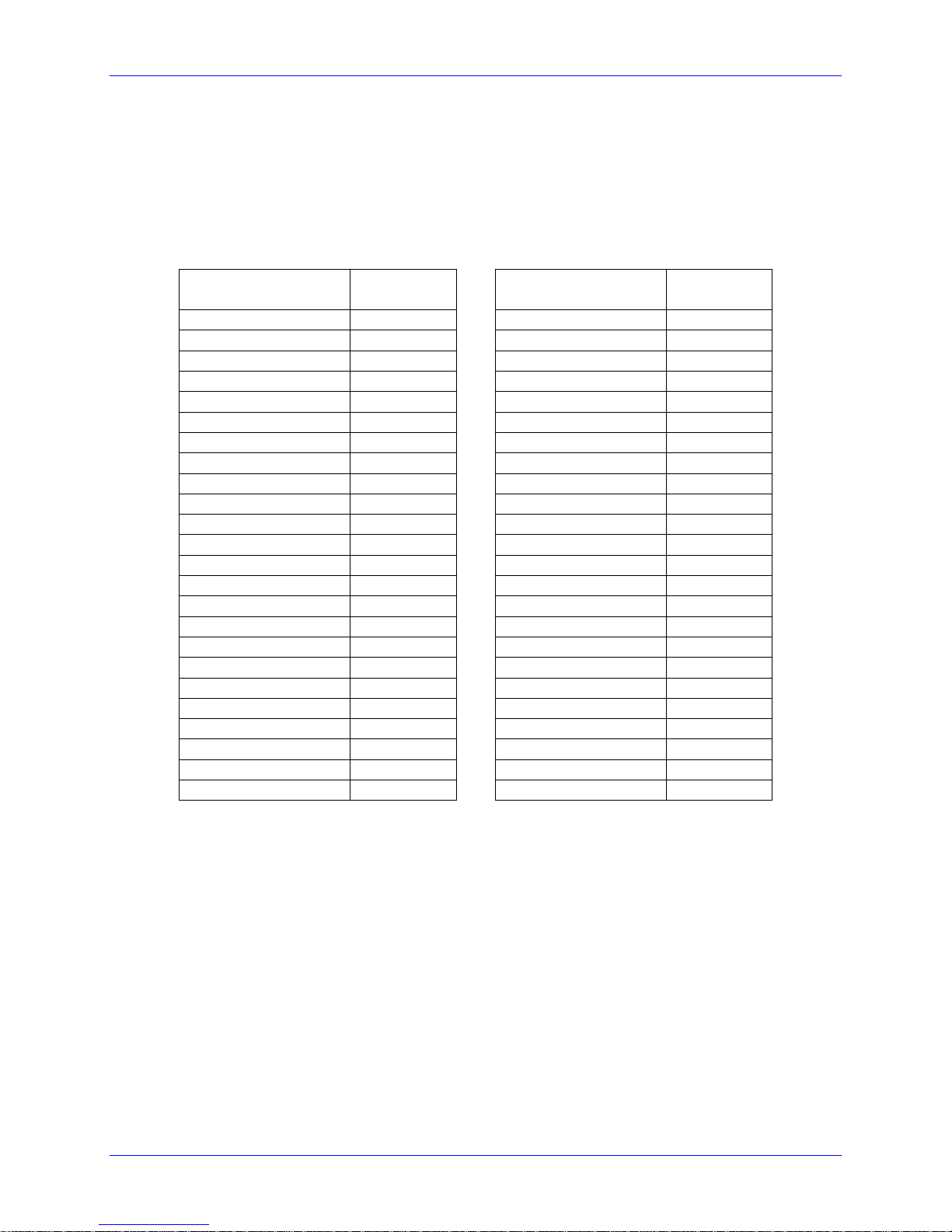

Example: Reading from and Writing to I/O Points on One ACC-11E with CPLC0

This example is for an ACC-11E at base address offset $A00000 with low-byte addressing.

Every scan, the following Background CPLC (BGCPLC0) reads all inputs on the ACC-11E and places

them into P-Variables (P7000–P7023) for general purpose use. The BGCPLC will also read from

P-Variables (P8000–P8023) and write their values to the output pins of ACC-11E as follows:

P-Variable Number

Pin

Number

P-Variable Number

Pin

Number

P7000

Input 0 P8000

Output 0

P7001

Input 1 P8001

Output 1

P7002

Input 2 P8002

Output 2

P7003

Input 3 P8003

Output 3

P7004

Input 4 P8004

Output 4

P7005

Input 5 P8005

Output 5

P7006

Input 6 P8006

Output 6

P7007

Input 7 P8007

Output 7

P7008

Input 8 P8008

Output 8

P7009

Input 9 P8009

Output 9

P7010

Input 10 P8010

Output 10

P7011

Input 11 P8011

Output 11

P7012

Input 12 P8012

Output 12

P7013

Input 13 P8013

Output 13

P7014

Input 14 P8014

Output 14

P7015

Input 15 P8015

Output 15

P7016

Input 16 P8016

Output 16

P7017

Input 17 P8017

Output 17

P7018

Input 18 P8018

Output 18

P7019

Input 19 P8019

Output 19

P7020

Input 20 P8020

Output 20

P7021

Input 21 P8021

Output 21

P7022

Input 22 P8022

Output 22

P7023

Input 23 P8023

Output 23

Page 26

ACC-11E User Manual

Using ACC-11E with Power UMAC 26

Example Code: Using BGCPLC1 as an example.

This example assumes that “acc11e.h” and “acc11e.c” have already been placed into the same folder as

the BGCPLC under C LanguageCPLCsbgcplc00 in the Power PMAC IDE Solution Explorer.

#include <gplib.h>

#include <stdio.h>

#include <dlfcn.h>

#include "../../Include/pp_proj.h"

#include "acc11e.h"

void user_plcc()

{

unsigned int ChannelNumber, ArrayIndex; // Allocate indices

for(ChannelNumber = 1; ChannelNumber < 25; ChannelNumber++)

{

ArrayIndex = ChannelNumber - 1;

/* Copy the state of each input into P7000-P7023 */

pshm->P[7000 + ArrayIndex] =

(double)ACC11E_GetInputState(ACC11E_BaseAddressOffset_E1, ByteSelectLow, ChannelNumber);

/* Copy the state of P8000-P8023 into outputs 1-24 */

ACC11E_SetOutputState(ACC11E_BaseAddressOffset_E1, ByteSelectLow, ChannelNumber,

(unsigned int)pshm->P[8000 + ArrayIndex]);

}

return;

}

User Written Functions

User written functions can be created as an alternative to the above described functions.

To do so:

Point a volatile unsigned int* pointer variable to the desired ACC-11E memory

location

Perform a whole 32-bit read of the memory location

To read I/O states, mask and shift to read the appropriate bit in the word; i.e., the state of

the I/O point

To write I/O states, perform a read-modify-write to change the appropriate bit in the

word (e.g., to enable or disable an output)

Table of ACC-11E I/O Registers in C

To access the I/O pins in ACC-11E, point a volatile unsigned int* pointer to the following registers:

Base Address

A00000

Base Address

B00000

Base Address

C00000

Base Address

D00000

Register

Description

piom+0xA00000/4+0

piom+0xB00000/4+0

piom+0xC00000/4+0

piom+0xD00000/4+0

Inputs 1–8

piom+0xA00000/4+1

piom+0xB00000/4+1

piom+0xC00000/4+1

piom+0xD00000/4+1

Inputs 9–16

piom+0xA00000/4+2

piom+0xB00000/4+2

piom+0xC00000/4+2

piom+0xD00000/4+2

Inputs 17–24

piom+0xA00000/4+3

piom+0xB00000/4+3

piom+0xC00000/4+3

piom+0xD00000/4+3

Outputs 1–8

piom+0xA00000/4+4

piom+0xB00000/4+4

piom+0xC00000/4+4

piom+0xD00000/4+4

Outputs 9–16

piom+0xA00000/4+5

piom+0xB00000/4+5

piom+0xC00000/4+5

piom+0xD00000/4+5

Outputs 17–24

piom+0xA00000/4+7

piom+0xB00000/4+7

piom+0xC00000/4+7

piom+0xD00000/4+7

Control Word

Page 27

ACC-11E User Manual

Using ACC-11E with Power UMAC 27

The useful data in each of these registers will be found in bits 8–32; the ACC-11E in Power PMAC does

not use bits 0–7 of any of its registers. The base addresses (left to right four columns) and bytes (right

end column) are selected with jumpers (see Addressing Setup and Jumper Settings section).

Only whole words at a time can be read in C; therefore, it is necessary to mask (using the bitwise “&”

operator) and shift (using the “<<” and “>>” operators) to obtain bit values.

A set of pointer variables can be predefined to each I/O register. Alternatively, a set of functions can be

created for reading and writing that will automatically point to, read from, and/or modify the appropriate

memory location, given the card’s base address, byte select, and pin number.

Page 28

ACC-11E User Manual

Using ACC-11E with Power UMAC 28

Setting Up the Control Word

The Control Word must be set equal to 7 every startup.

The function of each bit in the control word is as follows:

Control Word Bit Number

Value

I/O Bits

Modified

I/O Bits

Function

0

1

0–7

Inputs 1-8

1

1

8–15

Inputs 9-16

2

1

16–23

Inputs 17-24

3

0

24–31

Outputs 1-8

4

0

32–39

Outputs 9-16

5

0

40–47

Outputs 17-24

6

0

None

Register Select

7

0

None

Register Select

Example: Setting the Control Word in C in a Background C Program

This example Background C Program sets the Control Word equal to 7 for an ACC-11E at base address

offset $A00000 with low byte addressing using a Background C Program, and then returns.

#include <gplib.h> // Global Gp Shared memory pointer

#include "../../Include/pp_proj.h"

#include "acc11e.h"

int main(void)

{

InitLibrary();

ACC11E_SetControlWord(ACC11E_BaseAddressOffset_E1, ByteSelectLow);

CloseLibrary();

return 0;

}

In order for this program to run at startup, make sure to enable that option. For example, here a project

called “MultithreadedIO” has been created with the “acc11e_controlword” program created under C

LanguageBackground Programs. Then, from within the IDE Solution Explorer tree, go to

C LanguageBackground Programsacc11e_controlword, and then right-click on the

“acc11e_controlword” folder name and select Properties. Then, in the Properties tab, under “CPLC

Startup Option,” put a “1” (without the quotation marks) into the field next to the parameter “Run at

startup” (see the screenshot below).

Page 29

ACC-11E User Manual

Using ACC-11E with Power UMAC 29

Remember to put acc11e.c and acc11e.h from the previous section into the same folder as this BGCPLC

in order to run it properly.

Note

See Appendix for control word details and explanations.

Page 30

ACC-11E User Manual

Using ACC-11E with UMAC MACRO Station 30

USING ACC-11E WITH UMAC MACRO STATION

Setting up an ACC-11E on a MACRO station requires the following steps:

Establishing communication with the MACRO Station and enabling nodes

(Covered in alternate documentation i.e. MACRO16 CPU User Manual)

Setting up the control word

Transferring data over I/O Nodes

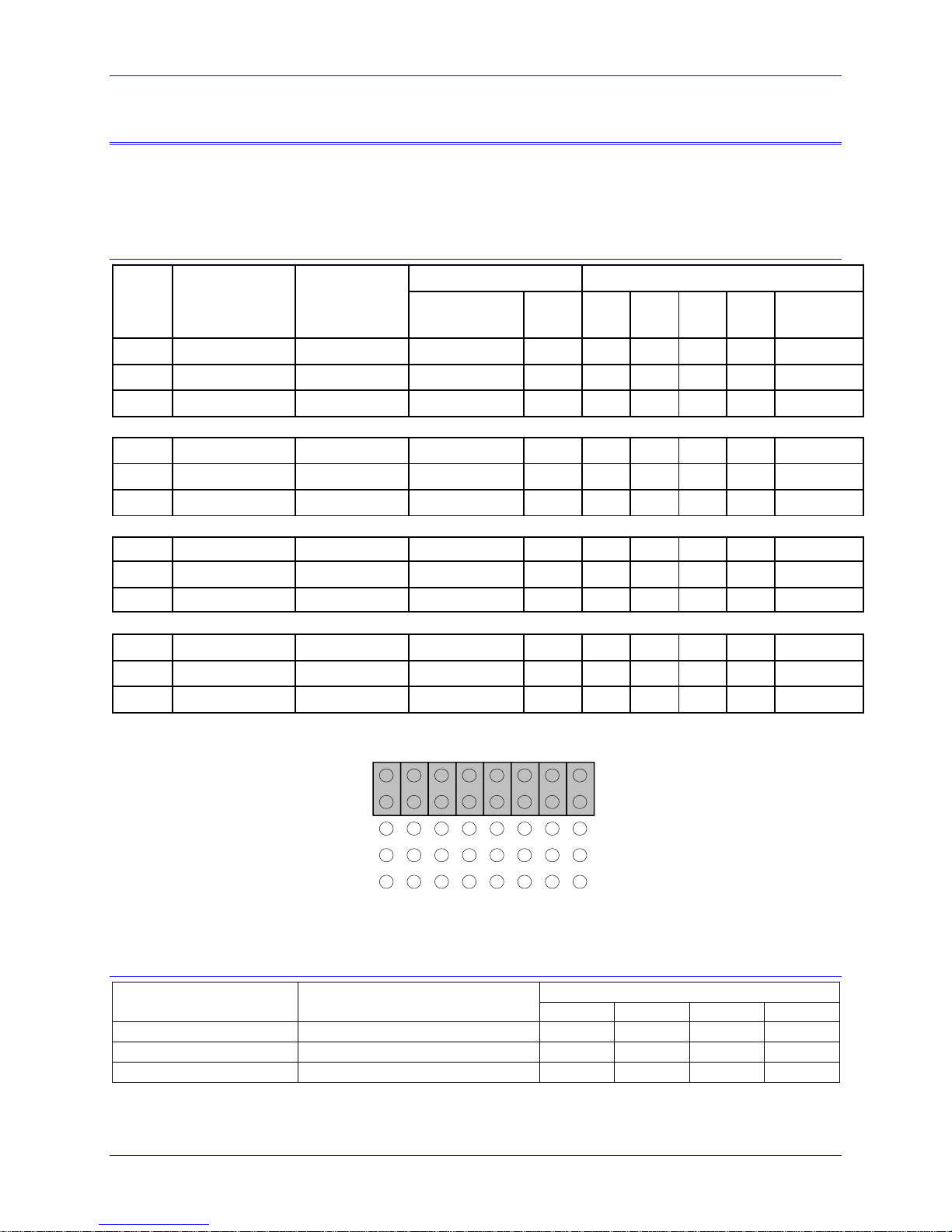

Quick Review: Nodes and Addressing

MACRO

CPU

ACC-11E

MACRO Station

Ring Controller

I/O Processing

User Access

$88XX$7 XXXX

I/O Data

Transfer

Automatic

Firmware Copy

Ultralite

Or

UMAC with ACC-5E

$C0XX

The above diagram represents three basic processes.

1. Starting on the right with I/O Processing, information is transferred to or from the ACC-11E I/O

Gate and the MACRO-Station CPU Gate 2B.

2. I/O is transferred between MACRO Station ($C0XX) and Ring Controller ($7XXXX) nodes.

ACC-11E input data is written to MACRO IC addresses ($7XXXX) on the Ring Controller, and

Ring Controller output data is written to MACRO Station IC addresses ($C0XX) on the MACRO

Station.

3. User Access: Ring Controller ($7XXXX) addresses are accessed thru M-Variables and used in

PLC and motion programs.

Note

The Ring Controller is sometimes referred to as the Master, but it is

the synchronizing Master. There can be more than one Master on a

MACRO ring, but there must be one, and only one, Ring Controller.

Note

Refer to the 16-Axis MACRO CPU manuals (SRM, USER, and

HRM) for more information on MACRO.

Page 31

ACC-11E User Manual

Using ACC-11E with UMAC MACRO Station 31

Each MACRO IC consists of 16 nodes: 2 auxiliary, 8 servo, and 6 I/O nodes.

Auxiliary nodes are for Ring Controller/Control registers and internal firmware use.

Servo nodes are used for motor control, carrying feedback, commands, and flag information.

I/O nodes are by default unoccupied and are user configurable for transferring various data.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0Node

Auxiliary

Nodes

I/ O Nodes

Servo Nodes

Each I/O node consists of 4 registers; one 24-bit and three 16-bit registers for a total of 72 bits of data:

5 4 2 1 0

24-bit

1st 16-bit

2

nd

16-bit

3rd 16-bit

3

24-bit

1st 16-bit

2

nd

16-bit

3rd 16-bit

6

24-bit

1st 16-bit

2

nd

16-bit

3rd 16-bit

7

24-bit

1st 16-bit

2

nd

16-bit

3rd 16-bit

9 810

24-bit

1st 16-bit

2

nd

16-bit

3rd 16-bit

11

24-bit

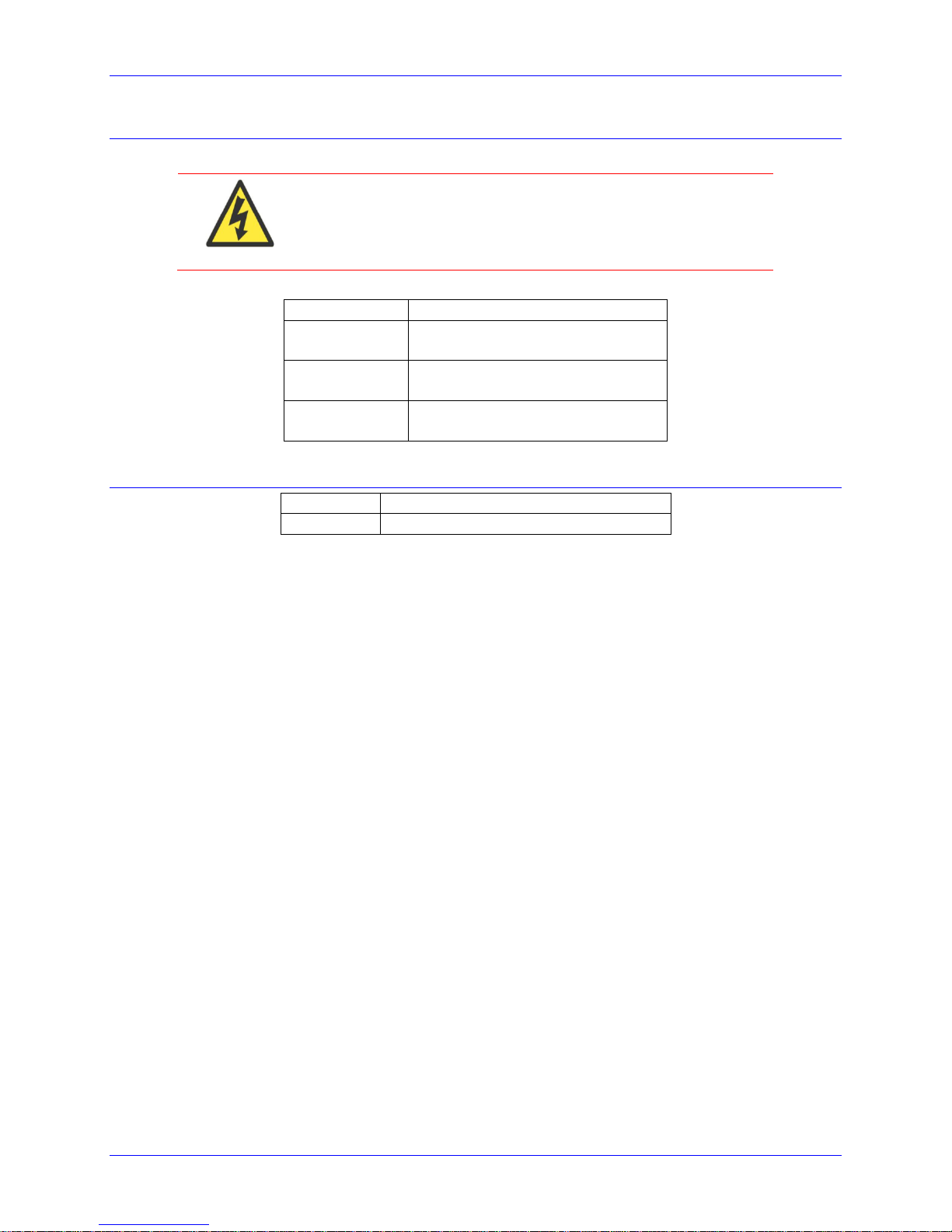

1st 16-bit

2

nd

16-bit

3rd 16-bit

13 12

A given MACRO Station can be populated with either a MACRO8 or MACRO16 CPU:

MACRO8 supports 1 MACRO IC (IC#0).

MACRO16 supports 2 MACRO ICs (IC#0 and IC#1).

The I/O node addresses ($C0XX) on the MACRO Station ICs are:

MACRO Station IC #0 Node Registers

Node 2 3 6 7

10

11

24-bit

X:$C0A0

X:$C0A4

X:$C0A8

X:$C0AC

X:$C0B0

X:$C0B4

16-bit

X:$C0A1

X:$C0A5

X:$C0A9

X:$C0AD

X:$C0B1

X:$C0B5

16-bit

X:$C0A2

X:$C0A6

X:$C0AA

X:$C0AE

X:$C0B2

X:$C0B6

16-bit

X:$C0A3

X:$C0A7

X:$C0AB

X:$C0AF

X:$C0B3

X:$C0B7

MACRO Station IC #1 Node Registers

Node 2 3 6 7

10

11

24-bit

X:$C0E0

X:$C0E4

X:$C0E8

X:$C0EC

X:$C0F0

X:$C0F4

16-bit

X:$C0E1

X:$C0E5

X:$C0E9

X:$C0ED

X:$C0F1

X:$C0F5

16-bit

X:$C0E2

X:$C0E6

X:$C0EA

X:$C0EE

X:$C0F2

X:$C0F6

16-bit

X:$C0E3

X:$C0E7

X:$C0EB

X:$C0EF

X:$C0F3

X:$C0F7

Page 32

ACC-11E User Manual

Using ACC-11E with UMAC MACRO Station 32

A given Ring Controller (Turbo PMAC2 Ultralite or UMAC with

two ACC-5Es) can be populated with up to 4 MACRO ICs (IC#0,

IC#1, IC#2, and IC#3) which can be queried with global variable

I4902:

If I4902=

Populated

MACRO IC #s

$0

None

$1

0

$3

0, 1

$7

0, 1, 2

$F

0, 1, 2, 3

The I/O node addresses ($7XXXX) for each of the Ring Controller MACRO ICs are:

Ring Controller MACRO IC #0 Node Registers

Station I/O Node#

2 3 6 7 10

11

Ring Controller

I/O Node#

2 3 6 7 10

11

24-bit

X:$78420

X:$78424

X:$78428

X:$7842C

X:$78430

X:$78434

16-bit

X:$78421

X:$78425

X:$78429

X:$7842D

X:$78431

X:$78435

16-bit

X:$78422

X:$78426

X:$7842A

X:$7842E

X:$78432

X:$78436

16-bit

X:$78423

X:$78427

X:$7842B

X:$7842F

X:$78433

X:$78437

Ring Controller MACRO IC #1 Node Registers

Station I/O Node#

2 3 6 7 10

11

Ring Controller

I/O Node#

18

19

22

23

26

27

24-bit

X:$79420

X:$79424

X:$79428

X:$7942C

X:$79430

X:$79434

16-bit

X:$79421

X:$79425

X:$79429

X:$7942D

X:$79431

X:$79435

16-bit

X:$79422

X:$79426

X:$7942A

X:$7942E

X:$79432

X:$79436

16-bit

X:$79423

X:$79427

X:$7942B

X:$7942F

X:$79433

X:$79437

Ring Controller MACRO IC #2 Node Registers

Station I/O Node#

2 3 6 7 10

11

Ring Controller

I/O Node#

34

35

38

39

42

43

24-bit

X:$7A420

X:$7A424

X:$7A428

X:$7A42C

X:$7A430

X:$7A434

16-bit

X:$7A421

X:$7A425

X:$7A429

X:$7A42D

X:$7A431

X:$7A435

16-bit

X:$7A422

X:$7A426

X:$7A42A

X:$7A42E

X:$7A432

X:$7A436

16-bit

X:$7A423

X:$7A427

X:$7A42B

X:$7A42F

X:$7A433

X:$7A437

Ring Controller MACRO IC #3 Node Registers

Station I/O Node#

2 3 6 7 10

11

Ring Controller I/O

Node#

50

51

54

55

58

59

24-bit

X:$7B420

X:$7B424

X:$7B428

X:$7B42C

X:$7B430

X:$7B434

16-bit

X:$7B421

X:$7B425

X:$7B429

X:$7B42D

X:$7B431

X:$7B435

16-bit

X:$7B422

X:$7B426

X:$7B42A

X:$7B42E

X:$7B432

X:$7B436

16-bit

X:$7B423

X:$7B427

X:$7B42B

X:$7B42F

X:$7B433

X:$7B437

Page 33

ACC-11E User Manual

Using ACC-11E with UMAC MACRO Station 33

Setting Up The Control Word

The Control Word must be set equal to 7 once on power-up, usually in an initialization PLC. The advised

method to set up the control word with MACRO is using the direct read/write parameters:

MS{anynode}, MI198 Direct Read/Write Format and Address

MS{anynode}, MI199 Direct Read/Write variable

Note

The direct read/write parameters require MACRO16 CPU firmware

1.16 or later.

The MS{anynode}, MI198 setting is base address (and byte location) dependent:

Chip Select

Base Address

Byte Location

Control Word Location

MI198 Setting

CS10

Y:$8800

Low

Y:$8807,0,8

MI198=$408807

Middle

Y:$8807,8,8

MI198=$488807

High

Y:$8807,16,8

MI198=$508807

CS12

Y:$8840

Low

Y:$8847,0,8

MI198=$408847

Middle

Y:$8847,8,8

MI198=$488847

High

Y:$8847,16,8

MI198=$508847

CS14

Y:$8880

Low

Y:$8887,0,8

MI198=$408887

Middle

Y:$8887,8,8

MI198=$488887

High

Y:$8887,16,8

MI198=$508887

CS16

Y:$88C0

Low

Y:$88C7,0,8

MI198=$4088C7

Middle

Y:$88C7,8,8

MI198=$4888C7

High

Y:$88C7,16,8

MI198=$5088C7

Note

CS16 Cannot be used with legacy MACRO16 CPU’s (rev 100 –104)

Note

MI198 and MI199 can be written to directly from the Pewin32Pro2

terminal window. However, their values are not saved and should be

executed in a startup PLC.

Page 34

ACC-11E User Manual

Using ACC-11E with UMAC MACRO Station 34

Example: Writing control words for two ACC-11E cards set to base addresses $8800,0,8 and $8800,8,8

Open PLC 1 Clear

I5111=1000*8388608/I10 while(I5111>0) endw ; 1-sec delay

CMD"MS0,MI198=$408807" ; Set control word for first ACC-11E at $8800 low byte addresses

CMD"MS0,MI199=$07" ; Write $07 into Y:$8807,0,8 (control word)

I5111=50*8388608/I10 while(I5111>0) endw ; 50-msec delay

CMD"MS0,MI198=$488807" ; Set control word for second ACC-11E at $8800 mid byte addresses

CMD"MS0,MI199=$07" ; Write $07 into Y:$8807,8,8 (control word)

I5111=50*8388608/I10 while(I5111>0) endw ; 50-msec delay

Disable PLC 1

Close

Note

See appendix for further control word details.

Page 35

ACC-11E User Manual

Using ACC-11E with UMAC MACRO Station 35

Transferring Data Points over I/O Nodes

This section illustrates how I/O data is transferred from ACC-11E ($88XX) registers, thru I/O nodes

($C0XX), and finally to the ring controller ($7XXXX) for user access using M-Variable pointers.

Note

It is assumed that communication over the MACRO ring has already

been established, and that the user is familiar with node activation on

both the Ring Controller and MACRO Station. Thus, any node(s)

used in subsequent example(s) have to have been enabled

previously.

Generally, there are three basic transfer methods. The decision of which to use might depend on what

types of I/O cards, and how many, are being used. The MI71 method is the typical choice for handling up

to six ACC-11E cards in one rack.

MACRO Station IC#0

Transfer MI-Variable

Used For:

Transfer Type

MI71

Most Applications

24-bit

MI69, MI70

Special cases, if:

24-bit registers are already in use

More than six cards are needed

16-Bit

MI171, MI172,

MI173

Special cases, if:

It is desired to fit 3 cards into 2 I/O nodes

More than six cards needed

24-Bit / 16-Bit

MACRO Station IC#1

Transfer MI-Variable

Used For:

Transfer Type

MI1071

Most Applications

24-bit

MI1069, MI1070

Special cases, if:

24-bit registers are already in use

More than six cards are needed

16-Bit

MI1171, MI1172,

MI1173

Special cases, if:

It is desired to fit 3 cards into 2 I/O nodes

More than six cards needed

24-Bit / 16-Bit

Note

The MACRO16 CPU is populated with 2 MACRO ICs (IC #0 and

#1), each of which has its own I/O transfer variables.

Page 36

ACC-11E User Manual

Using ACC-11E with UMAC MACRO Station 36

Preparing for I/O Data Transfer on the MACRO16 Station

The following parameters should be configured properly for the I/O node transfer to work properly:

MS{anynode}, MI992 Max. Phase frequency control

Typically, set to equal to ring controller’s I6800

MS{anynode}, MI997 Phase clock frequency control

Typically, set to equal to ring controller’s I6801

MS{anynode}, MI995 MACRO Ring configuration/status

Typically, set to = $4080

MS{anynode}, MI996 MACRO IC#0 node activate control

MS{anynode}, MI975 MACRO IC#0 I/O Node enable

MI975 should match enabled I/O nodes in MI996

MS{anynode}, MI8 MACRO Ring check Period

Typically set to = 8 (with default clock settings)

MS{anynode}, MI9 MACRO Ring error shutdown count

Typically set to = 4 (with default clock settings)

MS{anynode}, MI10 MACRO Sync packet shutdown count

Typically set to = 4 (with default clock settings)

MS{anynode},MI19 I/O node data transfer rate

= 0, transfer disabled.

> 0, transfer period in Phase clock cycles (typically set =4).

MS{anynode}, MI1996 MACRO IC#1 node activate control (if IC#1 is used)

MS{anynode}, MI1975 MACRO IC#1 I/O Node enable (if IC#1 is used)

MI1975 should match enabled I/O nodes in MI1996

Note

The following I/O data transfer method examples assume that

MACRO communication, I/O nodes enabling, and other MACRO ring

parameters have been configured properly on both the ring Controller

and MACRO Station.

Page 37

ACC-11E User Manual

Using ACC-11E with UMAC MACRO Station 37

MS{anynode},MI71: 24-Bit Transfer

This method is typically used when six or less ACC-11E cards are present in the rack.

MS{anynode},MI71 processes 24-bit register transfers. It is a 48-bit variable represented as 12

hexadecimal digits which are set up as follows (digit #1 is leftmost when constructing the word):

No. of consecutive node pairs:

=1 for 2 IO nodes

=2 for 4 IO nodes

=3 for 6 IO nodes (max.)

Reserved, = 0

Starting I/O node register

($C0XX)

No. of 24-bit banks per board

Always = 2 for ACC-11E

1 2 3 - 6 7 8 9 - 12Digit #:

For ACC-11E, = 0

Starting ACC-11E base address

($88XX)

Example 1: Transferring I/O data of one ACC-11E card (total of 48 bits) at base address $8800 (using

low bytes) over MACRO using two consecutive 24-bit registers of I/O nodes 2 and 3 ($C0A0, and

$C0A4 respectively) yields:

MS0,MI71=$10C0A0208800

Inputs (24 bits) / Outputs(24 bits)

24 24

16

16

16

16

16

16

24 24

16

16

16

16

16

16

24 24

16

16

16

16

16

16

MACRO IC

I/O Node#: 2 3 6 7 10 11

$C0A0 $C0A4 $C0A8 $C0AC $C0B0 $C0B4

24-bit reg. Address:

ACC-11E ($8800)

Page 38

ACC-11E User Manual

Using ACC-11E with UMAC MACRO Station 38

Example 2: Transferring I/O data of two ACC-11E cards (total of 96 bits) at consecutive $8800 addresses

(using low and middle bytes) over MACRO using four consecutive 24-bit registers of I/O nodes 2, 3, 6,

and 7 ($C0A0, $C0A4, $C0A8, and $C0AC respectively) yields:

MS0,MI71=$20C0A0208800

Inputs (24 bits) / Outputs(24 bits)

24 24

16

16

16

16

16

16

24 24

16

16

16

16

16

16

24 24

16

16

16

16

16

16

MACRO IC

I/O Node#: 2 3 6 7 10 11

$C0A0 $C0A4 $C0A8 $C0AC $C0B0 $C0B4

24-bit reg. Address:

ACC-11E ($8800 low bytes)

Inputs (24 bits) / Outputs(24 bits)

ACC-11E ($8800 middle bytes)

Example 3: Transferring I/O data of three ACC-11E cards (total of 144 bits) at consecutive $8800

addresses (using low, middle, and high bytes) over MACRO using six consecutive 24-bit registers of I/O

nodes 2, 3, 6, 7, 10, and 11 ($C0A0, $C0A4, $C0A8, $C0AC, $C0B0, and $C0B4 respectively) yields:

MS0,MI71=$30C0A0208800

24 24

16

16

16

16

16

16

24 24

16

16

16

16

16

16

24 24

16

16

16

16

16

16

MACRO IC

I/O Node#: 2 3 6 7 10 11

$C0A0 $C0A4 $C0A8 $C0AC $C0B0 $C0B4

24-bit reg. Address:

Inputs (24 bits) / Outputs(24 bits)

ACC-11E ($8800 low bytes)

Inputs (24 bits) / Outputs(24 bits)

ACC-11E ($8800 middle bytes)

Inputs (24 bits) / Outputs(24 bits)

ACC-11E ($8800 high bytes)

Page 39

ACC-11E User Manual

Using ACC-11E with UMAC MACRO Station 39

Example 4: Transferring I/O data of the maximum of six ACC-11E cards (total of 288 bits) at

consecutive $8800 addresses (using low, middle, and high bytes) and consecutive $8840 addresses (using

low, middle, and high bytes) over MACRO using six consecutive 24-bit registers of IC#0 I/O nodes 2, 3,

6, 7, 10, and 11 ($C0A0, $C0A4, $C0A8, $C0AC, $C0B0, and $C0B4 respectively) and six consecutive

IC#1 I/O nodes 2, 3, 6, 7, 10, and 11 ($C0E0, $C0E4, $C0E8, $C0EC, $C0F0, and $C0F4 respectively)

yields:

MS0,MI71=$30C0A0208800

MS0,MI1071=$30 C0E0208840

Note

Transferring multiple ACC-11E cards using MS{anynode},

MI71 requires them to be at the same base address, starting with

the first card set for low byte addressing, the second card set for

middle byte addressing, and then a third card (if present) set for

high byte addressing.

The 24-bit node registers used with MS{anynode}, MI71 must

be at consecutive addresses.

Note

A save MSSAV{anynode}, followed by a reset MS$$${anynode) at

the MACRO station is necessary for MI71 transfers to take effect.

Once a transfer is enabled, the I/O data is copied automatically by the firmware into the ring controllers’

node registers ($7XXXX) where it is accessible to the user. However, the MACRO protocol limits

handling of these registers to full words (16- or 24-bit).

The inputs can be read directly in full word assignments. The outputs can be written to directly in full

word assignments, but cannot report their current state.

Note

Reading the state of inputs can be done directly from I/O node

registers ($7XXXX) using full word assignments.

Note

Writing to outputs can be done directly to I/O node registers

($7XXXX) using full word assignments; however, reading the state

of outputs is not possible.

Page 40

ACC-11E User Manual

Using ACC-11E with UMAC MACRO Station 40

Creating input and output image (mirrored) words in a PLC program allows bitwise assignments, full user

access, and state reporting. The following diagram illustrates the basic concept of mirroring:

$7XXXX

Inputs

Outputs

PLC program

If inputs state has changed:

Copy full word to unused memory location

If user outputs have changed:

Copy full word to unused memory location

User Access

Inputs

Outputs

Write

WriteRead

Read

Example: For “example 1” above, using MI71 24-bit transfer to process one ACC-11E over MACRO

using I/O nodes 2 and 3, the following assignments and PLC program demonstrate the mirroring

implementation:

#define Inputs M4000 ; M-Variable pointer to hold 24-bit inputs

#define Outputs M4001 ; M-Variable pointer to hold 24-bit outputs

Inputs->X:$78420,0,24,U ; I/O Node 2 24-bit register (inputs)

Outputs->X:$78424,0,24,U ; I/O Node 3 24-bit register (outputs)

#define InMirror M4002 ; M-Variable pointer to hold inputs mirror word

#define OutMirror M4003 ; M-Variable pointer to hold outputs mirror word

#define OutState M4004 ; M-Variable pointer to latch current outputs state

InMirror->X:$10F0,0,24,U ; Reserve unused memory register (to hold inputs)

OutMirror->Y:$10F0,0,24,U ; Reserve unused memory register (to hold outputs)

OutState->* ; Self referenced

OutState=0 ; Initialize =0 on download

Open plc 1 clear

If (InMirror!=Inputs) ; Inputs state changed?

InMirror=Inputs ; Update inputs mirror word to match current state

EndIf ;

If (OutState!=OutMirror) ; Outputs state changed?

OutState=OutMirror ; Update state of outputs mirror word

Outputs=OutMirror ; Update outputs

EndIf

Close

Note

With the ACC-11E (or any other 24In/24Out card), the inputs are

copied through the first of the two 24-bit registers, and the outputs

are copied through the second of the two 24-bit registers.

Note

Turbo PMAC unusued (open) memory registers can be either X or Y

located at X/Y:$10F0 - $10FF (total of 32).

Make sure that the registers chosen for mirroring are not used in

another process.

Page 41

ACC-11E User Manual

Using ACC-11E with UMAC MACRO Station 41

The I/O data is now available in the pre-defined open memory registers. Bitwise maping can be

implemented for direct and convenient user access:

// Inputs

#define Input1 M3300 Input1->X:$0010F0,0

#define Input2 M3301 Input2->X:$0010F0,1

#define Input3 M3302 Input3->X:$0010F0,2

#define Input4 M3303 Input4->X:$0010F0,3

#define Input5 M3304 Input5->X:$0010F0,4

#define Input6 M3305 Input6->X:$0010F0,5

#define Input7 M3306 Input7->X:$0010F0,6

#define Input8 M3307 Input8->X:$0010F0,7

#define Input9 M3308 Input9->X:$0010F0,8

#define Input10 M3309 Input10->X:$0010F0,9

#define Input11 M3310 Input11->X:$0010F0,10

#define Input12 M3311 Input12->X:$0010F0,11

#define Input13 M3312 Input13->X:$0010F0,12

#define Input14 M3313 Input14->X:$0010F0,13

#define Input15 M3314 Input15->X:$0010F0,14

#define Input16 M3315 Input16->X:$0010F0,15

#define Input17 M3316 Input17->X:$0010F0,16

#define Input18 M3317 Input18->X:$0010F0,17

#define Input19 M3318 Input19->X:$0010F0,18

#define Input20 M3319 Input20->X:$0010F0,19

#define Input21 M3320 Input21->X:$0010F0,20

#define Input22 M3321 Input22->X:$0010F0,21

#define Input23 M3322 Input23->X:$0010F0,22

#define Input24 M3323 Input24->X:$0010F0,23

// Outputs

#define Output1 M3325 Output1->Y:$0010F0,0

#define Output2 M3326 Output2->Y:$0010F0,1

#define Output3 M3327 Output3->Y:$0010F0,2

#define Output4 M3328 Output4->Y:$0010F0,3

#define Output5 M3329 Output5->Y:$0010F0,4

#define Output6 M3330 Output6->Y:$0010F0,5

#define Output7 M3331 Output7->Y:$0010F0,6

#define Output8 M3332 Output8->Y:$0010F0,7

#define Output9 M3333 Output9->Y:$0010F0,8

#define Output10 M3334 Output10->Y:$0010F0,9

#define Output11 M3335 Output11->Y:$0010F0,10

#define Output12 M3336 Output12->Y:$0010F0,11

#define Output13 M3337 Output13->Y:$0010F0,12

#define Output14 M3338 Output14->Y:$0010F0,13

#define Output15 M3339 Output15->Y:$0010F0,14

#define Output16 M3340 Output16->Y:$0010F0,15

#define Output17 M3341 Output17->Y:$0010F0,16

#define Output18 M3342 Output18->Y:$0010F0,17

#define Output19 M3343 Output19->Y:$0010F0,18

#define Output20 M3344 Output20->Y:$0010F0,19

#define Output21 M3345 Output21->Y:$0010F0,20

#define Output22 M3346 Output22->Y:$0010F0,21

#define Output23 M3347 Output23->Y:$0010F0,22

#define Output24 M3348 Output24->Y:$0010F0,23

Page 42

ACC-11E User Manual

Using ACC-11E with UMAC MACRO Station 42

MS{anynode},MI69 and MI70: 16-Bit Transfer

This method is generally only used in special cases in which the 24-bit transfer method cannot be used

because either the 24-bit registers are already being used or because more than six ACC-11E cards are

needed.

MS{anynode},MI69/70 processes 16-bit register transfers. It is a 48-bit variable represented as 12

hexadecimal digits which are set up as follows (digit #1 is leftmost when constructing the word):

No. of consecutive nodes:

=1 for 1 IO node

=2 for 2 IO nodes

=3 for 3 IO nodes (max.)

Reserved, = 0

Starting I/O node register

($C0XX)

No. of 16-bit banks per board

Always = 3 for ACC-11E

1 2 3 - 6 7 8 9 - 12Digit #:

For ACC-11E, = 0

Starting ACC-11E base address

($88XX)

Example: Transferring I/O data of one ACC-11E card (total of 48 bits) at base address $8800 over

MACRO using three consecutive 16-bit registers of I/O node 2 ($C0A1, $C0A2, and $C0A3,

respectively) yields:

MS0,MI69=$10C0A1308800

24

16

16

16

$C0A1

$C0A2

$C0A3

2

ACC-11E ($8800)

16 bits

Inputs

8 bits 8 bits

Outputs

16 bits

I/O Node#:

16-bit reg. Addresses:

Page 43

ACC-11E User Manual

Using ACC-11E with UMAC MACRO Station 43

Note

Transferring multiple ACC-11E cards using MS{anynode},

MI69 and MI70 requires them to be at the same base address,

starting with the first card set for low byte addressing, the second

card set for middle byte addressing, and then a third card (if

present) set for high byte addressing.

The 16-bit node registers used with MS{anynode}, MI69 and

MI70 must be at consecutive addresses.

Note

A save MSSAV{anynode}, followed by a reset MS$$${anynode) at

the MACRO station is necessary for MI69 and MI70 transfers to

take effect.

The I/O data is now copied automatically by the firmware into the ring controllers’ node registers

($7XXXX) where it is accessible by the user. However, the MACRO protocol limits handling of these

registers to full words (16- or 24-bit).

The inputs can be read directly in full word assignments. The outputs can be written to directly in full

word assignments, but cannot report their current state.

Note

Reading the state of inputs can be done directly from I/O node