Page 1

^1 HARDWARE REFERENCE MANUAL

^2 UMAC-CPCI

Turbo CPU Board

^3 Turbo CPU Board

^4 4Ax-603625-xUxx

^5 January 28, 2003

Single Source Machine Control Power // Flexibility // Ease of Use

21314 Lassen Street Chatsworth, CA 91311 // Tel. (818) 998-2095 Fax. (818) 998-7807 // www.deltatau.com

Page 2

Copyright Information

© 2003 Delta Tau Data Systems, Inc. All rights reserved.

This document is furnished for the customers of Delta Tau Data Systems, Inc. Other uses are

unauthorized without written permission of Delta Tau Data Systems, Inc. Information contained

in this manual may be updated from time-to-time due to product improvements, etc., and may not

conform in every respect to former issues.

To report errors or inconsistencies, call or email:

Delta Tau Data Systems, Inc. Technical Support

Phone: (818) 717-5656

Fax: (818) 998-7807

Email: support@deltatau.com

Website: http://www.deltatau.com

Operating Conditions

All Delta Tau Data Systems, Inc. motion controller products, accessories, and amplifiers contain

static sensitive components that can be damaged by incorrect handling. When installing or

handling Delta Tau Data Systems, Inc. products, avoid contact with highly insulated materials.

Only qualified personnel should be allowed to handle this equipment.

In the case of industrial applications, we expect our products to be protected from hazardous or

conductive materials and/or environments that could cause harm to the controller by damaging

components or causing electrical shorts. When our products are used in an industrial

environment, install them into an industrial electrical cabinet or industrial PC to protect them

from excessive or corrosive moisture, abnormal ambient temperatures, and conductive materials.

If Delta Tau Data Systems, Inc. products are exposed to hazardous or conductive materials and/or

environments, we cannot guarantee their operation.

Page 3

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

Table of Contents

INTRODUCTION.......................................................................................................................................................1

Associated Manuals...................................................................................................................................................2

BOARD CONFIGURATION.....................................................................................................................................3

Option 1: Communications Interfaces.......................................................................................................................3

Option 2: Dual-Ported RAM.....................................................................................................................................3

Option 5: CPU and Memory Configurations.............................................................................................................3

Option 8: High-Accuracy Clock Crystal...................................................................................................................4

Option 9: Serial Port Configuration ..........................................................................................................................4

Option 10: Firmware Revision Specification............................................................................................................4

Option 16: Battery-Backed Parameter Memory........................................................................................................4

HARDWARE SETUP.................................................................................................................................................5

Clock-Source Jumpers...............................................................................................................................................5

Watchdog Timer Jumper...........................................................................................................................................5

Operation Mode Jumpers..........................................................................................................................................5

Firmware Reload Jumper..........................................................................................................................................5

Re-Initialization Jumper............................................................................................................................................5

Serial-Port Level Select Jumpers...............................................................................................................................6

DPRAM IC Select Jumper........................................................................................................................................6

Flash IC Firmware Bank Select Jumpers..................................................................................................................6

Flash IC Power Supply Select Jumper......................................................................................................................6

Power-Supply Check Select Jumper .........................................................................................................................6

Reset-Lock Jumper....................................................................................................................................................6

CONNECTIONS.........................................................................................................................................................7

Compact UBUS Connector.......................................................................................................................................7

Rear Field Wiring Connector....................................................................................................................................7

Front-Panel RS-232 Connector.................................................................................................................................7

Stack Connectors to Bridge Board............................................................................................................................7

Factory-Use Connectors............................................................................................................................................8

BOARD LAYOUT.......................................................................................................................................................9

JUMPER DESCRIPTIONS......................................................................................................................................11

E0: Reset-Lock Enable (Factory Use Only)............................................................................................................11

E1A: Servo and Phase Clock Direction Control......................................................................................................11

E1B: Servo/Phase Clock Source Control................................................................................................................11

E2: (Reserved for Future Use).................................................................................................................................11

E3: Re-Initialization on Reset Control....................................................................................................................12

E4: (Reserved for Future Use).................................................................................................................................12

E5: USB/Ethernet Communication Jumper.............................................................................................................12

E11: Power Supply Check Control..........................................................................................................................12

E17 – E18: Serial Port Select..................................................................................................................................12

E18A, B, C, D: Ethernet Communication Control..................................................................................................13

E19: Watchdog Disable Jumper..............................................................................................................................13

E20 – E22: Power-Up/Reset Load Source ..............................................................................................................13

E23: Firmware Reload Enable.................................................................................................................................13

E25A, B, C: Flash Memory Firmware Bank Select................................................................................................13

W1: Flash IC Power Supply Select Jumper.............................................................................................................14

CONNECTOR SUMMARY.....................................................................................................................................15

CONNECTOR PINOUTS.........................................................................................................................................17

Compact UBUS Connector (J1) Pin-Out.................................................................................................................17

Page 4

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

UMAC-CPCI Turbo CPU Board J2 Connector ......................................................................................................18

J4: RS-232 Serial Port Connector...........................................................................................................................19

ACCESSORIES.........................................................................................................................................................21

ACC-Cx Compact UBUS Backplane Boards..........................................................................................................21

ACC-8CR Test Breakout Board..............................................................................................................................21

ACC-11C Sinking I/O Board..................................................................................................................................21

ACC-24C2 PWM Axis Board.................................................................................................................................22

ACC-24C2A Analog Axis Board............................................................................................................................ 22

ACC-51C Analog Encoder Interpolator Board.......................................................................................................22

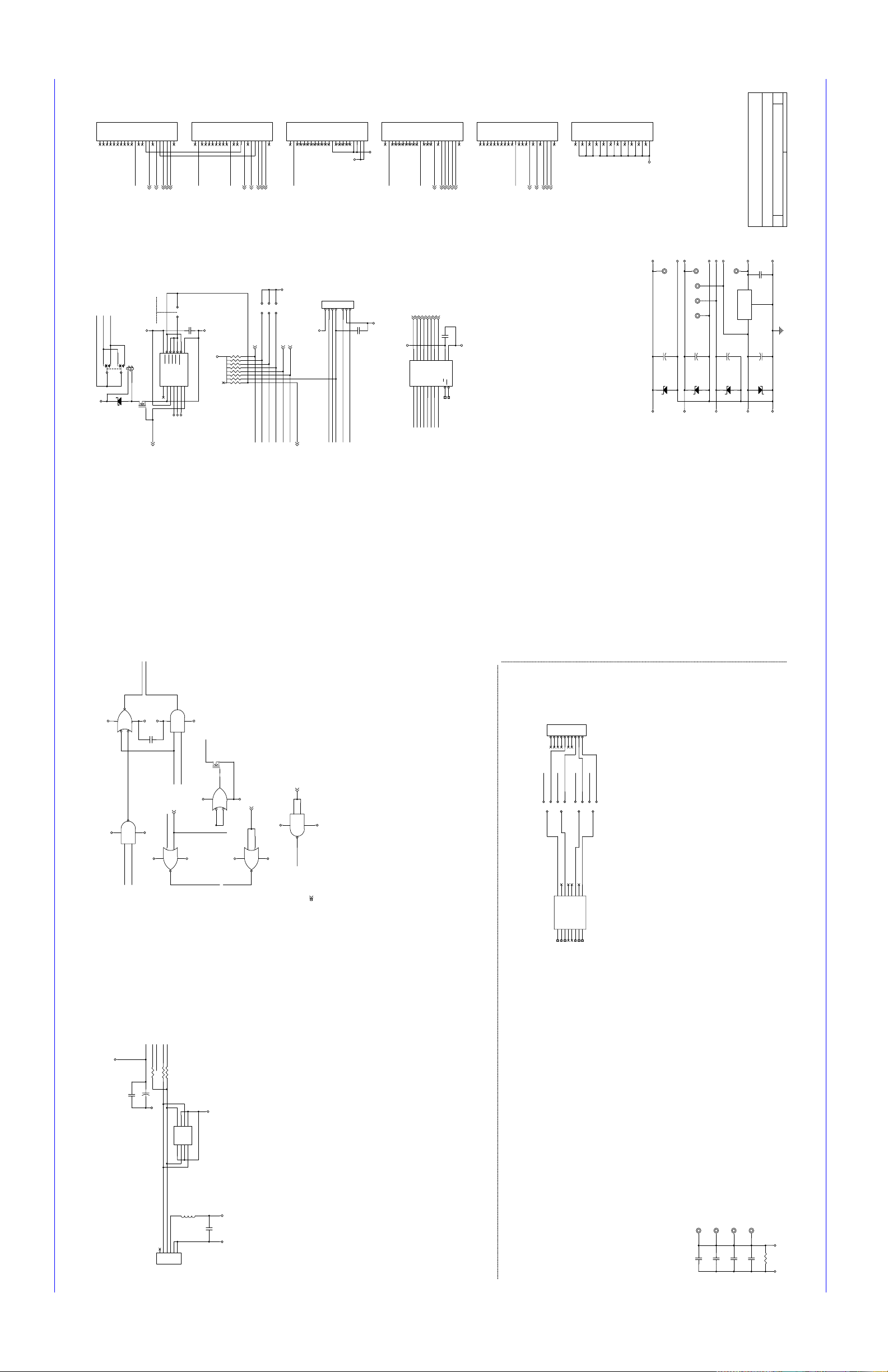

SCHEMATICS..........................................................................................................................................................23

Table of Contents

ii

Page 5

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

INTRODUCTION

Delta Tau’s UMAC-CPCI systems provide a compact and clean integration of motion and I/O control for

sophisticated automation equipment. The system consists of a modular set of 3U-size (100mm x 160mm)

boards in the “Compact PCI” format, implementing Turbo PMAC software and hardware functions,

communicating with each other over a common backplane (the “Compact UBUS”). All field wiring is

available on rear connectors, suitable for a user-designed distribution system to the machine. UMAC

(Universal Motion and Automation Controller) -CPCI systems provide integrated connectivity as well as

ease of assembly, diagnostics, and repair. UMAC-CPCI systems differ from “standard” UMAC systems

in that all field wiring comes to the back of the rack, behind the backplane, instead of direct top and

bottom access.

The UMAC-CPCI Turbo CPU board (Part number 3A0-603625-10x) implements a Turbo PMAC2 CPU

in the 3U CPCI form factor. Its software operation is completely identical to other Turbo PMAC2

controllers.

Note that a Compact PCI interface does not automatically come with a UMAC-CPCI system, nor is one

necessary to communicate to the system, given the other possible communications ports: RS-232, RS422, USB, and Ethernet.

This picture shows the UMAC-CPCI Turbo CPU

board. The connectors on the right side plug into the

“Compact UBUS” backplane board, with the bottom

right connector being the bus connector, and the top

right connector containing the external “field wiring”

signals, which typically pass through the backplane

board. The connector at lower left is an RS-232 port

intended for setup and diagnostics; the stack

connectors top and bottom provide the link to a CPCI

“bridge board”.

This picture shows a sample configuration of a

UMAC-CPCI system, not installed in its rack. It

consists of the following components:

1. Rack power supply (not a Delta Tau product)

2. UMAC-CPCI CPU board

3. ACC-11C Sinking I/O board

4. ACC-24C2A analog axis interface board

5. ACC-C8 8-slot Compact UBUS backplane.

Note the “pass-through” connector on the

back for field-wiring distribution. In this

picture, alternate slots in the backplane have

been left open to make each board more

visible. This does not have to be done in

actual use.

Introduction 1

Page 6

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

Associated Manuals

This document is the Hardware Reference Manual for the UMAC-CPCI Turbo CPU board for an UMACCPCI system. It describes the hardware features and provides setup instructions.

You will need other manuals as well to use your UMAC-CPCI system. Each accessory to the UMACCPCI Turbo CPU board has its own manual, describing its operation and any required software setup of

the Turbo CPU.

You will also need the Software Reference Manual for the Turbo PMAC family, and the User Guide for

the PMAC or Turbo PMAC families.

2 Introduction

Page 7

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

BOARD CONFIGURATION

The base version of the UMAC-CPCI Turbo CPU board provides a 1-slot 3U-format Eurocard board

with:

• 80 MHz DSP56303 CPU (120 MHz PMAC equivalent)

• 128k x 24 SRAM compiled/assembled program memory (Opt. 5C0)

• 128k x 24 SRAM user data memory (Opt. 5C0)

• 1M x 8 flash memory for user backup & firmware (Opt. 5C0)

• Latest released firmware version

• RS-232/422 serial interface, available both on front-panel DB-9 connector and on backside field-

wiring connector

• Backplane Compact UBUS expansion connector for communication to servo and I/O accessory

boards

• Backside field-wiring connector

Option 1: Communications Interfaces

The UMAC-CPCI Turbo CPU board comes standard only with an RS-232/422 serial interface. The

Option 1 family provides faster interfaces for high-speed communications – Universal Serial Bus (USB),

Ethernet, or the link to the CPCI bus through a “bridge” daughter board.

• Option 1: On-board 10-Base-T TCP/IP Ethernet interface. The key added components are U67 and

U32.

• Option 1A: On-board 12 Mbit/sec USB interface. The key added component is U67.

• Option 1B: Solder-side stack connectors to CPCI-bridge daughter board. This option should only be

ordered when the bridge board is to be installed on the left side of the CPU board, so the CPU board

is in the leftmost slot of the Compact UBUS backplane, and the bridge board is in the rightmost slot

of the Compact PCI bus backplane.

Option 2: Dual-Ported RAM

With either the Option 1 Ethernet interface, or the Option 1A USB interface, communications throughput

can be increased through the use of dual-ported RAM, which provides a bank of memory that can be

directly accessed by both the UMAC-CPCI Turbo CPU and the communications microcontroller.

• Option 2: 32k x 16 bank of on-board dual-ported RAM (requires Option 1 or 1A) in component U56.

Option 5: CPU and Memory Configurations

The various versions of Option 5 provide different CPU speeds and main memory sizes on the piggyback

CPU board. Only one Option 5xx may be selected for the board.

The CPU is a DSP563xx IC as component U1. It is currently available only as an 80 MHz or 100 MHz

device (with computational power equivalent to a 120 MHz or 150 MHz non-Turbo PMAC, respectively),

but higher speed versions may become available.

The compiled/assembled-program (“P”) memory SRAM ICs are located in U14, U15, and U16. These

ICs form the active memory for the firmware, compiled PLCs, and user-written phase/servo algorithms.

These can be 128k x 8 ICs (for a 128k x 24 bank), fitting in the smaller footprint, or they can be the larger

512k x 8 ICs (for a 512k x 24 bank), fitting in the full footprint.

The user-data memory (“X/Y”) SRAM ICs are located in U11, U12, and U13. These ICs form the active

memory for user motion programs, uncompiled PLC programs, and user tables and buffers. These can be

128k x 8 ICs (for a 128k x 24 bank), fitting in the smaller footprint, or they can be the larger 512k x 8 ICs

(for a 512k x 24 bank), fitting in the full footprint.

Board Configuration 3

Page 8

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

The flash memory IC is located in U10. This IC forms the non-volatile memory for the board’s firmware,

the user setup variables, and for user programs, tables, and buffers. It can be 1M x 8, 2M x 8, or 4M x 8

in capacity.

• Option 5C0 is the standard CPU and memory configuration. It is provided automatically if no Option

5xx is specified. It provides an 80 MHz DSP56303 CPU (120 MHz PMAC equivalent) with 8k x 24

of internal memory, an external 128k x 24 of compiled/assembled program memory, an external 128k

x 24 of user data memory; and a 1M x 8 flash memory. Setup variable I52 should be set and saved at

7 for 80 MHz operation.

• Option 5C3 provides an 80 MHz DSP56303 CPU (120 MHz PMAC equivalent) with 8k x 24 of

internal memory, an expanded external 512k x 24 of compiled/assembled program memory, an

expanded external 512k x 24 of user data memory, and a 4M x 8 flash memory. Setup variable I52

should be set and saved at 7 for 80 MHz operation.

• Option 5D0 provides a 100 MHz DSP56309 CPU (150 MHz PMAC equivalent) with 34k x 24 of

internal memory, an external 128k x24 of compiled/assembled program memory, an external 128k x

24 of user data memory; and a 1M x 8 flash memory. Setup variable I52 should be set and saved at 9

for 100 MHz operation.

• Option 5D3 provides a 100 MHz DSP56309 CPU (150 MHz PMAC equivalent) with 34k x 24 of

internal memory, an expanded external 512k x 24 of compiled/assembled program memory, an

expanded external 512k x 24 of user data memory, and a 4M x 8 flash memory. Setup variable I52

should be set and saved at 9 for 100 MHz operation.

Option 8: High-Accuracy Clock Crystal

The UMAC-CPCI Turbo CPU board has a clock crystal (component Y1) of nominal frequency 19.6608

MHz (~20 MHz). The standard crystal’s accuracy specification is +/-100 ppm.

• Option 8A provides a nominal 19.6608 MHz crystal with a +/-15 ppm accuracy specification.

Option 9: Serial Port Configuration

The UMAC-CPCI Turbo CPU board comes standard with a single RS-232/422 serial port, a second serial

port can be added.

• Option 9T adds an auxiliary RS-232 port on the CPU board. The key components added are ICs U28

and U43.

Option 10: Firmware Revision Specification

Normally the UMAC-CPCI Turbo CPU board is provided with the newest released firmware revision.

Some users may wish to “freeze” their designs on an older revision. A label on the U10 flash memory IC

shows the firmware revision loaded at the factory. The VERSION command can be used to report what

firmware revision is currently installed.

• Option 10 provides for a user-specified firmware version.

Option 16: Battery-Backed Parameter Memory

The contents of the standard memory are not retained through a power-down or reset unless they have

been saved to flash memory first. Option 16 provides supplemental battery-backed RAM for real-time

parameter storage that is ideal for holding machine state parameters in case of an unexpected powerdown.

• Option 16A provides a 32k x 24 bank of battery-backed parameter RAM in components U17, U18,

and U19 and a “can-stack” lithium battery in component BT1. While the average expected battery

life is over five years, a yearly replacement schedule is recommended. Replacement batteries can be

ordered from Delta Tau as Acc-1LS (Part # 100-0QTC85-000).

4 Board Configuration

Page 9

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

HARDWARE SETUP

Clock-Source Jumpers

In order to operate properly, the Turbo CPU board must receive servo and phase clock signals from a

source external to the board. These clock signals can be brought into the board from one of three possible

ports: the stack connector, the UBUS backplane connector, or the front-side main serial-port connector.

Jumpers E1A and E1B must be configured properly for the clock source used.

(Note: If the UMAC-CPCI Turbo CPU board cannot find the clock signal from the source specified by

these jumpers, it will generate its own 2.26kHz servo clock and its own 9.04kHz phase clock so it will

stay in operation.)

To receive the clock signals over the Compact-UBUS backplane, usually from an ACC-24C2x axisinterface board, E1A must connect pins 1 and 2, and E1B must connect pins 2 and 3. This configuration

is typical for an UMAC-CPCI system. The clock signals are output on the main serial port.

To receive the clock signals through the stack connectors, usually from the MACRO IC on the CPCI

“bridge” board, E1A must connect pins 1 and 2, and the E1B jumper must be removed. The clock signals

are output on the main serial port.

To receive the clock signals through the main serial port, usually from another UMAC system or a

reference signal generator, E1A must connect pins 2 and 3, and E1B must connect pins 1 and 2. This

configuration is rarely used, but permits complete synchronization to the system that is generating the

clock signals.

Watchdog Timer Jumper

Jumper E19 should be OFF for normal operation, leaving the watchdog timer circuit active and prepared

to shut down the card in case of a severe problem. Putting jumper E19 ON disables the watchdog timer

circuit. This should only be used for test purposes, in trying to track down the source of watchdog timer

trips. Normal operation of a system with this jumper ON should never be attempted, as an important

safety feature is disabled.

Operation Mode Jumpers

Jumpers E20, E21, and E22 control the operational mode of the UMAC-CPCI Turbo CPU. For normal

operation, E20 must be OFF, E21 must be ON, and E22 must be ON. Other settings of these jumpers are

for factory use only.

Firmware Reload Jumper

Jumper E23 should be OFF for normal operation. If you want to load new firmware into the flashmemory IC on the CPU, E23 should be ON when the card is powered up. This puts the card in “bootstrap

mode”, ready to accept new firmware. If you then try to establish communications to the card with the

Executive program, either over the main serial port or the optional USB or Ethernet ports, the Executive

program will automatically recognize that the card is in bootstrap mode, and prompt you for the firmware

file to download.

Re-Initialization Jumper

Jumper E3 should be OFF for normal operation, where the last saved I-variable values are loaded from

flash memory into active memory at power-up/reset. If E3 is ON during power-up/reset, the factory

default I-variable values are instead loaded into active memory at power-up/reset. The last saved values

are not lost when this happens. This jumper is typically only used when the system’s set up has a

problem severe enough that communications does not work – otherwise, a $$$*** command can be

used for re-initialization.

Board Configuration 5

Page 10

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

Serial-Port Level Select Jumpers

The standard serial port can be used for either RS-232 or RS-422 serial communications. To use RS-232,

jumpers E17 and E18 should connect pins 1 and 2; to use RS-422, jumpers E17 and E18 should connect

pins 2 and 3. The front-panel DB-9 serial connector provides only the RS-232 signals, so in order to use

this connector, E17 and E18 must both connect pins 1 and 2.

DPRAM IC Select Jumper

The UMAC-CPCI Turbo CPU board can provide dual-ported RAM (DPRAM) communications using

either the on-board Option 2B DPRAM IC through the USB or Ethernet port, or using the DPRAM IC on

the CPCI bridge daughter board through that board’s CPCI port. Jumper E24 must connect pins 1 and 2

to use the on-board Option 2B DPRAM; it must connect pins 2 and 3 to use the CPCI bridge board

DPRAM.

Flash IC Firmware Bank Select Jumpers

Some makes of the U10 flash memory IC on the UMAC-CPCI Turbo CPU board can store multiple

versions of the operating firmware inside. Jumpers E25A, E25B, and E25C select which bank is loaded

into active memory on a normal power-up/reset, and which bank will be written to if the board is powered

up or reset with the E23 jumper on.

The eight possible settings of these three jumpers provide eight banks for the firmware. A standard

production version of the UMAC-CPCI Turbo CPU board is shipped with firmware loaded only in the

bank selected by having all three of these jumpers OFF.

Flash IC Power Supply Select Jumper

Jumper W1 is set at the factory for the voltage level of the flash IC installed in U10. It connects pins 1

and 2 for a 3.3V flash IC; it connects pins 2 and 3 for a 5V flash IC. Even if this is a removable, not

soldered, jumper, it should not be changed by the user.

Power-Supply Check Select Jumper

The UMAC-CPCI Turbo CPU board has a circuit to evaluate the voltage levels received through the J1

Compact UBUS backplane connector. This circuit can then notify other boards in the system (without

software intervention) of a bad supply, so the outputs of those boards are automatically shut down.

Jumper E11 should be OFF if only the 5V supply is checked for this purpose; it should be ON if the +12V

and –12V backplane supplies are to be checked for this purpose. Note that many users will provide a

separate isolated +/-12V supply into the analog axis boards, and each analog axis board has its own

power-supply check circuit.

Reset-Lock Jumper

Putting jumper E0 ON locks the UMAC-CPCI Turbo CPU board in the reset state. This setting permits

the loading of logic into the programmable ICs on the board and is for factory use only. This jumper

should be OFF for all normal operation.

6 Hardware Setup

Page 11

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

CONNECTIONS

In a typical installation, the UMAC-CPCI Turbo CPU board is simply slid into a slot of a 3U-Eurocard

rack until it inserts into the mating connectors on the backplane board already installed in the rack. In

actual operation, all signals to the board come into the CPU board through the backplane. (The frontpanel RS-232 connector is intended for test and debugging purposes.)

Compact UBUS Connector

The J1 “Compact UBUS” connector at the bottom of the back edge of the board provides the means for

the UMAC-CPCI Turbo CPU board to communicate with axis and I/O boards through a common

backplane board, such as a Delta Tau ACC-Cx board, or a user-designed backplane board. It also

provides the 3.3V and 5V power supply lines to the CPU board.

Because of the design of the Compact UBUS, the CPU board can operate in any slot of the bus.

However, if the CPU board has the CPCI bridge board installed on it, the CPU board must be installed in

the end slot of the Compact UBUS backplane immediately adjacent to the Compact PCI bus backplane

board, so the bridge board can be installed in the adjacent CPCI end slot.

Rear Field Wiring Connector

The J2 field-wiring connector at the top of the back edge of the board provides the path for all of the

signals between the CPU board and the outside system. In a typical configuration, this connector is mated

with a “pass-through” connector on the Compact UBUS backplane board, and a system-specific

distribution system is installed behind the backplane.

The J2 connector contains the signals for the main serial port (either RS-232 or RS-422 levels), the

optional auxiliary RS-232 serial port, the optional USB port, and the optional Ethernet port. It also

provides the outputs of the relay for the CPU board’s watchdog timer.

Front-Panel RS-232 Connector

The J4 DB-9S connector on the front panel is a standard RS-232 connector for the main serial port into

the CPU, permitting a straight-across cable to a matching cable on a host computer. Jumpers E17 and

E18 must each connect pins 1 and 2 to permit use of this connector. These same signals are available on

the rear J2 connector; this front connector is intended for setup and diagnostic use more than use in the

actual application.

Stack Connectors to Bridge Board

Stacking socket connectors J11 and J12 on the top and bottom edges, respectively, of the component side

of the CPU board provide connection to the optional CPCI bridge board that can form a two-board

“stack” with the CPU board. (Mating prong connectors on the solder side of the bridge board must be

ordered.) In this configuration, the UMAC-CPCI Turbo CPU board can be installed in the rightmost slot

of a Compact UBUS backplane, and the bridge board can be installed in the leftmost slot of a CPCI

backplane.

If Option 2C is ordered, stacking “prong” connectors J11A and J12A are provided at the same locations

on the solder side of the board. These provide connection to mating socket connectors on the component

side of the bridge board. In this configuration, the UMAC-CPCI Turbo CPU board can be installed in the

leftmost slot of a Compact UBUS backplane, and the bridge board can be installed in the rightmost slot of

a CPCI backplane.

Connections 7

Page 12

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

Factory-Use Connectors

There are several connectors on the interior of the board for factory setup and diagnostic use. These are

not for customer use.

8

Connections

Page 13

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

BOARD LAYOUT

This diagram of the UMAC-CPCI Turbo CPU board shows the locations of the jumpers and connectors.

Detailed information about each of the jumpers and connectors follows.

UMAC-CPCI Turbo CPU Board Layout

Board Layout 9

Page 14

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

10 Board Layout

Page 15

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

JUMPER DESCRIPTIONS

Note:

Pin 1 of an E-point is masked by an X and a bold square in white ink on the composite

side, and by a square solder pad on the solder side.

E0: Reset-Lock Enable (Factory Use Only)

E Point &

Location Description Default

Physical Layout

Jump pins 1 and 2 to lock the UMAC-CPCI Turbo CPU board in

the “reset” state to permit installation of on-board logic. This

setting for factory use only.

Remove jumper to permit normal operation of board.

E1A: Servo and Phase Clock Direction Control

E Point &

Physical Layout

Location Description Default

Jump pins 1 and 2 or remove jumper for the UMAC-CPCI system

to use its internally generated servo and phase clock signals and to

output these signals on the field wiring connector on the CPU

board. E1B should connect pins 2 and 3 or be removed.

Jump pins 2 and 3 for the UMAC-CPCI system to expect to

receive its servo and phase clock signals on J2 field-wiring

connector on the Turbo CPU board. E1B should also connect pins

1 and 2.

E1B: Servo/Phase Clock Source Control

E Point &

Physical Layout

Location Description Default

Jump pin 1 to 2 to get phase and servo clocks from J7 RS422

connector (from an external source such as another UMAC).

Jump pin 2 to 3 to get phase and servo clocks from J1 backplane

connector (from an ACC-24C2x, or equivalent board).

Remove jumper to get phase and servo clocks from J2 Stack

connector (from an ACC-2E or equivalent board)

No jumper

installed

Pins 1-2

jumpered

Pins 2 – 3

jumpered

E2: (Reserved for Future Use)

E Point &

Physical Layout

Jumper Descriptions 11

Location Description Default

No jumper

installed

Page 16

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

E3: Re-Initialization on Reset Control

E Point &

Location Description Default

Physical Layout

Remove jumper for normal reset mode (default).

Jump pins 1 to 2 for re-initialization on reset.

E4: (Reserved for Future Use)

E Point &

Physical Layout

Location Description Default

No jumper

E5: USB/Ethernet Communication Jumper

E Point &

Physical Layout

Location Description Default

Jump 1-2 for Ethernet or USB communications from J7 (Ethernet

connector) or J3 (USB connector).

Jump 2-3 for Ethernet or USB communications through the back

J2 connector

No jumper

installed

installed

Factory

installed

E11: Power Supply Check Control

E Point &

Physical Layout

E11:

Location Description Default

Jump E11 pin 1 to 2 to include the +12V and –12V analog

supplies from the J1 backplane connector in the power-supply

check circuit, inhibiting outputs if these supplies fail.

Remove E11 jumper so only 5V digital supply is used in powersupply check circuit.

E17 – E18: Serial Port Select

E Point &

Physical Layout

E17:

E18:

Location Description Default

Jump E17 pin 1 to 2 to select RS-232 serial data input for main

serial port (J4 front-panel or J2 backside connector).

Jump E17 pin 2 to 3 to select RS-422 serial data input for main

serial port (J4 front-panel or J2 backside connector).

Jump E18 pin 1 to 2 to select RS-232 serial handshake input for

main serial port (J2 backside connector only).

Jump E18 pin 2 to 3 to select RS-422 serial handshake input f for

main serial port (J2 backside connector only).

No jumper

installed

Pins 1-2

jumpered

Pins 1-2

jumpered

12 Jumper Descriptions

Page 17

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

E18A, B, C, D: Ethernet Communication Control

E Point & Physical

Location Description Default

Layout

E18D1

E18C1

E18B1

Jump 1 to 2 to Ethernet Connection to J7 front connector

Jump 2-3 for Ethernet connection through back J2 connector

E19: Watchdog Disable Jumper

E Point & Physical

Layout

Location Description Default

Jump pin 1 to 2 to disable Watchdog timer (for test purposes

only.).

Remove jumper to enable Watchdog timer.

E20 – E22: Power-Up/Reset Load Source

E Point &

Physical Layout

E20:

Location Description Default

To load active memory from flash IC on power-up/reset,

Remove jumper E20;

Jump E21 pin 1 to 2;

Jump E22 pin 1 to 2.

Other combinations are for factory use only; the board will not

operate in any other configuration.

Pins 1-2

jumpered

No jumper

installed

No E20 jumper

installed

E21 and E22

jump pin 1 to 2

E23: Firmware Reload Enable

E Point &

Physical Layout

Location Description Default

Jump pin 1 to 2 to reload firmware through serial or host bus port.

Remove jumper for normal operations.

E25A, B, C: Flash Memory Firmware Bank Select

E Point &

Physical Layout

Location Description Default

Remove all jumpers to select standard factory-installed bank of

operational firmware.

Install one or more jumper(s) to select alternate bank of operation

firmware to install (E23 ON) or use (E23 OFF).

No jumper

installed

No jumpers

installed

Jumper Descriptions 13

Page 18

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

W1: Flash IC Power Supply Select Jumper

E Point &

Physical Layout

Location Description Default

B-1

(Note: This jumper is set at the factory and possibly hard soldered.

Users should not change this jumper.)

Jump pin 1 to 2 to select 3.3V supply for flash memory IC in U10.

Jump pin 2 to 3 to select 5V supply for flash memory IC in U10.

Setting

dependent on

flash IC used.

14 Jumper Descriptions

Page 19

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

CONNECTOR SUMMARY

J1: *

J2: *

J4: *

J5:

J6:

J10:

J11:

J11A:

J12:

J12A:

* Pinouts shown in next section. Connectors not flagged with an asterisk are for internal use or factory setup.

Compact UBUS Backplane Connector

“Thru-Backplane” Field Wiring Connector

RS-232 Front-Panel Serial-Port Connector

JTAG/OnCE (for factory use only): 10-pin IDC connector

JISP (for factory use only): 8-pin SIP connector

JISP_B (for factory use only) 8-pin SIP connector

First component-side stack connector to CPCI bridge board

First solder-side stack connector to CPCI bridge board

First component-side stack connector to CPCI bridge board

First solder-side stack connector to CPCI bridge board

Connector Summary 15

Page 20

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

16 Connector Summary

Page 21

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

CONNECTOR PINOUTS

Compact UBUS Connector (J1) Pin-Out

Row Z A B C D E F

25 GND 5V 3.3V 5V GND

24 GND BD02 5V V(I/O) BD01 BD00 GND

23 GND 3.3V BD05 BD04 5V BD03 GND

22 GND BD09 BD08 3.3V BD07 BD06 GND

21 GND 3.3V BD13 BD12 BD11 BD10 GND

20 GND BD17 GND BD16 BD15 BD14 GND

19 GND 3.3V BD20 BD19 GND BD18 GND

18 GND BD23 GND 3.3V BD22 BD21 GND

17 GND 3.3V {BD26} {BD25} GND {BD24} GND

16 GND {BD30} GND {BD29} {BD28} {BD27} GND

15 GND 3.3V BWR- BRD- GND {BD31} GND

14 (KEY) (KEY) (KEY) (KEY) (KEY) (KEY) (KEY)

13 (KEY) (KEY) (KEY) (KEY) (KEY) (KEY) (KEY)

12 (KEY) (KEY) (KEY) (KEY) (KEY) (KEY) (KEY)

11 GND CS10- CS4- CS3- GND CS2- GND

10 GND CS16- GND 3.3V CS14- CS12- GND

9 GND IREQ2- IREQ1- MEMCS1- GND MEMCS0- GND

8 GND PHASE+ GND SERVO+ WAIT- IREQ3- GND

7 GND PHASE- WDO SERVO- GND GND

6 GND BA02 GND 3.3V BA01 BA00 GND

5 GND BA04 BA03 RESET- GND BX/Y GND

4 GND BA07 GND V(I/O) BA06 BA05 GND

3 GND BA11 BA10 BA09 5V BA08 GND

2 GND {BA15} 5V {BA14} BA13 BA12 GND

1 GND 5V -12V PWRGUD +12V 5V GND

Notes:

1. Row 25 is physically at the top of the connector in its “normal” orientation; Row 1 is at the bottom.

Looking from the front of the rack, Column Z is on the left; Column F is on the right.

2. Supply (Vxx & xxV) and ground pins are in the same locations as the Compact PCI bus.

3. Spaces marked (KEY) are for the mechanical key; these are not pins.

4. Pins marked with {} brackets are reserved for future use; the signals inside the brackets are proposed

for future expansion to a 32-bit data bus and 16-bit address bus.

Connector Pinouts 17

Page 22

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

UMAC-CPCI Turbo CPU Board J2 Connector

Row Z A B C D E F

22 GND +5V GND

21 GND RxD/ CTS +5V TxD/ RTS GND

20 GND RD- RD+ GND SD- SD+ GND

19 GND CS+ CS- GND RS+/ RS- GND

18 GND DSR DTR INIT/ GND

17 GND SERVO- SERVO+ PHASE- PHASE+ GND

16 GND GND

15 GND AuxRxD/ AuxCTS AuxTxD/ AuxRTS GND

14 GND AuxDSR AuxDTR GND

13 GND USBDP (D+) GND USBDM (D-) GND

12 GND GND

11 GND EthTxF+ EthTxF- EthRxF+ EthRxF- GND

10 GND GND

9 GND GND

8 GND GND

7 GND GND

6 GND GND

5 GND GND

4 GND GND

3 GND GND

2 GND WD_NO WD_CO

M

1 GND GND

Notes:

1. Row 25 is physically at the top of the connector in its “normal” orientation; Row 1 is at the bottom. Looking

from the front of the rack, Column Z is on the left; Column F is on the right.

2. The RxD/, CTS, TxD/, and RTS lines are standard RS-232 signals. The inputs are only used if jumpers E17

and E18 each connect their pins 1 and 2. The DSR and DTR lines are simply shorted together.

3. The RD-, RD+, SD-, SD+, CS+, CS-, RS+, and RS- lines are standard RS-422 signals. The inputs are only

used if jumpers E17 and E18 each connect their pins 2 and 3.

4. The SERVO-, SERVO+, PHASE- and PHASE+ clock lines are at RS-422 levels. These signals are outputs if

jumper E1A connects its pins 1 and 2; they are inputs if jumper E1A connects pins 2 and 3.

5. The AuxRxD/, AuxCTS, AuxTxD/, and AuxRTS lines are standard RS-232 signals. These signals are

provided only if the Option 9T auxiliary serial port is ordered. The AuxDSR and AuxDTR lines are simply

shorted together.

6. The USBDP(D+) and USBDM(D-) signals are standard USB signals. They are only provided if the Option

1A USB interface is ordered.

7. The EthTxF+, EthTxF-, EthRxF+, and EthRxF- signals are standard Ethernet signals. They are only provided

if the Option 1 Ethernet interface is ordered.

8. The WD_NO (normally open), WD_COM (common) and WD_NC (normally closed) lines are the outputs of

the watchdog-timer hard-contact relay. The normally open contact is only conducting to common if the card is

powered and operating correctly. The normally closed contact is only conducting to common if the card is not

powered or the watchdog timer has tripped.

WD_NC GND

18 Connector Pinouts

Page 23

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

J4: RS-232 Serial Port Connector

(DB-9S Connector)

Pin # Symbol Function Description Notes

1 N.C. No connect

2 TXD- Output Send Data Low TRUE

3 RXD- Input Receive Data Low TRUE

4 DSR Bidirect Data Set Ready Shorted to DTR

5 GND Common UMAC CPCI Reference

6 DTR Bidirect Data Terminal Ready Shorted to DSR

7 CTS Input Clear to Send High TRUE

8 RTS Output Request to Send High TRUE

9 N.C. No connect

Jumpers E17 and E18 should connect pins 1 and 2 to use this port for RS-232 communications; they should connect pins 2

and 3 to use this port for RS-422 communications.

Connector Pinouts 19

Page 24

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

20 Connector Pinouts

Page 25

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

ACCESSORIES

The UMAC-CPCI Turbo CPU board is always used with accessory boards. Delta Tau provides several

accessory boards in the UMAC-CPCI family that can be used with the CPU board; other parties may

produce accessory boards as well. Each accessory board has its own hardware reference manual.

ACC-Cx Compact UBUS Backplane Boards

The ACC-Cx family of Compact UBUS backplane boards

provides the means for the CPU board to communicate with

other accessory boards. The x in the name of the backplane

board refers to the number of backplane data slots provided.

This picture shows an ACC-C8 8-slot backplane board. It has

a P47-style power connector suitable for a standard 1-slot

CPCI-format power supply.

ACC-8CR Test Breakout Board

The ACC-8CR board provides a behind-the-backplane breakout scheme for the J2 field wiring connector

on any of the 3U-format UMAC-CPCI board. It is designed to plug into the rear of an ACC-Cx Compact

UBUS backplane board, and it meets the Compact PCI physical specification (100mm x 80mm) for rear

distribution boards. It has 110 screw-down terminal points, one for each signal on the J2 field wiring

connector.

ACC-11C Sinking I/O Board

The ACC-11C board provides 32 isolated 12V-24V

sinking inputs and 16 isolated sinking outputs up to 24V

and 100mA per output. With its Option 1 mezzanine

board, an additional 32 inputs and 16 outputs are

provided, for a total of 96 I/O points in a single slot.

Schematics

Page 26

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

ACC-24C2 PWM Axis Board

The ACC-24C2 PWM axis board provides the interface circuitry for 4 axes of purely digital control in a

single slot, with direct PWM outputs, serial ADC inputs, quadrature encoder inputs, and input/output

flags. Because of pin limitations on the J2 field wiring connector, signals that are differential on other

ACC-24x2 boards are single-ended here. To take these signals any significant distance, differential line

drivers and receivers are required on a distribution board.

ACC-24C2A Analog Axis Board

The ACC-24C2A analog axis board provides the

interface circuitry for 4 axes of control in a single slot,

with analog interface to the servo drives. It also has

one pulse-and-direction output per axis for stepper

drives, or stepper-replacement servo drives. One 18-bit

D/A converter comes standard for each axis; Option 1

provides a second D/A converter per axis, which can be

used as part of a “sine-wave” control scheme, or for

non-servo use. Option 2 provides eight 12-bit A/D

converters.

ACC-51C Analog Encoder Interpolator Board

The ACC-51C provides the circuitry for the high-resolution interpolation of 2 or 4 analog sine/cosine

encoders, yielding 4096 states per line of the encoder. The board comes standard with two channels of

interface; Option 1 provides two additional channels.

22 Accessories

Page 27

O

-

+3P3V

RP10A

+5V

C99

TP7

PHASE+

1 2

.1UF

SIRQ-

3.3KSIP8I

C97

16

C95

RP10B

C98

.1UF

.1UF

645141378

V-

C2-

C2+

VCC

+V

C1+

C1-

U28

213

C96

.1UF

.1UF

.1UF

C32

U43

1234567

1K

R10

STD0

SERVO+

RP10C

RP10D

5 6

3 4

3.3KSIP8I

3.3KSIP8I

OSC_OUT

AuxTxD-

AuxTxD-

TXD

TXD

111210

TX

VCC

DIN

DOUT

SCK0

SRD0

7 8

AuxRxD-

AuxRxD-

RXD

RXD

RX

RTS

SCLK

CS

SC02

3.3KSIP8I

U4F

AuxRTS

N.C.

N.C.

SIRQ-

PHASE-

RP11A

1 2

19.6608Mhz

R1

13 12

AuxRTS

AuxCTS

AuxCTS

RTS

CTS

RTS

CTS

9

10111213141516

X1

CTS

IRQ

SHDN

GND X2

8 9

3.3KSIP8I

19.6608Mhz

10

(SO14)

VSS

C94

C93

Y2

MAX3100CEE

(QSOP)

RP11B

3 4

74ACT14

15

(SOL16)

MAX3232ECWE

22pf

22pf

3.6864Mhz

ECS-36-20-5P

SERVO-

RP11C

5 6

3.3KSIP8I

3.3KSIP8I

RP11D

MainCTS

MainRxD-

MainTxD-

MainRTS

422_CS+

422_RS+

422_CS-

422_SD-

422_RD+

422_RS-

422_RD-

422_SD+

422_RD+

422_SD-

422_RS-

422_RS+

422_RD-

422_SD+

422_CS-

422_CS+

R15

15K

R14

15K

RP3E

3.3K

6 1

GND

RP3A

3.3K

2 1

12

RX

RP2A

RP1A

3.3K

2 1

+5V

RP3D

3.3K

SOCKET REQ'D

GND

7 8

3.3KSIP8I

GND

5 1

RX

RP2C

RP1D

5 6

3.3K

5 1

RP1E

3.3K

6 1

+5V

C113

.1UF

GND

3

U38A

(SO14)

1

2

ENA422

+5V

2

E17

3

1

JUMP 2 TO 3 TO ENA PHASE,SERVO,INIT ON `J2'

JUMP 1 TO 2 TO DIS PHASE,SERVO,INIT ON `J2'

JUMP 2 TO 3 TO ENABLE "RS422" TRANSCEIVER

JUMP 1 TO 2 TO ENABLE "RS232" TRANSCEIVER

E18

E17

RXD

CTS-

+5V

IN-B

IN-B

VCC

OUT-B

OUT-D

EN-B,D

74ACT08

IN-A

U30

IN-A

OUT-A

EN-A,C

OUT-C

PHASE+

IN-C

SERVO+

U33C

74ACT14

(SO14)

5 6

3

1

E1B

2

ENA_P2-

RESET

ENA_P2-

1234567

PHASE-

C106

2

3

10111213141516

IN-D

IB-C

SERVO-

ENA_P1-

ENA_P1-

E18

C105

.1UF

17

1

C102

MC3486D

(SO16)

GND IN-D

8 9

2

E1A

3

1

CARD0

CARD0

GND

.1UF

C104

.1UF

756151489

V-

C2-

C2+

VCC

+V

C1+

C1-

U29

324

C103

.1UF

.1UF

TXD

IN-B

VCC

C100

.1UF

IN-A

OUT-A

U31

1234567

PHASE+

PHA

PHA

MainRxD-

MainTxD-

TXD

TXD

121311

RXD

TXD

OUT-B

N.C.

PHASE-

U38B

RXD

RXD

N.C.

OUT-A

MainCTS

MainRTS

RTS

CTS

RTS

CTS

RXEN TXEN

1 18

10

RXEN-

RTS-

CTS-

14151617181920

OUT-B

OUT-D

EN-B,D

EN-A,C

OUT-C

N.C.

8 13

SERVO+

SERVO-

6

(SO14)

74ACT08

4

5

OUT-C N.C.

VSS

12

9

SER

LTC1384CS

OUT-D

IN-C

SER

16

U38C

(SOL18)

3

4

5

6

7

8

910

RP25

RTS-

11

IN-D

C101

GND

MC75174BDW

(SOL20)

10

8

74ACT08

(SO14)

9

10

ENA422

1 2

GND

1KSIP10C

.1UF

GND

+5V

C36

.1UF

GND

1K

R2

+5V

MainTXD-

MainDTR

MainCTS

N.C.

J4

DB9F

J4

(JRS232)

MainTxD-

Front Panel

RT. angle through

RESET

RESET

(SO14)

U4C

74ACT14

5 6

3

Q5

SOT23

2N7002

(SOT23)

12

12

Q4

3

SOT23

2N7002

(SOT23)

(SO14)

U4B

U4A

RP12B

74ACT14

3 4

RP12A

74ACT14

(SO14)

C35

1 2

C1

.1UF

GND

R3

10K

INIT-

WDTC

INIT-

+3P3V

3.3KSIP10C

RP20

12

MainRXD-

MainRTS

N.C.

MainDSR

MainRTS

MainRxD-

MainCTS

+5V

D3

3 4

1KSIP6I

1 2

1KSIP6I

.01UF

RXD

CTS-

181716151413121120

B0B1B2B3B4B5B6

A0A1A2A3A4A5A6A7T/R

U27

234567891

9 10

8

7

6

5

4

3

BCTS-

BRXD

GND

594837261

1 3

1

56

BPHA

BSER

PHA_A

SER_A

10

CHGND

GND

MMBD301LT1

23

RP12C

1KSIP6I

BSA01

BSA00

BSA02

IRQB-

BSA01

BSA00

BSA02

BHA0

BHA1

MODD/IRQD-

BHA2

NMI-

NMI-

U4D

16151413121110

N.C.

N.C.INN.C.

U3

1234567

Q1

(SOT23)

MMBT3906LT1

IRQB-

10

B7

VCC

19

RESET

HACK-

T/R-

VCC

GND

OE

N.C.

C111

WDO

WDO

9 8

NMI

N.C.

MODE

N.C.

.1UF

74LCX245

(TSSOP20)

R_SERVO-

R_SERVO-

RP15

1 2

SERVO-

(SO14)

74ACT14

RST

N.C.

TOL

N.C.

C34

+

R4

21

21

R_SERVO+

R_PHASE-

R_PHASE-

R_SERVO+

R_PHASE+

3 4

5 6

7 8

PHASE-

SERVO+

PHASE+

U4E

C2

9

RST

GND

DS1231S

8

1UF

35V

tant

100K

E19

E0

TO LOAD

JUMP `E0'

`isp' PART

GND

+5V

R_PHASE+

33SIP8I

E1B 2 TO 3 ON = ENABLE `PHASE & SERVO' FROM `P1'

E1A 2 TO 3 = DISABLE `CARD0'

E1A 2 TO 1 = ENABLE `CARD0'

E1B 2 TO 1 OFF = DISABLE `PHASE & SERVO' FROM `P2'

E1B 2 TO 3 OFF = DISABLE `PHASE & SERVO' FROM `P1'

E1B 2 TO 1 ON = ENABLE `PHASE & SERVO' FROM `P2'

NOTE:

WD

D1

LED

RED

PWR

D2

LED

GRN

(SO14)

74ACT14

11 10

.1UF

D4

1 3

MMBD301LT1

(SOL16)

"Vbat" s/b 30mil trace

Vbat

+3P3V

BPHA

GND

U33B

C92

.1UF

3 4

+5V

U33A

3.3KSIP10C

1 2

3

4

5

6

7

8

9 10

IRQB-

WAIT2-

PHASE

WAIT1-

CTS-

RXD

PHASE

12

RP13

SHEET2

625-0SH2

SHEET3

625-0SH3

E1B EMPTY = ENABLE `PHASE & SERVO' FROM `J12/J12A'

RESET-

BBRCS-

BBRCS-

BBRAMCS-

RESET-

R6

1K

R5

1K

6

8

CEO

BATT

VCC RST

U2

VOUTONGND CEI

2 713

4 5

23

1

Q3

(SOT23)

MMBT3906LT1

Vout

D5

1 3

MMBD301LT1

Vout

+

D6

BT1

1 3

3.6V BAT

R7

100

BSER

74ACT14

(SO14)

U33E

74ACT14

(SO14)

11 10

U33F

74ACT14

(SO14)

74ACT14

(SO14)

13 12

53

+5V

SERVO

SERVO

of

13Monday, January 14, 2002

Delta Tau Data Systems, Inc.

603625-322A

UMAC-CPCI-CPU, DSP56309 CPU SECTI

D

Title

Size Document Number Rev

Date: Sheet

|625-0SH2.sch

|625-0SH3.sch

|Link

TRST-

Q2

2N7002

(SOT23)

12

GND

3

SOT23

C15

.1UF

MAX795SCSE

(SO8)

C16

.1UF

C17

NEC

FM0H103Z

.01FARAD

MMBD301LT1

RESET_A

RESET_A

U33D

74ACT14

(SO14)

9 8

4

GND

U50

1

2

NC7SZ08M5

(SOT23-5)

RESET-

CPURST-

+3P3V

+3P3V

BA02

BA00

BA01

BA04

BA05

BA03

10UF

16V

(TANT)

+

GND

+3P3V

C39

+

+5V

GND

C14

16V

10UF

(TANT)

RP4

12

+3P3V

OF DELTA TAU DATA SYSTEMS INC. ALL RIGHTS TO DESIGNS AND

DATA SYSTEMS INC. AND IS LOANED SUBJECT TO RETURN UPON

DEMAND. TITLE TO THIS DOCUMENT IS NEVER SOLD OR

ABOVE AGREEMENT.

OF DELTA TAU DATA SYSTEMS INC. ALL RIGHTS TO DESIGNS AND

THIS DOCUMENT IS THE CONFIDENTIAL PROPERTY OF DELTA TAU

INVENTIONS ARE RESERVED BY DELTA TAU DATA SYSTEMS INC.

POSSESSION OF THIS DOCUMENT INDICATES ACCEPTANCE OF THE

TRANSFERRED FOR ANY REASON. THIS DOCUMENT IS TO BE USED

DEMAND. TITLE TO THIS DOCUMENT IS NEVER SOLD OR

INVENTIONS ARE RESERVED BY DELTA TAU DATA SYSTEMS INC.

POSSESSION OF THIS DOCUMENT INDICATES ACCEPTANCE OF THE

ONLY PURSUANT TO WRITTEN LICENSE OR WRITTEN INSTRUCTIONS

ONLY PURSUANT TO WRITTEN LICENSE OR WRITTEN INSTRUCTIONS

DATA SYSTEMS INC. AND IS LOANED SUBJECT TO RETURN UPON

TRANSFERRED FOR ANY REASON. THIS DOCUMENT IS TO BE USED

THIS DOCUMENT IS THE CONFIDENTIAL PROPERTY OF DELTA TAU

ABOVE AGREEMENT.

BA01

BA02

BA00

23568911

147

B0B1B2B3B4B5B6

T/R1

GND

A0

OE1

U7

GND

A1A2A3A4A5A6A7

46444341403837

47

48

45

A0

A2

A1

+3P3V

3.3KSIP10C

9 10

8

7

6

5

4

3

BA03

A3

C22

BA04

VCC

VCC

42

A4

PRDY

PRDY

J5

BA05

10

A5

.1UF

ISPEN-

J5

(JTAG/OnCE)

+3P3V

BA08

BA09

BA07

BA06

BA09

BA06

BA10

BA07

BA08

12

1314151617181920212223

B8

B9

B7

GND

GND

GND

A9

GND

A8

36

A9

A8

A6

A10

A7

+3P3V

TDI

TDO

TCK

1234567

TSO

TSI

GND

TCK

GND

GND

TA-

GND

4

C40

.1UF

53

+3P3V

GND

GND

+3P3V

BA10_A

BA10_A

B10

A10

BA10

+3P3V

C26

BA11_A

BA11_A

B11

VCC

VCC

A11

BA11

C25

C21

HSIP8NO5

BA12_A

BA12_A

B12

A12

BA12

.01UF

.1UF

BA13_A

BA13_A

B13

A13

BA13

.1UF

GND

GND

+3P3V

BA14_A

BA14_A

B14

A14

BA14

GND

2425

B15

T/R2

74LCX16245

(TSSOP48)

OE2

A15

2627282930313233343539

BA15

GND

GND

C27

+3P3V

GUARD BAND

EXTAL

BHACK-

23568911

147

B0B1B2B3B4B5B6

T/R1

A0

OE1

(TSSOP48)

U8

46444341403837

47

48

HACK-

OSC_OUT

GUARD BAND

.1UF

+3P3V

BWR-

BRD-

BA05_A

BX/Y

BX/Y

BA05_A

BRD-

BA06_A

BWR-

10

VCC

GND

GND

GND

VCC

GND

A1A2A3A4A5A6A7

42

45

BA05

WR-

BA06

RD-

A19X/YP

+3P3V GND

C24

.1UF

A15

A17

ISPEN-

1234678

J6

(jisp)

J6

SDO

SDI

+3.3V

ispEN-

BA09_A

BA07_A

BA06_A

BA08_A

BA07_A

BA08_A

BA09_A

12

1314151617181920212223

B8

B9

B7

A9

A8

36

BA08

BA09

BA07

MODE

WR-

GND

MODE

SCLK

+3P3V

BA12

BA11

BA15

BA10

BA14

BA13

BA13

BA15

BA14

BA11

BA12

2425

B10

B11

B12

B13

B14

B15

VCC

T/R2

GND

74LCX16245

OE2

A15

A14

GND

A13

A12

VCC

A11

A10

2627282930313233343539

A11

A14

A13

A15

A12

C23

.1UF

TMS

DE-

TRST-

RESET-

9

1011121314

DE-

TMS

N.C.

N.C.

HEADER14_NO8

TRST-

RST-

+3.3V

GND

U9

1

2

NC7SZ00

(SOT23-5)

X/Y:$078000-$0780FF

WAIT1-

WAIT1-

WAIT2-

WAIT2-

+5V

C152

C151

C150

C153

.1UF

.1UF

U51

IOCS-

IOCS

U6B

A14

BA14

.1UF

147

T/R1

OE1

48

.1UF

WR

BWR-

X/Y:$078800-$0789FF

X/Y:$078100-$0781FF

X/Y:$078300-$0783FF

X/Y:$078200-$0782FF

CS2-

CS02-

CS3-

CS1-

CS00-

CS0-

CS3-

CS02-

CS0-

CS1-

CS2-

CS00-

23568911

B0B1B2B3B4B5B6

VCC

GND

A0

VCC

GND

A1A2A3A4A5A6A7

46444341403837

47

42

45

202122232622728333435

25

CS0

CS1

CS2

CS3

CS02

CS04

CS06

CS00

A8A9A10

A11

FLASHCS

DRAMCS

PRAMCS

9

4173

131415

16

10

11

BA08

BA10

DRAMCS-

FLASHCS-

BA09

PRAMCS-

BA11

BRD-

PRAMCS-

DRAMCS-

FLASHCS-

X/Y:$068000-$06FFFF EXTENDED MEMORY OFF_BOARD (32K)

X/Y:$074000-$077FFF

X/Y:$078E00-$078EFF

X/Y:$078A00-$078AFF

X/Y:$078400-$0787FF

X/Y:$078C00-$078CFF

X/Y:$078D00-$078DFF

X/Y:$078B00-$078BFF

X/Y:$078F00-$078FFF

MEMCS0-

CS14-

CS4-

MEMCS1-

CS16-

CS12-

CS06-

CS10-

CS04-

CS04-

CS06-

CS10-

12

10

1314151617181920212223

B8

B7

GND

GND

A8

36

37

CS10

CS12

CS14

CS16

BSCAN

TDI/A16RDA15

7

8

ISPEN-

BA15

A16

B9

A9

TDO/A17

19

A17 CS12-

CS14-

GND

GND

44

TCK

29131

WR-

MODE

B10

A10

CS4

TMS

CS16-

B11

A11

4541403846

CPURST-

VCC

VCC

RESET

RESET-

CS4-

MEMCS0-

B12

B13

A13

A12

47

IOCS_B

IOCS_A

VCCIO

+5V

MEMCS1-

GND

GND

39325

DPRCS0

VCCIO

482412

PWRGUD

B14

A14

2627282930313233343539

PWRG

DPRCS1

VCC

30

C87

C86

PWRGUD

2425

B15

T/R2

OE2

A15

PWRG

VMECS0

VMECS1

VCC

GND

18642

.1UF

.1UF

X/Y:$070000-$073FFF

X/Y:$060000-$067FFF EXTENDED MEMORY ON_BOARD (32K)

DPRCS0-

IOCS_A-

IOCS_B-

VMECS0-

VMECS0-

IOCS_A-

IOCS_B-

DPRCS0-

GND

(TSSOP48)

PI74FCT16245ATA

GND

CPURST-

43

N.C.

N.C.

GND

GND

GND

TURBO-DECODE5

36

ispLSI2032E-135LT48

GND

(TQFP48)

+5V

U34

F1ER

HREQ-

BFUL

EROR

IPOS

ENA422

HREQ-

F1ER

BFUL

IPOS

EROR

RTS-

TXD

181716151413121120

B0B1B2B3B4B5B6

A0A1A2A3A4A5A6A7T/R

234567891

BRTS-

BSC12

BTXD

BSC11

BSRD1

BSTD1

BHREQ-

BSCK1

C88

B7

RP14

3.3KSIP10C

910

8

7

6

5

4

3

1 2

GND

.1UF

10

VCC

GND

OE

(TSSOP20)

PI74FCT245TL

19

RESET

PRAM MEMORY P:

$000000-$00FFFF Firmware (64K)

$050000-$0BFFFF Plcc Extended Memory Option (448K)

$050000-$05FFFF Plcc Standard Memory Option (64K)

$040000-$0403FF User Written Phase (1K)

$040400-$040BFF User Written Servo (2K)

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

SCHEMATICS

Schematics 23

Page 28

O

-

of

23Tuesday, January 15, 2002

Delta Tau Data Systems, Inc.

603625-322A

UMAC-CPCI-CPU, MEMORY & I/O SECTI

D

Title

Size Document Number Rev

Date: Sheet

J11

(JEXP_A)

BD05_A

BD07_A

BD03_A

BD01_A

BD01_A

BD07_A

BD03_A

BD05_A

12

34

56

78

BD02_A

BD04_A

BD00_A

BD06_A

BD04_A

BD06_A

BD02_A

BD00_A

BD09_A

BD09_A

910

BD08_A

BD08_A

BD11_A

BD11_A

11 12

BD10_A

BD10_A

BD13_A

BD13_A

13 14

BD12_A

BD12_A

BD15_A

BD15_A

15 16

BD14_A

BD14_A

BD17_A

17 18

BD16_A

BD19_A

19 20

BD18_A

BD21_A

21 22

BD20_A

BD23_A

23 24

BD22_A

BA01_A

BA01_A

BA00_A

BA03_A

BA03_A

25 26

27 28

BA02_A

BA02_A

BA00_A

BA05_A

BA05_A

29 30

BA04_A

BA04_A

BA07_A

BA07_A

31 32

BA06_A

BA06_A

BA09_A

BA09_A

33 34

BA08_A

BA08_A

BA11_A

BA10_A

WAIT2-

BA13_A

BA11_A

BA13_A

WAIT2-

HEADER 20X2(FEM)

CLS120LDDV

35 36

37 38

39 40

BA12_A

BX/Y_A

BX/Y_A

BA10_A

BA12_A

SSM-120-L-DV-LC

J12

(JEXP_B)

JEXP

Modified

+5V

GND

HPBD5

HPBD1

HPBD3

HPBD1

HPBD5

HPBD3

12

34

56

78

HPBD4

HPBD2

HPBD0

+5V

GND

HPBD0

HPBD2

HPBD7

910

HPBD6

HPBD4

HPBD7

11 12

HPBD6

WAIT2-

GND

-12V

INIT-

29 30

31 32

33 34

19.6608Mhz

-5V

SDA

HEADER 25X2(MALE)

PWRG

HW2515GD450SM

37 38

39 40

41 42

43 44

45 46

47 48

49 50

SOLDER SIDE

DIRECTLY UNDER J12

BSA02

SCL

+5V

GND

+12V

35 36

GND

HEADER 20X2(MALE)

HW2015GD450SM

(JEXP_B)

SOLDER SIDE

DIRECTLY UNDER J11

+5V

HPBD1

J12A

12

34

HPBD0

+5V

GND

HDS-

HPBD3

HPBD7

HPBD5

BSA01

56

78

910

11 12

13 14

HPBD2

HPBD6

BSA00

HR/W

HPBD4

VMECS0-

CS02-

15 16

17 18

CS00-

CPCIDPR-

WDO

CS06-

CS1-

PHASE

BRD_A-

19 20

21 22

23 24

25 26

27 28

BWR_A-

SERVO

CS0-

RESET_A

CS04-

GND

-12V

-5V

WDO

HDS-

CS1-

CS06-

BRD_A-

SDA

INIT-

VMECS0-

BSA01

CS02-

HEADER 25X2(FEM)

CLS125LDDV

47 48

49 50

+12V

J11A

(JEXP_A)

BD01_A

BD07_A

BD03_A

BD05_A

12

34

56

BD06_A

BD02_A

BD00_A

BD04_A

BD15_A

BD17_A

BD09_A

BD13_A

BD11_A

78

910

11 12

13 14

15 16

BD08_A

BD14_A

BD12_A

BD16_A

BD10_A

17 18

BD19_A

19 20

BD18_A

BD21_A

21 22

BD20_A

BD23_A

BA01_A

23 24

BD22_A

BA00_A

BA03_A

25 26

BA02_A

27 28

BA05_A

29 30

BA04_A

BA07_A

31 32

BA06_A

BA09_A

33 34

BA08_A

BA11_A

35 36

BA10_A

BA13_A

37 38

BA12_A

WAIT2-

39 40

BX/Y_A

CS02-

CS1-

BRD_A-

CS0-

23 24

BWR_A-

CS0-

PHASE

25 26

SERVO

BWR_A-

WDO

27 28

29 30

RESET_A

RESET_A

INIT-

31 32

33 34

19.6608Mhz

19.6608Mhz

SDA

35 36

37 38

39 40

41 42

43 44

45 46

SCL

BSA02

PWRG

+5V

SCL

GND

BSA02

PWRG

VMECS0-

CS06-

HDS-

BSA01

13 14

15 16

17 18

19 20

21 22

HR/W

CS04-

CPCIDPR-

CS00-

BSA00

BSA00

CS04-

CS00-

HR/W

CPCIDPR-

SSM-125-L-DV-LC

HW20-09-GD-450-SM

HW25-09-GD-450-SM

UMAC-CPCI Turbo CPU Board Hardware Reference Manual

PHASE_B+

PHASE_B-

SERVO_B+

SERVO_B-

+5V

C82

.1UF

U25

VCC

RO

123

PHA

PHA

678

A

B

DE

DI GND

RE

ADM1485JR

4 5

R9 100

SERVO

PHASE

PHASE

C74

+5V

(SO8)

SERVO

678

A

B

VCC

RO

123

SER

SER

(SO8)

DE

DI GND

RE

ADM1485JR

4 5

ENA_P1-

ENA_P1-

C75

.1UF

+5V

U26

R19 100

.1UF

GND

C83

.1UF

C76

+5V

C77

.1UF

+5V

GND

.1UF

+5V

BRD-

BD01_B

BD02_B

BD00_B

23568911

147

B0B1B2B3B4B5B6

T/R1

GND

U22

GND

A1A2A3A4A5A6A7

A0

OE1

46444341403837

47

48

45

D0

D1

D2

IOCS_B-

+3P3V

IOCS_B-

+5V

BD01_A

BD02_A

BRD-

BD00_A

23568911

147

B0B1B2B3B4B5B6

T/R1

GND

A1A2A3A4A5A6A7

U20

GND

A0

OE1

46444341403837

47

48

45

D0

D2

D1

IOCS_A-

+3P3V

IOCS_A-

BD03_B

42

D3

C52

BD03_A

42

D3

C45

BD04_B

VCCB

VCCA

D4

BD04_A

VCCB

VCCA

D4

BD05_B

10

GND

GND

D5

.1UF

BD05_A

10

GND

GND

D5

.1UF

BD06_B

BD09_B

BD10_B

BD08_B

BD07_B

BD11_B

12

1314151617181920212223

B7

B8

B9

B10

GND

A10

GND

A9

A8

36

D7

D6

D11

D8

D10

D9

+3P3V

C51

+5V

BD06_A

BD11_A

BD08_A

BD09_A

BD10_A

BD07_A

12

1314151617181920212223

B7

B8

B9

B10

GND

A8

A10

GND

A9

36

D10

D6

D11

D9

D8

D7

+3P3V

C46

BD12_B

BD13_B

B11

B12

B13

VCCB

A13

A12

VCCA

A11

D13

D12

.1UF

BD12_A

BD13_A

B11

B12

B13

VCCB

A13

A12

VCCA

A11

D12

D13

.1UF

BD14_B

GND

GND

D14

BD14_A

GND

GND

D14

B14

A14

B14

A14

BD15_B

2627282930313233343539

D15

BD15_A

2627282930313233343539

D15

BRD-

2425

B15

T/R2

OE2

A15

IDT74FCT164245TPA

BRD-

2425

B15

T/R2

OE2

A15

IDT74FCT164245TPA

BD16_B

BRD-

23568911

147

T/R1

U23

(TSSOP48)

OE1

47

48

D16

BRD-

BD16_A

23568911

147

T/R1

(TSSOP48)

U21

OE1

47

48

D16

BD19_B

BD18_B

BD20_B

BD21_B

BD17_B

10

B0B1B2B3B4B5B6

GND

VCCB

VCCA

GND

A1A2A3A4A5A6A7

A0

46444341403837

42

45

D17

D21

D18

D20

D19

+3P3V

C50

.1UF

+5V

BD17_A

BD18_A

BD21_A

BD20_A

BD19_A

10

B0B1B2B3B4B5B6

GND

VCCB

A1A2A3A4A5A6A7

VCCA

GND

A0

46444341403837

42

45

D20

D17

D21

D18

D19

+3P3V

C47

.1UF

BD23_B

BA02_B

BA00_B

BA01_B

BD22_B

12

1314151617181920212223

B7

B8

B9

B10

GND

GND

A10

GND

A9

GND

A8

36

D23

BA02

D22

BA01

BA00

+3P3V

+5V

BA02_A

BD22_A

BA01_A

BA00_A

BD23_A

12

1314151617181920212223

B7

B8

B9

B10

GND

GND

A8

A10

GND

A9

GND

36

BA01

BA02

D22

D23

BA00

+3P3V

BA03_B

BA03

C49

BA03_A

BA03

C48

BX/Y_B

BA05_B

BA04_B

2425

B11

B12

B13

B14

B15

T/R2

GND

VCCB

(TSSOP48)

OE2

A15

A14

GND

A13

A12

VCCA

A11

2627282930313233343539

IDT74FCT164245TPA

BX/Y

BA05

BA04

R18 3.3K

GND

GND

.1UF

+5V

BA10_B

BA07_B

WDO_B

RESET_B

BA11_B

BA09_B

BA08_B

+5V

BA06_B

181716151413121120

B0B1B2B3B4B5B6

U52

A0A1A2A3A4A5A6A7T/R

234567891

BA06

BA07

BX/Y_A

BA13_B

BA04_A

BA12_B

2425

B11

B12

B13

B14

B15

T/R2

GND

VCCB

(TSSOP48)

OE2

A15

A14

GND

A13

A12

VCCA

A11

2627282930313233343539

IDT74FCT164245TPA

BA12

BA13

BA04

BX/Y

.1UF

GND

C127

.1UF

10

B7

VCC

GND

GND

OE

(TSSOP20)

PI74FCT245TL

19

BA09

BA08

BA10

RESET_A

BA11

WDO

EQU_1-

EQU_1-

+5V

CS10-

CS16-

CS16-

BA04_B

BA11_B

CS10-

IREQ2-

BA07_B

BA02_B

PHASE_B-

PHASE_B+

A1A2A3A4A5A6A7A8A9

A10

A11

A12

A13

A1A2A3A4A5A6A7A8A9

TRANSFERRED FOR ANY REASON. THIS DOCUMENT IS TO BE USED

DEMAND. TITLE TO THIS DOCUMENT IS NEVER SOLD OR

OF DELTA TAU DATA SYSTEMS INC. ALL RIGHTS TO DESIGNS AND

THIS DOCUMENT IS THE CONFIDENTIAL PROPERTY OF DELTA TAU

DATA SYSTEMS INC. AND IS LOANED SUBJECT TO RETURN UPON

ONLY PURSUANT TO WRITTEN LICENSE OR WRITTEN INSTRUCTIONS

J1

J1-1

+5V

BA11

BA07

ABOVE AGREEMENT.

POSSESSION OF THIS DOCUMENT INDICATES ACCEPTANCE OF THE

INVENTIONS ARE RESERVED BY DELTA TAU DATA SYSTEMS INC.

{BA15}

A14

A10

A11

A12

A13

(KEY)

BA04

(KEY)

(KEY)

BA02

PHASE-

CS10-

PHASE+

CS16-

IREQ2-

+3P3V

+3P3V

+3P3V

+3P3V

+3P3V

BD17_B

BD23_B

A15

A16

A17

A18

A19

A20

A21

A14

A15

A16

A17

A18

A19

A20

A21

BD17

BD09

BD23

+3.3V

+3.3V

{BD30}

+3.3V

+3.3V

BD09_B

A22

A23

A22

+3.3V

BD02_B

A24

A23

BD02

+5V

A25

A24

A25

+5V

J1-2

CONN175-CPCI

-12V

B1B2B3B4B5B6B7B8B9

B1B2B3B4B5B6B7B8B9

+5V

-12V

+5V

BA10_B

BA10

CS4-

IRQB-

IRQB-

GND

GND

GND

GND

BA03_B

WDO_B

WDO

GND

GND

GND

BA03

IREQ1-

IREQ1-

GND

GND

+5V

GND

BD05_B

BD13_B

BWR_B-

CS4-

BD20_B

B12

(KEY)

BD08_B

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B13

(KEY)

B14

B15

BWR-

B25

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

GND

{BD26}