Dell Vostro 3360 Schematics

1

WWW.MANUALS.CLAN.SU

2

3

4

5

6

7

8

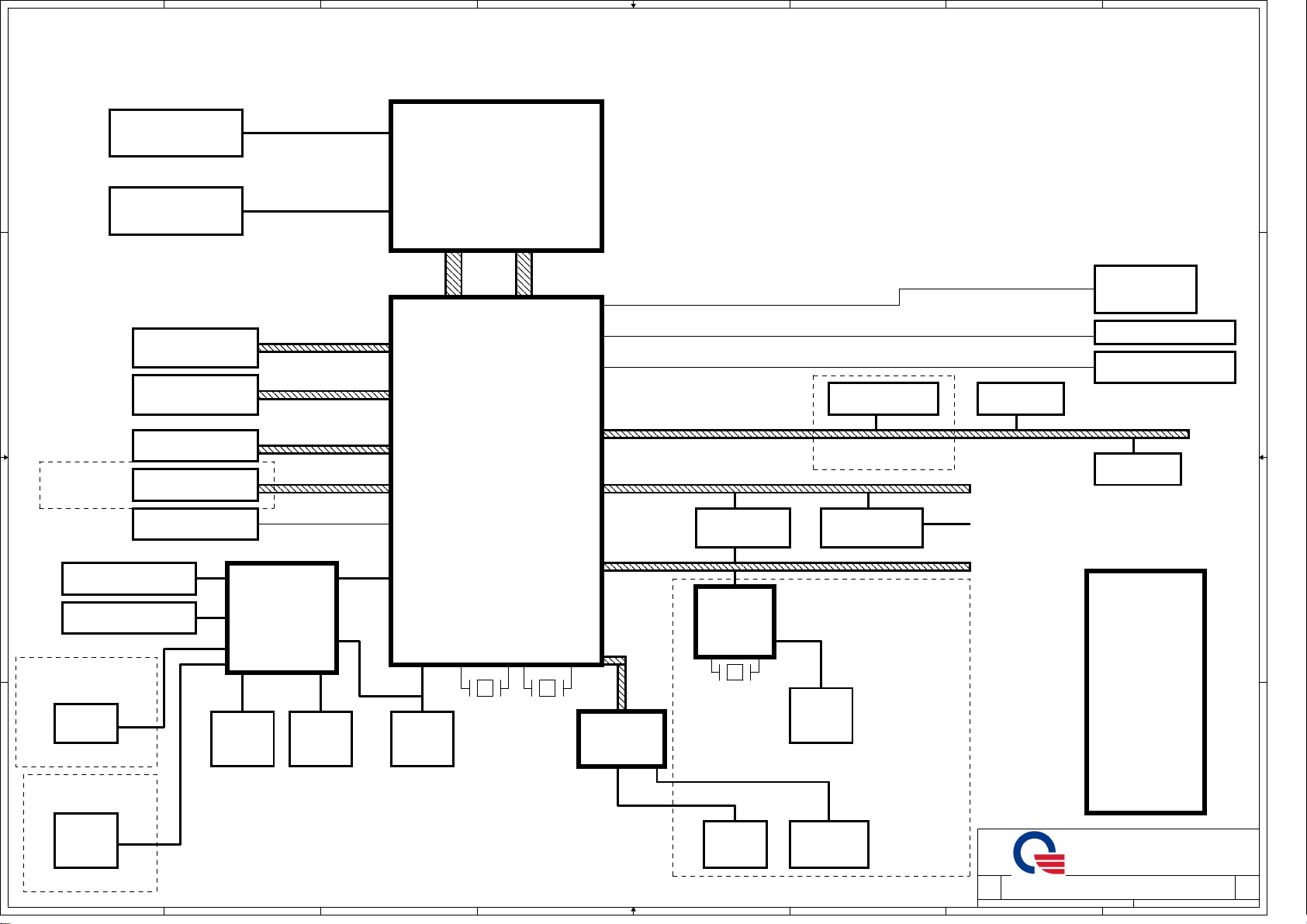

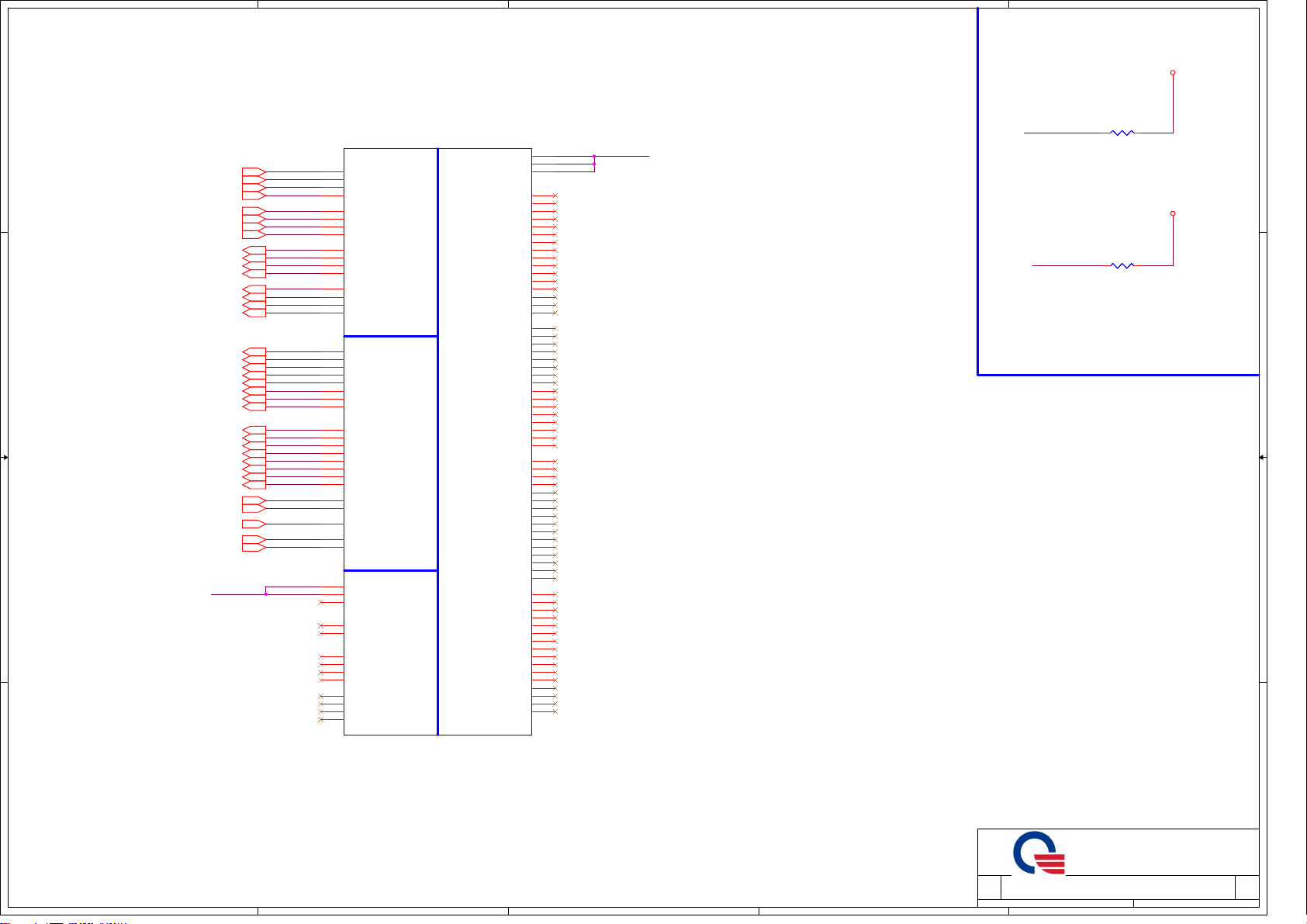

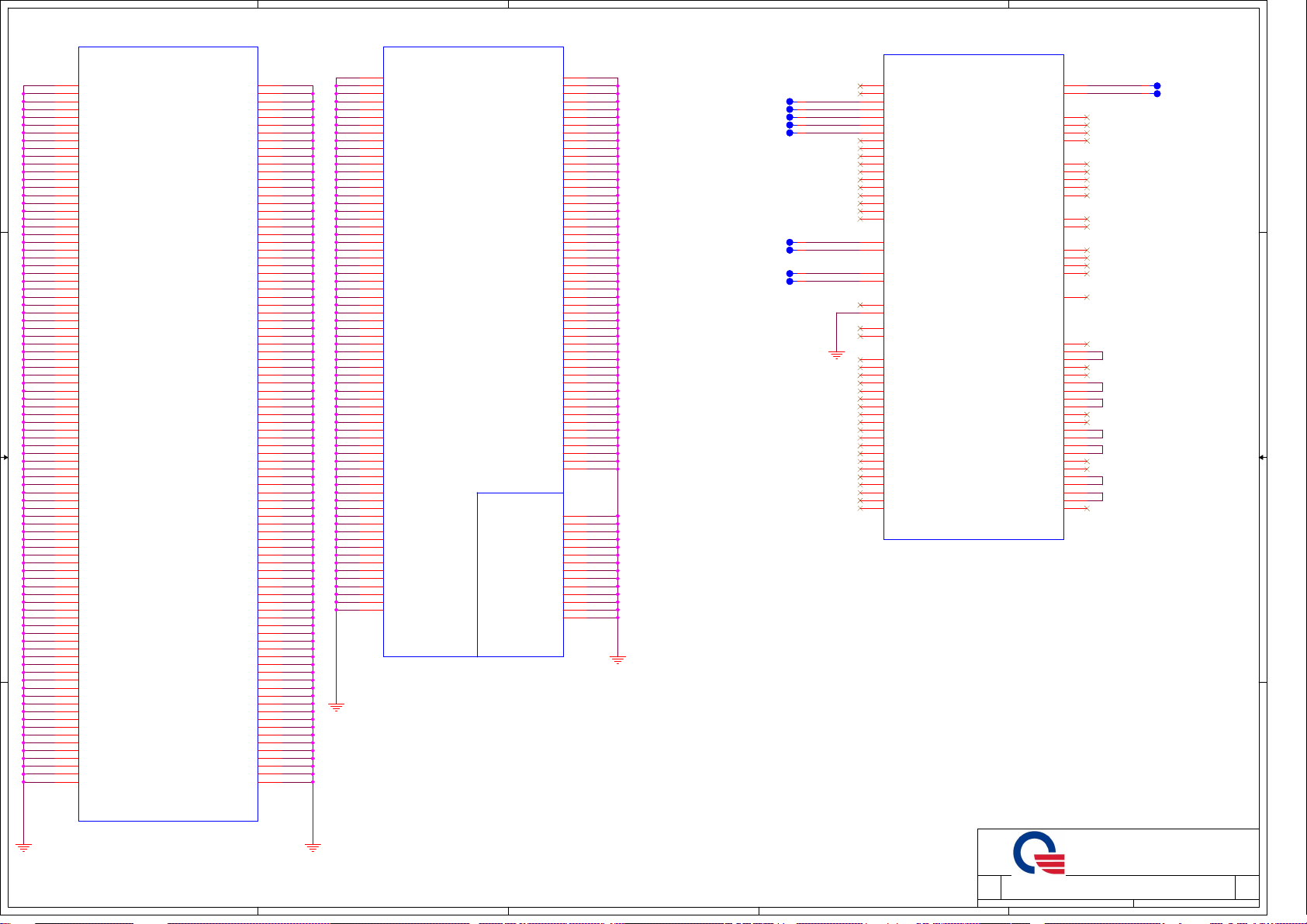

V07 BLOCK DIAGRAM

A A

DDRIII-SODIMM1

H=4mm

PAGE11

DDRIII 1333/1600 MT/s

CPU

Sandy Bridge(ULV) 17W

BGA 1023 DC

DDRIII-SODIMM2

H=4mm

B B

PAGE12

SATA -HDD

PAGE27

m-SATA

DDRIII 1333/1600 MT/s

SATA0 6Gb /S

SATA1 6Gb /S

FDI LINK

2.7GT /s

PAGE28

IO Board

USB3.0 Port W/P X1

USB3.0 Port x1

USB3.0 Ports x1

PAGE22

USB3.0

USB3.0

PAGE24

3-axis Fall Sensor

C C

Keyboard Conn.

PAGE33

PAGE26

SMBUS

LPC

KBC

Touch Pad

PAGE33

ITE 8518

PAGE 31

Hot key Board

Hot key

PAGE29

LED Board

D D

PWM FAN

&Thermal

SPI ROM

8MB

SPI ROM

8MB

PAGE35 PAGE32 PAGE32

2C GT2

31 mm X 24 mm

PAGE 6~10

DMI LINK

5GT /s

Mobile Intel

Series 7 Chipset

PCH

HM77

Panther Point

BGA 989

25 mm X 25 mm

PAGE 13~19

SPI

25MHz

32.768KHz

INT HDMI

INT CRT

INT Single CHANNEL LVDS

iGFX Interfaces

USB2.0

USB2.0

PCI-E

IHDA

Audio Codec

PAGE25

Card Reader

USB[10]

IO Board

U

SB[5]USB[4]

WLAN/BT WWAN/mSATA

PAGE28 PAGE28

PCIE[1]

PCIE[5]

IO Board

LAN

25MHz

RJ45

PAGE24

SATA1

Fingerprint

PAGE33

USB[8]

HDMI CONN

PAGE21

CRT CONN

LCD CONN

Camera

PAGE20

PAGE23

PAGE20

USB[12]

PCB STACK UP

10L

LAYER 1 : TOP

LAYER 2 : GND

LAYER 3 : IN1

LAYER 4 : GND

LAYER 5 : IN2

LAYER 6 : IN3

LAYER 7 : VCC

LAYER 8 : IN4

LAYER 9 : GND

LAYER 10: BOT

UMA

LED

PAGE38

1

2

Como JackSpeaker

PAGE24

3

4

5

6

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, January 09, 2012

Date: Sheet of

Monday, January 09, 2012

Date: Sheet of

Monday, January 09, 2012

7

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

V07

V07

V07

1 46

1 46

1 46

8

1A

1A

1A

1

WWW.MANUALS.CLAN.SU

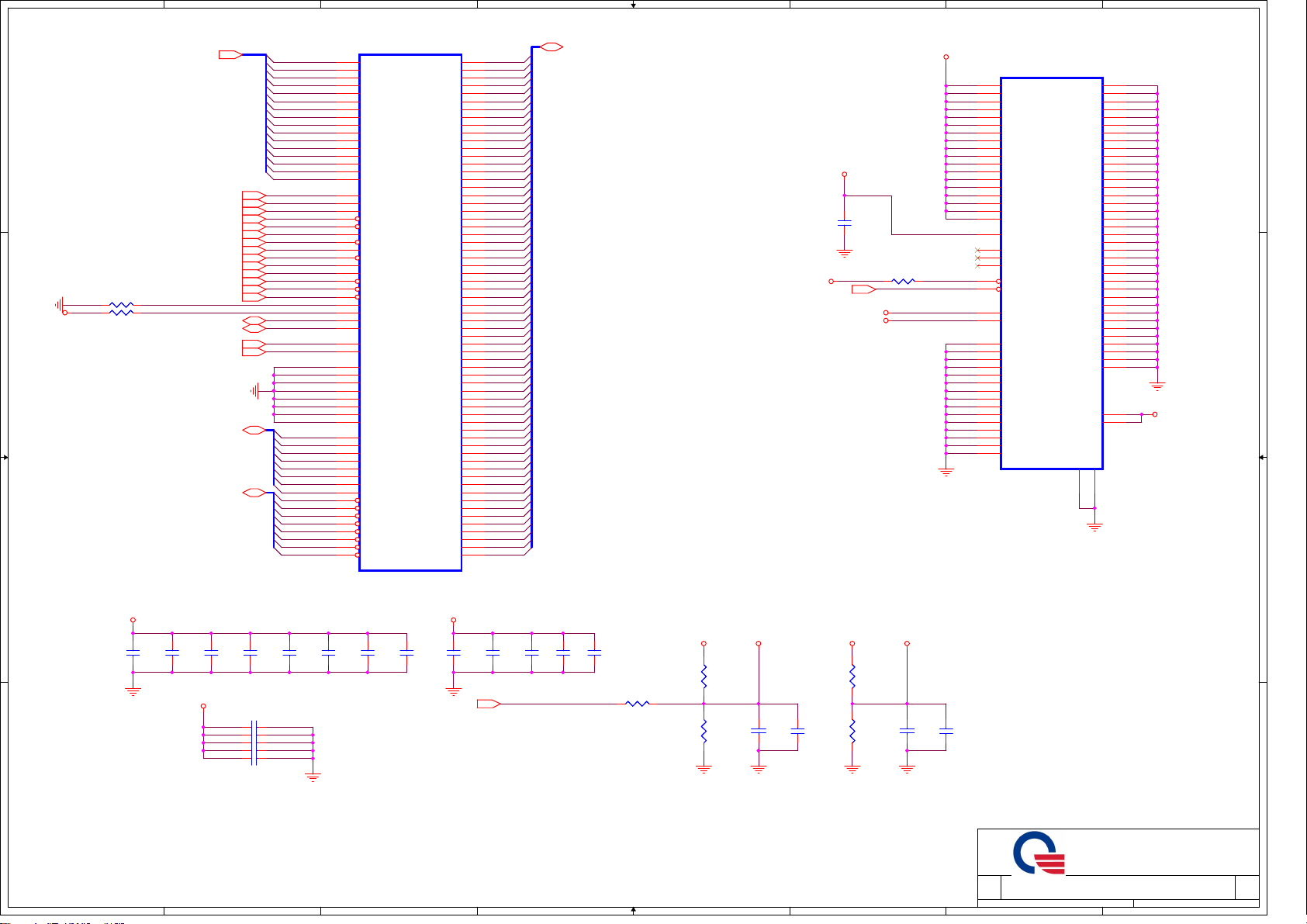

H14

SMBCLK

C9

SMBDATA

A A

+3.3V_SUS

2

2.2K2.2K

+3.3V_RUN

N-MOSFET

N

-MOSFET

+3.3V_RUN

+3.3V_SUS

3

4

5

WLAN_SCLK

+3.3V_RUN

6

7

8

202

200

JDIM1A

2.2K2.2K

A0

202

200

JDIM2A

A4

WLAN_SDATA

+3.3V_RUN

PCH

C8

G12

SML0CLK

SML0DATA

+3.3V_SUS

2.2K

+3.3V_RUN

N-MOSFET

N-MOSFET

+3.3V_RUN

CODEC_SCLK

CODEC_SDATA

2.2K2.2K

1

TS3A225ERTER

2

4

FALL SENSOR

6

LNG3DM

50

2.2K2.2K

E14

SMB_CLK_ME1

M16

SMB_DATA_ME1

+3.3V_ALW

B B

SMBDAT1116

SMBCLK1

115

+3.3V_ALW

SIO

ITE8518E

110

SMBCLK0

111 SMBDAT0

+3.3V_RUN

2.2K2.2K

SMBCLK3

C C

94

SMBDAT3

95

2.2K2.2K

2.2K2.2K

N-MOS

N-MOS

+3.3V_SUS

+3.3V_SUS

100

100

15

THERMAL(EMC2112)

14

3

4

9

8

Battery

Charger

2Eh

Function

DDR3

Thermal IC

Charge IC

Battery

Fall Sensor

WLAN

SMBus AddressIC

JDIM1A A0

JDIM2A A4

EMC1422

BQ24707RGRR

Battery

LNG3DM

WLAN Module X

0101_111xb (2Eh)

0b0001001x (0x12)

Check!!

SCREW PAD

0704 Delet H1~H10, H12~H25

CPU PCH GPU

D D

1

2

MB

H5

H5

*H-T276X292B315X331D118X142P2

*H-T276X292B315X331D118X142P2

1

H19

H19

*H-C197D91P2

*H-C197D91P2

H-C197D91P2

H-C197D91P2

1

H14

H14

H-TC158I142BC102D102PT

H-TC158I142BC102D102PT

H-TC158I142BC102D102PT

H-TC158I142BC102D102PT

1

3

H4

H4

*H-TC276BC315D118P2

H-T276X292B315X331D118X142P2

H-T276X292B315X331D118X142P2

H10

H10

H-TC158I142BC102D102PT

H-TC158I142BC102D102PT

1

*H-TC276BC315D118P2

H-TC158I142BC102D102PT

H-TC158I142BC102D102PT

H9

H9

H-TC158I142BC102D102PT

H-TC158I142BC102D102PT

H-TC158I142BC102D102PT

H-TC158I142BC102D102PT

1

H-TC276BC315D118P2

H-TC276BC315D118P2

1

H1

H1

*H-O114X95D114X95N

*H-O114X95D114X95N

H-O114X95D114X95N

H-O114X95D114X95N

1

4

H17

H17

*H-C236D91P2

*H-C236D91P2

H-C236D91P2

H-C236D91P2

1

H12

H12

*H-O114X95D114X95N

*H-O114X95D114X95N

H-O114X95D114X95N

H-O114X95D114X95N

1

H2

H2

*H-C236D91P2

*H-C236D91P2

H-C236D91P2

H-C236D91P2

1

H15

H15

H-TC158I142BC102D102PT

H-TC158I142BC102D102PT

H16

H16

H-TC158I142BC102D102PT

H-TC158I142BC102D102PT

H-TC158I142BC102D102PT

H-TC158I142BC102D102PT

1

H11

H11

*H-C236D91P2

*H-C236D91P2

H-C236D91P2

H-C236D91P2

1

H-TC158I142BC102D102PT

H-TC158I142BC102D102PT1H18

H7

H7

H-TC158I142BC102D102PT

H-TC158I142BC102D102PT

H-TC158I142BC102D102PT

H-TC158I142BC102D102PT

1

5

H18

*H-C118D63P2

*H-C118D63P2

H-C118D63P2

H-C118D63P2

1

H20

H20

*H-C43D43N

*H-C43D43N

H-C43D43N

H-C43D43N

1

H21

H21

*H-C43D43N

*H-C43D43N

H-C43D43N

H-C43D43N

1

For CPU Use

0704 Modify footprint from

"INTEL-CPU-BRACKET" to "intel-cpu-bkt2"

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, January 09, 2012

Date: Sheet of

Monday, January 09, 2012

Date: Sheet of

6

7

Monday, January 09, 2012

PROJECT :

SMB/SCREW PAD

SMB/SCREW PAD

SMB/SCREW PAD

V07

V07

V07

8

2 46

2 46

2 46

1A

1A

1A

1

WWW.MANUALS.CLAN.SU

2

3

4

5

6

7

8

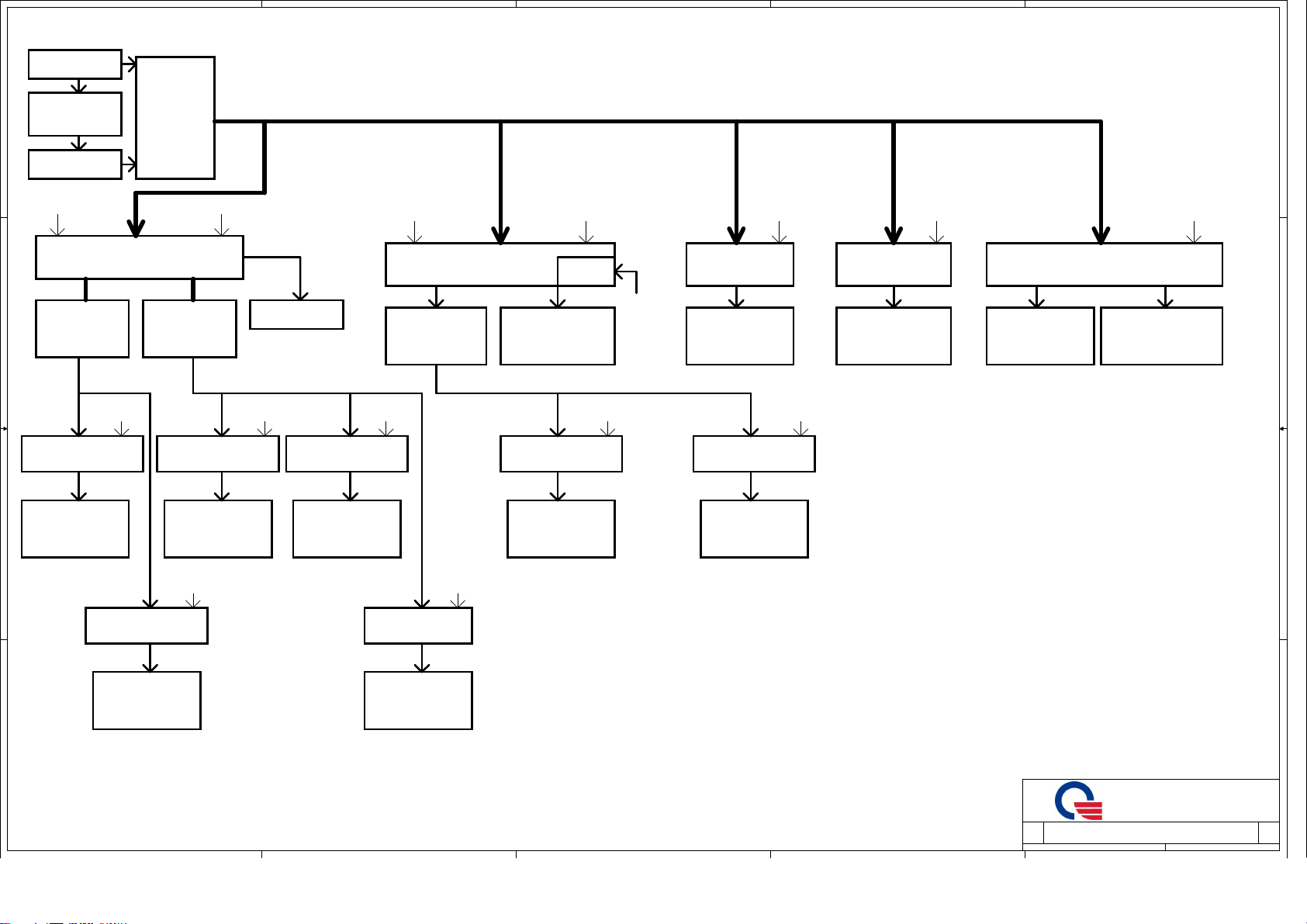

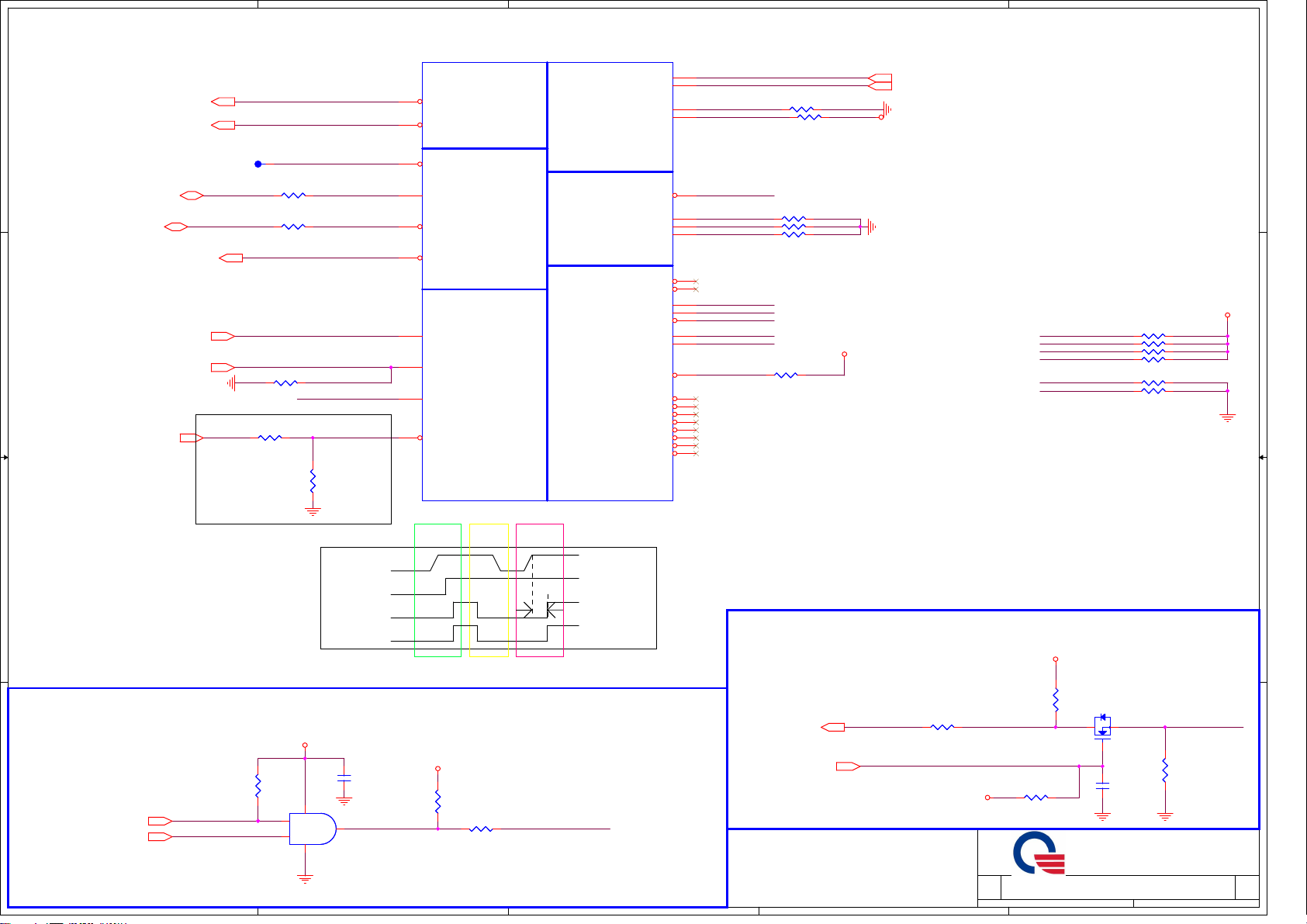

USB Master

A A

USB0

USB1

Port Assignment

External port#1 (USB3.0)

External port#2 (USB3.0/eSATA/

Power share/ debug port)

SATA Master

SATA0

SATA1

SATA2

USB2

External port#3 (USB3.0)

SATA3

USB3

External port#4 (USB3.0) (NC)

SATA4

USB4

MiniCard 1 (WLAN/BT/WiMAX)

SATA5

USB5

B B

USB6

iniCard 2 (WWAN)

M

X(FOR HM77)

Port Assignment

HDD

mSATA

NC

ODD (NC)

eSATA (NC)

NC

PCIE Master

PCIE 1

PCIE 2

PCIE 3

PCIE 4

PCIE 5

PCIE 6

PCIE 7

Port Assignment

WLAN

WWAN (NC)

Card reader (NC)

NC

LAN

Express card (NC)

NC

NCPCIE 8

USB7

X(FOR HM77)

FingerprintUSB8

USB9

USB10

USB11

USB12

Touch panel (NC, for debug)

Card Reader

Express Card (NC)

Camera

C C

D D

USB13

1

NC

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, January 09, 2012 3 46

Date: Sheet of

Monday, January 09, 2012 3 46

Date: Sheet of

2

3

4

5

6

Monday, January 09, 2012 3 46

7

PROJECT :

PORT ASSIGNMENT

PORT ASSIGNMENT

PORT ASSIGNMENT

R11

1A

1A

1A

8

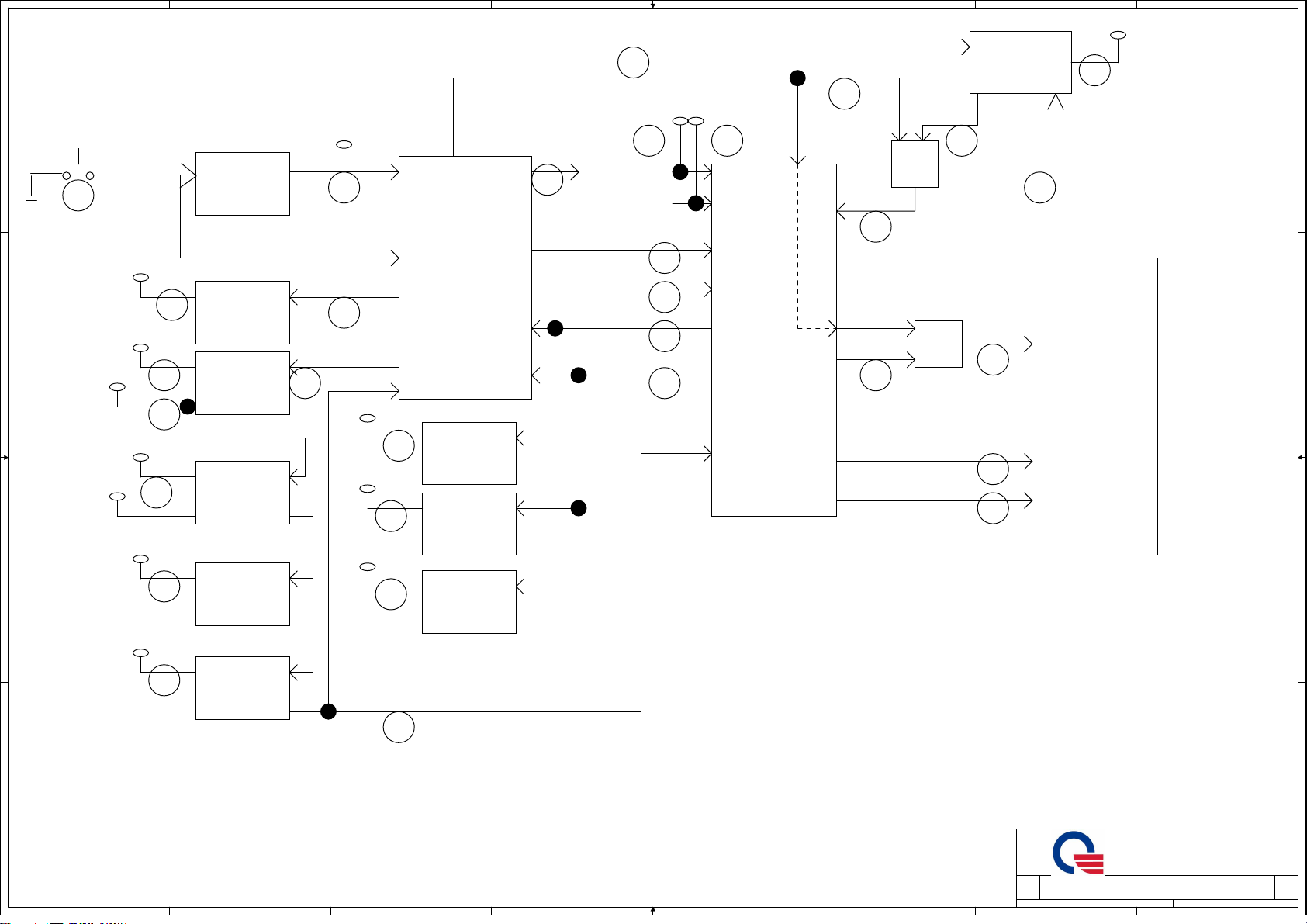

5

WWW.MANUALS.CLAN.SU

4

3

2

1

Adapter 65W

Charger

D D

BQ24707RGRR

PWR_SRC

Shapes:

Via:

VER : 1A

Battery 4S1P

+3.3V_EN2 ALW_ON

TI

TPS51125ARGER

C C

+3.3V_ALW

TDC: 3A

Shapes:

Via:

SUS_ON

Load Switch

FDC655BN

+5V_ALW

TDC: 6.52A

Shapes:

Via:

Load Switch

FDC655BN

+15V_ALW

SUS_ON

Load Switch

TPCC8065-H

RUN_ON

SIO_SLP_S5#

+1.5V_SUS

TDC: 7.9A

Shapes:

Via:

TI

TPS51216RUKR

+0.75V_DDR_VTT

TDC: 1A

Shapes:

Via:

Load Switch

FDC655BN

SIO_SLP_S3#

LDO

+1.5V_SUS

RUN_ON

RichTek

RT8241DGQW

+VCCSA_CORE

TDC: 4.2A

Shapes: 168mil

Via: 6

Load Switch

AON7410

VCCSA_EN

SIO_SLP_S3#

RichTek

RT8240BGQW

+1.05V_PCH

TDC: 10.39A

Shapes: 415.6mil

Via: 15

+3.3V_RUN

+VCC_CORE

TDC: 33A

Shapes:

Via:

ON

ISL95837HRZ-T

+VCC_iGFX_CORE

TDC: 29A

Shapes:

Via:

IMVP_VR_ON

+3.3V_SUS

TDC: 0.1A

B B

Shapes:

Via:

Load Switch

FDC655BN

+3.3V_RUN

TDC: 1.224A

Shapes:

Via:

A A

5

+5V_SUS

TDC: 0.1A

Shapes:

Via:

RUN_ON

+5V_RUN

TDC: 2.415A

Shapes:

Via:

1.05V_PCH_PWRGD

RichTek

RT8068AZQW

+1.8V_RUN

TDC: 0.921A

Shapes:

Via:

4

+1.5V_RUN

TDC: 0.817A

Shapes:

Via:

+1.5V_CPU

TDC: 5A

Shapes:

Via:

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Power Block Diagram

Power Block Diagram

Power Block Diagram

Date: Sheet of

Monday, January 09, 2012 4 46

Date: Sheet of

Monday, January 09, 2012 4 46

Date: Sheet of

3

2

Monday, January 09, 2012 4 46

PROJECT :

V04

V04

V04

1A

1A

1A

1

1

WWW.MANUALS.CLAN.SU

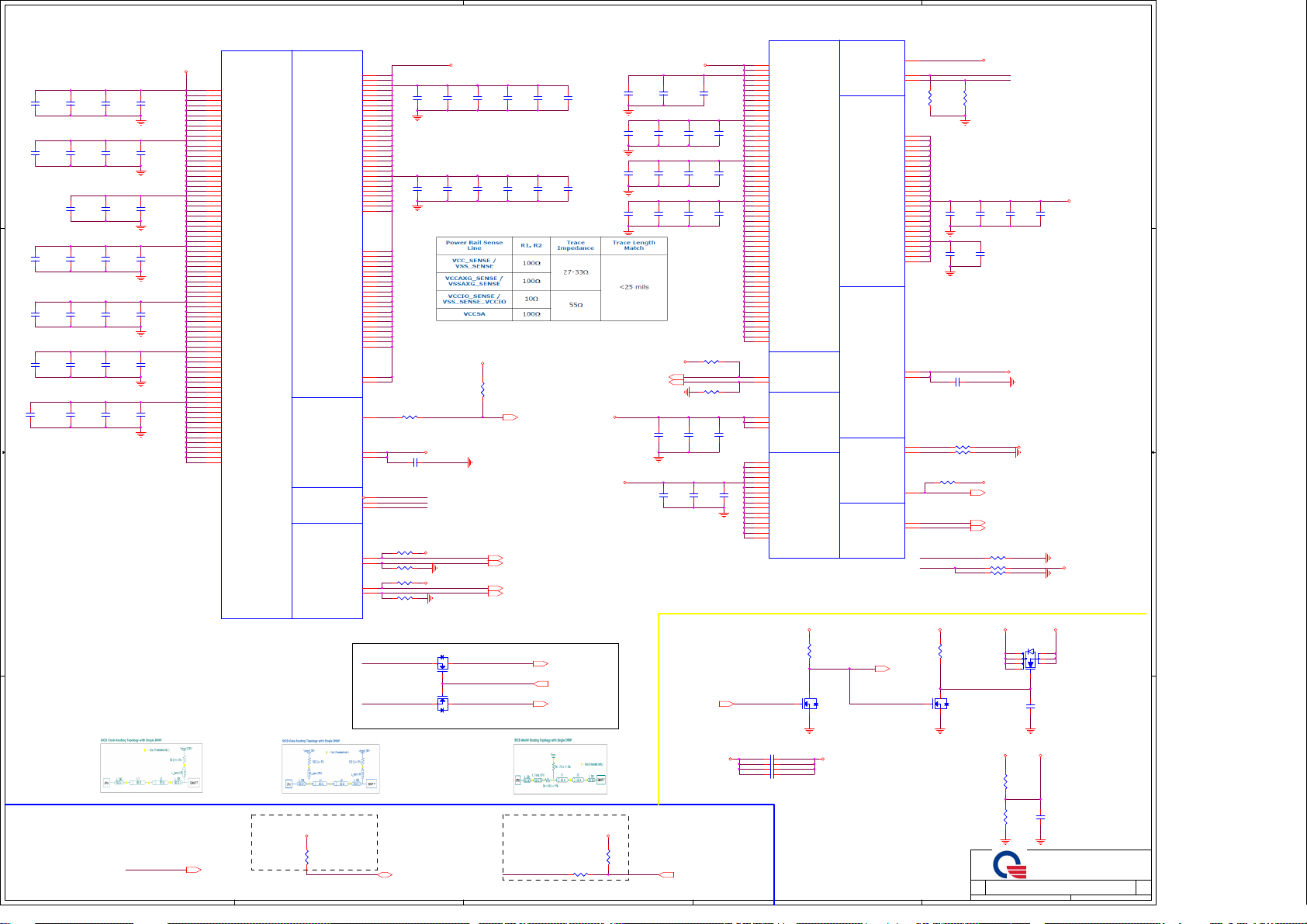

Battery Mode

2

3

4

IMVP_VR_ON

22

5

HWG after 120ms

ECPOWROK

6

EN

+VCC_CORE

SWITCH

7

8

+VCC_CORE

28

23

A A

SYS_PWR_SW#

1

EN

+3.3V_ALW

SWITCH

+3.3V_ALW

2

SUS_ON

EN

5

+5V_SUS +3.3V_SUS

6

+5V_SUS

+3.3V_SUS

7

SYS_PWROK

SWITCH

SUS_ON after 20ms

EC

EN

EN

SYS_PWR_SW#

ALW_ON

3

RUN_ON

15

+1.5V_SUS

HWPG

+5V_ALW

4

B B

+5V_RUN

+3.3V_RUN

16

+5V_ALW

SWITCH

+5V_RUN

+3.3V_RUN

SWITCH

RSMRST#

SIO_PWRBTN#

SLP_S5#

SLP_S3#

8

9

10

PCH

12

30

ECPOWROK

PM_DRAM_PWRGD

24

IMVP_PWRGD

AND

AND

29

SM_DRAMPWROK

25

27

SVID

CPU

17

+1.05V_PCH

+CPU_VTT

18

+1.05V_PCH

+CPU_VTT

SWITCH

+1.8V_RUN

C C

19

+1.8V_RUN

SWITCH

+VCCSA_CORE

EN

POK

EN

POK

+O.75V_DDR_VTT

+1.5V_CPU

13

14

11

+1.5V_SUS

SWITCH

+0.75V

SWITCH

+1.5V_CPU

SWITCH

EN

EN

EN

HWPG

UNCOREPWRGOOD

26

PLTRST#

31

POK

EN

HWPG

20

+VCCSA

SWITCH

21

D D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

POWER SEQUENCE

POWER SEQUENCE

POWER SEQUENCE

1A

1A

1A

8

1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, January 09, 2012 5 46

Date: Sheet of

Monday, January 09, 2012 5 46

Date: Sheet of

2

3

4

5

6

Monday, January 09, 2012 5 46

7

5

WWW.MANUALS.CLAN.SU

4

Ivy Bridge Processor (RESERVED, CFG)

3

2

1

DP & PEG Compensation

+1.05V_PCH

D D

U17A

U17A

DMI_TXN013

DMI_TXN113

DMI_TXN213

DMI_TXN313

DMI_TXP013

DMI_TXP113

DMI_TXP213

DMI_TXP313

DMI_RXN013

DMI_RXN113

DMI_RXN213

DMI_RXN313

DMI_RXP013

DMI_RXP113

DMI_RXP213

DMI_RXP313

C C

B B

eDP_ICOMPO 12mil

eDP_COMPIO 4mil

Programing Disable eDP interface(BIOS)

FDI_FSYNC013

FDI_FSYNC113

FDI_LSYNC013

FDI_LSYNC113

FDI_TXN013

FDI_TXN113

FDI_TXN213

FDI_TXN313

FDI_TXN413

FDI_TXN513

FDI_TXN613

FDI_TXN713

FDI_TXP013

FDI_TXP113

FDI_TXP213

FDI_TXP313

FDI_TXP413

FDI_TXP513

FDI_TXP613

FDI_TXP713

FDI_INT13

eDP_COMP

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

FDI_FSYNC0

FDI_FSYNC1

FDI_INT

FDI_LSYNC0

FDI_LSYNC1

M2

P6

P1

P10

N3

P7

P3

P11

K1

M8

N4

R2

K3

M7

P4

T3

U7

W11

W1

AA6

W6

V4

Y2

AC9

U6

W10

W3

AA7

W7

T4

AA3

AC8

AA11

AC12

U11

AA10

AG8

AF3

AD2

AG11

AG4

AF4

AC3

AC4

AE11

AE7

AC1

AA4

AE10

AE6

IC,IVB_2CBGA,0P7

IC,IVB_2CBGA,0P7

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

FDI0_TX#[0]

FDI0_TX#[1]

FDI0_TX#[2]

FDI0_TX#[3]

FDI1_TX#[0]

FDI1_TX#[1]

FDI1_TX#[2]

FDI1_TX#[3]

FDI0_TX[0]

FDI0_TX[1]

FDI0_TX[2]

FDI0_TX[3]

FDI1_TX[0]

FDI1_TX[1]

FDI1_TX[2]

FDI1_TX[3]

FDI0_FSYNC

FDI1_FSYNC

FDI_INT

FDI0_LSYNC

FDI1_LSYNC

eDP_COMPIO

eDP_ICOMPO

eDP_HPD#

eDP_AUX#

eDP_AUX

eDP_TX#[0]

eDP_TX#[1]

eDP_TX#[2]

eDP_TX#[3]

eDP_TX[0]

eDP_TX[1]

eDP_TX[2]

eDP_TX[3]

DMI Intel(R) FDI

DMI Intel(R) FDI

eDP

eDP

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

PEG_ICOMPO 12mil

PEG_ICOMPI, PEG_RCOMPO 4mil,

G3

G1

G4

H22

J21

B22

D21

A19

D17

B14

D13

A11

B10

G8

A8

B6

H8

E5

K7

K22

K19

C21

D19

C19

D16

C13

D12

C11

C9

F8

C8

C5

H6

F6

K6

G22

C23

D23

F21

H19

C17

K15

F17

F14

A15

J14

H13

M10

F10

D9

J4

F22

A23

D24

E21

G19

B18

K17

G17

E14

C15

K13

G13

K10

G10

D8

K4

PEG_COMP

eDP_COMP

eDP_COMPIO and ICOMPO signals should

be shorted near balls and

routed within 500 mils

PEG_ICOMPI and RCOMPO signals should

be routed within 500 mils

PEG_ICOMPO signals should

be routed within 500 mils

PEG_COMP

R218 24.9/F_4R218 24.9/F_4

1 2

+1.05V_PCH

R72 24.9/F_4R72 24.9/F_4

1 2

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

5

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Re

Date: Sheet of

Monday, January 09, 2012

Date: Sheet of

Monday, January 09, 2012

Date: Sheet of

4

3

2

Monday, January 09, 2012

PROJECT :

Ivy Bridge 1/5

Ivy Bridge 1/5

Ivy Bridge 1/5

1

V07

V07

V07

6 46

6 46

6 46

v

1A

1A

1A

5

WWW.MANUALS.CLAN.SU

4

3

2

1

Ivy Bridge Processor (CLK,MISC,JTAG)

U17B

U17B

J3

BCLK

MISC THERMAL PWR MANAGEMENT

SNB_IVB# N.A at SNB EDS #27637 0.7v1

TP26TP26

H_SNB_IVB#

H_CPUDET#

CATERR#

H_SNB_IVB#16

D D

H_CPUDET#31

F49

C57

C49

PROC_SELECT#

PROC_DETECT#

CATERR#

MISC THERMAL PWR MANAGEMENT

DPLL_REF_CLK

DPLL_REF_CLK#

CLOCKS

CLOCKS

BCLK#

H2

AG3

AG1

CLK_DP_P_R

CLK_DP_N_R

CLK_CPU_BCLKP

CLK_CPU_BCLKN

R216 1K_4R216 1K_4

1 2

R217 1K_4R217 1K_4

1 2

CLK_CPU_BCLKP 17

CLK_CPU_BCLKN 17

+1.05V_PCH

PECI_EC31

IMVP7_PROCHOT#31,45,46

Over 130 degree C will

drive low

C C

H_PM_SYNC13

H_PWRGOOD18

PECI_EC

IMVP7_PROCHOT#

PM_THRMTRIP#18

R21 43_4R21 43_4

1 2

R255 56_4R255 56_4

1 2

PM_THRMTRIP#

H_PM_SYNC

H_PWRGOOD

12

1.1V

PLTRST#16,24,28,31

R254 1.5K/F_4R254 1.5K/F_4

12

Intel spec VinH min =VCCIO X 0.7

B B

H_PROCHOT#

R25910K_4 R25910K_4

SM_DRAMPWROK

CPU_PLTRST#_RPLTRST#

12

R251

R251

750/F_4

750/F_4

+1.5V_CPU

PECI_EC_R

A48

PECI

C45

PROCHOT#

D45

THERMTRIP#

C48

PM_SYNC

B46

UNCOREPWRGOOD

BE45

SM_DRAMPWROK

D44

RESET#

IC,IVB_2CBGA,0P7

IC,IVB_2CBGA,0P7

Boot S3

S3 RSM

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

DDR3

MISC

DDR3

MISC

PRDY#

PREQ#

TCK

TMS

TRST#

TDI

TDO

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

JTAG & BPM

JTAG & BPM

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

CPU_DRAMRST#

AT30

BF44

BE43

BG43

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

R110 140/F_4R110 140/F_4

1 2

R111 25.5/F_4R111 25.5/F_4

1 2

R112 200/F_4R112 200/F_4

1 2

SM_RCOMP_0, SM_RCOMP_1 20mil / SM_RCOMP_2 15mil.

N53

N55

XDP_TCLK

L56

XDP_TMS

L55

XDP_TRST#

J58

XDP_TDI

M60

XDP_TDO

L59

K58

G58

E55

E59

G55

G59

H60

J59

J61

XDP_DBRST#

1 2

R267 1K_4R267 1K_4

+3.3V_RUN

XDP_TMS

XDP_TDI

XDP_TDO

IMVP7_PROCHOT#

XDP_TCLK

XDP_TRST#

+1.05V_PCH

R268 *51_4_NCR268 *51_4_NC

R261 *51_4_NCR261 *51_4_NC

R262 *51_4_NCR262 *51_4_NC

R258 62_4R258 62_4

R266 *51_4_NCR266 *51_4_NC

R263 *51_4_NCR263 *51_4_NC

1 2

1 2

12

12

12

12

DRAM_PWRGD

SYS_PWROK

SM_DRAMPWROK

100 ns after +1.5V_CPU

reaches 80%

Follow #DG1.0 436735 P107

DRAMRST# Routing Illustration

+1.5V_SUS

Follow #DG1.0 436735 P105

DDR Power Gating Topology

+3.3V_SUS

+1.5V_CPU

R108

R108

200/F_4

200/F_4

1 2

1 2

R109 130/F_4R109 130/F_4

4

SM_DRAMPWROK

3

U5

U5

74AHC1G09GW

74AHC1G09GW

3 5

12

C178

C178

0.1U/16V_4

0.1U/16V_4

SM_DRAMPWROK_R

4

12

R118

R118

200/F_4

A A

PM_DRAM_PWRGD13

EC_PWROK13,31

PM_DRAM_PWRGD

EC_PWROK

5

200/F_4

2

1

DDR3_DRAMRST#11,12

DDR_HVREF_RST_PCH9,17

R22 near the SODIMMs

R36 1K_4R36 1K_4

DDR_HVREF_RST_PCH

2

12

+3.3V_SUS

Size Document Number Rev

Size Document Number Rev

Size Document Number Re

Date: Sheet of

Date: Sheet of

Date: Sheet of

1 2

R41 1K_4R41 1K_4

Ivy Bridge 2/5

Ivy Bridge 2/5

Ivy Bridge 2/5

Monday, January 09, 2012

Monday, January 09, 2012

Monday, January 09, 2012

Q1

Q1

R34

R34

2N7002W

2N7002W

1K_4

1K_4

1 2

3 1

2

12

C17

C17

0.047U/10V_4

0.047U/10V_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

12

R42

R42

4.99K/F_4

4.99K/F_4

V07

V07

V07

7 46

7 46

7 46

CPU_DRAMRST#DDR3_DRAMRST#_RDDR3_DRAMRST#

v

1A

1A

1A

5

WWW.MANUALS.CLAN.SU

4

3

2

1

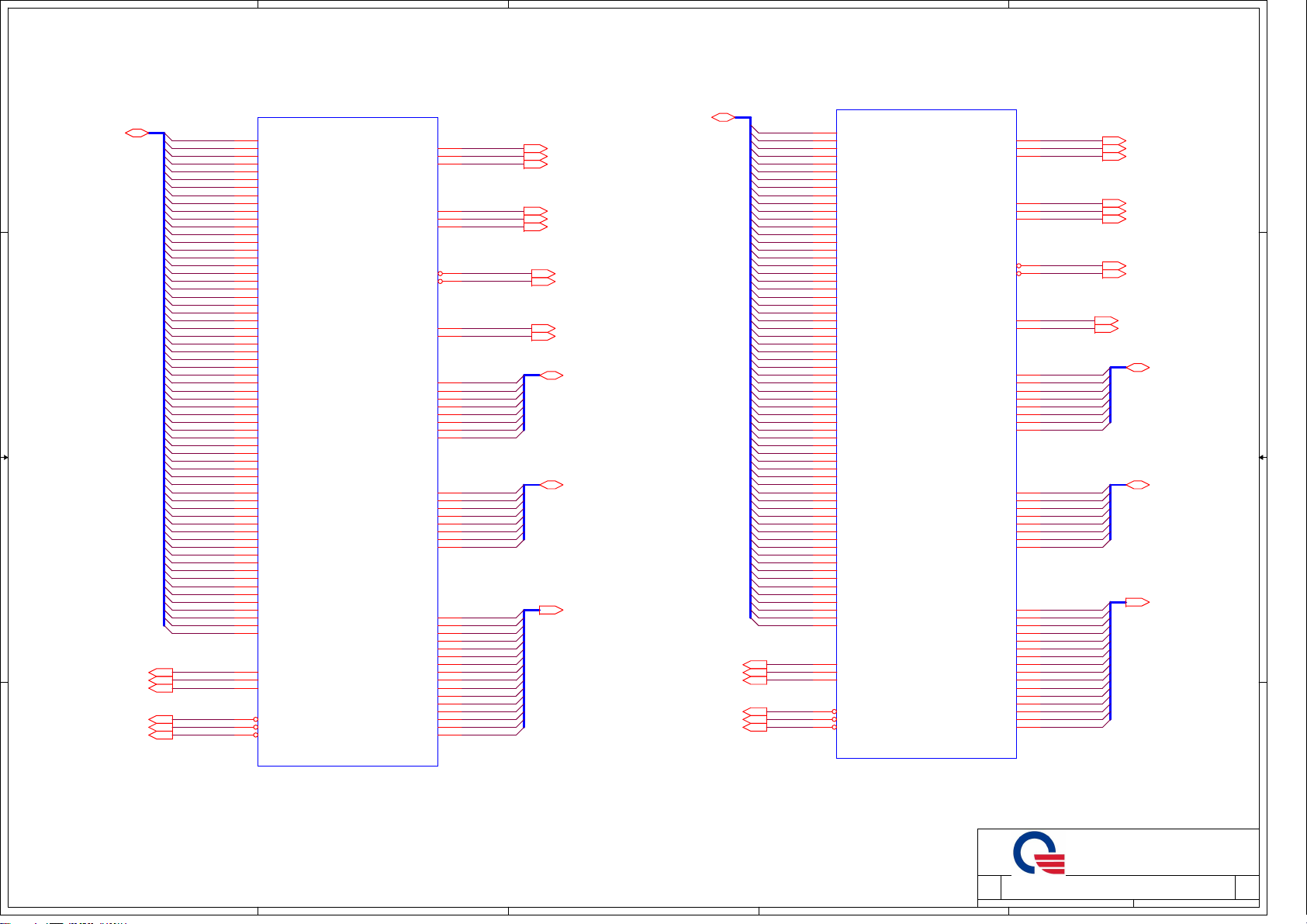

Ivy Bridge Processor (DDR3)

U17D

AL4

AL1

AN3

AR4

AK4

AK3

AN4

AR1

AU4

AT2

AV4

BA4

AU3

AR3

AY2

BA3

BE9

BD9

BD13

BF12

BF8

BD10

BD14

BE13

BF16

BE17

BE18

BE21

BE14

BG14

BG18

BF19

BD50

BF48

BD53

BF52

BD49

BE49

BD54

BE53

BF56

BE57

BC59

AY60

BE54

BG54

BA58

AW59

AW58

AU58

AN61

AN59

AU59

AU61

AN58

AR58

AK58

AL58

AG58

AG59

AM60

AL59

AF61

AH60

BG39

BD42

AT22

AV43

BF40

BD45

U17D

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

SB_CK[0]

SB_CK#[0]

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

AY34

AR22

BA36

BB36

BF27

BE41

BE47

AT43

BG47

AL3

AV3

BG11

BD17

BG51

BA59

AT60

AK59

AM2

AV1

BE11

BD18

BE51

BA61

AR59

AK61

BF32

BE33

BD33

AU30

BD30

AV30

BG30

BD29

BE30

BE28

BD43

AT28

AV28

BD46

AT26

AU22

M_B_CLKN0

M_B_CKE0

M_B_CLKP1

M_B_CLKN1

M_B_CKE1

M_B_CS#0

M_B_CS#1

M_B_ODT0

M_B_ODT1

M_B_DQSN0

M_B_DQSN1

M_B_DQSN2

M_B_DQSN3

M_B_DQSN4

M_B_DQSN5

M_B_DQSN6

M_B_DQSN7

M_B_DQSP0

M_B_DQSP1

M_B_DQSP2

M_B_DQSP3

M_B_DQSP4

M_B_DQSP5

M_B_DQSP6

M_B_DQSP7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_CLKP0

BA34

M_B_CLKP0 12

M_B_CLKN0 12

M_B_CKE0 12

M_B_CLKP1 12

M_B_CLKN1 12

M_B_CKE1 12

M_B_CS#0 12

M_B_CS#1 12

M_B_ODT0 12

M_B_ODT1 12

M_B_DQSN[7..0] 12

M_B_DQSP[7..0] 12

M_B_A[15..0] 12

U17C

D D

C C

B B

M_A_DQ[63..0]11

M_A_BS011

M_A_BS111

M_A_BS211

M_A_CAS#11

M_A_RAS#11

M_A_WE#11

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33 M_B_DQ34

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_BS0

M_A_BS1

M_A_BS2

M_A_CAS#

M_A_RAS#

M_A_WE#

AG6

AP11

AJ10

AR11

AP6

AU6

AV9

AR6

AP8

AT13

AU13

BC7

BB7

BA13

BB11

BA7

BA9

BB9

AY13

AV14

AR14

AY17

AR19

BA14

AU14

BB14

BB17

BA45

AR43

AW48

BC48

BC45

AR45

AT48

AY48

BA49

AV49

BB51

AY53

BB49

AU49

BA53

BB55

BA55

AV56

AP50

AP53

AV54

AT54

AP56

AP52

AN57

AN53

AG56

AG53

AN55

AN52

AG55

AK56

BD37

BF36

BA28

BE39

BD39

AT41

AJ6

AL6

AJ8

AL8

AL7

U17C

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

SA_CK[0]

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AV36

AY26

AT40

AU40

BB26

BB40

BC41

AY40

BA41

AL11

AR8

AV11

AT17

AV45

AY51

AT55

AK55

AJ11

AR10

AY11

AU17

AW45

AV51

AT56

AK54

BG35

BB34

BE35

BD35

AT34

AU34

BB32

AT32

AY32

AV32

BE37

BA30

BC30

AW41

AY28

AU26

M_A_CLKN0

M_A_CKE0

M_A_CLKP1

M_A_CLKN1

M_A_CKE1

M_A_CS#0

M_A_CS#1

M_A_ODT0

M_A_ODT1

M_A_DQSN0

M_A_DQSN1

M_A_DQSN2

M_A_DQSN3

M_A_DQSN4

M_A_DQSN5

M_A_DQSN6

M_A_DQSN7

M_A_DQSP0

M_A_DQSP1

M_A_DQSP2

M_A_DQSP3

M_A_DQSP4

M_A_DQSP5

M_A_DQSP6

M_A_DQSP7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_CLKP0

AU36

M_A_CLKP0 11

M_A_CLKN0 11

M_A_CKE0 11

M_A_CLKP1 11

M_A_CLKN1 11

M_A_CKE1 11

M_A_CS#0 11

M_A_CS#1 11

M_A_ODT0 11

M_A_ODT1 11

M_A_DQSN[7..0] 11

M_A_DQSP[7..0] 11

M_A_A[15..0] 11

M_B_DQ[63..0]12

M_B_BS012

M_B_BS112

M_B_BS212

M_B_CAS#12

M_B_RAS#12

M_B_WE#12

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_BS0

M_B_BS1

M_B_BS2

M_B_CAS#

M_B_RAS#

M_B_WE#

IC,IVB_2CBGA,0P7

IC,IVB_2CBGA,0P7

IC,IVB_2CBGA,0P7

A A

5

4

3

IC,IVB_2CBGA,0P7

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, January 09, 2012

Date: Sheet of

Monday, January 09, 2012

Date: Sheet of

Monday, January 09, 2012

PROJECT :

Ivy Bridge 3/5

Ivy Bridge 3/5

Ivy Bridge 3/5

1

V07

V07

V07

8 46

8 46

8 46

1A

1A

1A

5

WWW.MANUALS.CLAN.SU

Ivy Bridge Processor

CPU Core Power

SNB: 33A

IVY: 33A

10uF x 11

C92

C92

12

10U/6.3V_6

10U/6.3V_6

D D

C91

C91

12

10U/6.3V_6

10U/6.3V_6

C138

C138

12

1U/6.3V_4

1U/6.3V_4

C116

C116

12

1U/6.3V_4

1U/6.3V_4

C C

C114

C114

12

1U/6.3V_4

1U/6.3V_4

EC55

EC55

220P/50V_4

220P/50V_4

1 2

B B

A A

Layout note: need routing

together and ALERT need

between CLK and DATA

1uF x15

C147

C147

C130

C130

12

12

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

C122

C122

C153

C153

12

12

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

C152

C152

C109

C109

12

12

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

C150

C149

C149

12

1U/6.3V_4

1U/6.3V_4

C139

C139

12

1U/6.3V_4

1U/6.3V_4

C115

C115

12

1U/6.3V_4

1U/6.3V_4

C113

C113

12

1U/6.3V_4

1U/6.3V_4

C150

C112

C112

12

1U/6.3V_4

1U/6.3V_4

C140

C140

C121

C121

12

1U/6.3V_4

1U/6.3V_4

C94

C94

C133

C133

12

1U/6.3V_4

1U/6.3V_4

C135

C135

C151

C151

12

1U/6.3V_4

1U/6.3V_4

5

C90

C90

C97

C97

C141

C141

12

10U/6.3V_6

10U/6.3V_6

12

10U/6.3V_6

10U/6.3V_6

12

10U/6.3V_6

10U/6.3V_6

12

1U/6.3V_4

1U/6.3V_4

12

1U/6.3V_4

1U/6.3V_4

12

1U/6.3V_4

1U/6.3V_4

12

1U/6.3V_4

1U/6.3V_4

VR_SVID_CLK

+VCC_CORE

A26

A29

A31

A34

A35

A38

A39

A42

C26

C27

C32

C34

C37

C39

C42

D27

D32

D34

D37

D39

D42

E26

E28

E32

E34

E37

E38

F25

F26

F28

F32

F34

F37

F38

F42

G42

H25

H26

H28

H29

H32

H34

H35

H37

H38

H40

J25

J26

J28

J29

J32

J34

J35

J37

J38

J40

J42

K26

K27

K29

K32

K34

K35

K37

K39

K42

L25

L28

L33

L36

L40

N26

N30

N34

N38

VR_SVID_CLK 45

POWER

POWER

U17F

U17F

VCC[1]

VCC[2]

VCC[3]

VCC[4]

VCC[5]

VCC[6]

VCC[7]

VCC[8]

VCC[9]

VCC[10]

VCC[11]

VCC[12]

VCC[13]

VCC[14]

VCC[15]

VCC[16]

VCC[17]

VCC[18]

VCC[19]

VCC[20]

VCC[21]

VCC[22]

VCC[23]

VCC[24]

VCC[25]

VCC[26]

VCC[27]

VCC[28]

VCC[29]

VCC[30]

VCC[31]

VCC[32]

VCC[33]

VCC[34]

VCC[35]

VCC[36]

VCC[37]

VCC[38]

VCC[39]

VCC[40]

VCC[41]

VCC[42]

VCC[43]

VCC[44]

VCC[45]

VCC[46]

VCC[47]

VCC[48]

VCC[49]

VCC[50]

VCC[51]

VCC[52]

VCC[53]

VCC[54]

VCC[55]

VCC[56]

VCC[57]

VCC[58]

VCC[59]

VCC[60]

VCC[61]

VCC[62]

VCC[63]

VCC[64]

VCC[66]

VCC[67]

VCC[68]

VCC[69]

VCC[70]

VCC[71]

VCC[72]

VCC[73]

VCC[74]

VCC[75]

VCC[76]

IC,IVB_2CBGA,0P7

IC,IVB_2CBGA,0P7

CORE SUPPLY

CORE SUPPLY

Place PU resistor close to CPU

+1.05V_PCH +1.05V_PCH

4

1.05V_PCH

SNB: 8.5A

IVY: 8.5A

AF46

VCCIO[1]

AG48

VCCIO[3]

AG50

VCCIO[4]

AG51

VCCIO[5]

AJ17

VCCIO[6]

AJ21

VCCIO[7]

AJ25

VCCIO[8]

AJ43

VCCIO[9]

AJ47

VCCIO[10]

AK50

VCCIO[11]

AK51

VCCIO[12]

AL14

VCCIO[13]

AL15

VCCIO[14]

AL16

VCCIO[15]

AL20

VCCIO[16]

AL22

VCCIO[17]

AL26

VCCIO[18]

AL45

VCCIO[19]

AL48

VCCIO[20]

AM16

VCCIO[21]

AM17

VCCIO[22]

AM21

VCCIO[23]

AM43

VCCIO[24]

AM47

VCCIO[25]

AN20

VCCIO[26]

AN42

VCCIO[27]

AN45

VCCIO[28]

AN48

VCCIO[29]

AA14

VCCIO[30]

AA15

VCCIO[31]

AB17

VCCIO[32]

VCCIO[33]

VCCIO[34]

VCCIO[35]

VCCIO[36]

VCCIO[37]

VCCIO[38]

VCCIO[39]

VCCIO[40]

VCCIO[41]

VCCIO[42]

VCCIO[43]

VCCIO[44]

VCCIO[45]

VCCIO[46]

VCCIO[47]

VCCIO[48]

VCCIO[49]

VCCIO50

VCCIO51

VCCIO_SEL

VCCPQE[1]

VCCPQE[2]

RAILS

RAILS

VIDALERT#

VIDSOUT

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VIDSCLK

AB20

AC13

AD16

AD18

AD21

AE14

AE15

AF16

AF18

AF20

AG15

AG16

AG17

AG20

AG21

AJ14

AJ15

W16

W17

BC22

AM25

AN22

A44

B43

C44

F43

G43

AN16

AN17

PEG IO AND DDR IO

PEG IO AND DDR IO

VSS_SENSE_VCCIO

SENSE LINES SVID QUIET

SENSE LINES SVID QUIET

10uF x12

1 2

C175 1U/6.3V_4C175 1U/6.3V_4

H_CPU_SVIDALRT#

VR_SVID_CLK

VR_SVID_DATA

1 2

R98 100/F_4R98 100/F_4

1 2

R95 100/F_4R95 100/F_4

1 2

R44 10/F_4R44 10/F_4

1 2

R45 10/F_4R45 10/F_4

C35

C35

C98

C98

1 2

10U/6.3V_8

10U/6.3V_8

12

12

10U/6.3V_6

10U/6.3V_6

R226*0_4_NC R226*0_4_ NC

+1.05V_PCH

+VCC_CORE

+1.05V_PCH

C43

C43

C77

C77

+1.05V_PCH

12

10U/6.3V_8

10U/6.3V_8

12

10U/6.3V_6

10U/6.3V_6

H_VTTVID1

VCCIO_SENSE

VSSIO_SENSE

C82

C82

C83

C83

VCCSENSE

VSSSENSE

12

10U/6.3V_6

10U/6.3V_6

12

10U/6.3V_6

10U/6.3V_6

+3.3V_RUN

12

R222

R222

10K_4

10K_4

M3 VREF

Q4

Q4

SMDDR_VREF_DQ0_M3_C

*AP2302GN_NC

*AP2302GN_NC

SMDDR_VREF_DQ1_M3_C

*AP2302GN_NC

*AP2302GN_NC

SVID DATA SVID ALERTSVID CLK

12

R94

R94

130/F_4

130/F_4

VR_SVID_DATA VR_SVID_ALERT#H_CPU_SVIDALRT#

4

VR_SVID_DATA 45

SMDDR_VREF_DQ0_M3

31

2

DDR_HVREF_RST_PCH

2

SMDDR_VREF_DQ1_M3

31

Vgs=2.5V Rds=115m

Q2

Q2

C95

C95

C34

C85

C85

12

10U/6.3V_6

10U/6.3V_6

C72

C72

12

10U/6.3V_6

10U/6.3V_6

VCCSENSE 45

VSSSENSE 45

VCCIO_SENSE 43

VSSIO_SENSE 43

Pl

C34

12

12

10U/6.3V_6

10U/6.3V_6

10U/6.3V_8

10U/6.3V_8

C174

C174

C173

C173

12

12

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

H_VTTVID1 43

SMDDR_VREF_DQ0_M3 11

DDR_HVREF_RST_PCH 7,17

SMDDR_VREF_DQ1_M3 12

ace PU resistor close to CPU

1 2

R104 43_4R104 43_4

3

+1.8V_RUN

+VCCSA_CORE

CPU SA

SNB: 6A

IVY: 6A

3

CPU VGT

SNB: 29A

IVY: 29A

10uF x 12

1 2

C170

C170

12

10U/6.3V_6

10U/6.3V_6

C172

C172

12

10U/6.3V_6

10U/6.3V_6

C188

C188

12

10U/6.3V_6

10U/6.3V_6

VCC_AXG_SENSE45

VSS_AXG_SENSE45

CPU VCCPL

SNB: 1.2A

IVY: 1.2A

10uF x 1

1uF x 2

*10U/6.3V_6_NC

*10U/6.3V_6_NC

12

R103

R103

75/F_4

75/F_4

EC54

EC54

330P/50V_4

330P/50V_4

+VCC_GFX_CORE

C241

C241

C84

C84

2

Ivy Bridge Processor (GRAPHIC POWER)

POWER

POWER

U17G

U17G

EC52

EC52

3.3P/50V_4

3.3P/50V_4

C169

C169

C177

C177

C264

C264

C243

C243

C88

C88

12

10U/6.3V_6

10U/6.3V_6

12

10U/6.3V_6

10U/6.3V_6

12

10U/6.3V_6

10U/6.3V_6

12

R102100/F_4 R102100/F_4

12

R105100/F_4 R105100/F_4

12

1U/6.3V_4

1U/6.3V_4

12

AA46

VAXG[1]

AB47

VAXG[2]

AB50

VAXG[3]

AB51

VAXG[4]

AB52

VAXG[5]

AB53

VAXG[6]

AB55

VAXG[7]

AB56

VAXG[8]

AB58

VAXG[9]

AB59

VAXG[10]

AC61

VAXG[11]

AD47

VAXG[12]

AD48

VAXG[13]

AD50

VAXG[14]

AD51

VAXG[15]

AD52

VAXG[16]

AD53

VAXG[17]

AD55

VAXG[18]

AD56

VAXG[19]

AD58

VAXG[20]

AD59

VAXG[21]

AE46

VAXG[22]

N45

VAXG[23]

P47

VAXG[24]

P48

VAXG[25]

P50

VAXG[26]

P51

VAXG[27]

P52

VAXG[28]

P53

VAXG[29]

P55

VAXG[30]

P56

VAXG[31]

P61

VAXG[32]

T48

VAXG[33]

T58

VAXG[34]

T59

VAXG[35]

T61

VAXG[36]

U46

VAXG[37]

V47

VAXG[38]

V48

VAXG[39]

V50

VAXG[40]

V51

VAXG[41]

V52

VAXG[42]

V53

VAXG[43]

V55

VAXG[44]

V56

VAXG[45]

V58

VAXG[46]

V59

VAXG[47]

W50

VAXG[48]

W51

VAXG[49]

W52

VAXG[50]

W53

VAXG[51]

W55

VAXG[52]

W56

VAXG[53]

W61

VAXG[54]

Y48

VAXG[55]

Y61

VAXG[56]

F45

VAXG_SENSE

G45

VSSAXG_SENSE

BB3

VCCPLL[1]

BC1

VCCPLL[2]

BC4

VCCPLL[3]

L17

VCCSA[1]

L21

VCCSA[2]

N16

VCCSA[3]

N20

VCCSA[4]

N22

VCCSA[5]

P17

VCCSA[6]

P20

VCCSA[7]

R16

VCCSA[8]

R18

VCCSA[9]

R21

VCCSA[10]

U15

VCCSA[11]

V16

VCCSA[12]

V17

VCCSA[13]

V18

VCCSA[14]

V21

VCCSA[15]

W20

VCCSA[16]

IC,IVB_2CBGA,0P7

IC,IVB_2CBGA,0P7

SIO_SLP_S3#

DMN66D0LDW-7

DMN66D0LDW-7

C86 0.1U/16V_4C86 0.1U/16V_4

1 2

C89 0.1U/16V_4C89 0.1U/16V_4

1 2

C96 0.1U/16V_4C96 0.1U/16V_4

1 2

C106 0.1U/16V_4C106 0.1U/16V_4

1 2

GRAPHICS

GRAPHICS

SENSE

LINES

SENSE

LINES

1.8V RAIL

1.8V RAIL

SA RAIL

SA RAIL

VCCSA VID

VCCSA VID

+5V_ALW

12

R99

R99

10K_4

10K_4

PS_S3CNTRL

34

Q14A

Q14A

5

2

+VCC_GFX_CORE

EC53

EC53

33P/50V_4

33P/50V_4

1 2

C176

C176

12

10U/6.3V_6

10U/6.3V_6

C163

C163

12

10U/6.3V_6

10U/6.3V_6

C189

C189

12

10U/6.3V_6

10U/6.3V_6

12

*10U/6.3V_6_NC

*10U/6.3V_6_NC

10uF x 3

12

*10U/6.3V_6_NC

*10U/6.3V_6_NC

1 2

C171

C171

12

10U/6.3V_6

10U/6.3V_6

C162

C162

12

10U/6.3V_6

10U/6.3V_6

C190

C190

12

10U/6.3V_6

10U/6.3V_6

VCC_AXG_SENSE

VSS_AXG_SENSE

C242

C242

12

1U/6.3V_4

1U/6.3V_4

12

C78

C78

10U/6.3V_6

10U/6.3V_6

SIO_SLP_S3#13,25,31,41

+1.5V_SUS +1.5V_CPU

VR_SVID_ALERT# 45

CAD Note: +VDDR_REF_CPU should

have 10 mil trace width

AY43

SM_VREF

BE7

SA_DIMM_VREFDQ

BG7

SB_DIMM_VREFDQ

VREF

VREF

AJ28

VDDQ[1]

AJ33

VDDQ[2]

AJ36

VDDQ[3]

AJ40

VDDQ[4]

AL30

VDDQ[5]

AL34

VDDQ[6]

AL38

VDDQ[7]

AL42

VDDQ[8]

AM33

VDDQ[9]

AM36

VDDQ[10]

AM40

VDDQ[11]

AN30

VDDQ[12]

AN34

VDDQ[13]

AN38

VDDQ[14]

AR26

VDDQ[15]

AR28

VDDQ[16]

AR30

VDDQ[17]

AR32

VDDQ[18]

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

QUIET RAILS

QUIET RAILS

VSS_SENSE_VDDQ

SENSE LINES

SENSE LINES

lines

lines

VDDQ[19]

VDDQ[20]

VDDQ[21]

VDDQ[22]

VDDQ[23]

VDDQ[24]

VDDQ[25]

VDDQ[26]

VCCDQ[1]

VCCDQ[2]

VDDQ_SENSE

VCCSA_SENSE

VCCSA_VID[0]

VCCSA_VID[1]

AR34

AR36

AR40

AV41

AW26

BA40

BB28

BG33

AM28

AN26

R107 *51_4_NCR107 *51_4_NC

BC43

R106 *51_4_NCR106 *51_4_NC

BA43

R71 100/F_4R71 100/F_4

U10

D48

D49

VCCSA_VID0

VCCSA_VID1

PS_S3CNTRL 11

Q14B

Q14B

2

DMN66D0LDW-7

DMN66D0LDW-7

1

+VDDR_REF_CPU

R58

R58

*1K_4_NC

*1K_4_NC

1 2

SMDDR_VREF_DQ0_M3_C

SMDDR_VREF_DQ1_M3_C

R52

R52

*1K_4_NC

*1K_4_NC

1 2

+VDDR_REF_CPU

CPU MCH

SNB: 5A

IVY: 5A

10uF x 6

C158

C93

C93

C134

C134

12

12

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

C132

C132

C145

C145

12

12

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

C120 1U/6.3V_4C120 1U/6.3V_4

1 2

12

12

1 2

VCCSA_SENSE

VCCSA_VID0

VCCSA_VID1

R113 1K_4R113 1K_ 4

R114 *1K_4_NCR11 4 *1K_4_NC

R115 1K_4R115 1K_ 4

+15V_ALW

12

R91

R91

100K_4

100K_4

PS_S3CNTRL_S

61

Take care Q3 Vgs(MAX)=2.5

Size Document Number Rev

Size Document Number Rev

Size Document Number Re

Date: Sheet of

Date: Sheet of

Date: Sheet of

C158

C157

C157

12

*10U/6.3V_6_NC

*10U/6.3V_6_NC

+1.5V_CPU

+1.5V_CPU

+VCCSA_CORE

VCCSA_SENSE 44

VCCSA_VID0 44

VCCSA_VID1 44

1 2

1 2

1 2

+1.5V_SUS +1.5V_CPU

5A

Q11

Q11

AON7410

AON7410

8

762

5

4

12

C144

C144

*4700P/25V_4_NC

*4700P/25V_4_NC

+VDDR_REF_CPU

+1.5V_CPU

R101

R101

1K/F_4

1K/F_4

1 2

R93

R93

1K/F_4

1K/F_4

1 2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Ivy Bridge 4/5

Ivy Bridge 4/5

Ivy Bridge 4/5

Monday, January 09, 2012

Monday, January 09, 2012

Monday, January 09, 2012

1

12

*10U/6.3V_6_NC

*10U/6.3V_6_NC

3

1

12

0.1U/16V_4

0.1U/16V_4

C156

C156

+1.5V_CPU

+1.05V_PCH

S3 Power reduce

V07

V07

V07

9 46

9 46

9 46

v

1A

1A

1A

5

WWW.MANUALS.CLAN.SU

4

3

2

1

Ivy Bridge Processor (GND) Ivy Bridge Processor (RESERVED, CFG)

U17H

U17H

A13

VSS[1]

A17

VSS[2]

A21

VSS[3]

A25

VSS[4]

A28

VSS[5]

D D

C C

B B

A A

A33

A37

A40

A45

A49

A53

AA1

AA13

AA50

AA51

AA52

AA53

AA55

AA56

AA8

AB16

AB18

AB21

AB48

AB61

AC10

AC14

AC46

AC6

AD17

AD20

AD4

AD61

AE13

AE8

AF1

AF17

AF21

AF47

AF48

AF50

AF51

AF52

AF53

AF55

AF56

AF58

AF59

AG10

AG14

AG18

AG47

AG52

AG61

AG7

AH4

AH58

AJ13

AJ16

AJ20

AJ22

AJ26

AJ30

AJ34

AJ38

AJ42

AJ45

AJ48

AJ7

AK1

AK52

AL10

AL13

AL17

AL21

AL25

AL28

AL33

AL36

AL40

AL43

AL47

AL61

AM13

AM20

AM22

AM26

AM30

AM34

VSS[6]

VSS[7]

VSS[8]

VSS[9]

VSS[10]

VSS[11]

A9

VSS[12]

VSS[13]

VSS[14]

VSS[15]

VSS[16]

VSS[17]

VSS[18]

VSS[19]

VSS[20]

VSS[21]

VSS[22]

VSS[23]

VSS[24]

VSS[25]

VSS[26]

VSS[27]

VSS[28]

VSS[29]

VSS[30]

VSS[31]

VSS[32]

VSS[33]

VSS[34]

VSS[35]

VSS[36]

VSS[37]

VSS[38]

VSS[39]

VSS[40]

VSS[41]

VSS[42]

VSS[43]

VSS[44]

VSS[45]

VSS[46]

VSS[47]

VSS[48]

VSS[49]

VSS[50]

VSS[51]

VSS[52]

VSS[53]

VSS[54]

VSS[55]

VSS[56]

VSS[57]

VSS[58]

VSS[59]

VSS[60]

VSS[61]

VSS[62]

VSS[63]

VSS[64]

VSS[65]

VSS[66]

VSS[67]

VSS[68]

VSS[69]

VSS[70]

VSS[71]

VSS[72]

VSS[73]

VSS[74]

VSS[75]

VSS[76]

VSS[77]

VSS[78]

VSS[79]

VSS[80]

VSS[81]

VSS[82]

VSS[83]

VSS[84]

VSS[85]

VSS[86]

VSS[87]

VSS[88]

VSS[89]

VSS[90]

VSS

VSS

VSS[91]

VSS[92]

VSS[93]

VSS[94]

VSS[95]

VSS[96]

VSS[97]

VSS[98]

VSS[99]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

VSS[163]

VSS[164]

VSS[165]

VSS[166]

VSS[167]

VSS[168]

VSS[169]

VSS[170]

VSS[171]

VSS[172]

VSS[173]

VSS[174]

VSS[175]

VSS[176]

VSS[177]

VSS[178]

VSS[179]

VSS[180]

AM38

AM4

AM42

AM45

AM48

AM58

AN1

AN21

AN25

AN28

AN33

AN36

AN40

AN43

AN47

AN50

AN54

AP10

AP51

AP55

AP7

AR13

AR17

AR21

AR41

AR48

AR61

AR7

AT14

AT19

AT36

AT4

AT45

AT52

AT58

AU1

AU11

AU28

AU32

AU51

AU7

AV17

AV21

AV22

AV34

AV40

AV48

AV55

AW13

AW43

AW61

AW7

AY14

AY19

AY30

AY36

AY4

AY41

AY45

AY49

AY55

AY58

AY9

BA1

BA11

BA17

BA21

BA26

BA32

BA48

BA51

BB53

BC13

BC5

BC57

BD12

BD16

BD19

BD23

BD27

BD32

BD36

BD40

BD44

BD48

BD52

BD56

BD8

BE5

BG13

U17I

U17I

BG17

BG21

BG24

BG28

BG37

BG41

BG45

BG49

BG53

BG9

C29

C35

C40

D10

D14

D18

D22

D26

D29

D35

D4

D40

D43

D46

D50

D54

D58

D6

E25

E29

E3

E35

E40

F13

F15

F19

F29

F35

F40

F55

G51

G6

G61

H10

H14

H17

H21

H4

H53

H58

J1

J49

J55

K11

K21

K51

K8

L16

L20

L22

L26

L30

L34

L38

L43

L48

L61

M11

M15

IC,IVB_2CBGA,0P7

IC,IVB_2CBGA,0P7

VSS[181]

VSS[182]

VSS[183]

VSS[184]

VSS[185]

VSS[186]

VSS[187]

VSS[188]

VSS[189]

VSS[190]

VSS[191]

VSS[192]

VSS[193]

VSS[194]

VSS[195]

VSS[196]

VSS[197]

VSS[198]

VSS[199]

VSS[200]

VSS[201]

VSS[202]

VSS[203]

VSS[204]

VSS[205]

VSS[206]

VSS[207]

VSS[208]

VSS[209]

VSS[210]

VSS[211]

VSS[212]

VSS[213]

VSS[214]

VSS[215]

VSS[216]

VSS[217]

VSS[218]

VSS[219]

VSS[220]

VSS[221]

VSS[222]

VSS[223]

VSS[224]

VSS[225]

VSS[226]

VSS[227]

VSS[228]

VSS[229]

VSS[230]

VSS[231]

VSS[232]

VSS[233]

VSS[234]

VSS[235]

VSS[236]

VSS[237]

VSS[238]

VSS[239]

VSS[240]

VSS[241]

VSS[242]

VSS[243]

VSS[244]

VSS[245]

VSS[246]

VSS[247]

VSS[248]

VSS[249]

VSS

VSS

VSS[250]

VSS[251]

VSS[252]

VSS[253]

VSS[254]

VSS[255]

VSS[256]

VSS[257]

VSS[258]

VSS[259]

VSS[260]

VSS[261]

VSS[262]

VSS[263]

VSS[264]

VSS[265]

VSS[266]

VSS[267]

VSS[268]

VSS[269]

VSS[270]

VSS[271]

VSS[272]

VSS[273]

VSS[274]

VSS[275]

VSS[276]

VSS[277]

VSS[278]

VSS[279]

VSS[280]

VSS[281]

VSS[282]

VSS[283]

VSS[284]

VSS[285]

VSS[286]

VSS[287]

VSS[288]

VSS[289]

VSS[290]

VSS[291]

VSS[292]

VSS[293]

VSS[294]

VSS[295]

VSS[296]

VSS[297]

VSS[298]

VSS[299]

VSS[300]

VSS_NCTF_1

VSS_NCTF_2

VSS_NCTF_3

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_8

VSS_NCTF_9

VSS_NCTF_10

VSS_NCTF_11

NCTF

NCTF

VSS_NCTF_12

VSS_NCTF_13

VSS_NCTF_14

M4

M58

M6

N1

N17

N21

N25

N28

N33

N36

N40

N43

N47

N48

N51

N52

N56

N61

P14

P16

P18

P21

P58

P59

P9

R17

R20

R4

R46

T1

T47

T50

T51

T52

T53

T55

T56

U13

U8

V20

V61

W13

W15

W18

W21

W46

W8

Y4

Y47

Y58

Y59

A5

A57

BC61

BD3

BD59

BE4

BE58

BG5

BG57

C3

C58

D59

E1

E61

TP29TP29

TP28TP28

TP25TP25

TP27TP27

TP30TP30

TP15TP15

TP14TP14

TP16TP16

TP17TP17

CFG2

U17E

U17E

B50

CFG[0]

C51

CFG[1]

B54

CFG[2]

D53

CFG[3]

A51

CFG[4]

C53

CFG[5]

C55

CFG[6]

H49

CFG[7]

A55

CFG[8]

H51

CFG[9]

K49

CFG[10]

K53

CFG[11]

F53

CFG[12]

G53

CFG[13]

L51

CFG[14]

F51

CFG[15]

D52

CFG[16]

L53

CFG[17]

H43

VCC_VAL_SENSE

K43

VSS_VAL_SENSE

H45

VAXG_VAL_SENSE

K45

VSSAXG_VAL_SENSE

F48

VCC_DIE_SENSE

G48

RSVD47

H48

RSVD6

K48

RSVD7

BA19

RSVD8

AV19

RSVD9

AT21

RSVD10

BB21

RSVD11

BB19

RSVD12

AY21

RSVD13

BA22

RSVD14

AY22

RSVD15

AU19

RSVD16

AU21

RSVD17

BD21

RSVD18

BD22

RSVD19

BD25

RSVD20

BD26

RSVD21

BG22

RSVD22

BE22

RSVD23

BG26

RSVD24

BE26

RSVD25

BF23

RSVD26

BE24

RSVD27

IC,IVB_2CBGA,0P7

IC,IVB_2CBGA,0P7

BCLK_ITP

BCLK_ITP#

RESERVED

RESERVED

DC_TEST_A4

DC_TEST_C4

DC_TEST_D3

DC_TEST_D1

DC_TEST_A58

DC_TEST_A59

DC_TEST_C59

DC_TEST_A61

DC_TEST_C61

DC_TEST_D61

DC_TEST_BD61

DC_TEST_BE61

DC_TEST_BE59

DC_TEST_BG61

DC_TEST_BG59

DC_TEST_BG58

DC_TEST_BG4

DC_TEST_BG3

DC_TEST_BE3

DC_TEST_BG1

DC_TEST_BE1

DC_TEST_BD1

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

N59

N58

N42

L42

L45

L47

M13

M14

U14

W14

P13

AT49

K24

AH2

AG13

AM14

AM15

N50

A4

C4

D3

D1

A58

A59

C59

A61

C61

D61

BD61

BE61

BE59

BG61

BG59

BG58

BG4

BG3

BE3

BG1

BE1

BD1

TP31TP31

TP19TP19

IC,IVB_2CBGA,0P7

IC,IVB_2CBGA,0P7

5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, January 09, 2012

Date: Sheet of

Monday, January 09, 2012

Date: Sheet of

4

3

2

Monday, January 09, 2012

PROJECT :

Ivy Bridge 5/5

Ivy Bridge 5/5

Ivy Bridge 5/5

1

V07

V07

V07

10 46

10 46

10 46

1A

1A

1A

1

WWW.MANUALS.CLAN.SU

M_A_A[15..0]8

A A

SO-DIMMA SPD Address is 0XA0

SO-DIMMA TS Address is 0X30

M_A_BS08

M_A_BS18

M_A_BS28

M_A_CS#08

M_A_CS#18

M_A_CLKP08

M_A_CLKN08

M_A_CLKP18

M_A_CLKN18

M_A_CKE08

M_A_CKE18

M_A_CAS#8

M_A_RAS#8

R323 10K_4R323 10K_4

1 2

R322 10K_4R322 10K_4

1 2

B B

C C

+1.5V_SUS

12

12

C107

C107

0.1U/16V_4

0.1U/16V_4

M_A_WE#8

WLAN_SCLK12,17,25,26

WLAN_SDATA12,17,25,26

M_A_ODT08

M_A_ODT18

M_A_DQSP[7..0]8

M_A_DQSN[7..0]8

Place these Caps near So-Dimm0.

C142

C142

12

C100

C100

0.1U/16V_4

0.1U/16V_4

+1.5V_SUS

12

C127

C127

0.1U/16V_4

0.1U/16V_4

0.1U/16V_4

0.1U/16V_4

EC14 47P/50V_4EC14 47P/50V_4

1 2

EC8 47P/50V_4EC8 47P/50V_4

1 2

EC13 47P/50V_4EC13 47P/50V_4

1 2

EC10 47P/50V_4EC10 47P/50V_4

1 2

EC16 47P/50V_4EC16 47P/50V_4

1 2

C57

C57

12

10U/6.3V_6

10U/6.3V_6

2

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_BS0

M_A_BS1

M_A_BS2

M_A_CS#0

M_A_CS#1

M_A_CLKP0

M_A_CLKN0

M_A_CLKP1

M_A_CLKN1

M_A_CKE0

M_A_CKE1

M_A_CAS#

M_A_RAS#

M_A_WE#

DIMM0_SA0

DIMM0_SA1

WLAN_SCLK

WLAN_SDATA

M_A_ODT0

M_A_ODT1

M_A_DQSP0

M_A_DQSP1

M_A_DQSP2

M_A_DQSP3

M_A_DQSP4

M_A_DQSP5

M_A_DQSP6

M_A_DQSP7

M_A_DQSN0

M_A_DQSN1

M_A_DQSN2

M_A_DQSN3

M_A_DQSN4

M_A_DQSN5

M_A_DQSN6

M_A_DQSN7

C128

C128

12

10U/6.3V_6

10U/6.3V_6

SMDDR_VREF_DQ0_M39

C159

C159

12

10U/6.3V_6

10U/6.3V_6

98

97

96

95

92

91

90

86

89

85

107

84

83

119

80

78

109

108

79

114

121

101

103

102

104

73

74

115

110

113

197

201

202

200

116

120

11

28

46

63

136

153

170

187

12

29

47

64

137

154

171

188

10

27

45

62

135

152

169

186

JDIM2A

JDIM2A

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC#

A13

A14

A15

BA0

BA1

BA2

S0#

S1#

CK0

CK0#

CK1

CK1#

CKE0

CKE1

CAS#

RAS#

WE#

SA0

SA1

SCL

SDA

ODT0

ODT1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

SODIMM(204P,H4.0,STD)

SODIMM(204P,H4.0,STD)

C137

C137

12

10U/6.3V_6

10U/6.3V_6

(204P)

(204P)

PC2100 DDR3 SDRAM SO-DIMM

PC2100 DDR3 SDRAM SO-DIMM

+0.75V_DDR_VTT

C208

C208

12

10U/6.3V_6

10U/6.3V_6

SMDDR_VREF_DQ0_M3

M3 VREF

3

12

M_A_DQ0

5

DQ0

M_A_DQ4

7

DQ1

M_A_DQ3

15

DQ2

M_A_DQ7

17

DQ3

M_A_DQ1

4

DQ4

M_A_DQ5

6

DQ5

M_A_DQ2

16

DQ6

M_A_DQ6

18

DQ7

M_A_DQ13

21

DQ8

M_A_DQ9

23

DQ9

M_A_DQ10

33

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

129

131

141

143

130

132

140

142

147

149

157

159

146

148

158

160

163

165

175

177

164

166

174

176

181

183

191

193

180

182

192

194

M_A_DQ14

M_A_DQ12

M_A_DQ8

M_A_DQ11

M_A_DQ15

M_A_DQ20

M_A_DQ21

M_A_DQ23

M_A_DQ19

M_A_DQ16

M_A_DQ17

M_A_DQ22

M_A_DQ18

M_A_DQ30

M_A_DQ28

M_A_DQ25

M_A_DQ27

M_A_DQ29

M_A_DQ24

M_A_DQ31

M_A_DQ26

M_A_DQ33

M_A_DQ36

M_A_DQ38

M_A_DQ34

M_A_DQ37

M_A_DQ32

M_A_DQ35

M_A_DQ39

M_A_DQ41

M_A_DQ40

M_A_DQ47

M_A_DQ42

M_A_DQ44

M_A_DQ45

M_A_DQ43

M_A_DQ46

M_A_DQ49

M_A_DQ53

M_A_DQ54

M_A_DQ50

M_A_DQ48

M_A_DQ52

M_A_DQ51

M_A_DQ55

M_A_DQ60

M_A_DQ56

M_A_DQ59

M_A_DQ63

M_A_DQ57

M_A_DQ61

M_A_DQ58

M_A_DQ62

4

M_A_DQ[63..0] 8

H=4mm,STD

S3 Power reduce

+0.75V_DDR_VTT

R151

R151

22_4

22_4

1 2

Q19

Q19

31

PS_S3CNTRL

2

2N7002W

2N7002W

5

PS_S3CNTRL 9

+3.3V_RUN

DDR3_DRAMRST#7,12

+SMDDR_VREF_DQ0

+SMDDR_VREF_DIMM0

6

+1.5V_SUS

+3.3V_RUN

12

C212

C212

0.1U/16V_4

0.1U/16V_4

R152 *10K_4_NCR152 *10K_4_NC

1 2

DDR3_DRAMRST#

7

JDIM2B

JDIM2B

75

VDD1

76

VDD2

81

VDD3

82

VDD4

87

VDD5

88

VDD6

93

VDD7

94

VDD8

99

VDD9

100

VDD10

105

VDD11

106

VDD12

111

VDD13

112

VDD14

117

VDD15

118

VDD16

123

VDD17

124

VDD18

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS1

3

VSS2

8

VSS3

9

VSS4

13

VSS5

14

VSS6

19

VSS7

20

VSS8

25

VSS9

26

VSS10

31

VSS11

32

VSS12

37

VSS13

38

VSS14

43

VSS15

SODIMM(204P,H4.0,STD)

SODIMM(204P,H4.0,STD)

PC2100 DDR3 SDRAM SO-DIMM

PC2100 DDR3 SDRAM SO-DIMM

(204P)

(204P)

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VTT1

VTT2

GND

205

8

12

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

203

204

GND

206

+0.75V_DDR_VTT

M1 VREF

12

C8

C8

47P/50V_4

47P/50V_4

+1.5V_SUS

1 2

1 2

R90

R90

1K/F_4

1K/F_4

R92

R92

1K/F_4

1K/F_4

+SMDDR_VREF_DIMM0

12

C168

C168

0.1U/16V_4

0.1U/16V_4

12

C164

C164

47P/50V_4

47P/50V_4

12

C214

C214

1U/6.3V_4

1U/6.3V_4

12

C211

C211

1U/6.3V_4

1U/6.3V_4

R14 *0_4_NCR14 *0_4_NC

12

C213

C213

47P/50V_4

47P/50V_4

1 2

12

C202

C202

47P/50V_4

47P/50V_4

+1.5V_SUS

1 2

12

+SMDDR_VREF_DQ0

R11

R11

1K/F_4

1K/F_4

R13

R13

1K/F_4

1K/F_4

12

0.1U/16V_4

0.1U/16V_4

C3

C3

D D

Place these Caps near So-Dimm0.

1

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, January 09, 2012

Date: Sheet of

Monday, January 09, 2012

Date: Sheet of

3

4

5

6

Monday, January 09, 2012

7

PROJECT :

DDR3 DIMM-0

DDR3 DIMM-0

DDR3 DIMM-0

V07

V07

V07

11 46

11 46

11 46

8

1A

1A

1A

1

WWW.MANUALS.CLAN.SU

2

3

4

5

6

7

8

12

C204

C204

1U/6.3V_4

1U/6.3V_4

M_B_DQ[63..0] 8

12

12

C210

C210

C215

C215

47P/50V_4

47P/50V_4

47P/50V_4

47P/50V_4

R15 *0_4_NCR15 *0_4_NC

1 2

H=4mm,STD

+3.3V_RUN

12

C201

C201

0.1U/16V_4

0.1U/16V_4

R153 *10K_4_NCR153 *10K_4_NC

+1.5V_SUS +SMDDR_VREF_DIMM1+1.5V_SUS +SMDDR_VREF_DQ1

R87

R87

1K/F_4

1K/F_4

1 2

R88

R88

1K/F_4

1K/F_4

1 2

1 2

1 2

R9

1K/F_4R91K/F_4

R10

R10

1K/F_4

1K/F_4

+3.3V_RUN

DDR3_DRAMRST#7,11

M1 VREF

C4

C4

12

0.1U/16V_4

0.1U/16V_4

+SMDDR_VREF_DQ1

+SMDDR_VREF_DIMM1

12

C1

C1

47P/50V_4

47P/50V_4

1 2

DDR3_DRAMRST#

C166

C166

12

0.1U/16V_4

0.1U/16V_4

+1.5V_SUS

12

C155

C155

47P/50V_4

47P/50V_4

JDIM1B

JDIM1B

75

VDD1

76

VDD2

81

VDD3

82

VDD4

87

VDD5

88

VDD6

93

VDD7

94

VDD8

99

VDD9

100

VDD10

105

VDD11

106

VDD12

111

VDD13

112

VDD14

117

VDD15

118

VDD16

123

VDD17

124

VDD18

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS1

3

VSS2

8

VSS3

9

VSS4

13

VSS5

14

VSS6

19

VSS7

20

VSS8

25

VSS9

26

VSS10

31

VSS11

32

VSS12

37

VSS13

38

VSS14

43

VSS15

SODIMM(204P,H4.0,STD)

SODIMM(204P,H4.0,STD)

PC2100 DDR3 SDRAM SO-DIMM

PC2100 DDR3 SDRAM SO-DIMM

(204P)

(204P)

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VTT1

VTT2

GND

205

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

203

204

GND

206

+0.75V_DDR_VTT

JDIM1A

C124

C124

12

10U/6.3V_6

10U/6.3V_6

98

97

96

95

92

91

90

86

89

85

107

84

83

119

80

78

109

108

79

114

121

101

103

102

104

73

74

115

110

113

197

201

202

200

116

120

11

28

46

63

136

153

170

187

12

29

47

64

137

154

171

188

10

27

45

62

135

152

169

186

JDIM1A

A0