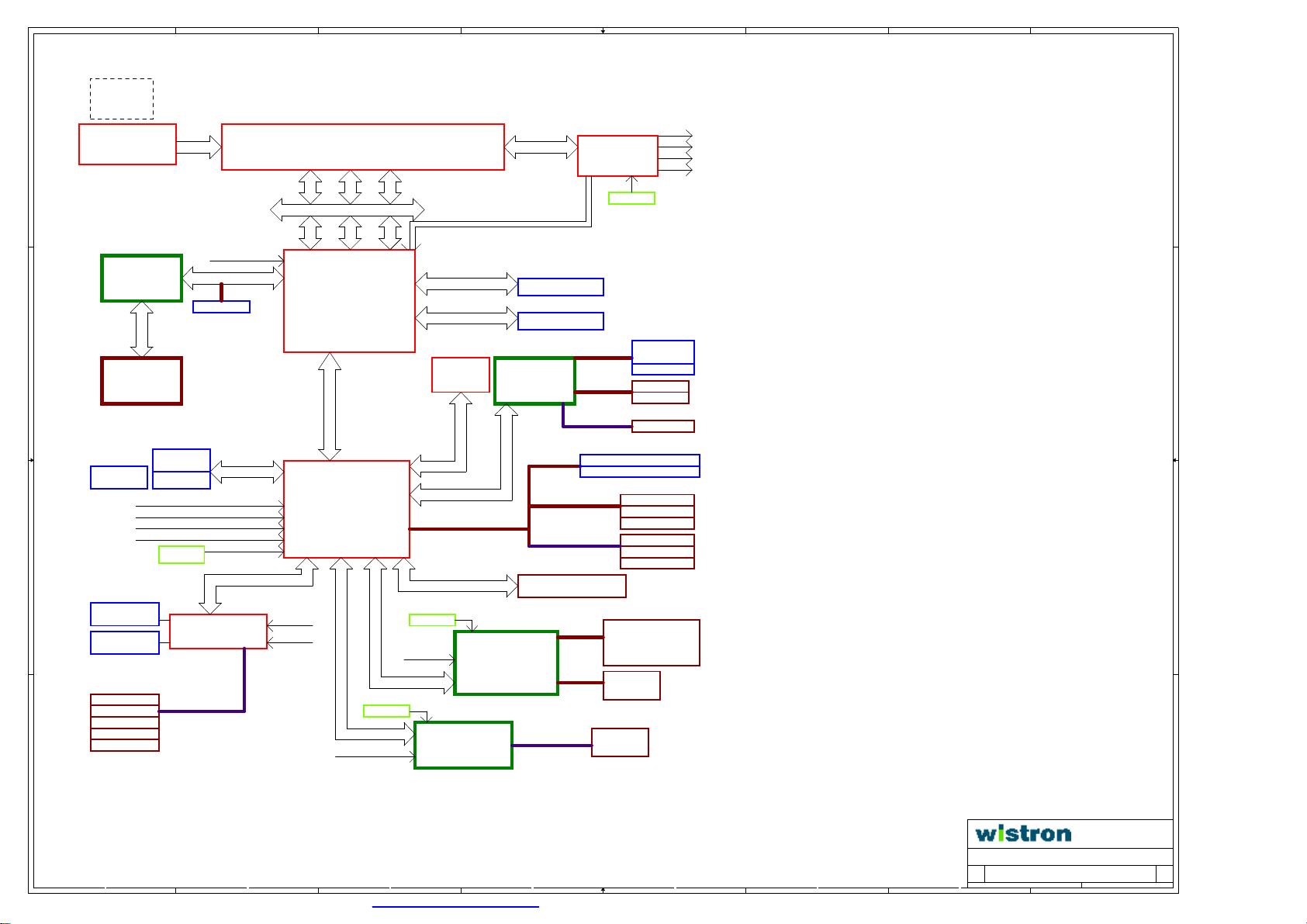

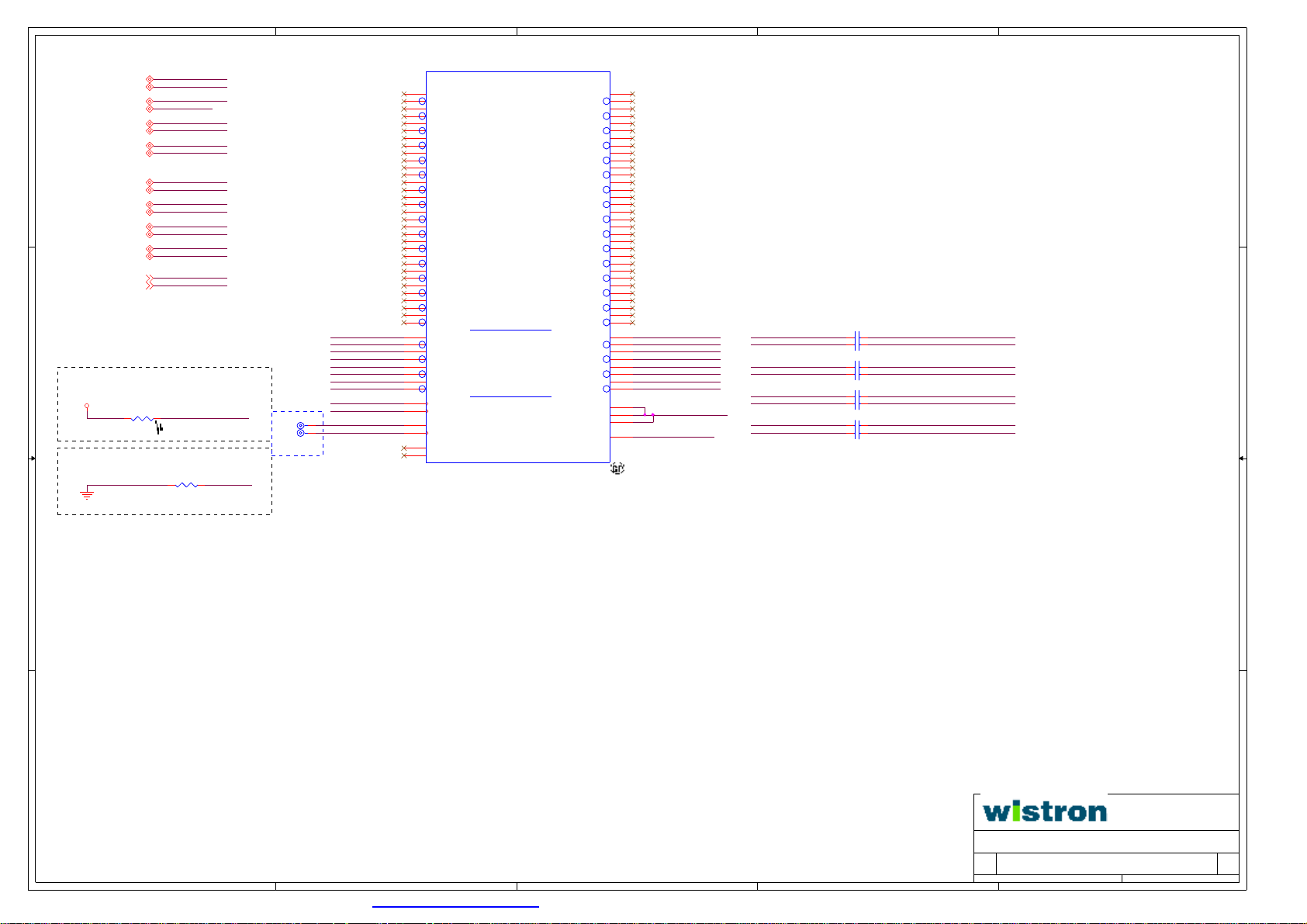

Dell Vostro 320 Schematics

8

Model: WestLake PCB Ver: A00

PCB: 08174 SCH Ver:01

PCBA: N867P (with 1394/card reader) Board ID[2:1]: 11

PCBA: W099P (w\o 1394/card reader) Board ID[2:1]: 10

4/30

D D

C C

B B

A A

VRM 11.1

ON-semi NCP5392

Realtek

RTD2270

LVDS

PANEL

17"/18.5"/19"

SATA 2

Port 2

CPU FAN1

SYSTEM FAN

COM1

LPT1

PS/2 KB

PS/2 MS

SYSTEM FAN

VGA CONN

SATA 1

Port 0

Port 1

100MHz/100MHz#

48MHz

33MHz

14.318MHz

32.768KHz

RTC

SIO

SMSC SCH5147

REAR RISER

7

6

LGA-775 PROCESSOR SOCKET

Conroe Core 2 Dual, Yorkfield Core 2 Quad processor, Wolfdale Dual Core

DATA

CTRL

CTRL

DATA

800MHz FSB

1066MHz FSB

1333MHz FSB

200MHz/200MHz#

266MHz/266MHz#

333MHz/333MHz#

Channel A

DOT/DOT#

96MHz/96MHz#

R,G,B

ADDR

ADDR

Intel

G41

Channel B

SPI Flash

SPI

HD Audio

USB BUS

INTERNAL

PCI-E X1

24.576MHz

100MHz /

100MHz#

Realtek

RTL8111DL

10/100/1000 LAN

SATA

LPC Bus

1254 pins

34mm x 34mm FC-BGA

DMI

Intel

ICH7

676 pins

31x31mm, 30 x 30 array

33MHz

14.318MHz

‧

PCI-E X1

25MHz

PCI-E X1

100MHz/100MHz#

5

200MHz/200MHz#

266MHz/266MHz#

333MHz/333MHz#

DDR2

Conexant

CX20582

Codec

MiniPCI Expree SLOT

VIA VT6325N

Controller of

IEEE1394 + Memory

card

REAR RISER

Clock CK-505

Realtek RTM875T-605

DIMM1

DIMM2

INTERNAL

SIDE

REAR

INTERNAL USB

Mini PCIE SLOT (PORT0)

WEB CAMERA(PORT1)

SIDE USB

REAR RISER

SIDE

SIDE

48MHz

33MHz

14.318MHz

100MHz/100MHz#

14.318MHz

SPK OUT

(2Watt)

Digi MIC

MIC IN

HP OUT

LINE OUT

USB 1(PORT5)

USB 2(PORT2)

USB 3(PORT3)

USB 4(PORT6)

USB 5(PORT7)

USB 0(PORT4)

4 IN 1 CONNECTOR

SD/MS/MMC/XD

IEEE1394

4pin type

RJ45

4

3

2

1

SHEET

Sheet 1

Sheet 2

Sheet 3

Sheet 4

Sheet 5

Sheet 6

Sheet 7

Sheet 8

Sheet 9

Sheet 10

Sheet 11

Sheet 12

Sheet 13

Sheet 14

Sheet 15

Sheet 16

Sheet 17

Sheet 18

Sheet 19

Sheet 20

Sheet 21

Sheet 22

Sheet 23

Sheet 24

Sheet 25

Sheet 26

Sheet 27

Sheet 28

Sheet 29

Sheet 30

Sheet 31

Sheet 32

Sheet 33

Sheet 34

Sheet 35

Sheet 36

Sheet 37

Sheet 38

Sheet 39

COVER PAGE

POWER MAP

CLOCK MAP

SEQUENCE MAP

GPIO/HOLE/EMI CAP

CLOCK GEN RTM875T

LGA-775 - FSB_VTT & Non-GTL

LGA-775 - Host Bus

LGA-775 - VCORE & GND

EAGLELAKE-G Host Bus

EAGLELAKE-G DMI & PCI-E 16X

EAGLELAKE-G DDR Channel A&B

EAGLELAKE-VGA

EAGLELAKE-G POWER & PLL

EAGLELAKE-G GND

GTL VREF SEL

DDR2 DIMM

DDR2 Terms & Decaps

VGA CONNECTOR

LVDS RTD22x0

PRT and SMBUS ISP

ICH7 DMI&PCIE&PCI&USB

ICH7 HOST/SATA/MSIC/LPC/AUD

ICH7 POWER & GND

SATA CONN

USB CONN

AUDIO CX20582-10Z

VT6325 1394/CARD READER

Gb LAN RTL8111DL

Mini PCIE SLOT

SPI & FAN & BUZZER & LED

SUPER I/O SMSC5147

REAR IO RISER

DC19V & SYS_EN CIRCUIT

VCC5SB / VCC3_3SB

VCC_12 & VCC5 & VCC3_3

VCC_1.8_DIMM / VCC_1.1_CORE

VRD 11.1

TEST COUPON

BOM Cofiguration

(R): Unmount

(E): EUP circuit

(F): card reader and 1394

(X): remove after MP

(N): For without 1394 and carder sku

8

7

6

PDF created with pdfFactory trial version www.pdffactory.com

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

COVER PAGE

COVER PAGE

COVER PAGE

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

EAGLELAKE

C

EAGLELAKE

C

EAGLELAKE

C

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

2

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

1 39Monday, May 25, 2009

1 39Monday, May 25, 2009

1 39Monday, May 25, 2009

1

A00

A00

A00

5

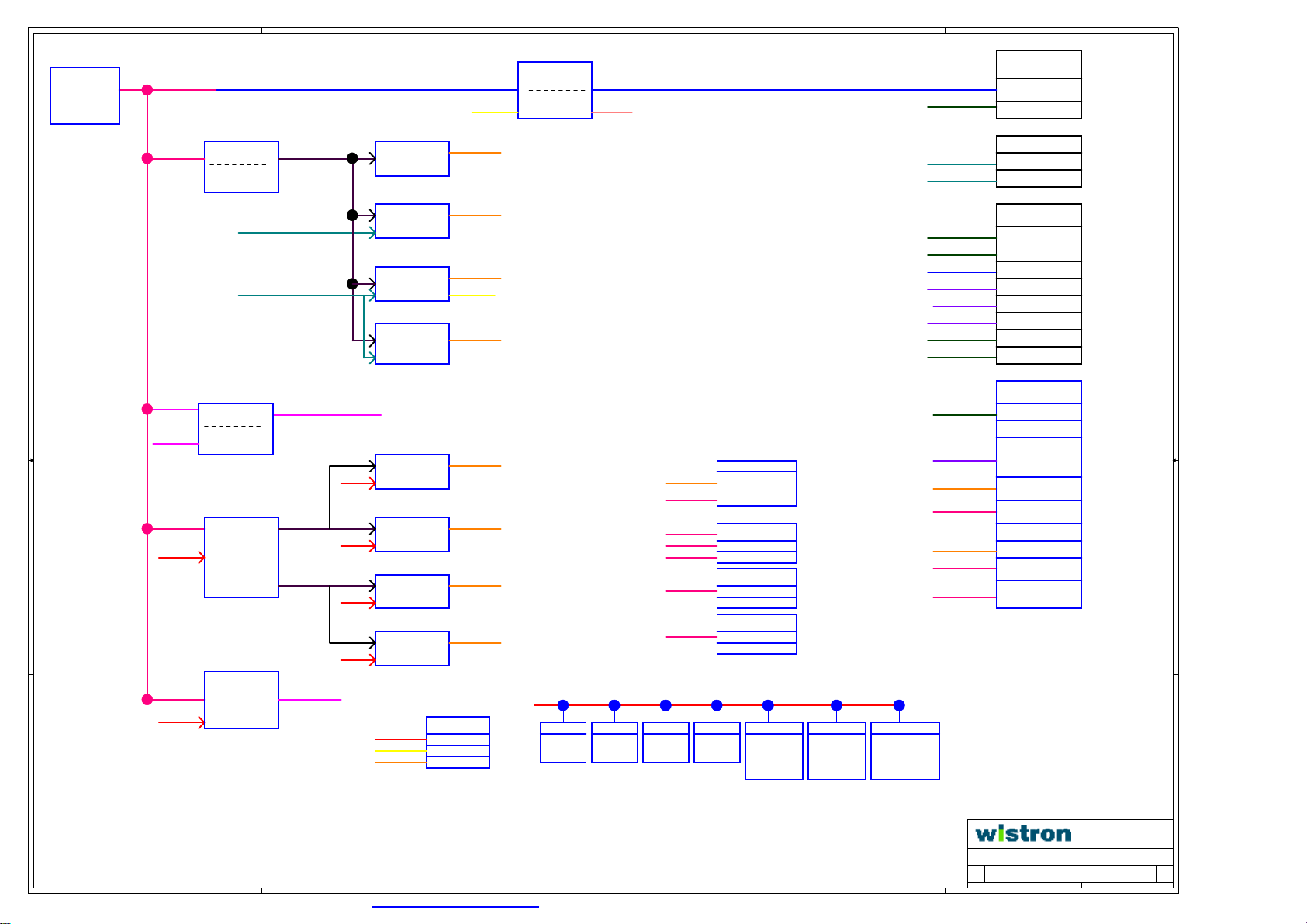

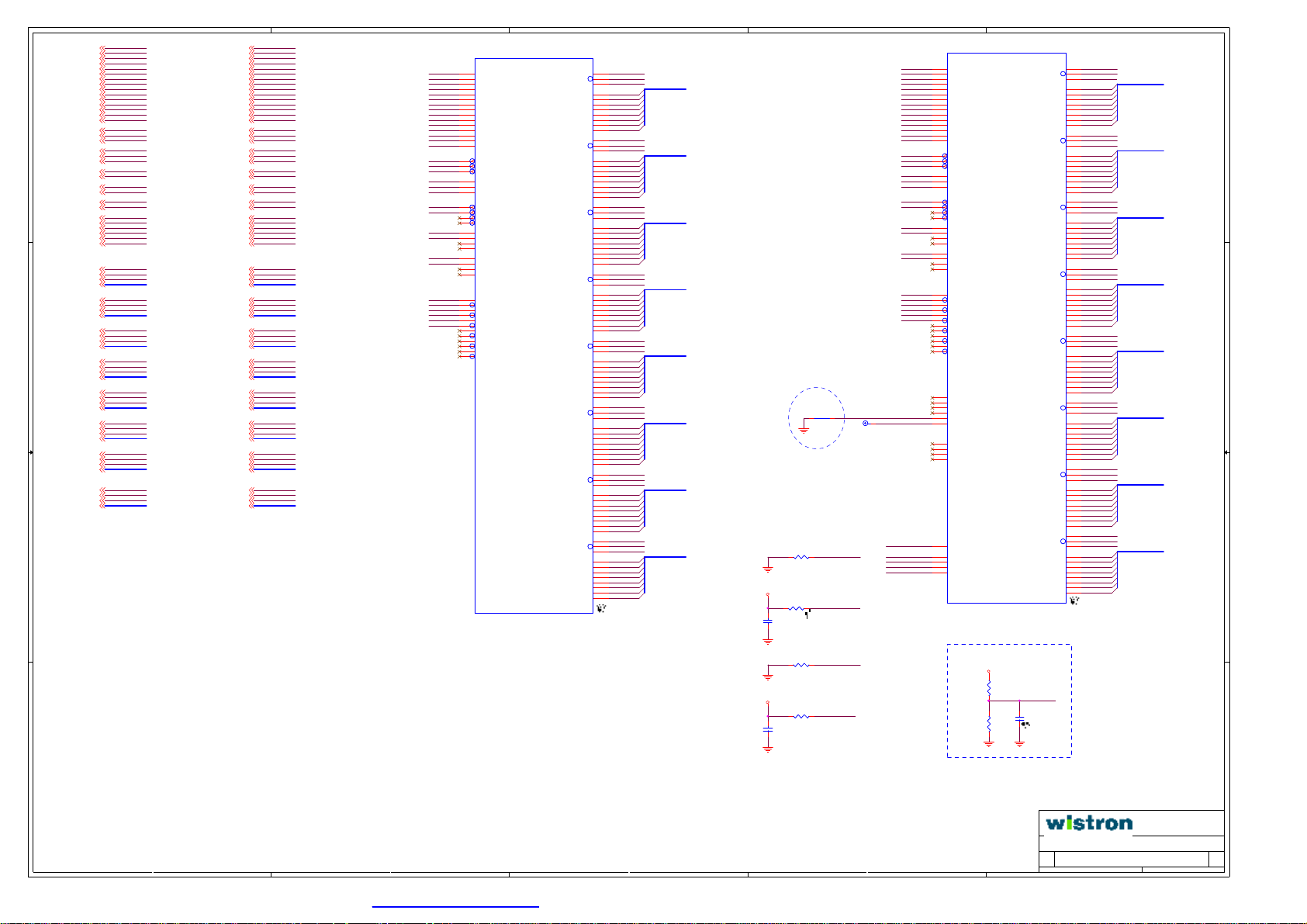

Westlake Power Map

POWER

ADAPTER

120W,

19V/ 6.3A

D D

C C

DC_19_IN

+1.8V(S3, S0) / 12A

APW7138

DC_19_IN V_1P8_MEM

P0803BDG NMOS

TO-252 8.3mohm

P0803BDG NMOS

TO-252 8.3mohm

3.3V

CORE_EN

+1.1V(S0) / 25A

APW7138

DC_19_IN

CORE_EN

P0803BDG NMOS

TO-252 8.3mohm

P0803BDG NMOS

TO-252 8.3mohm

V_1P1_CORE

+5VSB(S0,S3,S4,S5)/6A

VCC5SB

TPS51125

SYS_EN

B B

EN1

VO1

VO2

+3.3VSB(S0,S3,S4,S5)/5A

+12V(S0)/ 3A

DC_19_IN

SLP_S3*

A A

NCP1589

EN

1/3

VCC12

VO

SLP_S4

SLP_S3

SLP_S3

LAN_EN

4

+0.9V

APL5331KAC-TRL

LDO SO-8 3A

EN

+1.5V

APL5912-KAC

LDO SO-8 3A

EN

+1.2V

APL5912-KAC

LDO SO-8 5A

EN

+1.05V

APL5913-KAC

LDO SO-8 3A

EN

5V_USB

AO4468

NMOS SO-8

14mohm 9.2A

EN

+5V

AO4468

NMOS SO-8

14mohm 9.2A

EN

+3.3V

AO4468

NMOS SO-8

14mohm 9.2A

EN

APM2300AA

NMOS SOT23

25mohm 6A

EN

VCC12 VCC12

VCC5

VCC3_3

PG

SATAPWR1

VCC5

VCC3_3

VRM_EN

MEM_VTT

V_1P5_ICH

V_1P1_FSB

VRM_EN

V_ICH_CORE

VCC5_USB

VCC5DC_19_IN

VCC3_3VCC3_3SB

V_3P3_LAN

VRD11.1 / 60A

NCP5392

TO-252 9mohm

TO-252 6mohm

EN

(S0, S3)

(S0)

(S0)

(S0)

(S0, S3)

(S0)

(S0)

(S0, S3,S4)

VCC5_USB

USB X1 SIDE

VCC5_USB

0.5A

PG

3

(S0)

V_CORE_CPU

VRMPWRGD

USB X1 SIDE

VCC5_USB

0.5A

VCC3_3

VCC3_3SB

VCC5

VCC3_3SB

VCC3_3

V_3P3_LAN

VCC3_3

USB X1 SIDE

VCC5_USB

0.5A

+3.3VDUAL 10mA

VCC3_3AUX

VCC3_3

VCC3_3LAN

V_1P2_LAN

VCORE_1394

V_1P2

USB X1 SIDE

VCC5_USB

0.5A

SUPER I/O

CX20582

internal

RTL8111DL

internal

VT6325N

internal

USB X2 REAR

VCC_USB VCC5_USB

1.0A

2

USB X1 MPCIE

0.5A

USB X1 CAMERA

VCC5_USB

0.5A

VCORE

V_1P1_FSB

V_1P8_MEM

MEM_VTT

V_1P1_CORE

V_1P1_CORE

VCC3_3

V_1P5_ICH

V_1P8_MEM

V_1P5_ICH

V_1P1_FSB

V_1P1_CORE

V_ICH_CORE

V_1P5_ICH

VCC3_3

VCC3_3SB

VBAT

VCC5

VCC5SB

V_1P1_FSB

1

CPU (Core 2 Dual ,

Yorkfield)

VCORE 60A

VTT (1.1V) 4.6A

DDR2 DIMM

1.8V

VDD/VDDQ (S0, S3) 9.4A

0.9V

VTT(S0,S3) 1.2A

NB G41

1.1V

Core 18.8A

1.1V

DMI & PCIe 2.5A

3.3V

Misc 3.3V 70mA

1.5V

Misc 1.5V 15.8mA

1.8V

VCC_SM 1.87A

1.5V

VCC_SMCLK 250mA

1.1V

VTT 1.3A

1.1V

VC_CL 3.8A

SB ICH7

Vcc1_05 0.86 A

VccSus1_05

Vcc1_5_A/Vcc1_5B

VccUSBPLL\VccDMIPLL

VccSATAPLL 1 .89A

Vcc3_3 0.33A

VccSus3_3 52mA

VCCRTC

V5REF 6mA

V5REF_Sus 10mA

V_CPU_IO 14mA

5

4

PDF created with pdfFactory trial version www.pdffactory.com

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

POWER MAP

POWER MAP

POWER MAP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

EAGLELAKE

C

EAGLELAKE

C

EAGLELAKE

C

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

2 39Monday, May 25, 2009

2 39Monday, May 25, 2009

2 39Monday, May 25, 2009

A00

A00

A00

5

4

3

2

1

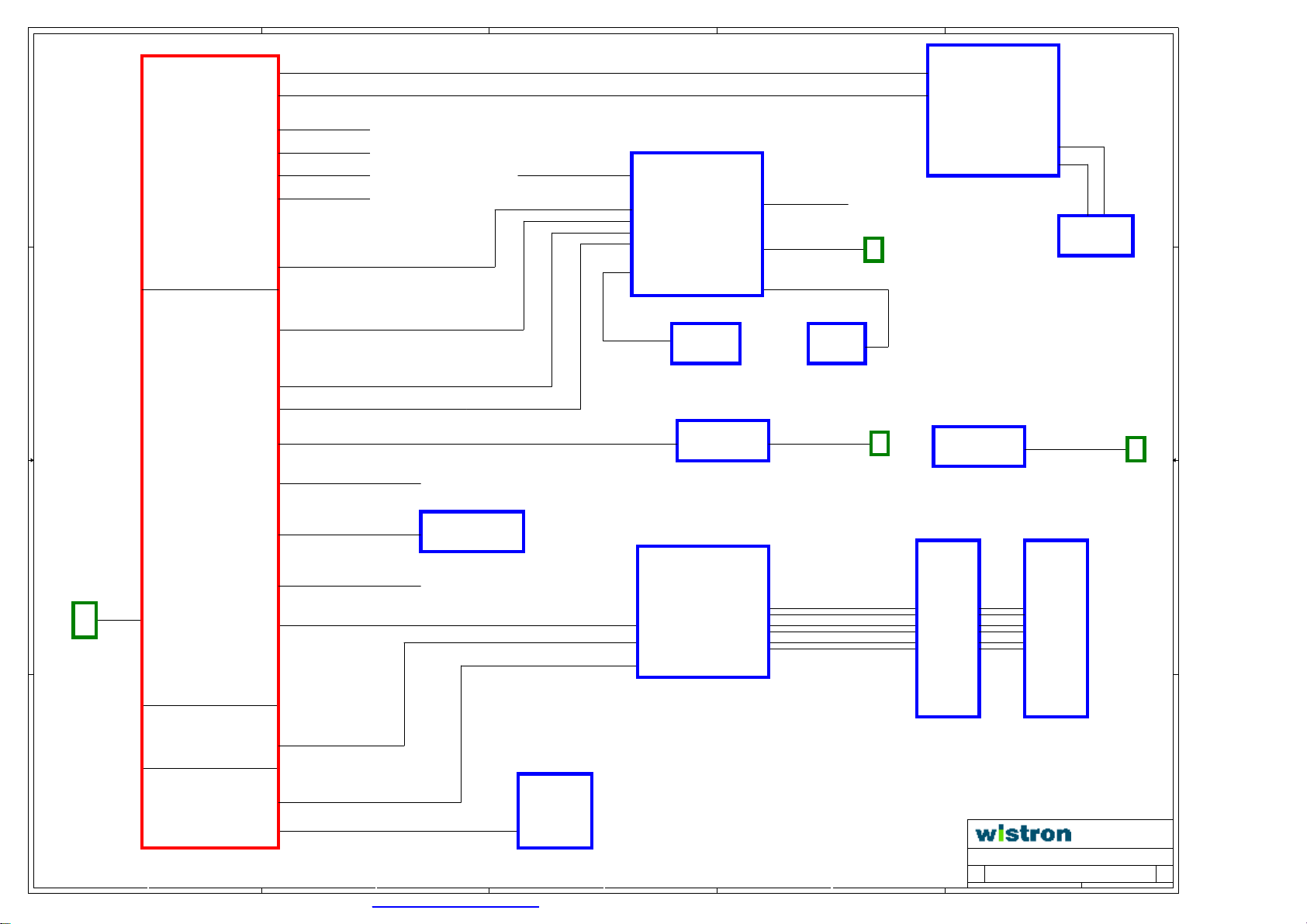

14.318 MHZ

33 MHZ

CLOCKI

PCICLK

SIO

33 MHZ

D D

C C

RTM875T

33 MHZ

33 MHZ

33 MHZ

33 MHZ

48 MHZ

100 MHZ

DBP

14.318 MHZ

24MHZ

CLK14

PCICLK

USBCLK

DMICLK

SATACLK

SUSCLK

HDA_BITCLK

SPI_CLK

CODEC

ICH

32.7 kHZ

32.768 kHZ

RTC

17.86/31.25 MHZ

KBCLK

MSCLK

MS/KB

SPI

100 MHZ

SRC CLOCK

100 MHZ

100 MHZ

LAN

25MHZ

VT6325

24.576MHZ

PAIRS

100 MHZ

B B

100 MHZ

100 MHZ

Mini Card

GCLKIN

MCH

DIMM

(DDR2)

DIMM

(DDR2)

REFCLKIN

14.318 MHZ

SRC CLOCK PAIR

A A

HOST CLOCK

PAIRS

5

96 MHZ

200/266/333MHz

200/266/333MHz

4

CPU

BCLK

HOST

CHANNEL A

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

CLOCK MAP

CLOCK MAP

CLOCK MAP

EAGLELAKE

EAGLELAKE

EAGLELAKE

CHANNEL B

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

3 39Monday, May 25, 2009

3 39Monday, May 25, 2009

3 39Monday, May 25, 2009

A00

A00

A00

PDF created with pdfFactory trial version www.pdffactory.com

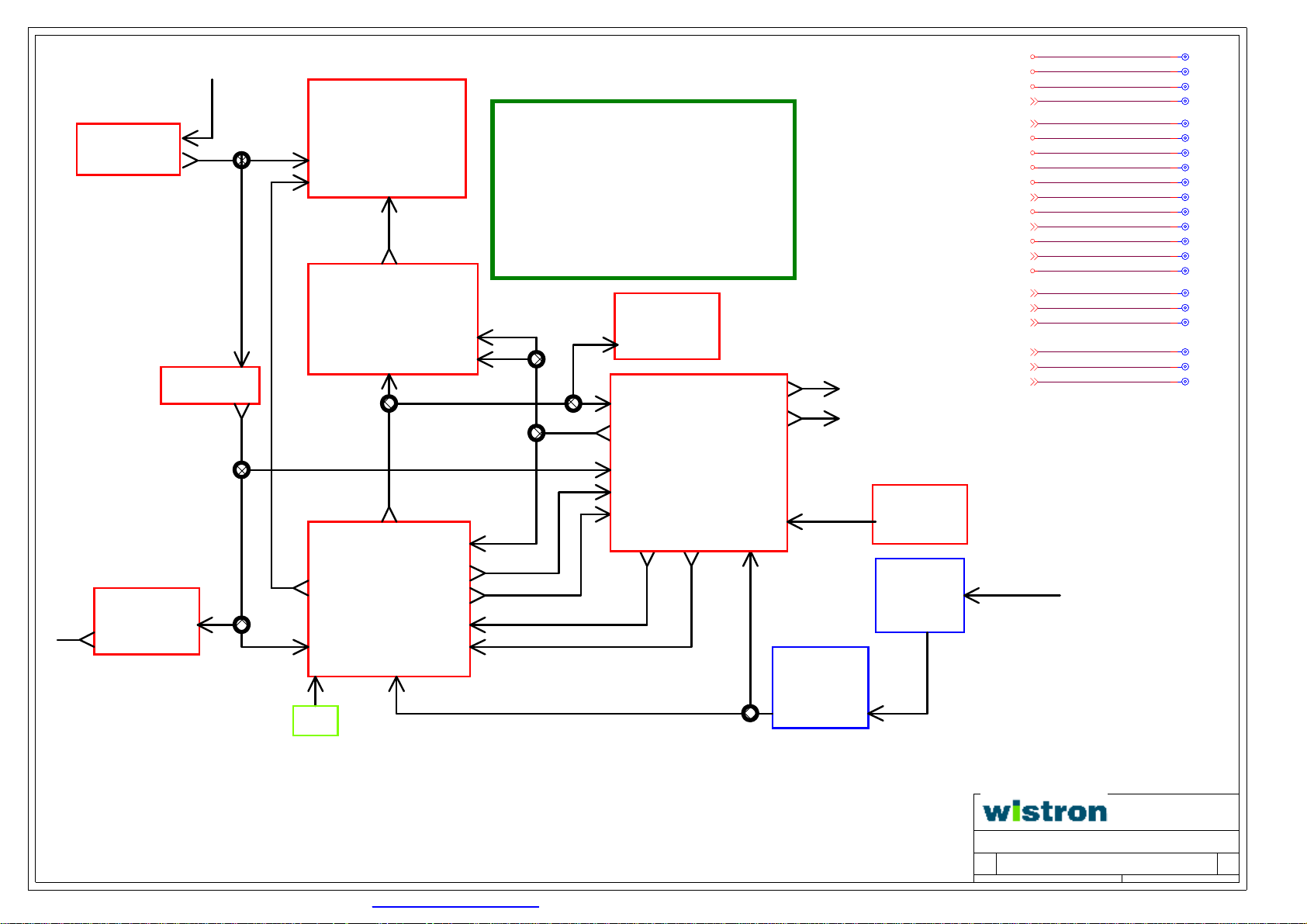

1

FSB_VTT_EN

During step 2~ 4:

Power sequence:

2. SLP_S4

2-A. SLP_S4 ---> MEM1.8V

3. SLP_S3

3-A. SLP_S3 ---> 12V, 5V, 3.3V

VRM

NCP5392

VRM_EN

VRM

Ready

4

5-A

LGA-775

PROCESSOR

SOCKET

VTTPWRWRGD

PWRGOOD

RESET#

3-B. 3.3V---> ICH 1.5V ---> FSB_VTT

---> ICH 1.05V

---> NB_CORE 1.1V

10

HCPURST

Intel

G41

RSTIN

Level shift

5-B

1 1

PLTRST

8

6-A

CLKs

CLOCKGEN

CK_PWRGD

RTM875T

CPUPWRGD

6

CK_PWRGD

VRMPWRGD

+RTVCC

0-A

RTC

Battery

Intel

ICH7

+3.3VSB

CL_PWRGD

PWROK

9

PWROK

SLP_S3*

SLP_S5*

PWR_BTN#

SB_RSMRST#

4. FSB_VTT ---> VRM

7

3

2

Realtek

RTL8111DL

PERST

PCIRST

PWRGD_3V

PWRG_PS

SLP_S3*

SLP_S5*

PB_OUT#

1-B

Super I/O

SMSC5147

SB_RSMRST#

0-E

0-D

+3.3VSB

PCIRST_OUT1

PCIRST_OUT2

PCIRST_OUT4

PB_IN#

+3.3VSB

9-A

1-A

TPS51125

+5VSB

+3.3VSB

VOUT VIN

PCI-E

IEEE 1394

Power

Button

POWER

ADAPTER

120W,

19V/ 6.3A

0-C

DC_19_IN

DC_19_IN

VCC3_3SB

RSMRST*23,32

PWRBTN*23,32

V_1P8_MEM

SLP_S3*23,32,36,37,38

V_1P1_CORE

PW_V1D1_PG37

V_1P1_FSB

VRM_EN37,38

VRMPWRGD7,32,38

SIO_PSPWRGD32

PWRGD_3V13,23,32

CPUPWRGD7,23

PLTRST*_NB13,23

CPURST*7,8,10,32

0-B

VCC5SB

VCC12

VCC5

VCC3_3

VCORE

ADP_IN

DC_19_IN

VCC5SB

VCC3_3SB

RSMRST*

PWRBTN*

VCC12

VCC5

VCC3_3

V_1P8_MEM

SLP_S3*

V_1P1_CORE

PW_V1D1_PG

V_1P1_FSB

VRM_EN

VCORE

VRMPWRGD

SIO_PSPWRGD

PWRGD_3V

CPUPWRGD

PLTRST*_NB

CPURST*

TP5 TPAD28TP5 TPAD28

TP18 TPAD28TP18 TPAD28

TP24 TPAD28TP24 TPAD28

TP61 TPAD28TP61 TPAD28

TP63 TPAD28TP63 TPAD28

TP21 TPAD28TP21 TPAD28

TP4 TPAD28TP4 TPAD28

TP25 TPAD28TP25 TPAD28

TP16 TPAD28TP16 TPAD28

TP10 TPAD28TP10 TPAD28

TP17 TPAD28TP17 TPAD28

TP15 TPAD28TP15 TPAD28

TP11 TPAD28TP11 TPAD28

TP2 TPAD28TP2 TPAD28

TP33 TPAD28TP33 TPAD28

TP3 TPAD28TP3 TPAD28

TP62 TPAD28TP62 TPAD28

TP14 TPAD28TP14 TPAD28

TP6 TPAD28TP6 TPAD28

TP13 TPAD28TP13 TPAD28

TP29 TPAD28TP29 TPAD28

PDF created with pdfFactory trial version www.pdffactory.com

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

SEQUENCE MAP

SEQUENCE MAP

SEQUENCE MAP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

EAGLELAKE

A3

EAGLELAKE

A3

EAGLELAKE

A3

Date: Sheet of

Date: Sheet of

1

Date: Sheet of

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

4 39Monday, May 25, 2009

4 39Monday, May 25, 2009

4 39Monday, May 25, 2009

A00

A00

A00

8

ICH 7

PIN

NAME

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

D D

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO13

GPIO14

GPIO15 E22

GPIO16

GPIO17

GPIO19

GPIO20

GPIO21

GPIO22

GPIO23

GPIO24

GPIO25

C C

GPIO26

GPIO27

GPIO28

GPIO29

GPIO30

GPIO31

GPIO32

GPIO33

GPIO35

GPIO36

GPIO37

GPIO39

GPIO48

GPIO49

B B

A A

POWER

PIN#

AB18

C8

G8

F7

F8

G7

AC21

AC18

E21

E20

A20

B23

F19GPIO12

E19

R4

AC22

D8

AH18

AF21

AF19

A13

AA5

R3

D20

A21

B21

E23

C3

A2

B3

AG18

AC19

AD21

AH19

AE19

AD20

AE20

A14

AG24

USAGE

WELL

ICH_BM_BUSY

MAIN

MAIN

P_REQ_N5

MAIN

PIRQJE

MAIN PIRQJF

PIRQJG

MAIN

PIRQJH

MAIN

MAIN -----GPI

W_DETECT_N

CB_DET_N

MAIN -----GPI

PANEL_DET

RESUME

IO_SMI* -----

LPC_PME*

RESUME

RESUME

non-use

RESUME

non-use

RESUME

AUD_EXPMUTE* ----- -----

RESUME

non-use

MAIN

AUD_SPKMUTE*

MAIN

P_GNT_N5

W_DISABLE* ----- High

MAIN

INV_DET*

MAIN

non-use

MAIN

LVDS_DET*

P_REQ_N4

MAIN

MAIN

non-use ----------

RESUME

LAN_EN

RESUME

RESUME

non-use

RESUME

SUSLED*

RESUME

PWRLED*

RESUME

OC*5

RESUME

OC*67

RESUME

OC*67

MAIN

non-use

MAIN

non-use

non-use

MAIN

CAMERA_EN

MAIN

BOARD_ID_1

MAIN

BOARD_ID_2

MAIN -----GPIGPIO38

RISER1_DET

RISER2_DET

MAIN

P_GNT_N4

CPU

CPUPWRGD

8

VCC3_3SB

EMI

12

EC8

EC8

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

VCC3_3 VCC3_3

12

EC7

EC7

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

VCC3_3 VCC3_3

12

EC13

EC13

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

VCC5_USB

12

EC15

EC15

VCC5

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

7

DURING

Default

RESET

Type

GPI

GPI

GPI

GPI

GPI

GPI

GPI

Native

GPI

GPI

GPI

GPI

GPO

GPO

GPOMAINA20GPIO18

GPI

GPO

GPI -----

Native

Native

GPO

GPO

GPO

GPO

GPO

Native

Native

Native

GPO

GPO

GPOMAINU2GPIO34

GPO

GPI

GPI

Native

Native

VCC3_3SB

12

EC12

EC12

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

EC9

EC9

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

EC14

EC14

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

VCC3_3

VCC5

7

Default

Setting

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

----------GPInon-useRESUME

----------GPIRESUME

IN

-----

----------

----------

---------High

-----

-----

-----

-----

-----

-----

-----

-----

-----

-----

Out

Low For LAN power enable (Default :Low enable)

-----

LowDMI_MODE

-----

-----

Out

-----

Out

-----

-----

-----

----------

----------

-----

-----

-----

-----

-----

High

-----

High

-----

-----

-----

-----

-----

-----GPI -----MAIN

-----

-----

-----

-----

12

EC16

EC16

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

NOTES

For wireless LAN card detected (L: existed)

For PWR BT&LED cable detected (L: existed)

For ICH7 inform scalar chip function

For SIO_SMI* function(low Active)

For SIO LPC_PME* function(low Active)IN

For AUDIO output Mute function (default : High)

I P/D 20K;For Speaker Mute function (default : High)

INTEGRATED P/U 20K

For wireless LAN disable(default : High enable)

For Inverter cable detected (L: existed)

For LVDS cable detected (L: existed)

Multiplexed with LDRQ1#

DMI use AC mode

For Suspend LED function

For PWR LED function

For Webcam enable function (default : High enable)

Multiplexed with SATA2GP

Multiplexed with SATA3GP

For Rear IO cable1 detected (L: existed)

For Rear IO cable2 detected (L: existed)

6

(87.00A52.220)

(87.00A52.220)

(R87.00A52.220)

(R87.00A52.220)

H8

H8

H7

H7

HOLE

HOLE

HOLE

HOLE

1

1

Mini PCIE holder

NB heatsink

60.3AG10.001

2D label

xx-xxxxxx-xxxxxxxx-xxxx-X01

Made in xxxxx

DP/N XXXXXX

40.3V302.001

6

5/20

5

SCH 5147

GP10

PLTRST*_1394

GP11

PLTRST*_RISER

GP12

PLTRST*_LAN

PLTRST*_DBP

GP14

non-use

GP15

GP16

PROCHOT*_L

SYS_FAN2_CTRL_SIO

GP17

GP20

ICH_BM_BUSY

GP21

KBDATA

GP22

KBCLK

IO_SMI*

GP27

GP32

MSDATA

GP33

MSCLK

GP36

KBRST*

GP37

A20GATE

non-use

GP40

GP41

non-use

GP42

LPC_PME*

GP43

AUTO_COLOR_SIO

Panel_FB

GP50

GP51

SMBUS_ISP

CPU_GTLREF_CTRL_1

GP52

CPU_GTLREF_CTRL_2

GP53

GP54

PRT_ISP

PANEL_SEL1

GP55

PANEL_SEL2

GP56

PANEL_SEL3

GP57

GP60

PECI_READY1

GP61

PECI_SIO_R

CN2

1

2

2

7

2

7

DVD-CON2-10-GP

DVD-CON2-10-GP

(R)

(R)

H1

H1

H2

H2

HOLE

HOLE

HOLE

HOLE

1

H10

H10

(R)

(R)

1

8

GEN315R140-8-F-A

GEN315R140-8-F-A

H3

H3

(R)

(R)

1

8

GEN315R140-8-F-A

GEN315R140-8-F-A

5

CN2

1

2

(R)

(R)

(R)

(R)

H5

H5

HOLE

HOLE

1

4

5

4

5

CN1

CN1

DVD-CON2-10-GP

DVD-CON2-10-GP

21.60695.102

21.60564.102

(R)

(R)

H4

H4

HOLE

HOLE

1

CPU Heatsink screw hole.

3

4

5

6

3

4

5

6

BIOS Post ValueGPIO # Usage

Native(nPCIRST_OUT3)

Native(nPCIRST_OUT1)

Native(nPCIRST_OUT2)

Native(nPCIRST_OUT4)

non-use

PROCHOT*

(Processor Hot Function)

Default High.Over 85 degree,

Enable PROCHOT Function

PWM3

Natice(PECI Request)

Native(KBDATA)

Native(KBCLK)

Native (IO_SMI*)

Native(MSDATA)

Native(MSCLK)

Native(KBRST*)

Native(A20GATE)

non-use

non-use

Native(nIO_PME)

AUTO_COLOR_SIO( Default: High)

Panel_FB

H:ISP ,L:disable(default)

GPO (Default: Low)

GPO(Default: High)

L:ISP ,H:disable(default)

PANEL type select

PANEL type select

PANEL type select

Native(PECI Ready)

Native(PECI IO)

1

H6

H6

2

3

(R)

(R)

1

8

GEN315R140-8-F-A

GEN315R140-8-F-A

6

7

H9

H9

2

3

(R)

(R)

1

8

GEN315R140-8-F-A

GEN315R140-8-F-A

6

7

4

3/11

3/11

HLDR-SUPPORT * 4

4

IN-POWER

N/A

O

N/A

O

N/A

O

N/A

O

N/A

N/A AUX (VTR)

OD

O

AUX (VTR)

I

AUX (VTR)

O

AUX (VTR)

O

AUX (VTR)

O

AUX (VTR)

O

AUX (VTR)

O

AUX (VTR)

O

AUX (VTR)

O

AUX (VTR)

AUX (VTR)

O

AUX (VTR)

O

AUX (VTR)

O

AUX (VTR)

I

AUX (VTR)

OD

AUX (VTR)AUX (VTR)

O

AUX (VTR)

O

AUX (VTR)

OD

AUX (VTR)

OD

AUX (VTR)

OD

AUX (VTR)AUX (VTR)

OD

AUX (VTR)

I

AUX (VTR)

I

42.3AG23.001

OUT-POWERI/O

AUX (VTR)

AUX (VTR)

AUX (VTR)

AUX (VTR)

MAIN (VCC)

AUX (VTR)N/A

MAIN (VCC)

MAIN (VCC)

MAIN (VCC)

AUX (VTR)

MAIN (VCC)

MAIN (VCC)

MAIN (VCC)

MAIN (VCC)

AUX (VTR)

AUX (VTR)

AUX (VTR)

MAIN (VCC)

AUX (VTR)

AUX (VTR)

AUX (VTR)

AUX (VTR)

AUX (VTR)

AUX (VTR)

AUX (VTR)

AUX (VTR)

ICH7

SMSC5147

SMBDATA

SMBCLK

SDA

SCLK

SDA1

SCLK1

5/25

3

ALERT_DATA

ALERT_CLK

ALERT_DATA

ALERT_CLK

SMBDATA

SMBCLK

3

SMBUS MAP

VCC3_3SB

4.7K 4.7K

4.7K

4.7K

VCC3_3

2

DIMM1 DIMM2

Address:

Address:

000

010

A0 A2

XDP connector

RTM875T-605

Mini card

0ohm : optional

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

GPIO/HOLE/EMI CAP

GPIO/HOLE/EMI CAP

GPIO/HOLE/EMI CAP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

EAGLELAKE

A2

EAGLELAKE

A2

EAGLELAKE

A2

Date: Sheet of

Date: Sheet of

Date: Sheet of

2

1

Address:

D2 :WRITE

D3 :READ

Address:

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

5 39Monday, May 25, 2009

5 39Monday, May 25, 2009

5 39Monday, May 25, 2009

1

A00

A00

A00

PDF created with pdfFactory trial version www.pdffactory.com

5

BSEL0

BSEL07

BSEL1

BSEL17

BSEL2

BSEL27

SMBCLK7,17,21,30,32

GMCH_BSEL0

GMCH_BSEL1

GMCH_BSEL2

CLK48_USB

CLK33_SL1_R_1

CLK33_SIO_R_1

CLK33_ICH_R_1

CLK14_ICH

CLK14_SIO

SMBDATA

SMBCLK

CLK96_DOT

CLK96_DOT*

CLKSRC_GMCH

CLKSRC_GMCH*

CLKSRC_SATA

CLKSRC_SATA*

CLKSRC_PE1X_1394

CLKSRC_PE1X_1394*

CLKSRC_PE1X_LAN

CLKSRC_PE1X_LAN*

CLKSRC_ICH

CLKSRC_ICH*

CLKSRC_PE1X_SL1

CLKSRC_PE1X_SL1*

DPL_REFSSCLKIN_DP

DPL_REFSSCLKIN_DP*

CLKH_CPU_XDP

CLKH_CPU_XDP*

CLKH_GMCH

CLKH_GMCH*

CLKH_CPU

CLKH_CPU*

ICH_VRMPWRGD

GMCH_BSEL013

GMCH_BSEL113

GMCH_BSEL213

D D

C C

CLK48_USB22

CLK33_DBP32

CLK33_SIO32

CLK33_ICH22

CLK14_ICH23

CLK14_SIO32

SMBDATA7,17,21,30,32

CLK96_DOT13

CLK96_DOT*13

CLKSRC_GMCH11

CLKSRC_GMCH*11

CLKSRC_SATA23

CLKSRC_SATA*23

CLKSRC_PE1X_139428

CLKSRC_PE1X_1394*28

CLKSRC_PE1X_LAN29

CLKSRC_PE1X_LAN*29

CLKSRC_ICH22

CLKSRC_ICH*22

CLKSRC_PE1X_SL130

CLKSRC_PE1X_SL1*30

DPL_REFSSCLKIN13

DPL_REFSSCLKIN*13

CLKH_CPU_XDP7

CLKH_CPU_XDP*7

CLKH_GMCH10

CLKH_GMCH*10

CLKH_CPU7

CLKH_CPU*7

ICH_VRMPWRGD23,38

Decoupling for Clock Driver

VCC3_CLK

L40

L40

VDDIO_CLK

1 2

FCM1608KFG-301T05-GP

FCM1608KFG-301T05-GP

L38

L38

1 2

BLM18PG181SN1D-GP

BLM18PG181SN1D-GP

(63.00000.00L)

(63.00000.00L)

L16

L16

1 2

BLM18PG181SN1D-GP

BLM18PG181SN1D-GP

(63.00000.00L)

(63.00000.00L)

L39

L39

1 2

BLM18PG181SN1D-GP

BLM18PG181SN1D-GP

(63.00000.00L)

(63.00000.00L)

HOST CLK

PCI CLK

REF CLK

USB CLK

DREF CLK

SRC CLK

SCD1U10V2MX-3GP

SCD1U10V2MX-3GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

Trace

Width

4 mils

4 mils

4 mils

4 mils

4 mils 18 mils

4 mils

VDDIO_CLK

12

C398

C398

(R)

(R)

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

C393

C393

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

C183

C183

C395

C395

DIFF

Space

10 mils

10 milS

10 milS

10 mils

10 mils

10 mils

4

12

C402

C402

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

VCC3_CLK_PCI

12

SCD1U10V2MX-3GP

SCD1U10V2MX-3GP

VCC3_CLK_48

12

C187

C187

(R)

(R)

SCD1U10V2MX-3GP

SCD1U10V2MX-3GP

VCC3_CLK_SRC

12

SCD1U10V2MX-3GP

SCD1U10V2MX-3GP

Other

Space

18 mils

X

X

X

18 mils

12

C400

C400

SCD1U10V2MX-3GP

SCD1U10V2MX-3GP

12

C394

C394

12

12

C403

C403

DIFF/Trace

Impedance

95 ohm

50 ohm ± 15%

50 ohm ± 15%

50 ohm ± 15%

95 ohm

95 ohm

12

C401

C401

SCD1U10V2MX-3GP

SCD1U10V2MX-3GP

SCD1U10V2MX-3GP

SCD1U10V2MX-3GP

12

C179

(R)C179

(R)

SCD1U10V2MX-3GP

SCD1U10V2MX-3GP

12

C190

C190

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

12

C396

C396

SCD1U10V2MX-3GP

SCD1U10V2MX-3GP

(R)

(R)

12

DIFF

Matched

10 mils

X

X

X

10 mils

25 mils

12

C404

C404

C399

C399

SCD1U10V2MX-3GP

SCD1U10V2MX-3GP

SCD1U10V2MX-3GP

SCD1U10V2MX-3GP

R550

R550

0R0603-PAD

0R0603-PAD

NB-CPU= 1700 mils

NOTE

VCC3_3

3

VCC3_3 VCC3_3

R164

R164

1KR2J-1-GP

12

C397

C397

12

VCC3_CLK

BSEL0

12

R159

R159

470R3J-2-GP

470R3J-2-GP

BSEL0

1 2

V_1P1_FSB

12

R289

R289

470R3J-2-GP

470R3J-2-GP

BSEL1

RTM875T Multi-function Pin at pin 4, 5, 6, 7

ICS9LPRGS0 Multi-function Pin at pin 4, 6, 7

STRAP

PIN

4

(4)

TME

6

(5)

SRC5_EN

7

(7)

ITP_EN

27M_SEL

1KR2J-1-GP

R162

R162

BSEL0_2

1 2

4K7R2J-2-GP

4K7R2J-2-GP

R163 10KR2J-3-GPR163 10KR2J-3-GP

R291 10KR2J-3-GPR291 10KR2J-3-GP

1 2

R290

R290

1 2

1KR2J-1-GP

1KR2J-1-GP

B

GMCH_BSEL1

BSEL1_R

STRAPPING MODE

"HIGH" = Overclocking Enable

"LOW" = Overclocking NOT Allowed

"HIGH" = PIN29/30 is SRC-5, 100MHz diff.

"LOW" = PIN29/30 is PCI_STOP/..

"HIGH" = PIN38/39 is CPUITP

"LOW" = PIN38/39 is SRC8

"HIGH" = PIN17/18 of RTM875T is 27MHz/27MHz_SS

PIN13/14 of RTM875T is SRC-0 diff.

"LOW" = PIN17/18 of RTM875T is SRC-1 diff.

PIN13/14 of RTM875T is DOT96 diff.

12

BSEL0_3

C

Q22

Q22

MMBT3904-3-GP

MMBT3904-3-GP

E

V_1P1_FSBV_1P1_FSB

12

B

R154

R154

470R3J-2-GP

470R3J-2-GP

BSEL2

2

R165

R165

BSEL0_4

1 2

1KR2J-1-GP

1KR2J-1-GP

C

Q21

Q21

MMBT3904-3-GP

MMBT3904-3-GP

E

R155 10KR2J-3-GPR155 10KR2J-3-GP

1 2

1

R167

R167

BSEL0_R

R156

R156

BSEL2

1 2

4K7R2J-2-GP

4K7R2J-2-GP

CPU

GMCH_BSEL2GMCH_BSEL0

133

200

1KR2J-1-GP

1KR2J-1-GP

BSEL2_2

R166

R166

B

BSEL0

FSA

0 1

12

BSEL2_3

C

Q20

Q20

MMBT3904-3-GP

MMBT3904-3-GP

E

BSEL1

FSB

B

0

1 2

1KR2J-1-GP

1KR2J-1-GP

BSEL2_4

C

Q23

Q23

MMBT3904-3-GP

MMBT3904-3-GP

E

BSEL2

FSC

BSEL2_R

01

0

0 0266 0

333 0 0 1

NET NAME

PCI2_R

CLK33_SIO_R

CLK33_ICH_R

PCI4_R(6)

U15

VCC3_CLK_PCI

VCC3_CLK_48

VCC3_CLK_PCI

VCC3_CLK_SRC

Design Note: BSEL

BIASING RES. ALWAYS

STUFF

B B

12

R295

R295

47KR2J-2-GP

47KR2J-2-GP

12

R296

R296

33KR2J-3-GP

33KR2J-3-GP

A A

12

R282

R282

10KR2J-3-GP

10KR2J-3-GP

VCC3_CLK

For RTM875T

12

12

12

R276

R276

10KR2J-3-GP

10KR2J-3-GP

12

R283

R283

10KR2J-3-GP

10KR2J-3-GP

(R)

(R)

VCC3_CLK

R285

R285

47KR2J-2-GP

47KR2J-2-GP

CLK48_USB

CLK14_ICH

R281

R281

33KR2J-3-GP

33KR2J-3-GP

VCC3_CLK

12

R288

R288

10KR2J-3-GP

10KR2J-3-GP

PCI2_R

CLK33_SIO_R

PCI4_R CLK33_DBP

12

R287

10KR2J-3-GP

10KR2J-3-GP

CLK33_ICH_R

(R)R287

(R)

12

R551

R551

10KR2J-3-GP

10KR2J-3-GP

5

CLOCK EMI CAPS. DEFAULT EMPTY

12

EC2

SC22P50V2JN-4GP

SC22P50V2JN-4GP

12

(R)EC2

(R)

EC3

SC22P50V2JN-4GP

SC22P50V2JN-4GP

4

(R)EC3

(R)

CLK33_SL1_R_1

CLK33_SIO_R_1

CLK33_ICH_R_1

PCI5 must connect

to ICH.

CLK48_USB

CLK14_ICH

CLK14_SIO

R278 33R2J-2-GPR278 33R2J-2-GP

R279 33R2J-2-GPR279 33R2J-2-GP

R286 33R2J-2-GPR286 33R2J-2-GP

R293 33R2J-2-GPR293 33R2J-2-GP

R284 22R2J-2-GPR284 22R2J-2-GP

R280 22R2J-2-GPR280 22R2J-2-GP

place close to clock gen.

12

EC4

SC22P50V2JN-4GP

SC22P50V2JN-4GP

12

(R)EC4

(R)

1 2

1 2

1 2

1 2

1 2

1 2

EC6

SC22P50V2JN-4GP

SC22P50V2JN-4GP

VDDIO_CLK

CLK33_SL1_R

PCI1_R

PCI2_R

CLK33_SIO_R

PCI4_R

CLK33_ICH_R

CK_XOUT

CK_XIN

BSEL0_R

BSEL1_R

BSEL2_R

CLK33_SIO

CLK33_ICH

CLK48_USB

BSEL2_R

12

EC5

(R)EC5

(R)EC6

(R)

(R)

SC22P50V2JN-4GP

SC22P50V2JN-4GP

3

U15

2

VDD_PCI

9

VDD_48

16

VDD_PLL3

53

VDD_REF

31

VDD_SRC

47

VDD_CPU

12

VDD_IO

20

VDD_PLL3_IO

26

VDD_SRC_IO

37

VDD_SRC_IO

41

VDD_CPU_IO

1

CR#_A/PCI_0

3

CR#_B/PCI_1

4

TME/PCI_2

5

SRC_5_EN/PCI_3

6

27M_SEL/PCI_4

7

ITP_EN/PCIF_5

51

XOUT

52

XIN

10

FSLA/USB48

49

FSLB/TEST_MODE

54

FSLC/TEST_SEL/REF

8

GND_PCI

11

GND_48

15

GND_IO

19

GND_PLL3

23

GND_SRC

34

GND_SRC

44

GND_CPU

50

GND_REF

RTM875T-605-VD-GRT-GP

RTM875T-605-VD-GRT-GP

71.00875.C0W

SRC_0/DOT96

SRC_0#/DOT96#

27MHZ/SRC_1/SE1

27MHZSS/SRC_1#/SE2

SRC_2/SATA

SRC_2#/SATA#

CR#_C/SRC_3

CR#_D/SRC_3#

PCI_STOP#/SRC_5

CPU_STOP#/SRC_5#

SRC_7/CR#_F

SRC_7#/CR#_E

SRC_8/CPU_ITP

SRC_8#/CPU_ITP#

CK_PWRGD/PD#

Crystal

12

55

SDATA

56

SCLK

13

14

17

18

21

22

24

25

27

SRC_4

28

SRC_4#

30

29

33

SRC_6

32

SRC_6#

36

35

39

38

43

CPU_1

42

CPU_1#

46

CPU_0

45

CPU_0#

48

40

RESET#

(23.30001.331)

(23.30001.331)

X3

X3

1 2

X-14D31818M-23GP

X-14D31818M-23GP

C181

C181

SC33P50V2JN-3GP

SC33P50V2JN-3GP

82.30005.971

82.30005.881

SMBDATA

SMBCLK

CLK96_DOT

CLK96_DOT*

CLKSRC_GMCH

CLKSRC_GMCH*

CLKSRC_SATA

CLKSRC_SATA*

CLKSRC_PE1X_1394

CLKSRC_PE1X_1394*

CLKSRC_PE1X_LAN

CLKSRC_PE1X_LAN*

CLKSRC_ICH

CLKSRC_ICH*

CLKSRC_PE1X_SL1

CLKSRC_PE1X_SL1*

DPL_REFSSCLKIN_DP

DPL_REFSSCLKIN_DP*

CLKH_CPU_XDP

CLKH_CPU_XDP*

CLKH_GMCH

CLKH_GMCH*

CLKH_CPU

CLKH_CPU*

1 2

R292

R292

1KR2J-1-GP

1KR2J-1-GP

12

C180

C180

SC27P50V2JN-2-GP

SC27P50V2JN-2-GP

2

SMBDATA 7,17,21,30,32

SMBCLK 7,17,21,30,32

CLK96_DOT 13

CLK96_DOT* 13

CLKSRC_GMCH 11

CLKSRC_GMCH* 11

CLKSRC_SATA 23

CLKSRC_SATA* 23

CLKSRC_PE1X_1394 28

CLKSRC_PE1X_1394* 28

CLKSRC_PE1X_LAN 29

CLKSRC_PE1X_LAN* 29

CLKSRC_ICH 22

CLKSRC_ICH* 22

CLKSRC_PE1X_SL1 30

CLKSRC_PE1X_SL1* 30

DPL_REFSSCLKIN 13

DPL_REFSSCLKIN* 13

CLKH_CPU_XDP 7

CLKH_CPU_XDP* 7

CLKH_GMCH 10

CLKH_GMCH* 10

CLKH_CPU 7

CLKH_CPU* 7

ICH_VRMPWRGDCK_PWRGD_R

CK_XIN

CK_XOUT

ICH_VRMPWRGD 23,38

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

CK505 RTM875T-605

CK505 RTM875T-605

CK505 RTM875T-605

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

EAGLELAKE

C

EAGLELAKE

C

EAGLELAKE

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

6 39Monday, May 25, 2009

6 39Monday, May 25, 2009

6 39Monday, May 25, 2009

A00

A00

A00

PDF created with pdfFactory trial version www.pdffactory.com

5

VID038

VID138

VID238

VID338

VID438

VID538

VID638

VID738

R498 0R2J-2-GP(R)R498 0R2J-2-GP(R)

1 2

R499 0R0402-PAD(R)R499 0R0402-PAD(R)

1 2

R496 0R2J-2-GP(R)R496 0R2J-2-GP(R)

1 2

R497 0R0402-PAD(R)R497 0R0402-PAD(R)

1 2

12

C94

C94

51R2J-2-GP

51R2J-2-GP

51R2J-2-GP

51R2J-2-GP

CPUSMI*

A20M*

FERR*

INTR

NMI

IGNNE*

STPCLK*

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VID7

VRD_VIDSEL

CLKH_CPU

CLKH_CPU*

CPU_GTLREF_3

H_TESTHI_12

THERMTRIP*

FORCEPH

CPUPWRGD

PROCHOT*

RSTBTN*

BSEL0

BSEL1

BSEL2

VRMPWRGD

CLKH_CPU_XDP

CLKH_CPU_XDP*

SMBCLK

SMBDATA

RSTBTN*

CPURST*

H_BPM*0_2

H_TESTHI_8

H_TESTHI_9

H_TESTHI_10

VCORE_SENSE

VSS_SENSE

VCORE_SENSE_AN3

VCORE_SENSE_AN5

V_1P5_ICH

12

C96

C96

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

VSS_SENSE_AN4

VSS_SENSE_AN6

MS_ID0

MS_ID1

TP9 TP-2TP9 TP-2

TP8 TP-2TP8 TP-2

TP7 TP-2TP7 TP-2

TP31 TP-2TP31 TP-2

TP28 TP-2TP28 TP-2

TP27 TP-2TP27 TP-2

VTT_OUT_RIGHT

LAYOUT NOTE: PLACE AT CPU

END OF ROUTE

VTT_OUT_RIGHT

R34 1KR2J-1-GP

R34 1KR2J-1-GP

1 2

X00 Check

(R)

(R)

CPUSMI*23

A20M*23

FERR*23

INTR23

NMI23

IGNNE*23

STPCLK*23

D D

VRD_VIDSEL38

CLKH_CPU6

CLKH_CPU*6

CPU_GTLREF_38

H_TESTHI_129

THERMTRIP*23

FORCEPH38

CPUPWRGD4,23

PROCHOT*38

RSTBTN*23

BSEL06

BSEL16

BSEL26

VRMPWRGD4,32,38

CLKH_CPU_XDP6

CLKH_CPU_XDP*6

SMBCLK6,17,21,30,32

SMBDATA6,17,21,30,32

H_TESTHI_108

VCORE_SENSE38

VSS_SENSE38

VCORE_SENSE

RSTBTN*23

CPURST*4,8,10,32

H_BPM*0_29

H_TESTHI_88

H_TESTHI_98

C C

4/21

VSS_SENSE

4/21

B B

A A

R150

R150

1 2

0R0402-PAD

0R0402-PAD

H_VCCPLL

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

R95

(R)R95

(R)

1 2

R96

(R)R96

(R)

1 2

signal 2005 perf FMB 2005 value FMB 2006 65W FMB(section4.4.6)

-----------------------------------------------------------------------------------MSID1 51 pd to VSS 51 pd to VSS 51 pd to VSS

MSID0 51 pd to VSS NC NC

4

U7C

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VID7

U7C

P2

SMI#

K3

A20M#

R3

FERR#/PBE#

K1

LINT0

L1

LINT1

N2

IGNNE#

M3

STPCLK#

A23

VCCA

B23

VSSA

D23

RSVD

C23

VCCIOPLL

AM2

VID0

AL5

VID1

AM3

VID2

AL6

VID3

AK4

VID4

AL4

VID5

AM5

FC11

AM7

FC12

AN7

FC16

F28

BCLK0

G28

BCLK1

AE8

SKTOCC#

AL1

THERMDA

AK1

THERMDC

AJ7

VSS

AH7

VSS

AN3

VCC_SENSE

AN4

VSS_SENSE

AN5

VCC_MB_REGULATION

AN6

VSS_MB_REGULATION

AL8

VCCP

AL7

VSS

F29

RSVD

Y2

VSS

(62.10055.311)

(62.10055.311)

XDP1

XDP1

12

HOOK1

16

HOOK2

18

HOOK3

29

TDI

23

TDO

31

TMS

30

TCK0

28

TCK1

13

BCLK0

15

BCLK1

22

SCL

24

SDA

14

VTT

HRS-CONN31D-2-GP

HRS-CONN31D-2-GP

(X)

(X)

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

DBR#

TRST#

RESET#

PWRGOOD

TESTHI11

TESTHI12

FORCEPH

TESTHI13

PWRGOOD

PROCHOT#

THERMTRIP#

BOOTSELECT

GND

GND

GND

GND

GND

GND

GND

GND

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

9

7

6

4

3

1

21

25

19

10

2

5

8

11

17

20

26

27

CPUSMI*

A20M*

FERR*

INTR

NMI

IGNNE*

STPCLK*

TP_PLL_VCCA

1

TP_PLL_VSSA

1

H_VCCPLL

TP_PLL_VCCIO

1

VRD_VIDSEL

CLKH_CPU

CLKH_CPU*

SKTOCC_N

1

VCORE_SENSE_AN3

VSS_SENSE_AN4

VCORE_SENSE_AN5

VSS_SENSE_AN6

TP_CPU_AL8

1

TP_CPU_AL7

1

XDP_TESTIN_N

1 2

NC_XDP_16

R504

(X)R504

(X)

NC_XDP_18

62R2J-GP

62R2J-GP

H_TDI

H_TDO

H_TMS

H_TCK

NC_XDP_28

CLKH_CPU_XDP

CLKH_CPU_XDP*

SMBCLK

SMBDATA

VTT_OUT_RIGHT VTT_OUT_LEFT

VRD_VIDSEL

RSVD

RSVD

COMP0

COMP1

COMP2

COMP3

COMP4

COMP5

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

MSID1

MSID0

LL_ID0

LL_ID1

F26

W3

P1

W2

F25

G25

G27

G26

G24

F24

AK6

G6

PM_SLP_N

L2

AH2

CPUPWRGD

N1

PROCHOT*

AL2

THERMTRIP*_1

M2

A13

T1

G2

R1

J2

PM_DPRSTP_N

T2

N5

AE6

C9

G10

D16

A20

E23

F23

J3

V1

W1

Bootselect_1

Y1

V2

AA2

H_BPM*0

H_BPM*1

H_BPM*2

H_BPM*3

H_BPM*4

H_BPM*5

RSTBTN*

H_TRST*

CPURST*_XDP

CPUPWRGD_XDP

H_TESTHI_0

H_TESTHI_1

H_DPSLP_N

H_TESTHI_12

H_TESTHI_2_7

FORCEPH

H_COMP0

H_COMP1

H_COMP2

H_COMP3

H_COMP4

H_BPM*1_2

CPU_GTLREF_3

MS_ID1

MS_ID0

51R2J-2-GP

51R2J-2-GP

R89

R89

12

R511

1KR2J-1-GP

1KR2J-1-GP

R501

1KR2J-1-GP

1KR2J-1-GP

(X)R511

(X)

12

12

(X)R501

(X)

3

4/18

R110

0R0402-PAD

0R0402-PAD

CPURST*

VTT_OUT_RIGHT

(R)R110

(R)

1 2

VTT_OUT_RIGHT

12

THERMTRIP*

R43

R43

51R2J-2-GP

51R2J-2-GP

2

H_TCK

H_TDI

H_TDO

H_TMS

H_TRST*

H_BPM*0

H_BPM*1

H_BPM*2

H_BPM*3

H_BPM*4

H_BPM*5

RSTBTN*23

BSEL06

BSEL16

BSEL26

51R2J-2-GP

51R2J-2-GP

R520

R520

12

4 mils Width on 6 mils Spacing

VTT_OUT_LEFT

VTT_OUT_RIGHT

VTT_OUT_LEFT

3/11

TESTHIx ,

4 mils Width on 6 mils Spacing

V_1P1_FSB

R522 51R2J-2-GPR522 51R2J-2-GP

1 2

R521 51R2J-2-GPR521 51R2J-2-GP

1 2

VTT_OUT_LEFT

R92 51R2J-2-GPR92 51R2J-2-GP

1 2

R82 51R2J-2-GPR82 51R2J-2-GP

1 2

R121 51R2J-2-GPR121 51R2J-2-GP

1 2

R112 51R2J-2-GPR112 51R2J-2-GP

1 2

R99 51R2J-2-GPR99 51R2J-2-GP

1 2

P.S connect to NB and ICH

AE1

AD1

AF1

AC1

AG1

AJ2

AJ1

AD2

AG2

AF2

AG3

RSTBTN*

AC2

AK3

AJ3

BSEL0

G29

BSEL1

H30

BSEL2

G30

E7

IMPSEL

F6

PSI_N

Y3

H_COMP7

AE3

H_COMP8

B13

D14

E6

D1

E5

VTT_OUT_RIGHT

R51 51R2J-2-GPR51 51R2J-2-GP

R46 51R2J-2-GPR46 51R2J-2-GP

R80 51R2J-2-GPR80 51R2J-2-GP

R60 51R2J-2-GPR60 51R2J-2-GP

R66 51R2J-2-GPR66 51R2J-2-GP

R55 51R2J-2-GPR55 51R2J-2-GP

R109 100R2F-L1-GP-U(R)R109 100R2F-L1-GP-U(R)

1 2

R32 130R2F-1-GP(R)R32 130R2F-1-GP(R)

1 2

R35 130R2F-1-GP(R)R35 130R2F-1-GP(R)

1 2

R108 51R2J-2-GPR108 51R2J-2-GP

1 2

R111 51R2J-2-GPR111 51R2J-2-GP

1 2

H_TESTHI_1

H_TESTHI_8

H_TESTHI_9

H_TESTHI_10

H_TESTHI_12

U7D

U7D

TCK

TDI

TDO

TMS

TRST#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

DBR#

ITPCLK0

ITPCLK1

BSEL0

BSEL1

BSEL2

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

(62.10055.311)

(62.10055.311)

LAYOUT: 4 mil on 5mil

1 2

1 2

1 2

1 2

1 2

1 2

CPUPWRGD

PROCHOT*

FORCEPH

H_DPSLP_N

PM_SLP_N

H_TESTHI_0

H_TESTHI_2_7

VTTPWRGD

VTT_OUT

VTT_OUT

VTT_SEL

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT_OUT_RIGHT

VTT_OUT_RIGHT

VTT_OUT_LEFT

V_1P1_FSB

A29

B25

B29

B30

C29

A26

B27

C28

A25

A28

A27

C30

A30

C25

C26

C27

B26

D27

D28

D25

D26

B28

D29

D30

AM6

AA1

J1

F27

H_BPM*0

H_BPM*1

H_BPM*2

H_BPM*3

H_BPM*4

H_BPM*5

4/21

(R)

(R)

R16 0R0402-PAD

R16 0R0402-PAD

1 2

VTT_PWRGD_1

VTT_OUT_LEFT

TP_CPUVTT_SEL

1

VTT_OUT_LEFT

0R2J-2-GP(R)

0R2J-2-GP(R)

R136

R136

1 2

0R2J-2-GP(R)

0R2J-2-GP(R)

R40

R40

1 2

0R2J-2-GP(R)

0R2J-2-GP(R)

R81

R81

1 2

0R2J-2-GP(R)

0R2J-2-GP(R)

R119

R119

1 2

FOR SUPPORT KENTSFIELD CPU

COMP PULLUPS/PULLDOWNS

R83 62R2J-GPR83 62R2J-GP

1 2

R78 62R2J-GPR78 62R2J-GP

1 2

R68 62R2J-GPR68 62R2J-GP

1 2

C33 SCD1U16V2ZY-2GPC33 SCD1U16V2ZY-2GP

1 2

C47 SCD1U16V2ZY-2GPC47 SCD1U16V2ZY-2GP

1 2

R59 62R2J-GPR59 62R2J-GP

12

R74 62R2J-GPR74 62R2J-GP

12

COMP PULLUPS/PULLDOWNS

R113 49D9R2F-GP(R) R113 49D9R2F-GP(R)

1 2

R100 49D9R2F-GPR100 49D9R2F-GP

1 2

R91 49D9R2F-GPR91 49D9R2F-GP

1 2

R71 49D9R2F-GP(R) R71 49D9R2F-GP(R)

1 2

C78 SCD1U16V2ZY-2GPC78 SCD1U16V2ZY-2GP

1 2

C79 SCD1U16V2ZY-2GPC79 SCD1U16V2ZY-2GP

1 2

R161 49D9R2F-GPR161 49D9R2F-GP

1 2

R102 49D9R2F-GPR102 49D9R2F-GP

1 2

R140 49D9R2F-GPR140 49D9R2F-GP

1 2

R106 49D9R2F-GPR106 49D9R2F-GP

1 2

R160 24D9R2F-L-GPR160 24D9R2F-L-GP

1 2

P.S connect to NB and ICH

VRMPWRGD

TP35

TP35

TP-2

TP-2

C56

C56

SCD1U10V2MX-3GP

SCD1U10V2MX-3GP

H_BPM*0_2

H_BPM*1_2

H_TESTHI_8

H_TESTHI_9

H_TMS

H_TDI

H_TDO

H_TRST*

H_TCK

H_COMP4

PM_DPRSTP_N

PSI_N

H_COMP7

VTT_OUT_RIGHT

12

SCD1U10V2MX-3GP

SCD1U10V2MX-3GP

1/6

H_COMP0

H_COMP1

H_COMP2

H_COMP3

H_COMP8

1

12

C66

C66

5

4

PDF created with pdfFactory trial version www.pdffactory.com

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

LGA-775 - FSB_VTT & Non-GTL

LGA-775 - FSB_VTT & Non-GTL

LGA-775 - FSB_VTT & Non-GTL

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

EAGLELAKE

C

EAGLELAKE

C

EAGLELAKE

C

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

7 39Monday, May 25, 2009

7 39Monday, May 25, 2009

7 39Monday, May 25, 2009

A00

A00

A00

5

HA*[3..35]10

HREQ*[0..4]10

H_ADSTB0*10

PECI_SIO32

H_ADSTB1*10

D D

C C

CPU_GTLREF1_DIVIDER16

B B

H_ADS*10

H_BNR*10

H_HIT*10

H_BPRI*10

H_DBSY*10

H_DRDY*10

H_HITM*10

H_LOCK*10

H_TRDY*10

H_DEFER*10

H_BR0*10

H_TESTHI_97

H_TESTHI_87

H_TESTHI_107

CPURST*4,7,10,32

H_RS*010

H_RS*110

H_RS*210

HD*[0..15]10

H_DBI0*10

H_DSTBN0*10

H_DSTBP0*10

HD*[16..31]10

H_DBI1*10

H_DSTBN1*10

H_DSTBP1*10

HD*[32..47]10

H_DBI2*10

H_DSTBN2*10

H_DSTBP2*10

HD*[48..63]10

H_DBI3*10

H_DSTBN3*10

H_DSTBP3*10

CPU_GTLREF_37

INIT*23

CPU_GTLREF1_DIVIDER

H_ADSTB0*

PECI_SIO

H_ADSTB1*

H_ADS*

H_BNR*

H_HIT*

H_BPRI*

H_DBSY*

H_DRDY*

H_HITM*

INIT*

H_LOCK*

H_TRDY*

H_DEFER*

H_BR0*

H_TESTHI_9

H_TESTHI_8

H_TESTHI_10

CPURST*

H_RS*0

H_RS*1

H_RS*2

H_DBI0*

H_DSTBN0*

H_DSTBP0*

H_DBI1*

H_DSTBN1*

H_DSTBP1*

H_DBI2*

H_DSTBN2*

H_DSTBP2*

H_DBI3*

H_DSTBN3*

H_DSTBP3*

CPU_GTLREF_3

HA*[3..35]10

HREQ*[0..4]10

HA*[3..35]10

DESIGN NOTE:

GTLREF VOLTAGE SHOULD BE 0.635*VTT

(63.5% OF 1.1V) = 0.7V

<FOR THIS DESIGN>

VTT_OUT_RIGHT VTT_OUT_RIGHT

12

R123

R123

57D6R2F-GP

57D6R2F-GP

CPU_GTLREF_0_R CPU_GTLREF_0 CPU_GTLREF_1

12

A A

R126

R126

100R2F-L1-GP-U

100R2F-L1-GP-U

R125 10R2J-2-GPR125 10R2J-2-GP

1 2

12

C83

C83

SC1U10V3ZY-6GP

SC1U10V3ZY-6GP

GTL_REF placement should never be placed greater

than 1.5’’ away from the CPU package pin

5

CPU_GTLREF_3

12

12

C82

C82

SC220P50V2KX-3GP

SC220P50V2KX-3GP

12

R129

R124

R124

0R0402-PAD

0R0402-PAD

(R)

(R)

4/18 4/18

R129

49D9R2F-GP

49D9R2F-GP

CPU_GTLREF_1_R

12

R132

R132

100R2F-L1-GP-U

100R2F-L1-GP-U

4

HREQ*0

HREQ*1

HREQ*2

HREQ*3

HREQ*4

H_ADSTB0*

PECI_SIO

TP_AC4

TP_AE4

H_ADSTB1*

CPU_GTLREF1_DIVIDER

R131 10R2J-2-GPR131 10R2J-2-GP

12

4

HA*3

HA*4

HA*5

M5

HA*6

HA*7

M4

HA*8

R4

HA*9

HA*10

U6

HA*11

HA*12

U5

HA*13

U4

HA*14

HA*15

HA*16

W5

TP_N4

N4

TP_P5

M6

R6

G5

HA*17

AB6

HA*18

W6

HA*19

HA*20

HA*21

AA4

HA*22

AD6

HA*23

AA5

HA*24

AB5

HA*25

AC5

HA*26

AB4

HA*27

AF5

HA*28

AF4

HA*29

AG6

HA*30

AG4

HA*31

AG5

HA*32

AH4

HA*33

AH5

HA*34

AJ5

HA*35

AJ6

AC4

AE4

AD5

1 2

C86

C86

SC1U10V3ZY-6GP

SC1U10V3ZY-6GP

L5

P6

L4

T5

T4

V5

V4

P5

K4

J5

K6

J6

Y6

Y4

(62.10055.311)

(62.10055.311)

U7A

U7A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

RSVD

RSVD

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

ADSTB0#

PCREQ#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

RSVD

RSVD

ADSTB1#

12

ADS#

BNR#

HIT#

RSP#

BPRI#

DBSY#

DRDY#

HITM#

IERR#

INIT#

LOCK#

TRDY#

BINIT#

DEFER#

EDRDY#

MCERR#

AP0#

AP1#

BR0#

TESTHI8

TESTHI9

TESTHI10

DP0#

DP1#

DP2#

DP3#

GTLREF1

GTLREF0

CS_GTLREF

GTLREF_SEL

RESET#

RS0#

RS1#

RS2#

CPU_GTLREF_2

12

R130

R130

0R0402-PAD

0R0402-PAD

(R)

(R)

C85

C85

SC220P50V2KX-3GP

SC220P50V2KX-3GP

D2

C2

D4

H4

G8

B2

C1

E4

AB2

P3

C3

E3

AD3

G7

F2

AB3

U2

U3

F3

G3

G4

H5

J16

H15

H16

J17

H2

H1

E24

H29

G23

B3

F5

A3

H_ADS*

H_BNR*

H_HIT*

TP_RSP*

H_BPRI*

H_DBSY*

H_DRDY*

H_HITM*

H_IERR*

INIT*

H_LOCK*

H_TRDY*

TP_BINIT*

H_DEFER*

CPU_GTLREF_2

TP_MCERR*

H_BR0*

H_TESTHI_9

H_TESTHI_8

H_TESTHI_10

CPU_GTLREF_1

CPU_GTLREF_0

TP_CS_GTLREF

CPURST*

H_RS*0

H_RS*1

H_RS*2

3

1

TP34TP-2 TP34TP-2

1

TP30TP-2 TP30TP-2

1

TP32TP-2 TP32TP-2

1

TP37TP-2 TP37TP-2

4 mils Width

6 mils Spacing

H_IERR*

RESET# & BR0#

5 mils Width

13 mils Spacing

H_BR0*

CPURST*

3

HD*[0..15]10

HD*[16..31]10

R84 62R2J-GPR84 62R2J-GP

1 2

C44 SCD1U16V2ZY-2GPC44 SCD1U16V2ZY-2GP

1 2

R145 62R2J-GPR145 62R2J-GP

R519 62R2J-GPR519 62R2J-GP

VTT_OUT_RIGHT

VTT_OUT_LEFT

12

V_1P1_FSB

12

HD*0

HD*1

HD*2

HD*3

HD*4

HD*5

HD*6

HD*7

HD*8

HD*9

HD*10

HD*11

HD*12

HD*13

HD*14

HD*15

H_DBI0*

H_DSTBN0*

H_DSTBP0*

HD*16

HD*17

HD*18

HD*19

HD*20

HD*21

HD*22

HD*23

HD*24

HD*25

HD*26

HD*27

HD*28

HD*29

HD*30

HD*31

H_DBI1*

H_DSTBN1*

H_DSTBP1*

2

B4

C5

A4

C6

A5

B6

B7

A7

A10

A11

B10

C11

D8

B12

C12

D11

A8

C8

B9

G9

F8

F9

E9

D7

E10

D10

F11

F12

D13

E13

G13

F14

G14

F15

G15

G11

G12

E12

2

1

U7B

U7B

HD*32

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

DBI0#

DSTBN0#

DSTBP0#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

DBI1#

DSTBN1#

DSTBP1#

(62.10055.311)

(62.10055.311)

GTL_REF placement should never be placed greater

than 1.5’’ away from the CPU package pin

V_1P1_FSB

V_1P1_FSB

G16

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DBI2#

DSTBN2#

DSTBP2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBI3#

DSTBN3#

DSTBP3#

12

12

12

12

HD*33

E15

HD*34

E16

HD*35

G18

HD*36

G17

HD*37

F17

HD*38

F18

HD*39

E18

HD*40

E19

HD*41

F20

HD*42

E21

HD*43

F21

HD*44

G21

HD*45

E22

HD*46

D22

HD*47

G22

H_DBI2*

D19

H_DSTBN2*

G20

H_DSTBP2*

G19

HD*48

D20

HD*49

D17

HD*50

A14

HD*51

C15

HD*52

C14

HD*53

B15

HD*54

C18

HD*55

B16

HD*56

A17

HD*57

B18

HD*58

C21

HD*59

B21

HD*60

B19

HD*61

A19

HD*62

A22

HD*63

B22

H_DBI3*

C20

H_DSTBN3*

A16

H_DSTBP3*

C17

R144

R144

57D6R2F-GP

57D6R2F-GP

(R)

(R)

R143

R143

100R2F-L1-GP-U

100R2F-L1-GP-U

(R)

(R)

R516

R516

49D9R2F-GP

49D9R2F-GP

(R)

(R)

R517

R517

100R2F-L1-GP-U

100R2F-L1-GP-U

(R)

(R)

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

12

12

LGA-775 - Host Bus

LGA-775 - Host Bus

LGA-775 - Host Bus

EAGLELAKE

EAGLELAKE

EAGLELAKE

R142

10R2J-2-GP

10R2J-2-GP

1 2

C89

C89

SC1U10V3ZY-6GP

SC1U10V3ZY-6GP

(R)

(R)

R518

10R2J-2-GP

10R2J-2-GP

1 2

C348

C348

SC1U10V3ZY-6GP

SC1U10V3ZY-6GP

(R)

(R)

HD*[32..47] 10

HD*[48..63] 10

(R)R142

(R)

CPU_GTLREF_2CPU_GTLREF_2_R

12

C90

C90

SC220P50V2KX-3GP

SC220P50V2KX-3GP

(R)

(R)

(R)R518

(R)

CPU_GTLREF_3CPU_GTLREF_3_R

12

C349

C349

SC220P50V2KX-3GP

SC220P50V2KX-3GP

(R)

(R)

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

8 39Monday, May 25, 2009

8 39Monday, May 25, 2009

8 39Monday, May 25, 2009

A00

A00

A00

PDF created with pdfFactory trial version www.pdffactory.com

5

VCORE

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

J9

U7E

U7E

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCC

AA8

D D

C C

B B

AC23

AC24

AC25

AC26

AC27

AC28

AC29

AC30

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AG11

AG12

AG14

AG15

AG18

AG19

AG21

AG22

AG25

AG26

AG27

AG28

AG29

AG30

AE11

AE12

AE14

AE15

AE18

AE19

AE21

AE22

AE23

AF11

AF12

AF14

AF15

AF18

AF19

AF21

AF22

VCC

AB8

VCC

AC8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AD8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AE9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AF8

VCC

AF9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AG8

VCC

AG9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AH8

VCC

VCC

VCC

VCC

AH9

AH11

AH12

AH14

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AH15

AH18

AH19

AH21

AH22

AH25

AH26

AH27

J30

K23

K24

K25

K26

K27

K28

K29

K30

K8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AJ8

AJ9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AH28

AH29

AH30

AJ21

M23

M24

M25

M26

M27

M28

M8

VCC

VCC

VCC

VCC

VCC

VCC

VCCL8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AK8

AK9

AJ22

AJ25

AJ26

AK11

VCC

VCC

AK12

AK14

AK15

AK18

AK19

AK21

AK25

AK22

4

M29

M30

N23

N24

N25

N26

N27

N28

N29

N8

VCC

VCC

VCC

AL9

AK26

N30

T23

T24

T25

T26

T8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AL11

VCCP8VCCR8VCC

VCC

VCC

VCC

VCC

T27

VCC

T28

VCC

T29

VCC

T30

VCC

U8

VCC

U23

VCC

U24

VCC

U25

VCC

U26

VCC

U27

VCC

U28

VCC

U29

VCC

U30

VCC

V8

VCC

W8

VCC

W23

VCC

W24

VCC

W25

VCC

W26

VCC

W27

VCC

W28

VCC

W29

VCC

W30

VCC

Y8

VCC

Y23

VCC

Y24

VCC

Y25

VCC

Y26

VCC

Y27

VCC

Y28

VCC

Y29

VCC

Y30

VCC

AN30

VCC

AN29

VCC

AN26

VCC

AN25

VCC

AN22

VCC

AN21

VCC

AN19

VCC

AN18

VCC

AN15

VCC

AN14

VCC

AN12

VCC

AN11

VCC

AN9

VCC

AN8

VCC

AM30

VCC

AM29

VCC

AM26

VCC

AM25

VCC

AM22

VCC

AM21

VCC

AM19

VCC

AM18

VCC

AM15

VCC

AM14

VCC

AM12

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AM8

AL12

AL14

AL15

AL18

AM9

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AM11

(62.10055.311)

(62.10055.311)

R523

R523

12

1KR2J-1-GP

1KR2J-1-GP

(R)

(R)

TP_A24

AG10

AG13

AG16

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA30

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AE10

AE13

AE16

AE17

AE20

AE24

AE25

AE26

AE27

AE28

AE29

AE30

AF10

AF13

AF16

AF17

AF20

AF23

AF24

AF25

AF26

AF27

AF28

AF29

AF30

A2

VSS

A6

VSS

A9

VSS

A12

VSS

A15

VSS

A18

VSS

A21

VSS

A24

VSS

AA3

VSS

AA6

VSS

AA7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB1

VSS

AB7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AC3

VSS

AC6

VSS

AC7

VSS

AD4

VSS

AD7

VSS

AE2

VSS

AE5

VSS

AE7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF3

VSS

AF6

VSS

AF7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AG7

VSS

VSS

VSS

VSS

3

H_TESTHI_12

TP_U1

U7

V23

V24

V25

V26

V27

V28

V29

V30

Y7

U7F

U7F

VSS

VSS

VSSW4VSSW7VSSY5VSS

V3

V7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSV6VSS

FC28

H_TESTHI_12 7

P27

P28

P29

P30

R23

R24

R25

R26

R27

R28

R29

R30

VSST3VSST6VSST7VSSU1VSS

R7

VSS

VSS

VSS

VSS

VSSR2VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSR5VSS

FC23

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH1

AH3

AH6

AG17

AG20

AG23

AG24

VSS

VSS

AH10

AH13

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ10

AJ13

AH16

AJ16

AH17

AH20

AH23

AH24

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AK2

AK5

AJ17

AJ20

AJ23

AK7

AJ24

AJ27

AJ28

AJ29

AJ30

AK10

AK13

AK16

AK17

AK20

P26

AK23

P25

VSS

VSS

AK24

P23

P24

VSS

VSS

VRDSEL

VSS

VSS

AK27

AK28

2

H24

H25

H26

H27

H28

K7

L23

L24

L25

L26

L27

L28

L29

L30

P7

VSS

VSS

VSSM1VSSM7VSSN3VSSN6VSSN7VSS

VSSP4VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL3

AL10

AL13

AL16

AL17

AL20

AK29

AK30

L3

L7

VSS

VSS

VSS

VSS

VSS

VSSJ4VSSJ7VSSK2VSSK5VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSL6VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AM1

AM4

AL23

AL24

AL27

AL28

AM10

VSS

VSS

AN1

AM13

AM16

AM17

AM20

AM23

AM24

AM27

AM28

VSS

AN2

FC27

FC26

VSS

AN10

H23

VSS

H22

VSS

H21

VSS

H20

VSS

H19

VSS

H18

VSS

H17

VSS

H14

VSS

H13

VSS

H12

VSS

H11

VSS

H10

VSS

H9

VSS

H8

VSS

H7

VSS

H6

VSS

H3

VSS

G1

VSS

F22

VSS

F19

VSS

F16

VSS

F13

VSS

F10

VSS

F7

VSS

F4

VSS

E29

VSS

E28

VSS

E27

VSS

E26

VSS

E25

VSS

E20

VSS

E17

VSS

E14

VSS

E11

VSS

E8

VSS

E2

VSS

D24

VSS

D21

VSS

D18

VSS

D15

VSS

D12

VSS

D9

VSS

D6

VSS

D5

VSS

D3

VSS

C24

VSS

C22

VSS

C19

VSS

C16

VSS

C13

VSS

C10

VSS

C7

VSS

C4

VSS

B24

VSS

B20

VSS

B17

VSS

B14

VSS

B11

VSS

B8

VSS

B5

VSS

B1

VSS

AN28

VSS

AN27

VSS

AN24

VSS

AN23

VSS

AN20

VSS

AN17

VSS

AN16

VSS

AN13

VSS

(62.10055.311)

(62.10055.311)

VTT_OUT_LEFT

TP_G1

TP_E29

1

1 2

H_BPM*0_2

R138

R138

51R2F-2-GP

51R2F-2-GP

TP36

TP36

1

TP-2

TP-2

H_BPM*0_2 7

TP_AL3

VCORE

12

C62

C62

SC22U6D3V6KX-1GP

SC22U6D3V6KX-1GP

12

C61

C61

SC22U6D3V6KX-1GP

SC22U6D3V6KX-1GP

12

C73

C73

SC22U6D3V6KX-1GP

SC22U6D3V6KX-1GP

12

C70

C70

SC22U6D3V6KX-1GP

SC22U6D3V6KX-1GP

12

C65

C65

SC22U6D3V6KX-1GP

SC22U6D3V6KX-1GP

12

C63

C63

SC22U6D3V6KX-1GP

SC22U6D3V6KX-1GP

12

C68

C68

SC22U6D3V6KX-1GP

SC22U6D3V6KX-1GP

12

C71

C71

SC22U6D3V6KX-1GP

SC22U6D3V6KX-1GP

12

C72

SC22U6D3V6KX-1GP

SC22U6D3V6KX-1GP

(R)C72

(R)

13 Pcs 22uF/cap

VCORE

12

C64

C64

SC22U6D3V6KX-1GP

A A

SC22U6D3V6KX-1GP

12

C69

C69

SC22U6D3V6KX-1GP

SC22U6D3V6KX-1GP

5

12

C75

C75

SC22U6D3V6KX-1GP

SC22U6D3V6KX-1GP

12

C74

C74

SC22U6D3V6KX-1GP

SC22U6D3V6KX-1GP

Inside CPU socket (component-side)

12

C76

C76

SC22U6D3V6KX-1GP

SC22U6D3V6KX-1GP

4

12

C77

(R)C77

(R)

SC22U6D3V6KX-1GP

SC22U6D3V6KX-1GP

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

LGA-775 - VCORE & GND

LGA-775 - VCORE & GND

LGA-775 - VCORE & GND

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

EAGLELAKE

C

EAGLELAKE

C

EAGLELAKE

C

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

9 39Monday, May 25, 2009

9 39Monday, May 25, 2009

9 39Monday, May 25, 2009

A00

A00

A00

PDF created with pdfFactory trial version www.pdffactory.com

5

4

3

2

1

HA*[3..35]8

HREQ*[0..4]8

H_ADSTB0*8

H_ADSTB1*8

H_DSTBP0*8

H_DSTBN0*8

H_DBI0*8

D D

C C

B B

H_DSTBP1*8

H_DSTBN1*8

H_DBI1*8

H_DSTBP2*8

H_DSTBN2*8

H_DBI2*8

H_DSTBP3*8

H_DSTBN3*8

H_DBI3*8

H_ADS*8

H_TRDY*8

H_DRDY*8

H_DEFER*8

H_HITM*8

H_HIT*8

H_LOCK*8

H_BR0*8

H_BNR*8

H_BPRI*8

H_DBSY*8

H_RS*08

H_RS*18

H_RS*28

CPURST*4,7,8,32

HD*[0..15]8

HD*[16..31]8

HD*[32..47]8

HD*[48..63]8

CLKH_GMCH6

CLKH_GMCH*6

HA*[3..35]

HREQ*[0..4]

H_ADSTB0*

H_ADSTB1*

H_DSTBP0*

H_DSTBN0*

H_DBI0*

H_DSTBP1*

H_DSTBN1*

H_DBI1*

H_DSTBP2*

H_DSTBN2*

H_DBI2*

H_DSTBP3*

H_DSTBN3*

H_DBI3*

H_ADS*

H_TRDY*

H_DRDY*

H_DEFER*

H_HITM*

H_HIT*

H_LOCK*

H_BR0*

H_BNR*

H_BPRI*

H_DBSY*

H_RS*0

H_RS*1

H_RS*2

CPURST*

HD*[0..15]

HD*[16..31]

HD*[32..47]

HD*[48..63]

CLKH_GMCH

CLKH_GMCH*

Host Interface

EAGLELAKE_DDR2

FSB_AB_3

FSB_AB_4

FSB_AB_5

FSB_AB_6

FSB_AB_7

FSB_AB_8

FSB_AB_9

FSB_AB_10

FSB_AB_11

FSB_AB_12

FSB_AB_13

FSB_AB_14

FSB_AB_15

FSB_AB_16

FSB_AB_17

FSB_AB_18

FSB_AB_19

FSB_AB_20

FSB_AB_21

FSB_AB_22

FSB_AB_23

FSB_AB_24

FSB_AB_25

FSB_AB_26

FSB_AB_27

FSB_AB_28

FSB_AB_29

FSB_AB_30

FSB_AB_31

FSB_AB_32

FSB_AB_33

FSB_AB_34

FSB_AB_35

FSB_REQ_0#

FSB_REQ_1#

FSB_REQ_2#

FSB_REQ_3#

FSB_REQ_4#

FSB_ADSTB_0#

FSB_ADSTB_1#

FSB_DSTBPB_0

FSB_DSTBNB_0

FSB_DINV_0#

FSB_DSTBPB_1

FSB_DSTBNB_1

FSB_DINV_1#

FSB_DSTBPB_2

FSB_DSTBNB_2

FSB_DINV_2#

FSB_DSTBPB_3

FSB_DSTBNB_3

FSB_DINV_3#

FSB_ADS#

FSB_TRDY#

FSB_DRDY#

FSB_DEFER#

FSB_HITM#

FSB_HIT#

FSB_LOCK#

FSB_BREQ0#

FSB_BNR#

FSB_BPRI#

FSB_DBSY#

FSB_RS_0#

FSB_RS_1#

FSB_RS_2#

FSB_CPURST#

RSVD#N25

82ELV-GP

82ELV-GP

EAGLELAKE_DDR2

HA*[3..35]

HREQ*[0..4]

HA*3

HA*4

HA*5

HA*6

HA*7

HA*8

HA*9

HA*10

HA*11

HA*12

HA*13

HA*14

HA*15

HA*16

HA*17