CXDP@,PXDP@ : Total debug Component (pop them until ST)

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

A B C D E

COMPAL CONFIDENTIAL

MODEL NAME : VAQ10

Diesel 15"

REV : 0.2 (X01)

2013.XX.XX

1@ : LVDS panel

2@ : eDP(QHD) panel

EMC@ : EMI/ESD/RF part

@ : Nopop Component

CONN@ : Connector Component

1

2

3

4

1

2

3

4

PCB NO :

BOM P/N :

GPIO MAP:

MB PCB

LA-9771P

4319MF31L01(TPM HDMI LVDS)

4319MF31L02(TPM HDMI QHD)

4319MF31L03(DTP HDMI LVDS)

4319MF31L04(DTP HDMI QHD)

D E

Description

PCB 0MF LA-9771P REV0 MB

Part Number

DAA0006I000

Title

Cover Sheet

Size Document Number

LA-9771P

Date: Tuesday January 15 2013 Sheet 1 of

BDBIOS.COM

Rev

0.2

65

A B

A

D

,

,

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTI L

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC

. ("DEL L") T HIS D OCUMEN T MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL

. IN ADD ITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIR

PARTY WITHO UT D ELL'S EXPR ESS W RITTEN CON SENT.

A B C D E

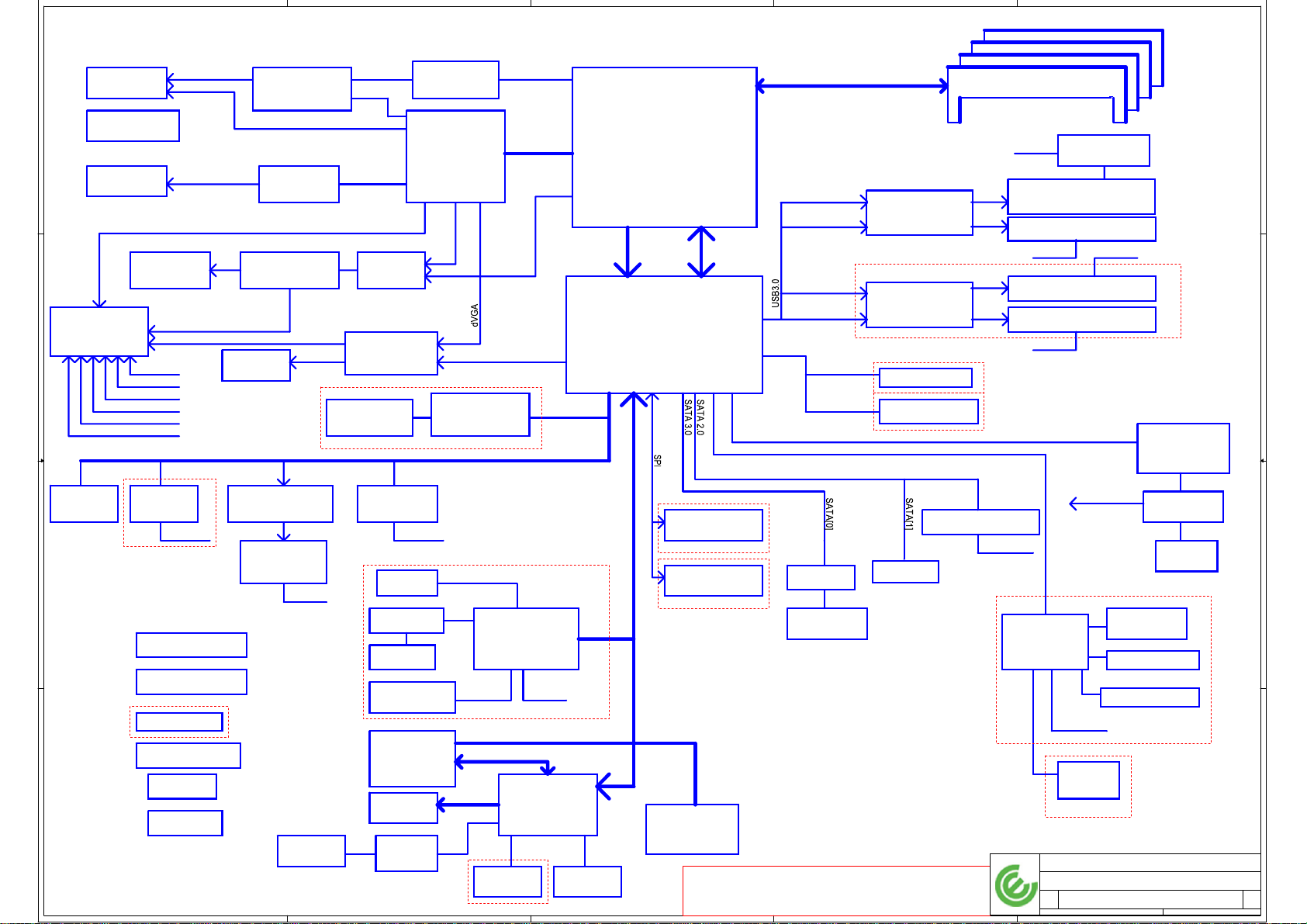

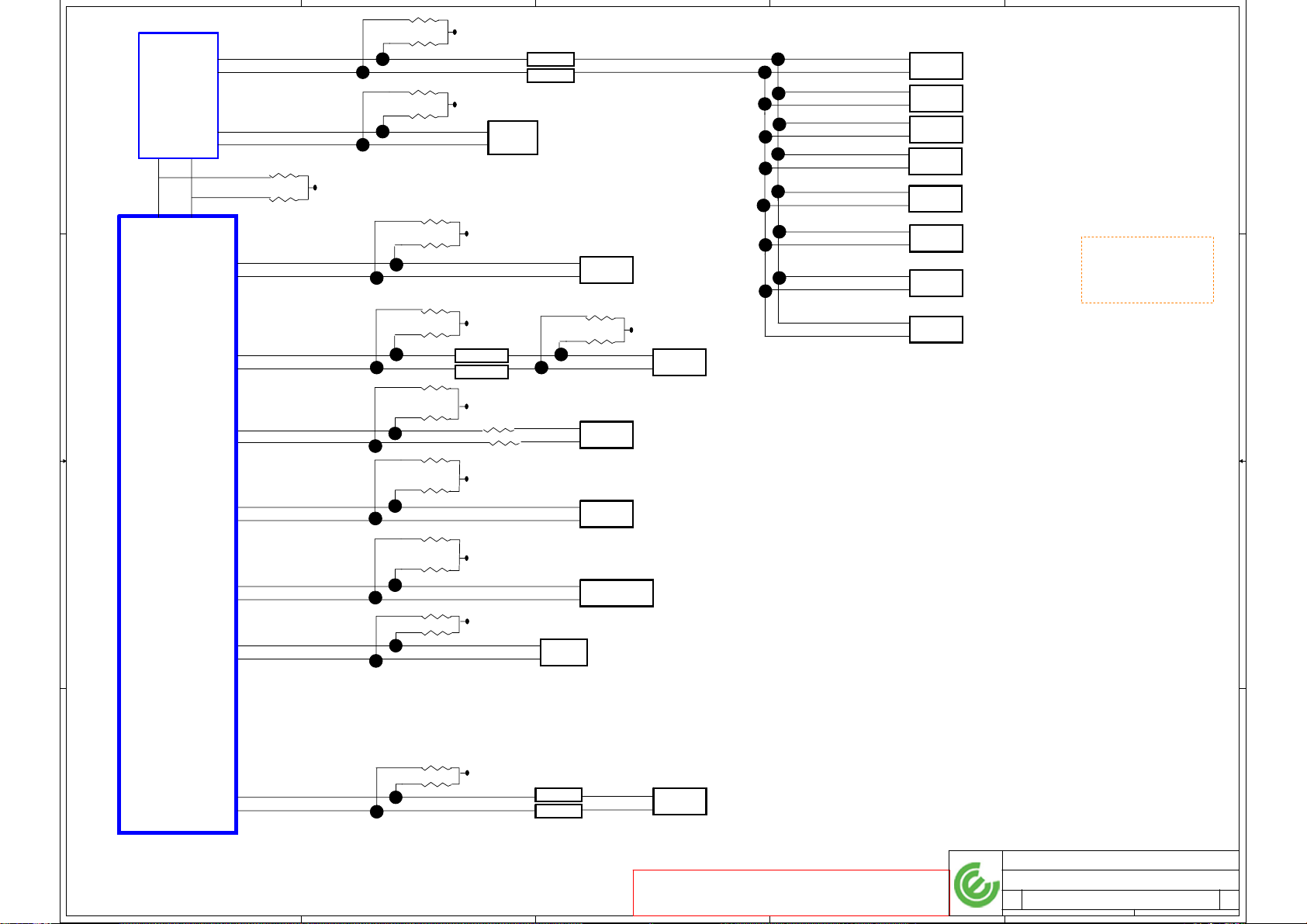

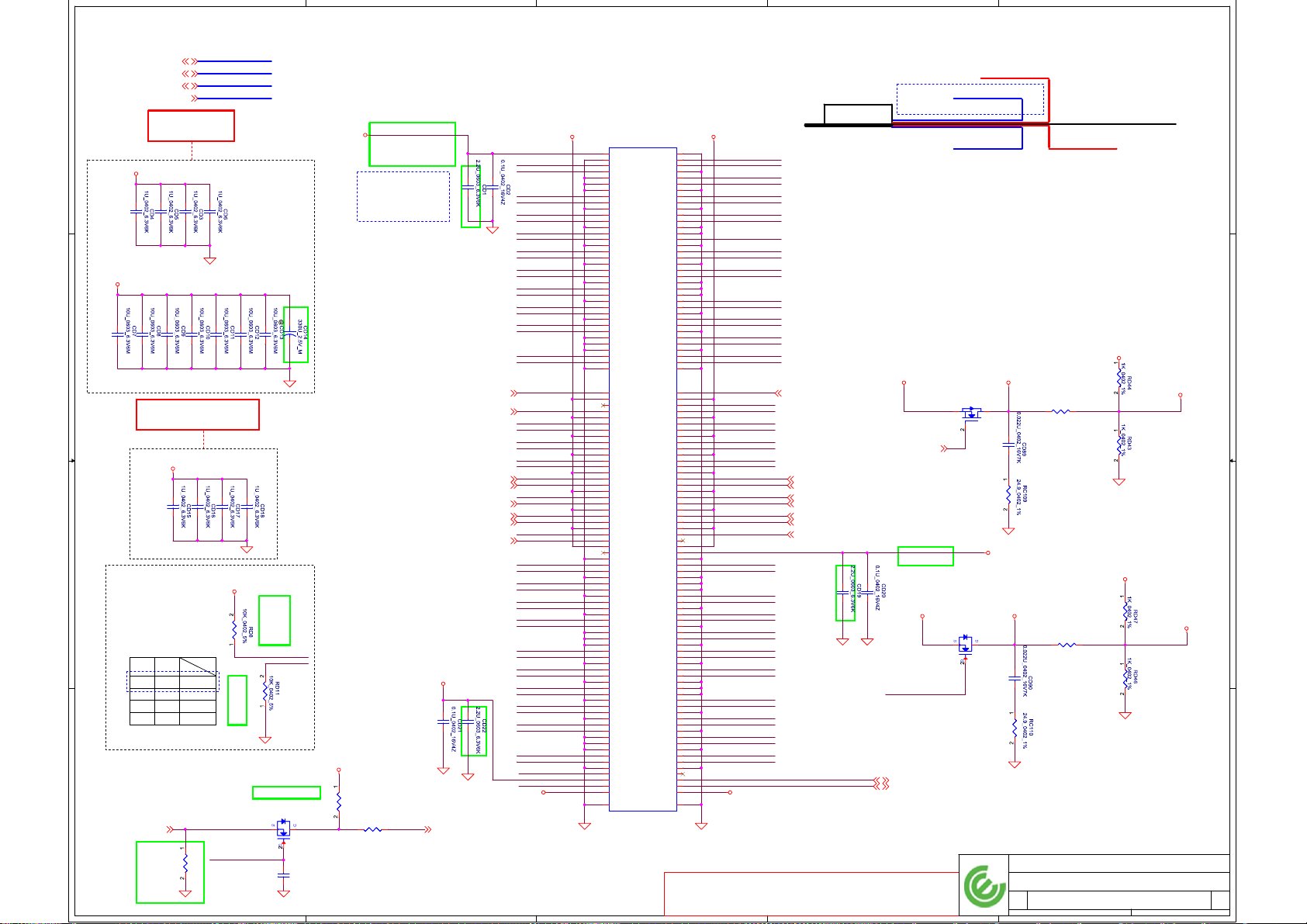

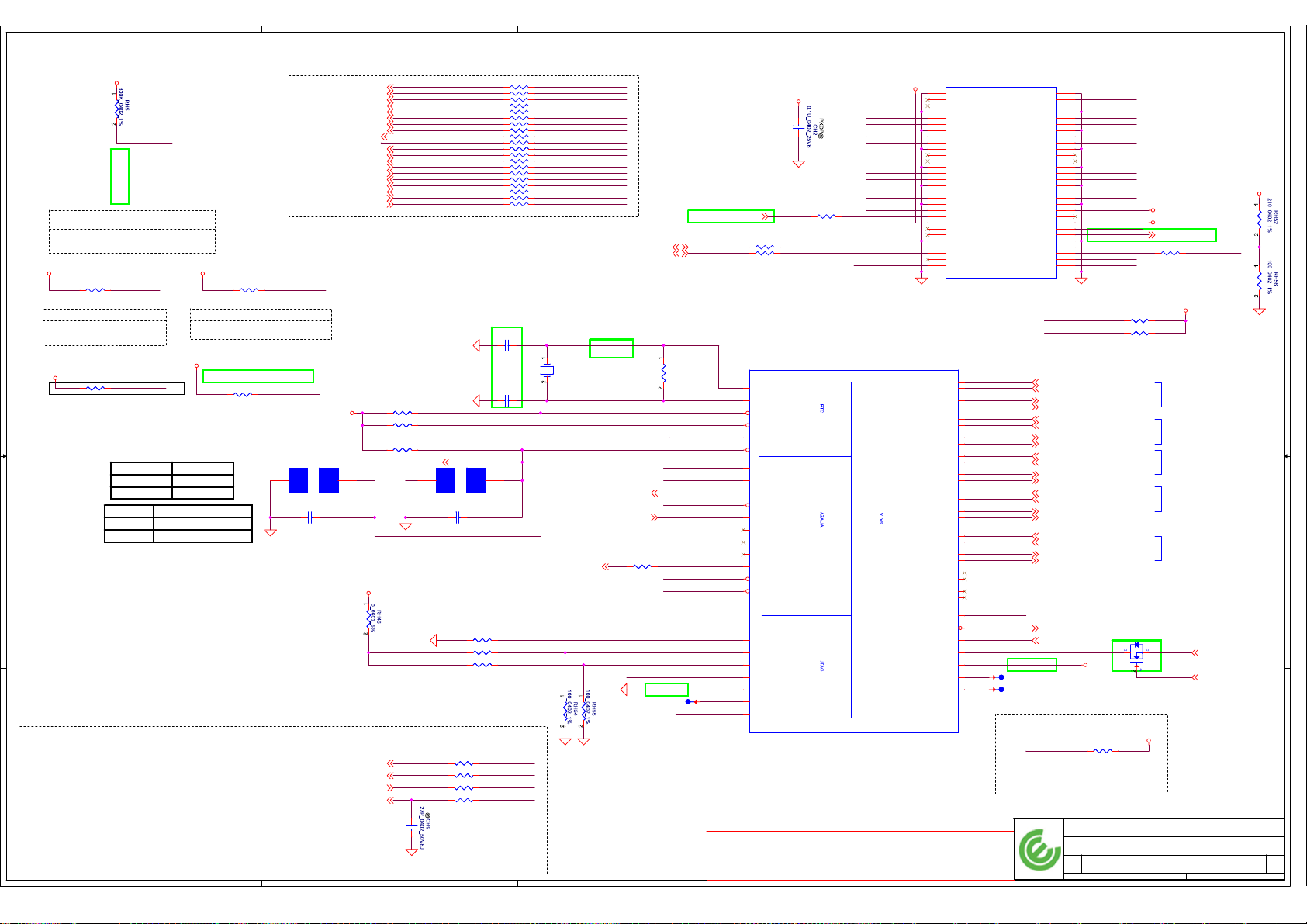

Block Diagram

IO/B

Intel Clarkville

I217LM

P38

LAN SWITCH

PI3L720

P38

RJ45

P39

DAI

USB2.0 [3,6]

SATA[2]

DOCK LAN

USB3.0 [3]

LPC

A B C D E

65

Date: Tuesda y, January 15, 2013

Sheet 2

of

TP CONN

KB CONN

P51

P48

CPU FAN

P27

Thermal

EMC4021

P27

on IO/B

DAI

To Docking side

IO/B

Dig. MIC

Through LVDS Cable

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Title

Block Diagram

Size Docume nt Number

LA-9771P

(DDR3L)

Memory BUS Dual Channel

1333/1600 MHz (XMP 1866MHz)

eDP

PEG x16(Gen3)

eDP to LVDS

(RTD2136S)

P2

DP_D

MXM CONN

TYPE A

DP_A

LVDS CONN

P30

eDP PWR CONN

P30

DP 1.2 CONN

P31

HDMI 1.4a

CONN

P35

DPB

LVDS MUX

(TS3DV20812)

P29

dEDP

DP Redriver

PS8330B

P31

dLVDS

DP

204pin DDRIII SO-DIMM x4

P13~P16

OC : 1866 MHz

Intel

HasWell

rPGA CPU

947 Pins

FDI

LANEX4

Intel

Lynx Point

BGA

695 Pins

1

2

3

4

1

2

3

4

Rev

0.2

USB2.0[0]

USB3.0 Conn Right Side

USB Charger

P41

DP_D

PCIE(8]

USB3.0[1]

USB3.0[2]

USB3.0[5]

USB3.0[6]

USB3.0 Repeater

(PS8723B)

P41

USB3.0 Repeater

(PS8723B)

P6-12

DMI

LANEX8

P18-26

DP

DP/HDMI DeMUX DP MUX

PS8339B

P35

PS8331

P34

DP

USB2.0[1] USB2.0[2]

USB3.0 Conn Left Side.

USB3.0 Conn Left Side.

DP

iGPU DP

DOCKING

DPA

P46

Dock CRT

VGA Switch

G3212RG1U

P32

SDXC/MMC

PCIE

USB2.0

USB2.0[9]

CRT

CRT CONN

P32

USB2.0[11]

USB2.0[12]

PCIE[7]

HD Audio I/F

HDD Conn

P36

FFS

LNG3DM

P36

BT module

Through LVDS Cable

SATA[3]

Card Reader

OZ777FJ2LN

IO/B

USH

BCM5882

PCIE[6]

PCIE[7]

SATA[4] PCIE[1]

PCIE[3]

Mini Card-3

EXPRESS

PCIE/SATA Repeater

Mini Card-1

PP

Card

(ASM1467)

WLAN/WiGi

P43

P44

P43

DOCK LAN

To Docking side

W25Q64FVSSIQ

P21

64M 4K sector

W25Q32FVSSIQ

P21

32M 4K sector

Discrete TPM

AT97SC3204

P42

USB / eSATA Conn.

P40

USB2.0[8]

ODD Conn.

P.37

HDA Codec

ALC 3226

IO/B

USB2.0[10]

USB2.0[4]

RFID

TDA8034HN

Smart Card

Fingerprint

CONN

SMSC SIO

MEC5048

USB2.0[5]

P7

P18

on wireless board

P52

GPU FAN

P27

INT.Speaker

Array MIC Jack

Headphone Jack

FP_USB USB2.0[7]

USH Module

BC BUS

SMSC KBC

MEC5075

8

BDBIOS.COM

PROPRIETARY NOTE:

THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC

. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DE LL

. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

(Co_LAY 5055)

P49

SIM Card

P44

LED

P50

SLGC55594AVTR USB

Power Share

P41

P17

iVGA

DP_B DP_C

USB3.0 Conn Right Side

P41

BT 4.0+LE

P51

Digital Camera

P30

Mini Card-2

WWAN/GPS

mSATA

P44

CPU XDP Port

PCH XDP Port

WiFi ON/OFF

DC/DC Interface

State

S0

ON

ON

ON

S3

ON

ON

OFF

S5 S4/AC

ON

OFF

OFF

S5 S4/AC don't exist

OFF

OFF

OFF

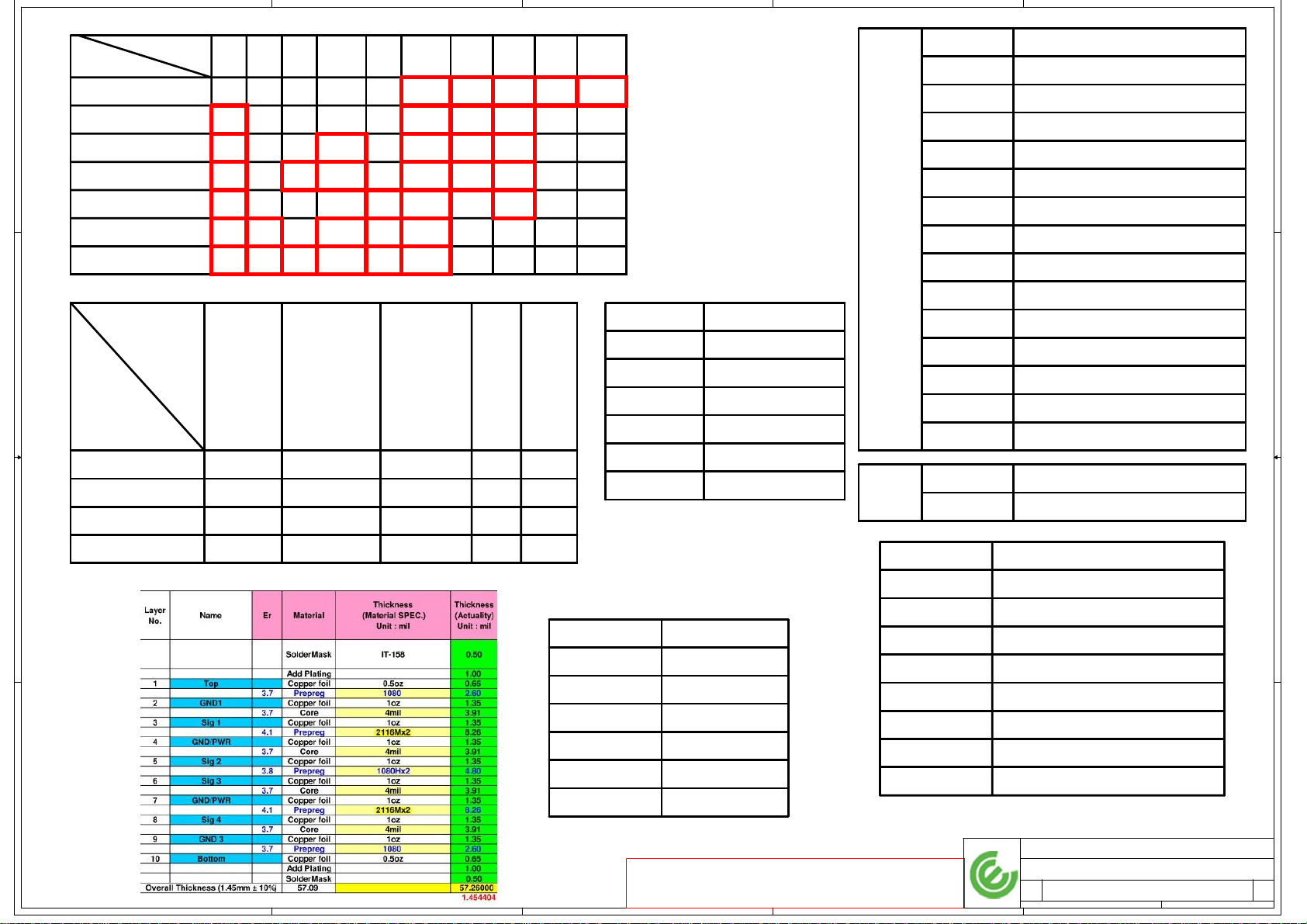

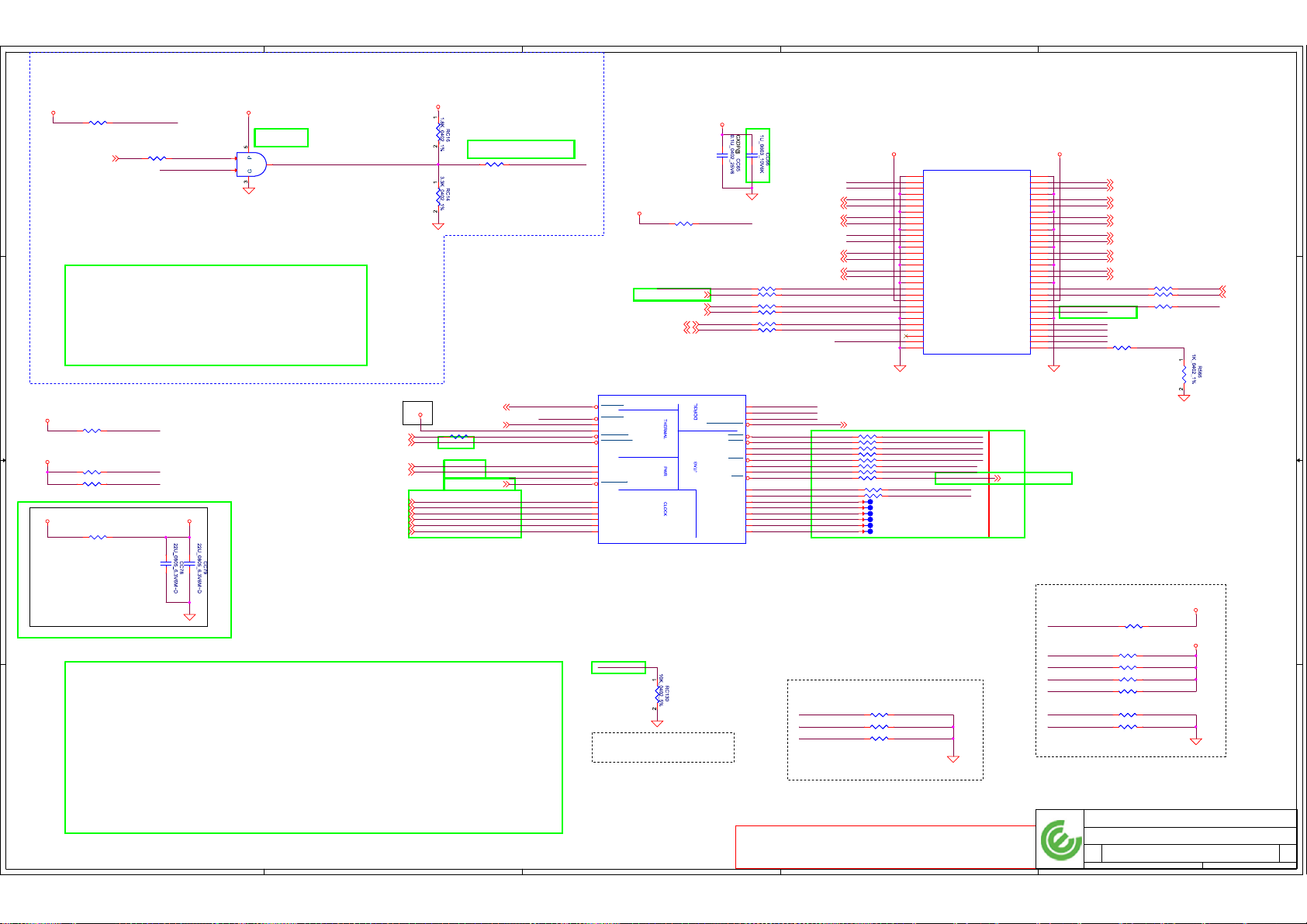

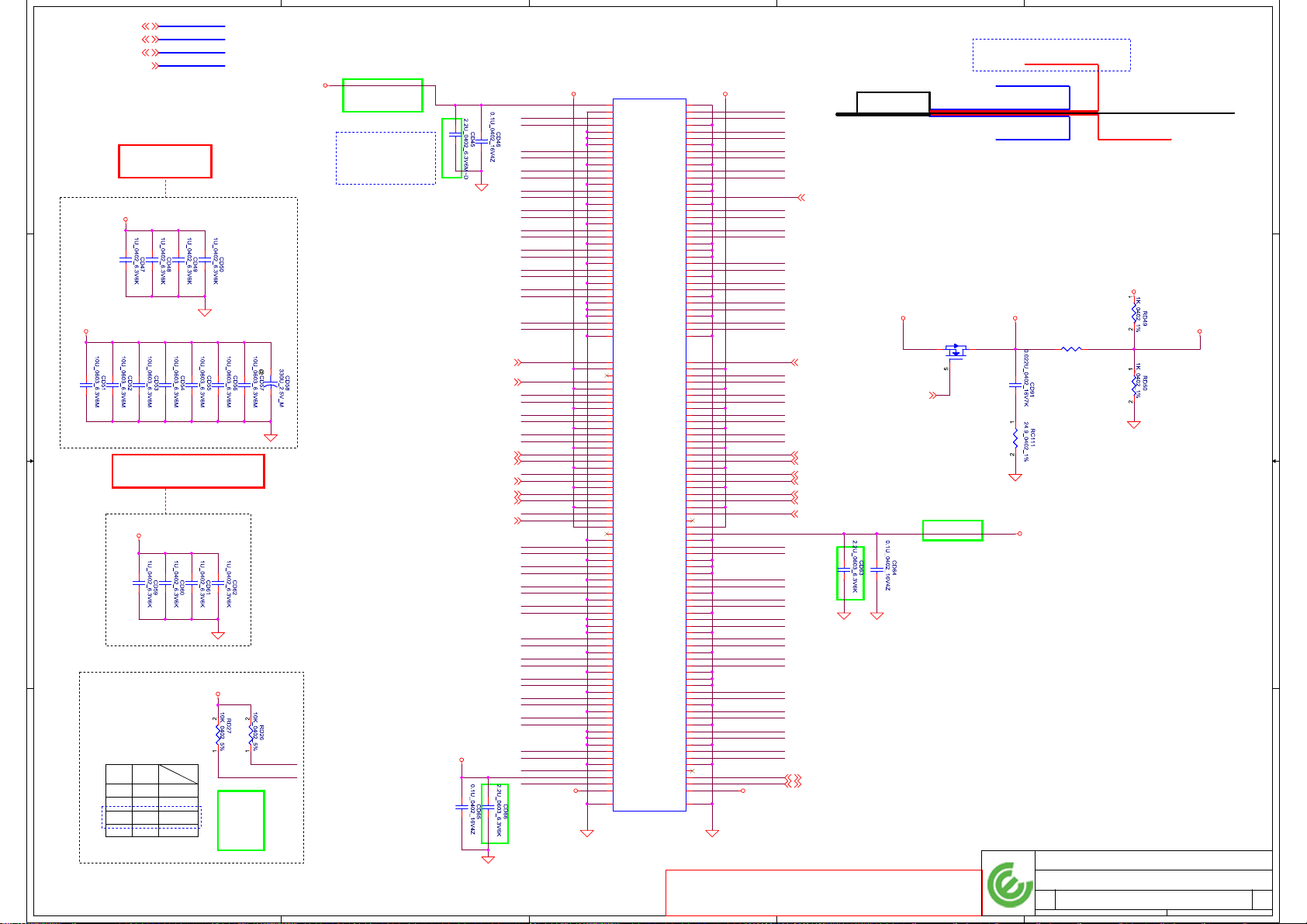

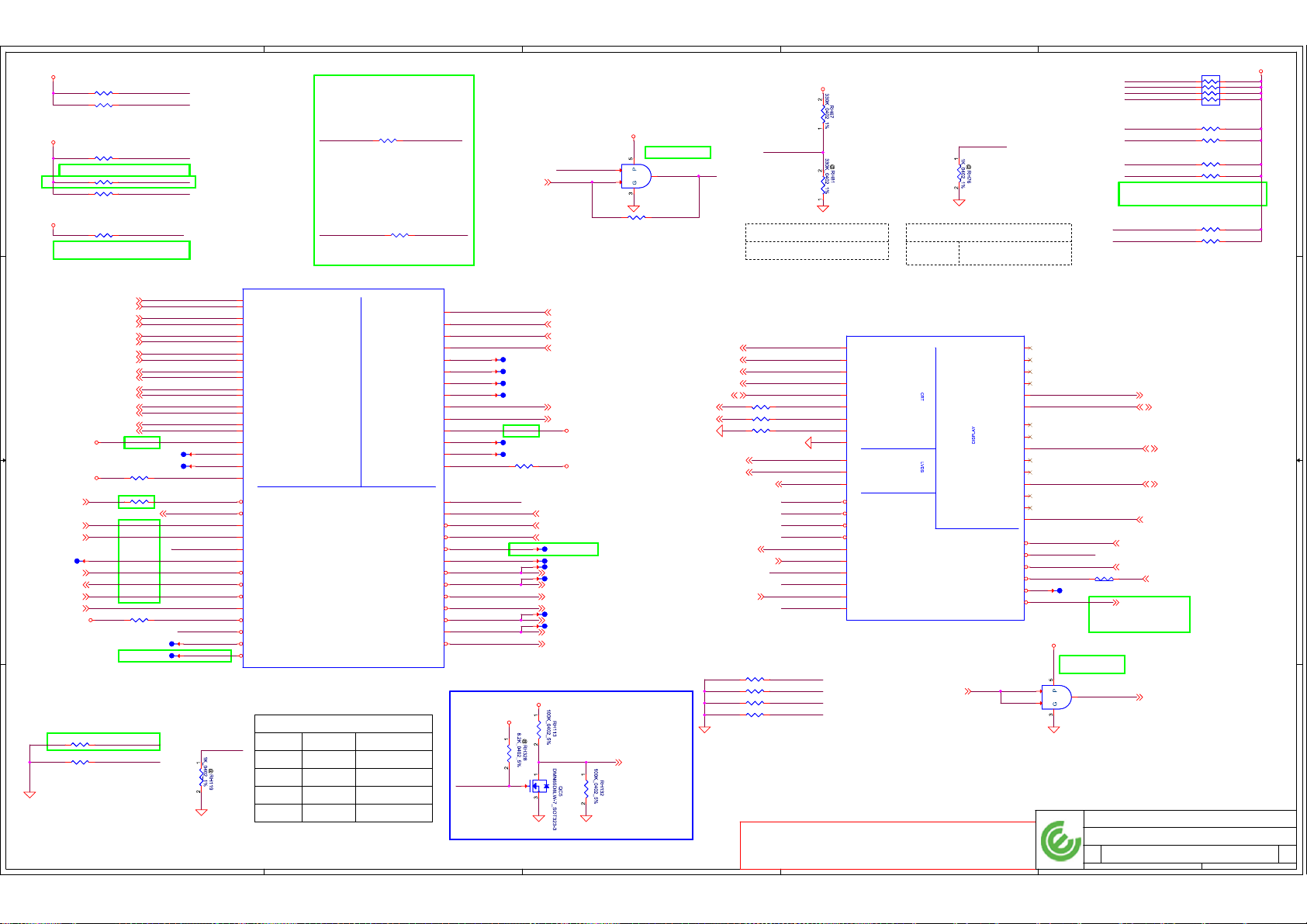

Stack up

5 4

+5V_ALW

+3.3V_SUS

+5V_RUN

+3.3V_ALW2 +1.35V_MEM

+3.3V_RUN

+3.3V_ALW

+1.5V_RUN

+3.3V_ALW_PCH

+0.675V_DDR_VTT

+3.3V_RTC_LDO

+VCC_CORE

+1.05V_RUN

5 4 3 2 1

POWER STATES

USB PORT#

DESTINATION

0

JUSB1 (Ext Right Side)

1

JUSB2 (Ext Right Side)

2

IO Board- JUSB1 (Ext Left Side)

3

Docking USB3.0

4

WLAN/WIGIG

5

WWAN/GPS/LTE/UWB/mSATA

PCH

6

Docking USB 2.0

7

USH

8

ESATA

9

IO Board- JUSB2 (Ext Left Side)

10 Express Card

11

NA

12

Carmera

13

NA

0

BIO

USH

1

NA

PCI EXPRESS

DESTINATION

Signal

SLP SLP SLP S4

SLP ALWAYS M

SUS RUN

S3# S4# S5# STATE# M# PLANE PLANE PLANE PLANE

CLOCKS

ON

OFF

OFF

OFF

OFF

OFF

OFF

USB3.0 PORT

DESTINATION

State

S0 (Full ON) / M0

S3 (Suspend to RAM) / M1

S4 (Suspend to DISK) / M1

S5 (SOFT OFF) / M1

S3 (Suspend to RAM) / M-OFF

S4 (Suspend to DISK) / M-OFF

S5 (SOFT OFF) / M-OFF

PM TABLE

HIGH

HIGH

HIGH HIGH

HIGH ON

ON

ON

ON

LOW HIGH HIGH HIGH HIGH ON

ON ON OFF

LOW LOW HIGH LOW HIGH ON

ON OFF OFF

LOW LOW LOW LOW HIGH ON

ON OFF OFF

LOW HIGH HIGH HIGH LOW ON

OFF ON OFF

LOW LOW

HIGH

LOW LOW ON

OFF OFF OFF

LOW LOW LOW LOW LOW ON

OFF OFF OFF

D

C

B

A

D

C

B

A

+3.3V_M +3.3V_M

+1.05V_M +1.05V_M

(M-OFF)

1

2

3

4

5

6

JUSB1 (Ext Right Side)

JUSB2 (Ext Right Side)

Dock

NA(define PCIE_2)

IO/B- JUSB1(Ext Left Side)

IO/B- JUSB2(Ext Left Side)

power

plane

ON

OFF

OFF

OFF

ON

ON

ON

OFF

Lane 1

Lane 2

Lane 3

Lane 4

Lane 5

Lane 6

Lane 7

Lane 8

mSATA/WWAN

10/100/1G LOM

MINI CARD-2 (WLAN)

NA

NA

NA

EXPRESS CARD

MMI(Card reader)

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Title

Index and Config.

SATA DESTINATION

SATA 0

HDD1

SATA 1

ODD

SATA 2

Dock

SATA 3 ESATA

SATA 4 mSATA

SATA 5

NA

Date: Tuesday January 15 2013 Sheet 3 of

2 1

Size Document Number

Rev

0.2

65

LA-9771P

,

,

BDBIOS.COM

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFOR MATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATI ON IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

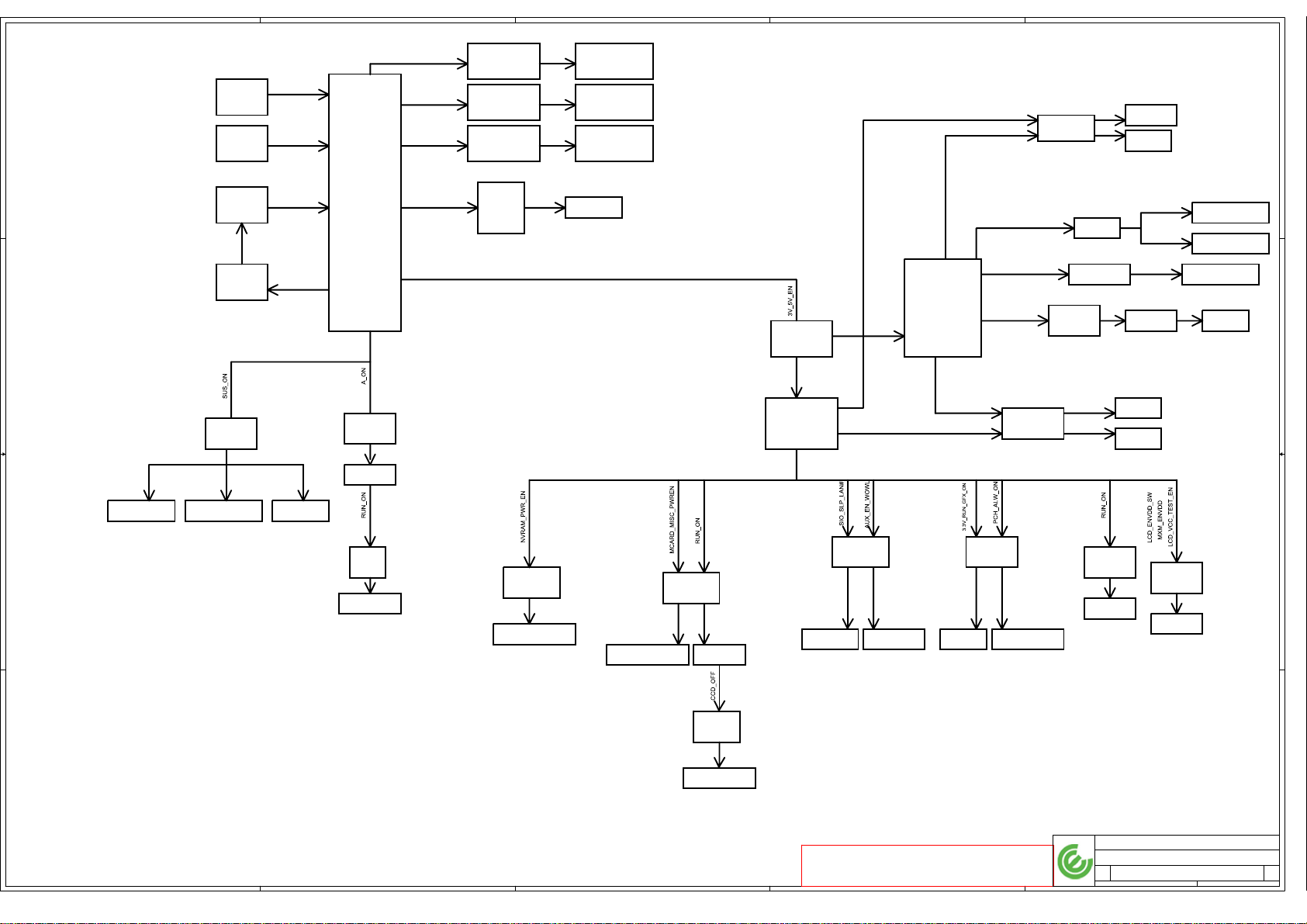

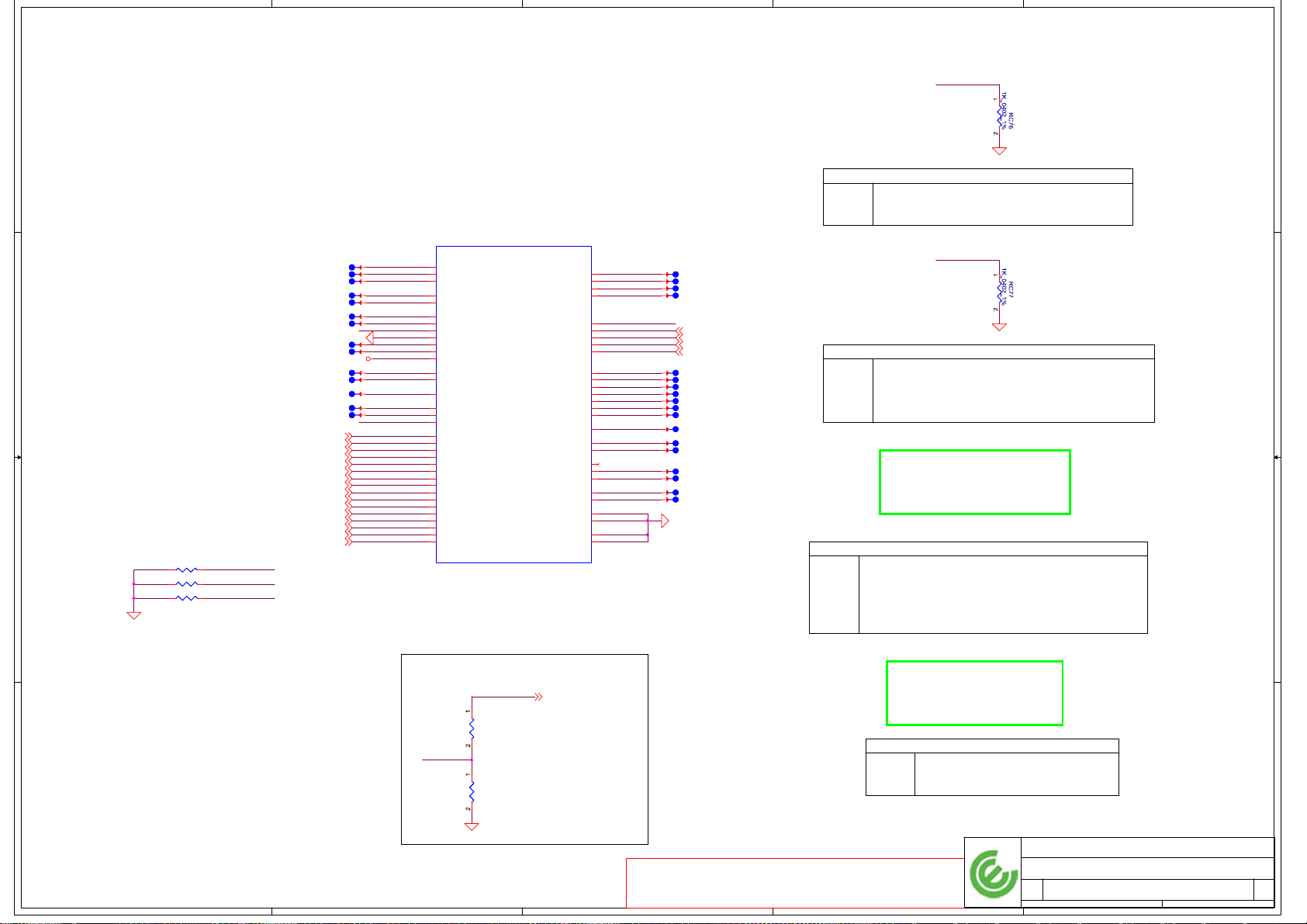

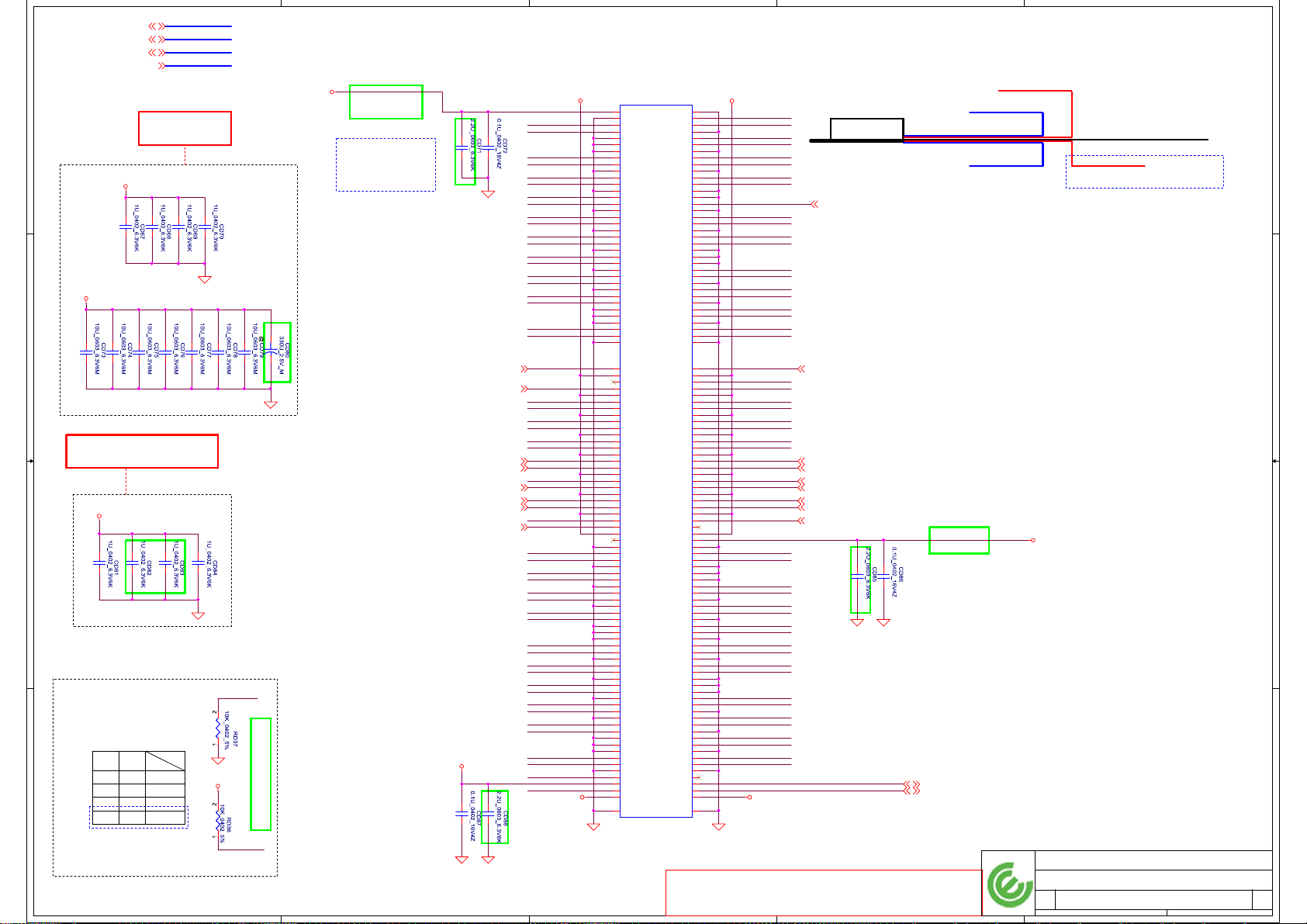

Docki/;PB

D

ADAPTER

BATTERY

CHARGER

C

RT8207

(PU200)

+V_DDR_REF +0.675V_DDR_VTT +1.35V_MEM

B

A

+5V_USB_PWR1

+5V_USB_PWR2

+5V_ESATA_PWR

Size Document Number

LA-9771P

Date: Tuesday, January 15, 201 3 Sheet 4 of

Rev

0.2

65

5 4

3

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Title

Power Rail

+3.3V_SUS

+5V_MOD

PWR_ SHARE_EN#

USB_SID E_EN#

D

C

B

A

2 1

+PWR_SRC_S

+BL_PWR_SRC

SUS_ON

MODC_EN

+MXM_PWR_SRC

+VCC_CORE

TP0610K

(PQ4)

FDC654P

(Q21)

SI4835DDY

(Q186)

ISL95812

(PU500)

TPS22965

(U43)

PCH_ALW_ON

EN_INVPW R

3.3V_RUN_GFX_ON

+PWR_SRC

IMVP_VR_ON

TPS51212

(PU300)

+1.05V_M

SI4164

(Q63)

+1.05V_RUN

TPS2560

(U45)

TPS2560

(U48)

5 4 3 2 1

+3.3V_PCIE_WWAN

TPS22966

(U56)

+3.3V_LAN +3.3V_WLAN +3V_MXM +3.3V_ALW_PCH

+3.3V_PCIE_FLASH +3.3V_RUN

PMV65XP

(Q24)

+CAMERA_VDD

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS W RITTEN CONSENT.

BDBIOS.COM

TPS22966

(U57)

ESATA_USB_PW R_EN#

TPS22965

(U62)

+LCDVDD

for LVDS/ED P pane l

SYN470D

(PU400)

+1.5V_RUN

TPS22966

(U34)

+5V_RUN

+5V_HDD

+5V_MXM

+3.3V_M

TPS51225

(PU101)

+3.3V_ALW

TPS22966

(U63)

RUN_ON

TPS22965

(U37)

+5V_ALW

TPS22966

(U35)

3.3V_RUN_GFX_ON

A_ON

+3.3V_ALW_PCH

2.2K

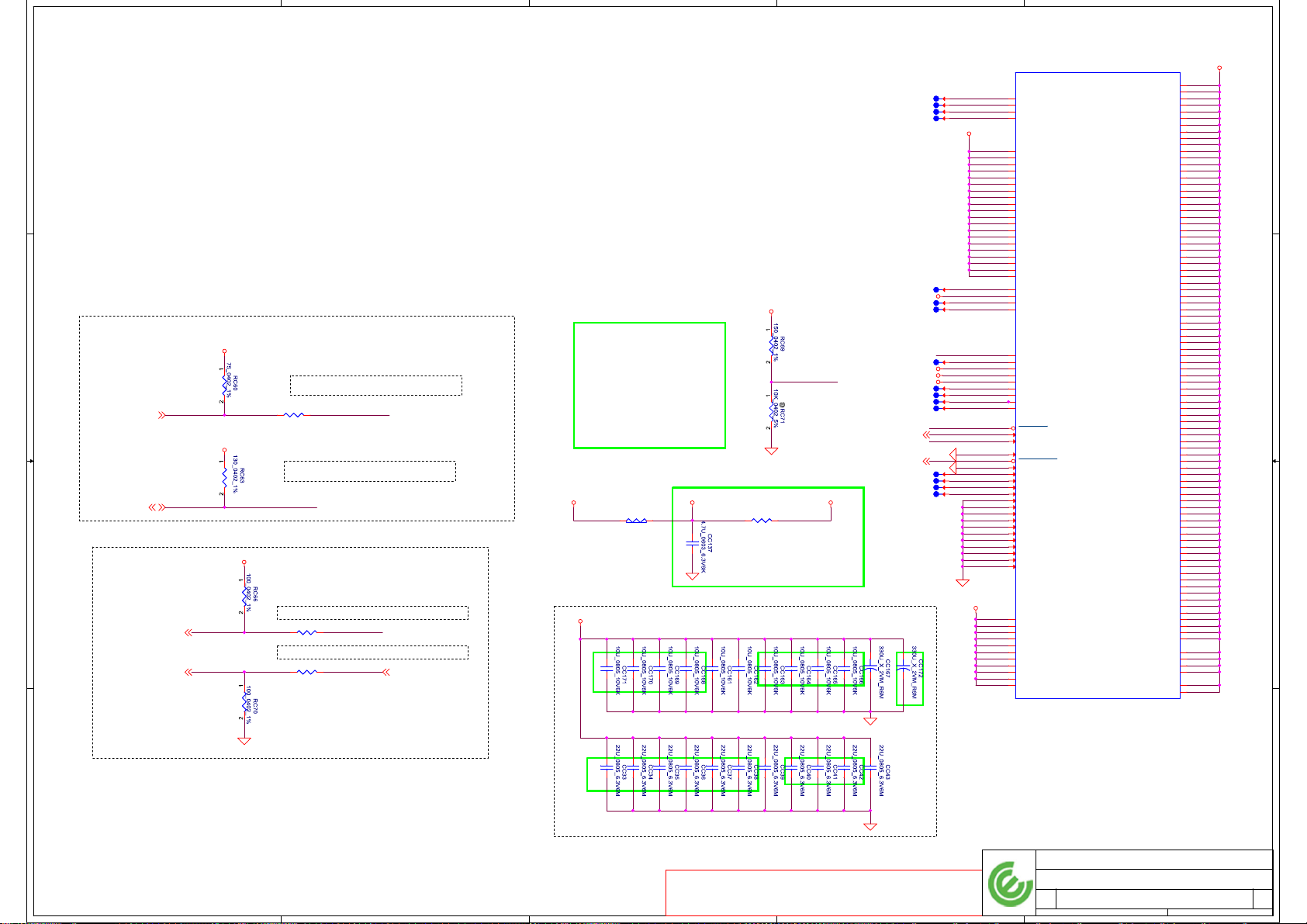

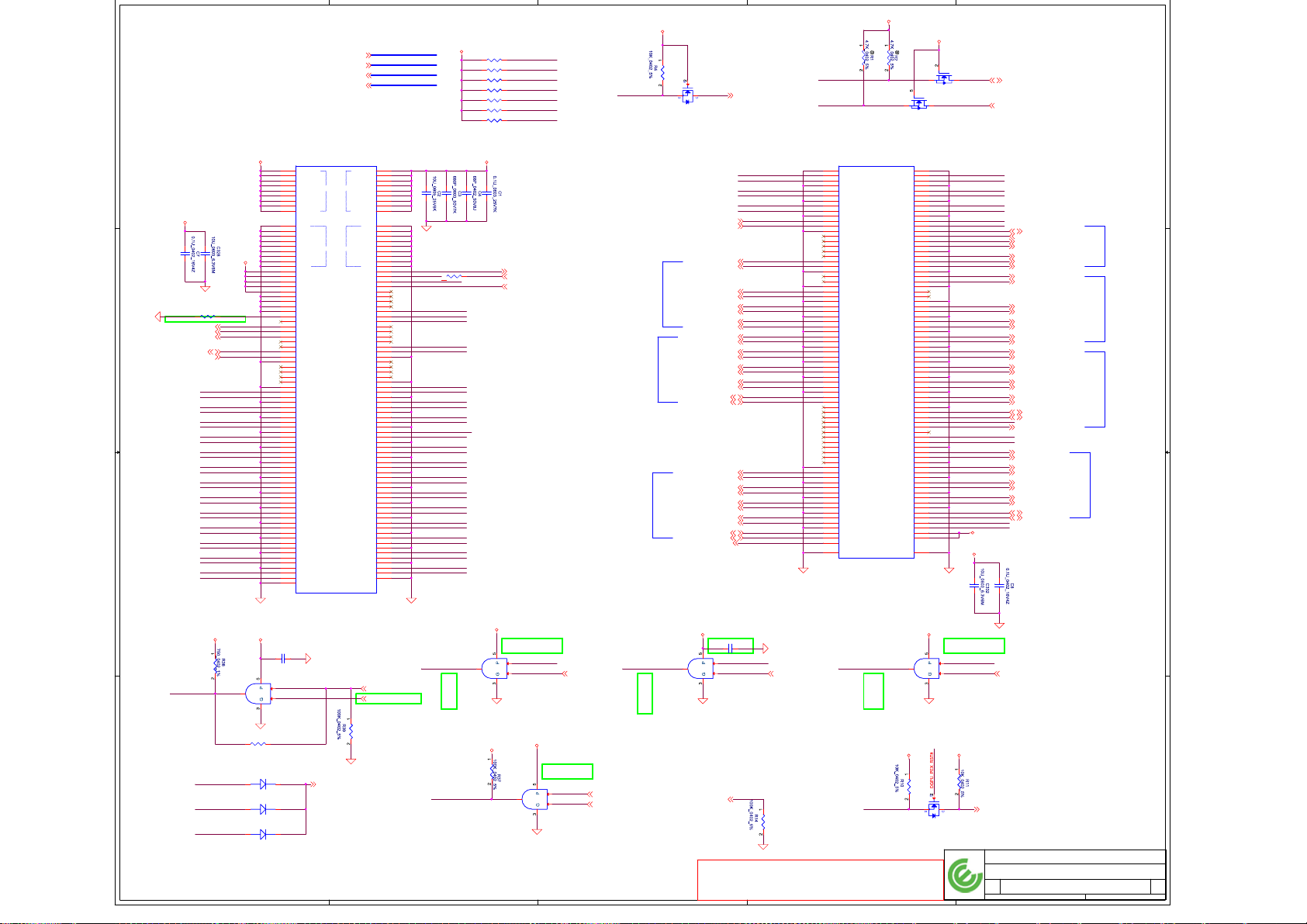

DOCK_SMB_CLK

DOCK_SMB_DAT

LCD_SMBCLK

LCD_SMDATA

PBAT_SMBCLK

PBAT SMBDAT

USH_SMBCLK

USH_SMBDAT

CARD SMBCLK

CARD SMBDAT

CHARGER_SMBCLK

CHARGER_SMBDAT

GPU_SMBCLK

GPU_SMBDAT

5

4

3

2

1

2.2K

2.2K

2.2K

2.2K

2.2K

2.2K

2@ 2.2K

2@ 2.2K

2.2K

2.2K

2.2K

2.2K

2.2K

2.2K

2.2K

2.2K

2.2K

2.2K

SMBUS Address [0x9a]

R10

U11

PCH

U8

R7

N11 K6

+3.3V_ALW_PCH

2N7002

2N7002

+3.3V_LAN

28

MEM_SMBCLK

MEM_SMBDATA

LAN_SMBCLK

LAN_SMBDATA

202

200

202

200

202

200

202

200

53

51

53

51

30

32

13

14

SMBUS Address [A0h]

A0h --> 1010 0000

SMBUS Address [A0h]

A0h --> 1010 0000

SMBUS Address [A4h]

A4h --> 1010 0100

SMBUS Address [A4h]

A4h --> 1010 0100

SMBUS Address [TBD]

SMBUS Address [TBD]

SMBUS Address [TBD]

SMBUS Address [TBD]

DIMMA

DIMMB

DIMMC

DIMMD

XDP1

XDP2

WWAN

RTD2136S

D

C

B

A

D

SMBUS Address

SMB_ADM1032: 0x98

SMB_DIAG_DUMP: 0x04

SMB_DIAG_DUMP2: 0x05

SMB_BLACKTOP: 0x60

C

B

A

SMBUS Address [C8]

31

LOM

2.2K

SML1_SMBDATA

SML1_SMBCLK

A5 B6

1D 1D

B4

+3.3V_ALW

+3.3V_ALW

2@ DMN66

2@ DMN66

+3.3V_ALW

100 ohm

100 ohm

+3.3V_SUS

+3.3V_ALW

+3.3V_ALW

10

9

+3.3V_RUN

SMBUS Address

APR_EC: 0x48

SPR_EC: 0x70

MSLICE_EC: 0x72

USB: 0x59

AUDIO: 0x34

SLICE_BATTERY: 0x17

SLICE_CHARGER: 0x13

+LCDVDD

127

129

7

1A

1A

1B

1B

KBC

1C

1C

1E

1E

MEC 5075

1F

1F

1G

1G

2A

2A

1H

1H

DOCKING

@2.2K

@2.2K

A3

B5

A4

A56

B59

A50

B53

A49

B52

B50

A47

A7

B7

19

18

EDP

6

BATTERY

CONN

M9

SMBUS Address [0x16]

SMBUS Address [TBD]

L9

7

8

Charger

2N7002

2N7002

USH

Express card

SMBUS Address [TBD]

SMBUS Address [0xFF]

68

MXM

SMBUS Address [TBD]

70

BDBIOS.COM

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Title

SMBUS Bolck Diagram

Size Document Num ber

LA-9771P

Rev

0.2

Date: Tuesday, January 15, 2013 Sheet 5 of

65

5

4

3

2

1

_

_

_

PROPRIETARY NOT E: THIS SHE ET OF ENGINEE RING DRAW ING AND SPECIFI CATIONS CONTAINS CON FIDENTIA L

TRADE SECRET AND OTHER PROPRIETAR Y INFORMA TION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS W RITTEN AUT HORIZATI ON OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

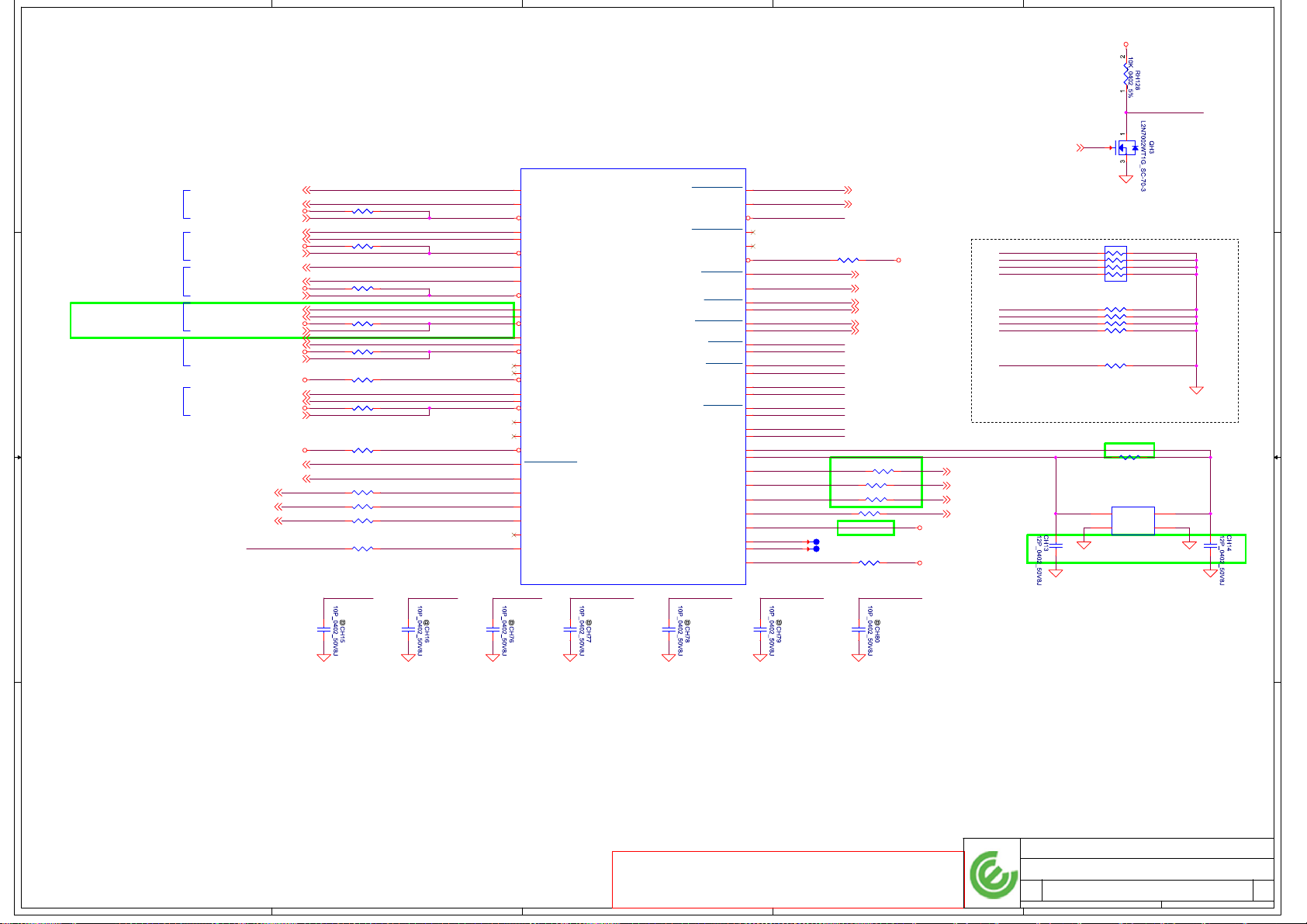

PEG_CRX_GTX_C_P[0..15] <17>

PEG_CRX_GTX_C_N[0..15] <17>

PEG_CTX_GRX_P[0..15] <17>

PEG_CTX_GRX_N[0..15] <17>

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Title

Haswell (1/7)

F29PEG_CRX_GTX_P7

E28PEG CRX GTX P6

F31PEG CRX GTX P5

E30PEG CRX GTX P4

F35PEG CRX GTX P3

E34PEG CRX GTX P2

F33PEG CRX GTX P1

D32PEG CRX GTX P0

4

Date: Tuesday, January 15, 2013 Sheet 6 of

2 1

Rev

0.2

65

Size Document Number

LA-9771P

H35PEG CTX GRX C N15 CC44 2

H34PEG_CTX_GRX_C_N14 CC45 2

J33PEG CTX GRX C N13

2

H32PEG_CTX_GRX_C_N12 CC73 2

J31PEG CTX GRX C N11 CC46 2

G30PEG_CTX_GRX_C_N10 CC74 2

C33PEG CTX GRX C N9 CC47 2

B32PEG_CTX_GRX_C_N8

2

B31PEG CTX GRX C N7 CC75 2

A30PEG CTX GRX C N6 CC48 2

B29PEG CTX GRX C N5 CC59 2

A28PEG CTX GRX C N4 CC76 2

B27PEG CTX GRX C N3

2

A26PEG CTX GRX C N2 CC62 2

B25PEG CTX GRX C N1 CC77 2

A24PEG CTX GRX C N0 CC50 2

J35PEG_CTX_GRX_C_P15 CC67 2

G34PEG CTX GRX C P14

2

H33PEG_CTX_GRX_C_P13 CC51 2

G32PEG CTX GRX C P12 CC52 2

H31PEG CTX GRX C P11 CC69 2

H30PEG CTX GRX C P10 CC54 2

B33PEG CTX GRX C P9

2

A32PEG CTX GRX C P8 CC70 2

C31PEG CTX GRX C P7 CC57 2

B30PEG CTX GRX C P6 CC58 2

C29PEG CTX GRX C P5 CC71 2

B28PEG CTX GRX C P4

2

C27PEG CTX GRX C P3 CC61 2

B26PEG CTX GRX C P2 CC72 2

C25PEG CTX GRX C P1 CC63 2

B24PEG_CTX_GRX_C_P0 CC64 2

L29PEG CRX GTX P15 CC17 2

L28PEG CRX GTX P14 CC18 2

L31PEG CRX GTX P13 CC19 2

K30PEG CRX GTX P12

2

L33PEG CRX GTX P11

K32PEG CRX GTX P10 CC22 2

L35PEG_CRX_GTX_P9

K34PEG CRX GTX P8

PEG_RCOMP

PEG_RXN_0

DMI_RXN _0 PEG_RXN_1

DMI_RXN _1 PEG_RXN_2

DMI_RXN _2 PEG_RXN_3

DMI_RXN _3 PEG_RXN_4

PEG_RXN_5

DMI_RXP_0 PEG_RXN_6

DMI_RXP_1 PEG_RXN_7

DMI_RXP_2 PEG_RXN_8

DMI_RXP_3 PEG_RXN_9

PEG_RXN_10

DMI_TXN_0 PEG_RXN_11

DMI_TXN_1 PEG_RXN_12

DMI_TXN_2 PEG_RXN_13

DMI_TXN_3 PEG_RXN_14

PEG_RXN_15

DMI_TXP_0 PEG_RXP_0

DMI_TXP_1 PEG_RXP_1

DMI_TXP_2 PEG_RXP_2

DMI_TXP_3 PEG_RXP_3

PEG_RXP_4

PEG_RXP_5

PEG_RXP_6

PEG_RXP_7

PEG_RXP_8

FDI_CSYNC PEG_RXP_9

DISP_INT PEG_RXP_10

PEG_RXP_11

PEG_RXP_12

PEG_RXP_13

PEG_RXP_14

PEG_RXP_15

PEG_TXN_0

PEG_TXN_1

PEG_TXN_2

PEG_TXN_3

PEG_TXN_4

PEG_TXN_5

PEG_TXN_6

PEG_TXN_7

PEG_TXN_8

PEG_TXN_9

PEG_TXN_10

PEG_TXN_11

PEG_TXN_12

PEG_TXN_13

PEG_TXN_14

PEG_TXN_15

PEG_TXP_0

PEG_TXP_1

PEG_TXP_2

PEG_TXP_3

PEG_TXP_4

PEG_TXP_5

PEG_TXP_6

PEG_TXP_7

PEG_TXP_8

PEG_TXP_9

PEG_TXP_10

PEG_TXP_11

PEG_TXP_12

PEG_TXP_13

PEG_TXP_14

PEG_TXP_15

1 OF 9

CONN@

CPU socket Reverse type.

5

D

C

B

A

5

4 3 2 1

+VCOMP_OUT

D

C

B

A

PEG COMP

2 1

PEG CRX GTX C P[0..15]

PEG CRX GTX C N[0..15]

PEG CTX GRX P[0..15]

PEG CTX GRX N[0..15]

1 0.22U 0402 16V7K PEG CRX GTX C N15

1 0 22U 0402 16V7K PEG CRX GTX C N14

1 0.22U 0402 16V7K PEG CRX GTX C N13

1 0 22U 0402 16V7K PEG CRX GTX C N12

1 0.22U 0402 16V7K PEG CRX GTX C N11

1 0 22U 0402 16V7K PEG CRX GTX C N10

1 0.22U 0402 16V7K PEG CRX GT X C N9

1 0.22U 0402 16V7K PEG_CRX_GTX_C_N8

1 0.22U 0402 16V7K PEG CRX GT X C N7

1 0.22U 0402 16V7K PEG_CRX_GTX_C_N6

1 0.22U 0402 16V7K PEG CRX GT X C N5

1 0.22U 0402 16V7K PEG CRX GT X C N4

1 0.22U 0402 16V7K PEG CRX GT X C N3

1 0.22U 0402 16V7K PEG CRX GT X C N2

1 0 22U 0402 16V7K PEG CRX GTX C N1

1 0.22U 0402 16V7K PEG CRX GT X C N0

1 0.22U_0402_16V7K PEG_CRX_GTX_C_P15

1 0.22U_0402_16V7K PEG_CRX_GTX_C_P14

1 0.22U_0402_16V7K PEG_CRX_GTX_C_P13

1 0.22U_0402_16V7K PEG_CRX_GTX_C_P12

1 0.22U_0402_16V7K PEG_CRX_GTX_C_P11

1 0.22U_0402_16V7K PEG_CRX_GTX_C_P10

1 0.22U 0402 16V7K PEG_CRX_GTX_C_P9

1 0.22U 0402 16V7K PEG CRX GTX C P8

1 0.22U 0402 16V7K PEG_CRX_GTX_C_P7

1 0.22U 0402 16V7K PEG CRX GTX C P6

1 0.22U 0402 16V7K PEG CRX GTX C P5

1 0 22U 0402 16V7K PEG CRX GTX C P4

1 0.22U 0402 16V7K PEG CRX GTX C P3

1 0 22U 0402 16V7K PEG CRX GTX C P2

1 0.22U 0402 16V7K PEG CRX GTX C P1

1 0 22U 0402 16V7K PEG CRX GTX C P0

1 0.22U 0402 16V7K PEG CTX GRX N15

1 0.22U 0402 16V7K PEG_CTX_GRX_N14

1 0.22U 0402 16V7K PEG CTX GRX N13

1 0.22U 0402 16V7K PEG_CTX_GRX_N12

1 0.22U 0402 16V7K PEG CTX GRX N11

1 0.22U 0402 16V7K PEG_CTX_GRX_N10

1 0.22U 0402 16V7K PEG CTX GRX N9

1 0.22U 0402 16V7K PEG_CTX_GRX_N8

1 0.22U 0402 16V7K PEG CTX GRX N7

1 0.22U 0402 16V7K PEG CTX GRX N6

1 0 22U 0402 16V7K PEG CT X GRX N5

1 0.22U 0402 16V7K PEG CTX GRX N4

1 0 22U 0402 16V7K PEG CT X GRX N3

1 0.22U 0402 16V7K PEG CTX GRX N2

1 0 22U 0402 16V7K PEG CT X GRX N1

1 0.22U 0402 16V7K PEG CTX GRX N0

1 0.22U 0402 16V7K PEG_CTX_GRX_P15

1 0.22U 0402 16V7K PEG CTX GRX P14

1 0.22U 0402 16V7K PEG_CTX_GRX_P13

1 0.22U 0402 16V7K PEG CTX GRX P12

1 0.22U 0402 16V7K PEG CTX GRX P11

1 0.22U 0402 16V7K PEG CTX GRX P10

1 0.22U 0402 16V7K PEG CTX GRX P9

1 0.22U 0402 16V7K PEG CTX GRX P8

1 0.22U 0402 16V7K PEG CTX GRX P7

1 0 22U 0402 16V7K PEG CTX GRX P6

1 0.22U 0402 16V7K PEG CTX GRX P5

1 0 22U 0402 16V7K PEG CTX GRX P4

1 0.22U 0402 16V7K PEG CTX GRX P3

1 0 22U 0402 16V7K PEG CTX GRX P2

1 0.22U 0402 16V7K PEG CTX GRX P1

1 0.22U 0402 16V7K PEG_CTX_GRX_P0

24.9_0402_1% RC2

CAD Note:

Trace width=12 mils ,Spacing=15mil

Max length= 400 mils.

Haswell rPGA EDS

JCPU1A

E23

PEG COMP

M29PEG CRX GTX N15 CC1

2

K28PEG CRX GTX N14 CC2

2

M31PEG CRX GTX N13 CC3

2

L30PEG CRX GTX N12 CC4

2

D21

C21

B21

A21

D20

C20

B20

A20

D18

C17

B17

A17

D17

C18

B18

A18

H29

J29

DMI CRX PTX N0

DMI CRX PTX N1

DMI CRX PTX N2

DMI CRX PTX N3

DMI CRX PTX P0

DMI_CRX_PTX_P1

DMI CRX PTX P2

DMI_CRX_PTX_P3

DMI CTX PRX N0

DMI CTX PRX N1

DMI CTX PRX N2

DMI CTX PRX N3

DMI CTX PRX P0

DMI CTX PRX P1

DMI CTX PRX P2

DMI CTX PRX P3

11/21

<19> DMI_CRX_PT X_N0

<19> DMI_CRX_PT X_N1

<19> DMI_CRX_PT X_N2

<19> DMI_CRX_PT X_N3

<19> DMI_CRX_PTX_P0

<19> DMI_CRX_PTX_P1

<19> DMI_CRX_PTX_P2

<19> DMI_CRX_PTX_P3

<19> DMI_CTX_PRX_N0

<19> DMI_CTX_PRX_N1

<19> DMI_CTX_PRX_N2

<19> DMI_CTX_PRX_N3

<19> DMI_CTX_PRX_P0

<19> DMI_CTX_PRX_P1

<19> DMI_CTX_PRX_P2

<19> DMI_CTX_PRX_P3

<19> FDI_CSYNC

<19> FDI_INT

M33PEG CRX GTX N11

CC5 2 L32PEG CRX GTX N10 CC6

2

M35PEG CRX GTX N9

L34PEG_CRX_GTX_N8

E29PEG CRX GTX N7

D28PEG_CRX_GTX_N6

E31PEG CRX GTX N5

D30PEG CRX GTX N4

E35PEG CRX GTX N3

D34PEG CRX GTX N2

E33PEG CRX GTX N1

E32PEG CRX GTX N0

CC7

2

CC8

2

CC9

2

CC10 2

CC11 2

CC12 2

CC13 2

CC14 2

CC15 2

CC16 2

CC20

CC21 2

CC23 2

CC24 2

CC25 2

CC26 2

CC27 2

CC28 2

CC29 2

CC30 2

CC31 2

CC32 2

_

_ _ _ _

_ _ _ _

_ _ _

_ _ _

_

_ _ _ _ _ _ _ _ _

_

_ _ _ _ _ . _ _ _ _ _ _

_

_ _ _ _ _ _ _ _ _ _ _

_

_ _ _ _ _ . _ _ _ _ _ _

_

_ _ _ _ _ _ _ _ _ _ _

_ _ _ . _ _ _ _ _ _

_

_ _ _ _ _ _ _ _ _ _ _

_

_

_

_ _ _ _ _ _ _ _ _ _ _

_

_

_ _ _ _ _ _ _ _ _

_ _ _

_ _ _ _ _ _ _ _ _

_ _ _

_ _ _ _ _ _ _ _ _

_ _ _

_ _ _ _ _ _ _ _ _

_ _ _

_ _ _ . _ _ _ _ _ _

_ _ _ _ _ _ _ _ _

_ _ _

_ _ _

_ _ _

_ _ _

_ _ _

_ _ _

_ _ _

_ _ _

_ _ _

_ _ _ _ _

_ _ _ _ _ _ _ _ _

_

_

_ _ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _ _

_ _ _ . _ _ _ _ _ _

_ _ _ _ _ _ _ _ _

_ _ _ . _ _ _ _ _ _

_ _ _ _ _ _ _ _ _

_ _ _ . _ _ _ _ _ _

_ _ _ _ _ _ _ _ _

_

_

_ _ _ _ _ _ _ _ _

_

_

_ _ _ _ _ _ _ _ _

_

_

_ _ _ _ _ _ _ _ _

_

_

_ _ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _ _

_ _ _ _ . _ _ _ _ _

_ _ _ _ _ _ _ _ _

_ _ _ _ . _ _ _ _ _

_ _ _ _ _ _ _ _ _

_ _ _ _ . _ _ _ _ _

_ _ _ _ _ _ _ _ _

_

_

_ _ _ _ _ _ _ _ _

_

_

_ _ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _ _

_ _ _ _ . _ _ _ _ _

_ _ _ _ _ _ _ _ _

_ _ _ _ . _ _ _ _ _

_ _ _ _ _ _ _ _ _

_ _ _ _ . _ _ _ _ _

_ _ _ _ _ _ _ _ _

_

_

BDBIOS.COM

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFOR MATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMAT ION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

CC53

CC55

CC68

CC56

CC49

CC60

5 4 3 2 1

SM_DRAMPWROK with DDR Power Gating Topology

+1.3 5V_ MEM

+PCH_VCC DSW 3_3 +PCH_VC CDSW 3 _3

SYS RES ET#

_ _

CFG3 R

1

2 1CPU PLTRST#

RC8

1K_0402_1 %

2

CFG3

XDP RST# R

CXDP

12/27

XDP TDO

XDP TRST# R

XDP TD I

XDP TMS R

12/

18,19,49> SIO_PW RB TN#

<11>

CPU_PWR_DEBUG

<19,48> SYS_ PW ROK

CFD PW RB TN# XDP

CPU PW R DEBUG R

SYS PW ROK X DP

DDR X DP SMBDAT R1

DDR XDP SMB CLK R1

XDP TCLK R

2

0 0402 5 %

2

0 0402 5 %

2

0 0402 5 %

2

0 0402 5 %

2

0 0402 5%

XDP@ RC6

1

CXDP@ RC7

1

@R C9

1

CXDP@ RC1 25

1

CXDP@ RC1 27

1

CLK_CPU_ITP <20>

CLK_CPU_ITP# <20>

2

0 0402 5%

2

0 0402 5%

CLK XDP CXDP@ RH107

1

CLK XDP# CXDP@ RH10 8

1

H CPUPW RGD CXDP @ RC5 1 2 1K 0402 1% H CPUPW RGD XDP

<13,14,15,16, 18,21,28,36,44>

DDR_XDP_W AN_SMBDAT

<13,14,15,16 ,18,21,28,36 ,44>

DDR_XDP_WAN_SM BCLK

12/27

1 2

S YS_ PW ROK _XDP

@ RC1 24

1K_0402_1%

RC5 need to close to JCPU1

<10> CFG0

<10> CFG1

<10> CFG2

<10> CFG3

<10> CFG4

<10> CFG5

<10> CFG6

<10> CFG7

1 2

PM DRAM P W RGD A

PM DRA M PW RGD CPU

AC10

5 4 3 2 1

BDBIOS.COM

Rev

0.2

65

Size Docum ent Num ber

LA-9771P

Date:

Tuesd ay, J anua ry 15, 201 3 Sheet 7 of

CFG17 <10>

CFG16 <10>

CFG8

<10>

CFG9

<10>

CFG10 <10>

CFG11 <10>

CFG19 <10>

CFG18 <10>

CFG12 <10>

CFG13 <10>

CFG14 <10>

CFG15 <10>

CFG17

CFG16

CFG8

CFG9

CFG10

CFG11

CFG19

CFG18

CFG12

CFG13

CFG14

CFG15

CAD Note:

Trace width=12~15 mil, Spcing=20 mils

Max trace length= 500 mil

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

2

100 0402 1%

2

75 0402 1%

2

100 0402 1%

SM RCOMP 0 RC42 1

SM RCOMP 1 RC55 1

SM RCOMP 2 RC49 1

RC35 2

RC40 2

RC41 2

XDP TDO R

XDP TCLK

XDP TRST#

Title

1

1 K 0402 1%

+1.05V_ RUN

1

5 1 0402 1%

1

5 1 0402 1%

1

5 1 0402 1%

1

5 1 0402 1%

1

5 1 0402 1%

1

5 1 0402 1%

Compal Electronics, Inc.

Haswell (2/7)

XDP DB RESET# R RC1 9 2

XDP TMS

@ RC27 2

XDP TDI R

@ RC29 2

XDP PREQ#

@ RC32 2

XDP P REQ# R

XDP _PRDY#_R

CFG0

CFG1

CFG2

CFG3

XDP OBS0

XDP OBS1

CFG4

CFG5

CFG6

CFG7

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

GND0

GND1

OBSFN_A0

OBSFN_C0

OBSFN_A1

OBSFN_C1

GND2

GND3

OBSDATA_A0 OBSDATA_C0

OBSDATA_A1 OBSDATA_C1

GND4

GND5

OBSDATA_A2 OBSDATA_C2

OBSDATA_A3 OBSDATA_C3

GND6

GND7

OBSFN_B0

OBSFN_D0

OBSFN_B1

OBSFN_D1

GND8

GND9

OBSDATA_B0 OBSDATA_D0

OBSDATA_B1 OBSDATA_D1

GND10

GND11

OBSDATA_B2 OBSDATA_D2

OBSDATA_B3 OBSDATA_D3

GND12

GND13

PWRGOOD/H OOK0 ITPCLK/H OOK4

HOOK1

ITPCLK #/HOOK5

VCC_OB S_AB VCC_OBS _CD

HOOK2

RESET#/ HOOK6

HOOK3

DBR#/HO OK7

GND14

GND15

SDA

TD0

SCL

TRST#

TCK1

TDI

TCK0

TMS

GND16

GND17

SAMTE_BS H-030-01-L -D-A

CONN@

+VCCIO_OUT

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

UC2

74AHC1 G09 GW _TS SOP 5~D

+3.3 V_A LW _PCH

CPU socket Reverse type.

H CPUPW RGD

12/27

CAD Note:

Avoid stub in the PWRGD path

while placing resistors RC25 & RC130

For ESD concern, please put near CPU

DDR3 COMPENSATION SIGNALS

ESD part

PAD~D T1 @

PAD~D T2 @

PAD~D T3 @

PAD~D T4 @

PAD~D T5 @

PAD~D T6 @

2

0 0402 5% X DP OBS1

RC57

1

12/27

12/

RC44

62_0402_5%

+1.0 5V_RUN +VCCS T

2 1

@ RC99

0_0603_5%~D

1 1

@ @

Refer CRB 1.0

2 2

Buffered reset to CPU

PM_SYNC

PWRG OOD

SM_DRA MPWROK

PLTRSTIN

DPLL_REF_CLKN

DPLL_REF_CLKP

SSC_DPLL_REF_ CLKN

SSC_DPLL_REF_C LKP

BCLKN

BCLKP

CONN@

23>

CPU_PLTRST#

AT26

G28

H28

F27

E27

D26

E26

C U PLTRST#

12/25

O

AT28

AL34

H PM S YNC

TRST

TDI

TDO

DBR

BPM_N_0

BPM_N_1

BPM_N_2

BPM_N_3

BPM_N_4

BPM_N_5

BPM_N_6

BPM_N_7

2 OF 9

PROCHOT

PRDY

THERMTRIP

PREQ

TCK

TMS

<49,58,5 9,60>

H_PROCHOT#

<27>

H_THERMTRIP#

<19>

H_PM_SYNC

<23>

H_CPUPWRGD

<20>

CLK_CPU_DPLL#

<20>

CLK_CPU_DPL L

<20>

CLK_CPU_SSC_DPLL#

<20>

CLK_CPU_SSC _DPLL

<20>

CLK_CPU_DMI#

<20>

CLK_CPU_DMI

1/ 1

12/27

XDP P RDY# R

XDP P REQ# R

XDP_TCLK _R

XDP TMS R

XDP TRS T# R

XDP TDI

XDP TDO

SYS RESE T#

XDP OBS0

2

0 0402 5%

2

0 0402 5%

2 0_0402_5%

2

0 0402 5%

2

0 0402 5%

2

0 0402 5%

2

0 0402 5%

1

0 0402 5%

2

0 0402 5%

XDP@ RC47 1

CXDP@ RC48 1

CXDP@ RC50 1

XDP@ RC56 1

XDP@ RC62 1

CXDP@ RC23 1

CXDP@ RC24 1

R RC26 2

CXDP@ RC30 1

CXDP@ RC31 1

AR29

XDP PRDY#

AT29

X DP PREQ#

AM34

XDP_TCL K

AN33

XDP TMS

AM33

XDP TRST#

AM31

XDP TDI R

AL33

XDP TDO R

AP33

X DP DBRESET

AR30

XDP OBS0 R

AN31

XDP OBS1 R

AN29

XDP OBS2 R

AP31

X DP OBS 3 R

AP30

X DP OBS 4 R

AN28

XDP OBS5 R

AP29

X DP OBS 6 R

AP28

X DP OBS 7 R

2

56 0402 5% H PROCHOT# R

AM30

AM35

12/25

RC64

1K_0402_1 %

2 H THERMTRIP#

100_0402_1%

2 H CATERR#

49.9_0402_1%

2 H PROCHOT#

1

@ RC1 26

+VCC IO_OUT

1

@ RC1 28

1

DDR3_DRAMRST#_CPU <13>

AR27

AK31

PECI EC

B

A

<49,55> 1.3 5V_ SUS _PW RGD

+1.0 5V_RUN

H CATERR# AN32

+VCCST

<48>

CPU_DETECT#

<49> PECI_EC

AP3

SM RCOMP0

AR3

SM RCOMP1

AP2

SM RCOMP2

AN3 DDR3 DRAMRST# CPU

AP32

CPU DETECT#

Haswell rPGA EDS

MISC

SM_RCOMP _0

SM_RCOMP _1

SM RCOMP 2

SM_DRAMRST

JCPU1B

SKTOCC

CATERR

PECI

FC AK31

Refer CRB 1.1

@

SYS_R SET# <18, 19,42

12/27

11/22 chan e to CXDP@/test point

PU/PD for JTAG signals

+3.3V_ RUN

D

C

B

A

D

C

B

A

2 1 RUNPWROK R 1

RC103 0_0402_5%

PM DRAM PW RGD A

2

+VCC IO_OUT +VCCIO_ OU T

JXDP1

1 1

2 2

Place near JXDP1

RC18

10K_0402_5%

12/19

12 27

12/27

4 RUNPWROK AND

2 1

P M DRAM PW RGD CP U

RC28

0_0402_5%

_ _ _

/

_

_ _ _ _

_ _ _

_ _

_ _ _ _ _ _ _ _ _ _

C _ _ _ _ _ _ _

<

27

_ _ _ _ _ _ _ _

_ _ _ _ _ @

_ _ _ _ _ _

_ _ _ _ _ _ _

_

_ _ _ _ _

_

_ _

_ _

_ _ _

_ _ _ _ _ _ _ C _ _ _ _

_ _ _ _ _

_ C _ _ _ _

_ C _ _ _ _

_ _ _ _ _ _ _

_ _ _ _ _ _

_ _ _ _ #_ _ _ _

E >

_ P _

<

27

_ _ _ _ _

_ _ _ _ _

_ _

_ _

_ _

_ _

_ _

_ _ g 1

_ _ _ _

_ _ _

_ _ _ _ _

_ _ _

_ _ _ _

_ _ _ _ _ _

_ _ _ _ _ _

_ _ _

CPU socket Reverse type.

PROPRIETARY NOTE: TH IS SHEET OF ENGI NEERING D RAWING AND SPEC IFICATIO NS CONTAI NS CONFID ENTIAL

TRADE SECRET AND OTHER PROPRIETAR Y INFORMA TION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS W RITTEN AUT HORIZATI ON OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

BDBIOS.COM

<15,16> DDR_B _D[0..63]

5

4

3

2

1

D6

AR5

AR6

AM5

AM6

AT5

AT6

AN5

AN6

AJ4

AK4

AJ1

AJ2

AM1

AN1

AK2

AK1

L2

M2

L4

M4

L1

M1

L5

M5

G7

J8

G8

G9

J7

J9

G10

J10

A8

B8

A9

B9

D8

E8

D9

E9

E15

D15

A15

B15

E14

D14

A14

B14

DDR B D16

DDR B D17

DDR B D18

DDR B D19

DDR B D20

DDR B D21

DDR B D22

DDR_B_D23

DDR B D24

DDR B D25

DDR B D26

DDR B D27

DDR B D28

DDR B D29

DDR B D30

DDR B D31

DDR B D32

DDR B D33

DDR B D34

DDR B D35

DDR B D36

DDR B D37

DDR B D38

DDR B D39

DDR_B_D40

DDR B D41

DDR B D42

DDR B D43

DDR B D44

DDR B D45

DDR B D46

DDR B D47

DDR B D48

DDR B D49

DDR B D50

DDR B D51

DDR_B_D52

DDR B D53

DDR B D54

DDR B D55

DDR B D56

DDR B D57

DDR B D58

DDR B D59

DDR_B_D60

DDR B D61

DDR B D62

DDR B D63

AC7

U4 M CLK DDR#0

V4 M CLK DDR0

AD9 DDR CKE0 DIMM2

U3 M_C LK_DDR#1

V3 M CLK DDR1

AC9 DDR CKE1 DIMM2

U2 M CLK DDR#4

V2 M CLK DDR4

AD8 DDR CKE4 DIMM1

U1 M CLK DDR#5

V1 M CLK DDR5

AC8 DDR_C KE5_DI MM1

M7

DDR CS0 DIMM2#

L9

DDR CS1 DIMM2#

M9

DDR CS4 DIMM1#

M10 DDR CS5 DIMM1#

M8

M ODT0

L7

M ODT1

L8

M ODT4

L10

M ODT5

V5 DDR A BS0

U5 DDR A BS1

AD1 DDR_A_B S2

V10

U6 DDR A RAS#

U7 DDR A W E#

U8 DDR A CAS#

V8 DDR A MA0

AC6 DDR A MA1

V9 DDR A MA2

U9 DDR A MA3

AC5 DDR A MA4

AC4 DDR A MA5

AD6 DDR A MA6

AC3 DDR A MA7

AD5 DDR A MA8

AC2 DDR A MA9

V6 DDR_A_MA10

AC1 DDR A MA11

AD4 DDR A MA12

V7 DDR A MA13

AD3 DDR A MA14

AD2 DDR A MA15

AP15 DDR A DQS#0

AP8 DDR A DQS#1

AJ8 DDR A DQS#2

AF3 DDR A DQS#3

J3

DDR_A _DQS#4

E2 DDR A DQS#5

C5 DDR A DQS #6

C11

DDR A DQS#7

AP14 DDR A DQS0

AP9 DDR A DQS1

AK8 DDR A DQS2

AG3 DDR A DQS3

H3 DDR_A_DQS4

E3 DDR A DQS5

C6 DDR A DQS6

C12

DDR A DQS7

DDR_A_D0 AR15

DDR A D1 AT14

DDR A D2 A M14

DDR A D3 AN14

DDR_A_D4 AT15

DDR A D5 AR14

DDR A D6 AN15

DDR A D7 A M15

DDR A D8 AM9

DDR A D9 AN 9

DDR A D10 A M8

DDR A D11 AN8

DDR_A_D12 AR9

DDR A D13 AT9

DDR A D14 AR8

DDR A D15 AT8

DDR A D16 AJ9

DDR A D17 AK9

DDR A D18 AJ6

DDR A D19 AK6

DDR A D20 AJ10

DDR A D21 AK10

DDR A D22 AJ7

DDR A D23 AK7

DDR_A_D24 AF4

DDR A D25 AF5

DDR A D26 AF1

DDR A D27 AF2

DDR A D28 AG4

DDR A D29 AG5

DDR A D30 AG1

DDR A D31 AG2

DDR A D32

J1

DDR A D33

J2

DDR A D34

J5

DDR A D35 H5

DDR A D36 H2

DDR A D37 H1

DDR A D38

J4

DDR A D39 H4

DDR A D40

F2

DDR B D0

DDR B D1

DDR B D2

DDR_B_D3

DDR B D4

DDR B D5

DDR B D6

DDR B D7

DDR B D8

DDR B D9

5

4

3

2

1

of

Rev

0.2

65

Size Document Number

LA-9771P

Date: Tuesday, January 15, 2013

Sheet

8

DDR B D10 A N12

DDR_B_D11 AM 11

DDR B D12 AT11

DDR B D13 A R11

DDR B D14 AM12

DDR B D15 A N11

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Title

Haswell (3/7)

CPU socket Reverse type.

JCPU1D

RSVD

SB_CKN0

SB_CKP0

SB_CKE_0

SB_CKN1

SB_CKP1

SB_CKE_1

SB_CKN2

SB_CKP2

SB_CKE_2

SB_CKN3

SB_CKP3

SB_CKE_3

SB_CS_N_0

SB_CS_N_1

SB_CS_N_2

SB_CS_N_3

SB_ODT_0

SB_ODT_1

SB_ODT_2

SB_ODT_3

SB_BS_0

SB_BS_1

SB_BS_2

VSS

SB_RAS

SB_WE

SB_CAS

SB_MA_ 0

SB_MA_ 1

SB_MA_ 2

SB_MA_ 3

SB_MA_ 4

SB_MA_ 5

SB_MA_ 6

SB_MA_ 7

SB_MA_ 8

SB_MA_ 9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

SB_MA_15

SB_DQS_N_0

SB_DQS_N_1

SB_DQS_N_2

SB_DQS_N_3

SB_DQS_N_4

SB_DQS_N_5

SB_DQS_N_6

SB_DQS_N_7

SB_DQS_ P_0

SB_DQS_ P_1

SB_DQS_ P_2

SB_DQS_ P_3

SB_DQS_ P_4

SB_DQS_ P_5

SB_DQS_ P_6

SB_DQS_ P_7

AR18

AT18

AM17

AM18

AR17

AT17

AN17

AN18

AT12

AR12

AG8

Y4 M CLK DDR#2

AA4 M CLK DDR2

AF10 DDR_C KE2_DIMM4

Y3 M CLK DDR#3

AA3 M CLK DDR3

AG10 DDR CKE3 DIMM4

Y2 M CLK DDR#6

AA2 M CLK DDR6

AG9 DDR CKE 6 DIMM3

Y1 M CLK DDR#7

AA1 M_C LK_DDR7

AF9 DD R CKE7 DIMM3

P4 DDR C S2 DIMM4#

R2 DDR CS3 DIMM4#

P3 DDR C S6 DIMM3#

P1 DDR C S7 DIMM3#

R4 M ODT2

R3 M ODT3

R1 M ODT6

P2 M ODT7

R7 DDR _B_BS0

P8 DDR B BS1

AA9 DDR B BS2

R10

R6 DDR B RAS#

P6 DDR B W E#

P7 DDR B CAS#

R8 DDR B MA0

Y5 DDR B MA1

Y10 DDR B MA2

AA5 DDR B MA3

Y7 DDR B MA4

AA6 DDR B MA5

Y6 DDR B MA6

AA7 DDR B MA7

Y8 DDR_B_MA8

AA10 DDR B MA9

R9 DDR B MA10

Y9 DDR B MA11

AF7 DD R B MA12

P9 DDR B MA13

AA8 DDR B MA14

AG7 DDR B MA15

AP18 DDR B DQS#0

AP11 DDR B DQS#1

AP5 DDR_B_DQS#2

AJ3 DDR B DQS#3

L3

DDR B DQS#4

H9 DDR B DQS#5

C8 DDR B DQS#6

C14 DDR B DQS#7

AP17 DDR B DQS0

AP12 DDR B DQS1

AP6 DDR_B_DQS2

AK3 DDR B DQS3

M3 DDR B DQS4

H8 DDR B DQS5

C9 DDR_B_DQS6

C15 DDR B DQS7

@ T64 PAD~D

M_CLK_DDR #2 <16>

M_CLK_DDR 2 <16>

DDR_CKE2_DIMM4 <16>

M_CLK_DDR #3 <16>

M_CLK_DDR 3 <16>

DDR_CKE3_DIMM4 <16>

M_CLK_DDR #6 <15>

M_CLK_DDR 6 <15>

DDR_CKE6_DIMM3 <15>

M_CLK_DDR #7 <15>

M_CLK_DDR 7 <15>

DDR_CKE7_DIMM3 <15>

DDR_CS2_D IMM4# <16>

DDR_CS3_D IMM4# <16>

DDR_CS6_D IMM3# <15>

DDR_CS7_D IMM3# <15>

M_ODT2 <16>

M_ODT3 <16>

M_ODT6 <15>

M_ODT7 <15>

DDR_B_BS0 <15,16>

DDR_B_BS1 <15,16>

DDR_B_BS2 <15,16>

DDR_B_RAS# <15,16>

DDR_B_W E# <15,16>

DDR_B_CAS# <15,16>

DDR_B_MA[0..15] <15,16>

DDR_B_DQS#[0..7] <15,16>

DDR_B_DQS[0..7] <15,16>

Haswell rPGA EDS

SB_DQ_ 0

SB_DQ_ 1

SB_DQ_ 2

SB_DQ_ 3

SB_DQ_ 4

SB_DQ_ 5

SB_DQ_ 6

SB_DQ_ 7

SB_DQ_ 8

SB_DQ_ 9

SB_DQ_ 10

SB_DQ_ 11

SB_DQ_ 12

SB_DQ_ 13

SB_DQ_ 14

SB_DQ_ 15

SB_DQ_ 16

SB_DQ_ 17

SB_DQ_ 18

SB_DQ_ 19

SB_DQ_ 20

SB_DQ_ 21

SB_DQ_ 22

SB_DQ_ 23

SB_DQ_ 24

SB_DQ_ 25

SB_DQ_ 26

SB_DQ_ 27

SB_DQ_ 28

SB_DQ_ 29

SB_DQ_ 30

SB_DQ_ 31

SB_DQ_ 32

SB_DQ_ 33

SB_DQ_ 34

SB_DQ_ 35

SB_DQ_ 36

SB_DQ_ 37

SB_DQ_ 38

SB_DQ_ 39

SB_DQ_ 40

SB_DQ_ 41

SB_DQ_ 42

SB_DQ_ 43

SB_DQ_ 44

SB_DQ_ 45

SB_DQ_ 46

SB_DQ_ 47

SB_DQ_ 48

SB_DQ_49

SB_DQ_ 50

SB_DQ_ 51

SB_DQ_ 52

SB_DQ_ 53

SB_DQ_ 54

SB_DQ_ 55

SB_DQ_ 56

SB_DQ_ 57

SB_DQ_ 58

SB_DQ_ 59

SB_DQ_ 60

SB_DQ_ 61

SB_DQ_ 62

SB_DQ_ 63

4 OF 9

CONN@

DDR A D52 D5

DDR_A_D53 E5

DDR A D54 B6

DDR A D55 A6

DDR A D56 E12

DDR A D57

D12

DDR A D58 B11

DDR A D59 A11

DDR A D60 E11

DDR_A_D61

D11

DDR A D62 B12

DDR A D63 A12

AM3

F16

F13

DDR A D51

D

C

B

A

JCPU1C

RSVD

SA_CKN0

SA_CKP0

SA_CKE_0

SA_CKN1

SA_CKP1

SA_CKE_1

SA_CKN2

SA_CKP2

SA_CKE_2

SA_CKN3

SA_CKP3

SA_CKE_3

SA_CS_N_0

SA_CS_N_1

SA_CS_N_2

SA_CS_N_3

SA_ODT _0

SA_ODT _1

SA_ODT _2

SA_ODT _3

SA_BS_0

SA_BS_1

SA_BS_2

VSS

SA_RAS

SA W E

SA_CAS

SA_MA_ 0

SA_MA_ 1

SA_MA_ 2

SA_MA_ 3

SA_MA_ 4

SA_MA_ 5

SA_MA_ 6

SA_MA_ 7

SA_MA_ 8

SA_MA_ 9

SA_MA_ 10

SA_MA_ 11

SA_MA_ 12

SA_MA_ 13

SA_MA_ 14

SA_MA_ 15

SA_DQS _N_0

SA_DQS _N_1

SA_DQS _N_2

SA_DQS _N_3

SA_DQS _N_4

SA_D QS_N_5

SA_DQS _N_6

SA_DQS _N_7

SA_DQS_P_0

SA_DQS_P_1

SA_DQS_P_2

SA_DQS_P_3

SA_DQS_P_4

SA_DQS_P_5

SA_DQS_P_6

SA_DQS_P_7

@T60 PAD~D

M_CLK_DDR#0 <14>

M_CLK_DDR0 <14>

DDR_CKE0 _DIMM2 <14>

M_CLK_DDR#1 <14>

M_CLK_DDR1 <14>

DDR_CKE1 _DIMM2 <14>

M_CLK_DDR#4 <13>

M_CLK_DDR4 <13>

DDR_CKE4 _DIMM1 <13>

M_CLK_DDR#5 <13>

M_CLK_DDR5 <13>

DDR_CKE5 _DIMM1 <13>

DDR_CS0_D IMM2# <14>

DDR_CS1_D IMM2# <14>

DDR_CS4_D IMM1# <13>

DDR_CS5_D IMM1# <13>

M_ODT0 <14>

M_ODT1 <14>

M_ODT4 <13>

M_ODT5 <13>

DDR_A_BS0 <13, 14>

DDR_A_BS1 <13, 14>

DDR_A_BS2 <13, 14>

DDR_A_RAS# <13,14>

DDR_A_W E# <13,14>

DDR_A_CAS# <13,14>

DDR_A_MA[0 ..15] <13,14>

DDR_A_DQS#[0..7] <13, 14>

DDR_A_DQS [0..7] <13, 14>

D

<13,14> DDR_A_D[0..63]

C

+SM_VREF

+SA_DIMM_VREFDQ

+SB_DIMM_VREFDQ

B

A

Haswell rPGA EDS

SA_DQ _0

SA_DQ _1

SA_DQ_2

SA_DQ _3

SA_DQ _4

SA_DQ _5

SA_DQ _6

SA_DQ _7

SA_DQ _8

SA_DQ _9

SA_DQ_ 10

SA_DQ_ 11

SA_DQ_ 12

SA_DQ_ 13

SA_DQ_ 14

SA_DQ_ 15

SA_DQ_ 16

SA_DQ_ 17

SA_DQ_ 18

SA_DQ_ 19

SA_DQ_ 20

SA_DQ_ 21

SA_DQ_ 22

SA_DQ_ 23

SA_DQ_ 24

SA_DQ_ 25

SA_DQ_ 26

SA_DQ_ 27

SA_DQ_ 28

SA_DQ_ 29

SA_DQ_ 30

SA_DQ_ 31

SA_DQ_ 32

SA_DQ_ 33

SA_DQ_ 34

SA_DQ_ 35

SA_DQ_ 36

SA_DQ_ 37

SA_DQ_ 38

SA_DQ_ 39

SA_DQ_ 40

SA_DQ_ 41

SA_DQ_ 42

SA_DQ_ 43

SA_DQ_ 44

SA_DQ_ 45

SA_DQ_ 46

SA_DQ_ 47

SA_DQ_ 48

SA_DQ_ 49

SA_DQ_ 50

SA_DQ_ 51

SA_DQ_ 52

SA_DQ_ 53

SA_DQ_ 54

SA_DQ_ 55

SA_DQ_ 56

SA_DQ_ 57

SA_DQ_ 58

SA_DQ_ 59

SA_DQ_ 60

SA_DQ_ 61

SA_DQ_ 62

SA_DQ_ 63

SM_V REF

SA_DIM M_VREFDQ

SB_DIM M_VREFDQ

3 OF 9

CONN@

DDR A D42 D2

DDR A D43 D3

DDR A D44 D1

DDR A D45

F3

DDR A D46 C3

DDR A D47 B3

DDR A D48 B5

DDR A D49 E6

DDR A D50 A5

F1

DDR_A_D41

_ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _

_ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _

_ _ _ _ _

_ _ _ _ _ _

_ _ _ _ _ _

_ _ _ _ _ _ _

_ _ _ _ _ _ _

_ _ _ _ _ _

_ _ _ _ _ _

_ _ _ _ _ _

_ _ _ _ _ _

_

_ _ _ _ _ _ _ _

_ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _

_ _ _ _ _ _

_ _ _ _ _ _

_ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _

_ _

5

D

C

B

A

5

2 1

Size Document Number

LA-9771P

Date: Tuesday January 15 2013 Sheet 9 of

Rev

0.2

65

M27 EDP CPU AUX#

N27 EDP CPU AUX

P27 EDP HPD#

E24 EDP COMP

R27

PAD~D T69@

P35 EDP CPU LANE N0

R35 EDP_CPU_LANE_P0

N34 EDP CPU LANE N1

P34 EDP_CPU_LANE_P1

P33 FDI CTX PRX N0

R33 FDI CTX PRX P0

N32 FDI CTX PRX N1

P32 FDI CTX PRX P1

EDP_AUXN

EDP_AUXP

EDP_HPD

EDP_RCOMP

EDP_DISP_UTIL

EDP_TXN_0

EDP_TXP_0

EDP_TXN_1

EDP_TXP_1

FDI_TXN_0

FDI_TXP_0

FDI_TXN_1

FDI_TXP_1

8 OF 9

24.9_0402_1% RC1

CAD Note:Trace width=20 mils ,Spacing=25mil,

Max length=100 mils.

EDP_CPU_AUX# <28>

EDP_CPU_AUX <28>

EDP_CPU_LANE_N0 <28>

EDP_CPU_LANE_P0 <28>

EDP_CPU_LANE_N1 <28>

EDP_CPU_LANE_P1 <28>

FDI_CTX_PRX_N0 <19>

FDI_CTX_PRX_P0 <19>

FDI_CTX_PRX_N1 <19>

FDI_CTX_PRX_P1 <19>

+VCCIO_OUT

2 1

EDP COMP

D

C

B

A

T28

U28

T30

U30

U29

V29

U31

V31

T34

U34

U35

V35

U32

T32

U33

V33

P29

R29

N28

P28

P31

R31

N30

P30

EDP HPD#

D

2

G

S

11/22 SSI EMO

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Title

Haswell (4/7)

HPD INVERSION FOR EDP

<28> CPU_EDP_HPD

CPU socket Reverse type.

3

.

4 3 2 1

COMPENSATION PU FOR eDP

+VCOMP_OUT

JCPU1H

DDIB_TXN0

DDIB_TXP0

DDIB_TXN1

DDIB_TXP1

DDIB_TXN2

DDIB_TXP2

DDIB_TXN3

DDIB_TXP3

DDIC_TXN0

DDIC_TXP0

DDIC_TXN1

DDIC_TXP1

DDIC_TXN2

DDIC_TXP2

DDIC_TXN3

DDIC_TXP3

DDID_TXN0

DDID_TXP0

DDID_TXN1

DDID_TXP1

DDID_TXN2

DDID_TXP2

DDID_TXN3

DDID_TXP3

CONN@

<34> DPD_CPU_LANE_N0

<34> DPD_CPU_LANE_P0

<34> DPD_CPU_LANE_N1

<34> DPD_CPU_LANE_P1

<34> DPD_CPU_LANE_N2

<34> DPD_CPU_LANE_P2

<34> DPD_CPU_LANE_N3

<34> DPD_CPU_LANE_P3

4

DPD CPU LANE N0

DPD CPU LANE P0

DPD CPU LANE N1

DPD CPU LANE P1

DPD CPU LANE N2

DPD CPU LANE P2

DPD_CPU_LANE_N 3

DPD CPU LANE P3

Haswell rPGA EDS

eDP

DDI

_

_ _

_ _ _ _

_ _ _

_ _ _ _ _

_ _ _

_ _ _

_ _ _

_

_

_ _ _

_ _ _

_ _ _

_ _ _

_ _ _

_ _ _

_ _ _ M ,

,

BDBIOS.COM

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFOR MATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATI ON IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5 4 3 2 1

CFG STRAPS for CPU

CFG2

D D

PEG Static Lane Reversal - CFG2 is for the 16x

FC G6

Rev

0.2

65

C

B

BDBIOS.COM

3

Haswell (5/7)

LA-9771P

Title

Size Document Number

5 4

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

CFG7

1: (Default) PEG Train immediately

following xxRESETB de assertion

0: PEG Wait for BIOS for training

CPU socket Reverse type.

Note: Reserve this circuit

for future compatibility

RESET_OUT#

RESET_OUT# <18,19,49>

@RC73

6.04K_0402_1%

FC G6

@RC72

2.67K_0402_1%

of

10

Date: Tuesday, January 15, 2013 Sheet

2 1

1:(Default) Normal Operation; Lane #

definition matches socket pin map definition

0:Lane Reversed

CFG4

Display Port Presence Strap

1 : Disabled; No Physical Display Port

attached to Embedded Display Port

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

12/26

PCIE Port Bifurcation Straps(PEG)

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2

disabled

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

12/26

PEG DEFER TRAINING

CFG2

CFG4

CFG[6:5]

Haswell rPGA EDS

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

CFG_RCOMP

CFG_16

CFG_18

CFG_17

CFG_19

RSVD

FC_G6

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

NC

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

VSS

VSS

VSS

VSS

9 OF 9

JCPU1I

RSVD_TP

RSVD_TP

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

TESTLO_G26

VSS

RSVD

RSVD

VCC

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

TESTLO_W 34

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CONN@

@T70 PAD~D

@T71 PAD~D

@T72 PAD~D

@T73 PAD~D

@T74 PAD~D

@T75 PAD~D

@T76 PAD~D

@T79 PAD~D

@T80 PAD~D

+VCC_CORE

@T82 PAD~D

@T81 PAD~D

@T85 PAD~D

@T84 PAD~D

@T83 PAD~D

<7> CFG0

<7> CFG1

<7> CFG2

<7> CFG3

<7> CFG4

<7> CFG5

<7> CFG6

<7> CFG7

<7> CFG8

<7> CFG9

<7> CFG10

<7> CFG11

<7> CFG12

<7> C FG13

<7> CFG14

<7> CFG15

2 1

H CPU TESTLO

RC45 49.9_0402_1%

2 1

CFG RCOMP

RC58 49.9_0402_1%

2 1

H CPU RSVD

RC59 49.9_0402_1%

AT1

AT2

AD10

A34

A35

W29

W28

H_CPU_RSVD G26

W33

AL30

AL29

F25

C35

B35

AL25

W30

W31

H CPU TESTLO W 34

C23

B23

D24

D23

AT31 CFG RCOMP

AR21 CFG16

AR23 CFG18

AP21 CFG17

AP23 CFG19

AR33

PAD~D T86@

PAD~D T78@

PAD~D T87@

PAD~D T88@

CFG16 <7>

CFG18 <7>

CFG17 <7>

CFG19 <7>

PAD~D T91@

PAD~D T90@

PAD~D T92@

PAD~D T89@

PAD~D T93@

PAD~D T95@

PAD~D T94@

PAD~D T96@

PAD~D T98@

PAD~D T97@

PAD~D T100 @

PAD~D T99 @

PAD~D T102 @

PAD~D T101 @

C

B

G6

AM27

AM26

F5

AM2

K6

E18

U10

P10

B1

A2

AR1

E21

E20

AP27

AR26

AL31

AL32

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

AT20

AR20

AP20

AP22

AT22

AN22

AT25

AN23

AR24

AT23

AN20

AP24

AP26

AN25

AN26

AP25

_ _ _ _ _ _ _ _ _

_

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFOR MATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATI ON IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

01: Reserved - (Device 1 function 1 disabled ; function

A

A

DELL CONFIDENTIAL/PROPRIETARY

5

4

3

2

1

+VCC_CORE

JCPU1E

RSVD

RSVD

RSVD

RSVD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

RSVD

VCC

RSVD

RSVD

VCC_ SENS E

RSVD

VCCIO_OUT

FC_A23

VCOMP _OUT

RSVD

RSVD

RSVD

RSVD

VIDAL ERT

VIDSCL K

VIDSOUT

VSS

PW R_DEBU G

VSS

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

CONN@

Haswell rPGA EDS

5 OF 9

AA26

AA28

AA34

AA30

AA32

AB26

AB29

AB25

AB27

AB28

AB30

AB31

AB33

AB34

AB32

AC26

AB35

AC28

AD25

AC30

AD28

AC32

AD31

AC34

AD34

AD26

AD27

AD29

AD30

AD32

AD33

AD35

AE26

AE32

AE28

AE30

AG28

AG34

AE34

AF25

AF26

AF27

AF28

AF29

AF30

AF31

AF32

AF33

AF34

AF35

AG26

AH26

AH29

AG30

AG32

AH32

AH35

AH25

AH27

AH28

AH30

AH31

AH33

AH34

AJ25

AJ26

AJ27

AJ28

AJ29

AJ30

AJ31

AJ32

AJ33

AJ34

AJ35

G25

H25

J25

K25

L25

M25

N25

P25

R25

T25

U25

U26

V25

V26

W26

W27

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

K27

L27

T27

V27

+1.35V_MEM

AB11

AB2

AB5

AB8

AE11

AE2

AE5

AE8

AH11

K11

N11

N8

T11

T2

T5

T8

W11

W2

W5

W8

N26

K26

AL27

AK27

VCCSE NSE R AL35

E17

AN35

A23

F22

W32

AL16

J27

AL13

H_CPU_SV IDALRT# AM28

VIDSCLK AM29

@T110 PAD~D

@T77 PAD ~D

@T112 PAD~D

@T113 PAD~D

@T115 PAD~D

+VCC_CORE

@T151 PAD~D

@T152 PAD~D

@T153 PAD~D

+VCCIO_OUT

+VCCIO2PCH_R

+VCOMP_OUT

@T160 PAD~D

@T159 PAD~D

@T164 PAD~D

@T154 PAD~D

<58> VIDSCLK

<7> CPU_PW R_DEBUG

D

C

B

D

C

B

2

@

1/11

+1.35V_MEM

12/20

12/20

VDDQ DECOUPLING

1 1 1 1 1 1 1 1 1 1

@ @ @ @ @ @ @ @

VCCSENSE

0_0402_5%

VSSSE NSE

0_0402_5%

2 1 VCCS ENSE R

RC67

CAD Note: RC68 SHOULD BE PLACED CLOSE TO CPU

+1.05V_RUN +VCCIO2PCH +VCCIO2PCH_R

1 2 2 1

@ R105 0_0603_5 @ RC106 0 _0603_5%~D

1

+1.05V_RUN

CPU PW R DEBUG

12/26

+VCCIO_OUT

CAD Note: Place the PU resistors close to CPU

RC60 close to CPU 300 - 1500mils

SVID ALERT

<58> VIDALERT_N

SVID DATA

<58> VIDSOUT

VCC_SENSE

<58> VCCSENSE

<58> VSSSENSE

2 1 VSSSENSE_R

RC68

VSSSE NSE_R <12>

2

@

2

2

@

2

2

@

2

IVR_ERROR

AR32

IST TRIGGER

AL26

AT34

AL22

AT33

AM21

AM25

AM22

AM20

AM24

AL19

AM23

AT32

+VCC_CORE

Y25

Y26

Y27

Y28

Y29

Y30

Y31

Y32

Y33

Y34

Y35

@T157 PAD~D

@T158 PAD~D

@T162 PAD~D

@T163 PAD~D

1

+ +

2 2

10/31

1

2

11

2 1

H CPU SVIDALRT#

43_0402_5% RC61

+VCCIO_OUT

CAD Note: Place the PU resistors close to CPU

RC63 close to CPU 300 - 1500mils

VIDSOUT

+VCC_CORE

CAD Note: RC67 SHOULD BE PLACED CLOSE TO CPU

VIDSOUT

AL28

AP35

H27

AP34

AT35

AR35

BDBIOS.COM

of

Date: Tuesday, January 15, 2013

Sheet

2

1

Rev

0.2

65

Compal Electronics, Inc.

Title

Haswell (6/7)

Size Document Number

LA-9771P

2

@

2

2

@

2

2

@

2

2

1

2

2

@

2

2

12/2

@

2

12/2

2

@

2

CPU socket Reverse type.

_

_ _

_ _ _ % _ 1 0 1 1 1 1 1 1 1 1 1

0

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATI ON OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFER RED OR COPI ED WITHOUT THE EXPRESS WR ITTEN AUTH ORIZAT ION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

D

C

B

VSSSENSE_R <11>

PAD~D T114

A

DELL CONFIDENTIAL/PROPRIETARY

4 3 2 1

5

D

C

B

A

5

A10

A13

A16

A19

A22

A25

A27

A29

A3

A31

A33

A4

A7

AA11

AA25

AA27

AA31

AA29

AB1

AB10

AA33

AA35

AB3

AC25

AC27

AB4

AB6

AB7

AB9

AC11

AD11

AC29

AC31

AC33

AC35

AD7

AE1

AE10

AE25

AE29

AE3

AE27

AE35

AE4

AE6

AE7

AE9

AF11

AF6

AF8

AG11

AG25

AE31

AG31

AE33

AG6

AH1

AH10

AH2

AG27

AG29

AH3

AG33

AG35

AH4

AH5

AH6

AH7

AH8

AH9

AJ11

AJ5

AK11

AK25

AK26

AK28

AK29

AK30

AK32

E19

AK34 B34

AK5 B4

AL1 B7

AL10 C1

AL11 C10

AL12 C13

AL14 C16

AL15 C19

AL17 C2

AL18 C22

AL2 C24

AL20 C26

AL21 C28

AL23 C30

E22 C32

AL3 C34

AL4 C4

AL5 C7

AL6 D10

AL7 D13

AL8 D16

AL9 D19

AM10 D22

AM13 D25

AM16 D27

AM19 D29

E25 D31

AM32 D33

AM4 D35

AM7 D4

AN10 D7

AN13 E1

AN16 E10

AN19 E13

AN2 E16

AN21 E4

AN24 E7

AN27 F10

AN30 F11

AN34 F12

AN4 F14

AN7 F15

AP1 F17

AP10 F18

AP13 F20

AP16 F21

AP19 F23

AP4 F24

AP7 F26

W25 F28

AR10 F30

AR13 F32

AR16 F34

AR19 F4

AR2 F6

AR22 F7

AR25 F8

AR28 F9

AR31 G1

AR34 G11

AR4 G2

AR7 G27

AT10 G29

AT13 G3

AT16 G31

AT19 G33

AT21 G35

AT24 G4

AT27 G5

AT3 H10

AT30 H26

AT4 H6

AT7 H7

B10 J11

B13 J26

B16 J28

B19 J30

B2 J32

B22 J34

J6

K1

K10

K2

K29

K3

K31

K33

K35

K4

K5

K7

K8

K9

L11

L26

L6

M11

M26

M28

M30

M32

M34

M6

N1

N10

N2

N29

N3

N31

N33

N35

N4

N5

N6

N7

N9

P11

P26

P5

R11

R26

R28

R30

R32

R34

R5

T1

T10

T29

T3

T31

T33

T35

T4

T6

T7

T9

U11

U27

V11

V28

V30

V32

V34

W1

W10

W3

W35

W4

W6

W7

W9

Y11

H11

AL24

F19

T26

AK35

AK33

6 OF 9 7 OF 9

CONN@ CONN@

CPU socket Reverse type.

4

CPU socket Reverse type.

Compal Electronics, Inc.

Title

Haswell (7/7)

Size Document Number

LA-9771P

Date: Tuesday, January 15, 2013 Sheet

Rev

0.2

65

BDBIOS.COM

12

of

2 1

Haswell rPGA EDS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

JCPU1F

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Haswell rPGA EDS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS_SENSE

RSVD

JCPU1G

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

@

PROPRIETARY NOTE:

THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC

. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5 4 3 2 1

JDIMM3 (Ch B1 H=9.2 REV)

5 4 3 2 1

Rev

0.2

65

DDRIII-SODIMM SLOT1

Size Docume nt Numb er

LA-9771P

Date: Tuesday J anuary 15 20 13

Sheet 13

of

2

10/30

DDR HV REF R ST PC H

RD45 1

3

1

1

2

CD92

0.047U_040 2_16V4Z

CONN List 0925A

BDBIOS.COM

+0.675V_DDR_VTT

DDR3_D RAMRST#_R <14,15,16>

DDR_XDP _WAN_SM BDAT <14,15,16, 18,21,28,36,4 4,7>

DDR_XD P_WAN_ SMBCLK <14,15,16, 18,21,28, 36,44,7>

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Title

+1.35V_MEM

RD5

1K_0402_5 %

3

1

1

2

RD12 1K_0402_5%

DDR HV REF R ST PC H

1

2

2

1/11

1

1

2

2 2 2 2 2 2 2

Layout Note:

Place near JDIMM1.203,204

+0.675V_ DDR_VTT

1

1 1

1

2

2 2

2

1

<15,21> DDR_HVR EF_RST_ PCH

2

M_CLK_DD R5 <8>

M_CLK_DD R#5 <8>

DDR_A_B S1 <14,8>

DDR_A_R AS# <14,8>

DDR_CS4 _DIMM1# <8>

M_ODT4 <8>

M_ODT5 <8>

+SM_VREF_DIMM

@

2

2 0402 1%

+1.35V_MEM

+SM_VREF _DIMM

2

2 0402 1%

RD41 1

DDR A D1

DDR A D5

DDR A DQS#0

DDR A DQS0

DDR A D2

DDR A D3

DDR A D13

DDR A D12

DDR3 D RAMRST # R

DDR A D11

DDR_A_D 10

DDR_A_D 17

DDR_A_D 16

DDR A D19

DDR A D18

DDR A D25

DDR A D24

DDR A DQS#3

DDR A DQS3

DDR A D27

DDR A D26

DDR A M A15

DDR_A_MA 14

DDR_A_MA 11

DDR_A_MA 7

DDR A MA6

DDR A MA4

DDR A MA2

DDR A MA0

M CLK DDR5

M CLK DD R#5

DDR A BS1

DDR A RAS#

M ODT4

M ODT5

DDR_A_D 33

DDR_A_D 32

DDR A D38

DDR A D39

DDR A D41

DDR A D40

DDR A DQS#5

DDR A DQS5

DDR A D43

DDR A D42

DDR A D52

DDR A D53

DDR A D54

DDR A D50

DDR_A_D 60

DDR_A_D 61

DDR_A_D QS#7

DDR A DQS7

DDR A D58

DDR A D59

+0.675V_ DDR_VTT

JDIMM1 REV Type H=5.2

CPU

+1.35V_MEM

+1.35V_MEM

JDIMM1 (Ch A1 H=5.2 REV)

TOP

QD1A

DMN66D 0LDW -7_SOT363- 6

1

6

DDR_C KE5_DIMM1 <8>

<8> DDR_CKE4_DIMM1

<14,8> DDR_A_ BS2

<8> M_CLK_DDR4

<8> M_CLK_DD R#4

<14,8> DDR_A_ BS0

<14,8> DDR_A_ WE#

<14,8> DDR_A_CAS#

<8> DDR_CS 5_DIMM1#

+3.3V_RUN

1

1

@

2

2

1/11

Layout Note:

Place near JDIMM1

+1.35V_MEM

1 1 1

1

2 2 2

2

+1.35V_MEM

1

1 1 1 1 1 1

D

C

B

A

D

C

B

A

<14,8> DDR_A_D QS#[0..7]

<14,8> DDR_A_D[ 0..63]

<14,8> DDR_A_ DQS[0

..7]

<14,8> DDR_A_ MA[0..15]

12/ 6

+SM_VREF

+SM_VREF_Q

QD2

L2N7002W T1G_SC -70-3

JDIMM1 CONN@

BOT

1 1

@

2 2

+SA_DIMM1_VR EFDQ

12/26

All VREF traces should

have 20 mil trace width

and 20 mil spacing to

other signals/planes.

1/ 1

1/8

1

@

+

DDR A D4

DDR A D0

DDR A D7

DDR A D6

DDR A D8

DDR A D9

DDR A DQS#1

DDR A DQ S1

DDR A D15

DDR_A_D 14

DDR_A_D 21

DDR_A_D 20

DDR A DQS#2

DDR A DQ S2

DDR A D23

DDR A D22

DDR A D29

DDR A D28

DDR A D31

DDR A D30

DDR_A_B S2

DDR_A_MA 12

DDR_A_MA 9

DDR A MA8

DDR A MA5

DDR A MA3

DDR A MA1

M CLK DD R4

M CLK DD R#4

DDR A MA10

DDR A BS0

DDR A W E#

DDR A CAS#

DDR A MA13

DDR_A_D 37

DDR_A_D 36

DDR_A_D QS#4

DDR A DQ S4

DDR A D34

DDR A D35

DDR A D45

DDR A D44

DDR A D47

DDR A D46

DDR A D48

DDR A D49

DDR A DQS#6

DDR A DQ S6

DDR A D51

DDR A D55

DDR_A_D 57

DDR_A_D 56

DDR A D63

DDR A D62

DIMM1 SA0

DIMM1 SA1

VREF_DQ VSS1

VSS2 DQ4

DQ0 DQ5

DQ1 VSS3

VSS4 DQS#0

DM0 DQS0

VSS5 VSS6

DQ2 DQ6

DQ3 DQ7

VSS7 VSS8

DQ8 DQ12

DQ9 DQ13

VSS9 VSS10

DQS#1 DM1

DQS1 RESET#

VSS11 VSS12

DQ10 DQ14

DQ11 DQ15

VSS13 VSS14

DQ16 DQ20

DQ17 DQ21

VSS15 VSS16

DQS#2 DM2

DQS2 VSS17

VSS18 DQ22

DQ18 DQ23

DQ19 VSS19

VSS20 DQ28

DQ24 DQ29

DQ25 VSS21

VSS22 DQS#3

DM3 DQS3

VSS23 VSS24

DQ26 DQ30

DQ27 DQ31

VSS25 VSS26

CKE0 CKE1

VDD1 VDD2

NC1 A15

BA2 A14

VDD3 VDD4

A12/BC# A11

A9 A7

VDD5 VDD6

A8 A6

A5 A4

VDD7 VDD8

A3 A2

A1 A0

VDD9 VDD10

CK0 CK1

CK0# CK1#

VDD11 VDD12

A10/AP BA1

BA0 RAS#

VDD13 VDD14

WE# S0#

CAS# ODT0

VDD15 VDD16

A13 ODT 1

S1# NC2

VDD17 VDD18

NCTEST VREF_CA

VSS27 VSS28

DQ32 DQ36

DQ33 DQ37

VSS29 VSS30

DQS#4 DM4

DQS4 VSS31

VSS32 DQ38

DQ34 DQ39

DQ35 VSS33

VSS34 DQ44

DQ40 DQ45

DQ41 VSS35

VSS36 DQS#5

DM5 DQS5

VSS37 VSS38

DQ42 DQ46

DQ43 DQ47

VSS39 VSS40

DQ48 DQ52

DQ49 DQ53

VSS41 VSS42

DQS#6 DM6

DQS6 VSS43

VSS44 DQ54

DQ50 DQ55

DQ51 VSS45

VSS46 DQ60

DQ56 DQ61

DQ57 VSS47

VSS48 DQS#7

DM7 DQS7

VSS49 VSS50

DQ58 DQ62

DQ59 DQ63

VSS51 VSS52

SA0 EVENT#

VDDSPD SDA

SA1 SCL

VTT1 VTT2

G1 G2

FOX_AS0A621- N2R6-7H

JDIMM2 (Ch A0 H=5.2 STD) JDIMM4 (Ch B0 H=5.2 REV)

+1.35V_MEM

+SA_DIMM_V REFDQ

+SA_DIMM_VR EFDQ_Q

+SA_DIMM1_VR EFDQ

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

206

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

201

203

205

_ _

_ _ _ _

_ _

_ _