Page 1

5

4

3

2

1

Model: Mission Hills/Sawgrass

PCB Ver: A00

PCB Number: 10097-1

SCH Ver: 06

PCBA:

D D

C C

B B

A A

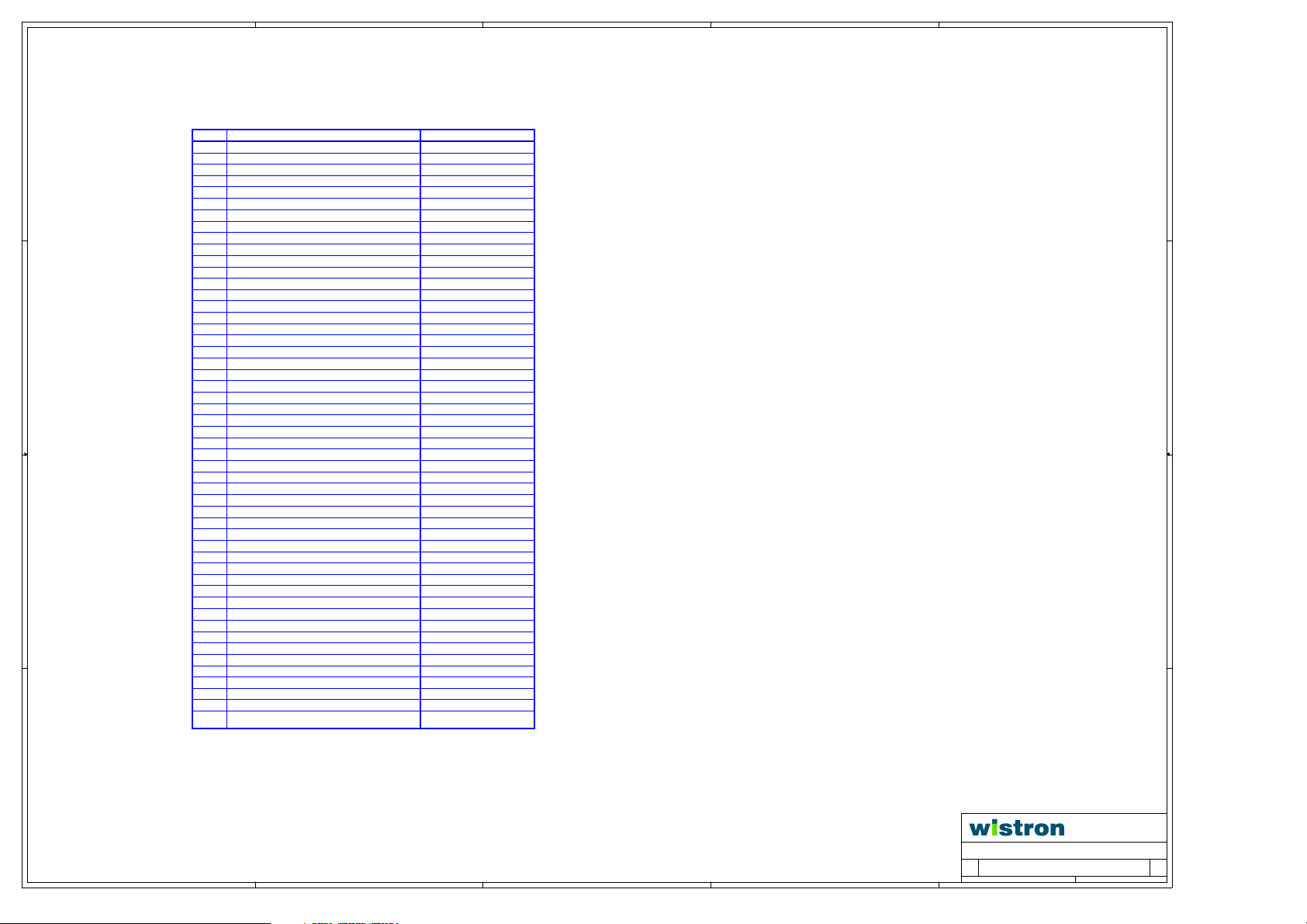

TITLE

PAGE

01

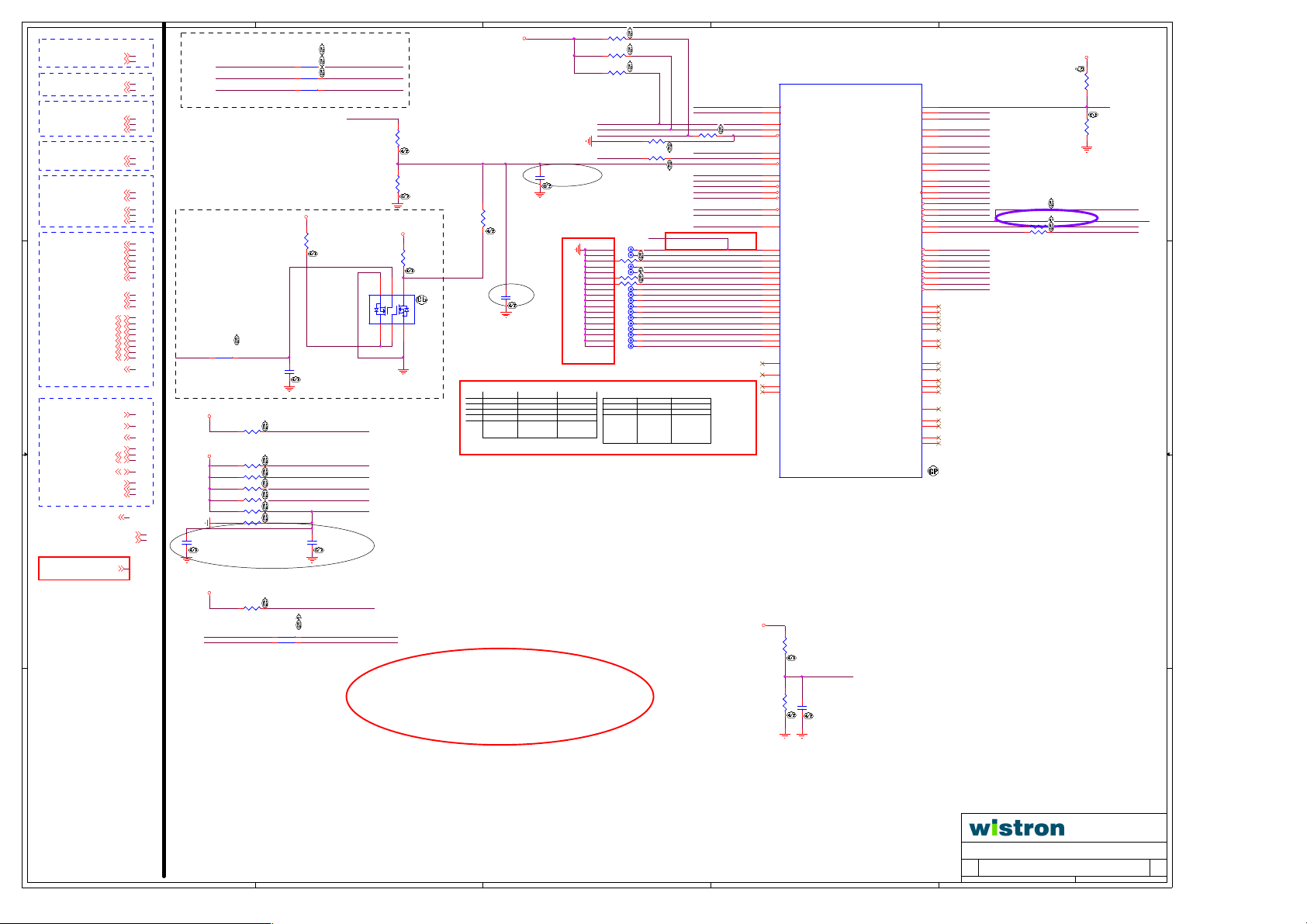

Cover Page

BLOCK DIAGRAM

02

03 Power Delivery

POWER GOOD AND RESET DIAGRAM

04

05

CLOCKS DIAGRAM

06

Power Sequence

POWER Map

07

08

GPIO

09

CLOCK GEN - CK505

CPU LGA 1155_1

10

CPU LGA 1155_2

11

CPU LGA 1155_3

12

CPU LGA 1155_4

13

14 XDP/80 PORT HEADER

DDR3 CHA DIMM 0

15

TBD

16

DDR3 CHB DIMM 0

17

18

TBD

19

PCH_Cougar_AUDIO/GPIO/SPI

20

PCH_Cougar_CLK/FDI/ONFI

PCH_Cougar_SATA/FAN/DP

21

PCH_Cougar_PCI/PCIE/DMI/USB

22

PCH_Cougar_GND/STRAPS

23

PCH_Cougar_POWER

24

SATA Port

25

PCIEX16 CONNECTOR

26

VGA Port

27

HDMI Port

28

TBD

29

FRONT USB

30

USB+RJ45 / REAR USB

31

32 Gb LAN RTL8151ED

33

AUDIO CX20641/CX20651

AUDIO CODEC JACKS

34

DSW

35

SIO SCH5514E

36

KeyBoard and MouSe

37

Serial & Parallel port

38

39

FAN CIRCUITS/HOLE

TBD

40

PCIEX1 CONNECTOR

41

TBD

42

TBD

43

TBD

44

45

PWR/FNT PNL

46

DUAL POWER

47

DDR POWER

SYSTEM POWER

48

CPU_VTT & CPU_SA49

50 CPU_VRD 12-1 & CPU_AXG

51 CPU_VRD 12-2

Quantity

PCB BOARD SIZE

4 Layers

244mmX 218mm

BOM Configuration

Unmount:(R)

Unmount after MP (X)

SB BUILD

Sugar Bay :

LGA1155 : Sandy Brighe

Chipset : Cougar Point H61

LAN : Gb LAN RTL8151ED

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Mission Hills

C

Rosa_Mission Hills

C

Rosa_Mission Hills

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

1 51Sunday, March 20, 2011

1 51Sunday, March 20, 2011

1 51Sunday, March 20, 2011

of

of

of

SA

SA

SA

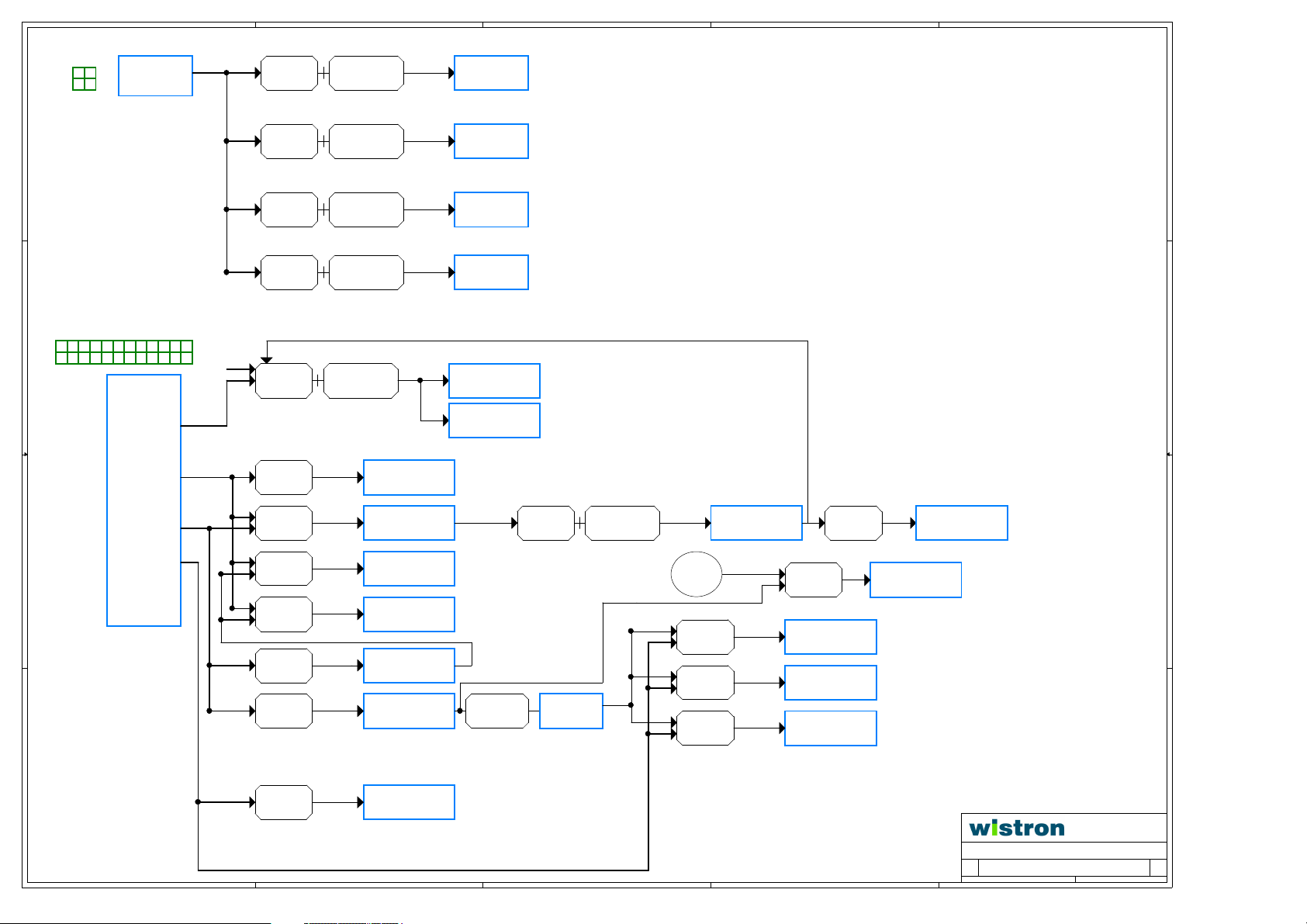

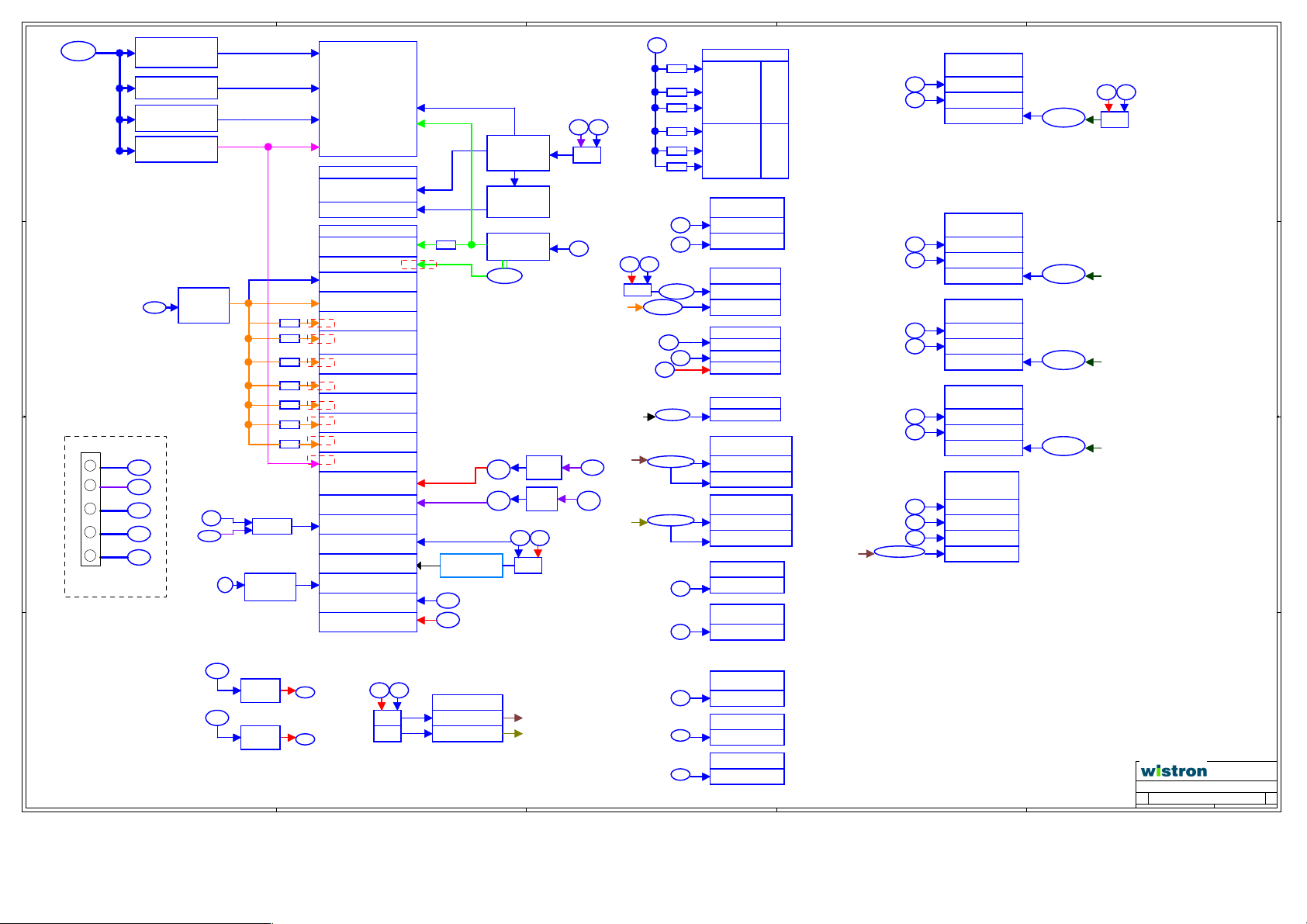

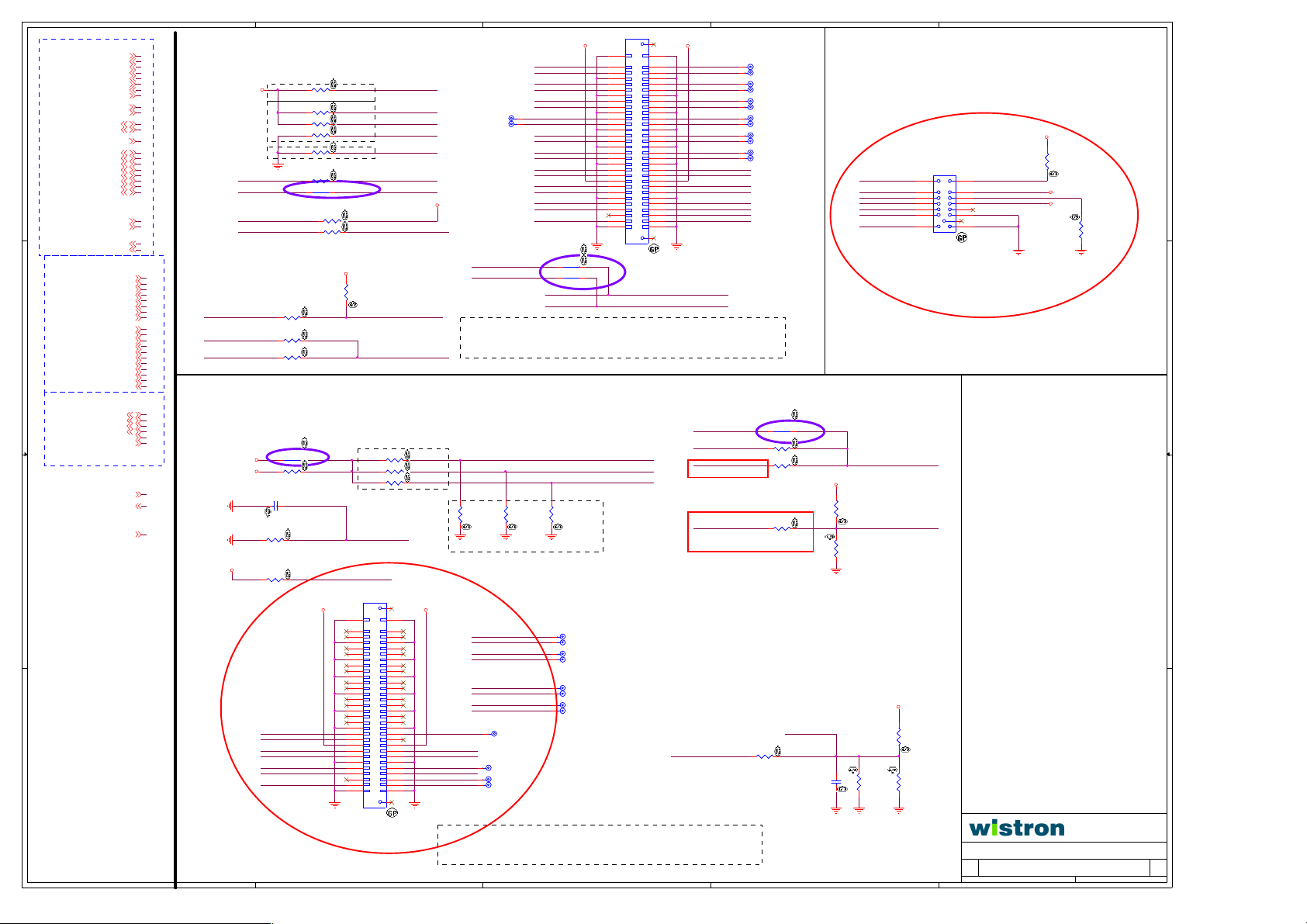

Page 2

5

PCB BOARD SIZE

244mmX 218mm

4 Layer

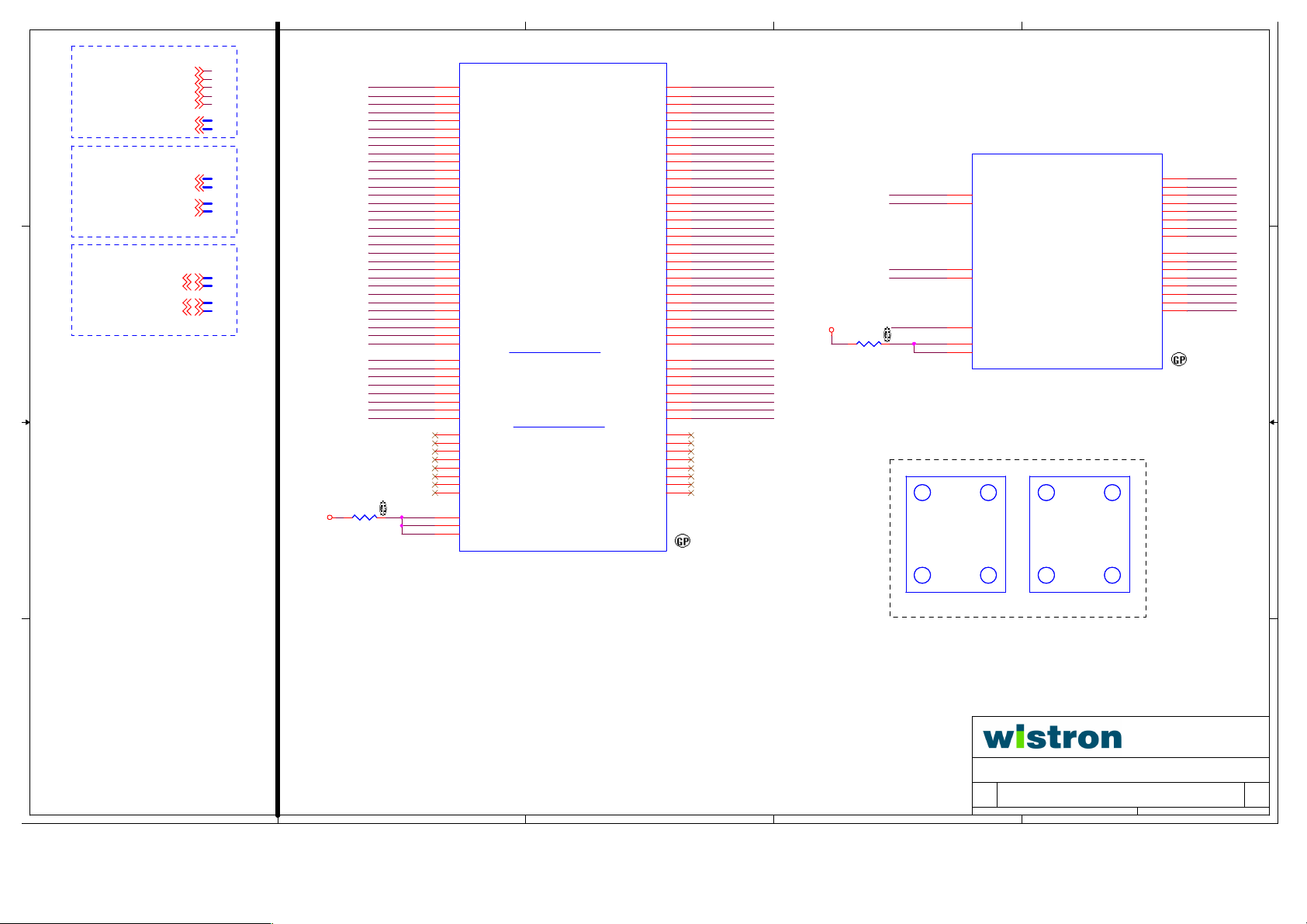

Internal Slot/Header

VRM 12

( 3 Phase 95W)

Front/Rear IO

Chipset

D D

PCIE_X16

PCI EXPRESS Gen2

4

INTEL

Sandy Bridge

SOCKET FCLGA LGA1155

(95W)

0.9144mmX0.9144mm

3

Channel A

64 bit

1066/133 3MHZ

Channel B

64 bit

1066/133 3MHZ

DDR3 DIMM

Unbuffered 4GB

DDR3 DIMM

Unbuffered 4GB

2

1

100MHz

100MHz

D-SUB PORT

HDMI PORT

C C

USB2.0X2 FRONT HEADER

USB2.0X2 FRONT HEADER

USB2.0x2 REAR (+RJ45)

USB 2.0 *10

SPI Flash ROM

4MB/2MB

RGB

Port D

480Mb/S

SPI BUS

USB2.0x2 REAR

B B

USB2.0x2 REAR

SATA *4

REAR

Line - IN

REAR

Line - Out

REAR

MIC -IN

FRONT

A A

MIC -IN

FRONT

HP - OUT

5

HDA CODEC

CX20641/20651

SATA2.0 BUS

High Definition Audio

4

FDI

DMI

INTEL PCH

Sugar Bay

FCBGA 942PIN

27mm X 27mm

LPC BUS

SIO SCH5514E

COM + PS/2 KBMS

REAR HEADER

PECI

Wait for change

PCIE Gen1 Interface

PCIE Gen1 Interface

PCIE Gen1 Interface

PCIE Gen1 Interface

133MHz

100MHz

96MHz

14.318M Hz

32.768K Hz

FAN CNTL

3

PCIE X1

PCIE X1

PCIE X1

Realtek LAN

RTL8111E-VL

25M

32.7K

CPU 1X4 FAN

SYS 1X3 FAN

(For MT)

SYS 1X3 FAN

(For ST/DT)

RJ45

2

14.318M Hz

33MHz

24MHz or 48MHz

100 MHz

120 MHz

133 MHz

PCH

CLOCK

Buffer

25M

ATX-24PIN PWR CONN CPU-4PIN CONN

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Mission Hills

C

Rosa_Mission Hills

C

Rosa_Mission Hills

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

2 51Sunday, March 20, 2011

2 51Sunday, March 20, 2011

2 51Sunday, March 20, 2011

SA

SA

SA

www.schematic-x.blogspot.com

Page 3

5

CPU 2X2 POWER CONN

VCC12CPU

Peak 18A

Continue 14A

PWM

NCP6131

NCP5901*3

3 Phase Design

4

AOD452AL*3

AOD472AL*6

V_CPU_CORE

TDC=85A

Imax=112A

3

2

1

D D

PWM V_AXG

NCP6131

NCP5901*1

AOD452AL*1

AOD472AL*2

TDC=25A

Imax=35A

1 Phase Design

PWM V_CPU_VCCIO

NCP1589D

AOD452AL*1

AOD472AL*1

TDC=7.5A

Imax=17A

1 Phase Design

LDO V_SA

APL5611

ATX 2X12 POWER CONN

C C

+12V

10 A

VCC

14 A

VCC5A

1A

B B

VCC3

-12V

19 A

0.2A

V_SM

SB3V

COMP

LM358 AO4468

LDO

APL5315

SWITCH

N-MOSFET

P-MOSFET

SWITCH 5VDUAL_USB_R

N-MOSFET

P-MOSFET

SWITCH 5VDUAL_USB_F

N-MOSFET

P-MOSFET

P-MOSFET

AO3409 TDC= ?A

LDO

APL1085

AOD472AL*1

N-MOSFET

V_3P3_DAC_FB

Imax=100mA

5V_DUAL

Imax= 13.3A

Imax= 3A+1A

Imax= 2A

Imax= 1.5A

TDC=?mA

TDC= ?A

TDC= ?A

TDC= ?A

SB5V

Imax= 1.5A

VCC3A

TDC= 1.5A

TDC=8.8A

Imax=8.8A

V_1P05_PCH

TDC=6.2A

Imax=6.2A

V_1P05_ME

TDC=?A

Imax=1.8A

P-MOSFET

AO3409

1 Phase Design

PWM V_SM

NCP1589

Imax= 1.5A

SB3V

TDC= 1.5A

AOD452AL*1

AOD472AL*1

BATTERY

SWITCH V_3P3_EPW

N-MOSFET

P-MOSFET

SWITCH V_3P3_PCIVAUX

N-MOSFET

P-MOSFET

SWITCH V_3P3_LAN

N-MOSFET

P-MOSFET

TDC=?A

Imax=18A

LDO

APL5336

DIODE

BAT54C

TDC= ?A

Imax= 0.016A

TDC= ?A

Imax= 1.5A

TDC= ?A

Imax= 0.218A

V_SM_VTT

TDC=1A

Imax=1A

V_3P0_BAT_VERG

TDC=6 uA

Imax=6 uA

A A

LDO

APL1085

5

V_1P8_SFR

TDC=1A

Imax=1.6A

4

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Mission Hills

C

Rosa_Mission Hills

C

Rosa_Mission Hills

C

Date: Sheet

Date: Sheet

3

2

Date: Sheet

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

3 51Sunday, March 20, 2011

3 51Sunday, March 20, 2011

3 51Sunday, March 20, 2011

of

of

of

SA

SA

SA

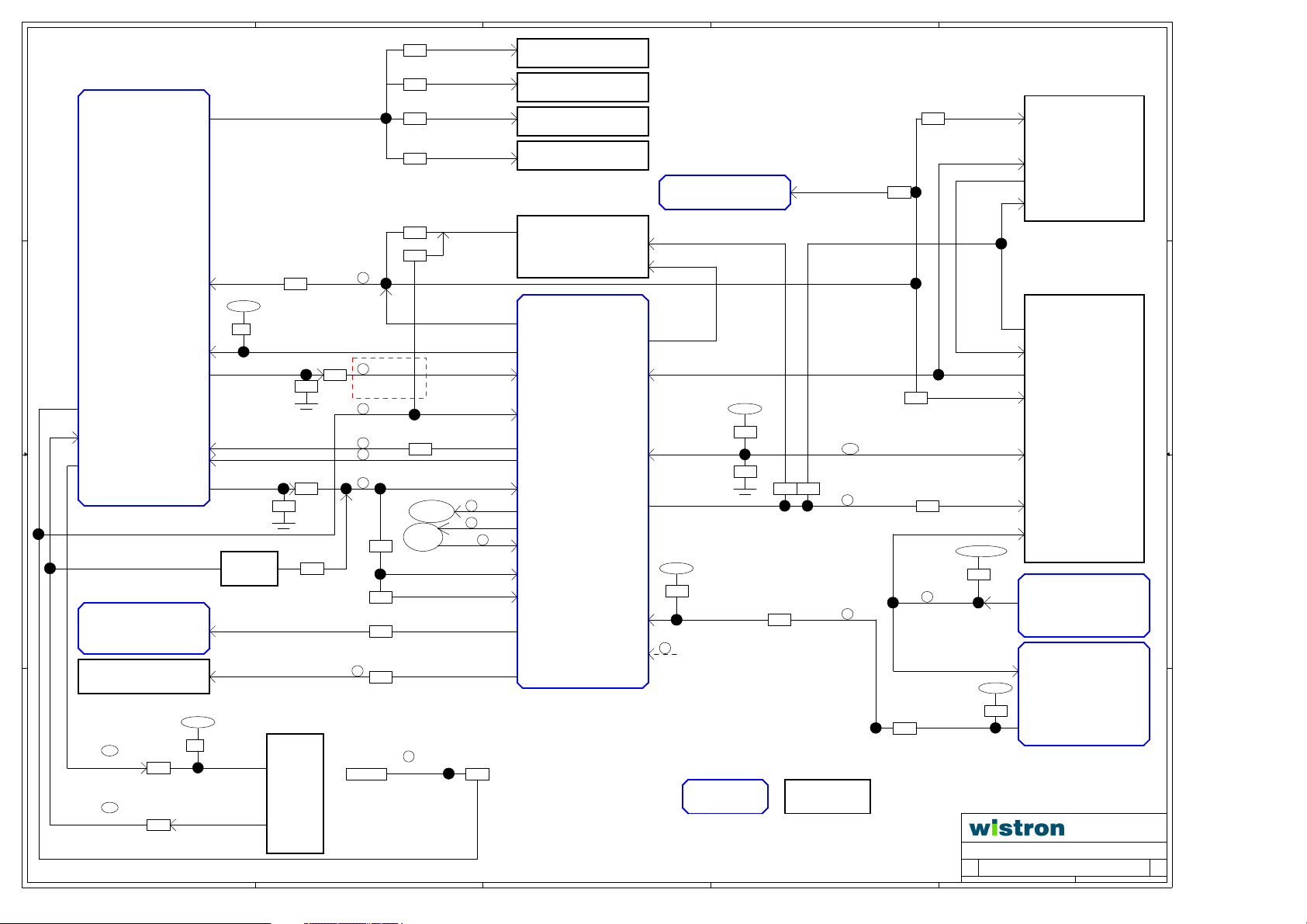

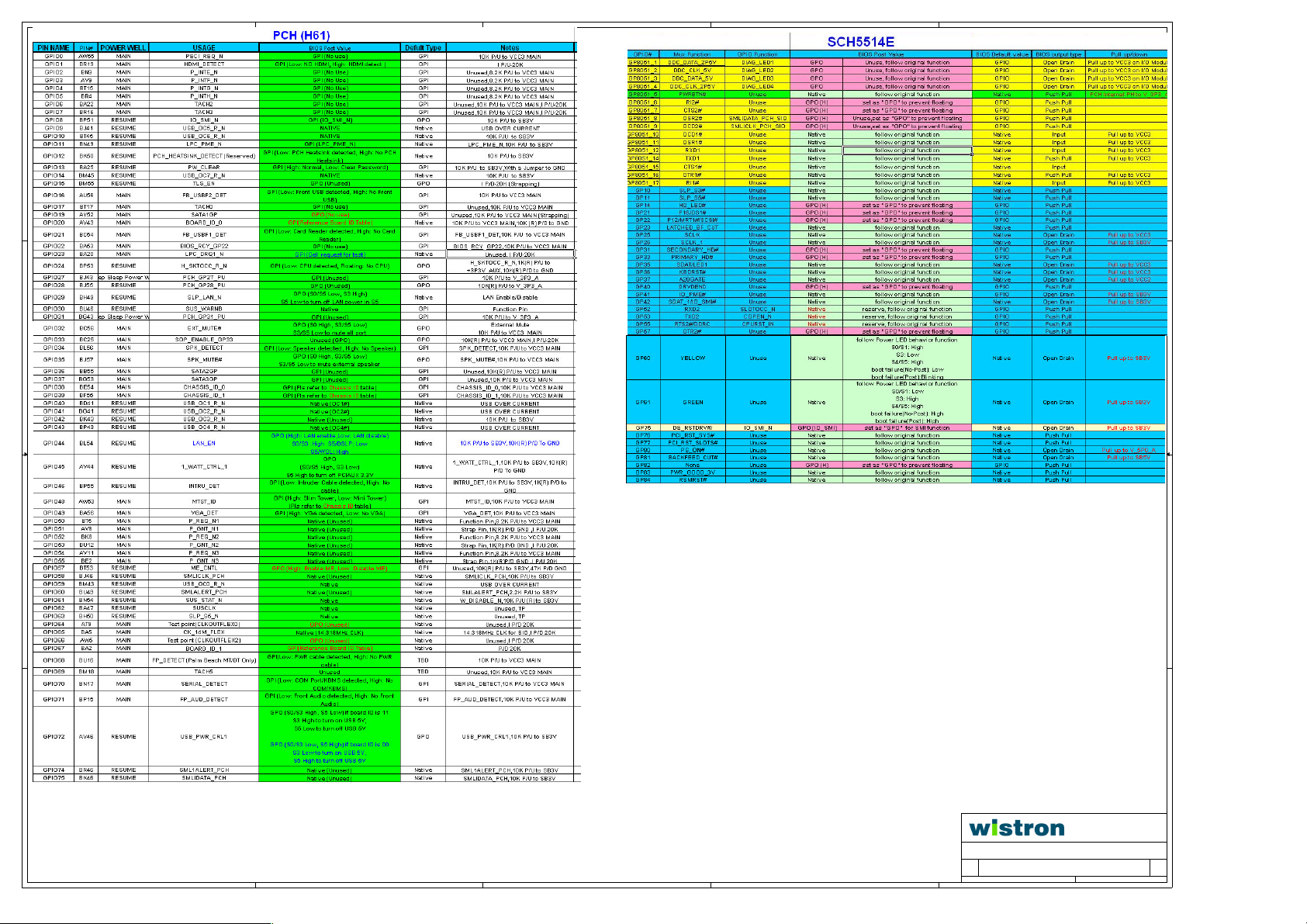

Page 4

5

PLTRST#

D D

PIN97

PLTRST_SL_N

SIO SCH5514E

LRESET#

PIN16

PLTRST_SIO_N

VCC3

Rs

C C

PWRBTN#

PIN36

PWROK_PS

PIN125

PSON#

PIN55

B B

AUDIO CX20641

PCI RISER

KBRST#

PIN120 AM40

RSMRST#

PIN60

SLP_S3#

PIN123

SLP_S4#

PIN124

PWRGD_3V

PIN59

RESET#

RSMRST_N PCH_RSMRST_N

SLP_S3_N

SLP_S4_N

PWRGD_3V_L PWRGD_3V

PWRGD_3V

Logic

AUD_LINK_RST_N_R

PCIRST_SL_N

RESET#

SB5V

9

PS_ON_N

A A

SIO_PSON*

Rs

Rs

ATX_ON_N

Rs

Rs

Rs

Rs

Rs

POWER

PS_ON#

4

PCIERST_N

Rs

PCIERST_N

Rs

PLTRST_RISER_N

Rs

PCIERST_N

Rs

PCH_XDP_RST

Rs

Rs

17

PLTRST_N

KBRST_N

6

Rs

The signal is active after SLP_SUS

2

8

7

13

16

LEDH1

Rs

Rs

Rs

Rs

Rs

SB5V SB3V

5V_DUAL

2

PB_IN_N

SW_ON_N

SLP_S3_PCH_N

LAN_PWROK

AUD_LINK_RST_N

P_PCIRST_N

3

2

1

PCI EXPRESS X1

RESET#

PCI EXPRESS X1

RESET#

XDP_PLTRST_N

PCI EXPRESS X16

RESET#

Rs

PCI EXPRESS X1

RESET#

RESET#

Pin46

XDP FOR PCH

XDP_PWRGD

Pin39

DBR#

Pin48

LAN Realtek

RTL8151ED

PCH_XDP_PWRGD

RESET#

Pin2

PLTRST_BLAN_N

H_TAPPWRGOOD

Rs

Intel PCH

PLTRST#

AV34

RCIN#

RSMRST#

BK38

PWRBTN#

AK36

SLP_S3#

AV35

SLP_S4#

AP35

PWROK

3

4

AM24

SLP_SUS#

SUS_WARN#

5

SUS_ACK#

MEPWROKPCH_MEPWROK_R

AL33

LAN_RST#

AY31

ACZ_RST#

AV14

PCIRST#

AH10

Rs

JTAG_RST#

SYS_RST#

CPUPWRGD

PCH_SYSPWROK

RTCRST#

H_TRST_N

FP_RST_N

AL38

V_SM

H_CPURST_N

Rd

Rs

H_DRAMPWRGDDRAMPWRGD

AW32

11

Rs

H_PWRGD

B38

SB3V

Rs Rs

Rs

AT38

AK24

PCH_SYSPWROK

1

Rs

15

Rs

H_PWRGD

V_1P1_VTT

Rs

12

14

H_VTTPWRGD

VRMPWRGD

Rs

VCC3

Rs

XDP FOR CPU

RESET#

Pin41

DBR#

Pin48

TRST#

Pin54

H_TAPPWRGOOD

Pin45

CPU LGA1155

H_TAPPWRGOOD

AK34

TRST#

AM39

DBR#

AL40

RSTIN#

AF34

SM_DRAMPWROK

AH37

VCCPWRGOOD

AH36

VTTPWRGD

AG37

ISL95870

VTTPGOOD

Pin10

VRD12

EN

Pin1

VR_RDY

Pin39

10

PSPWRGD_SIO

PWRGD_PS_D

<Variant Name>

<Variant Name>

Rs

PSPWRGD

PWROK_PS

CHIP SOCKET or SLOT

SW_ON_N

5

4

3

2

<Variant Name>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Mission Hills

C

Rosa_Mission Hills

C

Rosa_Mission Hills

C

Date: Sheet

Date: Sheet

Date: Sheet

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

4 51Sunday, March 20, 2011

4 51Sunday, March 20, 2011

4 51Sunday, March 20, 2011

of

of

of

SA

SA

SA

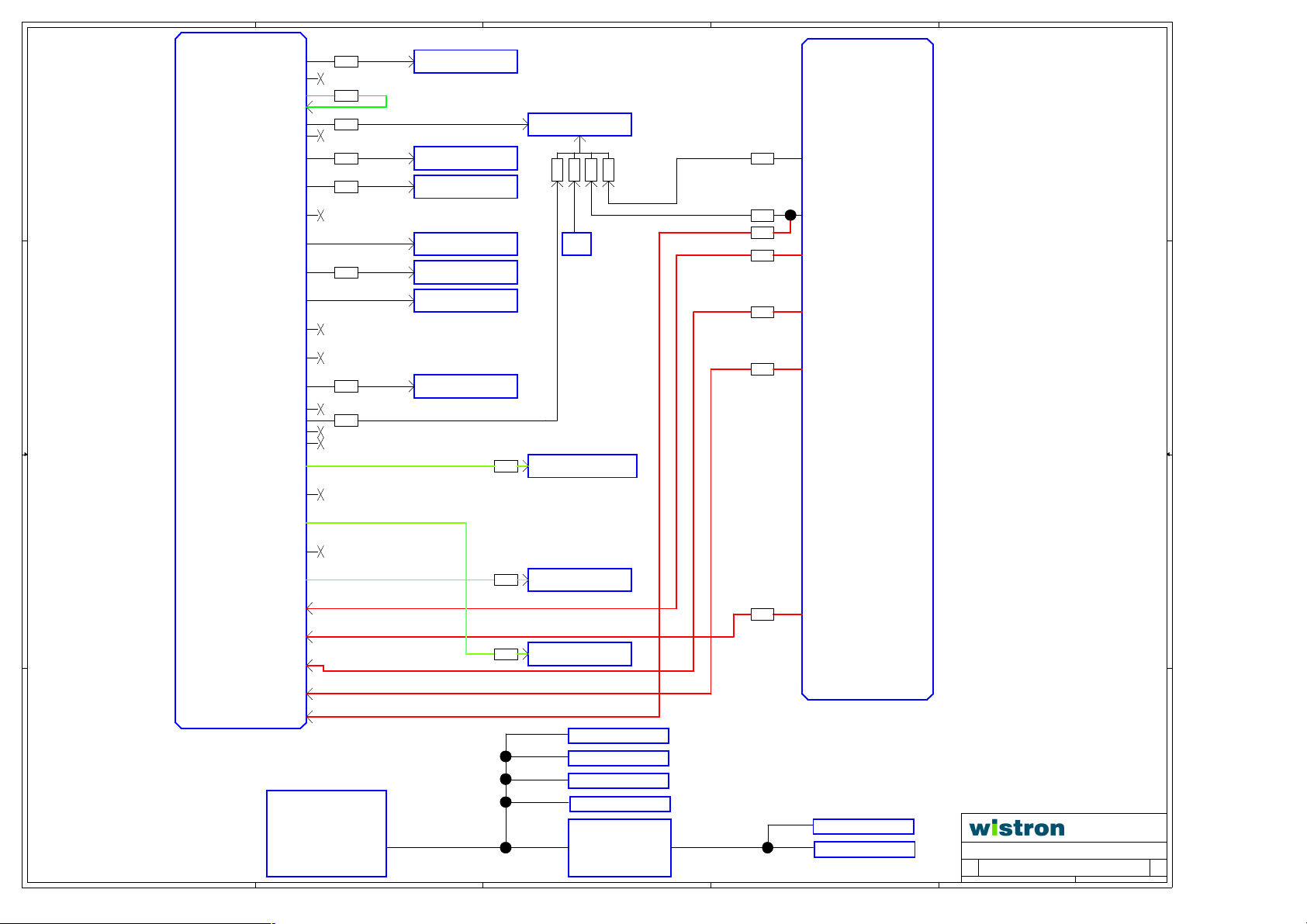

Page 5

5

Intel PCH

CLKOUT_PCI0

CLKOUT_PCI1

Loopback

D D

C C

B B

CLKOUT_PCI2

PCICLK_IN

CLKOUT_PCI3

CLKOUT_PCI4

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

CLKOUT_PCIE0_N

CLKOUT_PCIE0_P

CLKOUT_PCIE1_N

CLKOUT_PCIE1_P

CLKOUT_PCIE2_N

CLKOUT_PCIE2_P

CLKOUT_PCIE3_N

CLKOUT_PCIE3_P

CLKOUT_PCIE4_N

CLKOUT_PCIE4_P

CLKOUT_PCIE5_N

CLKOUT_PCIE5_P

CLKOUT_PCIE6_N

CLKOUT_PCIE6_P

CLKOUT_PCIE7_N

CLKOUT_PCIE7_P

CLKOUT_FLEX0

CLKOUT_FLEX1(14M)

CLKOUT_FLEX2

CLKOUT_FLEX3(48M)

CLKOUT_PEG_A_N

CLKOUT_PEG_A_P

CLKOUT_PEG_B_N

CLKOUT_PEG_B_P

CLKOUT_BCLK0_N

CLKOUT_BCLK0_P

CLKOUT_BCLK1_N

CLKOUT_BCLK1_P

CLKOUT_DMI_N

CLKOUT_DMI_P

CLKIN_DOT_N

CLKIN_DOT_P

CLKIN_BCLK_N

CLKIN_BCLK_P

CLKIN_SATA_N

CLKIN_SATA_P

CLKIN_DMI_N

CLKIN_DMI_P

Rs

Rs

Rs

R0

R0

R0

R0

Rs

4

LPC PORT80

3

2

CK505

BTM: Buffer Through Mode

Need CK505 to provide 4 clock to PCH

FCIM: Full Clock Intergration Mode

Remove CK505

1

SIO SCH5514E

CPU XDP HEADER

R0R0R0

R0

Rs

USB48

PCIEX1(RISER)

REF

DOT96C_LR

DOT96T_LR

Realtek LAN

OSC

Rs

Rs

Rs

PCH XDP HEADER

PCIEX1(RISER)

Rs

Rs

SATAC_LR

SATAT_LR

PCIEXC_LR

PCIEXT_LR

PCIEX1(RISER)

PCIE_X16 (RISER)

R0

CPU DMI

R0

CPUC_LR

CPUT_LR

R0

Rs

CPU BCLK

REFCLKIN

Note: Red Color is Gen2 spec.

Note: R0 is 0 ohm optional resister

A A

Note: Rs is serie resister

Note: Green Color is direct-parallel option

5

4

SMB_CLK_RESUME

SMB_DATA_RESUME SMB_DATA_MAIN

DDR3 CHA(VREF)

DDR3 CHB(VREF)

PCIEX16

PCIEX1

3

SMB_CLK_MAIN

DDR3

Clock Generator

2

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Mission Hills

C

Rosa_Mission Hills

C

Rosa_Mission Hills

C

Date: Sheet

Date: Sheet

Date: Sheet

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

5 51Sunday, March 20, 2011

5 51Sunday, March 20, 2011

5 51Sunday, March 20, 2011

of

of

of

SA

SA

SA

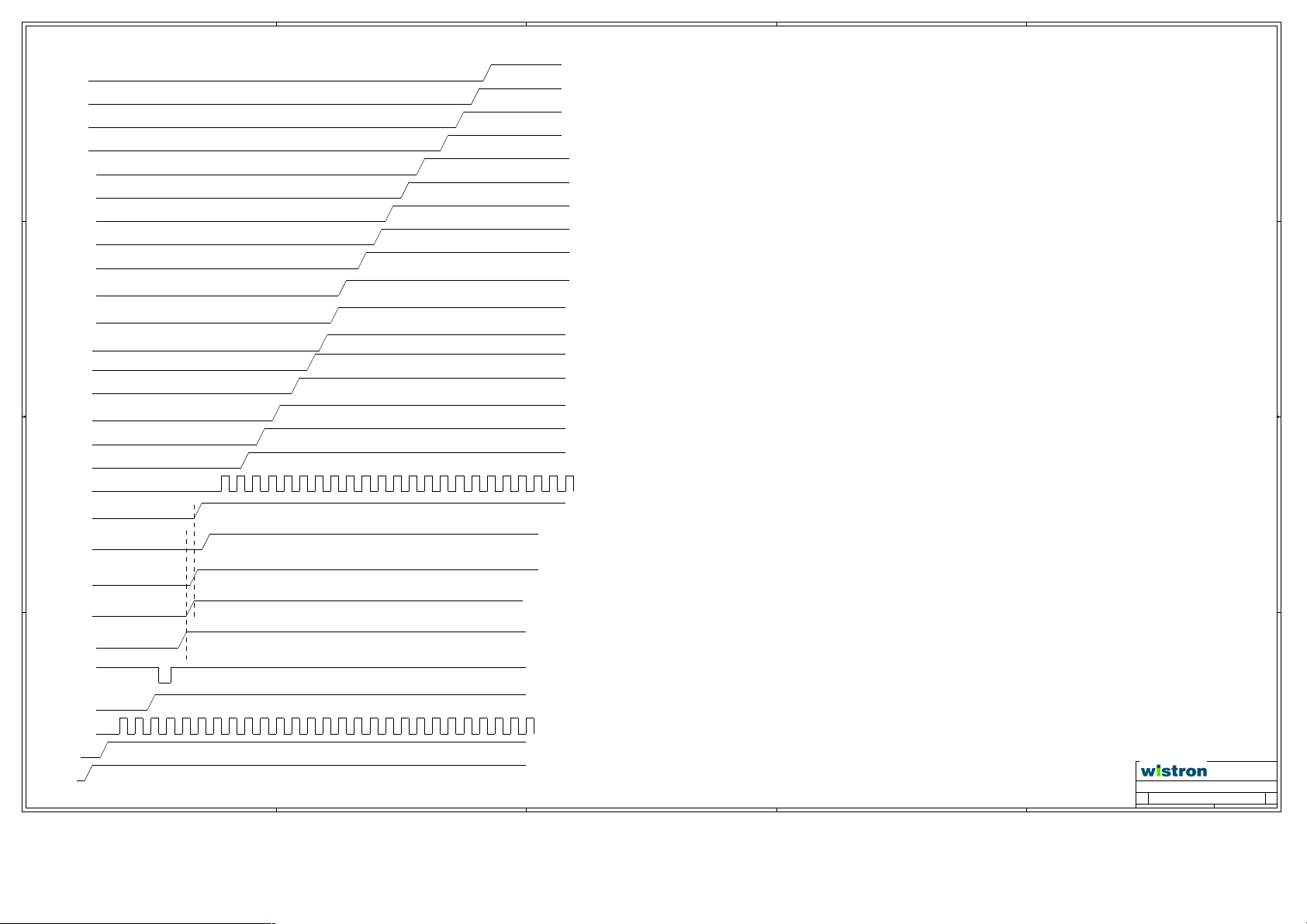

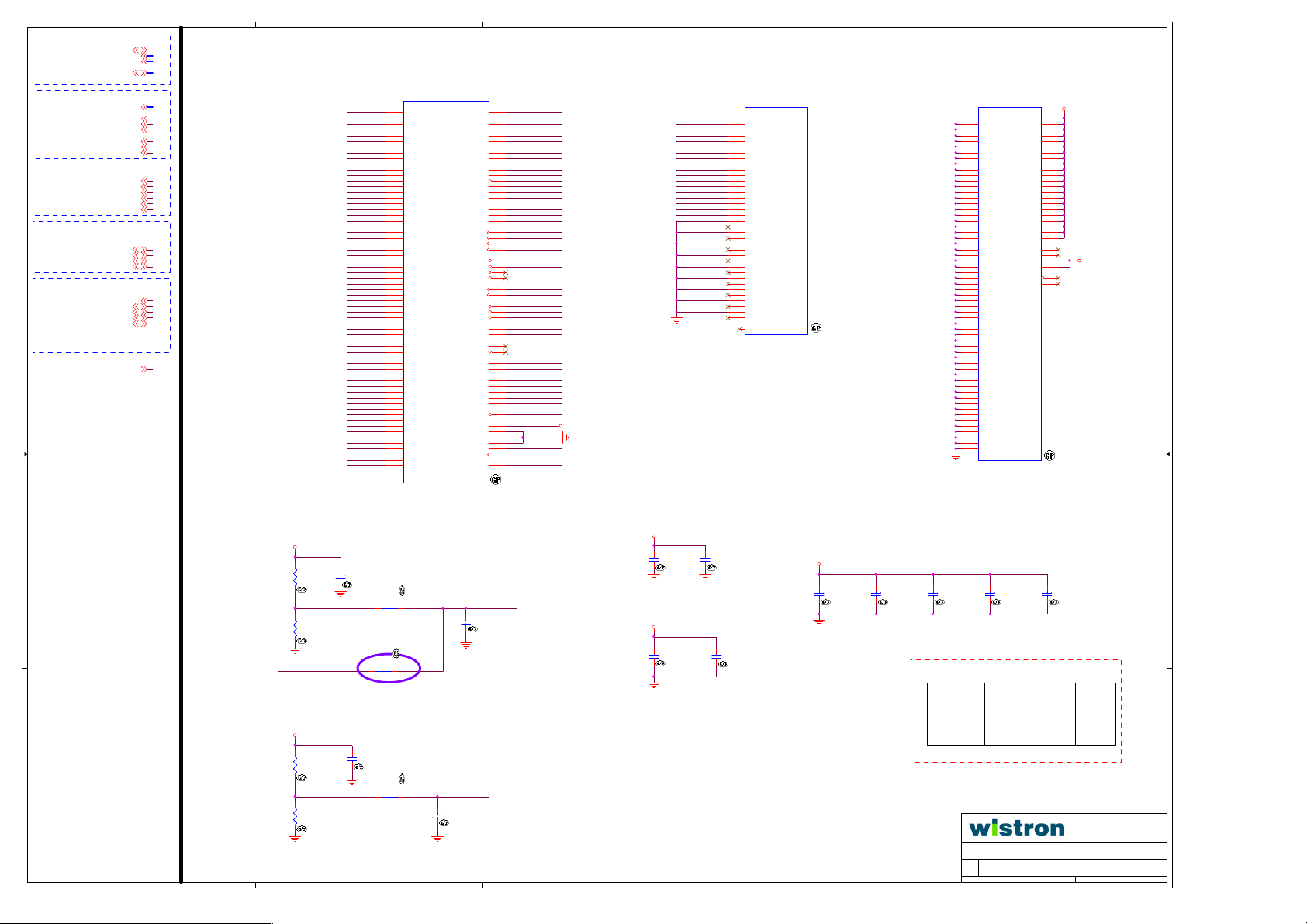

Page 6

5

4

3

2

1

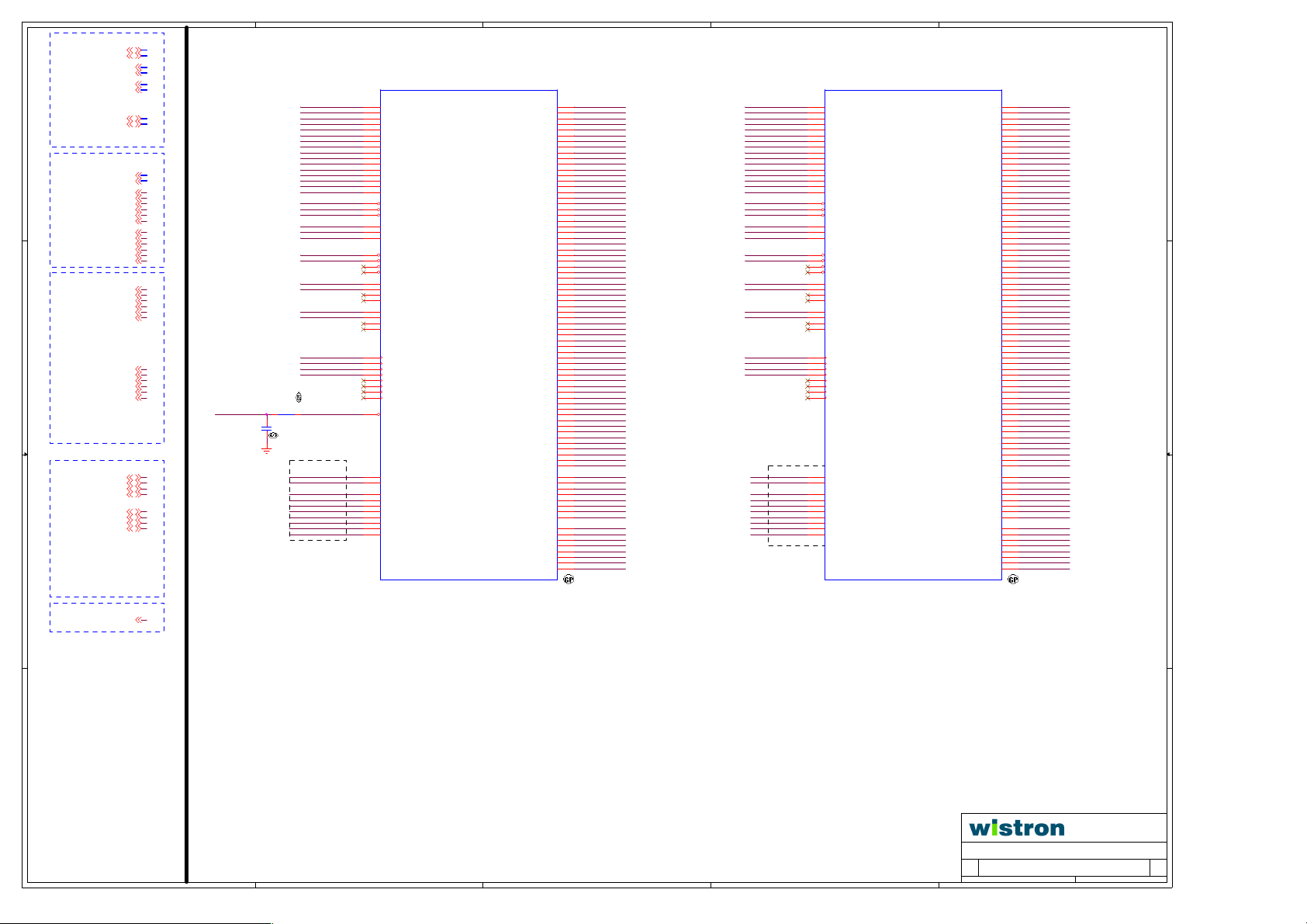

POWER ON SEQUENCE

DMI Mes sage

PLTRST

H_PWRGD

D D

PCH_SYS PWROK

PWRGD_3 V

PSPWRGD _SIO

VCCP/V_ SA/VAXG

H_VTTPW RGD

CPU_VCC IO

+12/VCC /VCC3

C C

H_DRAMP WRGD

V_SM

PS_ON_N

SIO_PSO N*

SLP_S3_ N

SLP_S4_ N

—

SW_ON_N

—

PB_IN_S IO_N

SUSCLK

PCH_RSM RST_N

B B

SUS_ACK

SUS_WAR N

SB5V/SB 3V

SLP_SUS B

PWR But ton

5VA/3VA

A A

—

RTCCLK

RTCRST

VccRTC

5

4

3

2

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

Rosa_Mission Hills

D

Rosa_Mission Hills

D

Rosa_Mission Hills

D

Date: Sheet

Date: Sheet

Date: Sheet

1

Wistr on Inco rpor ated

Wistr on Inco rpor ated

Wistr on Inco rpor ated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

6 51Sunday, March 20, 2011

6 51Sunday, March 20, 2011

6 51Sunday, March 20, 2011

of

of

of

SA

SA

SA

Page 7

5

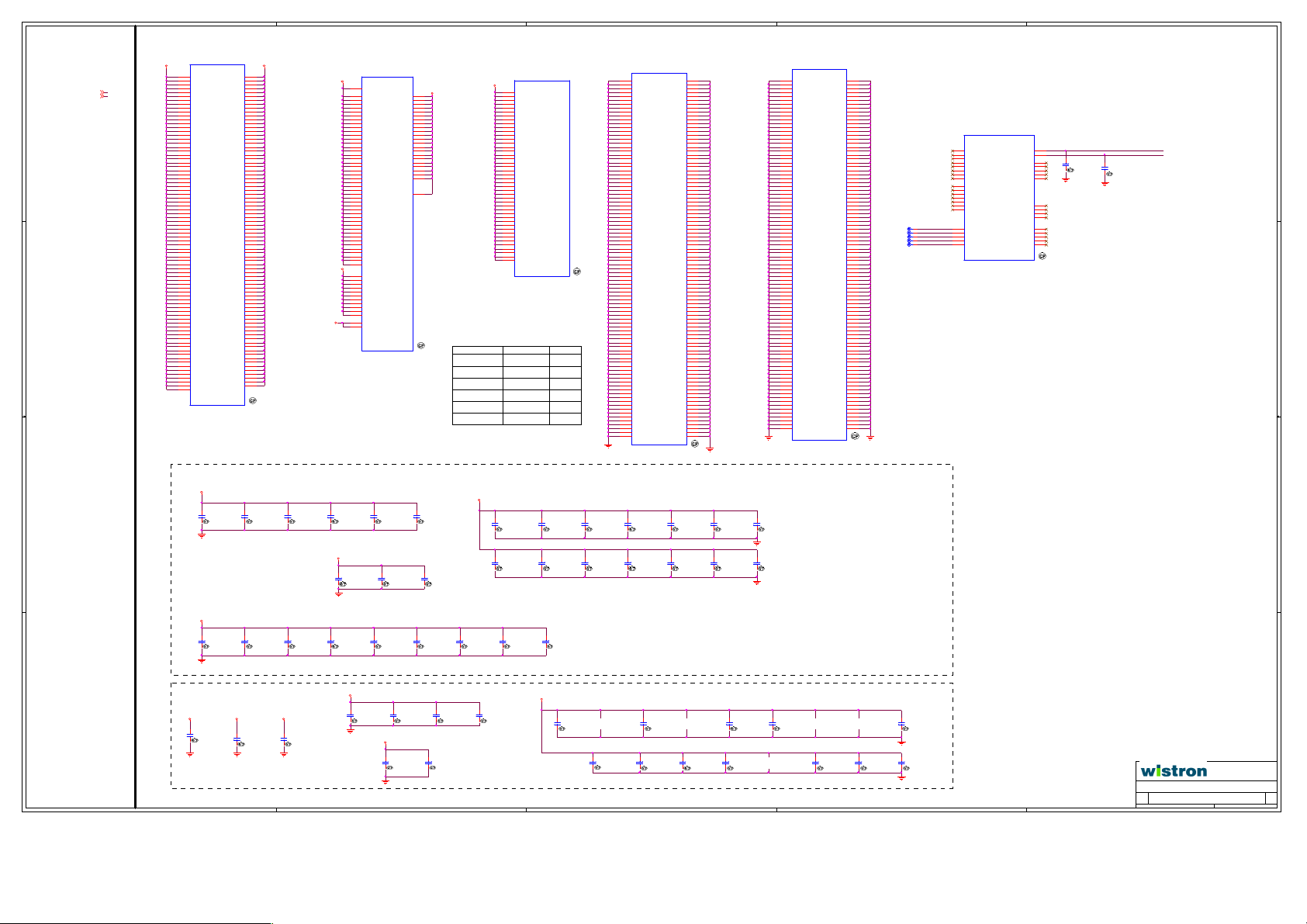

CPU Core Regulator(VRD 12)

VCC12CPU

D D

VTT

85A VR_TDC112A 0.65V-1.3V V_CPU_CORE

3-phase Switching

NCP6131

GFx VR

0.65V-1.3V TDC=25A Imax=35A

1-phase Switching

NCP6131

V_SA

0.85V or 0.925V TDC=8.8A Imax=8.8A

1-phase Switching

APL5611

1.00V or 1.05V TDC=7.5A Imax=17A

1-phase Switching

NCP1589D

V_AXG

V_SA

V_CPU_VCCIO

65A

Intel LGA1155

Sandy Bridge

25A

8.8A

7.5A

DDR3 DIMM X2 & Termination

+1.5V

V_SM(S0,S1) 7A

V_SM(S3) 1.0A

+0.75V

V_SM_VTT(S0) 1A

Intel PCH H61

1.8V

V_1P8_SFR 0.5A

(VCCVRM)

1.8V V_NAND_IO ?A

(VCCPNAND)

V_1P05_ME 1.8A

1.05V

V_1P05_PCH

1.05V 6.2A

C C

B B

V_SM

+12V

VCC5A

VCC

VCC3

-12V

POWER SUPPLY

LM358COMP

BAT

VCC3A

VCC

DIODE BAT54C

V_3P3_DAC_FB

3.3V 100mA Linear

APL5315

Filter

Filter

Filter

Filter

Filter

Filter

Filter

(VCCASW)

1.05V

V_1P05_PCH 6.2A

(VCCIO)

V_1P05_PCH_SRC ?A

1.05V

(VCCCLKDMI)

1.05V

VCCSATA_PLL_PCH 32mA

(VCCSATAPLL)

1.05V

VCCDMI_PLL_PCH 45mA

(VCCAPLL_EXP)

1.05V

VCCIPL_PLL_PCH 6mA

(VCCFDIPLL)

1.05V

VCCCLK_PLL_PCH 52mA

(VCCACLK)

1.05V

VCCA_DPLLA 78mA

(VCCADPLLA)

1.05V

VCCA_DPLLB 78mA

(VCCADPLLB)

V_CPU_VCCIO ?A

1.05V

(VCCDMI & V_PROC_IO)

SB3V 0.123A

3.3V

(VCCSUSHDA & VCCSUS)

V_3P3_A

VCC3A

(VCCDSW3_3)

V_3P0_BAT_VREG 1mA

(DSWVRMEN)

VCC3 0.203A

3.3V

(VCC3_3)

3.3V

V_3P3_EPW 0.016A

(VCCSPI)

3.3V

V_3P3_DAC_FB 60mA

(VCCADAC)

5V S0

VCC

(V5REF)

5V S3

SB5V

(V5REF_SUS)

4

4.5A

1A

CPU / DDR3

V_SM 1.5V 25A

1-phase Switching

NCP1589

DDR3 MEM_VTT

V_SM_VTT

0.75V 1A Linea r

APL5336

Filter

?A

V_1P8_SFR

1.8V 1.6A Linea r

APL1085

V_NAND_IO

SB3V

VCC3A

VCC3

V_3P3_EPW

TDC= ?A

Imax= 0.016A

1mA

1mA

VCC

SB5V

Switch

P-MOSFET

AO3409

LDO

APL1085

SB3V

VCC5A

VCC

Switch

VCC3

VCC3A

VCC5A

SB3V VCC3

Switch

3

VCC3

V_3P3_LAN

V_1P05_LAN

BAT

SB3V

V_3P3_ EPW

5VDUAL_USB_F

5VDUAL_USB_R

2

Filter

Filter

Filter

Filter

Filter

Filter

CK 505

+3.3V

VDD_48

+3.3V

VDD_PCI

+3.3V

VDD_REF

+3.3V

VDD_SRC TBD mA

+3.3V

VDD_PLL3 TBD mA

+3.3V

VDD_CPU TBD mA

3.3V

(250mA)

0.8V

(80mA)

+12V

VCC3

PCIE X16 Slot

5.5A

+12V

3.0A

3.3V

0.38A

3.3Vaux

V_3P3_PCIVAUX

SB3V VCC3

Switch

1

CX20641/20651

VCC

VCC3

VCC3

(NA mA)

5V

(NA mA)

3.3V

RTL8111E-VL

70mA

3.3V

300mA

1.05V

SCH5514E

+3.0V

4.5

µ

A

+3.3V

22mA

+3.3V S3

17mA

SPI ROM(4MB+2MB)

+3.3V

175mA

USB(4 Front)

5VDUAL_USB_F

S0:

5VDUAL_USB_F

S3:

USB(6 Rear)

5VDUAL_USB_R

S0:

5VDUAL_USB_R

S3:

(0.4A)

(0.6A)

PCIE X1 Slot

+12V

VCC3

+12V

3.3V

3.3Vaux

0.5A

3.0A

0.1A

V_3P3_PCIVAUX

PCIE X1 Slot

+12V

VCC3

+12V

3.3V

3.3Vaux

0.5A

3.0A

0.1A

V_3P3_PCIVAUX

PCIE X1 Slot

+12V

VCC3

(2A)

+12V

(3A)

VCC

-12V

5VDUAL_USB_R

+12V

3.3V

3.3Vaux

Serial Port

P/S2 Header

19mA

+12V

30mA

+5V

-19mA

-12V

1A

+5V

0.5A

3.0A

0.1A

V_3P3_PCIVAUX

CRT

(1A fuse)

+5V_VGA

VCC

HDMI

VCC3

3.3V

(0.5 A fuse x 1)

VCC5A

P-MOSFET

AO3409

A A

5

VCC3A

P-MOSFET

AO3409

SB5V

SB3V

SB5V

Switch

Switch

VCC

USB

5VDUAL_USB_R

(PS/2 X2)

5VDUAL_USB_F

4

+12V

+12V

+12V

3

CPU Fans

200mA

+12V

SYS Fans (MT)

200mA

+12V

SYS Fans (ST/DT)

200mA

+12V

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

Rosa_Mission Hills

D

Rosa_Mission Hills

D

Rosa_Mission Hills

D

Date: Sheet

Date: Sheet

2

Date: Sheet

1

Wistr on Inco rpor ated

Wistr on Inco rpor ated

Wistr on Inco rpor ated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

7 51Sunday, March 20, 2011

7 51Sunday, March 20, 2011

7 51Sunday, March 20, 2011

of

of

of

SA

SA

SA

Page 8

5

D D

C C

4

3

2

1

B B

A A

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Mission Hills

C

Rosa_Mission Hills

C

Rosa_Mission Hills

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

8 51Sunday, March 20, 2011

8 51Sunday, March 20, 2011

8 51Sunday, March 20, 2011

of

of

of

SA

SA

SA

Page 9

5

PCH Buffer CLOCK

CK_96M_DREF_DP22

CK_96M_DREF_DN22

CK_SATA_PCH_DP21

CK_SATA_PCH_DN21

100M_DMI_PCH_DP22

100M_DMI_PCH_DN22

CK_SATA_PCH_DP

CK_SATA_PCH_DN

100M_DMI_PCH_DN

100M_DMI_PCH_DP

R523 10KR2J-3-GPR523 10KR2J-3-GP

1 2

R515 10KR2J-3-GPR515 10KR2J-3-GP

1 2

R396 10KR2J-3-GPR396 10KR2J-3-GP

1 2

R402 10KR2J-3-GPR402 10KR2J-3-GP

1 2

4

3

2

1

14M CLOCK

D D

CK_14M_PCH20

CK_14M_PCH

R375 10KR2J-3-GPR375 10KR2J-3-GP

12

CK_96M_DREF_DP

CK_96M_DREF_DN

R480 10KR2J-3-GPR480 10KR2J-3-GP

12

R477 10KR2J-3-GPR477 10KR2J-3-GP

12

Terminate PCH CLK Inputs

C C

Remove CLK GEN

Use PCH Internal CLK

B B

A A

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Mission Hills

C

Rosa_Mission Hills

C

Rosa_Mission Hills

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

9 51Sunday, March 20, 2011

9 51Sunday, March 20, 2011

9 51Sunday, March 20, 2011

of

of

of

SA

SA

SA

Page 10

5

CLOCK

CK_PE_100M_MCP_DP20

CK_PE_100M_MCP_DN20

CPU_SA

CPU_VTT

D D

CPU_AXG

CPU_VCORE

ITP

C C

OTHER

B B

03/21:follow CRB1.0 rout the CFG[0] to XDP !

VCCSA_VID49

VCCSA_SENSE49

VCCIO_SEL49

VCCTT_SENSE49

VSSTT_SENSE49

VCCAXG_SENSE50

VSSAXG_SENSE50

VCC_SENSE50

VSS_SENSE50

H_VIDSCK_VR50

H_VIDSOUT_VR50

H_VIDALERT_N_VR50

H_TDO14

H_TDI14

H_TCK14

H_TMS14

H_TRST_N14

H_PRDY_N14

H_PREQ_N14

XDP_DBRESET_N14

CK_XDP_S_DN14

CK_XDP_S_DP14

H_BPM#014

H_BPM#114

H_BPM#214

H_BPM#314

H_BPM#414

H_BPM#514

H_BPM#614

H_BPM#714

H_CPURST_N14,36

PLTRST_N14,19,36

H_PWRGD14,19

FP_RST_DBR_N19

H_DRAMPWRGD19,46

H_PECI21,36

H_PROCHOT_N36,50

H_THERMTRIP_N21

H_PM_SYNC_021

H_SKTOCC_N19,36

H_CPURST_N14,36

H_SNB_N23

SMB_CLK_RESUME19,26,32,36,41

SMB_DATA_RESUME19,26,32,36,41

TPEV_SNB_PCUDEBUG_014

MINIMIZE STUB BETWEEN THESE AND RESISTORS AT SINAL PAGE

PLACE IN CRB AREA

H_VIDSCK_VR

H_VIDSOUT_VR H_VIDSOUT

H_VIDALERT_N_VR

R355 0R0402-PAD-2-GPR355 0R0402-PAD-2-GP

1 2

R350 0R0402-PAD-2-GPR350 0R0402-PAD-2-GP

1 2

R329 0R0402-PAD-2-GPR329 0R0402-PAD-2-GP

1 2

Defensive Design

SB3V

12

R341

R341

100KR2J-1-GP

100KR2J-1-GP

PLTRST_N

V_CPU_VCCIO

C460

C460

12

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

PLTRST_CPU_N

R336

R336

1 2

0R0402-PAD-2-GP

0R0402-PAD-2-GP

V_SM

R494 200R2F-L-GPR494 200R2F-L-GP

1 2

R372 1KR2J-1-GP(R)R372 1KR2J-1-GP(R)

1 2

R342 1KR2J-1-GP(R)R342 1KR2J-1-GP(R)

1 2

R338 51R2J-2-GPR338 51R2J-2-GP

1 2

R334 51R2J-2-GP(R)R334 51R2J-2-GP(R)

1 2

R348 51R2J-2-GP(R)R348 51R2J-2-GP(R)

1 2

R352 1KR2J-1-GPR352 1KR2J-1-GP

1 2

SB3V

R606 220R5J-GP(R)R606 220R5J-GP(R)

1 2

H_PROCHOT_N

R343 0R0402-PAD-2-GPR343 0R0402-PAD-2-GP

H_THERMTRIP_N CPU_THERMTRIP_N

R333 0R0402-PAD-2-GPR333 0R0402-PAD-2-GP

12

1 2

1 2

PLTRST_CPU_N1

(R)

(R)

C301

C301

SC100P50V2JN-3GP

SC100P50V2JN-3GP

H_DRAMPWRGD

H_PECI

H_CATERR_N

H_PROCHOT_R_N

CPU_THERMTRIP_N

H_PWRGD

C449

C449

12

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

FP_RST_DBR_N

H_PROCHOT_R_N

4

H_VIDSCK

H_VIDALERT_N

PLTRST_N

2010/12/20

Add EMI Cap

V_CPU_VCCIO

1234

5

6

12

R349

R349

1K3R2F-1-GP

1K3R2F-1-GP

(R)

(R)

12

R365

R365

665R2F-2-GP

665R2F-2-GP

(R)

(R)

12

R339

R339

75R2J-1-GP

75R2J-1-GP

V_CPU_VCCIO

12

PLTRST_CPU_N2

(84.27002.E3F)

(84.27002.E3F)

2N7002DW-1-GP

2N7002DW-1-GP

U25

U25

RESERVED

0

RESERVED

1

NORM RESERVE

2

3,4,7-17 RESERVED RESERVED RESERVED

R330

R330

43R2J-GP

43R2J-GP

H

12

12

C567

C567

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

03/21:follow CRB1.0 rout the CFG[0] to XDP !

2010/12/20

Add EMI Cap

C472

C472

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

LCFG

DESCRIPTION

RESERVED

RESERVED

RESERVED

RESERVED

PEG REVERSAL[0] ,X16

3

R335 75R2F-2-GPR335 75R2F-2-GP

1 2

R353 110R2F-GPR353 110R2F-GP

1 2

R351 90D9R2F-1-GP(R)R351 90D9R2F-1-GP(R)

1 2

CK_PE_100M_MCP_DP

H_VIDSCK

H_VIDSOUT

H_VIDALERT_N

(R) R322

(R)

1 2

100R2J-2-GP

100R2J-2-GP

H_DRAMPWRGD

R491

R491

1 2

120R2F-GP

120R2F-GP

2010/12/20

Add EMI Cap

TP88TPAD28 TP88TPAD28

1

TP89TPAD28 TP89TPAD28

1

R381 1KR2J-1-GP(R)R381 1KR2J-1-GP(R)

1 2

TP90TPAD28 TP90TPAD28

1

TP91TPAD28 TP91TPAD28

1

R393 1KR2J-1-GP(R)R393 1KR2J-1-GP(R)

1 2

R415 1KR2J-1-GP(R)R415 1KR2J-1-GP(R)

1 2

TP92TPAD28 TP92TPAD28

1

TP93TPAD28 TP93TPAD28

1

TP94TPAD28 TP94TPAD28

1

TP95TPAD28 TP95TPAD28

1

TP96TPAD28 TP96TPAD28

1

TP97TPAD28 TP97TPAD28

1

TP98TPAD28 TP98TPAD28

1

TP99TPAD28 TP99TPAD28

1

TP100TPAD28 TP100TPAD28

1

TP101TPAD28 TP101TPAD28

1

TP102TPAD28 TP102TPAD28

1

CFG6/SEL1

1 1

0

* NOA[6:5] 11:D EFAULT X16; 10:2 X8; 01:RESERVED; 00:X8,X4,X4 *

CK_PE_100M_MCP_DN

R323

R323

1 2

R322

44D2R2F-GP

44D2R2F-GP

H_PWRGD

H_DRAMPWRGD_CPU

H_CPURST_N

H_PM_SYNC_0

H_PECI

H_CATERR_N

H_PROCHOT_R_N

CPU_THERMTRIP_N

H_SKTOCC_N

H_SNB_N

SNB_DDR_VREF

TPEV_SNB_PCUDEBUG_0

TPEV_SNB_PCUDEBUG_1

TPEV_SNB_PCUDEBUG_2

TPEV_SNB_PCUDEBUG_3

TPEV_SNB_PCUDEBUG_4

TPEV_SNB_PCUDEBUG_5

TPEV_SNB_PCUDEBUG_6

TPEV_SNB_PCUDEBUG_7

TPEV_SNB_PCUDEBUG_8

TPEV_SNB_PCUDEBUG_9

TPEV_SNB_PCUDEBUG_10

TPEV_SNB_PCUDEBUG_11

TPEV_SNB_PCUDEBUG_12

TPEV_SNB_PCUDEBUG_13

TPEV_SNB_PCUDEBUG_14

TPEV_SNB_PCUDEBUG_15

TPEV_SNB_PCUSTB_0

TPEV_SNB_PCUSTB_1

Default is X16PEG CONFIG TABLE

PCIE CONFIGCFG5/SEL0

1 X 16

1

1 X 8

H_VIDALERT_N_1

V_SM

AT14

C37

AJ19

G35

AJ33

AJ22

M36

M38

G37

G36

AY3

W2

W1

B37

A37

J40

F36

E38

J35

E37

H34

K32

H36

J36

J37

K36

L36

N35

L37

J38

L35

N36

N38

N39

N37

N40

H7

H8

U27E

U27E

SAN-1U2NF

SAN-1U2NF

(62.10055.441)

(62.10055.441)

BCLK_0

BCLK#_0

VIDSCLK

VIDSOUT

VIDALERT#

UNCOREPWRGOOD

SM_DRAMPWROK

RESET#

PM_SYNC

PECI

CATERR#

PROCHOT#

THERMTRIP#

SKTOCC#

PROC_SEL

SM_VREF

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

RSVD#AT14

RSVD#AY3

RSVD#H7

RSVD#H8

12

R500

R500

100R2F-L1-GP-U

100R2F-L1-GP-U

2

5 OF 11

5 OF 11

VCCIO_SEL

P33

VCCP_SELECT

VCCSA_VID

VCCSA_SENSE

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSSIO_SENSE

VCCAXG_SENSE

VSSAXG_SENSE

RSVD#C40

RSVD#D40

BPM#_0

BPM#_1

BPM#_2

BPM#_3

BPM#_4

BPM#_5

BPM#_6

BPM#_7

RSVD#B39

RSVD#J33

RSVD#L34

RSVD#L33

RSVD#K34

RSVD#N33

RSVD#M34

RSVD#AV1

RSVD#AW2

RSVD#L9

RSVD#J9

RSVD#K9

RSVD#L31

RSVD#J31

RSVD#K31

RSVD#AD34

RSVD#AD35

TRST#

PRDY#

PREQ#

DBR#

VCCSA_VID

P34

VCCSA_SENSE

T2

VCC_SENSE

A36

VSS_SENSE

B36

VCCTT_SENSE

AB4

VSSTT_SENSE

AB3

VCCAXG_SENSE

L32

VSSAXG_SENSE

M32

H_TDO

L39

TDO

H_TDI

L40

TDI

H_TCK

M40

TCK

H_TMS

L38

TMS

H_TRST_N

J39

K38

K40

E39

C40

D40

H40

H38

G38

G40

G39

F38

E40

F40

B39

J33

L34

L33

K34

N33

M34

AV1

AW2

L9

J9

K9

L31

J31

K31

AD34

AD35

H_PRDY_N

H_PREQ_N

ITP_CLKINP

ITP_CLKINN

H_BPM#0

H_BPM#1

H_BPM#2

H_BPM#3

H_BPM#4

H_BPM#5

H_BPM#6

H_BPM#7

12/23 JACK

R427 0R0402-PAD-2-GPR427 0R0402-PAD-2-GP

R433 0R2J-2-GP(R)R433 0R2J-2-GP(R)

R432 0R2J-2-GP(R)R432 0R2J-2-GP(R)

1 2

1 2

1 2

1

VCC

R429

R429

10KR2J-3-GP

10KR2J-3-GP

1 2

R421

R421

4K7R2J-2-GP

4K7R2J-2-GP

1 2

XDP_DBRESET_N

FP_RST_DBR_N

CK_XDP_S_DP

CK_XDP_S_DN

SNB_DDR_VREF

12

R493

R493

Remove Potentiometer

A A

5

4

3

100R2F-L1-GP-U

100R2F-L1-GP-U

12

C406

C406

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

2

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Mission Hills

C

Rosa_Mission Hills

C

Rosa_Mission Hills

C

Date: Sheet

Date: Sheet

Date: Sheet

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

10 51Sunday, March 20, 2011

10 51Sunday, March 20, 2011

10 51Sunday, March 20, 2011

of

of

of

SA

SA

SA

Page 11

5

4

3

2

1

FDI

DL_ FSYNC_020

DL_ LSYNC_02 0

DL_ FSYNC_120

DL_ LSYNC_12 0

FDI _INT20

FDI _TX_DP [0..7]20

D D

FDI _TX_DN[0 ..7]20

PCIEX16

EXP _A_TX_ DP[0..15 ]2 6

EXP _A_TX_ DN[0..15]2 6

EXP _A_RX_ DP[0..15 ]26

EXP _A_RX_ DN[0..15]26

DMI

DMI_ IT_MR_D P[0..3]22

DMI_ IT_MR_D N[0..3]22

DMI_ MT_IR_D P[0..3]22

DMI_ MT_IR_D N[0..3]22

C C

B B

V_C PU_VCCI O

EXP _A_RX_ DP0

EXP _A_RX_ DN0

EXP _A_RX_ DP1

EXP _A_RX_ DN1

EXP _A_RX_ DP2

EXP _A_RX_ DN2

EXP _A_RX_ DP3

EXP _A_RX_ DN3

EXP _A_RX_ DP4

EXP _A_RX_ DN4

EXP _A_RX_ DP5

EXP _A_RX_ DN5

EXP _A_RX_ DP6

EXP _A_RX_ DN6

EXP _A_RX_ DP7

EXP _A_RX_ DN7

EXP _A_RX_ DP8

EXP _A_RX_ DN8

EXP _A_RX_ DP9

EXP _A_RX_ DN9

EXP _A_RX_ DP10

EXP _A_RX_ DN10

EXP _A_RX_ DP11

EXP _A_RX_ DN11

EXP _A_RX_ DP12

EXP _A_RX_ DN12

EXP _A_RX_ DP13

EXP _A_RX_ DN13

EXP _A_RX_ DP14

EXP _A_RX_ DN14

EXP _A_RX_ DP15

EXP _A_RX_ DN15

DMI_ IT_MR_D P0

DMI_ IT_MR_D N0

DMI_ IT_MR_D P1

DMI_ IT_MR_D N1

DMI_ IT_MR_D P2

DMI_ IT_MR_D N2

DMI_ IT_MR_D P3

DMI_ IT_MR_D N3

R29 6

R29 6

1 2

24D 9R2F-L-G P

24D 9R2F-L-G P

PEG _COMP

B11

B12

D12

D11

C10

E10

AA4

AA5

C9

E9

B8

B7

C6

C5

A5

A6

E2

E1

F4

F3

G2

G1

H3

H4

J1

J2

K3

K4

L1

L2

M3

M4

N1

N2

W5

W4

V3

V4

Y3

Y4

P3

P4

R2

R1

T4

T3

U2

U1

B5

C4

B4

U27C

U27C

PEG_RX_0

PEG_RX#_0

PEG_RX_1

PEG_RX#_1

PEG_RX_2

PEG_RX#_2

PEG_RX_3

PEG_RX#_3

PEG_RX_4

PEG_RX#_4

PEG_RX_5

PEG_RX#_5

PEG_RX_6

PEG_RX#_6

PEG_RX_7

PEG_RX#_7

PEG_RX_8

PEG_RX#_8

PEG_RX_9

PEG_RX#_9

PEG_RX_10

PEG_RX#_10

PEG_RX_11

PEG_RX#_11

PEG_RX_12

PEG_RX#_12

PEG_RX_13

PEG_RX#_13

PEG_RX_14

PEG_RX#_14

PEG_RX_15

PEG_RX#_15

DMI_RX_0

DMI_RX#_0

DMI_RX_1

DMI_RX#_1

DMI_RX_2

DMI_RX#_2

DMI_RX_3

DMI_RX#_3

PE_RX_0

PE_RX#_0

PE_RX_1

PE_RX#_1

PE_RX_2

PE_RX#_2

PE_RX_3

PE_RX#_3

PEG_ICOMPO

PEG_RCOMPO

PEG_COMPI

SAN-1U2 NF

SAN-1U2 NF

(62.1 0055.44 1)

(62.1 0055.44 1)

PEGDMIGEN

PEGDMIGEN

3 OF 11

3 OF 11

PEG_TX_0

PEG_TX#_0

PEG_TX_1

PEG_TX#_1

PEG_TX_2

PEG_TX#_2

PEG_TX_3

PEG_TX#_3

PEG_TX_4

PEG_TX#_4

PEG_TX_5

PEG_TX#_5

PEG_TX_6

PEG_TX#_6

PEG_TX_7

PEG_TX#_7

PEG_TX_8

PEG_TX#_8

PEG_TX_9

PEG_TX#_9

PEG_TX_10

PEG_TX#_10

PEG_TX_11

PEG_TX#_11

PEG_TX_12

PEG_TX#_12

PEG_TX_13

PEG_TX#_13

PEG_TX_14

PEG_TX#_14

PEG_TX_15

PEG_TX#_15

DMI_TX_0

DMI_TX#_0

DMI_TX_1

DMI_TX#_1

DMI_TX_2

DMI_TX#_2

DMI_TX_3

DMI_TX#_3

PE_TX_0

PE_TX#_0

PE_TX_1

PE_TX#_1

PE_TX_2

PE_TX#_2

PE_TX_3

PE_TX#_3

C13

C14

E14

E13

G14

G13

F12

F11

J14

J13

D8

D7

D3

C3

E6

E5

F8

F7

G10

G9

G5

G6

K7

K8

J5

J6

M8

M7

L6

L5

N5

N6

V7

V6

W7

W8

Y6

Y7

AA7

AA8

P8

P7

T7

T8

R6

R5

U5

U6

EXP _A_TX_ DP0

EXP _A_TX_ DN0

EXP _A_TX_ DP1

EXP _A_TX_ DN1

EXP _A_TX_ DP2

EXP _A_TX_ DN2

EXP _A_TX_ DP3

EXP _A_TX_ DN3

EXP _A_TX_ DP4

EXP _A_TX_ DN4

EXP _A_TX_ DP5

EXP _A_TX_ DN5

EXP _A_TX_ DP6

EXP _A_TX_ DN6

EXP _A_TX_ DP7

EXP _A_TX_ DN7

EXP _A_TX_ DP8

EXP _A_TX_ DN8

EXP _A_TX_ DP9

EXP _A_TX_ DN9

EXP _A_TX_ DP10

EXP _A_TX_ DN10

EXP _A_TX_ DP11

EXP _A_TX_ DN11

EXP _A_TX_ DP12

EXP _A_TX_ DN12

EXP _A_TX_ DP13

EXP _A_TX_ DN13

EXP _A_TX_ DP14

EXP _A_TX_ DN14

EXP _A_TX_ DP15

EXP _A_TX_ DN15

DMI_ MT_IR_D P0

DMI_ MT_IR_D N0

DMI_ MT_IR_D P1

DMI_ MT_IR_D N1

DMI_ MT_IR_D P2

DMI_ MT_IR_D N2

DMI_ MT_IR_D P3

DMI_ MT_IR_D N3

V_C PU_VCCI O

U27D

U27D

R47 5

R47 5

1 2

24D 9R2F-L-G P

24D 9R2F-L-G P

DL_ FSYNC_0

DL_ LSYNC_0

DL_ FSYNC_1

DL_ LSYNC_1

FDI _INT

FDI _COMP

AC5

AC4

AE5

AE4

AG3

AE2

AE1

FDI_FSYNC_0

FDI_LSYNC_0

FDI_FSYNC_1

FDI_LSYNC_1

FDI_INT

FDI_COMPIO

FDI_ICOMPO

SAN-1U2 NF

SAN-1U2 NF

(62.1 0055.44 1)

(62.1 0055.44 1)

Sandy Bridge Socket

SKT 2

SKT 1

SKT 1

SKT 2

4 OF 11

4 OF 11

FDI _TX_DP 0

AC8

FDI_TX_0

FDI_TX#_0

FDI_TX_1

FDI_TX#_1

FDI_TX_2

FDI_TX#_2

FDI_TX_3

FDI_TX#_3

FDI_TX_4

FDI_TX#_4

FDI_TX_5

FDI_TX#_5

FDI_TX_6

FDI_TX#_6

FDI_TX_7

FDI_TX#_7

FDI

FDI

LINK

LINK

AC7

AC2

AC3

AD2

AD1

AD4

AD3

AD7

AD6

AE7

AE8

AF3

AF2

AG2

AG1

FDI _TX_DN0

FDI _TX_DP 1

FDI _TX_DN1

FDI _TX_DP 2

FDI _TX_DN2

FDI _TX_DP 3

FDI _TX_DN3

FDI _TX_DP 4

FDI _TX_DN4

FDI _TX_DP 5

FDI _TX_DN5

FDI _TX_DP 6

FDI _TX_DN6

FDI _TX_DP 7

FDI _TX_DN7

Back Plate

Load Plate

Load Plate

(22.7 8003.01 1)

(22.7 8003.01 1)

<Variant Name>

<Variant Name>

A A

5

4

3

2

<Variant Name>

Title

Title

Title

Size Docume nt Number Rev

Size Docume nt Number Rev

Size Docume nt Number Rev

B

B

B

Date: Shee t

Date: Shee t

Date: Shee t of

Back Plate

(22.7 8002.01 1)

(22.7 8002.01 1)

Ros a_Mission Hills

Ros a_Mission Hills

Ros a_Mission Hills

Wistro n In corpo rated

Wistro n In corpo rated

Wistro n In corpo rated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

11 51Sunday, March 2 0, 2011

11 51Sunday, March 2 0, 2011

11 51Sunday, March 2 0, 2011

of

1

of

SA

SA

SA

Page 12

5

DDR DATA

M_DATA_A[0..63]15

M_DATA_B[0..63]17

M_DQS_A_DP[0..8]15

M_DQS_A_DN[0..8]15

M_DQS_B_DP[0..8]17

M_DQS_B_DN[0..8]17

M_DATA_A_CB[0..7]15

D D

M_DATA_B_CB[0..7]17

DDR CMD/ADD

M_MAA_A[0..15]15

M_MAA_B[0..15]17

M_WE_A_N15

M_CAS_A_N15

M_RAS_A_N15

M_SBS_A015

M_SBS_A115

M_SBS_A215

M_WE_B_N17

M_CAS_B_N17

M_RAS_B_N17

M_SBS_B017

M_SBS_B117

M_SBS_B217

DDR CTRL

M_SCS_A_N015

M_SCS_A_N115

M_SCKE_A015

M_SCKE_A115

M_ODT_A015

M_ODT_A115

C C

M_SCS_B_N017

M_SCS_B_N117

M_SCKE_B017

M_SCKE_B117

M_ODT_B017

M_ODT_B117

DDR CLOCK

CK_M_DDR0_A_DP15

CK_M_DDR0_A_DN15

CK_M_DDR1_A_DP15

CK_M_DDR1_A_DN15

CK_M_DDR0_B_DP17

CK_M_DDR0_B_DN17

CK_M_DDR1_B_DP17

CK_M_DDR1_B_DN17

DDR3_DRAMRST_N

(R) C474

(R)

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

C474

Can be left as no connects if no support ECC.

B B

DDR OTHERS

DDR3_DRAMRST_N15,17

R637

R637

1 2

0R0402-PAD-2-GP

0R0402-PAD-2-GP

12

M_WE_A_N

M_CAS_A_N

M_RAS_A_N

M_SBS_A0

M_SBS_A1

M_SBS_A2

M_SCS_A_N0

M_SCS_A_N1

M_SCKE_A0

M_SCKE_A1

M_ODT_A0

M_ODT_A1

CK_M_DDR0_A_DP

CK_M_DDR0_A_DN

CK_M_DDR1_A_DP

CK_M_DDR1_A_DN

DDR3_DRAMRST_N-1

M_DQS_A_DP8

M_DQS_A_DN8

M_DATA_A_CB0

M_DATA_A_CB1

M_DATA_A_CB2

M_DATA_A_CB3

M_DATA_A_CB4

M_DATA_A_CB5

M_DATA_A_CB6

M_DATA_A_CB7

M_MAA_A0

M_MAA_A1

M_MAA_A2

M_MAA_A3

M_MAA_A4

M_MAA_A5

M_MAA_A6

M_MAA_A7

M_MAA_A8

M_MAA_A9

M_MAA_A10

M_MAA_A11

M_MAA_A12

M_MAA_A13

M_MAA_A14

M_MAA_A15

AW24

AW23

AW32

AW29

AW28

AW30

AW33

AW25

AW27

AW26

AW18

AW13

AW12

AV27

AY24

AV23

AT24

AT23

AU22

AV22

AT22

AV28

AU21

AT21

AU20

AT20

AV30

AU28

AY29

AV20

AU29

AV32

AU33

AV19

AT19

AU18

AV18

AV31

AU32

AU30

AY25

AU24

AU25

AY27

AV26

AV13

AV12

AU12

AU14

AY13

AU13

AU11

AY12

4

U27A

U27A

SAN-1U2NF

SAN-1U2NF

(62.10055.441)

(62.10055.441)

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

SA_MA_15

SA_WE#

SA_CAS#

SA_RAS#

SA_BS_0

SA_BS_1

SA_BS_2

SA_CS#_0

SA_CS#_1

SA_CS#_2

SA_CS#_3

SA_CKE_0

SA_CKE_1

SA_CKE_2

SA_CKE_3

SA_ODT_0

SA_ODT_1

SA_ODT_2

SA_ODT_3

SA_CK_0

SA_CK#_0

SA_CK_1

SA_CK#_1

SA_CK_2

SA_CK#_2

SA_CK_3

SA_CK#_3

SM_DRAMRST#

SA_DQS_8

SA_DQS#_8

SA_ECC_CB_0

SA_ECC_CB_1

SA_ECC_CB_2

SA_ECC_CB_3

SA_ECC_CB_4

SA_ECC_CB_5

SA_ECC_CB_6

SA_ECC_CB_7

DDR_0

DDR_0

1 OF 11

1 OF 11

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

AJ3

AJ4

AL3

AL4

AJ2

AJ1

AL2

AL1

AN1

AN4

AR3

AR4

AN2

AN3

AR2

AR1

AV2

AW3

AV5

AW5

AU2

AU3

AU5

AY5

AY7

AU7

AV9

AU9

AV7

AW7

AW9

AY9

AU35

AW37

AU39

AU36

AW35

AY36

AU38

AU37

AR40

AR37

AN38

AN37

AR39

AR38

AN39

AN40

AL40

AL37

AJ38

AJ37

AL39

AL38

AJ39

AJ40

AG40

AG37

AE38

AE37

AG39

AG38

AE39

AE40

AK3

AP3

AW4

AV8

AV37

AP38

AK38

AF38

AK2

AP2

AV4

AW8

AV36

AP39

AK39

AF39

3

M_DATA_A0

M_DATA_A1

M_DATA_A2

M_DATA_A3

M_DATA_A4

M_DATA_A5

M_DATA_A6

M_DATA_A7

M_DATA_A8

M_DATA_A9

M_DATA_A10

M_DATA_A11

M_DATA_A12

M_DATA_A13

M_DATA_A14

M_DATA_A15

M_DATA_A16

M_DATA_A17

M_DATA_A18

M_DATA_A19

M_DATA_A20

M_DATA_A21

M_DATA_A22

M_DATA_A23

M_DATA_A24

M_DATA_A25

M_DATA_A26

M_DATA_A27

M_DATA_A28

M_DATA_A29

M_DATA_A30

M_DATA_A31

M_DATA_A32

M_DATA_A33

M_DATA_A34

M_DATA_A35

M_DATA_A36

M_DATA_A37

M_DATA_A38

M_DATA_A39

M_DATA_A40

M_DATA_A41

M_DATA_A42

M_DATA_A43

M_DATA_A44

M_DATA_A45

M_DATA_A46

M_DATA_A47

M_DATA_A48

M_DATA_A49

M_DATA_A50

M_DATA_A51

M_DATA_A52

M_DATA_A53

M_DATA_A54

M_DATA_A55

M_DATA_A56

M_DATA_A57

M_DATA_A58

M_DATA_A59

M_DATA_A60

M_DATA_A61

M_DATA_A62

M_DATA_A63

M_DQS_A_DP0

M_DQS_A_DP1

M_DQS_A_DP2

M_DQS_A_DP3

M_DQS_A_DP4

M_DQS_A_DP5

M_DQS_A_DP6

M_DQS_A_DP7

M_DQS_A_DN0

M_DQS_A_DN1

M_DQS_A_DN2

M_DQS_A_DN3

M_DQS_A_DN4

M_DQS_A_DN5

M_DQS_A_DN6

M_DQS_A_DN7

M_MAA_B0

M_MAA_B1

M_MAA_B2

M_MAA_B3

M_MAA_B4

M_MAA_B5

M_MAA_B6

M_MAA_B7

M_MAA_B8

M_MAA_B9

M_MAA_B10

M_MAA_B11

M_MAA_B12

M_MAA_B13

M_MAA_B14

M_MAA_B15

M_WE_B_N

M_CAS_B_N

M_RAS_B_N

M_SBS_B0

M_SBS_B1

M_SBS_B2

M_SCS_B_N0

M_SCS_B_N1

M_SCKE_B0

M_SCKE_B1

M_ODT_B0

M_ODT_B1

CK_M_DDR0_B_DP

CK_M_DDR0_B_DN

CK_M_DDR1_B_DP

CK_M_DDR1_B_DN

M_DQS_B_DP8

M_DQS_B_DN8

M_DATA_B_CB0

M_DATA_B_CB1

M_DATA_B_CB2

M_DATA_B_CB3

M_DATA_B_CB4

M_DATA_B_CB5

M_DATA_B_CB6

Can be left as no connects if no support ECC.

M_DATA_B_CB7

AK24

AM20

AM19

AK18

AP19

AP18

AM18

AL18

AN18

AY17

AN23

AU17

AT18

AR26

AY16

AV16

AR25

AK25

AP24

AP23

AM24

AW17

AN25

AN26

AL25

AT26

AU16

AY15

AW15

AV15

AL26

AP26

AM26

AK26

AL21

AL22

AL20

AK20

AL23

AM22

AP21

AN21

AN16

AN15

AL16

AM16

AP16

AR16

AL15

AM15

AR15

AP15

2

U27B

U27B

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

SB_MA_15

SB_WE#

SB_CAS#

SB_RAS#

SB_BS_0

SB_BS_1

SB_BS_2

SB_CS#_0

SB_CS#_1

SB_CS#_2

SB_CS#_3

SB_CKE_0

SB_CKE_1

SB_CKE_2

SB_CKE_3

SB_ODT_0

SB_ODT_1

SB_ODT_2

SB_ODT_3

SB_CK_0

SB_CK#_0

SB_CK_1

SB_CK#_1

SB_CK_2

SB_CK#_2

SB_CK_3

SB_CK#_3

SB_DQS_8

SB_DQS#_8

SB_ECC_CB_0

SB_ECC_CB_1

SB_ECC_CB_2

SB_ECC_CB_3

SB_ECC_CB_4

SB_ECC_CB_5

SB_ECC_CB_6

SB_ECC_CB_7

DDR_1

DDR_1

SAN-1U2NF

SAN-1U2NF

(62.10055.441)

(62.10055.441)

2 OF 11

2 OF 11

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

AG7

AG8

AJ9

AJ8

AG5

AG6

AJ6

AJ7

AL7

AM7

AM10

AL10

AL6

AM6

AL9

AM9

AP7

AR7

AP10

AR10

AP6

AR6

AP9

AR9

AM12

AM13

AR13

AP13

AL12

AL13

AR12

AP12

AR28

AR29

AL28

AL29

AP28

AP29

AM28

AM29

AP32

AP31

AP35

AP34

AR32

AR31

AR35

AR34

AM32

AM31

AL35

AL32

AM34

AL31

AM35

AL34

AH35

AH34

AE34

AE35

AJ35

AJ34

AF33

AF35

AH7

AM8

AR8

AN13

AN29

AP33

AL33

AG35

AH6

AL8

AP8

AN12

AN28

AR33

AM33

AG34

M_DATA_B0

M_DATA_B1

M_DATA_B2

M_DATA_B3

M_DATA_B4

M_DATA_B5

M_DATA_B6

M_DATA_B7

M_DATA_B8

M_DATA_B9

M_DATA_B10

M_DATA_B11

M_DATA_B12

M_DATA_B13

M_DATA_B14

M_DATA_B15

M_DATA_B16

M_DATA_B17

M_DATA_B18

M_DATA_B19

M_DATA_B20

M_DATA_B21

M_DATA_B22

M_DATA_B23

M_DATA_B24

M_DATA_B25

M_DATA_B26

M_DATA_B27

M_DATA_B28

M_DATA_B29

M_DATA_B30

M_DATA_B31

M_DATA_B32

M_DATA_B33

M_DATA_B34

M_DATA_B35

M_DATA_B36

M_DATA_B37

M_DATA_B38

M_DATA_B39

M_DATA_B40

M_DATA_B41

M_DATA_B42

M_DATA_B43

M_DATA_B44

M_DATA_B45

M_DATA_B46

M_DATA_B47

M_DATA_B48

M_DATA_B49

M_DATA_B50

M_DATA_B51

M_DATA_B52

M_DATA_B53

M_DATA_B54

M_DATA_B55

M_DATA_B56

M_DATA_B57

M_DATA_B58

M_DATA_B59

M_DATA_B60

M_DATA_B61

M_DATA_B62

M_DATA_B63

M_DQS_B_DP0

M_DQS_B_DP1

M_DQS_B_DP2

M_DQS_B_DP3

M_DQS_B_DP4

M_DQS_B_DP5

M_DQS_B_DP6

M_DQS_B_DP7

M_DQS_B_DN0

M_DQS_B_DN1

M_DQS_B_DN2

M_DQS_B_DN3

M_DQS_B_DN4

M_DQS_B_DN5

M_DQS_B_DN6

M_DQS_B_DN7

1

A A

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Mission Hills

C

Rosa_Mission Hills

C

Rosa_Mission Hills

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsi n Tai Wu Rd

21F, 88, Hsi n Tai Wu Rd

21F, 88, Hsi n Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

12 51Sunday, March 20, 2011

12 51Sunday, March 20, 2011

12 51Sunday, March 20, 2011

of

of

of

SA

SA

SA

Page 13

5

4

3

2

1

V_CPU_CORE

U27F

U27F

A12

VCC

A13

VCC

A14

VCC

A15

VCC

DIMM_DQ_CPU_VREF_B17

DIMM_DQ_CPU_VREF_A15

D D

C C

A16

A18

A24

A25

A27

A28

B15

B16

B18

B24

B25

B27

B28

B30

B31

B33

B34

C15

C16

C18

C19

C21

C22

C24

C25

C27

C28

C30

C31

C33

C34

C36

D13

D14

D15

D16

D18

D19

D21

D22

D24

D25

D27

D28

D30

D31

D33

D34

D35

D36

E15

E16

E18

E19

E21

E22

E24

E25

E27

E28

E30

E31

E33

E34

E35

F15

F16

F18

F19

F21

F22

F24

F25

F27

F28

F30

F31

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

SAN-1U2NF

SAN-1U2NF

(62.10055.441)

(62.10055.441)

V_CPU_CORE

6 OF 11

6 OF 11

F32

VCC

F33

VCC

F34

VCC

G15

VCC

G16

VCC

G18

VCC

G19

VCC

G21

VCC

G22

VCC

G24

VCC

G25

VCC

G27

VCC

G28

VCC

G30

VCC

G31

VCC

G32

VCC

G33

VCC

H13

VCC

H14

VCC

H15

VCC

H16

VCC

H18

VCC

H19

VCC

H21

VCC

H22

VCC

H24

VCC

H25

VCC

H27

VCC

H28

VCC

H30

VCC

H31

VCC

H32

VCC

J12

VCC

J15

VCC

J16

VCC

J18

VCC

J19

VCC

J21

VCC

J22

VCC

J24

VCC

J25

VCC

J27

VCC

J28

VCC

J30

VCC

K15

VCC

K16

VCC

K18

VCC

K19

VCC

K21

VCC

K22

VCC

K24

VCC

K25

VCC

K27

VCC

K28

VCC

K30

VCC

L13

VCC

L14

VCC

L15

VCC

L16

VCC

L18

VCC

L19

VCC

L21

VCC

L22

VCC

L24

VCC

L25

VCC

L27

VCC

L28

VCC

L30

VCC

M14

VCC

M15

VCC

M16

VCC

M18

VCC

M19

VCC

M21

VCC

M22

VCC

M24

VCC

M25

VCC

M27

VCC

M28

VCC

M30

VCC

V_1P8_SFR

V_CPU_VCCIO

V_SA

M13

A11

AA3

AB8

AF8

AG33

AJ16

AJ17

AJ26

AJ28

AJ32

AK15

AK17

AK19

AK21

AK23

AK27

AK29

AK30

D10

D6

G3

G4

N3

N4

N7

R3

R4

R7

U3

U4

U7

W3

H10

H11

H12

J10

K10

K11

L11

L12

M10

M11

M12

AK11

AK12

A7

B9

E3

E4

J3

J4

J7

J8

L3

L4

L7

V8

U27H

U27H

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCPLL

VCCPLL

SAN-1U2NF

SAN-1U2NF

(62.10055.441)

(62.10055.441)

8 OF 11

8 OF 11

V_SM

AJ13

VDDQ

AJ14

VDDQ

AJ23

VDDQ

AJ24

VDDQ

AR20

VDDQ

AR21

VDDQ

AR22

VDDQ

AR23

VDDQ

AR24

VDDQ

AU19

VDDQ

AU23

VDDQ

AU27

VDDQ

AU31

VDDQ

AV21

VDDQ

AV24

VDDQ

AV25

VDDQ

AV29

VDDQ

AV33

VDDQ

AW31

VDDQ

AY23

VDDQ

AY26

VDDQ

AY28

VDDQ

AJ20

VDDQ

POWER

POWER

V_CPU_AXG

AB33

AB34

AB35

AB36

AB37

AB38

AB39

AB40

AC33

AC34

AC35

AC36

AC37

AC38

AC39

AC40

T33

T34

T35

T36

T37

T38

T39

T40

U33

U34

U35

U36

U37

U38

U39

U40

W33

W34

W35

W36

W37

W38

Y33

Y34

Y35

Y36

Y37

Y38

CPU Power Capac itor Quantity

Net

Vcore

VCCSA 2+010uf 0805

VDDQ 922uf 0805

VCCPLL

7 OF 11

7 OF 11

U27G

U27G

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

VCCAXG

SAN-1U2NF

SAN-1U2NF

(62.10055.441)

(62.10055.441)

CAP AMOUNT

22uf 0805

14+4

22uf 0805 9+16(R)VCCIO

22uf 0805 4+2(R)V_AXG

10uf 0805

1

AM27

AM3

AM30

AM36

AM37

AM38

AM39

AM4

AM40

AM5

AN10

AN11

AN14

AN17

AN19

AN22

AN24

AN27

AN30

AN31

AN32

AN33

AN34

AN35

AN36

AN5

AN6

AN7

AN8

AN9

AP1

AP11

AP14

AP17

AP22

AP25

AP27

AP30

AP36

AP37

AP4

AP40

AP5

AR11

AR14

AR17

AR18

AR19

AR27

AR30

AR36

AR5

AT1

AT10

AT12

AT13

AT15

AT16

AT17

AT2

AT25

AT27

AT28

AT29

AT3

AT30

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AT39

AT4

AT40

AT5

AT6

AT7

AT8

AT9

AU1

AU15

AU26

AU34

AU4

AU6

AU8

AV10

A4

AV39

U27I

U27I

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SAN-1U2NF

SAN-1U2NF

(62.10055.441)

(62.10055.441)

9 OF 11

9 OF 11

G8

VSS

H1

VSS

H17

VSS

H2

VSS

H20

VSS

H23

VSS

H26

VSS

H29

VSS

H33

VSS

H35

VSS

H37

VSS

H39

VSS

H5

VSS

H6

VSS

H9

VSS

J11

VSS

J17

VSS

J20

VSS

J23

VSS

J26

VSS

J29

VSS

J32

VSS

K1

VSS

K12

VSS

K13

VSS

K14

VSS

K17

VSS

K2

VSS

K20

VSS

K23

VSS

K26

VSS

K29

VSS

K33

VSS

K35

VSS

K37

VSS

K39

VSS

K5

VSS

K6

VSS

L10

VSS

L17

VSS

L20

VSS

L23

VSS

L26

VSS

L29

VSS

L8

VSS

M1

VSS

M17

VSS

M2

VSS

M20

VSS

M23

VSS

M26

VSS

M29

VSS

M33

VSS

M35

VSS

M37

VSS

M39

VSS

M5

VSS

M6

VSS

M9

VSS

N8

VSS

P1

VSS

P2

VSS

P36

VSS

P38

VSS

P40

VSS

P5

VSS

P6

VSS

R33

VSS

R35

VSS

R37

VSS

R39

VSS

R8

VSS

T1

VSS

T5

VSS

T6

VSS

U8

VSS

V1

VSS

V2

VSS

V33

VSS

V34

VSS

V35

VSS

V36

VSS

V37

VSS

V38

VSS

V39

VSS

V40

VSS

V5

VSS

W6

VSS

Y5

VSS

Y8

VSS

AY37

VSS

B3

VSS

A17

A23

A26

A29

A35

AA33

AA34

AA35

AA36

AA37

AA38

AA6

AB5

AC1

AC6

AD33

AD36

AD38

AD39

AD40

AD5

AD8

AE3

AE33

AE36

AF1

AF34

AF36

AF37

AF40

AF5

AF6

AF7

AG36

AH2

AH3

AH33

AH36

AH37

AH38

AH39

AH40

AH5

AH8

AJ12

AJ15

AJ18

AJ21

AJ25

AJ27

AJ36

AJ5

AK1

AK10

AK13

AK14

AK16

AK22

AK28

AK31

AK32

AK33

AK34

AK35

AK36

AK37

AK4

AK40

AK5

AK6

AK7

AK8

AK9

AL11

AL14

AL17

AL19

AL24

AL27

AL30

AL36

AL5

AM1

AM11

AM14

AM17

AM2

AM21

AM23

AM25

U27J

U27J

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SAN-1U2NF

SAN-1U2NF

(62.10055.441)

(62.10055.441)

10 OF 11

10 OF 11

AV11

VSS

AV14

VSS

AV17

VSS

AV3

VSS

AV35

VSS

AV38

VSS

AV6

VSS

AW10

VSS

AW11

VSS

AW14

VSS

AW16

VSS

AW36

VSS

AW6

VSS

AY11

VSS

AY14

VSS

AY18

VSS

AY35

VSS

AY4

VSS

AY6

VSS

AY8

VSS

B10

VSS

B13

VSS

B14

VSS

B17

VSS

B23

VSS

B26

VSS

B29

VSS

B32

VSS

B35

VSS

B38

VSS

B6

VSS

C11

VSS

C12

VSS

C17

VSS

C20

VSS

C23

VSS

C26

VSS

C29

VSS

C32

VSS

C35

VSS

C7

VSS

C8

VSS

D17

VSS

D2

VSS

D20

VSS

D23

VSS

D26

VSS

D29

VSS

D32

VSS

D37

VSS

D39

VSS

D4

VSS

D5

VSS

D9

VSS

E11

VSS

E12

VSS

E17

VSS

E20

VSS

E23

VSS

E26

VSS

E29

VSS

E32

VSS

E36

VSS

E7

VSS

E8

VSS

F1

VSS

F10

VSS

F13

VSS

F14

VSS

F17

VSS

F2

VSS

F20

VSS

F23

VSS

F26

VSS

F29

VSS

F35

VSS

F37

VSS

F39

VSS

F5

VSS

F6

VSS

F9

VSS

G11

VSS

G12

VSS

G17

VSS

G20

VSS

G23

VSS

G26

VSS

G29

VSS

G34

VSS

G7

VSS

TP28TPAD28 TP28TPAD28 1

TP65TPAD28 TP65TPAD28

TP68TPAD28 TP68TPAD28 1

TP4TPAD24 TP4TPAD24

TP3TPAD24 TP3TPAD24 1

1

1

TP_CPU_A38

TP_CPU_AU40

TP_CPU_AW38

TP_CPU_C2

TP_CPU_D1

U27K

U27K

AB7

RSVD#AB7

AD37

RSVD#AD37

AG4

RSVD#AG4

AJ29

RSVD#AJ29

AJ30

RSVD#AJ30

AJ31

RSVD#AJ31

AV34

RSVD#AV34

AW34

RSVD#AW34

P35

RSVD#P35

P37

RSVD#P37

P39

RSVD#P39

R34

RSVD#R34

R36

RSVD#R36

R38

RSVD#R38

R40

RSVD#R40

A38

NCTF#A38

AU40

NCTF#AU40

AW38

NCTF#AW38

C2

NCTF#C2

D1

NCTF#D1

SAN-1U2NF

SAN-1U2NF

(62.10055.441)

(62.10055.441)

11 OF 11

11 OF 11

C495

C495

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

DIMM_DQ_CPU_VREF_B

DIMM_DQ_CPU_VREF_A

C464

C464

12

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

AH1

FC_AH1

AH4

FC_AH4

12

AT11

RSVD#AT11

AP20

RSVD#AP20

AN20

RSVD#AN20

AU10

RSVD#AU10

AY10

RSVD#AY10

AF4

RSVD#AF4

AB6

RSVD#AB6

AE6

RSVD#AE6

AJ11

RSVD#AJ11

D38

RSVD#D38

C39

RSVD#C39

C38

RSVD#C38

J34

A38,AU40,AW38,C2,D1

A38,AU40,AW38,C2,D1

RSVD#J34

N34

NCTF TEST PIN:

NCTF TEST PIN:

RSVD#N34

SPARES

SPARES

Place in the CPU Cavity Area

V_CPU_AXG

C348

C348

C339

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C339

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C340

C340

12

12

SC22U6D3V5MX-2GP

B B

SC22U6D3V5MX-2GP

C355

C355

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C373

C373

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C354

C354

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

V_CPU_CORE

C367

C367

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C368

C368

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C338

C338

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C333

C333

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C352

C352

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C336

C336

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C350

C350

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

V_SM

C378

C378

C380

C380

C382

12

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

V_CPU_VCCIO

C379

C370

C370

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

(R)C363

(R)

C379

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

V_CPU_CORE

C264

(R)C264

(R)

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C341

C341

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C371

C371

C366

C366

12

Place on back side

A A

V_1P8_SFR

12

C437

(R)C437

(R)

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

5

C362

(R)C362

(R)

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

V_SAV_SA

C363

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C266

C266

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

V_CPU_AXG

C553

C553

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

(R)

(R)

4

C382

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C356

C356

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C557

C557

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

(R)

(R)

C267

C267

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C372

C372

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C265

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C353

C353

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C381

C381

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

(R)C265

(R)

12

V_CPU_VCCIO

C335

C335

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C365

C365

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C315

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

(R)C315

(R)

C369

C369

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C254

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

C349

C349

12

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C307

(R)C307

(R)

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

(R)C254

(R)

C261

(R)C261

(R)

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

3

C337

C337

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C259

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

(R)C259

(R)

C351

C351

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

C257

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

C555

(R)C555

(R)

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

(R)C257

(R)

C334

C334

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C554

(R)C554

(R)

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C256

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C556

(R)C556

(R)

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

<Variant Name>

<Variant Name>

12

12

(R)C256

(R)

C260

(R)C260

(R)

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

C258

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

2

(R)C258

(R)

<Variant Name>

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

Rosa_Mission Hills

D

Rosa_Mission Hills

D