5

RepairLap.com

PCB Number: 13048-1

4

3

2

1

PAGE

01

02

D D

03 Power Delivery

04

05

06

07

08

09

10

11

12

13

14 XDP/80 PORT HEADER

15

16

17

18

C C

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

B B

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

A A

51

52

53

54

55

56

57

TITLE

Cover Page

BLOCK DIAGRAM

POWER GOOD AND RESET DIAGRAM

CLOCKS DIAGRAM

Power Sequence

TBD

GPIO TABLE

TBD

CPU uLGA 1150_1

CPU uLGA 1150_2

CPU uLGA 1150_3

CPU uLGA 1150_4

DIMM A

DIMM B

TBD

PCH_AUDIO/GPIO/SPI

PCH_CLK

PCH_SATA/FAN/DP/VGA

PCH_FDI/PCIE/DMI/USB

PCH_GND/STRAPS

PCH_POWER

VGA/HDMI

Panel control

DPtoLVDS_RTD2136R

USB/USB30

Card Reader OZ621

LAN RTL8151GD

AUDIO ALC3661

AMP TPA3131

TOUCH/WEBCAM

NGFF

SATA/LED/BTN

FAN CIRCUITS/HOLE

TPM

SIO_SCH5553

DSW

DC IN

TBD

RT8243_3V&5V

CPU VRM 12-5 _1

CPU VRM 12-5 _2

NCP1589-> +12V

Run PWR/USB PWR

MEM_1D5V/MEM_VTT

PCH_1D05V

1D5V PCH POWER

GPU JET PCIE

GPU_JET IO

GPU_JET MEMORY

GPU_JET STRAP

GPU_JET POWER

GPU_DDR3 64MX16

GPU_POWER CORE

GPU_POWER 0D95V/1D8V

GPU_POWER 3D3V/ 1D5V

5

4

Quantity

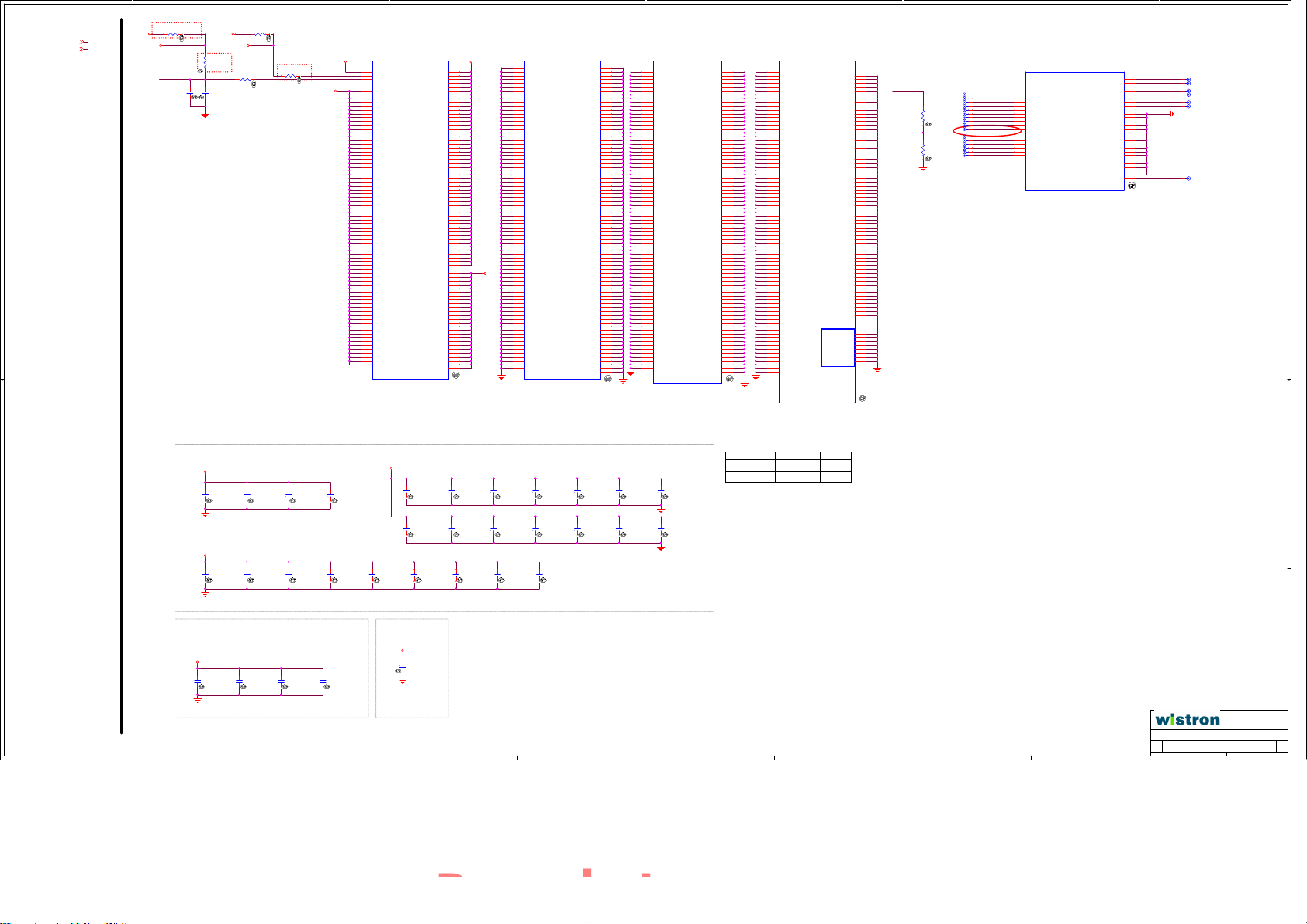

Model : Tigris AIO

PCB version : 1

PCB Number: 13048

SCH Ver : A00

PCBA : A00

BOM Configuration

(R):Unmount

(G):GPU

(U):UMA

(T):Touch

(E):External Adapter(19V)

(I):Internal PSU(12V)

(S):Tigris AIO

(C):Caspian

PCB BOARD SIZE

6 Layers

265mm X 190mm

Haswell Platform :

LGA1155 : Haswell CPU

Chipset : Haswell PCH H81

3

2

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Cover Page

Cover Page

Cover Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Tigris AIO

Custom

Rosa_Tigris AIO

Custom

Rosa_Tigris AIO

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

1 58Monday, January 06, 2014

1 58Monday, January 06, 2014

1 58Monday, January 06, 2014

1

1

1

1

5

RepairLap.com

4

3

2

1

PCB BOARD SIZE

265mm X 184mm

4 Layer

D D

C C

Internal Slot/Header

Front/Rear IO

Chipset

B B

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Incorporated

Wistron Incorporated

A A

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Tigris AIO

Custom

Rosa_Tigris AIO

Custom

Rosa_Tigris AIO

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

2 58Monday, January 06, 2014

2 58Monday, January 06, 2014

2 58Monday, January 06, 2014

1

1

1

1

5

RepairLap.com

4

3

2

1

GPU_POWER

SI4128*1

D D

PWM

RT8243B

DC_IN

SI4712*1

SI4128*1

SI4712*1

Dual PWM Design

PSU_12V

ADP_19V

2013.5.11

PWM +1.5V_PWR

RT8237

SIR172ADP*1

2013.5.11

3D3V_PWR

Imax=6.5A

5V_PWR

Imax=7.5A

12V_PWRPWM

Imax=3A

Imax=16ASIRA12DP*2

3D3V_S5

Imax=6.5A

5V_S5

Imax=7.5A

+12V_S0

Imax=3ANCP1589A

1D5V_S3

Imax=16A

3D3V_S0

5V_S0

VCC5_USB

LDO

APL5337

APL5930

+DDR3_VTT

0D75_S0

Imax=1A

1D5V_PCHLDO

Imax=0.75A

1D5V_S0

PWM

RT8237

C C

NCP81102

2013.5.11

SI4128*1

SI4712*1

PWM

SIR172ADP*3

SIRA12DP*6

3 Phase Design

1D05V_PCH

Imax=7A

V_CPU_CORE

TDC=37A

Imax=60ANCP81151

GPU_POWER

GPU_POWER

0.92V~1.22V

PWM SIR172AP*2

ISL62882

SIRA12DP*2

VGA_CORE

Imax=27A

OCP>41A

B B

3D3V_S0

+VDDR3

LDO

APL5930

+1.8V_REG

Imax=1.5A

+MVDD1D5V_S3

LDO

APL5611

A A

5

4

+0.95V_REG

Imax=4.5A

3

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Power Delivery

Power Delivery

Power Delivery

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Tigris AIO

Custom

Rosa_Tigris AIO

Custom

Rosa_Tigris AIO

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

3 58Monday, January 06, 2014

3 58Monday, January 06, 2014

3 58Monday, January 06, 2014

1

1

1

5

RepairLap.com

D D

4

3

2

1

PCH_1D05V_PG

PCH_1D05V_PG

Intel

VRD12.5

ISL62882

C C

VRM_EN

VR_READY

10

14

EVEREST CPU

UNCOREPWRGOOD

RESET#

H_PWRGD

PLTRST#

15

PLTRST#

15

SLP_S3_N

9

SLP_S5_N

8

7

RSMRST_N

PWRGD_3V

PWRBTN#

PLTRST_N

12

PWR_GOOD_3V

PLTRST*_SIO

SLP_S3#

SLP_S5#

PWRGD_PS

11

PSPWRGD

SUPER IO

SCH5553

RSMRST#

6

4

+3.3VSB

PCIRST1#

PCIRST2#

PANSWH#

+3.3VSB

3

15

RT8243

+5VSB

+3.3VSB

VOUT

PCIEx16

CardReader

LAN

WLAN

5

PB_IN_SW

VIN

Power

Button

POWER SUPPLY

180W,12V

3

ADP_19V

AC core_IN

2

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Power Good & Reset Diagram

Power Good & Reset Diagram

Power Good & Reset Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Tigris AIO

C

Rosa_Tigris AIO

C

Rosa_Tigris AIO

C

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

1

1

1

4 58Monday, January 06, 2014

4 58Monday, January 06, 2014

4 58Monday, January 06, 2014

1

APWROK

PCH_SYSPWROK

PWROK

INTEL PCH

B B

13

PROCPWRGD

SYS_PWROK

+RTVCC

PLTRST#

H81

SLP_S3#

SLP_S5#

PWRBTN#

RSMRST#

+3.3VSB

1

RTC

A A

5

Battery

4

5

RepairLap.com

4

3

2

1

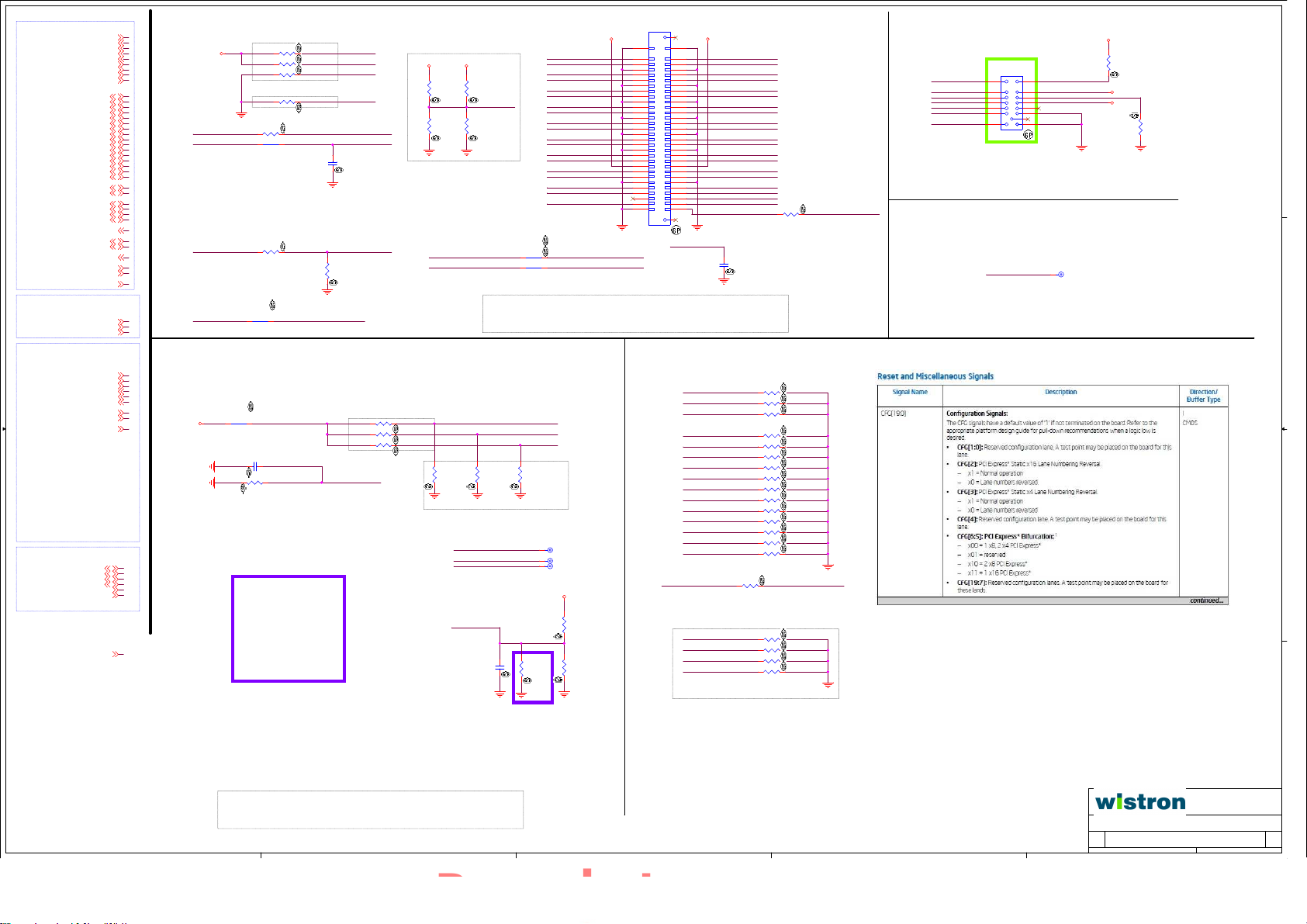

Intel PCH

CLKOUT_33MHZ0

Rs

CLKOUT_33MHZ1

D D

C C

B B

Loopback

CLKOUT_33MHZ2

PCICLK_IN

CLKOUT_33MHZ3

CLKOUT_33MHZ4

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

CLKOUT_PCIE0_N

CLKOUT_PCIE0_P

CLKOUT_PCIE1_N

CLKOUT_PCIE1_P

CLKOUT_PCIE2_N

CLKOUT_PCIE2_P

CLKOUT_PCIE3_N

CLKOUT_PCIE3_P

CLKOUT_PCIE4_N

CLKOUT_PCIE4_P

CLKOUT_PCIE5_N

CLKOUT_PCIE5_P

CLKOUT_PCIE6_N

CLKOUT_PCIE6_P

CLKOUT_PCIE7_N

CLKOUT_PCIE7_P

CLKOUT_FLEX0

CLKOUT_FLEX1(48M)

CLKOUT_FLEX2

CLKOUT_FLEX3(14M)

CLKOUT_PEG_A_N

CLKOUT_PEG_A_P

CLKOUT_PEG_B_N

CLKOUT_PEG_B_P

CLKOUT_DP#

CLKOUT_DP_P

CLKOUT_DPNS#

CLKOUT_DPNS_P

CLKOUT_DMI_N

CLKOUT_DMI_P

Rs

Rs

R0

R0

Rs

Rs

R0

R0

LPC PORT80

CPU XDP HEADER

PCIEX1(WLAN)

Realtek LAN

CARD READER

GPU

CPU SSC_DPLL

CPU DPLL

CPU DMI

SIO SCH5555

R0

Intel

Intel

IntelIntel

PCH

PCH

PCHPCH

SMLICLK_PCH

SMLIDATA_PCH

SMB_CLK_RESUME

SMB_DATA_RESUME

SIO SCH5555

SIO SCH5555

SIO SCH5555SIO SCH5555

DDR3 CHA(VREF)

DDR3 CHB(VREF)

Switch

Switch

SwitchSwitch

SMB_CLK_MAIN

SMB_DATA_MAIN

DDR3

Scalar

TV-TUNER

WIRELESS

GPU

REFCLKIN

A A

Note: R0 is 0 ohm optional resister

Note: Rs is serie resister

Note: Green Color is direct-parallel option

5

4

3

2

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Clock Diagram

Clock Diagram

Clock Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Tigris AIO

C

Rosa_Tigris AIO

C

Rosa_Tigris AIO

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

5 58Monday, January 06, 2014

5 58Monday, January 06, 2014

5 58Monday, January 06, 2014

1

1

1

5

RepairLap.com

Destination Signal NameSource

D D

POWER ON SEQUENCE

4

3

2

1

PCH

CPU

PCH

CPU/Board

CPU VRM PCH

CPU VRM CPU

CPU CPU VRM

C C

PCH CPU

PCHBoard

Board CPU VRM

Board PCH

Board Board

Board

Board

Board

Board

SIO Board

B B

PCH Board

PCH Board

PCH Board

Board PCH

Board PCH

SIO

Board

PCH

Board

Board

PCH

Board PCH

A A

Board

Board

PCH

PCH

PCHBoard

Board PCH

DMI Message

PLTRST

PCH_SYSPWROK

V_CPU_CORE

CPU SVID

H_DRAMPWRGD

PWROK3

PCH_1D05V_PG

V_1P05_PCH/

V_1P5_PCH

+12V

VCC/VCC3

V_SM

SIO_PSON_N

SLP_S3#

SLP_S4#

SUSCLK

RSMRST#

SB5V/SB3V

SUS3V_ON#/

SUS5V_ON#

SLP_SUS#

PWR button

DPWROK

5VA/3VA

RTCCLK

<Variant Name>

<Variant Name>

RTCRST#

VccRTC

5

4

3

2

<Variant Name>

Title

Title

Title

Power Sequence

Power Sequence

Power Sequence

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

Rosa_Tig ris AIO

D

Rosa_Tig ris AIO

D

Rosa_Tig ris AIO

D

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

6 58Monday, January 06, 20 14

6 58Monday, January 06, 20 14

6 58Monday, January 06, 20 14

1

1

1

5

RepairLap.com

D D

C C

4

3

2

1

B B

<Variant Name>

<Variant Name>

A A

5

4

3

2

<Variant Name>

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Title

Title

Title

TBD

TBD

TBD

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Tigris AIO

B

Rosa_Tigris AIO

B

Rosa_Tigris AIO

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

Hsichih, Taipei

7 58Monday, January 06, 2014

7 58Monday, January 06, 2014

7 58Monday, January 06, 2014

1

1

1

1

5

RepairLap.com

Intel B75 GPIO

D D

C C

4

3

2

1

SIO SMSC5555

B B

A A

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

GPIO TABLE

GPIO TABLE

GPIO TABLE

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

Rosa_Tig ris AIO

D

Rosa_Tig ris AIO

D

Rosa_Tig ris AIO

D

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

8 58Monday, January 06, 20 14

8 58Monday, January 06, 20 14

8 58Monday, January 06, 20 14

1

1

1

5

RepairLap.com

D D

C C

4

3

2

1

B B

A A

<Variant Name>

<Variant Name>

5

4

<Variant Name>

Title

Title

Title

TBD

TBD

TBD

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Tigris AIO

C

Rosa_Tigris AIO

C

Rosa_Tigris AIO

C

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

9 58Monday, January 06, 2014

9 58Monday, January 06, 2014

9 58Monday, January 06, 2014

1

1

1

5

RepairLap.com

4

3

2

1

CLOCK

CK_PE_100M_MCP_DP19

CK_PE_100M_MCP_DN19

CPU_VCORE

VCC_SENSE42

VSS_SENSE42

H_VIDSCK_VR42

H_VIDSOUT_VR42

XDP

H_VIDALERT_N_VR42

H_TDO14

H_TDI14

H_TCK14

H_TMS14

H_TRST_N14

H_PRDY_N14

H_PREQ_N14

XDP_DBRESET_N14

HSW_XDP_MBP_014

HSW_XDP_MBP_114

HSW_PCUDEBUG_014

HSW_PCUDEBUG_114

HSW_PCUDEBUG_214

HSW_PCUDEBUG_314

HSW_PCUDEBUG_414

HSW_PCUDEBUG_514

HSW_PCUDEBUG_614

HSW_PCUDEBUG_714

HSW_PCUDEBUG_814

HSW_PCUDEBUG_914

HSW_PCUDEBUG_1014

HSW_PCUDEBUG_1114

HSW_PCUDEBUG_1214

HSW_PCUDEBUG_1314

HSW_PCUDEBUG_1414

HSW_PCUDEBUG_1514

HSW_PCUSTB_0_DP14

HSW_PCUSTB_0_DN14

HSW_PCUSTB_1_DP14

HSW_PCUSTB_1_DN14

H_CPURST_N10

XDP_PWR_DEBUG14

D D

C C

OTHER

H_CPURST_N10

VCCST13

H_PWRGD14,18

PLTRST_N21,37

H_SKTOCC_N18

FP_RST_PCH_N18

H_DRAMPWRGD18

CK_DPNS_R_DN19

CK_DPNS_R_DP19

VR_READY14,18,37,42

H_PM_SYNC_020

CPU_THERMTRIP_N20

H_PECI20,37

PLTRST_CPU_N14,20

H_PROCHOT_N37,42

H_PROCHOT_R_N37,42

B B

A A

MINIMIZE STUB BETWEEN THESE AND RESISTORS AT SINAL PAGE

PLACE IN CRB AREA

H_VIDSCK_VR H_VIDSCK

H_VIDALERT_N_VR

PLTRST_CPU_N

1 2

R745 0R0402-PAD-2-GP

1 2

R770 0R0402-PAD-2-GP

1 2

R742 0R0402-PAD-2-GP

R72

1 2

0R0402-PAD-2-GP

Defensive Design

VR_READY

PLTRST_N PLTRST_N_R

V_1P05_PCH

R55 150KR2J-GP(R)

R59 1K3R2F-1-GP(R)

V_SM

R58 10KR2J-3-GP

H_PROCHOT_N

1 2

1 2

R757 1K8R2F-GP

1 2

C26 SCD1U16V2KX-3GP

Joey_SC_0916

R743

R73 150R2F-1-GP

R64 10KR2J-3-GP(R)

Joey_SA_0417 Remove FP_RST_DBR_N

SC100P50V2JN-3GP

1 2

12

0R0402-PAD-2-GP

1 2

1 2

12

(R)

C25

V_CPU_VCCIO_RIGHT

12

H_VIDSOUTH_VIDSOUT_VR

H_VIDALERT_N

MMBT3904DW-1-GP

H_DRAMPWRGD

12

R765

3K3R2J-3-GP

12

R774

51R2J-2-GP

H_PROCHOT_R_N

PWR_DEBUG

12

(R)

R63

665R2F-2-GP

V_CPU_VCCIO_RIGHT

(R75.03904.07C)

6

Q11A

2

1

H_PWRGD

V_CPU_VCCIO_RIGHT

R749 75R2F-2-GP

R769 110R2F-GP

R767 90D9R2F-1-GP(R)

12

R62

75R2F-2-GP

(R)

PLTRST_CPU_N2

(R75.03904.07C)

3

Q11B

5

MMBT3904DW-1-GP

4

1 2

1 2

1 2

12

(R)

R61

43R2J-GP

PLTRST_CPU_N1

H_VIDSCK

H_VIDSOUT

H_VIDALERT_N

H_DRAMPWRGD

Joey_SC_0916

R57 100KR2J-1-GP(R)

DIMM_CA_CPU_VREF_A

V_CPU_CORE

1 2

R746 44D2R2F-GP

12

R768 100R2F-L1-GP-U(R)

1 2

R764 0R0402-PAD-2-GP

12

C38

SCD1U16V2KX-3GP

2010/12/20 SB

Add EMI Cap

03/21:follow CRB1.0 rout the CFG[0] to XDP !

12

R828 49D9R2F-GP

12

C413

SCD022U16V2KX-3GP

DIMM_CA_CPU_VREF_RC

12

R758

24D9R2F-L-GP

XDP_PWR_DEBUG

TP60TPAD28

SB3V

Joey_SA_0417

FP_RST_PCH_N

R744 0R0402-PAD-2-GP

XDP_DBRESET_N

12

TP99TPAD28

TP94TPAD28

Joey_SA_0417 Remove 2.2ohm

VCC3

12

R35

10KR2F-2-GP

(R)

R38 10KR2F-2-GP(R)

R42 10KR2F-2-GP(R)

R47 10KR2F-2-GP(R)

CK_PE_100M_MCP_DN

CK_PE_100M_MCP_DP

H_VIDALERT_N_1

H_DRAMPWRGD_CPU

H_PWRGD

H_CPURST_N

H_PM_SYNC_0

H_PECI

TP_H_CATERR_N

1

H_PROCHOT_R_N

CPU_THERMTRIP_N

H_SKTOCC_N

DIMM_CA_CPU_VREF_A

HSW_PCUDEBUG_0

HSW_PCUDEBUG_1

HSW_PCUDEBUG_2

HSW_PCUDEBUG_3

HSW_PCUDEBUG_4

HSW_PCUDEBUG_5

HSW_PCUDEBUG_6

HSW_PCUDEBUG_7

HSW_PCUDEBUG_8

HSW_PCUDEBUG_9

HSW_PCUDEBUG_10

HSW_PCUDEBUG_11

HSW_PCUDEBUG_12

HSW_PCUDEBUG_13

HSW_PCUDEBUG_14

HSW_PCUDEBUG_15

HSW_PCUSTB_0_DP

HSW_PCUSTB_0_DN

HSW_PCUSTB_1_DP

HSW_PCUSTB_1_DN

H_TCK

H_TDI

H_TDO

H_TMS

H_TRST_N

H_PRDY_N

H_PREQ_N

1 2

TESTLOW_2

TP_RSVD_K8

1

TP_RSVD_J10

1

R740

R741

DEFENSIVE DESIGN PWR_DEBUG

1 2

1 2

1 2

CPU1E

V4

BCLK#

V5

BCLK

C38

VIDSCLK

C37

VIDSOUT

B37

VIDALERT#

AK21

SM_DRAMPWROK

AB35

PWRGOOD

M39

RESET#

P36

PM_SYNC

N37

PECI

M36

CATERR#

K38

PROCHOT#

F37

THERMTRIP#

D38

SKTOCC#

AB38

SM_VREF

AA37

CFG0

Y38

CFG1

AA36

CFG2

W38

CFG3

V39

CFG4

U39

CFG5

U40

CFG6

V38

CFG7

T40

CFG8

Y35

CFG9

AA34

CFG10

V37

CFG11

Y34

CFG12

U38

CFG13

W34

CFG14

V35

CFG15

Y36

CFG17

Y37

CFG16

V36

CFG19

W36

CFG18

D39

TCK

F38

TDI

F39

TDO

E39

TMS

E37

TRST#

L39

PRDY#

L37

PREQ#

G40

DBR#

N5

TESTLO_N5

K8

RSVD_TP_K8

J10

RSVD_TP_J10

HASWE1NFU

0R0402-PAD-2-GP

1 2

0R0402-PAD-2-GP

1 2

1 2

R74 0R0402-PAD-2-GP

PWR_DEBUG_N

12

(R)

R51

0R2J-2-GP

DIMM_CA_VREF_A

DIMM_CA_VREF_B

MMBT3904DW-1-GP

12

(R)

C20

SCD1U16V2KX-3GP

HASWELL

VCC3

(R75.03904.07C)

6

Q9A

2

1

RSVD_T35

RSVD_M38

TESTLO_P6

RSVD_H15

RSVD_H14

RSVD_AV2

RSVD_TP_J16

RSVD_TP_H16

PWR_DEBUG

RSVD_TP_K13

RSVD_TP_J8

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

RSVD_AB36

RSVD_TP_AW2

RSVD_TP_AV1

RSVD_AC8

VCOMP_OUT

RSVD_AB33

RSVD_M10

RSVD_L10

RSVD_M11

RSVD_L12

RSVD_W8

RSVD_R33

RSVD_P33

VCC_SENSE

VSS_SENSE

RSVD_N35

DPLL_REF_CLK#

DPLL_REF_CLK

CFG_RCOMP

DIMM_CA_VREF_A 15

DIMM_CA_VREF_B 16

12

R37

10KR2F-2-GP

(R)

(R75.03904.07C)

3

Q9B

MMBT3904DW-1-GP

4

5 OF 10

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

RSVD_K9

RSVD_J9

VCC_M8

RSVD_U8

RSVD_T8

RSVD_Y8

PWR_DEBUG_1VR_READY

5

HSW_XDP_MBP_0

G39

HSW_XDP_MBP_1

J39

TP_CPU_G38

G38

TP_CPU_H37

H37

TP_CPU_H38

H38

TP_CPU_J38

J38

TP_CPU_K39

K39

TP_CPU_K37

K37

TP_CPU_T35

T35

TP_CPU_M38

M38

TESTLOW_1

P6

K9

VCCST

TP_RSVD_H15

H15

TP_RSVD_J9

J9

TP_RSVD_H14

H14

M8

TP_RSVD_AV2

AV2

TP_RSVD_J16

J16

TP_RSVD_H16

H16

PWR_DEBUG

N40

N39

VSS

TP_RSVD_V7

V7

VSS

TP_RSVD_AB6

AB6

VSS

TP_RSVD_K13

K13

TP_RSVD_J8

J8

DDR_RCOMP_0

R1

DDR_RCOMP_1

P1

DDR_RCOMP_2

R2

TP_RSVD_AB36

AB36

TP_RSVD_AW2

AW2

TP_RSVD_AV1

AV1

TP_RSVD_AC8

AC8

P4

TP_RSVD_U8

U8

TP_RSVD_AB33

AB33

CPU_VSS_T8

T8

TP_RSVD_Y8

Y8

TP_RSVD_M10

M10

TP_RSVD_L10

L10

TP_RSVD_M11

M11

TP_RSVD_L12

L12

TP_RSVD_W8

W8

TP_RSVD_R33

R33

TP_RSVD_P33

P33

VCC_SENSE

E40

N33

VSS

J11

VSS

M9

VSS

J7

VSS

VSS_SENSE

F40

V_1P05_PECI_VCOM

N35

CK_DPNS_R_DN

W6

CK_DPNS_R_DP

W5

TPEV_CFG_RCOMP

H40

PWR_DEBUG

1

TP59 TPAD28

1

TP54 TPAD28

1

TP46 TPAD28

1

TP51 TPAD28

1

TP57 TPAD28

1

TP50 TPAD28

1

TP44 TPAD28

1

TP43 TPAD28

1 2

R829 49D9R2F-GP

1

TP76 TPAD28

1

TP98 TPAD28

1

TP77 TPAD28

V_CPU_CORE

1

TP107 TPAD28

1

TP74 TPAD28

1

TP75 TPAD28

1

TP95 TPAD28

TP101 TPAD28

TP82 TPAD28

TP100 TPAD28

1 2

1 2

1 2

TP40 TPAD28

TP105 TPAD28

TP109 TPAD28

TP93 TPAD28

TP91 TPAD28

TP61 TPAD28

TP97 TPAD28

TP96 TPAD28

TP83 TPAD28

TP92 TPAD28

TP85 TPAD28

TP80 TPAD28

TP90 TPAD28

TP62 TPAD28

TP63 TPAD28

(R)

R71

49D9R2F-GP

TP41 TPAD28

R728

49D9R2F-GP

Joey_SA_0417

Joey_SA_0418

1

1

1

R145 100R2F-L1-GP-U

R146 75R2F-2-GP

R147 100R2F-L1-GP-U

1

1

1

1

V_VCCIOA_LOAD

1

1

1

1

1

1

1

1

1

1

1

12

1

12

5

4

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

CPU LGA 1155_1

CPU LGA 1155_1

CPU LGA 1155_1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Tigris AIO

C

Rosa_Tigris AIO

C

Rosa_Tigris AIO

C

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

10 58Monday, January 06, 2014

10 58Monday, January 06, 2014

10 58Monday, January 06, 2014

1

1

1

5

RepairLap.com

D D

DMI

DMI_IT_MR_DP[0..3]21

DMI_IT_MR_DN[0..3]21

DMI_MT_IR_DP[0..3]21

DMI_MT_IR_DN[0..3]21

FDI

FDI_CSYNC21

FDI_INT21

FDI_TX_DN[0..1]21

FDI_TX_DP[0..1]21

CK_DP_DP19

CK_DP_DN19

C C

DP PORT B

DDSP_B_TX_DN_033

DDSP_B_TX_DP_033

DDSP_B_TX_DN_133

DDSP_B_TX_DP_133

DDSP_B_TX_DN_233

DDSP_B_TX_DP_233

DDSP_B_TX_DN_333

DDSP_B_TX_DP_333

HDMI

DDSP_C_TX_DP_024

DDSP_C_TX_DN_024

DDSP_C_TX_DP_124

DDSP_C_TX_DN_124

DDSP_C_TX_DP_224

DDSP_C_TX_DN_224

DDSP_C_TX_DP_324

DDSP_C_TX_DN_324

eDISPLAY PORT D

B B

DPD_LANE0P26

DPD_LANE0N26

DPD_LANE1P26

DPD_LANE1N26

DISP_UTIL_CPU26

PEG_RXN[7..0]49

PEG_RXN7

PEG_RXN6

PEG_RXN5

PEG_RXN4

PEG_RXN3

PEG_RXN2

PEG_RXN1

PEG_RXN0

PEG_RXP[7..0]49

PEG_RXP7

PEG_RXP6

PEG_RXP5

PEG_RXP4

PEG_RXP3

PEG_RXP2

PEG_RXP1

PEG_RXP0

V_VCCIOA_LOAD

12

R831

24D9R2F-L-GP

Sandy Bridge Socket

SKT1

4

CPU1C

E15

PEG_RX0

F15

PEG_RX#0

D14

PEG_RX1

E14

PEG_RX#1

E13

PEG_RX2

F13

PEG_RX#2

D12

PEG_RX3

E12

PEG_RX#3

E11

PEG_RX4

F11

PEG_RX#4

F10

PEG_RX5

G10

PEG_RX#5

E9

PEG_RX6

F9

PEG_RX#6

F8

PEG_RX7

G8

PEG_RXP7

PEG_RXN7

PEG_RXP6

PEG_RXN6

PEG_RXP5

PEG_RXN5

PEG_RXP4

PEG_RXN4

PEG_RXP3

PEG_RXN3

PEG_RXP2

PEG_RXN2

PEG_RXP1

PEG_RXN1

PEG_RXP0

PEG_RXN0

DMI_IT_MR_DP0

DMI_IT_MR_DN0

DMI_IT_MR_DP1

DMI_IT_MR_DN1

DMI_IT_MR_DP2

DMI_IT_MR_DN2

DMI_IT_MR_DP3

DMI_IT_MR_DN3

TP_PEG_D1

1

TP106TPAD28

TP_PEG_C2

1

TP103TPAD28

TP_PEG_B3

1

TP104TPAD28

TP_PEG_A4

1

TP102TPAD28

PEG_COMP

D3

D4

E4

E5

F5

F6

G4

G5

H5

H6

J4

J5

K5

K6

L4

L5

U3

T3

U1

V1

W2

V2

Y3

W3

D1

C2

B3

A4

P3

PEG_RX#7

PEG_RX8

PEG_RX#8

PEG_RX9

PEG_RX#9

PEG_RX10

PEG_RX#10

PEG_RX11

PEG_RX#11

PEG_RX12

PEG_RX#12

PEG_RX13

PEG_RX#13

PEG_RX14

PEG_RX#14

PEG_RX15

PEG_RX#15

DMI_RX0

DMI_RX#0

DMI_RX1

DMI_RX#1

DMI_RX2

DMI_RX#2

DMI_RX3

DMI_RX#3

RSVD_TP_D1

RSVD_TP_C2

RSVD_TP_B3

RSVD_TP_A4

PEG_RCOMP

HASWE1NFU

HASWELL

3 OF 10

PEG_TX0

PEG_TX#0

PEG_TX1

PEG_TX#1

PEG_TX2

PEG_TX#2

PEG_TX3

PEG_TX#3

PEG_TX4

PEG_TX#4

PEG_TX5

PEG_TX#5

PEG_TX6

PEG_TX#6

PEG_TX7

PEG_TX#7

PEG_TX8

PEG_TX#8

PEG_TX9

PEG_TX#9

PEG_TX10

PEG_TX#10

PEG_TX11

PEG_TX#11

PEG_TX12

PEG_TX#12

PEG_TX13

PEG_TX#13

PEG_TX14

PEG_TX#14

PEG_TX15

PEG_TX#15

DMI_TX0

DMI_TX#0

DMI_TX1

DMI_TX#1

DMI_TX2

DMI_TX#2

DMI_TX3

DMI_TX#3

PCIEX16 swap

CPU_CFG2 pull Low pag14

SKT2

SKT3

A12

B12

B11

C11

C10

D10

B9

C9

C8

D8

B7

C7

A6

B6

B5

C5

E1

E2

F2

F3

G1

G2

H2

H3

J1

J2

K2

K3

M2

M3

L1

L2

AA4

AA5

AB3

AB4

AC5

AC4

AC1

AC2

3

PEG_C_TXP7

PEG_C_TXN7

PEG_C_TXP6

PEG_C_TXN6

PEG_C_TXP5

PEG_C_TXN5

PEG_C_TXP4

PEG_C_TXN4

PEG_C_TXP3

PEG_C_TXN3

PEG_C_TXP2

PEG_C_TXN2

PEG_C_TXP1

PEG_C_TXN1

PEG_C_TXP0

PEG_C_TXN0

DMI_MT_IR_DP0

DMI_MT_IR_DN0

DMI_MT_IR_DP1

DMI_MT_IR_DN1

DMI_MT_IR_DP2

DMI_MT_IR_DN2

DMI_MT_IR_DP3

DMI_MT_IR_DN3

PEG_C_TXN7

PEG_C_TXN6

PEG_C_TXN5

PEG_C_TXN4

PEG_C_TXN3

PEG_C_TXN2

PEG_C_TXN1

PEG_C_TXN0

PEG_C_TXP7

PEG_C_TXP6

PEG_C_TXP5

PEG_C_TXP4

PEG_C_TXP3

PEG_C_TXP2

PEG_C_TXP1

PEG_C_TXP0

1 2

C146 SCD22U10V2KX-1GP

1 2

C133 SCD22U10V2KX-1GP

1 2

C148 SCD22U10V2KX-1GP

(G)

1 2

C135 SCD22U10V2KX-1GP

(G)

1 2

C150 SCD22U10V2KX-1GP

(G)

1 2

C137 SCD22U10V2KX-1GP

(G)

1 2

C152 SCD22U10V2KX-1GP

(G)

1 2

C139 SCD22U10V2KX-1GP

(G)

(G)

(G)

1 2

C147 SCD22U10V2KX-1GP

1 2

C134 SCD22U10V2KX-1GP

1 2

C149 SCD22U10V2KX-1GP

(G)

1 2

C136 SCD22U10V2KX-1GP

(G)

1 2

C151 SCD22U10V2KX-1GP

(G)

1 2

C138 SCD22U10V2KX-1GP

(G)

1 2

C153 SCD22U10V2KX-1GP

(G)

1 2

C140 SCD22U10V2KX-1GP

(G)

(G)

(G)

V_VCCIOA_LOAD

NOTE.

If PEG is not implemented, the RX&TX pairs can be left as No Connect

12

FDI_CSYNC

R830

FDI_INT

24D9R2F-L-GP

FDI_COMP

CK_DP_DN

CK_DP_DP

DISP_UTIL_CPU DDSP_C_TX_DP_1

TP_DISP_K11

1

TP88TPAD28

TP_DISP_J12

1

TP84TPAD28

FDI_TX_DN0

FDI_TX_DP0

FDI_TX_DN1

FDI_TX_DP1

2

PEG_TXN7

PEG_TXN6

PEG_TXN5

PEG_TXN4

PEG_TXN3

PEG_TXN2

PEG_TXN1

PEG_TXN0

PEG_TXP7

PEG_TXP6

PEG_TXP5

PEG_TXP4

PEG_TXP3

PEG_TXP2

PEG_TXP1

PEG_TXP0

CPU1D

D16

FDI_CSYNC

D18

FDI_INT

R4

DP_COMP

U5

SSC_DPLL_REF_CLK#

U6

SSC_DPLL_REF_CLK

E16

EDP_DISP_UTIL

K11

RSVD_TP_K11

J12

RSVD_TP_J12

B14

FDI0_TX0#0

A14

FDI0_TX00

C13

FDI0_TX0#1

B13

FDI0_TX01

HASWE1NFU

PEG_TXN[7..0] 49

PEG_TXP[7..0] 49

HASWELL

4 OF 10

DDIB_TXB0

DDIB_TXB#0

DDIB_TXB1

DDIB_TXB#1

DDIB_TXB2

DDIB_TXB#2

DDIB_TXB3

DDIB_TXB#3

DDIC_TXC0

DDIC_TXC#0

DDIC_TXC1

DDIC_TXC#1

DDIC_TXC2

DDIC_TXC#2

DDIC_TXC3

DDIC_TXC#3

DDID_TXD0

DDID_TXD#0

DDID_TXD1

DDID_TXD#1

DDID_TXD2

DDID_TXD#2

DDID_TXD3

DDID_TXD#3

E17

F17

F18

G18

G19

H19

F20

G20

D19

E19

C20

D20

D21

E21

C22

D22

B15

C15

A16

B16

B17

C17

A18

B18

1

DDSP_B_TX_DP_0

DDSP_B_TX_DN_0

DDSP_B_TX_DP_1

DDSP_B_TX_DN_1

DDSP_B_TX_DP_2

DDSP_B_TX_DN_2

DDSP_B_TX_DP_3

DDSP_B_TX_DN_3

DDSP_C_TX_DP_0

DDSP_C_TX_DN_0

DDSP_C_TX_DN_1

DDSP_C_TX_DP_2

DDSP_C_TX_DN_2

DDSP_C_TX_DP_3

DDSP_C_TX_DN_3

DPD_LANE0P

DPD_LANE0N

DPD_LANE1P

DPD_LANE1N

DPD_LANE2P

DPD_LANE2N

DPD_LANE3P

DPD_LANE3N

Joey_SA_0410

Joey_SA_0517

1

1

1

1

DP

HDMI

eDP

TP7 TPAD28

TP6 TPAD28

TP5 TPAD28

TP4 TPAD28

A A

Load Plate

(22.78003.021)

5

Back Plate

(22.78006.031)

4

CPU Cover

(42.3EQ28.002)

3

2

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

CPU LGA 1155_2

CPU LGA 1155_2

CPU LGA 1155_2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Tigris AIO

Custom

Rosa_Tigris AIO

Custom

Rosa_Tigris AIO

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

11 58Monday, January 06, 2014

11 58Monday, January 06, 2014

11 58Monday, January 06, 2014

1

1

1

5

RepairLap.com

DDR DATA

M_DATA_A[0..63]15

M_DATA_B[0..63]16

M_DQS_A_DP[0..7]15

M_DQS_A_DN[0..7]15

M_DQS_B_DP[0..7]16

D D

M_DQS_B_DN[0..7]16

DDR CMD/ADD

M_MAA_A[0..15]15

M_MAA_B[0..15]16

M_WE_A_N15

M_CAS_A_N15

M_RAS_A_N15

M_SBS_A015

M_SBS_A115

M_SBS_A215

M_WE_B_N16

M_CAS_B_N16

M_RAS_B_N16

M_SBS_B016

M_SBS_B116

M_SBS_B216

DDR CTRL

M_SCS_A_N015

C C

M_SCS_A_N115

M_SCKE_A015

M_SCKE_A115

M_ODT_A015

M_ODT_A115

M_SCS_B_N016

M_SCS_B_N116

M_SCKE_B016

M_SCKE_B116

M_ODT_B016

M_ODT_B116

DDR CLOCK

CK_M_DDR0_A_DP15

CK_M_DDR0_A_DN15

CK_M_DDR1_A_DP15

CK_M_DDR1_A_DN15

CK_M_DDR0_B_DP16

CK_M_DDR0_B_DN16

B B

CK_M_DDR1_B_DP16

CK_M_DDR1_B_DN16

DDR OTHERS

DDR3_DRAMRST_N15,16

DIMM_DQ_CPU_VREF_B16

DIMM_DQ_CPU_VREF_A15

M_DATA_A0

M_DATA_A1

M_DATA_A2

M_DATA_A3

M_DATA_A4

M_DATA_A5

M_DATA_A6

M_DATA_A7

M_DATA_A8

M_DATA_A9

M_DATA_A10

M_DATA_A11

M_DATA_A12

M_DATA_A13

M_DATA_A14

M_DATA_A15

M_DATA_A16

M_DATA_A17

M_DATA_A18

M_DATA_A19

M_DATA_A20

M_DATA_A21

M_DATA_A22

M_DATA_A23

M_DATA_A24

M_DATA_A25

M_DATA_A26

M_DATA_A27

M_DATA_A28

M_DATA_A29

M_DATA_A30

M_DATA_A31

M_DATA_A32

M_DATA_A33

M_DATA_A34

M_DATA_A35

M_DATA_A36

M_DATA_A37

M_DATA_A38

M_DATA_A39

M_DATA_A40

M_DATA_A41

M_DATA_A42

M_DATA_A43

M_DATA_A44

M_DATA_A45

M_DATA_A46

M_DATA_A47

M_DATA_A48

M_DATA_A49

M_DATA_A50

M_DATA_A51

M_DATA_A52

M_DATA_A53

M_DATA_A54

M_DATA_A55

M_DATA_A56

M_DATA_A57

M_DATA_A58

M_DATA_A59

M_DATA_A60

M_DATA_A61

M_DATA_A62

M_DATA_A63

M_DQS_A_DP0

M_DQS_A_DP1

M_DQS_A_DP2

M_DQS_A_DP3

M_DQS_A_DP4

M_DQS_A_DP5

M_DQS_A_DP6

M_DQS_A_DP7

M_DQS_A_DN0

M_DQS_A_DN1

M_DQS_A_DN2

M_DQS_A_DN3

M_DQS_A_DN4

M_DQS_A_DN5

M_DQS_A_DN6

M_DQS_A_DN7

AD38

AD39

AF38

AF39

AD37

AD40

AF37

AF40

AH40

AH39

AK38

AK39

AH37

AH38

AK37

AK40

AM40

AM39

AP38

AP39

AM37

AM38

AP37

AP40

AV37

AW37

AU35

AV35

AT37

AU37

AT35

AW35

AW6

AW4

AE39

AJ39

AN39

AV36

AV32

AE38

AJ38

AN38

AU36

AW5

AU32

AY6

AU6

AV4

AU4

AV6

AY4

AR1

AR4

AN3

AN4

AR2

AR3

AN2

AN1

AL1

AL4

AJ3

AJ4

AL2

AL3

AJ2

AJ1

AG1

AG4

AE3

AE4

AG2

AG3

AE2

AE1

AV5

AP3

AK3

AF3

AP2

AK2

AF2

4

CPU1A

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS8

SA_DQS#0

SA_DQS#1

SA_DQS#2

SA_DQS#3

SA_DQS#4

SA_DQS#5

SA_DQS#6

SA_DQS#7

SA_DQS#8

HASWE1NFU

HASWELL

1 OF 10

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_ODT0

SA_ODT1

SA_ODT2

SA_ODT3

SA_ECC_CB0

SA_ECC_CB1

SA_ECC_CB2

SA_ECC_CB3

SA_ECC_CB4

SA_ECC_CB5

SA_ECC_CB6

SA_ECC_CB7

SA_BS0

SA_BS1

SA_BS2

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_CS#2

SA_CS#3

SA_CK0

SA_CK#0

SA_CK1

SA_CK#1

SA_CK2

SA_CK#2

SA_CK3

SA_CK#3

RSVD_AW12

SA_RAS#

SA_WE#

RSVD_AV20

RSVD_AW27

SA_CAS#

SM_DRAMRST#

M_MAA_A0

AU13

M_MAA_A1

AV16

M_MAA_A2

AU16

M_MAA_A3

AW17

M_MAA_A4

AU17

M_MAA_A5

AW18

M_MAA_A6

AV17

M_MAA_A7

AT18

M_MAA_A8

AU18

M_MAA_A9

AT19

M_MAA_A10

AW11

M_MAA_A11

AV19

M_MAA_A12

AU19

M_MAA_A13

AY10

M_MAA_A14

AT20

M_MAA_A15

AU21

M_ODT_A0

AW10

M_ODT_A1

AY8

AW9

AU8

AW33

AV33

AU31

AV31

Can be left as no connects

AT33

if no support ECC.

AU33

AT31

AW31

M_SBS_A0

AV12

M_SBS_A1

AY11

M_SBS_A2

AT21

M_SCKE_A0

AV22

M_SCKE_A1

AT23

AU22

AU23

M_SCS_A_N0

AU14

M_SCS_A_N1

AV9

AU10

AW8

CK_M_DDR0_A_DP

AY15

CK_M_DDR0_A_DN

AY16

CK_M_DDR1_A_DP

AW15

CK_M_DDR1_A_DN

AV15

AV14

AW14

AW13

AY13

TP_RSVD_AW12

AW12

M_RAS_A_N

AU12

M_WE_A_N

AU11

TP_RSVD_AV20

AV20

TP_RSVD_AW27

AW27

M_CAS_A_N

AU9

DDR3_DRAMRST_N

AK22

12

1

1

1

(R)

C412

SCD1U10V2KX-5GP

3

TP81 TPAD28

TP71 TPAD28

TP65 TPAD28

M_DATA_B0

M_DATA_B1

M_DATA_B2

M_DATA_B3

M_DATA_B4

M_DATA_B5

M_DATA_B6

M_DATA_B7

M_DATA_B8

M_DATA_B9

M_DATA_B10

M_DATA_B11

M_DATA_B12

M_DATA_B13

M_DATA_B14

M_DATA_B15

M_DATA_B16

M_DATA_B17

M_DATA_B18

M_DATA_B19

M_DATA_B20

M_DATA_B21

M_DATA_B22

M_DATA_B23

M_DATA_B24

M_DATA_B25

M_DATA_B26

M_DATA_B27

M_DATA_B28

M_DATA_B29

M_DATA_B30

M_DATA_B31

M_DATA_B32

M_DATA_B33

M_DATA_B34

M_DATA_B35

M_DATA_B36

M_DATA_B37

M_DATA_B38

M_DATA_B39

M_DATA_B40

M_DATA_B41

M_DATA_B42

M_DATA_B43

M_DATA_B44

M_DATA_B45

M_DATA_B46

M_DATA_B47

M_DATA_B48

M_DATA_B49

M_DATA_B50

M_DATA_B51

M_DATA_B52

M_DATA_B53

M_DATA_B54

M_DATA_B55

M_DATA_B56

M_DATA_B57

M_DATA_B58

M_DATA_B59

M_DATA_B60

M_DATA_B61

M_DATA_B62

M_DATA_B63

M_DQS_B_DP0

M_DQS_B_DP1

M_DQS_B_DP2

M_DQS_B_DP3

M_DQS_B_DP4

M_DQS_B_DP5

M_DQS_B_DP6

M_DQS_B_DP7

M_DQS_B_DN0

M_DQS_B_DN1

M_DQS_B_DN2

M_DQS_B_DN3

M_DQS_B_DN4

M_DQS_B_DN5

M_DQS_B_DN6

M_DQS_B_DN7

AE34

AE35

AG35

AH35

AD34

AD35

AG34

AH34

AL34

AL35

AK31

AL31

AK34

AK35

AK32

AL32

AN34

AP34

AN31

AP31

AN35

AP35

AN32

AP32

AM29

AM28

AR29

AR28

AL29

AL28

AP29

AP28

AR12

AP12

AL13

AL12

AR13

AP13

AM13

AM12

AR10

AP10

AM10

AL10

AF35

AL33

AP33

AN28

AN12

AN25

AF34

AK33

AN33

AN29

AN13

AN26

AR9

AP9

AR6

AP6

AR7

AP7

AM9

AL9

AL6

AL7

AM6

AM7

AH6

AH7

AE6

AE7

AF6

AF7

AP8

AL8

AG7

AR8

AM8

AG6

AJ6

AJ7

CPU1B

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS8

SB_DQS#0

SB_DQS#1

SB_DQS#2

SB_DQS#3

SB_DQS#4

SB_DQS#5

SB_DQS#6

SB_DQS#7

SB_DQS#8

HASWE1NFU

2

HASWELL

2 OF 10

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_ODT0

SB_ODT1

SB_ODT2

SB_ODT3

SB_ECC_CB0

SB_ECC_CB1

SB_ECC_CB2

SB_ECC_CB3

SB_ECC_CB4

SB_ECC_CB5

SB_ECC_CB6

SB_ECC_CB7

SB_BS0

SB_BS1

SB_BS2

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_CS#2

SB_CS#3

SB_CK0

SB_CK#0

SB_CK1

SB_CK#1

SB_CK2

SB_CK#2

SB_CK3

SB_CK#3

SB_CAS#

RSVD_AL20

SB_RAS#

SB_WE#

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

M_MAA_B0

AL19

M_MAA_B1

AK23

M_MAA_B2

AM22

M_MAA_B3

AM23

M_MAA_B4

AP23

M_MAA_B5

AL23

M_MAA_B6

AY24

M_MAA_B7

AV25

M_MAA_B8

AU26

M_MAA_B9

AW25

M_MAA_B10

AP18

M_MAA_B11

AY25

M_MAA_B12

AV26

M_MAA_B13

AR15

M_MAA_B14

AV27

M_MAA_B15

AY28

M_ODT_B0

AM17

M_ODT_B1

AL16

AM16

AK15

AM26

AM25

AP25

AP26

Can be left as no connects

AL26

if no support ECC.

AL25

AR26

AR25

M_SBS_B0

AK17

M_SBS_B1

AL18

M_SBS_B2

AW28

M_SCKE_B0

AW29

M_SCKE_B1

AY29

AU28

AU29

M_SCS_B_N0

AP17

M_SCS_B_N1

AN15

AN17

AL15

CK_M_DDR0_B_DP

AM20

CK_M_DDR0_B_DN

AM21

CK_M_DDR1_B_DP

AP22

CK_M_DDR1_B_DN

AP21

AN20

AN21

AP19

AP20

M_CAS_B_N

AP16

AL20

M_RAS_B_N

AM18

M_WE_B_N

AK16

DIMM_DQ_CPU_VREF_A

AB39

DIMM_DQ_CPU_VREF_B

AB40

C40

SCD1U16V2KX-3GP

12

1

12

C39

SCD1U16V2KX-3GP

A A

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

CPU LGA 1155_3

CPU LGA 1155_3

CPU LGA 1155_3

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Tigris AIO

Custom

Rosa_Tigris AIO

Custom

Rosa_Tigris AIO

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

12 58Monday, January 06, 2014

12 58Monday, January 06, 2014

12 58Monday, January 06, 2014

1

1

1

5

RepairLap.com

4

3

2

1

For support Broadwell CPU

1 2

R826 0R2J-2-GP

VCCST10

PWRGD_3V18,20,37

D D

C C

V_1P05_PCH

V_CPU_VCCIO2PCH

VCCST

SCD1U16V2KX-3GP

12

C452

V_1P05_PCH

V_CPU_VCCIO_RIGHT

12

R824

0R3J-0-U-GP

12

C440

SC4D7U6D3V3KX-GP

R823 0R2J-2-GP(R)

R772 0R2J-2-GP(R)

1 2

1 2

R773

1 2

0R2J-2-GP

V_CPU_CORE

V_CPU_CORE

V_CPU_VCCIO_OUT

VCCIO2PCH

HASWELL

6 OF 10

CPU1I

A5

C31

VCC

C33

VCC

L16

VCC

L15

VCC

J35

VCC

H33

VCC

H35

VCC

J21

VCC

J22

VCC

J23

VCC

J24

VCC

J25

VCC

J26

VCC

J27

VCC

J28

VCC

J29

VCC

J30

VCC

J32

VCC

J34

VCC

K19

VCC

K21

VCC

K23

VCC

K25

VCC

K27

VCC

K29

VCC

K31

VCC

M13

VCC

K33

VCC

K35

VCC

L19

VCC

L20

VCC

L21

VCC

L22

VCC

L23

VCC

L24

VCC

L25

VCC

L26

VCC

L27

VCC

L28

VCC

L29

VCC

L30

VCC

L32

VCC

L33

VCC

M17

VCC

M15

VCC

M19

VCC

M21

VCC

M23

VCC

M25

VCC

M27

VCC

M29

VCC

M33

VCC

AJ12

VDDQ

AJ13

VDDQ

AJ15

VDDQ

AJ17

VDDQ

AJ20

VDDQ

AJ21

VDDQ

AJ24

VDDQ

AJ25

VDDQ

AJ28

VDDQ

AJ29

VDDQ

AJ9

VDDQ

AT17

VDDQ

AT22

VDDQ

AU15

VDDQ

AU20

VDDQ

AU24

VDDQ

AV10

VDDQ

AV11

VDDQ

AV13

VDDQ

AV18

VDDQ

AV23

VDDQ

AV8

VDDQ

AW16

VDDQ

AY12

VDDQ

AY14

VDDQ

AY9

VDDQ

VSS

A7

VSS

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A23

VSS

AA3

VSS

AA6

VSS

AA7

VSS

AA8

VSS

AA33

VSS

AA35

VSS

AA38

VSS

AB5

VSS

AB7

VSS

AB34

VSS

AB37

VSS

AC3

VSS

AC6

VSS

AC7

VSS

AC33

VSS

AC34

VSS

AC35

VSS

AC36

VSS

AC37

VSS

AC38

VSS

AC39

VSS

AC40

VSS

AD1

VSS

AD2

VSS

AD3

VSS

AD4

VSS

AD5

VSS

AD6

VSS

AD7

VSS

AD8

VSS

AD33

VSS

AD36

VSS

AE5

VSS

AE8

VSS

AE33

VSS

AE36

VSS

AE37

VSS

AE40

VSS

AF1

VSS

AF4

VSS

AF5

VSS

AF8

VSS

AF33

VSS

AF36

VSS

AG5

VSS

AG8

VSS

AG33

VSS

AG36

V_SM

VSS

AG37

VSS

AG38

VSS

AG39

VSS

AG40

VSS

AH1

VSS

AH2

VSS

AH3

VSS

AH4

VSS

AH5

VSS

AH8

VSS

AH33

VSS

AH36

VSS

AJ11

VSS

AJ14

VSS

AJ16

VSS

AJ18

VSS

AJ19

VSS

AJ22

VSS

AJ23

VSS

AJ26

VSS

AJ27

VSS

AJ30

VSS

AJ31

VSS

AJ32

VSS

AJ33

VSS

HASWE1NFU

CPU1F

P8

VCC

L40

VCCIO_OUT

AB8

VCCIO2PCH

L31

VCC

L18

VCC

L17

VCC

J33

VCC

A24

VCC

A25

VCC

A26

VCC

A27

VCC

A28

VCC

A29

VCC

A30

VCC

G33

VCC

B25

VCC

B27

VCC

B29

VCC

B31

VCC

J31

VCC

B33

VCC

G31

VCC

B35

VCC

C24

VCC

C25

VCC

C26

VCC

C27

VCC

C28

VCC

C29

VCC

C30

VCC

C32

VCC

C34

VCC

C35

VCC

D25

VCC

D27

VCC

D29

VCC

D31

VCC

E33

VCC

D33

VCC

E31

VCC

D35

VCC

E24

VCC

E25

VCC

E26

VCC

E27

VCC

E28

VCC

E29

VCC

E30

VCC

E32

VCC

E34

VCC

F23

VCC

F25

VCC

F27

VCC

F29

VCC

F31

VCC

E35

VCC

F33

VCC

F35

VCC

G22

VCC

G23

VCC

G24

VCC

G25

VCC

G26

VCC

G27

VCC

G28

VCC

G29

VCC

G30

VCC

G32

VCC

G34

VCC

G35

VCC

H23

VCC

H25

VCC

H27

VCC

H29

VCC

H31

VCC

L34

VCC

HASWE1NFU

HASWELL

9 OF 10

AJ5

VSS

AJ8

VSS

AJ34

VSS

AJ35

VSS

AJ36

VSS

AJ37

VSS

AJ40

VSS

AK1

VSS

AK4

VSS

AK5

VSS

AK6

VSS

AK7

VSS

AK8

VSS

AK9

VSS

AK10

VSS

AK11

VSS

AK12

VSS

AK13

VSS

AK14

VSS

AK18

VSS

AK19

VSS

AK24

VSS

AK25

VSS

AK26

VSS

AK27

VSS

AK28

VSS

AK29

VSS

AK30

VSS

AK36

VSS

AL5

VSS

AL11

VSS

AL14

VSS

AL17

VSS

AL21

VSS

AL22

VSS

AL24

VSS

AL27

VSS

AL30

VSS

AL36

VSS

AL37

VSS

AL38

VSS

AL39

VSS

AL40

VSS

AM1

VSS

AM2

VSS

AM3

VSS

AM4

VSS

AM5

VSS

AM11

VSS

AM14

VSS

AM15

VSS

AM19

VSS

AM24

VSS

AM27

VSS

AM30

VSS

AM31

VSS

AM32

VSS

AM33

VSS

AM34

VSS

AM35

VSS

AM36

VSS

AN5

VSS

AN6

VSS

AN7

VSS

AN8

VSS

AN9

VSS

AN10

VSS

AN11

VSS

AN14

VSS

AN16

VSS

AN18

VSS

AN19

VSS

AN22

VSS

AN23

VSS

AN24

VSS

AN27

VSS

AN30

VSS

AN36

VSS

AN37

VSS

AN40

VSS

AP1

VSS

CPU1G

AP11

VSS

AP14

VSS

AP15

VSS

AP24

VSS

AP27

VSS

AP30

VSS

AP36

VSS

AP4

VSS

AP5

VSS

AR11

VSS

AR14

VSS

AR16

VSS

AR17

VSS

AR18

VSS

AR19

VSS

AR20

VSS

AR21

VSS

AR22

VSS

AR23

VSS

AR24

VSS

AR27

VSS

AR30

VSS

AR31

VSS

AR32

VSS

AR33

VSS

AR34

VSS

AR35

VSS

AR36

VSS

AR37

VSS

AR38

VSS

AR39

VSS

AR40

VSS

AR5

VSS

AT1

VSS

AT10

VSS

AT11

VSS

AT12

VSS

AT13

VSS

AT14

VSS

AT15

VSS

AT16

VSS

AT2

VSS

AT24

VSS

AT25

VSS

AT26

VSS

AT27

VSS

AT28

VSS

AT29

VSS

AT3

VSS

AT30

VSS

AT32

VSS

AT34

VSS

AT36

VSS

AT38

VSS

AT39

VSS

AT4

VSS

AT5

VSS

AT6

VSS

AT7

VSS

AT8

VSS

AT9

VSS

AU2

VSS

AU25

VSS

AU3

VSS

AU30

VSS

AU34

VSS

AU38

VSS

AU5

VSS

AU7

VSS

AV21

VSS

AV28

VSS

AV3

VSS

AV30

VSS

AV34

VSS

AV38

VSS

AV7

VSS

AW26

VSS

AW3

VSS

AW30

VSS

HASWE1NFU

V_CPU_CORE

HASWELL

7 OF 10

AW32

VSS

AW34

VSS

AW36

VSS

AW7

VSS

AY17

VSS

AY23

VSS

AY26

VSS

AY27

VSS

AY30

VSS

AY5

VSS

AY7

VSS

B24

VSS

B26

VSS

B28

VSS

B30

VSS

B34

VSS

B36

VSS

B4

VSS

B8

VSS

C4

VSS

C6

VSS

C12

VSS

C14

VSS

C16

VSS

C18

VSS

C19

VSS

C21

VSS

C23

VSS

C36

VSS

B10

VSS

B23

VSS

C3

VSS

D9

VSS

D11

VSS

D13

VSS

D15

VSS

D17

VSS

D2

VSS

D23

VSS

D24

VSS

D26

VSS

D28

VSS

D30

VSS

D34

VSS

D36

VSS

D37

VSS

D5

VSS

D6

VSS

D7

VSS

E7

VSS

E8

VSS

E10

VSS

E18

VSS

E3

VSS

E20

VSS

E22

VSS

E23

VSS

E36

VSS

E38

VSS

B32

VSS

E6

VSS

F1

VSS

F32

VSS

F12

VSS

F14

VSS

F16

VSS

F19

VSS

F21

VSS

F22

VSS

F24

VSS

F26

VSS

F28

VSS

F30

VSS

F34

VSS

F36

VSS

F4

VSS

D32

VSS

F7

VSS

G9

VSS

G11

VSS

CPU1J

G3

VSS

G6

VSS

G7

VSS

G12

VSS

G13

VSS

G14

VSS

G15

VSS

G16

VSS

G17

VSS

G21

VSS

G36

VSS

G37

VSS

H1

VSS

H4

VSS

H7

VSS

H8

VSS

H9

VSS

H10

VSS

H11

VSS

H13

VSS

H17

VSS

H18

VSS

H20

VSS

H21

VSS

H22

VSS

H24

VSS

H26

VSS

H28

VSS

H30

VSS

H32

VSS

H34

VSS

H36

VSS

H39

VSS

J3

VSS

J6

VSS

J18

VSS

J19

VSS

J20

VSS

J36

VSS

J37

VSS

K1

VSS

K4

VSS

K7

VSS

K10

VSS

K14

VSS

K17

VSS

K18

VSS

K20

VSS

K22

VSS

K24

VSS

K26

VSS

K28

VSS

K30

VSS

K34

VSS

K36

VSS

K40

VSS

L3

VSS

L6

VSS

L7

VSS

L8

VSS

L9

VSS

L11

VSS

L13

VSS

L14

VSS

L35

VSS

L38

VSS

M1

VSS

M12

VSS

M14

VSS

M16

VSS

M18

VSS

M20

VSS

M22

VSS

M24

VSS

M26

VSS

M28

VSS

M30

VSS

M32

VSS

M34

VSS

M37

VSS

HASWE1NFU

10 OF 10

HASWELL

NCTF TEST PIN: AU40,

K15

VSS

K16

VSS

K32

VSS

L36

VSS

M4

VSS

M5

VSS

M6

VSS

M7

VSS

M35

VSS

M40

VSS

N1

VSS

N2

VSS

N3

VSS

N4

VSS

N6

VSS

N7

VSS

N8

VSS

N34

VSS

P2

VSS

P5

VSS

P7

VSS

P34

VSS

P35

VSS

P38

VSS

R3

VSS

R5

VSS

R6

VSS

R7

VSS

R8

VSS

R35

VSS

R40

VSS

T1

VSS

T2

VSS

T4

VSS

T5

VSS

T6

VSS

T7

VSS

T33

VSS

T39

VSS

U2

VSS

U4

VSS

U7

VSS

U33

VSS

U34

VSS

U37

VSS

V3

VSS

V6

VSS

V8

VSS

V33

VSS

V40

VSS

W1

VSS

W4

VSS

W7

VSS

W33

VSS

W35

VSS

W37

VSS

Y4

VSS

Y5

VSS

Y6

VSS

Y33

VSS

AU40

VSS_NCTF_AU40

AV39

VSS_NCTF_AV39

AW38

VSS_NCTF_AW38

AY3

VSS_NCTF_AY3

B38

VSS_NCTF_B38

B39

VSS_NCTF_B39

C40

VSS_NCTF_C40

D40

VSS_NCTF_D40

AV39,AW38,AY3,B38,B39,C40,D40

PWRGD_3V

6K04R2F-GP

2K67R2F-2-GP

HASWELL

8 OF 10

RSVD_TP_K12

RSVD_TP_J13

RSVD_TP_P37

RSVD_TP_N38

RSVD_TP_R36

RSVD_TP_C39

RSVD_TP_N36

TP_RSVD_K12

TP_RSVD_J13

TP_RSVD_P37

TP_RSVD_N38

TP_RSVD_R36

TP_RSVD_C39

TP_CPU_N36

1

TP87 TPAD28

1

TP79 TPAD28

1

TP47 TPAD28

1

TP55 TPAD28

1

TP45 TPAD28

1

TP58 TPAD28

1

TP53 TPAD28

K12

J13

P37

N38

R36

C39

U35

VSS

P40

VSS

R38

VSS

T37

VSS

V34

VSS

R39

VSS

T38

VSS

U36

VSS

P39

VSS

T36

VSS

R37

VSS

J14

VSS

N36

CPU1H

TP_RSVD_AY18

AY18

1

TP72TPAD28

TP_RSVD_AW24

1

TP68TPAD28

TP_RSVD_AW23

1

TP69TPAD28

TP_RSVD_AV29

1

TP64TPAD28

12

R162

12

R163

TP_RSVD_AV24

1

TP67TPAD28

TP_RSVD_AU39

1

TP49TPAD28

TP_RSVD_AU27

1

TP66TPAD28

TP_RSVD_AU1

1

TP108TPAD28

TP_RSVD_AT40

1

TP48TPAD28

TP_RSVD_AK20

1

TP70TPAD28

VCCST_PWRGD

TP_RSVD_T34

1

TP56TPAD28

TP_RSVD_R34

1

TP52TPAD28

TP_RSVD_J40

1

TP42TPAD28

TP_RSVD_J17

1

TP73TPAD28

TP_RSVD_J15

1

TP78TPAD28

TP_RSVD_H12

1

TP86TPAD28

RSVD_AY18

AW24

RSVD_AW24

AW23

RSVD_AW23

AV29

RSVD_AV29

AV24

RSVD_AV24

AU39

RSVD_AU39

AU27

RSVD_AU27

AU1

RSVD_AU1

AT40

RSVD_AT40

AK20

RSVD_AK20

Y7

RSVD_Y7

T34

RSVD_T34

R34

RSVD_R34

J40

RSVD_J40

J17

RSVD_J17

J15

RSVD_J15

H12

RSVD_H12

HASWE1NFU

PLACE ALL 0805 CAPS INSIDE CPU SOCKET CAVITY

B B

V_CPU_CORE

V_SM

12

C64

SC22U6D3V5MX-2GP

12

C83

SC22U6D3V5MX-2GP

12

C82

SC22U6D3V5MX-2GP

12

C55

SC22U6D3V5MX-2GP

12

C425

SC22U6D3V5MX-2GP

12

C74

SC22U6D3V5MX-2GP

12

12

C57

SC22U6D3V5MX-2GP

C70

SC22U6D3V5MX-2GP

V_CPU_CORE

(R)

12

C91

SC22U6D3V5MX-2GP

12

C58

SC22U6D3V5MX-2GP

12

C61

SC22U6D3V5MX-2GP

(R)

12

C66

SC22U6D3V5MX-2GP

12

C72

SC22U6D3V5MX-2GP

12

C62

SC22U6D3V5MX-2GP

(R)

12

C59

SC22U6D3V5MX-2GP

12

C53

SC22U6D3V5MX-2GP

12

C69

SC22U6D3V5MX-2GP

(R)

12

C63

SC22U6D3V5MX-2GP

12

C89

SC22U6D3V5MX-2GP

12

C77

SC22U6D3V5MX-2GP

(R)

12

C78

SC22U6D3V5MX-2GP

12

C90

SC22U6D3V5MX-2GP

12

C54

SC22U6D3V5MX-2GP

12

C73

SC22U6D3V5MX-2GP

12

C427

SC22U6D3V5MX-2GP

12

C426

SC22U6D3V5MX-2GP

12

C424

SC22U6D3V5MX-2GP

CPU Power Capacitor Quantity

Vcore

V_SM 22uf 0805 4+5(R)

Net

CAP AMOUNT

22uf 0805 22

PLACE CAPS AT TOP SOCKET EDGE

A A

5

V_CPU_CORE

12

C76

SC22U6D3V5MX-2GP

12

C65

SC22U6D3V5MX-2GP

12

C68

SC22U6D3V5MX-2GP

12

C81

SC22U6D3V5MX-2GP

V_CPU_VCCIO_RIGHT

12

C411

SC4D7U6D3V3KX-GP

4

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

CPU LGA 1155_4

CPU LGA 1155_4

CPU LGA 1155_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Tigris AIO

Custom

Rosa_Tigris AIO

Custom

Rosa_Tigris AIO

Custom

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

13 58Monday, January 06, 2014

13 58Monday, January 06, 2014

13 58Monday, January 06, 2014

1

1

1

5

RepairLap.com

XDP for CPU

D D

H_TDO10

H_TDI10

H_TMS10

H_TCK10

H_TRST_N10

H_PREQ_N10

H_PRDY_N10

XDP_DBRESET_N10

H_PWRGD10,18

HSW_PCUDEBUG_010

HSW_PCUDEBUG_110

HSW_PCUDEBUG_210

HSW_PCUDEBUG_310

HSW_PCUDEBUG_410

HSW_PCUDEBUG_510

HSW_PCUDEBUG_610

HSW_PCUDEBUG_710

HSW_PCUDEBUG_810

HSW_PCUDEBUG_910

HSW_PCUDEBUG_1010

HSW_PCUDEBUG_1110

HSW_PCUDEBUG_1210

HSW_PCUDEBUG_1310

HSW_PCUDEBUG_1410

HSW_PCUDEBUG_1510

HSW_XDP_MBP_010

HSW_XDP_MBP_110

HSW_PCUSTB_0_DP10

HSW_PCUSTB_0_DN10

HSW_PCUSTB_1_DP10

HSW_PCUSTB_1_DN10

XDP_PWR_DEBUG10

SMB_DATA_MAIN15,16,26,37,50

SMB_CLK_MAIN15,16,26,37 ,50

HSW_STRAP_1322

CK_100M_CPU_XDP_DN19

CK_100M_CPU_XDP_DP19

PLTRST_CPU_N10,20

APS CONNECTOR

C C

SLP_S3_N18,37,39,42,45,47,48

SLP_S4_N18,37,45,46

PCH_SLP_M_N18

XDP for PCH

LANCLK_REQ_N1 8,29

PCH_JTAG_RST_R18

PCH_JTAG_TDO18

PCH_JTAG_TDI18

PCH_JTAG_TMS18

PCH_JTAG_TCK18

PWRBTN_N18,34,37

IGC_EN_N18 ,22

VR_READY10,18,37,42

XDP for CPU

V_CPU_VCCIO_RIGHT

PLace Near CPU

PLTRST_CPU_N

H_PWRGD

PWRBTN_N

R638 1KR2J-1-GP

R698 0R0402-PAD-2-GP

2012/04/05 SB BOM Change 249 to 1k

R696 1KR2J-1-GP

1 2

R697 0R0402-PAD-2-GP

XDP for PCH

1 2

SB3V

R862 0R0402-PAD-2-GP

C173 SCD1U16V2KX-3GP

R254 51R2J-2-GP

PLace Near XDP CONN

1 2

R644 51R2J-2-GP(R)

1 2

R645 51R2J-2-GP(R)

1 2

R699 51R2J-2-GP

H_TCK TERMINATI ON PLACE

NEAR CPU WITHIN 1.1 INCH

1 2

R643 51R2J-2-GP

PLace Any where

1 2

1 2

1 2

Stuff 200 ohm for ES2

Empty for production

(R)

12

12

12

12

(R)

R695

1KR2F-3-GP

XDP_PLTRST_N

PCH_JTAG_TCK

Stuff Always

B B

LPC DEBUG PORT

L_AD018,36,37

L_AD118,36,37

L_AD218,36,37

L_AD318,36,37

L_FRAME_N18,36,37

CK_P_33M_LPCP8019

Joey_SA_0424 Remove

PLTRST_SL_N36,37,49,52

4

H_TDI

H_TMS

H_TCK

H_TRST_N

H_RSTOUT_XDP_N

XDP_VR_READYVR_READY

C394

SCD1U16V2KX-3GP

XDP_PWRGD

1 2

R864 200R2F-L-GP

1 2

R866 200R2F-L-GP

1 2

R865 200R2F-L-GP

Stuff for ES2 and empty after production

V_CPU_VCCIO_RIGHT VCC3

12

R639

51R2F-2-GP

12

(R)

R640

825R2F-GP

PLace Near XDP CONN

CK_100M_CPU_XDP_DN

CK_100M_CPU_XDP_DP

12

R889

100R2F-L1-GP-U

PCH_JTAG_RST_R

SC1U10V2KX-1GP

3

XDPC1

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

(R)

SMC-CONN60A-GP

MH1

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

MH2

XDP_DBRESET_N

12

(R)

R642

249R2F-GP

H_TDO

12

(R)

R641

100R2F-L1-GP-U

R637 0R0402-PAD-2-GP

R636 0R0402-PAD-2-GP

1 2

1 2

V_CPU_VCCIO_RIGHT V_CPU_VCCIO_RIGHT

H_PREQ_N

H_PRDY_N

HSW_PCUDEBUG_0

HSW_PCUDEBUG_1

HSW_PCUDEBUG_2

HSW_PCUDEBUG_3

HSW_XDP_MBP_0

HSW_XDP_MBP_1

HSW_PCUDEBUG_4

HSW_PCUDEBUG_5

HSW_PCUDEBUG_6

HSW_PCUDEBUG_7

XDP_PLTRST_N

XDP_PWR_DEBUG

XDP_VR_READY

SMB_DATA_MAIN

SMB_CLK_MAIN

H_TCK

CK_XDP_S_DN

CK_XDP_S_DP

All parts can be placed at back side

MCP TERMINATION

HSW_PCUDEBUG_0

HSW_PCUDEBUG_1

HSW_PCUDEBUG_2

HSW_PCUDEBUG_3

HSW_PCUDEBUG_4

HSW_PCUDEBUG_5

HSW_PCUDEBUG_6

HSW_PCUDEBUG_7

HSW_PCUDEBUG_8

HSW_PCUDEBUG_9

HSW_PCUDEBUG_10

HSW_PCUDEBUG_11

HSW_PCUDEBUG_12

HSW_PCUDEBUG_14

HSW_PCUDEBUG_15

HSW_PCUSTB_0_DP

HSW_PCUSTB_0_DN

HSW_PCUSTB_1_DP

HSW_PCUSTB_1_DN

12

R891

100R2F-L1-GP-U

PCH_JTAG_TDO

PCH_JTAG_TDI

PCH_JTAG_TMS

(R)

C160

12

PCH_JTAG_TDOPCH_JTAG_PWR

PCH_JTAG_TDI

PCH_JTAG_TMS

12

R890

100R2F-L1-GP-U

1

1

1

12

(R)

R218

10KR2J-3-GP

TP110 TPAD28

TP112 TPAD28

TP111 TPAD28

SB3V

12

R216

20KR2J-L2-GP

12

R217

10KR2J-3-GP

HSW_PCUSTB_0_DP

HSW_PCUSTB_0_DN

HSW_PCUDEBUG_8

HSW_PCUDEBUG_9

HSW_PCUDEBUG_10

HSW_PCUDEBUG_11

HSW_PCUSTB_1_DP

HSW_PCUSTB_1_DN

HSW_PCUDEBUG_12

HSW_PCUDEBUG_13

HSW_PCUDEBUG_14

HSW_PCUDEBUG_15

CK_XDP_S_DPXDP_PWRGD

CK_XDP_S_DN

H_RSTOUT_XDP_N

XDP_DBRESET_N

H_TDO

H_TRST_N

H_TDI

H_TMS

PRIVACY_MSR_EN_N

R646 1KR2J-1-GP

12

C367

SCD1U16V2KX-3GP

1 2

R776 1KR2J-1-GP(R)

1 2

R754 1KR2J-1-GP(R)

1 2

R735 1KR2J-1-GP

1 2

R722 1KR2J-1-GP(R)

1 2

R777 1KR2J-1-GP(R)

1 2

R755 1KR2J-1-GP(R)

1 2

R736 1KR2J-1-GP(R)

1 2

R723 1KR2J-1-GP(R)

1 2

R752 1KR2J-1-GP(R)

1 2

R718 1KR2J-1-GP(R)

1 2

R731 1KR2J-1-GP(R)

1 2

R751 1KR2J-1-GP(R)

1 2

R775 1KR2J-1-GP(R)

1 2

R734 1KR2J-1-GP(R)

1 2

R721 1KR2J-1-GP(R)

1 2

R720 1KR2J-1-GP

1 2

R719 1KR2J-1-GP(R)

1 2

R732 1KR2J-1-GP(R)

1 2

R753 1KR2J-1-GP(R)

1 2

R733 1KR2J-1-GP(R)

1 2

HSW_PCUDEBUG_3

HSW_STRAP_13HSW_PCUDEBUG_13

2

LPC DEBUG PORT

CK_P_33M_LPCP80

PLTRST_SL_N

L_AD0

L_AD1

L_AD2

L_AD3

L_FRAME_N

Joey_1A_1210

(R)

LPC1

1

3

5

7

9

11

13

FOX-CONN14A-S1-GP

INIT_3V

2

4

FWH_ID0

6

8

10

12

NP1

14

Pin height 2.3m m

Follow Eagle

APS CONNECTOR

PCH_SLP_M_N

1

TP117 TPAD28

VCC3

12

R508

4K7R2J-2-GP

VCC3

VCC

(R)

R509

10KR2J-3-GP

1 2

1

CLOSE TO CPU

Joey_SA_0417

A A

<Variant Name>

<Variant Name>

<Variant Name>

All parts can be placed at back side

5

4

3

2

Title

Title

Title

XDP/80 PORT HEADER

XDP/80 PORT HEADER

XDP/80 PORT HEADER

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_Tigris AIO

Custom

Rosa_Tigris AIO

Custom

Rosa_Tigris AIO

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

14 57Monday, January 06, 2014

14 57Monday, January 06, 2014

14 57Monday, January 06, 2014

SB

SB

SB

5

RepairLap.com

DDR DATA

DDR CMD/ADD

D D

DDR CTRL

M_DATA_A[0 ..63]12

M_DQS_A_ DP[0..7]12

M_DQS_A_ DN[0..7]12

M_MAA_A[0..15]12

M_WE_A _N12

M_CAS_A_ N12

M_RAS_A_ N12

M_SBS_A012

M_SBS_A112

M_SBS_A212

M_SCS_A_ N012

M_SCS_A_ N112

M_SCKE_A 012

M_SCKE_A 112

M_ODT_A012

M_ODT_A112

DDR CLOCK

CK_M_DDR0_ A_DP12

CK_M_DDR0_ A_DN12

CK_M_DDR1_ A_DP12

CK_M_DDR1_ A_DN12

DDR OTHERS

DDR3_DRAMRS T_N12,16

SMB_DATA_MAIN14,16,26 ,37,50

SMB_CLK_ MAIN14,16,26 ,37,50

SMB_CLK_ RESUME18,33,37

C C

B B

A A

SMB_DATA_RESUME18,33,37

DIMM_DQ_CP U_VREF_A12

DIMM_CA_VREF_A10

DDR3_DRAMRS T_N

5

R808

1 2

0R0402-PAD-2-GP

DDR3_DRAMRS T_N_A_1

V_SM_VTT

12

(R)

C422

SCD1U10V2KX-5GP

4

M_MAA_A0

M_MAA_A1

M_MAA_A2

M_MAA_A3

M_MAA_A4

M_MAA_A5

M_MAA_A6

M_MAA_A7

M_MAA_A8

M_MAA_A9

M_MAA_A1 0

M_MAA_A1 1

M_MAA_A1 2

M_MAA_A1 3

M_MAA_A1 4

M_MAA_A1 5

M_SBS_A2

M_SBS_A0

M_SBS_A1

M_DQS_A_ DN0

M_DQS_A_ DN1

M_DQS_A_ DN2

M_DQS_A_ DN3

M_DQS_A_ DN4

M_DQS_A_ DN5

M_DQS_A_ DN6

M_DQS_A_ DN7

M_DQS_A_ DP0

M_DQS_A_ DP1

M_DQS_A_ DP2

M_DQS_A_ DP3

M_DQS_A_ DP4

M_DQS_A_ DP5

M_DQS_A_ DP6

M_DQS_A_ DP7

M_ODT_A0

M_ODT_A1

DIMM_CA_VREF_A

DIMM_DQ_VR EF_A

4

M_DATA_A0

M_DATA_A1

M_DATA_A2

M_DATA_A3

M_DATA_A4

M_DATA_A5

M_DATA_A6

M_DATA_A7

M_DATA_A8

M_DATA_A9

M_DATA_A10

M_DATA_A11

M_DATA_A12

M_DATA_A13

M_DATA_A14

M_DATA_A15

M_DATA_A16

M_DATA_A17

M_DATA_A18

M_DATA_A19

M_DATA_A20

M_DATA_A21

M_DATA_A22

M_DATA_A23

M_DATA_A24

M_DATA_A25

M_DATA_A26

M_DATA_A27

M_DATA_A28

M_DATA_A29

M_DATA_A30

M_DATA_A31

M_DATA_A32

M_DATA_A33

M_DATA_A34

M_DATA_A35

M_DATA_A36

M_DATA_A37

M_DATA_A38

M_DATA_A39

M_DATA_A40

M_DATA_A41

M_DATA_A42

M_DATA_A43