Dell 7557 Schematics

1

www.schematic-x.blogspot.com

2

3

4

5

6

7

8

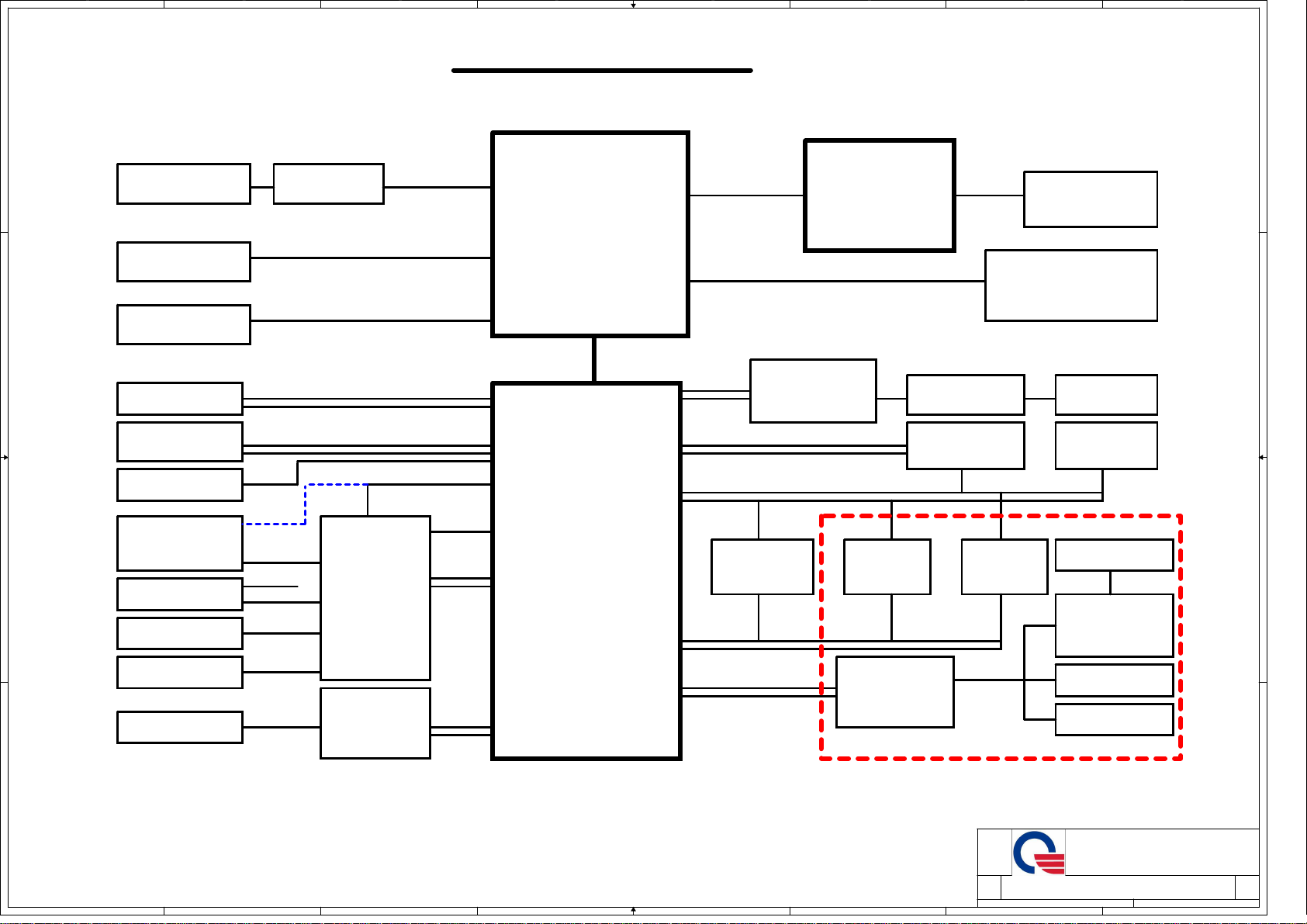

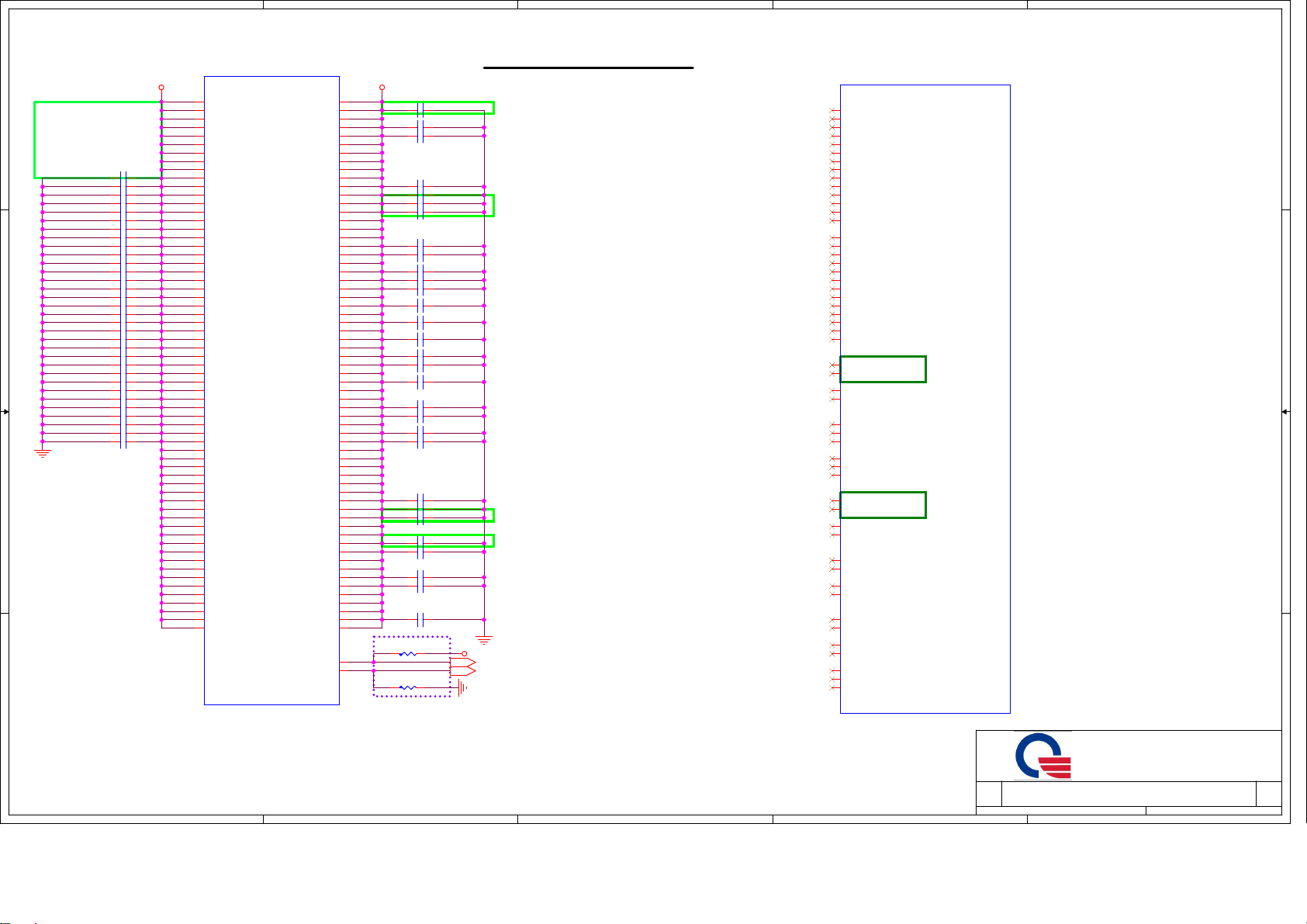

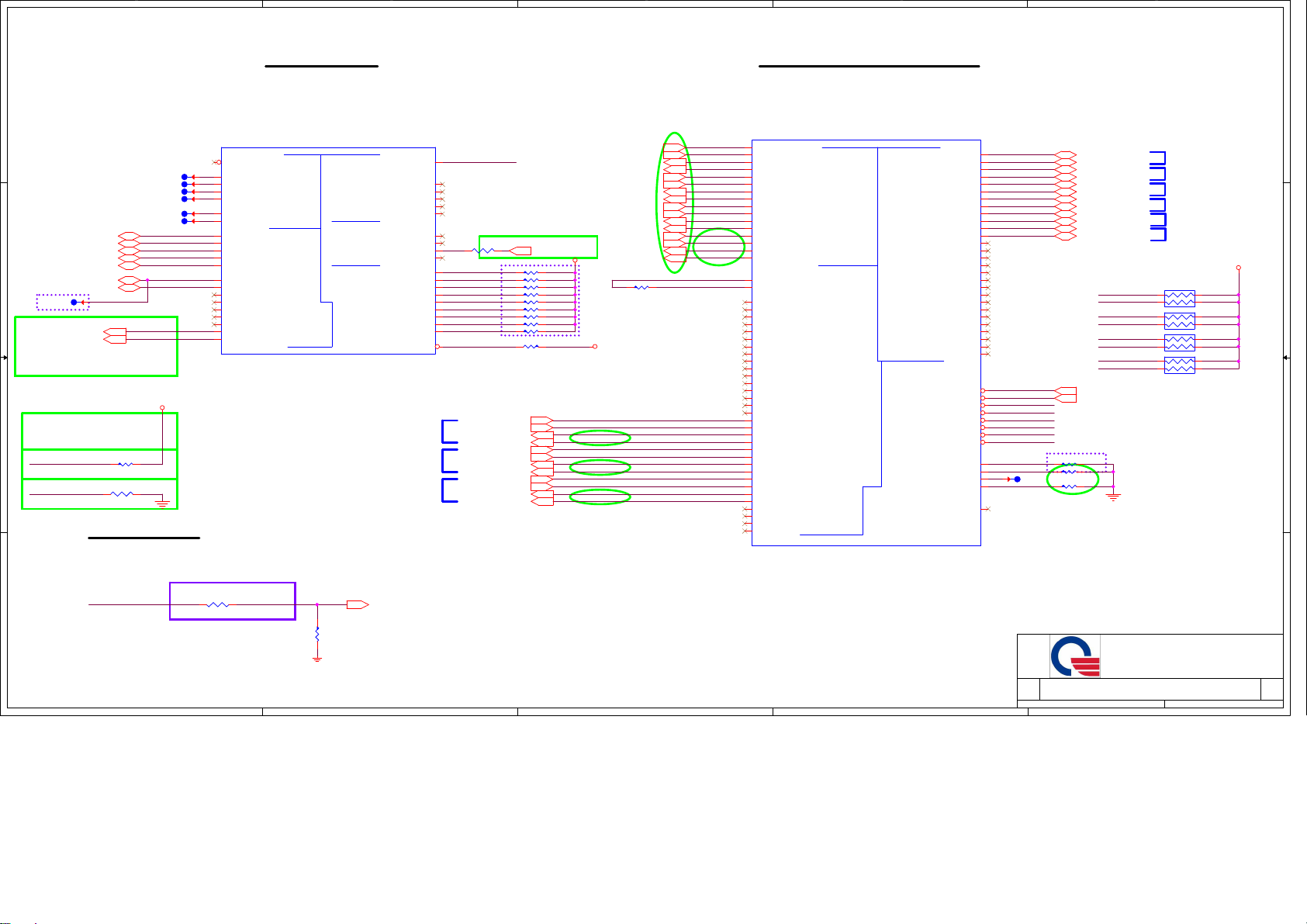

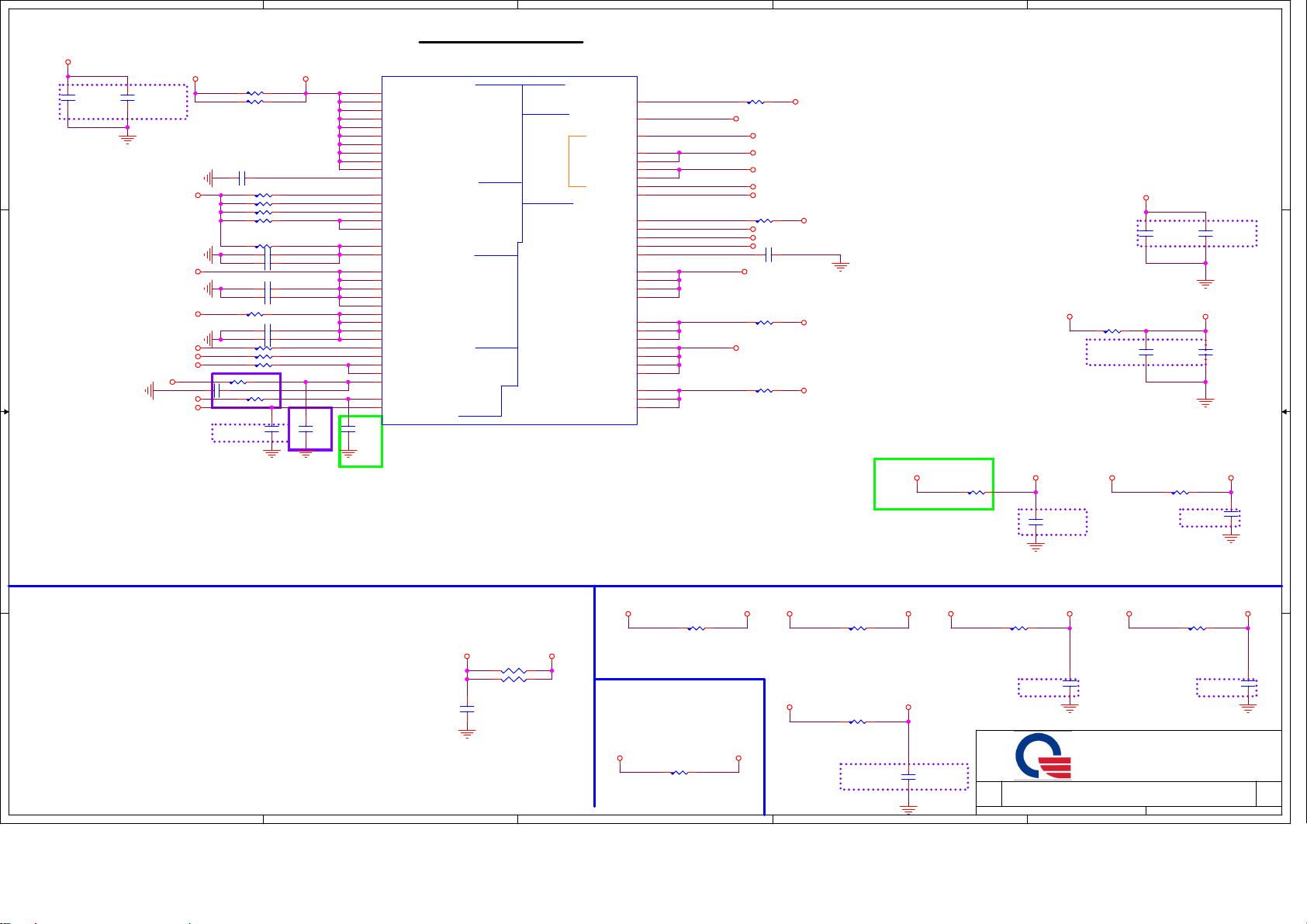

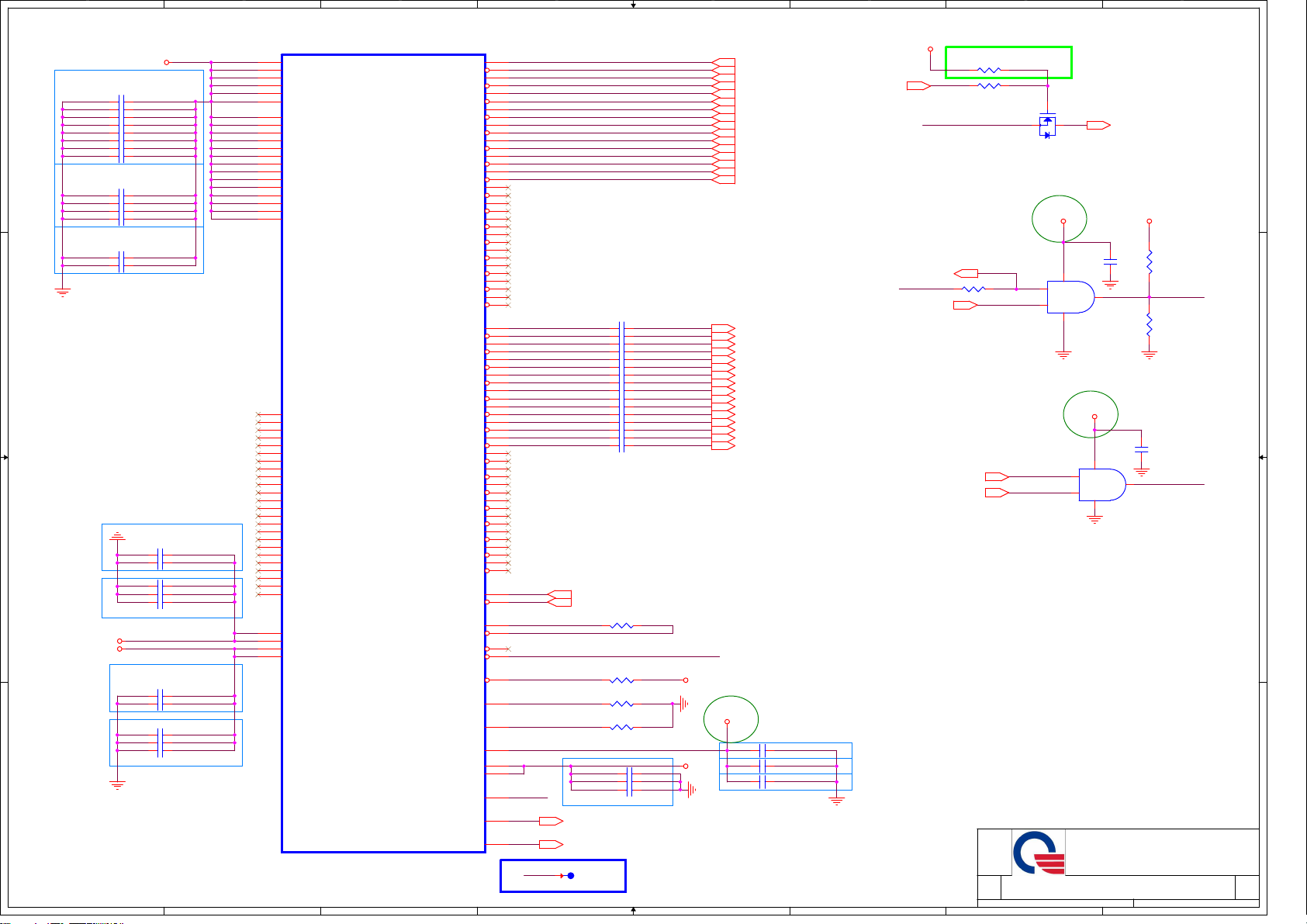

Block Diagram

01

A A

HDMI Conn.

PAGE 30

Re-Driver

PS8407A

PAGE 30

INT HDMI

CPU

PEG x 8

Skylake-H

Channel A

DDR3 SO-DIMM

PAGE 15

DDR3L 1600MT/s 1.35V

Channel B

DDR3 SO-DIMM

B B

M.2(NGFF) SSD

Flash ROM

4 MB for ME

Flash ROM

8 MB for BIOS+EC

16 MB (Reserve)

C C

Touch Pad

K/B

PAGE 16

PAGE 28

PAGE 28

PAGE 27

PAGE 27

PAGE 31

PAGE 31

PCIE Gen III x4 / SATA III 2,3

SPI

SPI

I2C

PS2

DDR3L 1600MT/s 1.35V

SATA3 6GB /S

EC

ITE

IT8528E

Package : LQPF128

I2C

LPC

Processor : Quad Core

Power : 45W (35W w/dGPU)

Package : BGA1440

Size : 42x28 (mm)

SYSTEM MEMORY

PAGE 2~8

5GT/s

DMI X 4

Mobile Intel

Sunrise point - H

Platform Controller Hub

Power : 2.8 Watt

Package : FCBGA837

eDP 4 Lanes

Giga LAN

PCIE

PCIE Port 5

RTL8111GUHDD

PCIE

USB2.0

Port 1

USB 3.0

Power Share

USB3.0

PAGE 34

Port 1

Size : 23 x 23 (mm)

FAN

PAGE 33

Card Reader

SD slot Realtek

PAGE 35

9 x 9mm

PAGE 26

RTS5227S

PAGE 35

PCIE

PCIe Port7

HDA

PAGE 9~14

GPU

Nvidia

N16P-GX

29 x 29 mm

Package : BGA908

PAGE 37

PCIE Port 6

Port 2 Port 3

Audio Codec

Realtek

ALC3246

IO Board

IO Board

IO BoardIO Board

50W

PAGE 17~21

TRANSFORMER RJ45

Port 5

Port 2 Port 3

GDDR5 x 8

(256 Mb x 16)

15.6" eDP Panel

UHD 3840 x 2160

PAGE 37 PAGE 37

NGFF

WLAN + BT

USB 3.0USB 3.0

Type AType A

PAGE 22~25

PAGE 29

Camera

PAGE 29PAGE 36

Port 4

Sub Woofer

AMP

ANPEC

ALC1003-CGT

Universal Jack

SPEAKER

D D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

1

2

PROJECT :

PROJECT :

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

Date: Sheet of

Monday, May 25, 2 015

Date: Sheet of

Monday, May 25, 2 015

Date: Sheet of

3

4

5

6

Monday, May 25, 2 015

7

PROJECT :

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

AM9A

AM9A

AM9A

1 57

1 57

1 57

8

A0

A0

A0

5

4

3

2

1

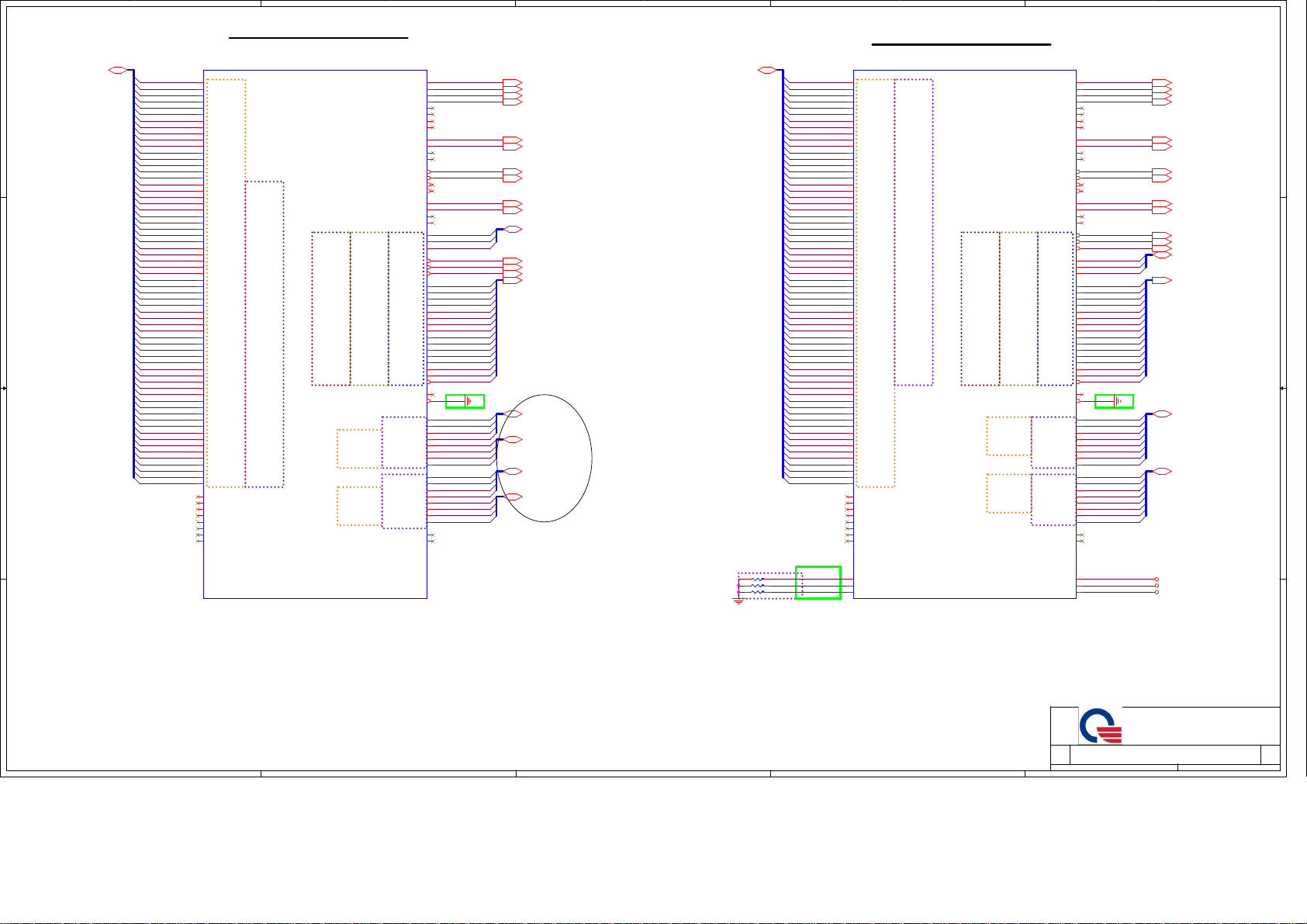

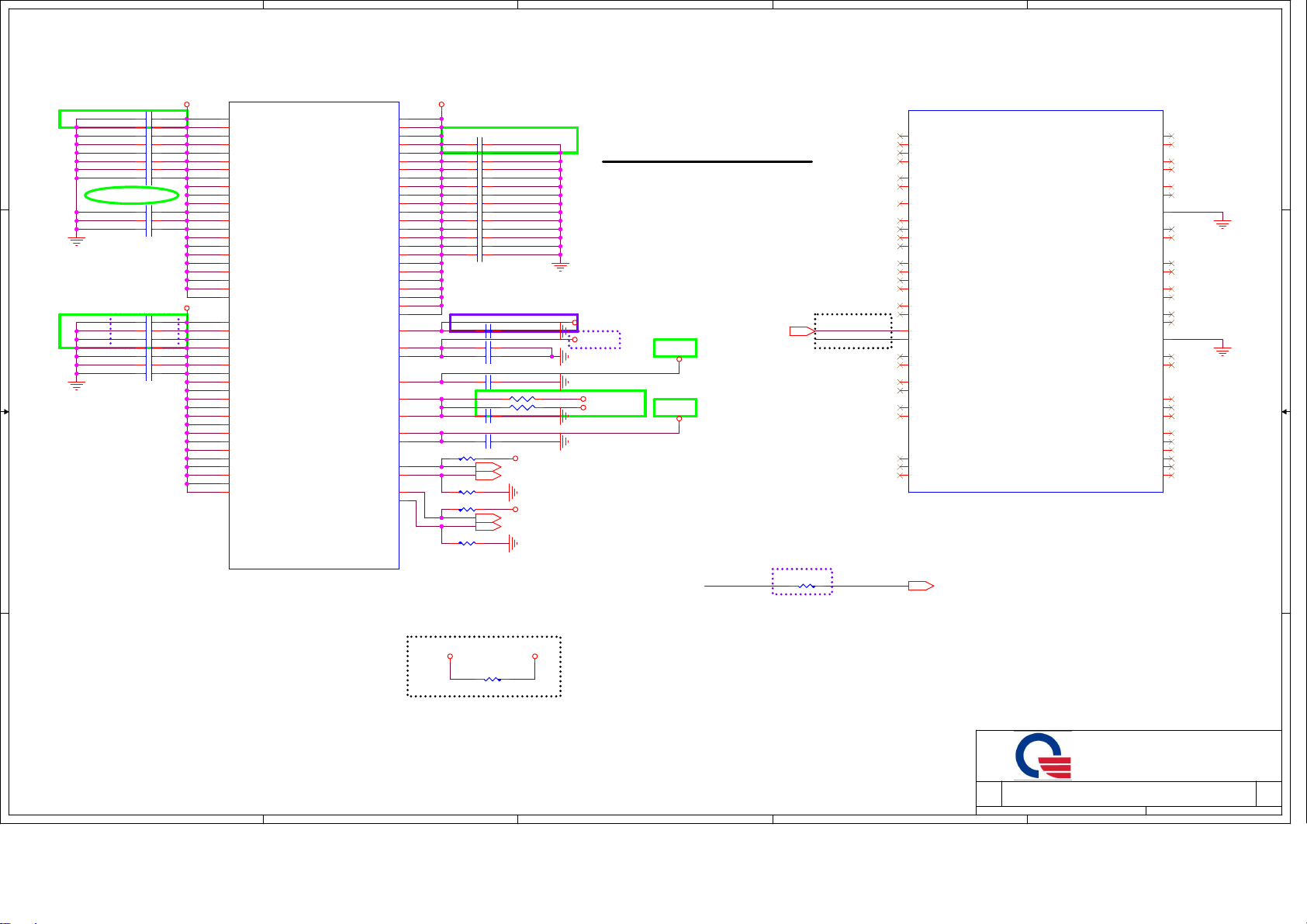

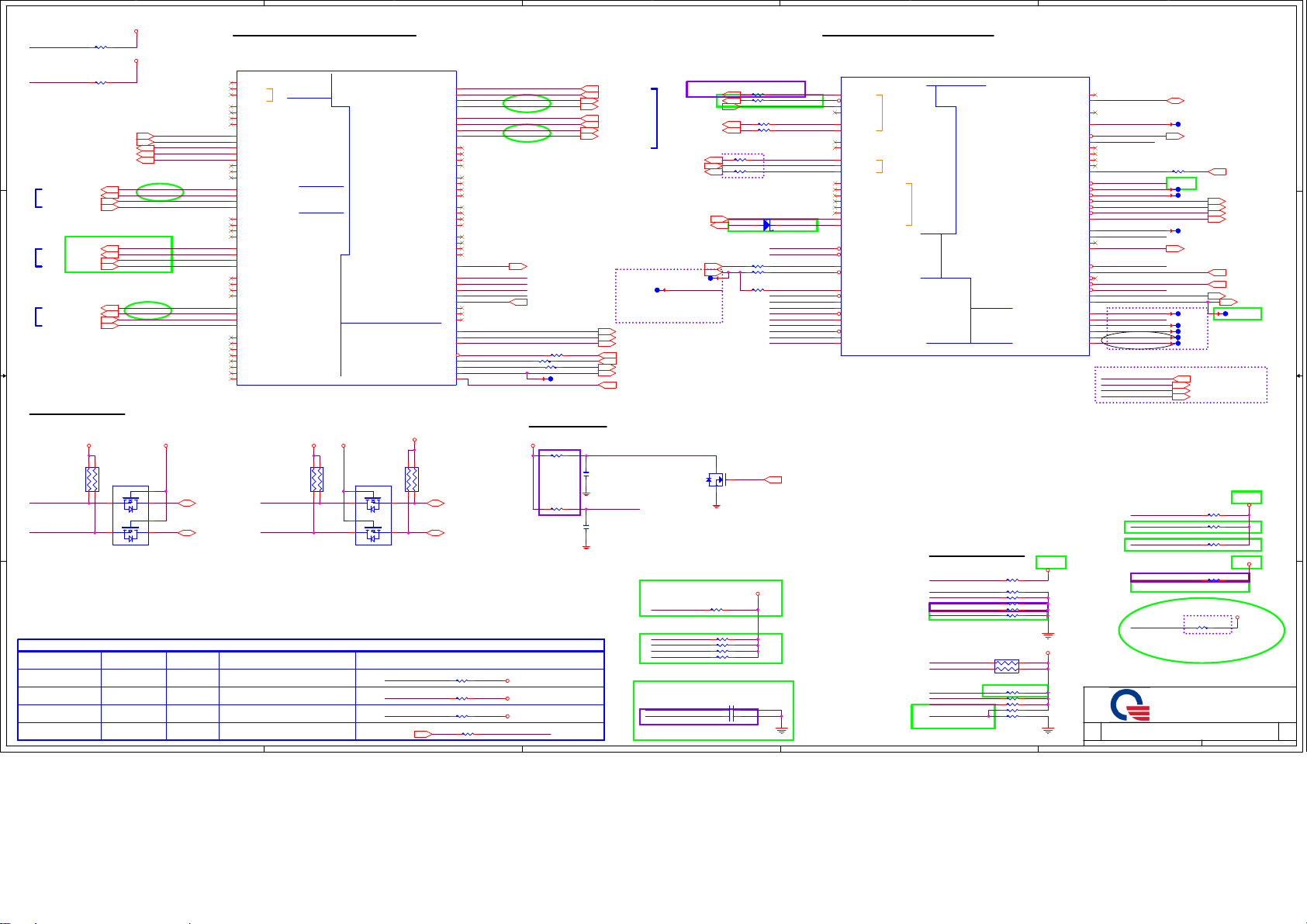

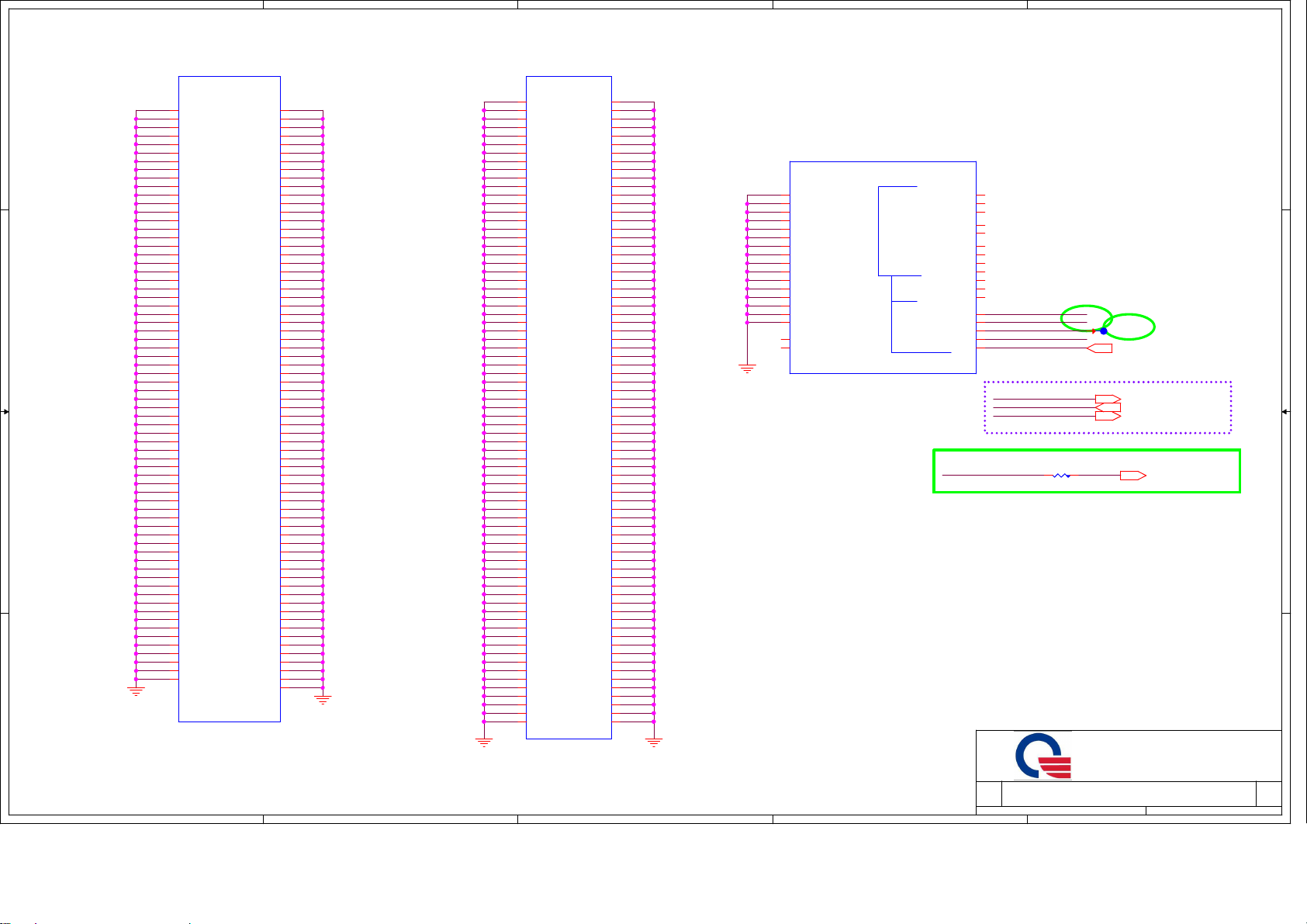

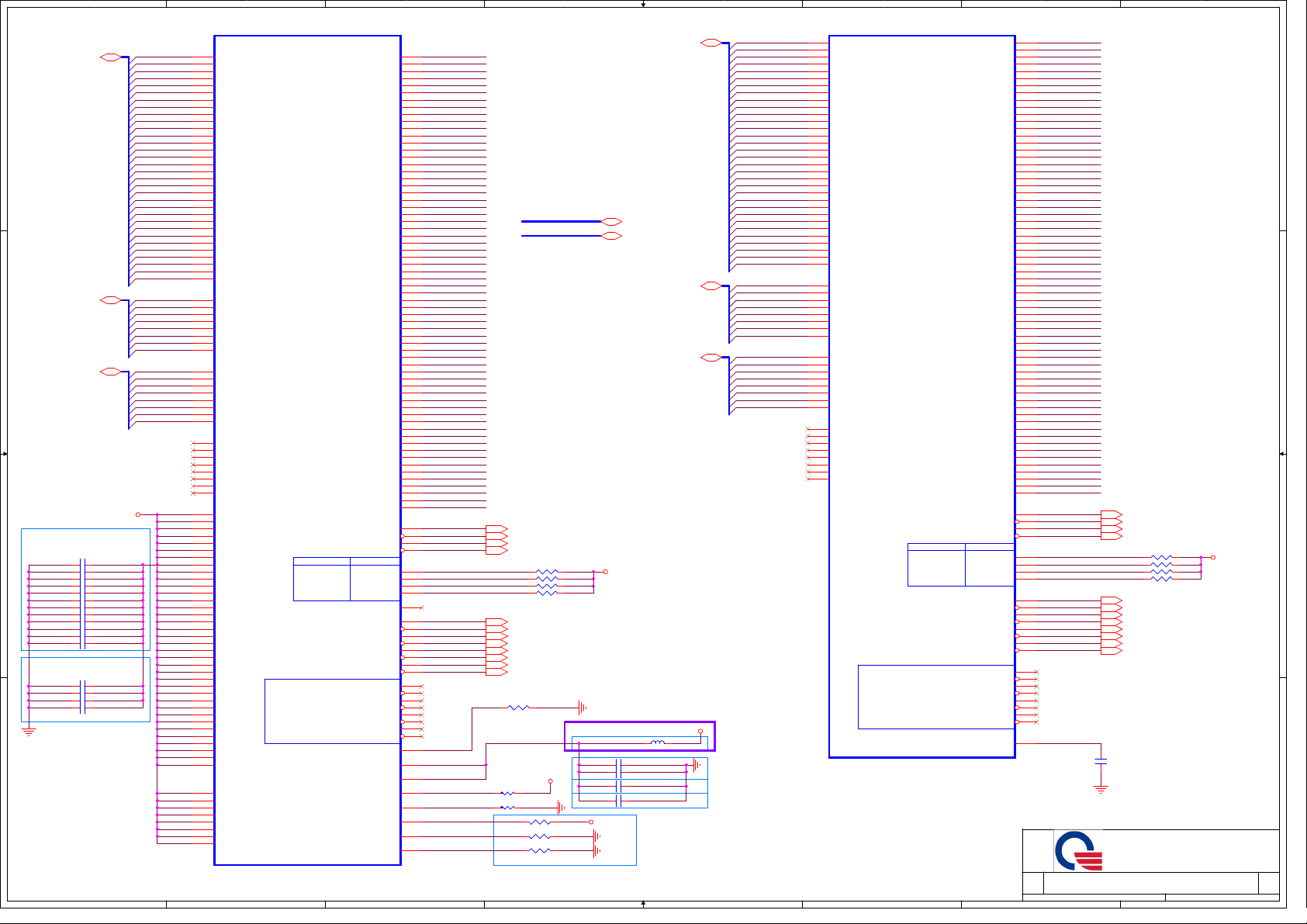

Skylake Processor (DDR3-CH-A)

SKL with DDR3L is IL memory design.

M_A_DQ[63:0]15 M_B_DQ[63:0 ]16

D D

C C

B B

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

For ECC

U10A

Interleve

BR6

DDR0_DQ[0]

BT6

DDR0_DQ[1]

BP3

DDR0_DQ[2]

BR3

DDR0_DQ[3]

BN5

DDR0_DQ[4]

BP6

DDR0_DQ[5]

BP2

DDR0_DQ[6]

BN3

DDR0_DQ[7]

BL4

DDR0_DQ[8]

BL5

DDR0_DQ[9]

BL2

DDR0_DQ[10]

BM1

DDR0_DQ[11]

BK4

DDR0_DQ[12]

BK5

DDR0_DQ[13]

BK1

DDR0_DQ[14]

BK2

DDR0_DQ[15]

BG4

DDR0_DQ[16]/DDR0_DQ[32]

BG5

DDR0_DQ[17]/DDR0_DQ[33]

BF4

DDR0_DQ[18]/DDR0_DQ[34]

BF5

DDR0_DQ[19]/DDR0_DQ[35]

BG2

DDR0_DQ[20]/DDR0_DQ[36]

BG1

DDR0_DQ[21]/DDR0_DQ[37]

BF1

DDR0_DQ[22]/DDR0_DQ[38]

BF2

DDR0_DQ[23]/DDR0_DQ[39]

BD2

DDR0_DQ[24]/DDR0_DQ[40]

BD1

DDR0_DQ[25]/DDR0_DQ[41]

BC4

DDR0_DQ[26]/DDR0_DQ[42]

BC5

DDR0_DQ[27]/DDR0_DQ[43]

BD5

DDR0_DQ[28]/DDR0_DQ[44]

BD4

DDR0_DQ[29]/DDR0_DQ[45]

BC1

DDR0_DQ[30]/DDR0_DQ[46]

BC2

DDR0_DQ[31]/DDR0_DQ[47]

AB1

DDR0_DQ[32]/DDR1_DQ[0]

AB2

DDR0_DQ[33]/DDR1_DQ[1]

AA4

DDR0_DQ[34]/DDR1_DQ[2]

AA5

DDR0_DQ[35]/DDR1_DQ[3]

AB5

DDR0_DQ[36]/DDR1_DQ[4]

AB4

DDR0_DQ[37]/DDR1_DQ[5]

AA2

DDR0_DQ[38]/DDR1_DQ[6]

AA1

DDR0_DQ[39]/DDR1_DQ[7]

V5

DDR0_DQ[40]/DDR1_DQ[8]

V2

DDR0_DQ[41]/DDR1_DQ[9]

U1

DDR0_DQ[42]/DDR1_DQ[10]

U2

DDR0_DQ[43]/DDR1_DQ[11]

V1

DDR0_DQ[44]/DDR1_DQ[12]

V4

DDR0_DQ[45]/DDR1_DQ[13]

U5

DDR0_DQ[46]/DDR1_DQ[14]

U4

DDR0_DQ[47]/DDR1_DQ[15]

R2

DDR0_DQ[48]/DDR1_DQ[32]

P5

DDR0_DQ[49]/DDR1_DQ[33]

R4

DDR0_DQ[50]/DDR1_DQ[34]

P4

DDR0_DQ[51]/DDR1_DQ[35]

R5

DDR0_DQ[52]/DDR1_DQ[36]

P2

DDR0_DQ[53]/DDR1_DQ[37]

R1

DDR0_DQ[54]/DDR1_DQ[38]

P1

DDR0_DQ[55]/DDR1_DQ[39]

M4

DDR0_DQ[56]/DDR1_DQ[40]

M1

DDR0_DQ[57]/DDR1_DQ[41]

L4

DDR0_DQ[58]/DDR1_DQ[42]

L2

DDR0_DQ[59]/DDR1_DQ[43]

M5

DDR0_DQ[60]/DDR1_DQ[44]

M2

DDR0_DQ[61]/DDR1_DQ[45]

L5

DDR0_DQ[62]/DDR1_DQ[46]

L1

DDR0_DQ[63]/DDR1_DQ[47]

BA2

DDR0_ECC[0]

BA1

DDR0_ECC[1]

AY4

DDR0_ECC[2]

AY5

DDR0_ECC[3]

BA5

DDR0_ECC[4]

BA4

DDR0_ECC[5]

AY1

DDR0_ECC[6]

AY2

DDR0_ECC[7]

DDR CHANNEL A

SKL_H_BGA_B GA/BGA

SKYLAKE_HALO

Non-Interleve

BGA1440

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

Interleve

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSP[7]/DDR1_DQSP[5]

Interleve

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

1 OF 14

DDR0_CKP[0]

DDR0_CKN[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CLKP[2]

DDR0_CLKN[2]

DDR0_CLKP[3]

DDR0_CLKN[3]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_CS#[2]

DDR0_CS#[3]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_ODT[2]

DDR0_ODT[3]

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

DDR0_ALERT#

Non-Interleve

DDR0_DQSN[0]

DDR0_DQSN[1]

Non-Interleve

DDR0_DQSP[0]

DDR0_DQSP[1]

DDR0_DQSP[8]

DDR0_DQSN[8]

REV = 1

AG1

AG2

AK1

AK2

AL3

AK3

AL2

AL1

AT1

AT2

AT3

AT5

AD5

AE2

AD2

AE5

AD3

AE4

AE1

AD4

AH5

AH1

AU1

AH4

AG4

AD1

AH3

AP4

AN4

AP5

AP2

AP1

AP3

AN1

AN3

AT4

AH2

AN2

AU4

AE3

AU2

AU3

AG3

AU5

BR5

BL3

BG3

BD3

AB3

V3

R3

M3

BP5

BK3

BF3

BC3

AA3

U3

P3

L3

AY3

BA3

M_A_CLKP0

M_A_CLKN0

M_A_CLKN1

M_A_CLKP1

M_A_CKE0

M_A_CKE1

M_A_CS#0

M_A_CS#1

M_A_ODT0

M_A_ODT1

M_A_BS#0

M_A_BS#1

M_A_BS#2

M_A_RAS#

M_A_WE#

M_A_CAS#

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_CLKP0 15

M_A_CLKN0 15

M_A_CLKN1 15

M_A_CLKP1 15

M_A_CKE0 15

M_A_CKE1 15

M_A_CS#0 15

M_A_CS#1 15

M_A_ODT0 15

M_A_ODT1 15

M_A_BS#[2:0] 1 5

M_A_RAS# 15

M_A_WE# 15

M_A_CAS# 15

M_A_A[15:0] 1 5

3/11 add GND 3/11 add GND

M_A_DQSN0

M_A_DQSN1

M_A_DQSN2

M_A_DQSN3

M_A_DQSP4

M_A_DQSP5

M_A_DQSP6

M_A_DQSP7

M_A_DQSP0

M_A_DQSP1

M_A_DQSP2

M_A_DQSP3

M_A_DQSN4

M_A_DQSN5

M_A_DQSN6

M_A_DQSN7

M_A_DQSN[3:0 ] 15

M_A_DQSP[7:4] 15

M_A_DQSP[3:0] 15

M_A_DQSN[7:4 ] 15

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

For ECC

For ECC

Place close to CPU

R301 121/F_4

R299 75/F_4

R298 100/F_4

Follow SKL -H WP(V0.9 1)

support DD R3L SO-DIM M

#549401 pa ge 26

DDR_RCO MP_0

DDR_RCO MP_1

DDR_RCO MP_2 +VREFDQ_SB

2/10 add net name

Skylake Processor (DDR3-CH-B)

SKL with DDR3L is IL memory design.

U10B

Interleve Non-Interleve

BT11

DDR1_DQ[0]/DDR0_DQ[16]

BR11

DDR1_DQ[1]/DDR0_DQ[17]

BT8

DDR1_DQ[2]/DDR0_DQ[18]

BR8

DDR1_DQ[3]/DDR0_DQ[19]

BP11

DDR1_DQ[4]/DDR0_DQ[20]

BN11

DDR1_DQ[5]/DDR0_DQ[21]

BP8

DDR1_DQ[6]/DDR0_DQ[22]

BN8

DDR1_DQ[7]/DDR0_DQ[23]

BL12

DDR1_DQ[8]/DDR0_DQ[24]

BL11

DDR1_DQ[9]/DDR0_DQ[25]

BL8

DDR1_DQ[10]/DDR0_DQ[26]

BJ8

DDR1_DQ[11]/DDR0_DQ[27]

BJ11

DDR1_DQ[12]/DDR0_DQ[28]

BJ10

DDR1_DQ[13]/DDR0_DQ[29]

BL7

DDR1_DQ[14]/DDR0_DQ[30]

BJ7

DDR1_DQ[15]/DDR0_DQ[31]

BG11

DDR1_DQ[16]/DDR0_DQ[48]

BG10

DDR1_DQ[17]/DDR0_DQ[49]

BG8

DDR1_DQ[18]/DDR0_DQ[50]

BF8

DDR1_DQ[19]/DDR0_DQ[51]

BF11

DDR1_DQ[20]/DDR0_DQ[52]

BF10

DDR1_DQ[21]/DDR0_DQ[53]

BG7

DDR1_DQ[22]/DDR0_DQ[54]

BF7

DDR1_DQ[23]/DDR0_DQ[55]

BB11

DDR1_DQ[24]/DDR0_DQ[56]

BC11

DDR1_DQ[25]/DDR0_DQ[57]

BB8

DDR1_DQ[26]/DDR0_DQ[58]

BC8

DDR1_DQ[27]/DDR0_DQ[59]

BC10

DDR1_DQ[28]/DDR0_DQ[60]

BB10

DDR1_DQ[29]/DDR0_DQ[61]

BC7

DDR1_DQ[30]/DDR0_DQ[62]

BB7

DDR1_DQ[31]/DDR0_DQ[63]

AA11

DDR1_DQ[32]/DDR1_DQ[16]

AA10

DDR1_DQ[33]/DDR1_DQ[17]

AC11

DDR1_DQ[34]/DDR1_DQ[18]

AC10

DDR1_DQ[35]/DDR1_DQ[19]

AA7

DDR1_DQ[36]/DDR1_DQ[20]

AA8

DDR1_DQ[37]/DDR1_DQ[21]

AC8

DDR1_DQ[38]/DDR1_DQ[22]

AC7

DDR1_DQ[39]/DDR1_DQ[23]

W8

DDR1_DQ[40]/DDR1_DQ[24]

W7

DDR1_DQ[41]/DDR1_DQ[25]

V10

DDR1_DQ[42]/DDR1_DQ[26]

V11

DDR1_DQ[43]/DDR1_DQ[27]

W11

DDR1_DQ[44]/DDR1_DQ[28]

W10

DDR1_DQ[45]/DDR1_DQ[29]

V7

DDR1_DQ[46]/DDR1_DQ[30]

V8

DDR1_DQ[47]/DDR1_DQ[31]

R11

DDR1_DQ[48]

P11

DDR1_DQ[49]

P7

DDR1_DQ[50]

R8

DDR1_DQ[51]

R10

DDR1_DQ[52]

P10

DDR1_DQ[53]

R7

DDR1_DQ[54]

P8

DDR1_DQ[55]

L11

DDR1_DQ[56]

M11

DDR1_DQ[57]

L7

DDR1_DQ[58]

M8

DDR1_DQ[59]

L10

DDR1_DQ[60]

M10

DDR1_DQ[61]

M7

DDR1_DQ[62]

L8

DDR1_DQ[63]

AW11

DDR1_ECC[0]

AY11

DDR1_ECC[1]

AY8

DDR1_ECC[2]

AW8

DDR1_ECC[3]

AY10

DDR1_ECC[4]

AW10

DDR1_ECC[5]

AY7

DDR1_ECC[6]

AW7

DDR1_ECC[7]

G1

DDR_RCOMP[0]

H1

DDR_RCOMP[1]

J2

DDR_RCOMP[2]

SKL_H_BGA_B GA/BGA

DDR CHANNEL B

SKYLAKE_HALO

BGA1440

DDR3L LPDDR3 DDR4DDR3L LPDDR3 DDR4

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

Interleve Non-Interleve

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

Interleve Non-Interleve

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSP[5]/DDR1_DQSP[3]

2 OF 14

M_B_CLKP0

AM9

DDR1_CKP[0]

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[1]

DDR1_CLKP[2]

DDR1_CLKN[2]

DDR1_CLKP[3]

DDR1_CLKN[3]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_CS#[2]

DDR1_CS#[3]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_ODT[2]

DDR1_ODT[3]

DDR1_MA[3]

DDR1_MA[4]

DDR1_PAR

DDR1_ALERT#

DDR1_DQSN[6]

DDR1_DQSN[7]

DDR1_DQSP[6]

DDR1_DQSP[7]

DDR1_DQSP[8]

DDR1_DQSN[8]

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

REV = 1

Follow SKL -H WP(V0.9 1) support DDR3L SO- DIMM

#549401 pa ge 41

AN9

AM8

AM7

AM11

AM10

AJ10

AJ11

AT8

AT10

AT7

AT11

AF11

AE7

AF10

AE10

AF7

AE8

AE9

AE11

AH10

AH11

AF8

AH8

AH9

AR9

AJ9

AK6

AK5

AL5

AL6

AM6

AN7

AN10

AN8

AR11

AH7

AN11

AR10

AF9

AR7

AT9

AJ7

AR8

BP9

BL9

BG9

BC9

AC9

W9

R9

M9

BR9

BJ9

BF9

BB9

AA9

V9

P9

L9

AW9

AY9

BN13

BP13

BR13

M_B_CLKN 0

M_B_CLKN 1

M_B_CLKP1

M_B_CKE0

M_B_CKE1

M_B_CS#0

M_B_CS#1

M_B_ODT0

M_B_ODT1

M_B_RAS#

M_B_WE #

M_B_CAS#

M_B_BS#0

M_B_BS#1

M_B_BS#2

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DQSN0

M_B_DQSN1

M_B_DQSN2

M_B_DQSN3

M_B_DQSN4

M_B_DQSN5

M_B_DQSN6

M_B_DQSN7

M_B_DQSP0

M_B_DQSP1

M_B_DQSP2

M_B_DQSP3

M_B_DQSP4

M_B_DQSP5

M_B_DQSP6

M_B_DQSP7

For ECC

+DDR_VREF _CA

+VREFDQ_SA

M_B_CLKP0 16

M_B_CLKN 0 16

M_B_CLKN 1 16

M_B_CLKP1 16

M_B_CKE0 16

M_B_CKE1 16

M_B_CS#0 1 6

M_B_CS#1 1 6

M_B_ODT0 16

M_B_ODT1 16

M_B_RAS# 16

M_B_WE # 16

M_B_CAS# 16

M_B_BS#[2:0 ] 16

M_B_A[15:0] 16

M_B_DQSN[7 :0] 16

M_B_DQSP[7 :0] 16

+DDR_VREF _CA

+VREFDQ_SA

+VREFDQ_SB

02

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Docu ment Number Rev

Size Docu ment Number Rev

Size Docu ment Number Rev

Date: Sheet

Monday, May 25, 20 15

Date: Sheet of

Monday, May 25, 20 15

Date: Sheet of

5

4

3

2

Monday, May 25, 20 15

PROJECT :

CPU

CPU

CPU

AM9A

AM9A

AM9A

2 57

2 57

1

2 57

A0

A0

A0

of

5

4

3

2

1

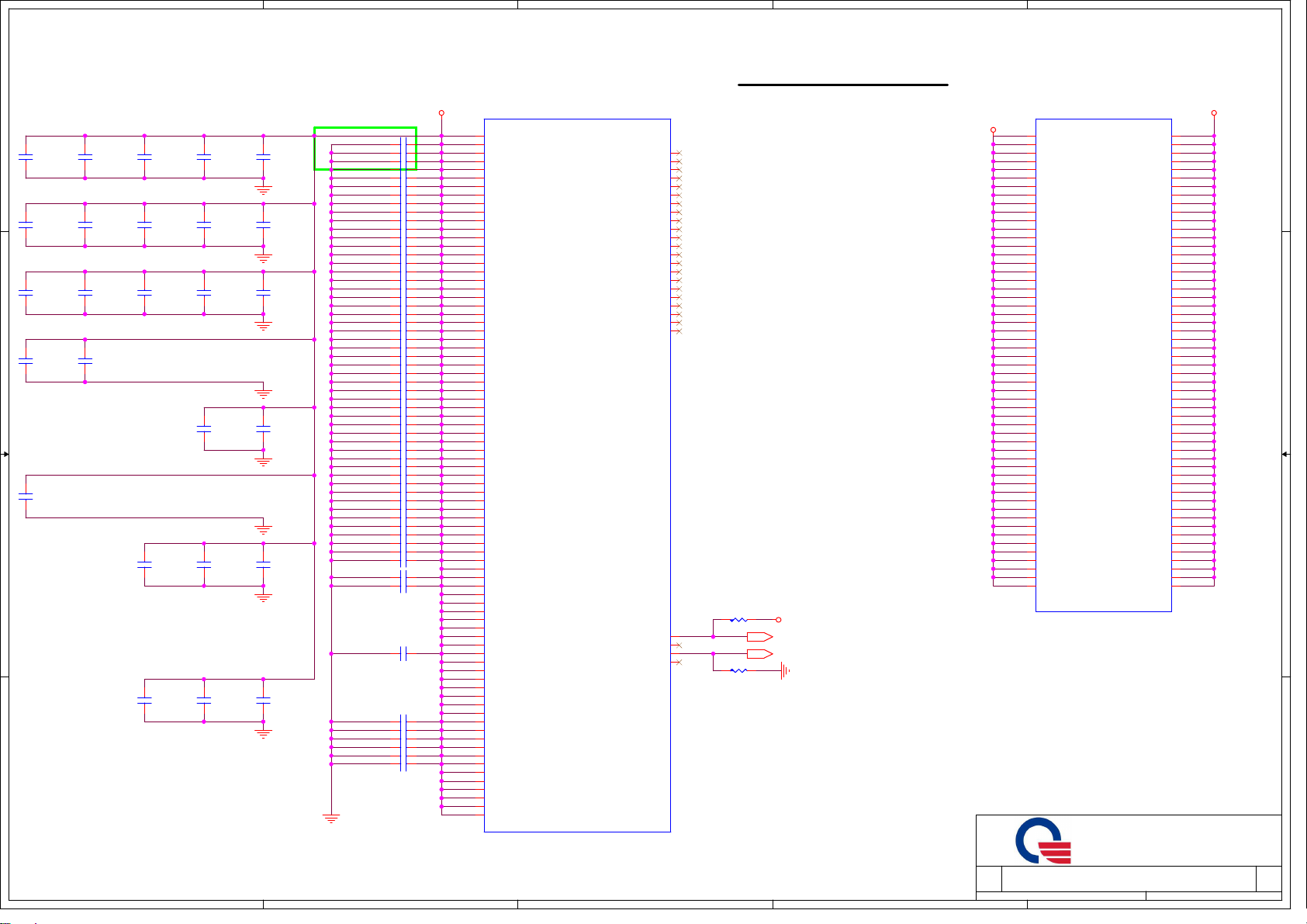

03

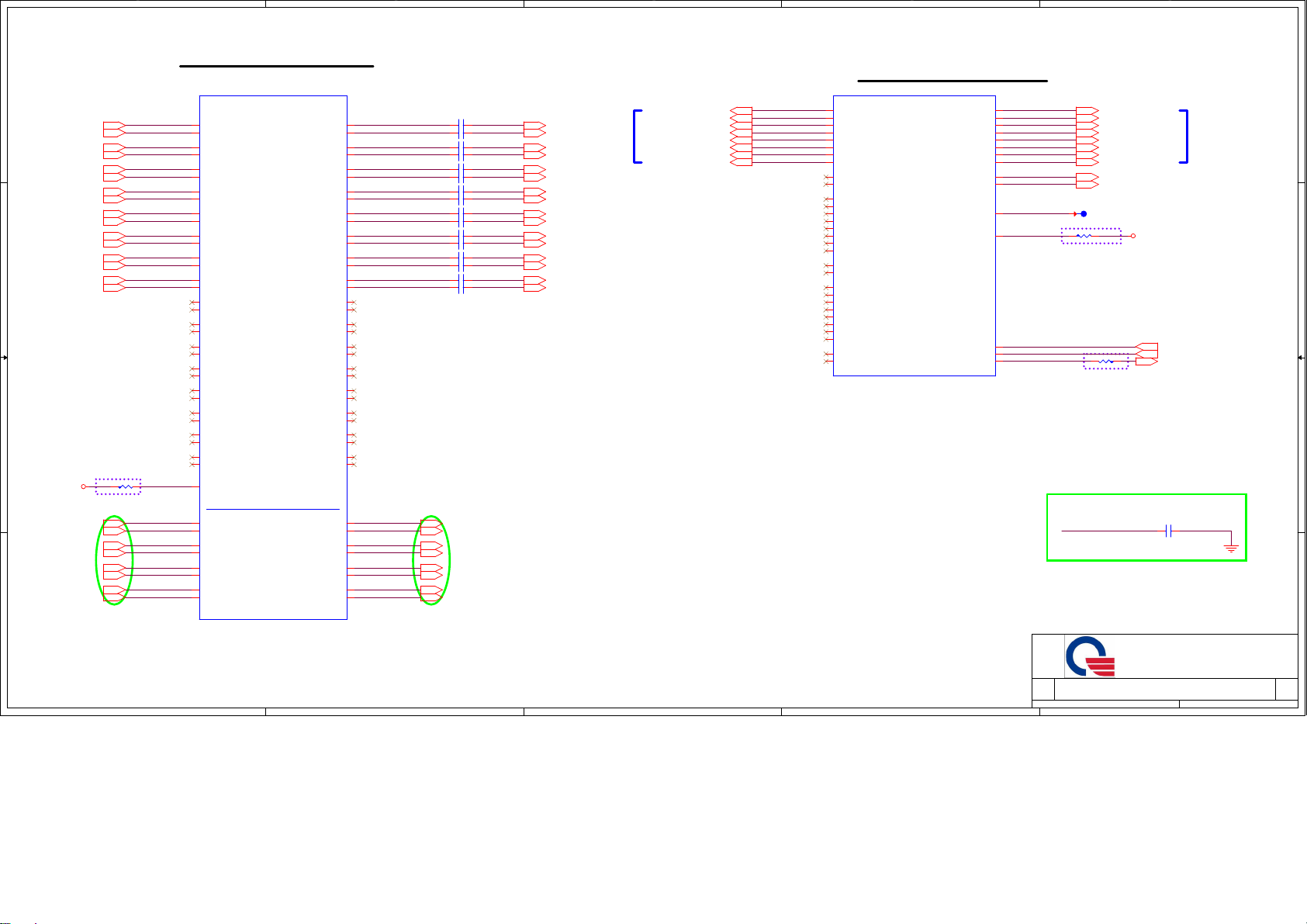

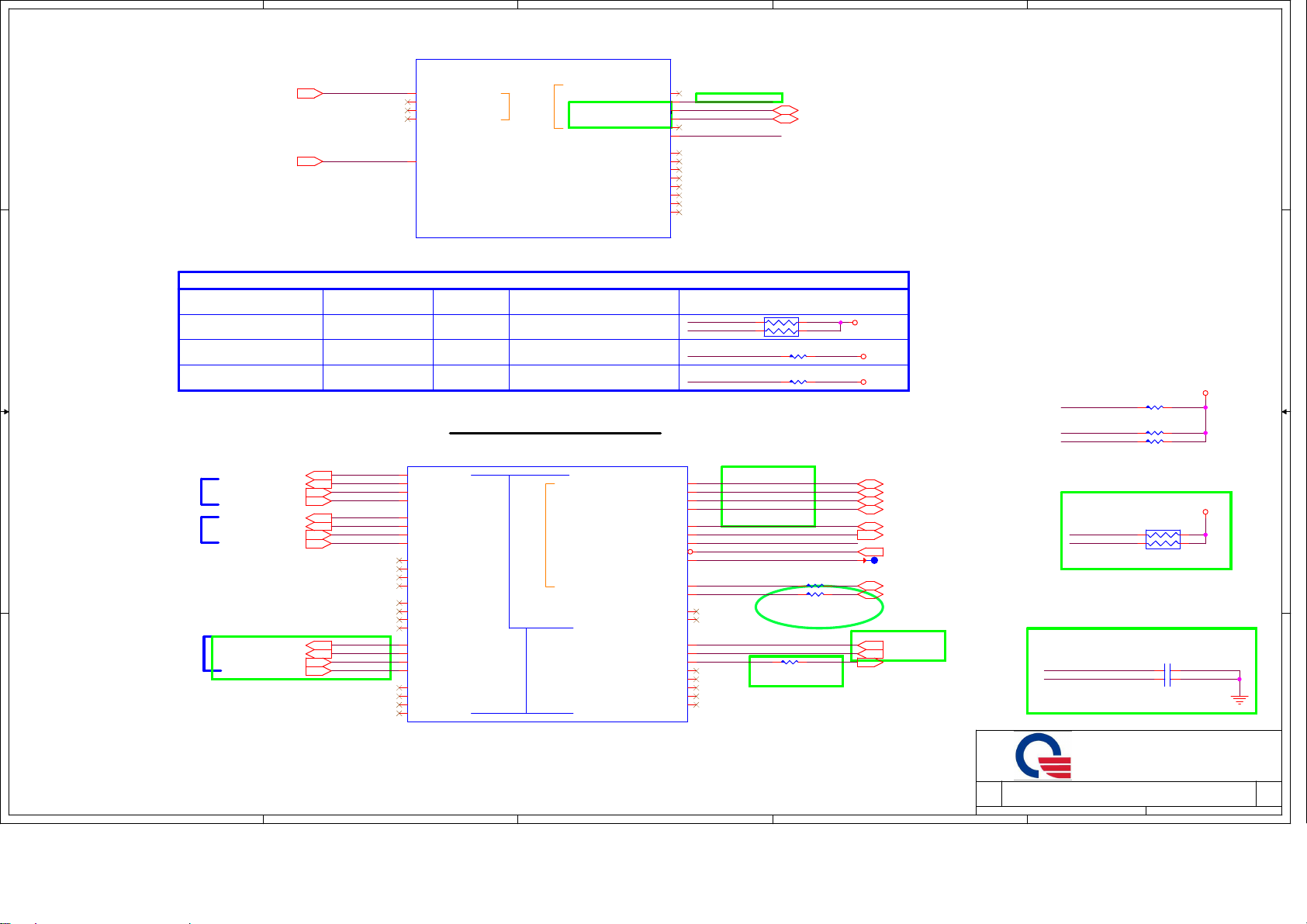

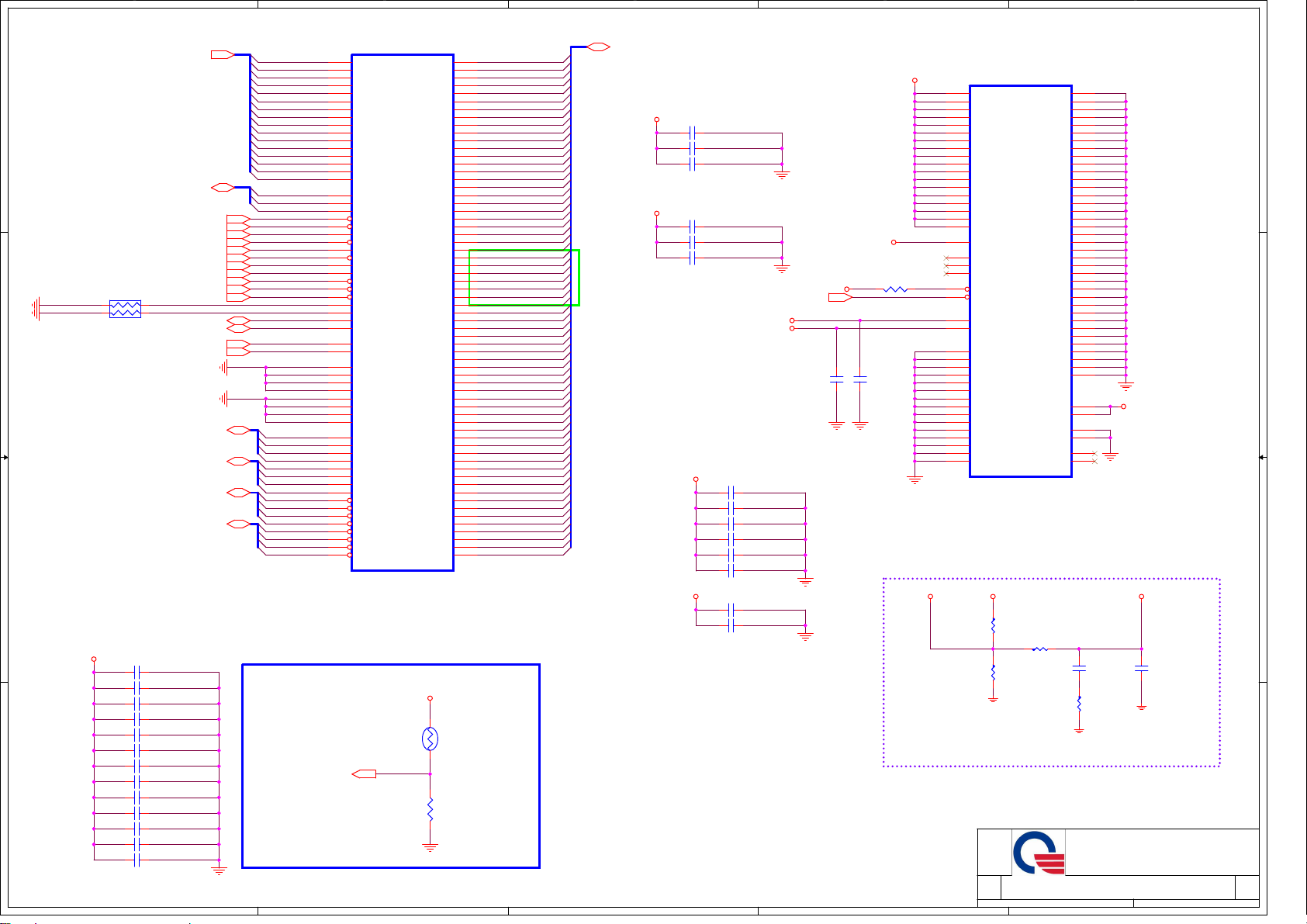

Skylake Processor (PEG, DMI)

SKYLAKE_HALO

D D

PEG_RXP717

PEG_RXN71 7

PEG_RXP617

PEG_RXN61 7

PEG_RXP517

PEG_RXN51 7

PEG_RXP417

PEG_RXN41 7

PEG_RXP317

PEG_RXN31 7

PEG_RXP217

PEG_RXN21 7

PEG_RXP117

C C

B B

PEG_RXN11 7

PEG_RXP017

PEG_RXN01 7

546884 V1.0 P188

+VCCIO

DMI_RXP09

DMI_RXN09

DMI_RXP19

DMI_RXN19

DMI_RXP29

DMI_RXN29

DMI_RXP39

DMI_RXN39

A A

2/3 Port

PEG_RXP7

PEG_RXN7

PEG_RXP6

PEG_RXN6

PEG_RXP5

PEG_RXN5

PEG_RXP4

PEG_RXN4

PEG_RXP3

PEG_RXN3

PEG_RXP2

PEG_RXN2

PEG_RXP1

PEG_RXN1

PEG_RXP0

PEG_RXN0

R300

PEG_RCOMP

24.9/F_4

Place inside CPU cavity

DMI_RXP0

DMI_RXN0

DMI_RXP1

DMI_RXN1

DMI_RXP2

DMI_RXN2

DMI_RXP3

DMI_RXN3

U10C

E25

PEG_RXP[0]

D25

PEG_RXN[0]

E24

PEG_RXP[1]

F24

PEG_RXN[1]

E23

PEG_RXP[2]

D23

PEG_RXN[2]

E22

PEG_RXP[3]

F22

PEG_RXN[3]

E21

PEG_RXP[4]

D21

PEG_RXN[4]

E20

PEG_RXP[5]

F20

PEG_RXN[5]

E19

PEG_RXP[6]

D19

PEG_RXN[6]

E18

PEG_RXP[7]

F18

PEG_RXN[7]

D17

PEG_RXP[8]

E17

PEG_RXN[8]

F16

PEG_RXP[9]

E16

PEG_RXN[9]

D15

PEG_RXP[10]

E15

PEG_RXN[10]

F14

PEG_RXP[11]

E14

PEG_RXN[11]

D13

PEG_RXP[12]

E13

PEG_RXN[12]

F12

PEG_RXP[13]

E12

PEG_RXN[13]

D11

PEG_RXP[14]

E11

PEG_RXN[14]

F10

PEG_RXP[15]

E10

PEG_RXN[15]

G2

PEG_RCOMP

D8

DMI_RXP[0]

E8

DMI_RXN[0]

E6

DMI_RXP[1]

F6

DMI_RXN[1]

D5

DMI_RXP[2]

E5

DMI_RXN[2]

J8

DMI_RXP[3]

J9

DMI_RXN[3]

SKL_H_BGA_BG A/BGA

BGA1440

3 OF 14

PEG_TXP[0]

PEG_TXN[0]

PEG_TXP[1]

PEG_TXN[1]

PEG_TXP[2]

PEG_TXN[2]

PEG_TXP[3]

PEG_TXN[3]

PEG_TXP[4]

PEG_TXN[4]

PEG_TXP[5]

PEG_TXN[5]

PEG_TXP[6]

PEG_TXN[6]

PEG_TXP[7]

PEG_TXN[7]

PEG_TXP[8]

PEG_TXN[8]

PEG_TXP[9]

PEG_TXN[9]

PEG_TXP[10]

PEG_TXN[10]

PEG_TXP[11]

PEG_TXN[11]

PEG_TXP[12]

PEG_TXN[12]

PEG_TXP[13]

PEG_TXN[13]

PEG_TXP[14]

PEG_TXN[14]

PEG_TXP[15]

PEG_TXN[15]

DMI_TXP[0]

DMI_TXN[0]

DMI_TXP[1]

DMI_TXN[1]

DMI_TXP[2]

DMI_TXN[2]

DMI_TXP[3]

DMI_TXN[3]

REV = 1

PEG_TXP7

B25

PEG_TXN7

A25

PEG_TXP6

B24

PEG_TXN6

C24

PEG_TXP5

B23

PEG_TXN5

A23

PEG_TXP4

B22

PEG_TXN4

C22

PEG_TXP3

B21

PEG_TXN3

A21

PEG_TXP2

B20

PEG_TXN2

C20

PEG_TXP1

B19

PEG_TXN1

A19

PEG_TXP0

B18

PEG_TXN0

C18

A17

B17

C16

B16

A15

B15

C14

B14

A13

B13

C12

B12

A11

B11

C10

B10

DMI_TXP0

B8

DMI_TXN0

A8

DMI_TXP1

C6

DMI_TXN1

B6

DMI_TXP2

B5

DMI_TXN2

A5

DMI_TXP3

D4

DMI_TXN3

B4

C589 0.22U/16V_4

C591 0.22U/16V_4

C595 0.22U/16V_4

C592 0.22U/16V_4

C596 0.22U/16V_4

C598 0.22U/16V_4

C601 0.22U/16V_4

C600 0.22U/16V_4

C602 0.22U/16V_4

C603 0.22U/16V_4

C605 0.22U/16V_4

C604 0.22U/16V_4

C606 0.22U/16V_4

C610 0.22U/16V_4

C614 0.22U/16V_4

C611 0.22U/16V_4

2/3 Port

DMI_TXP0 9

DMI_TXN0 9

DMI_TXP1 9

DMI_TXN1 9

DMI_TXP2 9

DMI_TXN2 9

DMI_TXP3 9

DMI_TXN3 9

PEG_TXP7_C 17

PEG_TXN7_C 17

PEG_TXP6_C 17

PEG_TXN6_C 17

PEG_TXP5_C 17

PEG_TXN5_C 17

PEG_TXP4_C 17

PEG_TXN4_C 17

PEG_TXP3_C 17

PEG_TXN3_C 17

PEG_TXP2_C 17

PEG_TXN2_C 17

PEG_TXP1_C 17

PEG_TXN1_C 17

PEG_TXP0_C 17

PEG_TXN0_C 17

#546884 PDG 1. 0 page 163 #546884 PDG 1.0 page 155

INT_HDMI_TXP230

INT_HDMI_TXN230

INT_HDMI_TXP130

HDMI eDP

INT_HDMI_TXN130

INT_HDMI_TXP030

INT_HDMI_TXN030

INT_HDMI_TXCP30

INT_HDMI_TXCN30

INT_HDMI_TXP2

INT_HDMI_TXN2

INT_HDMI_TXP1

INT_HDMI_TXN1

INT_HDMI_TXP0

INT_HDMI_TXN0

INT_HDMI_TXCP

INT_HDMI_TXCN

K36

K37

H37

H36

D27

E27

H34

H33

F37

G38

F34

F35

E37

E36

F26

E26

C34

D34

B36

B34

F33

E33

C33

B33

A27

B27

J35

J34

J37

J38

Skylake Processor (DDI, eDP)

U10D

DDI1_TXP[0]

DDI1_TXN[0]

DDI1_TXP[1]

DDI1_TXN[1]

DDI1_TXP[2]

DDI1_TXN[2]

DDI1_TXP[3]

DDI1_TXN[3]

DDI1_AUXP

DDI1_AUXN

DDI2_TXP[0]

DDI2_TXN[0]

DDI2_TXP[1]

DDI2_TXN[1]

DDI2_TXP[2]

DDI2_TXN[2]

DDI2_TXP[3]

DDI2_TXN[3]

DDI2_AUXP

DDI2_AUXN

DDI3_TXP[0]

DDI3_TXN[0]

DDI3_TXP[1]

DDI3_TXN[1]

DDI3_TXP[2]

DDI3_TXN[2]

DDI3_TXP[3]

DDI3_TXN[3]

DDI3_AUXP

DDI3_AUXN

SKL_H_BGA_BG A/BGA

SKYLAKE_HALO

BGA1440

4 OF 14

EDP_TXP[0]

EDP_TXN[0]

EDP_TXP[1]

EDP_TXN[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXP

EDP_AUXN

EDP_DISP_UTIL

EDP_RCOMP

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

REV = 1

EDP_TXP0

D29

EDP_TXN0

E29

EDP_TXP1

F28

EDP_TXN1

E28

EDP_TXN2

B29

EDP_TXP2

A29

EDP_TXN3

B28

EDP_TXP3

C28

EDP_AUXP

C26

EDP_AUXN

B26

EDP_DISP_UTIL

A33

EDP_RCOMP

D37

AUD_AZACPU_ SCLK

G27

AUD_AZACPU_ SDO

G25

AUD_AZACPU_ SDI_R

G29

EDP_TXP0 29

EDP_TXN0 29

EDP_TXP1 29

EDP_TXN1 29

EDP_TXN2 29

EDP_TXP2 29

EDP_TXN3 29

EDP_TXP3 29

EDP_AUXP 29

EDP_AUXN 29

TP1

R29 24. 9/F_4

Place inside CPU cavity

R18 20_4

Place near CPU

PDG V1.0 P351

EMI

AUD_AZACPU_ SCLK

+VCCIO

AUD_AZACPU_ SCLK 10

AUD_AZACPU_ SDO 10

AUD_AZACPU_ SDI 10

EC10 *10P/50V_4_NC

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size D ocument Number Rev

Size D ocument Number Rev

Size D ocument Number Rev

Date: Sheet of

Monday, May 25, 2015

Date: Sheet of

Monday, May 25, 2015

Date: Sheet of

5

4

3

2

Monday, May 25, 2015

PROJECT :

CPU

CPU

CPU

AM9A

AM9A

AM9A

A0

A0

3 57

3 57

1

3 57

A0

5

4

3

2

1

SVID

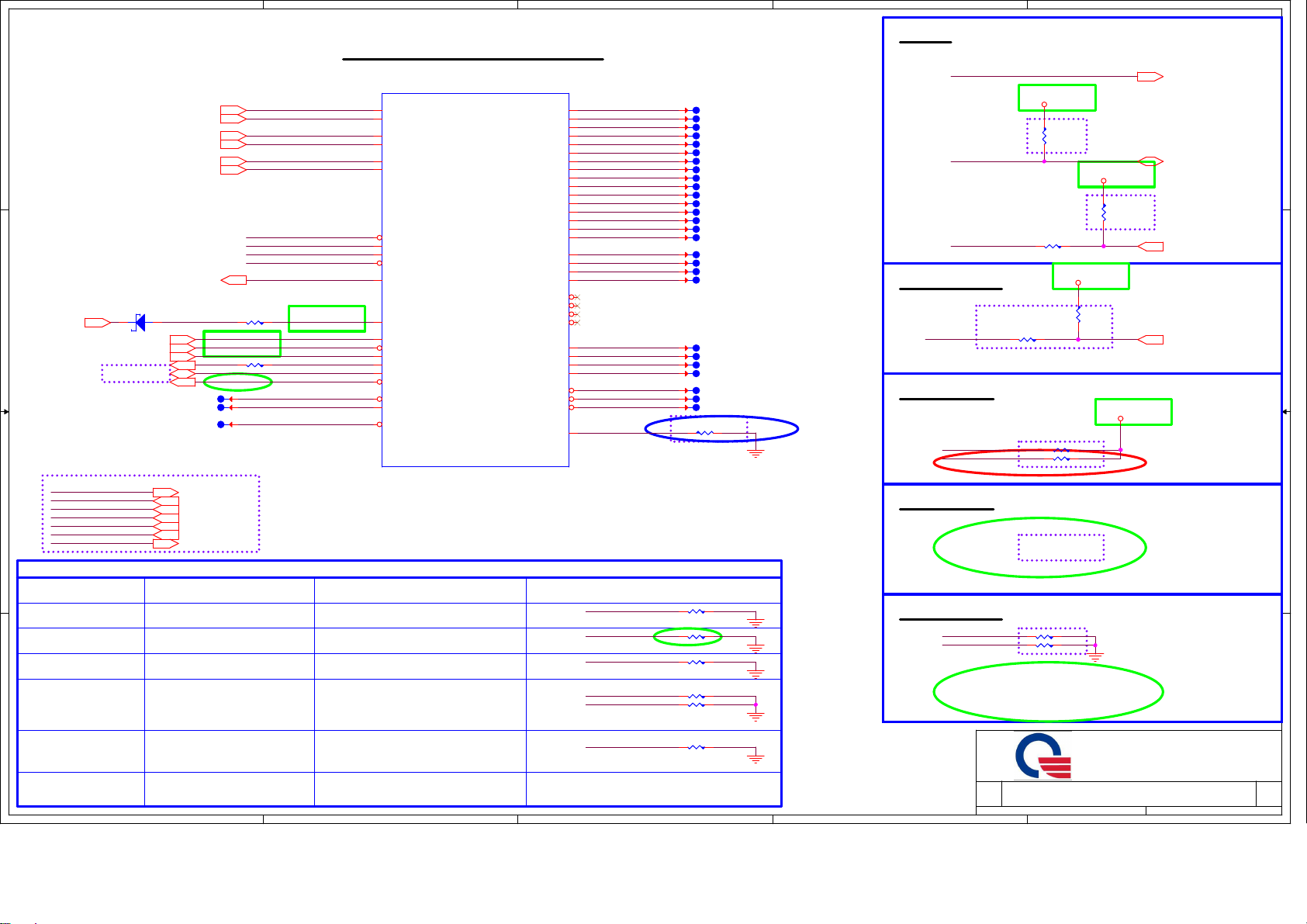

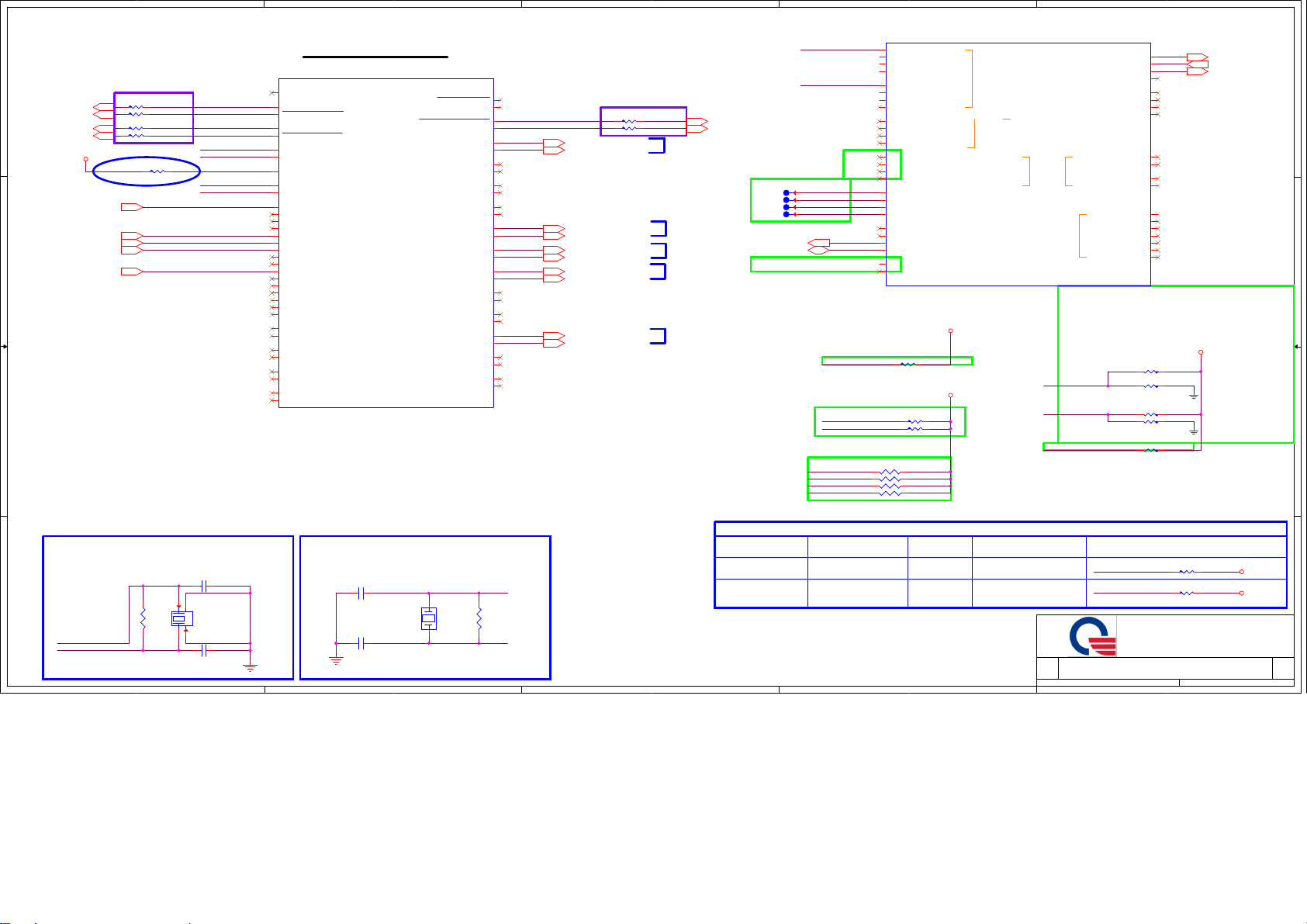

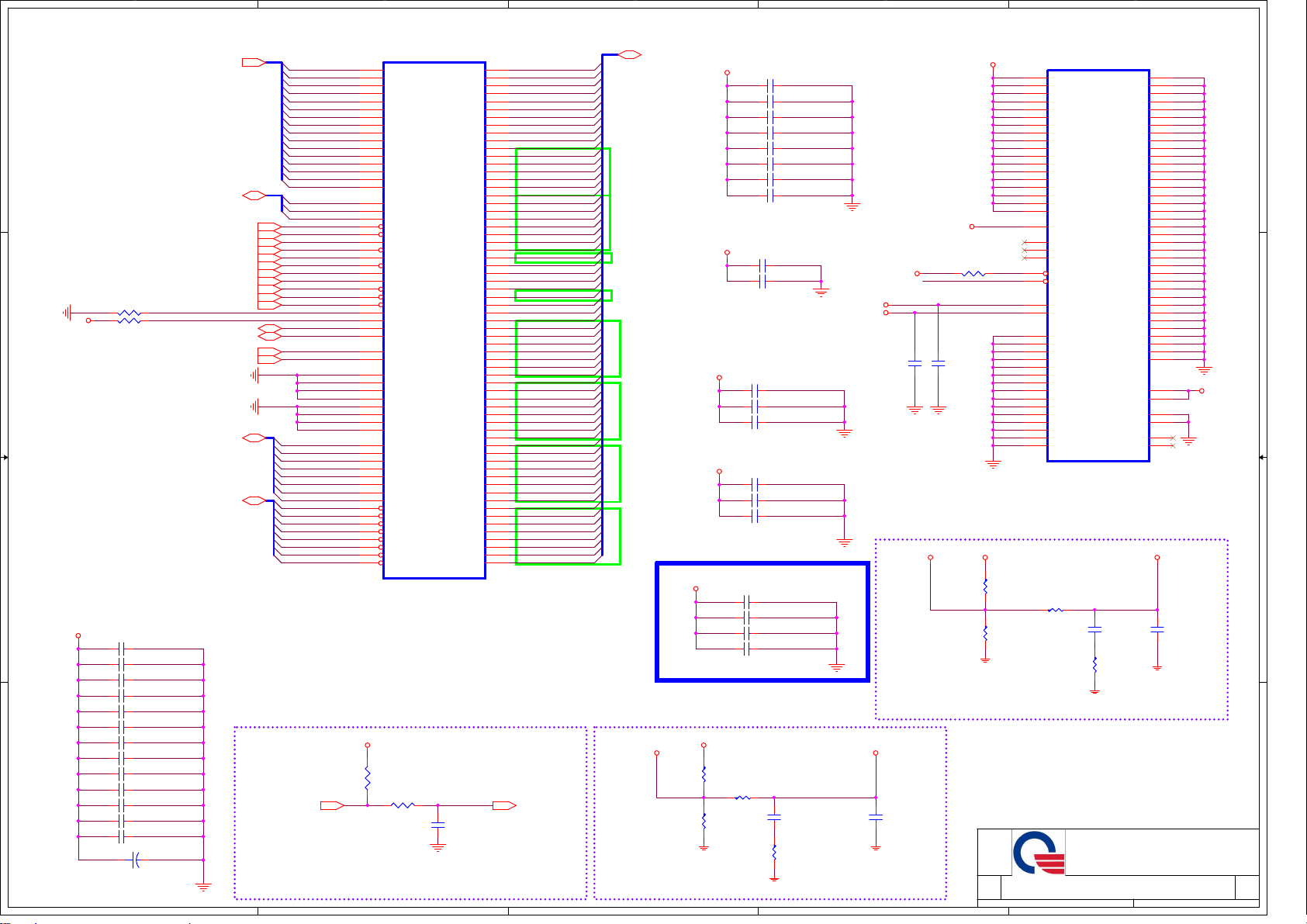

Skylake Processor (CLK, SVID, CFG)

U10E

D D

C C

B B

HWPG26,33

PCH_THERMT RIP#10

Connector Less Debug Hoo ks Routing Guidelines

#546884 PDG (V1.0) page 505

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST #

PROC_PREQ#

PROC_PRDY#

CLK_CPU_BCLKP12

CLK_CPU_BCLKN12

PCI_CLK_CPU_BCLKP12

PCI_CLK_CPU_BCLKN12

CPU_24MHZ_CLKP12

CPU_24MHZ_CLKN12

DDR_VTT _CTRL46

VCCST_PWR GD

D13 SDM10K45-7-F

21

H_PWRGOO D10

CPU_PLTRST #10

H_PM_SYNC10

H_PM_DOWN10

H_PECI10,26

PROC_TDO 10

PROC_TDI 10

PROC_TMS 10

PROC_TCK 10

PROC_TRST # 14

PROC_PREQ# 14

PROC_PRDY# 14

2/3 remove 0 ohm

TP55

TP77

TP58

CLK_CPU_BCLKP

CLK_CPU_BCLKN

PCI_CLK_CPU_BCLKP

PCI_CLK_CPU_BCLKN

CPU_24MHZ_CLKP

CPU_24MHZ_CLKN

CPU_VIDALERT#

VR_SVID_CLK

VR_SVID_DATA

H_PROCHOT #_R

DDR_VTT _CTRL

VTT EN

2/9 add net name

R314 60.4/F_4

R265 20_4

H_PECI

2/3 remove 0 ohm

VCCST_PWR GD_R

H_PM_SYNC

H_PM_DOWN_ R

H_SKTOCC#

H_PROC_SELECT #

H_CATERR#

B31

BCLKP

A32

BCLKN

D35

PCI_BCLKP

C36

PCI_BCLKN

E31

CLK24P

D31

CLK24N

BH31

VIDALERT#

BH32

VIDSCK

BH29

VIDSOUT

BR30

PROCHOT#

BT13

DDR_VTT _CNTL

H13

VCCST_PWR GD

BT31

PROCPWRGD

BP35

RESET#

BM34

PM_SYNC

BP31

PM_DOWN

BT34

PECI

J31

THERMTRIP#

BR33

SKTOCC#

BN1

PROC_SELECT#

BM30

CATERR#

SKL_H_BGA_BGA/BGA

SKYLAKE_HALO

BGA1440

100 MHz

100 MHz fo r PCIe

24 MHz

(1V)

5 OF 14

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[17]

CFG[16]

CFG[19]

CFG[18]

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST #

PROC_PREQ#

PROC_PRDY#

CFG_RCOMP

REV = 1

CFG [0..19] Internal

PU 3K to VCCIO

BN25

BN27

BN26

BN28

BR20

BM20

BT20

BP20

BR23

BR22

BT23

BT22

BM19

BR19

BP19

BT19

BN23

BP23

BP22

BN22

BR27

BT27

BM31

BT30

BT28

BL32

BP28

BR28

BP30

BL30

BP27

BT25

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG17

CFG16

CFG19

CFG18

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST #

PROC_PREQ#

PROC_PRDY#

CFG_RCOMP

TP63

TP5

TP62

TP6

TP69

TP76

TP70

TP74

TP64

TP68

TP65

TP67

TP10

TP71

TP73

TP72

TP8

TP7

TP66

TP9

PROC_TDI & PROC_TMS & BPM[3:0]

& PREQ# & CFG[19:0] had internal PU

TP59

TP2

TP61

TP60

TP57

TP3

TP4

R280 49.9/F_4

CFG_RCOMP PD resistor re fer to

#550607 SKL-H schematic page 16

Place near CPU

SIVD CLK

SVID DATA

SVID ALERT

Procssor HOT

CPU PU/PD

Thermtrip

CPU STRAP PIN

Pin Name Usage

CFG[0]

CFG[2]

CFG[4]

CFG[6:5]

A A

CFG[7]

CFG[1] CFG[3]

Stall reset sequence after PCU

PLL lock until de-asserted

PCI Express* Static x16 Lane

Numbering Reversal.

eDP enable 1 = Disabled(Default)

PCI Express* Bifurcation 00 = 1 x8, 2 x4 PCI Express*

PEG Training 1 = PEG Train immediately following

Reserved configuration lanes.

1 = (Default) Normal Operation; No stall.

0 = Stall.

1 = Normal operation (Default)

0 = Lane numbers rev ersed.

0 = Enabled

01 = reserved

10 = 2 x8 PCI Express*

11 = 1 x16 PCI Express*(default)

RESET# de-assertion.(default)

0 = PEG Wait for BIOS for training.

Configuration Circuitry

CFG0

CFG2

2/4 pop R21 Lane numbers reversed

CFG4

CFG5

CFG6

CFG7

R281 *1K_4_NC

R279 1K_4

R283 1K_4

R288 1K_4

R285 *1K_4_NC

R287 *1K_4_NC

JTAG PU/PD

CFG[19:8]

5

4

3

2

VR_SVID_CLK

VR_SVID_DATA

CPU_VIDALERT#

Place near CPU

H_PROCHOT #_R

PDG V1.0 P210

+VCC_1.00

R274 220_4

R269 499/F_4

2/11 change to +VCC_1.00

Place near CPU

R271

100_4

+VCC_1.00

Place near CPU

+VCC_1.00

R270

1K_4

+VCC_1.00

R273

56.2/F_4

VR_SVID_CLK 41

VR_SVID_DATA 41

VR_SVID_ALERT# 41

H_PROCHOT # 26,40,41

Place near CPU

VCCST_PWR GD

H_CATERR#

R318 1K_4

R272 *10K_4_NC

Place near CPU

Thermtrip PU 1K ohms

PDG #546884 P213

PROC_TCK

PROC_TRST #

2/4 move R841 to PCH JTAG page

Size D ocument Nu mber Rev

Size D ocument Nu mber Rev

Size D ocument Nu mber Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Placed to within 200ps(1 ") of CPU pin

R276 *51_4_NC

R268 *51_4_NC

#546884 PDG 1.0 page 504

CPU

CPU

Monday, May 25, 2015

Monday, May 25, 2015

Monday, May 25, 2015

CPU

2/3 remove R186 1K_4

double PU

#546884 PDG page 616-> PD 5 1 ohm

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

AM9A

AM9A

AM9A

04

4 57

4 57

4 57

A0

A0

A0

5

PDG V1.0 #546844 page 573 VCC decoupling

47uFx4, 22uFx8, 10uFx28, 1uFx63

leverage other BU to optimums capacitor design

2/11 remove 47u*4,

22u*4

D D

C C

B B

A A

+VCCIN +VCCIN

AA13

AA31

AA32

AA33

AA34

AA35

AA36

AA37

AA38

AB29

12

C17222U/6.3V/X6S_6

AB30

12

C19522U/6.3V/X6S_6

AB31

12

C18222U/6.3V/X6S_6

AB32

12

C20522U/6.3V/X6S_6

C14110U/6.3V/X6S_4

C23510U/6.3V/X6S_4

C28810U/6.3V/X6S_4

C9210U/6 .3V/X6S_4

C6310U/6 .3V/X6S_4

C8310U/6 .3V/X6S_4

C10710U/6.3V/X6S_4

C16010U/6.3V/X6S_4

C26210U/6.3V/X6S_4

C12310U/6.3V/X6S_4

C12010U/6.3V/X6S_4

C15510U/6.3V/X6S_4

C10110U/6.3V/X6S_4

C26410U/6.3V/X6S_4

C12210U/6.3V/X6S_4

C14910U/6.3V/X6S_4

C6410U/6 .3V/X6S_4

C23410U/6.3V/X6S_4

C22010U/6.3V/X6S_4

C6610U/6 .3V/X6S_4

C15110U/6.3V/X6S_4

C6510U/6 .3V/X6S_4

C6210U/6 .3V/X6S_4

C23310U/6.3V/X6S_4

C10610U/6.3V/X6S_4 C129 1U/10V/X6S_4

C23210U/6.3V/X6S_4

C25310U/6.3V/X6S_4

C25210U/6.3V/X6S_4

AB35

AB36

AB37

AB38

AC13

AC14

AC29

AC30

AC31

AC32

AC33

AC34

AC35

AC36

AD13

AD14

AD31

AD32

AD33

AD34

AD35

AD36

AD37

AD38

AE13

AE14

AE30

AE31

AE32

AE35

AE36

AE37

AE38

AF35

AF36

AF37

AF38

K13

K14

L13

N13

N14

N30

N31

N32

N35

N36

N37

N38

P13

5

SKYLAKE_HALO

U10G

BGA1440

VCC

S0

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

SKL_H_BGA_BGA/BGA

7 OF 14

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC_SENSE

VSS_SENSE

REV = 1

4

VCC = 60A (QC:35W+GT2)

VCC = 68A (QC:45W+GT2)

V32

V33

C148 10U/6.3V/X6S_4

V34

V35

C124 1U/10V/X6S_4

V36

C121 1U/10V/X6S_4

V37

V38

W13

W14

W29

W30

C126 1U/10V/X6S_4

W31

C270 1U/10V/X6S_4

W32

C161 10U/6.3V/X6S_4

W35

C158 10U/6.3V/X6S_4

W36

W37

W38

Y29

C246 1U/10V/X6S_4

Y30

C84 1U/10V/X6S_4

Y31

Y32

C266 1U/10V/X6S_4

Y33

C138 1U/10V/X6S_4

Y34

C127 1U/10V/X6S_4

Y35

Y36

C81 1U/10V/X6S_4

L14

P29

C251 1U/10V/X6S_4

P30

P31

C137 1U/10V/X6S_4

P32

P33

C82 1U/10V/X6S_4

P34

C45 1U/10V/X6S_4

P35

P36

C279 1U/10V/X6S_4

R13

R31

R32

C269 1U/10V/X6S_4

R33

R34

R35

C79 1U/10V/X6S_4

R36

C80 1U/10V/X6S_4

R37

R38

T29

T30

T31

T32

T35

C277 1U/10V/X6S_4

T36

C105 1U/10V/X6S_4

T37

C159 10U/6.3V/X6S_4

T38

U29

U30

C157 10U/6.3V/X6S_4

U31

C100 1U/10V/X6S_4

U32

U33

U34

C44 1U/10V/X6S_4

U35

C114 1U/10V/X6S_4

U36

V13

V14

V31

C104 1U/10V/X6S_4

P14

R26 100/F_4

AG37

AG38

R23 100/F_4

Please near CPU

4

Skylake Processor (POWER)

+VCCIN

VCCCORE_SENSE 41

VSSCORE_SENSE 41

3

VCCOPC, VCCOPC_1p8, VCCEOPIO is OPC (On Package Cache)

realted power rail and used for 4+4e processor

Pandora support 4+2 Processor (w/o OPC)

Rail is unconnected for those pins w/o OPC

#544924 EDS (V0.92) page129 Note3

Unconnected for Processors without OPC.

#544924 EDS (V0.91) page121

3

U10J

BJ17

BJ19

BJ20

BK17

BK19

BK20

BL16

BL17

BL18

BL19

BL20

BL21

BM17

BN17

BJ23

BJ26

BJ27

BK23

BK26

BK27

BL23

BL24

BL25

BL26

BL27

BL28

BM24

BL15

BM16

BL22

BM22

BP15

BR15

BT15

BP16

BR16

BT16

BN15

BM15

BP17

BN16

BM14

BL14

BJ35

BJ36

AT13

AW13

AU13

AY13

BT29

BR25

BP25

SKL_H_BGA_BGA/BGA

2

SKYLAKE_HALO

BGA1440

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCCOPC_SENSE

VSSOPC_SENSE

RSVD

RSVD

VCCEOPIO

VCCEOPIO

VCCEOPIO

RSVD

RSVD

RSVD

VCCEOPIO_SENSE

VSSEOPIO_SENSE

RSVD

RSVD

VCC_OPC_1P8

VCC_OPC_1P8

RSVD

RSVD

ZVM#

MSM#

ZVM2#

MSM2#

OPC_RCOMP

OPCE_RCOMP

OPCE_RCOMP2

2

10 OF 14

1

05

REV = 1

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size D ocument Nu mber Rev

Size D ocument Nu mber Rev

Size D ocument Nu mber Rev

Date: Sheet of

Monday, May 25, 2015

Date: Sheet of

Monday, May 25, 2015

Date: Sheet of

Monday, May 25, 2015

PROJECT :

CPU

CPU

CPU

1

AM9A

AM9A

AM9A

5 57

5 57

5 57

A0

A0

A0

5

PDG V1.0 #546844 page 573 & 574 decoupling capacitor

VCCSA: 220uFx1, 47uFx1, 10uFx10, 1uFx3

VCCIO: 47uFx2, 10uFx3, VDDQ: 22uFx4, 10uFx10

VDDQC: 10uFx1, VCCST:1uFx1, VCCSTG: 1uFx1

VCCPLL: 1uFx1, VCCPLL_OC: 1uFx2,

2/11 47u*1 change

to 22u*2

D D

C C

B B

leverage other BU to optimums capacitor design

+VCCSA

12

C16422U/6.3V/X6S_6

12

C17422U/6.3V/X6S_6

C13010U/6.3V/X6S_4

C13110U/6.3V/X6S_4

C11610U/6.3V/X6S_4

C14310U/6.3V/X6S_4

C14210U/6.3V/X6S_4

2/9 remove 3*10u

22uFx4 Please

near VR

2/11 47u*2 change

to 22u*4, 2pcs NC

C4110U/6.3V/X6S_4

C371U/10V/X6S_4

C951U/10V/X6S_4

C741U/10V/X6S_4

12

C20322U/6.3V/X6S_6

12

12

C618*22U/6.3V/X6S_6_NC

12

C613*22U/6.3V/X6S_6_NC

C19110U/6.3V/X6S_4

C21810U/6.3V/X6S_4

C21710U/6.3V/X6S_4

+VCCIO

U10I

J30

K29

K30

K31

K32

K33

K34

K35

L31

L32

L35

L36

L37

L38

M29

M30

M31

M32

M33

M34

M35

M36

AG12

G15

G17

G19

G21

H15

H16

H17

H19

H20

H21

H26

H27

J15

J16

J17

J19

J20

J21

J26

J27

SKL_H_BGA_BGA/BGA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

SKYLAKE_HALO

BGA1440

S0

S0

9 OF 14

(PLL)

(PLL)

VCCSA_SENSE

VSSSA_SENSE

VCCIO_SENSE

VSSIO_SENSE

S3

VDDQC

VCCPLL_OC

VCCPLL_OC

S3

VCCST

VCCSTG

S0

VCCSTG

S0

VCCPLL

VCCPLL

REV = 1

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

4

EDS V0.92 #544924 page 135~140 power rail

VDDQ: 1.35V/2.8A (DDR3L), 1.2V/2.8A (DDR4/LPDDR3)

VCCSA: 0.55-1.15V/11.1A, VCCIO: 0.95V/5.5A

VCCST: 1.0V/120mA, VCCPLL: 1.0V/145mA

+V_VDDQ

AA6

2/11 22u*2 change to NC

AE12

AF5

AF6

AG5

AG9

AJ12

AL11

AP6

AP7

AR12

AR6

AT12

AW6

AY6

J5

J6

K12

K6

L12

L6

R6

T6

W6

Y12

BH13

G11

H30

H29

G30

H28

J28

M38

M37

H14

J14

1 2

C284 *22U/6.3V/X6S_6_NC

1 2

C383 *22U/6.3V/X6S_6_NC

1 2

C388 22U/6.3V/X6S_6

1 2

C385 22U/6.3V/X6S_6

C320 10U/6.3V/X6S_4

C281 10U/6.3V/X6S_4

C283 10U/6.3V/X6S_4

C280 10U/6.3V/X6S_4

C328 10U/6.3V/X6S_4

C335 10U/6.3V/X6S_4

C380 10U/6.3V/X6S_4

C282 10U/6.3V/X6S_4

C292 10U/6.3V/X6S_4

C381 10U/6.3V/X6S_4

4/31 change to 1u

C290 1U/10V/X6S_4C22722U/6.3V/X6S_6

C340 1U/10V/X6S_4

C300 1U/10V/X6S_4

C168 1U/10V/X6S_4

VCCSTG_R

R22 100/F_4

R30 100/F_4

R46 100/F_4

R47 100/F_4

1 2

R16 *0_6_NC

1 2

R15 0_6

C111 1U/10V/X6S_4

C156 1U/10V/X6S_4

+VCCSA

VCCSA_SENSE 41

VSSSA_SENSE 4 1

+VCCIO

VCCIO_SENSE 47

VSSIO_SENSE 47

VCCPLL_OC source from VD DQ

EDS V0.92 #544924 P129 n ote 4 & 5

+VDDQ_CPU_C LK

+V_VDDQ

+VCC_1.00_PP

+VCC_1.00

3

Skylake Processor (POWER)

PROC_TRIGIN14

+VCC_1.00

2/11 change to +VCC_1.00

VCCSTG source from VCCST

EDS V0.92 #544924 P129 n ote 4 & 5

+VCC_1.00

2/11 change to +VCC_1.00

Debug pin

PROC_TRIGIN

PROC_TRIGOUT _R

2

U10K

D1

RSVD_TP

E1

RSVD_TP

E3

RSVD_TP

E2

RSVD_TP

BR1

RSVD_TP

BT2

RSVD_TP

BN35

RSVD

J24

RSVD

H24

RSVD

BN33

RSVD

BL34

RSVD

N29

RSVD

R14

RSVD

AE29

RSVD

AA14

RSVD

A36

RSVD

A37

RSVD

H23

PROC_TRIGIN

J23

PROC_TRIGOUT

F30

RSVD

E30

RSVD

B30

RSVD

C30

RSVD

G3

RSVD

J3

RSVD

BR35

RSVD

BR31

RSVD

BH30

RSVD

SKL_H_BGA_BGA/BGA

SKYLAKE_HALO

BGA1440

11 OF 14

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

VSS

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

VSS

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

NCTF

NCTF

NCTF

NCTF

NCTF

NCTF

REV = 1

1

06

BM33

BL33

BJ14

BJ13

BK28

BJ28

BJ18

BJ16

BK16

BK24

BJ24

BK21

BJ21

BT17

BR17

BK18

BJ34

BJ33

G13

AJ8

BL31

B2

B38

BP1

BR2

C1

C38

Place near CPU

PROC_TRIGOUT _R PROC_TRIGOUT

R36 30_4

PROC_TRIGOUT 14

VDDQC for SKL - U/Y seri es, H series left NC.

#550607 reference schema tic P18

+VDDQ_CPU_C LK

R49 0_4_

+V_VDDQ

0430 add bom

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size D ocument Nu mber Rev

Size D ocument Nu mber Rev

Size D ocument Nu mber Rev

Date: Sheet of

Monday, May 25, 2015

Date: Sheet of

Monday, May 25, 2015

Date: Sheet of

5

4

3

2

Monday, May 25, 2015

PROJECT :

CPU

CPU

CPU

1

AM9A

AM9A

AM9A

6 57

6 57

6 57

A0

A0

A0

5

leverage other BU to optimums capacitor design

D D

C274

10U/6.3V/X6S_4

C256

10U/6.3V/X6S_4

C278

1U/10V/X6S_4

C C

C152

1U/10V/X6S_4

C98

1U/10V/X6S_4

B B

A A

C176

10U/6.3V/X6S_4

C55

10U/6.3V/X6S_4

C71

1U/10V/X6S_4

C136

1U/10V/X6S_4

C170

10U/6.3V/X6S_4

10U/6.3V/X6S_4

C76

1U/10V/X6S_4

C134

1U/10V/X6S_4

C73

1U/10V/X6S_4

5

C162

10U/6.3V/X6S_4

C255

10U/6.3V/X6S_4

C133

1U/10V/X6S_4

C132

1U/10V/X6S_4

C145

1U/10V/X6S_4

C102

1U/10V/X6S_4

2/11 change to NC

C273

10U/6.3V/X6S_4

C163

10U/6.3V/X6S_4

C112

1U/10V/X6S_4

C150

1U/10V/X6S_4

C128

1U/10V/X6S_4

C78

1U/10V/X6S_4

4

PDG V1.0 #546884 P573-574 decupling

47uFx6, 22uFx8, 10uFx35, 1uFx68.

VCCGT = 55A (QC+GT2)

+VCCGT

12

C242*22U/6.3V_6_NC

12

C238*22U/6.3V_6_NC

12

C237*22U/6.3V_6_NC

12

C239*22U/6.3V_6_NC

12

C24122U/6.3V_6

12

C18122U/6.3V_6

12

C16922U/6.3V_6

12

C21222U/6.3V_6

C8610U/10V_4

C6110U/10V_4C119

C1541 0U/10V_4

C2581 0U/10V_4

C1391 0U/10V_4

C2671 0U/10V_4

C6710U/10V_4

C2611 0U/10V_4

C1531 0U/10V_4

C5810U/10V_4

C2601 0U/10V_4

C1131 0U/10V_4

C9710U/10V_4

C1171 0U/10V_4

C9610U/10V_4

C9110U/10V_4

C5910U/10V_4

C9910U/10V_4

C1151 0U/10V_4

C1101 0U/10V_4

C2681 0U/10V_4

C5710U/10V_4

C5610U/10V_4

C2591 0U/10V_4

C1181 0U/10V_4

C601U/6.3V_4

C2911U/6.3V_4

C721U/6.3V_4

C751U/6.3V_4

C2891U/6.3V_4

C1031U/6.3V_4

C2931U/6.3V_4

C771U/6.3V_4

C941U/6.3V_4

C1351U/6.3V_4

C1441U/6.3V_4

C1091U/6.3V_4

C931U/6.3V_4

C2751U/6.3V_4

C701U/6.3V_4

C871U/6.3V_4

C891U/6.3V_4

C1471U/6.3V_4

C1461U/6.3V_4

C1401U/6.3V_4

C17747U/4V/X6S_8

C16747U/4V/X6S_8

C17947U/4V/X6S_8

C18047U/4V/X6S_8

C16547U/4V/X6S_8

C16647U/4V/X6S_8

4

U10N

AJ29

VCCGT

AJ30

VCCGT

AJ31

VCCGT

AJ32

VCCGT

AJ33

VCCGT

AJ34

VCCGT

AJ35

VCCGT

AJ36

VCCGT

AK31

VCCGT

AK32

VCCGT

AK33

VCCGT

AK34

VCCGT

AK35

VCCGT

AK36

VCCGT

AK37

VCCGT

AK38

VCCGT

AL13

VCCGT

AL29

VCCGT

AL30

VCCGT

AL31

VCCGT

AL32

VCCGT

AL35

VCCGT

AL36

VCCGT

AL37

VCCGT

AL38

VCCGT

AM13

VCCGT

AM14

VCCGT

AM29

VCCGT

AM30

VCCGT

AM31

VCCGT

AM32

VCCGT

AM33

VCCGT

AM34

VCCGT

AM35

VCCGT

AM36

VCCGT

AN13

VCCGT

AN14

VCCGT

AN31

VCCGT

AN32

VCCGT

AN33

VCCGT

AN34

VCCGT

AN35

VCCGT

AN36

VCCGT

AN37

VCCGT

AN38

VCCGT

AP13

VCCGT

AP14

VCCGT

AP29

VCCGT

AP30

VCCGT

AP31

VCCGT

AP32

VCCGT

AP35

VCCGT

AP36

VCCGT

AP37

VCCGT

AP38

VCCGT

AR29

VCCGT

AR30

VCCGT

AR31

VCCGT

AR32

VCCGT

AR33

VCCGT

AR34

VCCGT

AR35

VCCGT

AR36

VCCGT

AT14

VCCGT

AT31

VCCGT

AT32

VCCGT

AT33

VCCGT

AT34

VCCGT

AT35

VCCGT

AT36

VCCGT

AT37

VCCGT

AT38

VCCGT

AU14

VCCGT

AU29

VCCGT

AU30

VCCGT

AU31

VCCGT

AU32

VCCGT

AU35

VCCGT

AU36

VCCGT

AU37

VCCGT

AU38

VCCGT

SKL_H_BGA_BGA/BGA

SKYLAKE_HALO

S0

BGA1440

14 OF 14

3

2

Skylake Processor (POWER)

SKYLAKE_HALO

+VCCGT

S0 S0

VCCGT_SENSE

VSSGTX_SENSE

VSSGT_SENSE

VCCGTX_SENSE

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

REV = 1

3

AF29

AF30

AF31

AF32

AF33

AF34

AG13

AG14

AG31

AG32

AG33

AG34

AG35

AG36

AH13

AH14

AH29

AH30

AH31

AH32

AJ13

AJ14

VCCGTX is processor w/ GT3/4 power rail.

Pandora support 4+2 Processor.

Rail is unconnected for those pins w/o OPC

#544924 EDS page127 Note2

AH38

AH35

AH37

AH36

R21 100/F_4

R24 100/F_4

+VCCGT

VCCGT_SENSE 41

VSSGT_SENSE 41

2

Size D ocument Nu mber Rev

Size D ocument Nu mber Rev

Size D ocument Nu mber Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

U10H

BG34

VCCGT

BG35

VCCGT

BG36

VCCGT

BH33

VCCGT

BH34

VCCGT

BH35

VCCGT

BH36

VCCGT

BH37

VCCGT

BH38

VCCGT

BJ37

VCCGT

BJ38

VCCGT

BL36

VCCGT

BL37

VCCGT

BM36

VCCGT

BM37

VCCGT

BN36

VCCGT

BN37

VCCGT

BN38

VCCGT

BP37

VCCGT

BP38

VCCGT

BR37

VCCGT

BT37

VCCGT

BE38

VCCGT

BF13

VCCGT

BF14

VCCGT

BF29

VCCGT

BF30

VCCGT

BF31

VCCGT

BF32

VCCGT

BF35

VCCGT

BF36

VCCGT

BF37

VCCGT

BF38

VCCGT

BG29

VCCGT

BG30

VCCGT

BG31

VCCGT

BG32

VCCGT

BG33

VCCGT

BC36

VCCGT

BC37

VCCGT

BC38

VCCGT

BD13

VCCGT

BD14

VCCGT

BD29

VCCGT

BD30

VCCGT

BD31

VCCGT

BD32

VCCGT

BD33

VCCGT

BD34

VCCGT

BD35

VCCGT

BD36

VCCGT

BE31

VCCGT

BE32

VCCGT

BE37

VCCGT

SKL_H_BGA_BGA/BGA

Monday, May 25, 2015

Monday, May 25, 2015

Monday, May 25, 2015

1

07

+VCCGT

BGA1440

8 OF 14

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

CPU

CPU

CPU

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

REV = 1

1

AM9A

AM9A

AM9A

AV29

AV30

AV31

AV32

AV33

AV34

AV35

AV36

AW14

AW31

AW32

AW33

AW34

AW35

AW36

AW37

AW38

AY29

AY30

AY31

AY32

AY35

AY36

AY37

AY38

BA13

BA14

BA29

BA30

BA31

BA32

BA33

BA34

BA35

BA36

BB13

BB14

BB31

BB32

BB33

BB34

BB35

BB36

BB37

BB38

BC29

BC30

BC31

BC32

BC35

BE33

BE34

BE35

BE36

7 57

7 57

7 57

A0

A0

A0

5

4

3

2

1

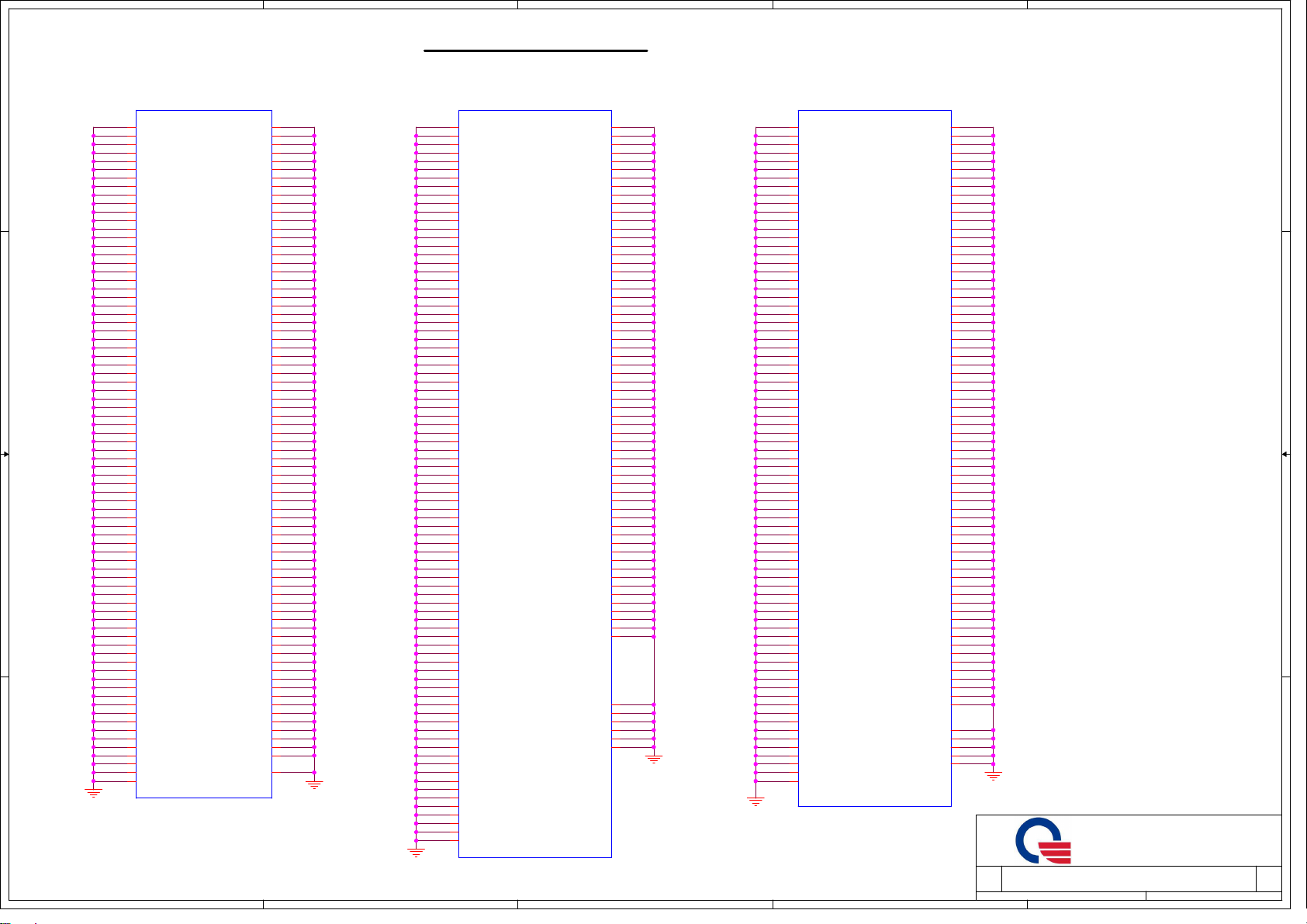

Skylake Processor (GROUND)

SKYLAKE_HALO

U10F

D D

C C

B B

A A

Y38

Y37

Y14

Y13

Y11

Y10

W34

W33

W12

V30

V29

V12

U38

U37

T34

T33

T14

T13

T12

T11

T10

R30

R29

R12

P38

P37

P12

N34

N33

N12

N11

N10

M14

M13

M12

K38

K11

K10

W5

W4

W3

W2

W1

L34

L33

L30

L29

Y9

Y8

Y7

V6

U6

T9

T8

T7

T5

T4

T3

T2

T1

P6

N9

N8

N7

N6

N5

N4

N3

N2

N1

M6

K9

K8

K7

K5

K4

K3

K2

BGA1440

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SKL_H_BGA_BGA/BGA

5

6 OF 14

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NCTFVSS

REV = 1

K1

J36

J33

J32

J25

J22

J18

J10

J7

J4

H35

H32

H25

H22

H18

H12

H11

G28

G26

G24

G23

G22

G20

G18

G16

G14

G12

G10

G9

G8

G6

G5

G4

F36

F31

F29

F27

F25

F23

F21

F19

F17

F15

F13

F11

F9

F8

F5

F4

F3

F2

E38

E35

E34

E9

E4

D33

D30

D28

D26

D24

D22

D20

D18

D16

D14

D12

D10

D9

D6

D3

C37

C31

C29

C27

D38

C17

C13

BT32

BT26

BT24

BT21

BT18

BT14

BT12

BT9

BT5

BR36

BR34

BR29

BR26

BR24

BR21

BR18

BR14

BR12

BR7

BP34

BP33

BP29

BP26

BP24

BP21

BP18

BP14

BP12

BP7

BN34

BN31

BN30

BN29

BN24

BN21

BN20

BN19

BN18

BN14

BN12

BN9

BN7

BN4

BN2

BM38

BM35

BM28

BM27

BM26

BM23

BM21

BM13

BM12

BM9

BM6

BM2

BL29

BK29

BK15

BK14

BJ32

BJ31

BJ25

BJ22

BH14

BH12

BH9

BH8

BH5

BH4

BH1

BG38

BG13

BG12

BF33

BF12

BE29

BE6

BD9

BC34

BC12

BB12

4

SKYLAKE_HALO

U10L

VSS

VSS

C9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SKL_H_BGA_BGA/BGA

BGA1440

12 OF 14

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

REV = 1

C25

C23

C21

C19

C15

C11

C8

C5

BM29

BM25

BM18

BM11

BM8

BM7

BM5

BM3

BL38

BL35

BL13

BL6

BK25

BK22

BK13

BK6

BJ30

BJ29

BJ15

BJ12

BH11

BH10

BH7

BH6

BH3

BH2

BG37

BG14

BG6

BF34

BF6

BE30

BE5

BE4

BE3

BE2

BE1

BD38

BD37

BD12

BD11

BD10

BD8

BD7

BD6

BC33

BC14

BC13

BC6

BB30

BB29

BB6

BB5

C2

BT36

BT35

BT4

BT3

BR38

SKYLAKE_HALO

U10M

BB4

BB3

BB2

BB1

BA38

BA37

BA12

BA11

BA10

BA9

BA8

BA7

BA6

B9

AY34

AY33

AY14

AY12

AW30

AW29

AW12

AW5

AW4

AW3

AW2

AW1

AV38

AV37

AU34

AU33

AU12

AU11

AU10

AU9

AU8

AU7

AU6

AT30

AT29

AT6

AR38

AR37

AR14

AR13

AR5

AR4

AR3

AR2

AR1

AP34

AP33

AP12

AP11

AP10

AP9

AP8

AN30

AN29

AN12

AN6

AN5

AM38

AM37

AM12

AM5

AM4

AM3

AM2

AM1

AL34

AL33

AL14

AL12

AL10

AL9

AL8

AL7

AL4

3

BGA1440

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SKL_H_BGA_BGA/BGA

13 OF 14

AK30

VSS

AK29

VSS

AK4

VSS

AJ38

VSS

AJ37

VSS

AJ6

VSS

AJ5

VSS

AJ4

VSS

AJ3

VSS

AJ2

VSS

AJ1

VSS

AH34

VSS

AH33

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

REV = 1

AH12

AH6

AG30

AG29

AG11

AG10

AG8

AG7

AG6

AF14

AF13

AF12

AF4

AF3

AF2

AF1

AE34

AE33

AE6

AD30

AD29

AD12

AD11

AD10

AD9

AD8

AD7

AD6

AC38

AC37

AC12

AC6

AC5

AC4

AC3

AC2

AC1

AB34

AB33

AB6

AA30

AA29

AA12

A30

A28

A26

A24

A22

A20

A18

A16

A14

A12

A10

A9

A6

B37

B3

A34

A4

A3

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size D ocument Nu mber Rev

Size D ocument Nu mber Rev

Size D ocument Nu mber Rev

Date: Sheet of

Monday, May 25, 2015

Date: Sheet of

Monday, May 25, 2015

Date: Sheet of

Monday, May 25, 2015

PROJECT :

CPU

CPU

CPU

1

AM9A

AM9A

AM9A

?

08

8 57

8 57

8 57

A0

A0

A0

5

4

3

2

1

09

SPT-H PCH (SPI) SPT-H PCH (DMI/PCIE/USB3/USB2)

SPI_CS0# for 1 st SPI device, SPI_CS1# for

D D

second SPI dev ice, SPI_CS3# f or TPM.

#546884 PDG (V 1.0) page 620

?

U14A

BD17

GPP_A11/PME#

AG15

TP23

TP19

TP28

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_CS0#

PCH_SPI_CLK

PCH_SPI_CS1#

PCH_SPI_IO2

PCH_SPI_IO3

CAP_LED

+3.3V_SUS

TP27

TP29

TP25

Connector Less Debug Hooks

Routing Guidel ines

#546884 PDG (V 1.0) page 505

PCH_SPI_SI27

PCH_SPI_SO27

PCH_SPI_CS0#27

PCH_SPI_CLK27

C C

B B

PCH_SPI_CS1#26,27

PCH_SPI_IO227

PCH_SPI_IO327

TP38

THSCR_EN29

CAP_LED31

3/11 KB_DET# move to P10

PCH_TP_INTR#

3/1 add P U 10K

PCH_SPI_IO3

3/2 add P D 100

1 2

R174 *100_4_NC

R148 10K_4

AG14

AF17

AE17

AR19

AN17

BB29

BE30

BD31

BC31

AW31

BC29

BD30

AT31

AN36

AL39

AN41

AN38

AH43

AG44

RSVD

RSVD

RSVD

RSVD

TP2

TP1

SPI0_MOSI

SPI0_MISO

SPI0_CS0#

SPI0_CLK

SPI0_CS1#

SPI0_IO2

SPI0_IO3

SPI0_CS2#

GPP_D1

GPP_D0

GPP_D3

GPP_D2

GPP_D22

GPP_D21

SPT_PCH_H/S KT

SPT-H_PCH

(Primary) (Primary)

1 OF 12

GPP_B13/PLTRST#

GPP_G16/GSXCLK

GPP_G12/GSXDOUT

GPP_G13/GSXSLOAD

GPP_G14/GSXDIN

GPP_G15/GSXSRESET#

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

GPP_H18/SML4ALERT#

GPP_H17/SML4DATA

GPP_H16/SML4CLK

GPP_H15/SML3ALERT#

GPP_H14/SML3DATA

GPP_H13/SML3CLK

GPP_H12/SML2ALERT#

GPP_H11/SML2DATA

GPP_H10/SML2CLK

INTRUDER#

REV = 1.3

LAN

WLAN

Card Reader

BB27

P43

R39

R36

R42

R41

AF41

AE44

BC23

BD24

BC36

BE34

BD39

BB36

BA35

BC35

BD35

AW35

BD34

BE11

?

PCI_PLTRST#

3/17 change name

R149 0_4

SML4ALERT#

SML4DATA

SML4CLK

SML3ALERT#

SML3DATA

SML3CLK

SML2ALERT#

SML2DATA

SML2CLK

SM_INTRUDER #

R210 *10K_4_NC

R419 *10K_4_NC

R217 *10K_4_NC R413 100/F_4

R205 *10K_4_NC

R199 *10K_4_NC

R196 *10K_4_NC

R423 *10K_4_NC

R192 *10K_4_NC

R188 *10K_4_NC

R406 1M_4

PDG P623->PU 1M ohm

CRB P102->PU 330K ohm

PCIE_RXN537

PCIE_RXP537

PCIE_TXN537

PCIE_TXP537

PCIE_RXN636

PCIE_RXP636

PCIE_TXN636

PCIE_TXP636

PCIE_RXN735

PCIE_RXP735

PCIE_TXN735

PCIE_TXP735

DMI_TXN03

DMI_TXP03

DMI_RXN03

DMI_RXP03

DMI_TXN13

DMI_TXP13

DMI_RXN13

DMI_RXP13

DMI_TXN23

DMI_TXP23

DMI_RXN23

DMI_RXP23

DMI_TXN33

DMI_TXP33

+3V_RTC

DMI_RXN33

DMI_RXP33

PCH_TP_INTR# 31

+3.3V_SUS

SMLINK[4:2] is for Server.

External pull-up resistor is

required???

PCH EDS V1.0 P247&248

#546884 PDG (V 1.2) page 224 D evice Down

move to device page

#546884 PDG (V 1.2) page 226 M ini-Card

move to device page

move to device page

PCIERCOMP_N

PCIERCOMP_P

PCIE_RXN5

PCIE_RXP5

PCIE_TXN5

PCIE_TXP5

PCIE_RXN6

PCIE_RXP6

PCIE_RXN7

PCIE_RXP7

PCIE_TXN7

PCIE_TXP7

DMI_TXN0

DMI_TXP0

DMI_RXN0

DMI_RXP0

DMI_TXN1

DMI_TXP1

DMI_RXN1

DMI_RXP1

DMI_TXN2

DMI_TXP2

DMI_RXN2

DMI_RXP2

DMI_TXN3

DMI_TXP3

DMI_RXN3

DMI_RXP3

PLTRST# Buffer

U14B

L27

DMI_RXN0

N27

DMI_RXP0

C27

DMI_TXN0

B27

DMI_TXP0

E24

DMI_RXN1

G24

DMI_RXP1

B28

DMI_TXN1

A28

DMI_TXP1

G27

DMI_RXN2

E26

DMI_RXP2

B29

DMI_TXN2

C29

DMI_TXP2

L29

DMI_RXN3

K29

DMI_RXP3

B30

DMI_TXN3

A30

DMI_TXP3

B18

PCIE_RCOMPN

C17

PCIE_RCOMPP

H15

PCIE1_RXN/USB3_7_RXN

G15

PCIE1_RXP/USB3_7_RXP

A16

PCIE1_TXN/USB3_7_TXN

B16

PCIE1_TXP/USB3_7_TXP

B19

PCIE2_TXN/USB3_8_TXN

C19

PCIE2_TXP/USB3_8_TXP

E17

PCIE2_RXN/USB3_8_RXN

G17

PCIE2_RXP/USB3_8_RXP

L17

PCIE3_RXN/USB3_9_RXN

K17

PCIE3_RXP/USB3_9_RXP

B20

PCIE3_TXN/USB3_9_TXN

C20

PCIE3_TXP/USB3_9_TXP

E20

PCIE4_RXN/USB3_10_RXN

G19

PCIE4_RXP/USB3_10_RXP

B21

PCIE4_TXN/USB3_10_TXN

A21

PCIE4_TXP/USB3_10_TXP

K19

PCIE5_RXN

L19

PCIE5_RXP

D22

PCIE5_TXN

C22

PCIE5_TXP

G22

PCIE6_RXN

E22

PCIE6_RXP

B22

PCIE6_TXN

A23

PCIE6_TXP

L22

PCIE7_RXN

K22

PCIE7_RXP

C23

PCIE7_TXN

B23

PCIE7_TXP

K24

PCIE8_RXN

L24

PCIE8_RXP

C24

PCIE8_TXN

B24

PCIE8_TXP

SPT_PCH_H/S KT

SPT-H_PCH

DMI

PCIe/USB 3

2 OF 12

USB 2.0

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_F15/USB2_OC4#

GPP_F16/USB2_OC5#

GPP_F17/USB2_OC6#

GPP_F18/USB2_OC7#

USB2_VBUSSENSE

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2N_11

USB2P_11

USB2N_12

USB2P_12

USB2N_13

USB2P_13

USB2N_14

USB2P_14

USB2_COMP

RSVD_AB13

USB2_ID

GPD7/RSVD

?

REV = 1.3

AF5

AG7

AD5

AD7

AG8

AG10

AE1

AE2

AC2

AC3

AF2

AF3

AB3

AB2

AL8

AL7

AA1

AA2

AJ8

AJ7

W2

W3

AD3

AD2

V2

V1

AJ11

AJ13

AD43

AD42

AD39

AC44

Y43

Y41

W44

W43

AG3

AD10

AB13

AG2

BD14

USB2_N1

USB2_P1

USB2_N2

USB2_P2

USB2_N3

USB2_P3

USB2_N4

USB2_P4

USB2_N5

USB2_P5

USB2_N6

USB2_P6

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

USB_OC4#

USB_OC5#

USB_OC6#

USB_OC7#

USBCOMP

TP22

USB2_N1 34

USB2_P1 34

USB2_N2 38

USB2_P2 38

USB2_N3 38

USB2_P3 38

USB2_N4 29

USB2_P4 29

USB2_N5 36

USB2_P5 36

USB2_N6 29

USB2_P6 29

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

USB_OC4#

USB_OC5#

USB_OC6#

USB_OC7#

USB_OC0# 34

USB_OC1# 38

Place near Pin

R382 113/F_4

R120 1K_4

R361 0_4

If this signal is not in use, then it

should have a 1k PD to ground .

#546717 EDS (V 1.2) page 288

2/3 add R896,R 897

USB3.0 Conn/MB(PS)

USB3.0 Conn / DB

USB3.0 Conn / DB

Camera

BT

Touch Screen

2

RP13 10KX2

RP12 10KX2

RP11 10KX2

RP10 10KX2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

+3.3V_SUS

PCI_PLTRST#

A A

5

1 2

R165 *SH ORT_4_NC

PLTRST#

R166

100K_4

PLTRST# 17,26,28,35,36,37

4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size D ocument Number Rev

Size D ocument Number Rev

Size D ocument Number Rev

Date: Sheet of

Monday, May 25, 2015

Date: Sheet of

Monday, May 25, 2015

Date: Sheet of

3

2

Monday, May 25, 2015

PROJECT :

PCH

PCH

PCH

AM9A

AM9A

AM9A

A0

A0

9 5 7

9 5 7

1

9 5 7

A0

5

+3.3V_RU N

DCR_EN

2/25 modif y

KB_DET#

D D

SSD

R428 1 0K_4

+3.3V_S US

R429 1 0K_4

KB_LED _DET31

KB_DET#31

DCR_EN29

BT_RADIO_ DIS#36

WLAN_ ON/OFF#36

#546884 PDG (V1.2) page 396 NGFF

2/3 Remove to conn page

PCIE_TXP 1128

PCIE_TXN1 128

PCIE_RX P1128

PCIE_RX N1128

iAMT used.

WLAN_ ON/OFF#

KB_DET#

DCR_EN

3/10 change PCIE port

SATA_TXN028

HDD

C C

SSD

SATA_TXP028

SATA_RXN 028

SATA_RXP 028

PCIE_TXP 1228

PCIE_TXN1 228

PCIE_RX P1228

PCIE_RX N1228

SATA_TXN0

SATA_TXP0

SATA_RXN 0

SATA_RXP 0

PCIE_RX P12

PCIE_RX N12

2/3 Remove to conn page

SPT-H PCH (PCIE/SATA/FAN/CLINK) SPT-H PCH (AUDIO/SMBus/JTAG)

?

U14C

AV2

CL_CLK

AV3

CL_DATA

AW2

CL_RST#

R44

GPP_G8/FAN_PWM_0

R43

GPP_G9/FAN_PWM_1

U39

GPP_G10/FAN_PWM_2

N42

GPP_G11/FAN_PWM_3

U43

GPP_G0/FAN_TACH_0

U42

GPP_G1/FAN_TACH_1

U41

GPP_G2/FAN_TACH_2

M44

GPP_G3/FAN_TACH_3

U36

GPP_G4/FAN_TACH_4

P44

GPP_G5/FAN_TACH_5

T45

GPP_G6/FAN_TACH_6

T44

GPP_G7/FAN_TACH_7

B33

PCIE11_TXP

C33

PCIE11_TXN

K31

PCIE11_RXP

L31

PCIE11_RXN

AB33

GPP_F10/SCLOCK

AB35

GPP_F11/SLOAD

AA44

GPP_F13/SDATAOUT0

AA45

GPP_F12/SDATAOUT1

B38

PCIE14_TXN/SATA1B_TXN

C38

PCIE14_TXP/SATA1B_TXP

D39

PCIE14_RXN/SATA1B_RXN

E37

PCIE14_RXP/SATA1B_RXP

C36

PCIE13_TXN/SATA0B_TXN

B36

PCIE13_TXP/SATA0B_TXP

G35

PCIE13_RXN/SATA0B_RXN

E35

PCIE13_RXP/SATA0B_RXP

A35

PCIE12_TXP

B35

PCIE12_TXN

H33

PCIE12_RXP

G33

PCIE12_RXN

J45

PCIE20_TXP/SATA7_TXP

K44

PCIE20_TXN/SATA7_TXN

N38

PCIE20_RXP/SATA7_RXP

N39

PCIE20_RXN/SATA7_RXN

H44

PCIE19_TXP/SATA6_TXP

H43

PCIE19_TXN/SATA6_TXN

L39

PCIE19_RXP/SATA6_RXP

L37

PCIE19_RXN/SATA6_RXN

SPT_PCH_ H/SKT

(Primary)

SPT-H_PCH

CLINK

FAN

3 OF 12

Leakage Isolation

+3.3V_S US

+3.3V_RU N+3.3V_S US +3 .3V_SUS

2

2

B B

SMB_ME1 _DAT

PCH STRAPING

A A

Pin Name Usage

SPKR / GPP_B14

SMBALERT# / GPP_C2