Page 1

5

4

3

2

1

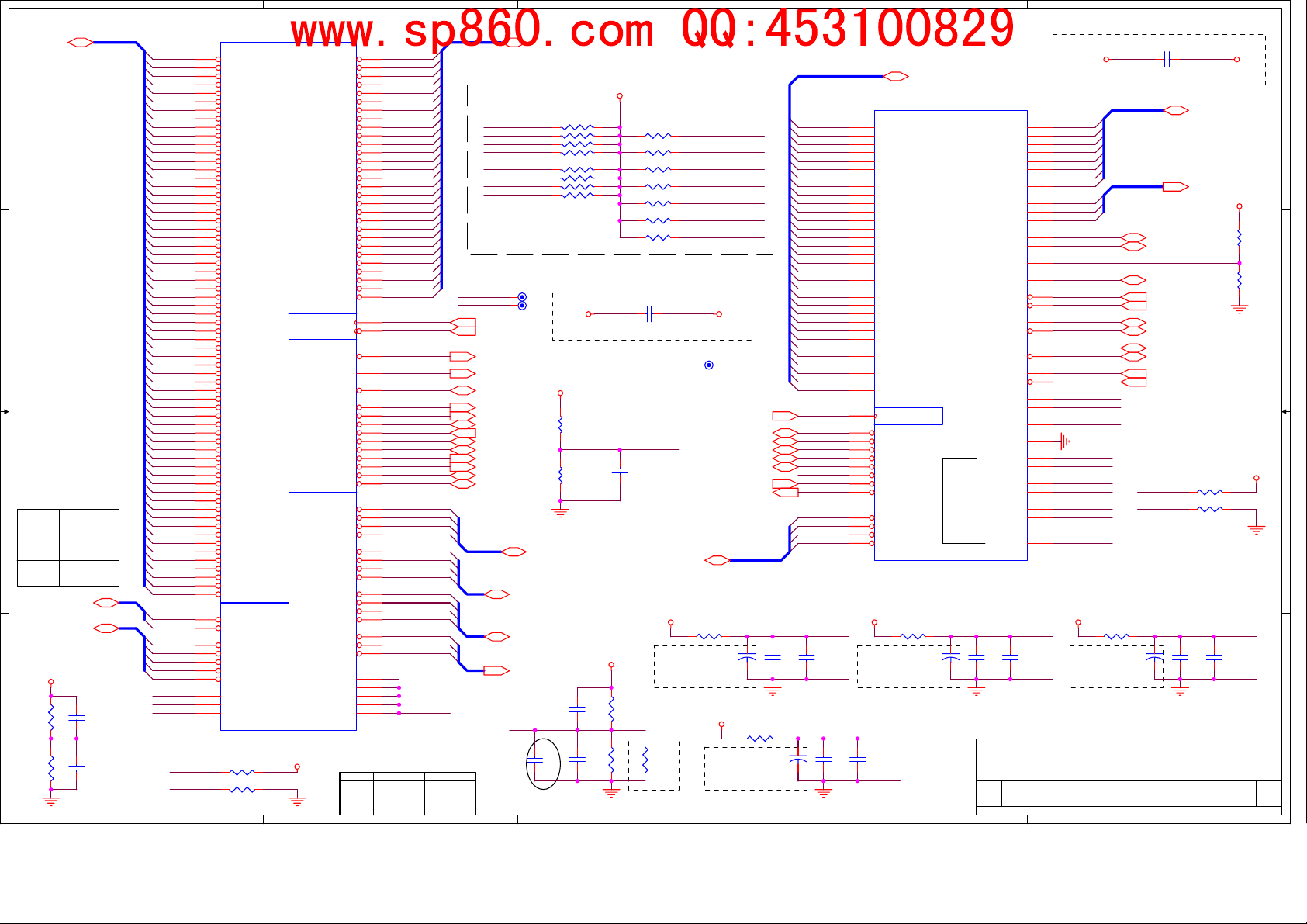

CPU

755SA1

A-PDF Watermark DEMO: Purchase from www.A-PDF.com to remove the watermarkA-PDF Watermark DEMO: Purchase from www.A-PDF.com to remove the watermarkA-PDF Watermark DEMO: Purchase from www.A-PDF.com to remove the watermark

www.sp860.com QQ:453100829

100/133/200MHZ

CPUCLK

CPUCLK#

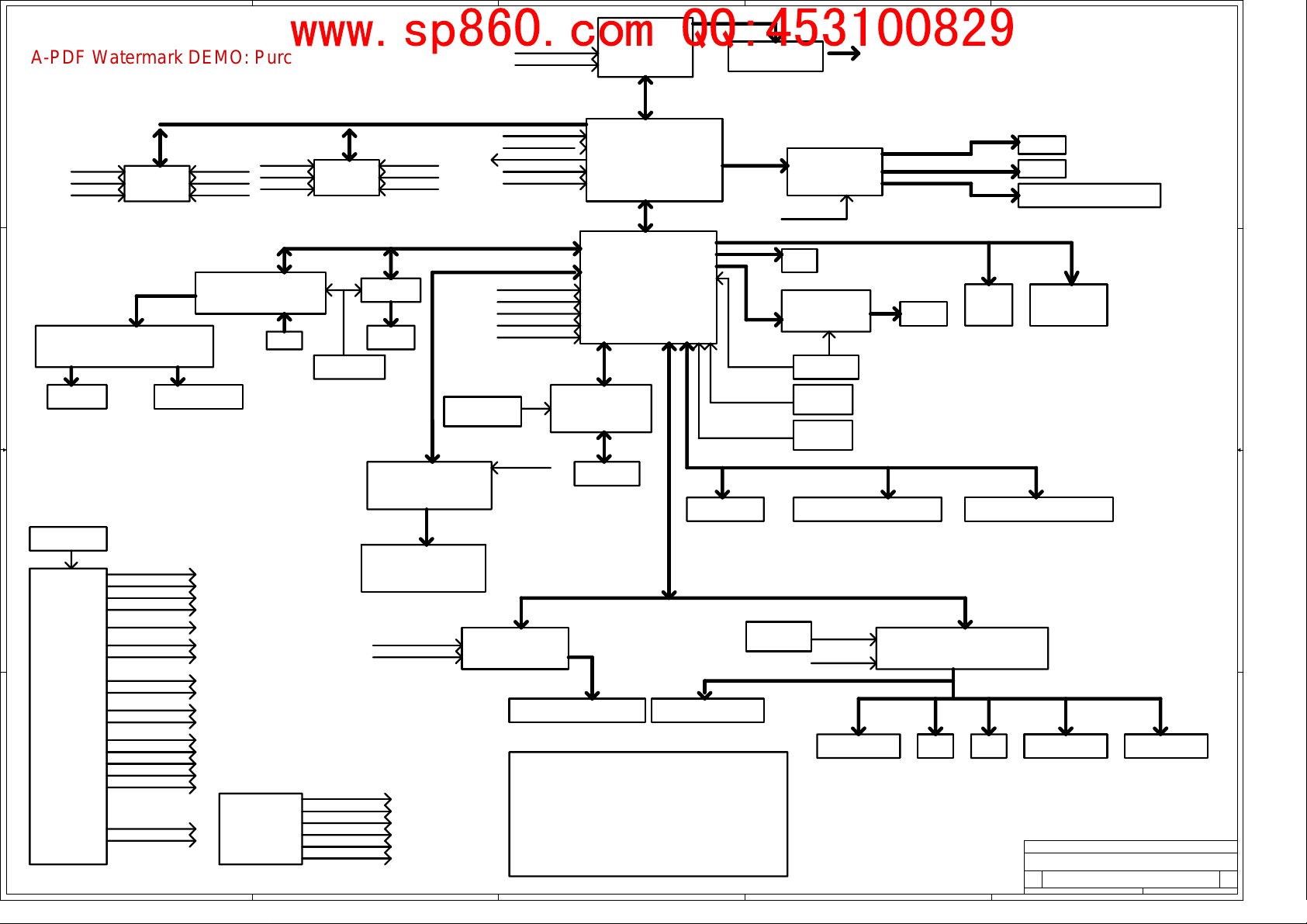

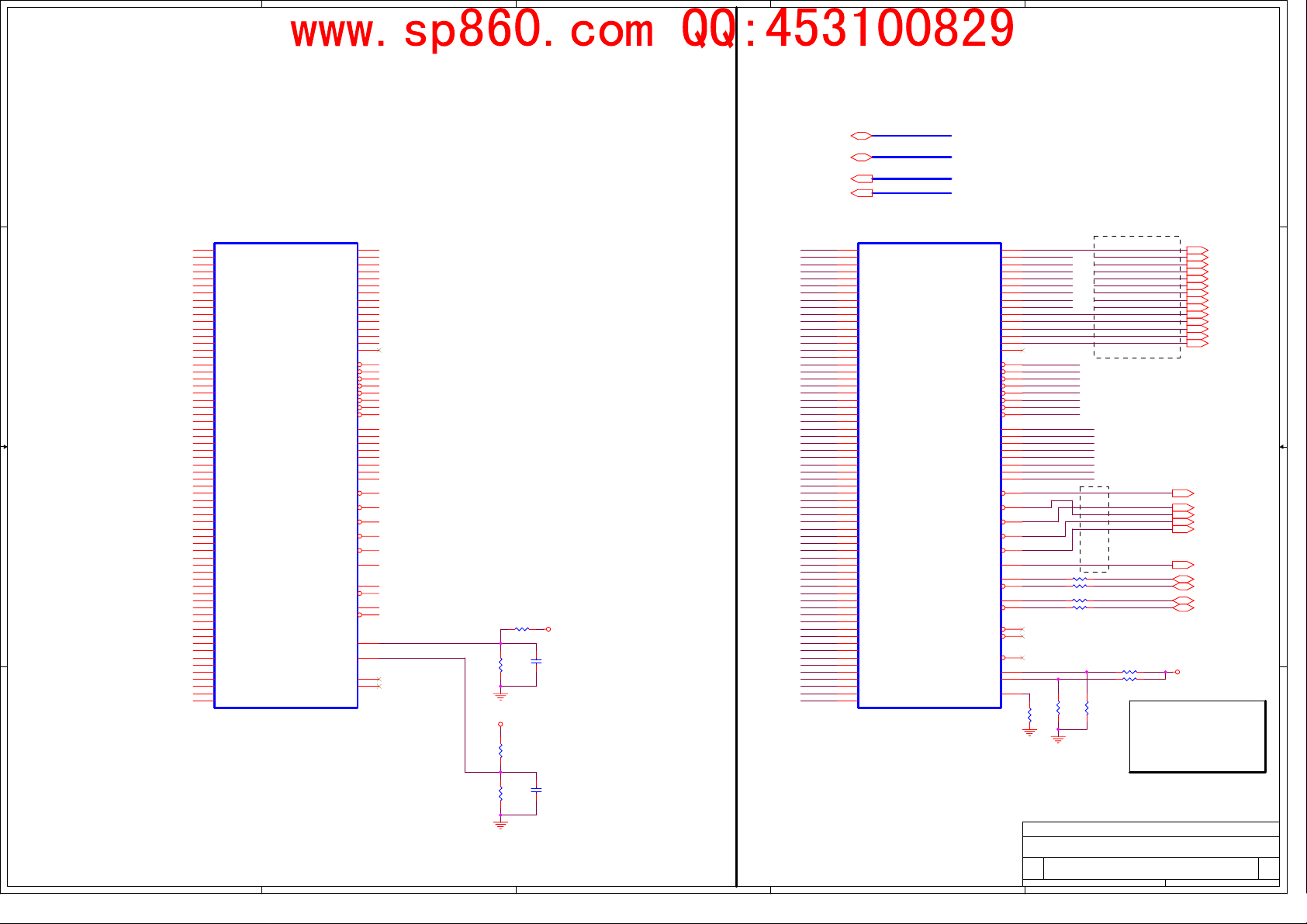

BLOCK DIAGRAM

Pentium 4

Socket 478

Vcore

Page 3

THERMAL

ADM1032

+3V

EC

Page 3

HOST BUS

D D

755SA1 P/N:

DDRCLK0

DDRCLK1

DDRCLK2

DDR 2

+2.5V

+1.25V terminal

Page 9

AUDIO CODEC

C C

B B

Clock Gen

A A

AMPLIFIER

INTERNAL

SPK

Page 24

CRYSTAL

14.318MHz

ICS

ICS952005

+3V

Page 5

NS

LM4835

CPUCLK

CPUCLK#

SIS648CLK

SIS648CLK#

FWSDCLK

AGPCLK 66MHZ

AGPCLK1 66MHZ

648ZCLK 133MHZ

963ZCLK 133MHZ

USB-48MHZ

393-48MHZ

963PCICLK 33MHZ

PCLK_CB 33MHZ

PCLK_M 33MHZ

LPC_CLK 33MHZ

PCLK_EC 33MHZ

963REF1 14.318MHZ

963REF3 33MHZ

5

+5V

Page 24

PHONE JACK

* 2

100/133/166MHZ

DDRCLK0#

DDRCLK1#

DDRCLK2#

VT1612A

Page 25

100/133MHZ

Clock Buf

ICS93722

+3V

DDRCLK0

DDRCLK1

DDRCLK2

ICS

+3V

MIC

Page 25

+2.5V

Page 5

DDR 1

+2.5V

+1.25V terminal

+5V

Page 23

CRYSTAL

24.576M HZ

DDRCLK0

DDRCLK0#

DDRCLK1

DDRCLK1#

DDRCLK2

DDRCLK2#

DDR RAM BUS

100/133/200MHZ

DDRCLK0#

DDRCLK1#

DDRCLK2#

Page 9

AC Link

+5V

+3V

MDC

Page 27

RJ45/11

CRYSTAL

24.576M HZ

TI1410

+12V

+5V

+3V

Page 22

68PIN-CONN

393-48MHZ

LPC_CLK_33MHZ

100/133/166MHZ

4

SIS648CLK

SIS648CLK#

FWSDCLKO

AGPCLK 66MHZ

648ZCLK 66/133MHZ

PCI BUS

963ZCLK 66/133MHZ

963PCICLK 33MHZ

USB-48MHZ

963REF1 14.318MHZ

963REF3 33MHZ

IEEE-1394

PCLK_CB 33MHZ

+3V

LPC

PC87383

Page 29

Parallel

Power Switch CONN & AC_IN.......Page 30

Vcore......Page 32

+2.5V,+1.5V,+1.25V.......Page 33

+1.8V.......Page 34

+3V,+5V.......Page 35

North Bridge

VDDQ

SIS

648(FX)

+3V

+2.5V

+1.8V

+1.5V

HyperZip BUS

South Bridge

Vcore

+3V

+1.8V

TSB43AB22

SIS

963

Page 18

+3V

Page 26

1394 CONN

FLASH ROM

3

AGP

Page 6

USB1-3

Page 28

LPC BUS

+5V

ATI M9+C

AGPCLK1 66MHZ

RTC

LAN(PHY)

CRYSTAL

CRYSTAL

32.768K

CRYSTAL

12M HZ

CARD READER

CRYSTAL

32.768K

PCLK_EC 33MHZ

+5V

+2.5V

+3V

+1.5V

Page 11

+3V

REALTEK

RTL8201BL

Page 27

25M HZ

INT K/B

IDE

HDD

RJ45/11

+5V

2.5"

+5V

PRIMARY

MASTER

WIRELESS CONN

Page 28

K/B CONTROLLER

2

PC97551

T/P

Page 30

NS

+5V

FAN

Page 25

Page 16

CRT

Page 17

LCD

S-Video TV

Page 16

Page 21

CD-ROM

SECONDARY

MASTER

+3V

Page 31

CHARGER

Title

Size Document Number Rev

Date: Sheet of

+5V

Page 28

BATTERY

Page 36

Unwill International Corp.

755SA1

2410

SYSTEM BLOCK DIAGRAM

1

Page 36

138Monday, December 08, 2003

A

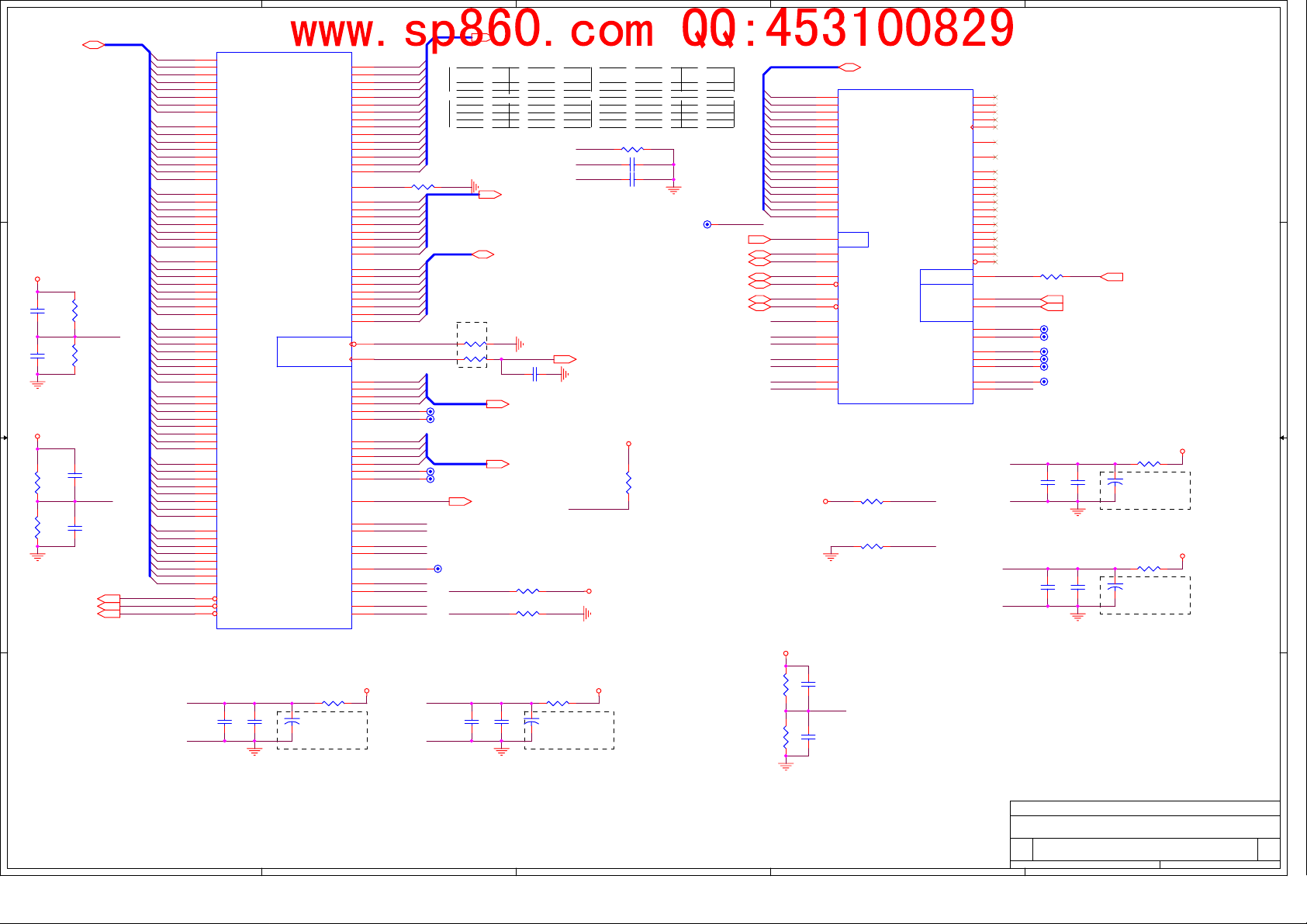

Page 2

5

4

3

2

1

RA to RB

Modify 1 : Change R371 to 3.48k_1 for +1.8V

Modify 2 : Remove C392 for +1.8V Power ON Sequence

Modify 3 : Modify for Schematic Error

Modify 4 : Change R414 to 0 ohm for +3v_ON Voltage Level

Modify 5 : Modify for Schematic Error

Modify 6 : Add 2200P for Switching Power Quality

Modify 7 : Change PR12 to 0 ohm for EC Voltage Level

D D

Modify 8 : Modify R524 Connect to VCC_AMP for VR1

Modify 9 : Modify Schematic for S3 Power Sequence

Modify 10 : Add C660 for 648 Request

Modify 11 : Reserve C655,C656,C657,C658,C659,C661,C662 for 648 Request

Modify 12 : Add R830 470 ohm for HVREF

Modify 13 : Change PR2,PR4,PR6,PR8 for Total Power Accuracy

Modify 14 : Add R831 for CMOS Discharge Safety

Modify 15 : Remove 0 ohm for Software Bug

Modify 16 : Change Wireless CONN Pin Define for Design Issue

Modify 17 : Remove R for VRAM On Board

Modify 18 : Add 0 ohm for CPU Power Current Return Path

Modify 19 : Add Schematic and modify R557,R556 value for SPK volume

Modify 20 : Add Schematic for EC to select CPU frequency

Modify 21 : Add R839,R840 and DDR memory capacitance for DDR stability

Modify 22 : Add bypass capacitance for difference power plane

Modify 23 : Add capacitance for sis648 system stability

Modify 24 : Add capacitance for VGA system stability

Modify 25 : Add MEM_ID select for VRAM on Board

Modify 26 : Add for EC SMP fuction

Modify 27 : Improve Audio Signal Quality

C C

Modify 28 : Add schematic for audio

Modify 29 : Modify for EMI

www.sp860.com QQ:453100829

B B

A A

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

Unwill International Corp.

755SA1

2410

REVISION HISTORY

238Monday, December 08, 2003

1

A

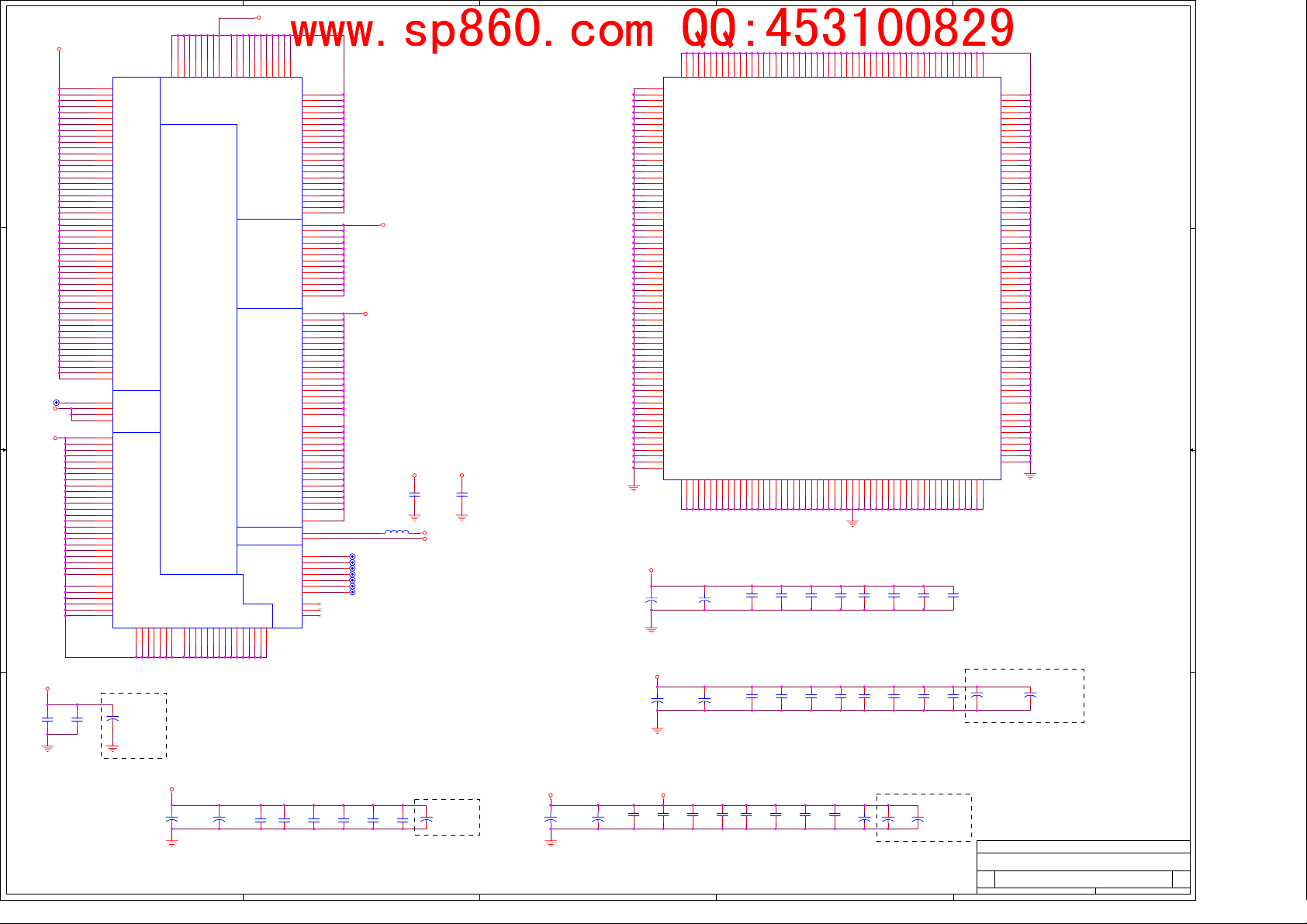

Page 3

5

www.sp860.com QQ:453100829

HA#[3..31]6

RS#[0..2]6

ADS#

TP50

D D

IERR#

TP48

FERR#18

STPCLK#4,18

TP43

TP40

DBSY#6

DRDY#6

HTRDY#6

HLOCK#6

BREQ0#6

DEFER#6

PROCHOT#

CPU_GHI#

IGNNE#18

CPUSLP#18

CPUPWRGD6

CPURST#6

C C

B B

A A

Z0312

FERR#

STPCLK#

Z0313

INIT#

INIT#18

Z0314

ADS#6

BREQ0#

BNR#6

HIT#6

HITM#6

BPRI#6

HTCK

HTDI

HTMS

HTRST#

HTDO

PROCHOT#

IGNNE#

SMI#

SMI#18

A20M#

A20M#18

CPUSLP#

CPUPWRGD

CPURST#

TEST_GROUP0

TEST_GROUP1

TEST_GROUP2

R117 0

HD#[0..63]6

THERMDA Z0321Z0320

THERMDC

ADS#

GHI#

DPSLP#

BPM#2

BPM#3

BPM#4

BPM#5

R122 0

R121 0

5

+3V

AC3

V6

B6

Y4

AA3

W5

AB2

H5

H2

J6

G1

G4

H6

G2

F3

E3

D2

E2

D4

C1

F7

E6

D5

C3

B2

B5

C6

AB26

AB23

AB25

AD24

AA2

AC21

AC20

AC24

AC23

AA20

AB22

U6

W4

Y3

A6

AD25

AC6

AB5

AC4

Y6

AA5

AB4

R393 200

C404

1000P

IERR

MCERR

FERR

STPCLK

BINIT

INIT

RSP

DBSY

DRDY

TRDY

ADS

LOCK

BRO

BNR

HIT

HITM

BPR

DEFER

TCK

TDI

TMS

TRST

TDO

PROCHOT

IGNNE

SMI

A20M

SLP

PWRGOOD

RESET

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TESTHI9

TESTHI10

TESTHI11

TESTHI12

BPM0

BPM1

BPM2

BPM3

BPM4

BPM5

HD0

HD1

HD2

B21

B22

A23

HD#0

HD#2

HD#1

TP16

TP17

C407

2.2U_X5R

HD3

A25

HD#3

RS#1

RS#0

F1G5F4

RS0

HD4

C21

D22

HD#4

HD#5

RS1

HD5

RS#2

RS2

HD6

B24

HD#6

HD7

C23

C24

HD#8

HD#7

CPUCLK#

CPUCLK

Z0316

Z0317

Z0318

HD8

HA#3

HA3

HD9

B25

HD#9

HA#4

HA4

HD10

G22

HD#10

HA#11

HA#10

HA#5

HA5

HD11

H21

HD#11

1

2

3

4

SMBus Address is 0x4C

ADM1032 or MAX6692 or LM86

HA#12

HA#7

HA#9

HA#6

HA#8

HA9

HA8

HA7

HA6

HA11

HA10

HD12

HD13

HD14

HD15

HD16

HD17

C26

D23

J21

D25

H22

E24

G23

HD#12

HD#14

HD#13

HD#18

HD#15

HD#17

HD#16

U41

SMBCLK

VCC

SMBDATA

D+

D-

ALERT#

THERM#

MAX6692/ADM1032

HA#13

HA12

HD18

F23

HD#19

GND

HA#14

HA13

HD19

F24

HD#20

HA14

HD20

HA#15

HA#16

HA15

HD21

E25

HD#22

HD#21

8

7

6

5

F26

HA#17

HA16

HD22

D26

HD#23

HA#18

HA17

HD23

L21

HD#24

HA#19

HA18

HD24

G26

HD#25

HA19

HD25

H24

HD#26 HA#20

4

HA#21

HA20

HD26

M21

HD#27

4

HA#22

HA21

HD27

L22

HD#28

HA#23

HA22

HD28

J24

HD#29

HA#24

HA23

HD29

K23

HD#30

HA#25

HA24

HD30

H25

HD#31

HA#26

HA25

HD31

M23

HD#32

HA#27

HA26

HD32

N22

HD#33

HA#28

HA28

HA27

HD33

HD34

P21

HD#34

TP47

HA#29

M24

HD#35

HA#30

HA29

HD35

N23

HD#36

TP45

HA#31

HA30

HD36

M26

HD#37

Z0301

HA32

HA31

HD37

HD38

N26

HD#38

TP44

Z0302

Z0303

HA33

HD39

N25

HD#39

TP42

Z0304

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

HA34

HD40

R21

P24

HD#40

HD#41

HA35

HD41

R25

HD#42

HD42

R24

HD#43

AF4

HD43

T26

HD#44

Z0305

AF3

VCCVID

HD44

T25

HD#45

30mil

R37

4.7K_OP

ITP_CLK

ITP_CLK#

TP39

AC26

AD26

ITP_CLK0

ITP_CLK1

VCCVIDPRG

HD45

HD46

HD47

HD48

T22

T23

U26

U24

HD#46

HD#47

HD#48

HD#49

TP46

Z0306

AC1

HD49

U23

HD#50

Z0307

V5

AP0

HD50

V25

HD#51

+1.2V

AP1

HD51

U21

HD#52

TP3

Z0308

J26

DEP0

HD52

HD53

V22

HD#53

Z0309

K25

DEP1

HD54

V24

HD#54

Z0310

Z0311

K26

DEP2

HD55

W26

HD#55

HD#56

L25

DEP3

HD56

Y26

HD57

W25

HD#58

HD#57

AE5

Y23

3

AE4

AE3

AE2

VID0

VID1

VID2

VID3

VIDPWRGD

COMP0

COMP1

ADSTB0

ADSTB1

DBRESET

THERMDA

THERMDC

THERMTRIP

VCC_SENSE

VSS_SENSE

HD58

HD59

HD60

HD61

Y24

Y21

AA25

HD#61

HD#59

HD#60

AE1

VID4

BCLK0

BCLK1

LINT0

LINT1

STBP0

STBP1

STBP2

STBP3

STBN0

STBN1

STBN2

STBN3

DB#0

DB#1

DB#2

DB#3

REQ0

REQ1

REQ2

REQ3

REQ4

BSEL0

BSEL1

HD62

HD63

AA22

AA24

SOCKET478

HD#62

HD#63

TP2

TP1

TP49

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

U10A

AD2

AF22

AF23

L24

P1

D1

E5

L5

R5

AE25

F21

J23

P23

W23

E22

K22

R22

W22

E21

G25

P26

V21

J1

K5

J4

J3

H3

B3

C4

A2

AD6

AD5

A5

A4

Z0315

CPUCLK

CPUCLK#

CPUCOM0

CPUCOM#0

INTR

NMI

HASTB#0

HASTB#1

DBRESET

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

DBI#0

DBI#1

DBI#2

DBI#3

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

THERMDA

THERMDC

BSEL1

Z0322

Z0323

BSEL0

CPU HOT THROTTLING/SHUT DOWN PROTECT CIRCUIT

CPU_CORE

R159

FAN_SMBCLK 5,31

FAN_SMBDATA 5,31

PROCHOT# Z0319

R126 1K

3

4.7K

Q13

2N3904

CPU_VID0 32

CPU_VID1 32

CPU_VID2 32

CPU_VID3 32

CPU_VID4 32

R38 4.7K_OP

+3V

R833

1K

R834 0

R160 0

CPUCLK 5

CPUCLK# 5

INTR 18

NMI 18

HASTB#[0..1] 6

HDSTBP#[0..3] 6

HDSTBN#[0..3] 6

DBI#[0..3] 6

HREQ#[0..4] 6

THERMTRIP# 18

BSEL0

Z0324

C178

1U_10V

+1.25V +1.2V

+1.2V

TP37

TP5

TP4

Q46

2N7002

Q14

2N3904

BSEL0

BSEL1

HTCK

HTRST#

CPUCOM0

CPUCOM#0

FSB_SEL Function

L 133MHz

H 100MHz

2

R390 1K

R42 1K_OP

R125 27

R113 680

R92 61.9_1

R104 61.9_1

BSEL1 BSEL0 Function

L L 100MHz

L Hi-Z 133MHz

H L RSVD

H H RSVD

PM_CPU_STP#5,19

Modify 20

Reserve for Smart Power

FSB_SEL 31

SMART_C231

SMART_SLP31

SMART_C331

1632_OFF# 30,35

2

1

CPU_CORE

FERR#

R115 61.9_1

BREQ0#

R106 51.1_1

PROCHOT#

R127 61.9_1

+3V

Title

Size Document Number Rev

Date: Sheet of

CPUPWRGD

R68 51.1_1

THERMTRIP#

R123 61.9_1

R114 56.2_1

A20M#

R70 56.2_1

STPCLK#

R23 56.2_1

CPUSLP#

SMI#

R118 56.2_1

INIT#

R94 56.2_1

IGNNE#

R124 56.2_1

INTR

R107 56.2_1

NMI

R119 56.2_1

HTMS

R112 39

R27 150_1

DBRESET

CPURST#

R63 51.1_1

HTDO

R120 75_1

HTDI

R105 150_1

ITP_CLK

R24 1K

ITP_CLK#

R25 1K

BPM#3

R49

BPM#4

R50

BPM#2

R51

BPM#5

DPSLP#

GHI#

R54

R40

R31

R41

R26

R116

STPCLK#

BAT54_OPD3

CPUSLP#

BAT54_OPD4

DPSLP#

BAT54_OPD2

TEST_GROUP0

TEST_GROUP1

TEST_GROUP2

BAT54

D13

Unwill International Corp.

755SA1

2410

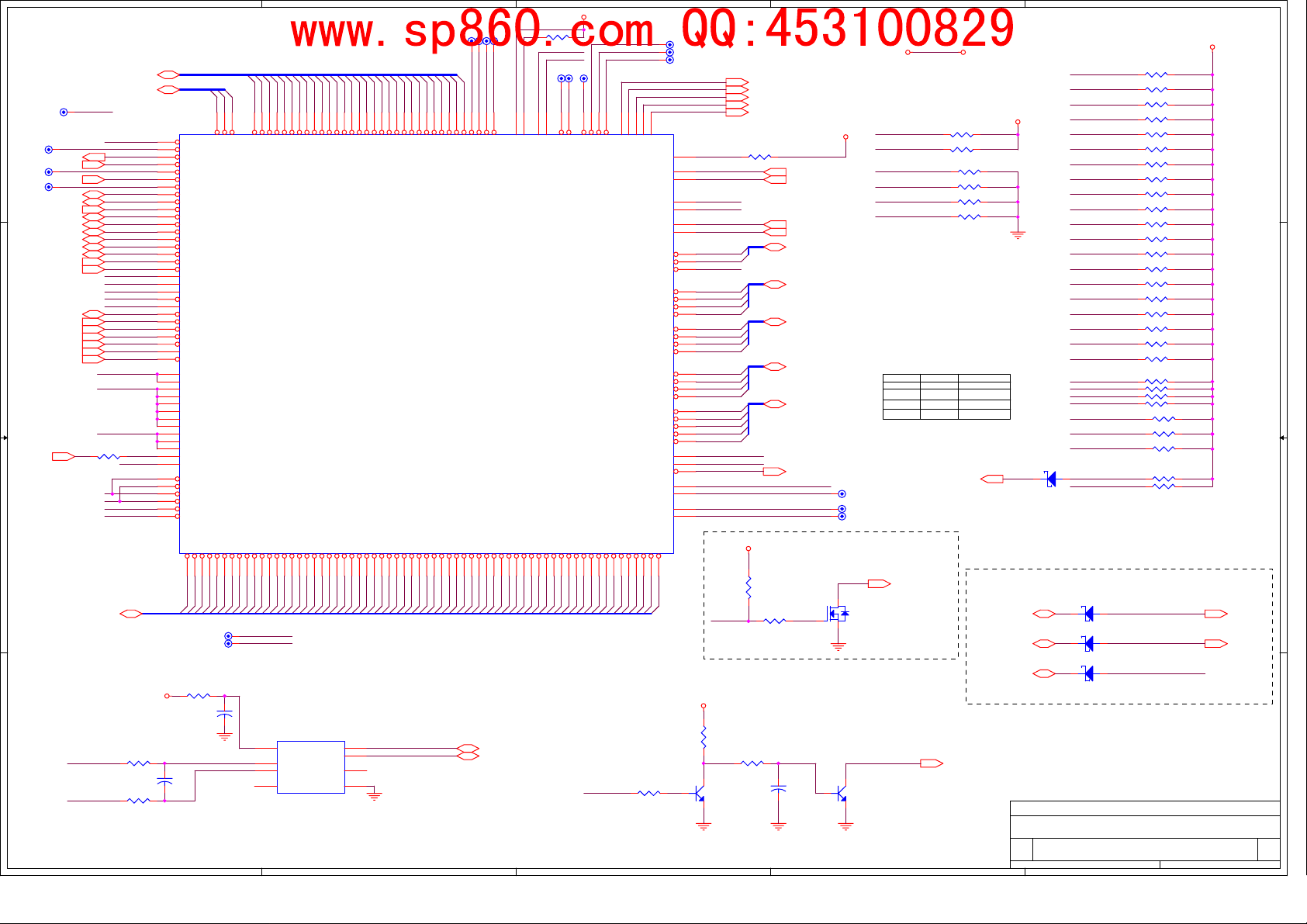

P4 CPU1(Host)

1

61.9_1

61.9_1

61.9_1

61.9_1

61.9_1

61.9_1

61.9_1

61.9_1

61.9_1

STPCLK# 4,18

CPUSLP# 18

338Monday, December 08, 2003

A

Page 4

5

4

3

2

1

www.sp860.com QQ:453100829

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

D D

C C

B B

A A

C25

VSS

C5

VSS

C7

VSS

C9

VSS

D10

VSS

D12

VSS

D14

VSS

D16

VSS

D18

VSS

D20

VSS

D21

VSS

D24

VSS

D3

VSS

D6

VSS

D8

VSS

E1

VSS

C22

VSS

E11

VSS

E13

VSS

E15

VSS

E17

VSS

E19

VSS

E23

VSS

E26

VSS

E4

VSS

E7

VSS

E9

VSS

F10

VSS

F12

VSS

F14

VSS

F16

VSS

F18

VSS

F2

VSS

F22

VSS

F25

VSS

F5

VSS

F8

VSS

G21

VSS

G24

VSS

G3

VSS

R23

VSS

R1

VSS

P5

VSS

P25

VSS

P22

VSS

R26

VSS

P2

VSS

+3V

U47

53

74AHC14_1G

2 4

1

VCC

VCC

VSS

VSS

H1H4H23

BAT_THROT_EN31

VCC

VSS

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H26

A11

A13

A15

A17

A19

A21

A24

A26A3A9

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

Q35

Z0406

Z0405

R453 1K

+3V

AC_IN30,31,35

SUS_CLK

Z0409

5

R446

33K_1

C447

680P

Q33

2N7002

Z0408

Modify 5

Q34

2N7002

Q36

Z0407

BAT54D41

VCC

VSS

AB14

AB16

2N7002

2N7002

VCC

VSS

VCC

VSS

AB18

VCC

VSS

AB20

AE10

VCC

VCC

VSS

VSS

AB21

AB24

AB3

STPCLK# 3,18

VCC

VSS

AE12

VCC

VSS

AB6

AE14

VCC

VSS

AB8

AE16

VCC

VSS

AC11

AE18

VCC

VSS

AC13

4

CPU_CORE

AE20

AE6

VCC

VCC

VSS

VSS

AC15

AC17

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

AD10

AD12

Z0402

For Prescoot Processor Use

R39

0

R832 0

AF9

VCC

VSS

AD14

B11

VCC

VSS

AD16

B13

VCC

VSS

AD18

B15

VCC

VSS

AD21

B17

VCC

VSS

AD23

B19B7B9

VCC

VCC

VSS

VSS

AD4

AD8

VCC

VSS

AE11

C10

VCC

VSS

AE13

C12

VCC

VSS

AE15

C14

C16

C18

C20C8D11

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

AE17

AE19

AE22

AE24

Z0403

R841 0

D13

VCC

VCC

VCC

VSS

VSS

VSS

AE26

AE7

AE9

CPU_CORE

D15

D17

D19D7D9

VCC

VCC

VCC

VSS

VSS

VSS

AF1

AF10

AF12

R35

49.9_1_OP

R36

0_OP

Modify 18

VCC

VSS

AF14

VCC

VSS

AF16

3

E10

VCC

VSS

AF18

E12

VCC

VSS

AF20

TP38

E14

AF26

Z0404

E16

E18

VCC

VCC

VCC

SKTOCC#

VSS

VSS

AF6

AF8

E20E8F11

VCC

VCC

VSS

VSS

B10

B12

C66

C59

220P

220P

VCCIOPLL

VCCA

VSSA

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C17

C19

C2

U10B

AE23

AD20

AD22

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

R4

G6

J2

J22

J25

J5

K21

K24

K3

K6

L1

L23

L26

L4

M2

M22

M25

M5

N21

N24

N3

N6

SOCKET478

CPU_CORE

AA21

AA6

F20

F19

VCC

VSS

B23

F9

VCC

VSS

B26B4B8

GTLREF0

VSS

VSS

GTLREF1

GTLREF2

VSS

VSS

C11

C13

F6

GTLREF3

VSS

C15

F13

F15

F17

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

B14

B16

B18

B20

2

C77

220P

C45

4.7U_10V_0805

CPUGTLVREFA

CPUGTLVREFB

C72

CLOSE CPU

220P

VCCIOPLL

VCCA_CPU

VSS_CPU

C89

4.7U_10V_0805

C101

4.7U_10V_0805

C84

1U_10V

C103

0.1u

R32 QT1608RL120

R33 QT1608RL120

C46

4.7U_10V_0805

CPU_CORE

Modify 3

CPU_CORECPU_CORE

R61

49.9_1

CPUGTLVREFACPUGTLVREFB

2/3VCORE2/3VCORE

C73

R67

1U_10V

100_1

C50

4.7U_10V_0805

C137

4.7U_10V_0805

C105

C104

1U_10V

1U_10V

C102

C86

0.1u

0.1u

Title

Size Document Number Rev

2410

Date: Sheet of

R52

49.9_1

R48

C63

100_1

1U_10V

C47

4.7U_10V_0805

C134

4.7U_10V_0805

C85

1U_10V

C87

0.1u

C131

1U_10V

C49

4.7U_10V_0805

C135

4.7U_10V_0805

C96

1U_10V

C97

1U_10V

C48

4.7U_10V_0805

C90

4.7U_10V_0805

C132

1U_10V

Unwill International Corp.

755SA1

P4 CPU2(Power)

1

C100

4.7U_10V_0805

C136

4.7U_10V_0805

C52

0.1u

438Monday, December 08, 2003

C51

0.1u

A

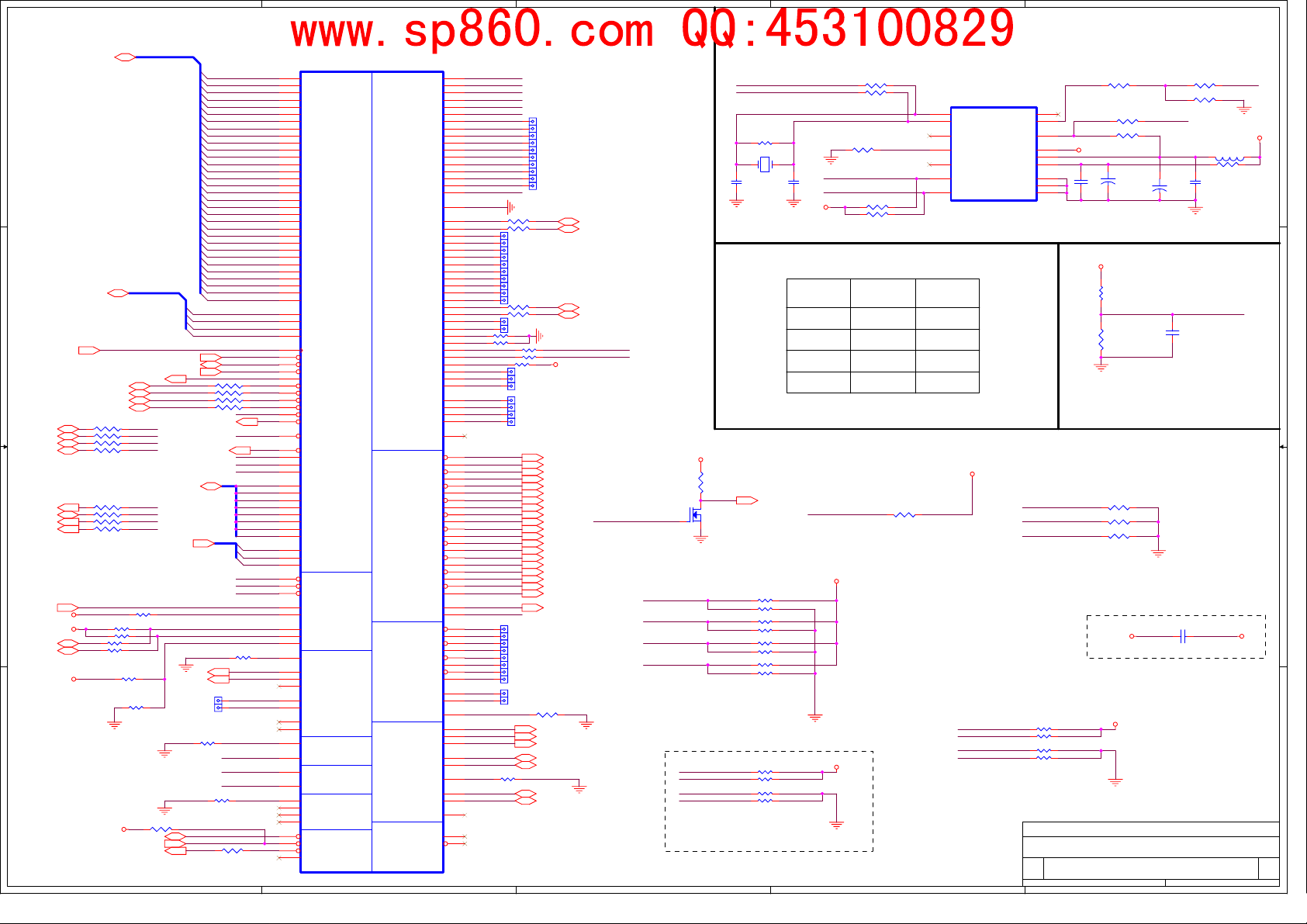

Page 5

5

4

3

2

1

www.sp860.com QQ:453100829

Main Clock Generator

C291

0.1u

+3V_VDDA

C273

0.1u

C292

0.1u

+3V

B57

D D

QT2012RL030HC_3A_0805

+

4.7U_10V_0805

C297

C296

+

4.7U_10V_0805

C249

0.1u

+3V+3V

0.1u

0.1u

C290

0.1u

0.1u

C248

C256

C247

Modify 15

R312

10K

FOR CYPRESS

FS0

FS1

FS2

FS3

FS4

R227 0

R228

R211

R212

R336

0_OP

0

0

0

CPU_CORE

R340

Z0503 Z0506

Q20

2N3904_OP

10K

C C

Frequency

Selection

+3V

R287 2.7K_OP

2.7K_OP

R309

R310 2.7K_OP

R311 2.7K_OP

R288 2.7K

B B

SB_SM_CLK9,19

SB_SM_DATA9,19

FAN_SMBCLK3,31

FAN_SMBDATA3,31

Q19

2N3904_OP

CK_SM_CLK

CK_SM_DATA

R335

10K

R243

B53

CK_SM_CLK

CK_SM_DATA

R315 0_OP

R236 0_OP

475_1

25MIL

C245

0.1u

CBVDD

R305

R304

FB_OUT

PCI_STP#19

PM_CPU_STP#3,19

PCI_STP#

PM_CPU_STP#

+3V

QT2012RL030HC_3A_0805

C219

0.1u

FWDSDCLKO7

U30

1

VDDREF

Z0501

Z0502

Z0505Z0504

Z0507

C250

0.01u

ICS952005

11

VDDZ

13

VDDPCI

19

VDDPCI

28

VDD48

29

VDDAGP

42

VDDCPU

48

VDDSD

5

VSSREF

8

VSSZ

18

VSSPCI

24

VSSPCI

25

VSS48

32

VSSAGP

41

VSSCPU

46

VSSSD

12

PCI_STOP#

45

CPU_STOP#

33

PD#/VTT_PWRGD

38

IREF

36

VDDA

37

VSSA

C274

10P

6

Z0522 Z0523

PCICLK_F0/FS3

PCICLK_F1/FS4

24_48M/MULTISEL

XIN

Y2

14.318MHz_DIP

CPUCLK0

CPUCLK#0

CPUCLK1

CPUCLK#1

AGPCLK0

AGPCLK1

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

REF0/FS0

REF1/FS1

REF2/FS2

7

Clock Buffer (DDR)

U33

3

VDD

12

VDD

23

VDD

10

VDD

Z0524

0

7

SCLK

Z0525

0

22

SDATA

8

CLKIN

9

CLKIN#

20

FB_IN

21

FB_IN#

GND

61115

CLK0

CLK1

CLK2

CLK3

CLK4

CLK5

CLK#0

CLK#1

CLK#2

CLK#3

CLK#4

CLK#5

FB_OUT

FB_OUT#

GND

GND

GND

28

ICS93722

SDCLK

ZCLK0

ZCLK1

SCLK

SDATA

XOUT

C264

10P

Place near to the Clock Outputs

Z0508

40

Z0509

39

Z0510

44

Z0511

43

47

Z0513

31

Z0540

30

Z0515

9

Z0516

10

14

FS4 PCICLK

15

Z0517

16

Z0518

17

20

21

Z0520

22

23

FS0 963REF1

2

FS1

48M

3

4

27

26

35

34

(3 OPTIONS)

1: (ICS)

2: (Cypress)

3. (Hitachi)

FS2

Z0521

MULTISEL

R313

R249

Place near to the Clock Buffer

Z0527

2

Z0528

4

Z0529

13

Z0530

17

Z0531

24

Z0532

26

Z0533

1

Z0534

5

Z0535

14

Z0536

16

Z0537

25

Z0538

27

19

18

R306 22

R279

R286

R327

R318

R284

R278

R274

R299

R331

R330

R281

R273

R239

R240

R237

R238

R241

R242

R314 22

R291

R292

R317

R293

R294

R290 22

C302

10P

33

33

33

33

22

22

22

22

22

22

22

22

22

22

0

0

0

0

0

0

0

0

0

0

0

0

CPUCLK

CPUCLK#

SIS648CLK

SIS648CLK#

AGPCLK

AGPCLK1

648ZCLK

963ZCLK

PCLK_ECFS3

PCLK_CB

LPC_CLK

IO_CLK

USB-48M

CK_SM_CLK

CK_SM_DATA

DDRCLK0

DDRCLK3

DDRCLK2

DDRCLK1

DDRCLK4

DDRCLK5

DDRCLK#0

DDRCLK#3

DDRCLK#2

DDRCLK#1

DDRCLK#4

DDRCLK#5

CPUCLK 3

CPUCLK# 3

SiS648CLK 6

SiS648CLK# 6

AGPCLK 6

AGPCLK1 11

648ZCLK 7

963ZCLK 18

PCLK_EC 31

PCICLK 18

PCLK_1394 26

PCLK_CB 22

LPC_CLK 29

963REF1 19

IO_CLK 29

USB_48M 20

DDRCLK0 9

DDRCLK3 9

DDRCLK2 9

DDRCLK1 9

DDRCLK4 9

DDRCLK5 9

DDRCLK#0 9

DDRCLK#3 9

DDRCLK#2 9

DDRCLK#1 9

DDRCLK#4 9

DDRCLK#5 9

FB_OUTZ0539

Place near to the Clock Outputs

R225

CPUCLK

R226

CPUCLK#

R223

SiS648CLK

R224

SiS648CLK#

AGPCLK

AGPCLK1

648ZCLK

963ZCLK

PCICLK

PCLK_CB

PCLK_EC

LPC_CLK

963REF1

USB_48M

IO_CLK

PCLK_1394

MULTISEL

Place near to the Clock Buffer

DDRCLK0

DDRCLK1

DDRCLK2

DDRCLK3

DDRCLK4

DDRCLK5

DDRCLK#0

DDRCLK#1

DDRCLK#2

DDRCLK#3

DDRCLK#4

DDRCLK#5

FB_OUT

C238 10P

C239 10P

C312 10P

C294 10P

C295 10PR316

C309 10P

C313 10P

C310 10P

C293 10P

C261 10P

C341 10P

C314 10P

R229

C279 10P

C319 10P

C327 10P

C287 10P

C284 10P

C277 10P

C276 10P

C331 10P

C336 10P

C301 10P

C280 10P

C272 10P

C307 10P

49.9_1

49.9_1

49.9_1

49.9_1

0_OP

Place near to the Clock Buffer

+2.5VS

B55

QT2012RL030HC_3A_0805

A A

C266

+

4.7U_10V_0805

5

C269

+

4.7U_10V_0805

C282

0.1u

C311

0.1u

C298

0.1u

CBVDD

FUNCTIONALITY

BIT5BIT6

10000100 10066.67

1

0

1

00

11

4

1 133.3

0101

0

010101

0 33.3

FS0FS1FS2FS3FS4 AGP

1

1 1 167

CPU

100

100

3

DDR_RAM

166.67

133

66.67

66.67

66.67

PCI

33.3

33.310 010 1 1 133.3 133.3

33.366.67

33.3

ZCLK

133.3

133.3

133

133.3

133

2

Title

Size Document Number Rev

Date: Sheet of

Unwill International Corp.

755SA1

2410

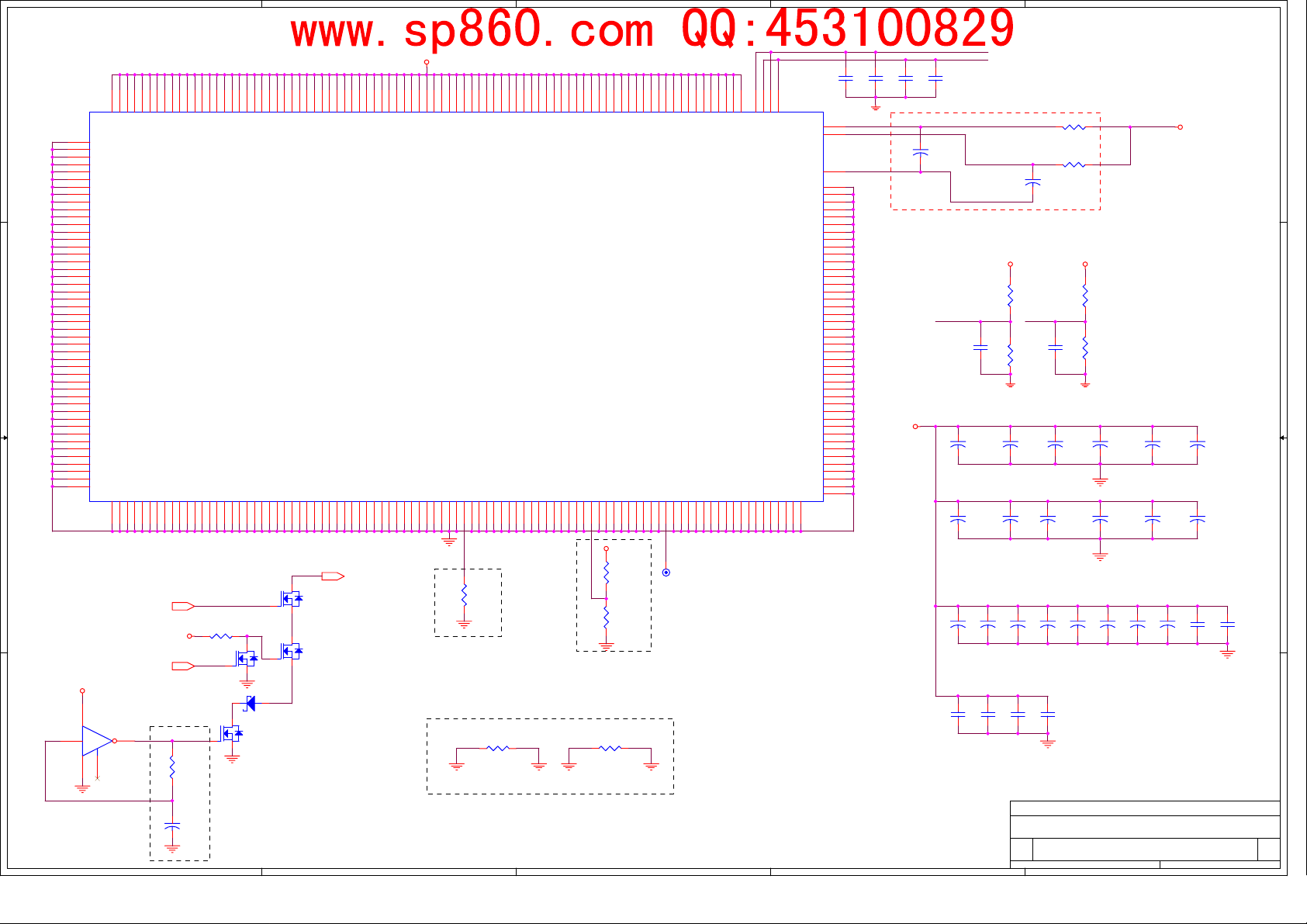

CLOCK GEN ICS952005

1

538Monday, December 08, 2003

A

Page 6

5

U28A

C24

HD63#

E23

HD62#

B24

HD61#

D23

HD60#

D25

HD59#

F24

HD58#

C26

HD57#

B25

HD56#

B26

HD55#

D27

HD54#

D26

HD53#

E27

HD52#

B27

HD51#

D28

HD50#

C28

HD49#

B28

HD48#

E29

HD47#

F28

HD46#

B29

HD45#

C30

HD44#

B30

HD43#

B31

HD42#

C32

HD41#

D29

HD40#

C33

HD39#

B33

HD38#

B35

HD37#

D32

HD36#

B34

HD35#

E31

HD34#

D31

HD33#

D33

HD32#

D35

HD31#

G31

HD30#

C35

HD29#

F33

HD28#

E33

HD27#

D34

HD26#

E35

HD25#

F32

HD24#

J34

HD23#

G34

HD22#

H35

HD21#

F35

HD20#

J33

HD19#

J31

HD18#

G35

HD17#

H33

HD16#

J35

HD15#

K32

HD14#

N33

HD13#

K33

HD12#

L31

HD11#

L33

HD10#

K35

HD9#

L35

HD8#

M35

HD7#

M33

HD6#

P32

HD5#

P33

HD4#

L34

HD3#

N34

HD2#

N35

HD1#

P35

HD0#

AG31

HADSTB1#

AA33

HADSTB0#

W35

HREQ4#

Y33

HREQ3#

W31

HREQ2#

W33

HREQ1#

Y35

HREQ0#

D22

HCOMP_P

C22

HCOMP_N

B22

HCOMPVREF_N

SiS648

R178 20_1

R180 110_1

www.sp860.com QQ:453100829

HA31#

HA30#

HA29#

HA28#

HA27#

HA26#

HA25#

HA24#

HA23#

HA22#

HA21#

HA20#

HA19#

HA18#

HA17#

HA16#

HA15#

HA14#

HA13#

HA12#

HA11#

HA10#

CPUCLK#

CPURST#

CPUPWRGD

HDSTBP3#

HDSTBP2#

HDSTBP1#

HDSTBP0#

HDSTBN3#

HDSTBN2#

HDSTBN1#

HDSTBN0#

CPU_CORE

HA9#

HA8#

HA7#

HA6#

HA5#

HA4#

HA3#

CPUCLK

ADS#

BREQ0#

BPRI#

BNR#

HLOCK#

HIT#

HITM#

DEFER#

HTRDY#

DRDY#

DBSY#

DBI3#

DBI2#

DBI1#

DBI0#

RS#2

RS#1

RS#0

HVREF0

HVREF1

HVREF2

HVREF3

HVREF4

648FX

648

Host

HNCVREF

pin B22

Voltage

Divider

NC

C173

0.01u

HNCVREF

C179

0.01u

HD#[0..63]

1/3 Vcore

30 mil

5

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

HD#53

HD#52

HD#51

HD#50

HD#49

HD#48

HD#47

HD#46

HD#45

HD#44

HD#43

HD#42

HD#41

HD#40

HD#39

HD#38

HD#37

HD#36

HD#35

HD#34

HD#33

HD#32

HD#31

HD#30

HD#29

HD#28

HD#27

HD#26

HD#25

HD#24

HD#23

HD#22

HD#21

HD#20

HD#19

HD#18

HD#17

HD#16

HD#15

HD#14

HD#13

HD#12

HD#11

HD#10

HD#9

HD#8

HD#7

HD#6

HD#5

HD#4

HD#3

HD#2

HD#1

HD#0

HASTB#1

HASTB#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

HPCOMP

HNCOMP

HNCVREF

20 mil

Rds-on(n) = 10 ohm

HNCOMP

HPCOMP

Rds-on(p) = 56 ohm

20 mil

HD#[0..63]3

D D

C C

B B

648

648FX

HASTB#[0..1]3

HREQ#[0..4]3

CPU_CORE

R161

A A

150_1

R182

75_1

648

AH33

AG33

AJ35

AF32

AJ34

AH32

AG35

AE31

AH35

AF35

AE35

AE33

AE34

AF33

AG34

AC33

AD32

AD33

AC35

AD35

AC31

AC34

AB35

AB32

AB33

AA35

AA31

Y32

AA34

AJ31

AJ33

B23

F22

V35

U31

R34

V33

T33

U34

R35

T35

V32

W34

U33

F26

B32

E34

R31

E25

D30

H32

M32

D24

F30

G33

N31

R33

T32

U35

AA26

W26

U26

R26

L20

4

HA#31

HA#30

HA#29

HA#28

HA#27

HA#26

HA#25

HA#24

HA#23

HA#22

HA#21

HA#20

HA#19

HA#18

HA#17

HA#16

HA#15

HA#14

HA#13

HA#12

HA#11

HA#10

HA#9

HA#8

HA#7

HA#6

HA#5

HA#4

HA#3

SiS648CLK

SiS648CLK#

CPURST#

CPUPWRGD

ADS#

BREQ0#

BPRI#

BNR#

HLOCK#

HIT#

HITM#

DEFER#

HTRDY#

DRDY#

DBSY#

DBI#3

DBI#2

DBI#1

DBI#0

HDSTBP#3

HDSTBP#2

HDSTBP#1

HDSTBP#0

HDSTBN#3

HDSTBN#2

HDSTBN#1

HDSTBN#0

RS#2

RS#1

RS#0

HVREF

R178 R180

20 1%

14 1%

110 1%

100 1%

4

HA#[3..31]

AGNT#

AGPRBF#

AGPWBF#

AREQ#

AFRAME#

ATRDY#

AGPPAR

ASTOP#

SiS648CLK

SiS648CLK#

SiS648CLK 5

SiS648CLK# 5

CPURST# 3

CPUPWRGD 3

ADS# 3

BREQ0# 3

BPRI# 3

BNR# 3

HLOCK# 3

HIT# 3

HITM# 3

DEFER# 3

HTRDY# 3

DRDY# 3

DBSY# 3

30 mil width

10mil space

HA#[3..31] 3

8

7

6

RP15 8P4RX8.2K_OP

8

7

6

RP28 8P4RX8.2K_OP

T1

+1.8V

T2

AGP_VDDQ

350mv

DBI#[0..3] 3

HDSTBP#[0..3] 3

HDSTBN#[0..3] 3

RS#[0..2] 3

2/3

HVREF

Vcore

C176

0.1u

CLOSE 648

R283

324_1

R289

100_1

AGP_VDDQ

1

2

3

45

1

2

3

45

CPU_CORE

C165

0.01u

C185

0.01u

3

R255 8.2K_OP

R247 8.2K_OP

R271 8.2K_OP

R215 8.2K_OP

R265 8.2K_OP

R275 8.2K_OP

R277 8.2K_OP

AGPADSTB1

SB_STB

AGPADSTB0

DBI_LOW

AIRDY#

ADEVSEL#

ASERR#

Modify 22

C689 220P_OP

AGPVREFGC

C299

0.1u

AC/BE#[0..3]11

+3V

4.7U_10V_0805_OP

R179

75_1

R830

R181

470

150_1

T3

R198 0

Modify 11

+3V

AGPCLK

66MHz

AGPCLK5

AFRAME#11

AIRDY#11

ATRDY#11

ASTOP#11

ADEVSEL#11

AREQ#11

AGNT#11

AC/BE#[0..3]

C655

+3V

R194 0

4.7U_10V_0805_OP

Modify 12 Modify 11

3

C658

C220

0.01u

AAD[0..31]

AAD0

AAD1

AAD2

AAD3

AAD4

AAD5

AAD6

AAD7

AAD8

AAD9

AAD10

AAD11

AAD12

AAD13

AAD14

AAD15

AAD16

AAD17

AAD18

AAD19

AAD20

AAD21

AAD22

AAD23

AAD24

AAD25

AAD26

AAD27

AAD28

AAD29

AAD30

AAD31

AGPCLK

AFRAME#

AIRDY#

ATRDY#

ASTOP#

ADEVSEL#

ASERR#

AREQ#

AGNT#

AC/BE#3

AC/BE#2

AC/BE#1

AC/BE#0

C1XAVDD

C212

0.1u

C207

0.01u

2

AGP_VDDQ

AAD[0..31] 11

U28B

Y5

AAD0/VBD7

W4

AAD1/VBD6

V2

AAD2/VBD5

W6

AAD3/VBD4

V4

AAD4/VBD3

U2

AAD5/VBD2

V5

AAD6/VBD1

U4

AAD7/VBD0

R2

AAD8/VAD6

T4

AAD9/VAD5

R3

AAD10/VAD4

T5

AAD11/VAD7

P2

AAD12/VAD8

R4

AAD13/VAD9

N2

AAD14/VAD10

R6

AAD15/VAD11

L3

AAD16/VADE

L4

AAD17/VAVSYNC

K2

AAD18/VAHSYNC

L6

AAD19/VBD11

J2

AAD20/VBD10

J3

AAD21/VBD8

K4

AAD22/VBD9

J4

AAD23/VAD1

J6

AAD24/VAD0

H4

AAD25/VAD2

G3

AAD26/VAD3

H5

AAD27/VBDE

F2

AAD28/VBCTL0

G4

AAD29/VBCTL1

E2

AAD30/VBHSYNC

G6

AAD31/VBVSYNC

D8

AGPCLK

N6

AFRAME#

M4

AIRDY#

N4

ATRDY#

M2

ASTOP#

L2

ADEVSEL#

P5

ASERR#

C6

AREQ#/VBCAD

E8

AGNT#

K5

AC/BE3#

M5

AC/BE2#

P4

AC/BE1#

U6

AC/BE0#

SiS648

+3V

R218 0

4.7U_10V_0805_OP

3.3V

1.5V

C656

648

AGP 8x

SBA7

SBA6

SBA5

SBA4

SBA3

SBA2

SBA1

SBA0/VBCLK

ST0

ST1

ST2

ADBIH/PIPE#/VGPIO3

AD_STB0#/VAGCLK#

AD_STB1#/VBGCLK#

3.3V

ADBIL

AGP8XDET#

APAR

WBF#/VGPIO2

RBF#/VBHCLK

AD_STB0/VAGCLK

AD_STB1/VBGCLK

SB_STB

SB_STB#

AGPCOMP_P

AGPCOMP_N

AGPVREF

AGPVSSREF

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

C1XAVSS

C1XAVDD

C4XAVSS

C4XAVDD

C240

0.01u

A1XAVDD A4XAVDD

C232

0.1u

A1XAVSSC1XAVSS

E3

F4

D2

F5

E4

B2

E6

B3

B6

F7

B5

D6

C4

C7

N3

B4

D7

T2

U3

G2

H2

C2

D3

W2

Y2

W3

Y4

B8

C8

A7

B7

AL36

AK34

AJ36

AK35

25 mil25 mil

SBA7

SBA6

SBA5

SBA4

SBA3

SBA2

SBA1

SBA0

ST0

ST1

ST2

Modify 11 Modify 11

C4XAVDD

C205

0.1u

C4XAVSS

25 mil

2

Title

Size Document Number Rev

Date: Sheet of

Unwill International Corp.

2410

SBA[0..7]

ST[0..2]

DBI_LOW

AGPPIPE#

GC_DET#

AGPPAR

AGPWBF#

AGPRBF#

AGPADSTB0

AGPADSTB#0

AGPADSTB1

AGPADSTB#1

SB_STB

SB_STB#

AGPCOMP_P

AGPCOMP_N

AGPVREFGC

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

C1XAVSS

C1XAVDD

C4XAVSS

C4XAVDD

+3V

R230 0

4.7U_10V_0805_OP

AGPCOMP_N

AGPCOMP_P

C657

755SA1

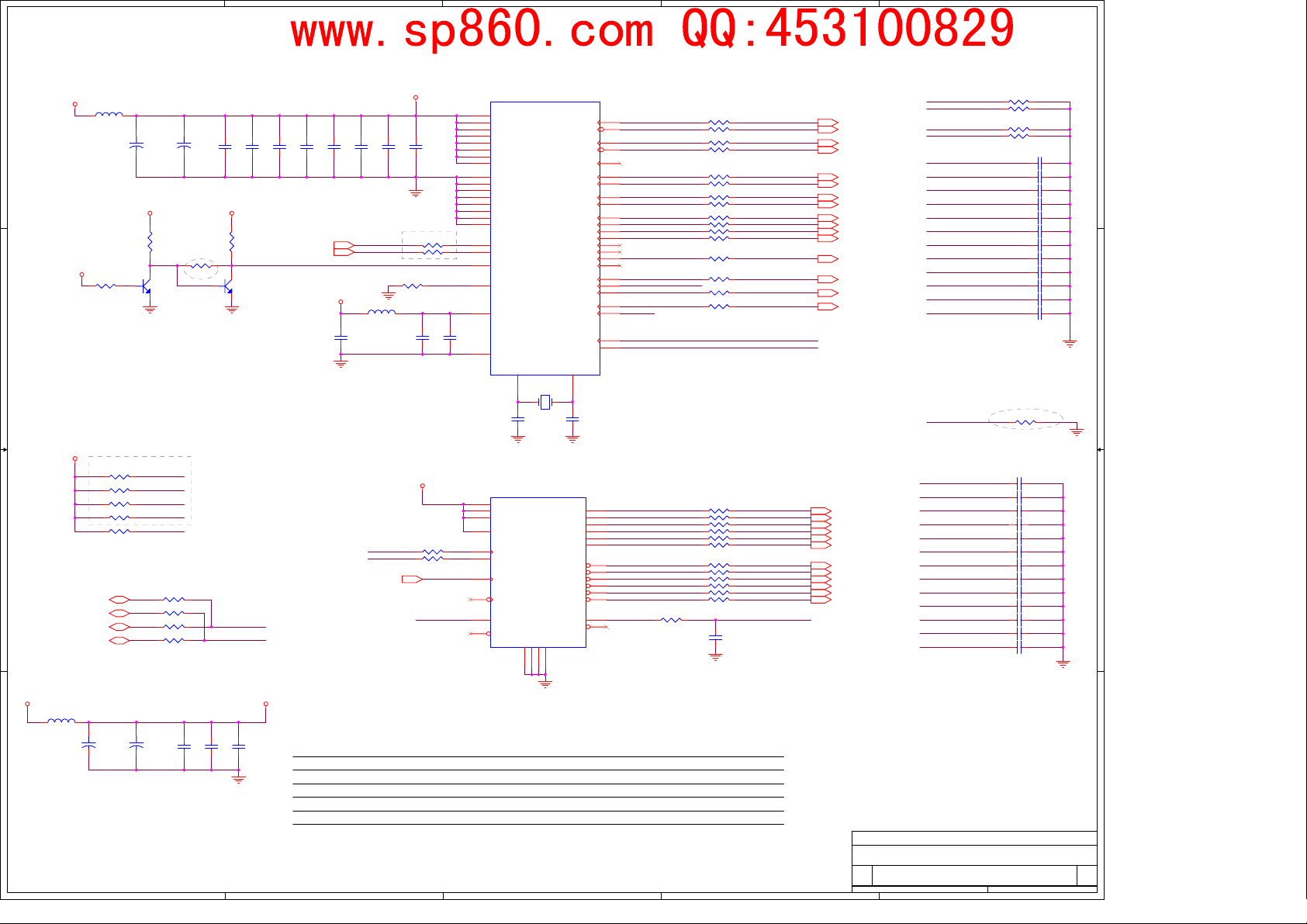

SiS648 (HOST&AGP)

1

C667 220P

SBA[0..7] 11

ST[0..2] 11

DBI_LO 11

DBI_HI 11

AGPPAR 11

AGPWBF# 11

AGPRBF# 11

AGPADSTB0 11

AGPADSTB#0 11

AGPADSTB1 11

AGPADSTB#1 11

SB_STB 11

SB_STB# 11

20 mil

20 mil

C243

0.01u

638Monday, December 08, 2003

1

Modify 22

+3V

AGP_VDDQ

AGP_VDDQ

R28249.9_1

R28040.2_1

C242

25 mil

0.1u

A4XAVSS

R199

4.7K_OP

R210

0

A

Page 7

5

4

3

2

1

MA[0..14]

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

R195 0_OP

DQM[0..7]

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQS[0..7]

DQM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

SDRCLK

FWDSDCLK FWDSDCLKO

CS#0

CS#1

CS#2

CS#3

CS#4

CS#5

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

S3AUXSW#

DDRVREFA

DDRVREFB

DDRCOMP_P

DDRCOMP_N

DRAM_SEL

DLLAVDD

DLLAVSS

DDRAVDD

DDRAVSS

R301 0

R308 22

T34

T35

T5

T25

SRAS#10

SCAS#10

SWE#10

R337

150_1

DDRVREFA

R329

150_1

C192

0.01u

DDRVREFB

C201

0.01u

MD[0..63]

SRAS#

SCAS#

SWE#

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

AN35

AP36

AK33

AM33

AN34

AK32

AR34

AN33

AM32

AL31

AR31

AL30

AN32

AR33

AN31

AM31

AP30

AR30

AM29

AL27

AN30

AN29

AL28

AN28

AP26

AN25

AR24

AL24

AL25

AR26

AM25

AN24

AN21

AP20

AN20

AL18

AM21

AR21

AL19

AM19

AL15

AL14

AN15

AR15

AN16

AM15

AN14

AL13

AM13

AL12

AL11

AR12

AP14

AR14

AN13

AP12

AL10

AR11

AM9

AR9

AM11

AN11

AP10

AN9

AL17

AR19

AN19

SiS648

U28C

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

SRAS#

SCAS#

SWE#

MD[0..63]10

D D

+2.5VS

C338

0.01u

C C

C318

0.01u

+2.5VS

R190

150_1

R191

150_1

B B

www.sp860.com QQ:453100829

AR23

MA0

AN23

MA1

AN22

MA2

AM23

MA3

AL23

MA4

AL26

MA5

AN26

MA6

AN27

MA7

AR27

MA8

AR28

MA9

AP22

MA10

AN18

MA11

AR22

MA12

AP28

MA13

AM27

MA14

Z0701

AL33

NC/MA15

AR35

DQM0

AR32

DQM1

AL29

DQM2

648

Memory

DQS0/CSB0#

DQS1/CSB1#

DQS2/CSB2#

DQS3/CSB3#

DQS4/CSB4#

DQS5/CSB5#

DQS6/CSB6#

DQS7/CSB7#

SDRCLKI/DRAMTEST

FWDSDCLKO

S3AUXSW#/CKE6

DDRCOMP_P

DDRCOMP_N

NC/DRAM_SEL/TRAP2

DDRVREFA

DDRVREFB

DQM3

DQM4

DQM5

DQM6

DQM7

CS0#

CS1#

CS2#

CS3#

CS4#

CS5#

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

DLLAVDD

DLLAVSS

DDRAVDD

DDRAVSS

AP24

AL20

AP16

AN12

AN10

AP34

AP32

AR29

AR25

AR20

AR16

AR13

AR10

AL22

AL21

AM17

AL16

AN17

AR17

AP18

AR18

AP4

AT3

AR3

AP3

AR2

AN4

AP2

AF16

AF23

AR8

AP8

AP1

AL35

AL34

AM35

AN36

MA[0..14] 10

NB Hardware Trap Table

DLLEN#

DRAM_SEL

TRAP0

TRAP1 partial-swing mode full-swing mode 0

TEST1

TEST2

CLOSE TO NB

CS#[0..3]

CKE[0..3]

T26

DDRCOMP_N

DDRCOMP_P

enable PLL disable PLL

SDR DDR

normal NB debug mode

Type Select II Disable 0

ENTEST

PWROK

AUXOK

DQM[0..7] 10

DQS[0..7] 10

C330 10P

CS#[0..3] 10

CKE[0..3] 9,10

S3AUXSW# 22,29,31

R334 40.2_1

R333 40.2_1

FWDSDCLKO 5

S3AUXSW#

1

R217 4.7K

C354 0.1u

C360 0.1u

+3VS

R343

4.7K

+2.5VS

Default0

0

1(DDR)

0

0Type Select III Disable

T21

133MHz

648ZCLK

648ZCLK5

ZUREQ18

ZDREQ18

ZSTB018

ZSTB#018

ZSTB118

ZSTB#118 AUXOK 19,31

ZAD[0..16]

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZAD16

648ZCLK

ZUREQ

ZDREQ

ZSTB0

ZSTB#0

ZSTB1

ZSTB#1

ZVREF

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

ZCOMP_N

ZCOMP_P

VDDZ_1.8

VDDZ_1.8

AH5

AK2

AH2

AH4

AG3

AG6

AF4

AG2

AF5

AG4

AD2

AE6

AE2

AE4

AL3

AK5

AE3

AF2

AK4

AN1

AM2

AL2

AL1

AD5

AD4

AJ4

AJ6

AL6

AL4

AJ2

AJ3

U28D

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZAD16

ZCLK

ZUREQ

ZDREQ

ZSTB0

ZSTB0#

ZSTB1

ZSTB1#

ZVREF

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

ZCOMP_N

ZCOMP_P

SiS648

25MIL

R300 56

R297 56

ZAD[0..16] 18

1.8V

648

MuTIOL

NC/DACAVDD1

NC/DACAVSS1

NC/DACAVDD2

NC/DACAVSS2

NC/ECLKAVDD

NC/ECLKAVSS

NC/DCLKAVDD

NC/DCLKAVSS

ZCOMP_N

ZCOMP_P

NC/ROUT

NC/GOUT

NC/BOUT

NC/HSYNC

NC/VSYNC

NC/VCOMP

NC/VOSCI

NC/VGPIO0

NC/VGPIO1

NC/VRSET

NC/INT#A

NC/VVBWN

PCIRST#

PWROK

AUXOK

TRAP1

TRAP0

TESTMODE2

TESTMODE1

TESTMODE0

DLLEN#

ENTEST

B12

B13

A13

A11

B11

E15

A15

E13

C11

D15

C10

E14

D13

C12

D14

C13

B14

C14

B15

C15

AN2

AM4

AN3

F9

D10

C9

B9

B10

E10

D9

Z0702

PWROK

AUXOK

TRAP1

TRAP0

648TEST2

648TEST1

648TEST0

DLLEN#

ENTEST

R345 0

25MIL

Z1XAVDD

Z1XAVSS

25MIL

Z4XAVDD

Z4XAVSS

PCIRST#

PWROK 19,31

T17

T16

T14

T10

T11

T22

C343

0.1u

C320

0.1u

C339

0.01u

C329

0.01u

PCIRST# 11,18,21,22,26,27,29,31

R338 0

C659

4.7U_10V_0805_OP

+3V

Modify 11

R332 0

C660

4.7U_10V_0805

+3V

Modify 10

DLLAVDD

A A

5

C224

0.1u

C226

0.01u

R213 0

C661

4.7U_10V_0805_OP

+3V +3V

Modify 11 Modify 11

25MIL25MIL

DDRAVDD

C237

0.1u

DDRAVSSDLLAVSS

4

C241

0.01u

R220 0

C662

4.7U_10V_0805_OP

3

R328

150_1

R307

49.9_1

C317

0.1u

ZVREF

C304

0.1u

20 Mil

1/4 0.45V

Title

Size Document Number Rev

2

Date: Sheet of

Unwill International Corp.

755SA1

2410

SiS648 (DDR/MuTIOL)

1

738Monday, December 08, 2003

A

Page 8

5

VDDZ_1.8

4

3

2

1

CPU_CORE

W24

Y13

N15

N20

N16

N18

N19

N22

R24

T13

U24

CPU_Core

3.3V

2.5_DIMM

VDDM

VDDM

VDDM

VDDM

AB24

AC25

AD12

AD25

VDDM

AE11

VDDM

AE12

V13

IVDD/PVDD

IVDD/PVDD

IVDD/PVDD

648

Power

VDDM

VDDM

AE13

AE16

AE17

IVDD/PVDD

IVDD/PVDD

IVDD/PVDD

VDDM

VDDM

VDDM

AE18

AE19

AE20

IVDD/PVDD

IVDD/PVDD

NC/IVDD/PVDD

VDDM

VDDM

VDDM

AE21

AE22

AE23

VDDM

AE24

IVDD

VDDM

AE25

IVDD

VDDM

AE26

U28E

M20

NC/VTT/VTT

N25

NC/VTT/VTT

P25

NC/VTT/VTT

L25

VTT

L26

VTT

C150

0.1u

Z0801

C153

1U_10V

AA25

AE14

AE15

AB25

AD22

AD20

AD18

AD16

AD14

AC13

M18

M19

M21

M22

M23

M24

M25

M26

R25

T25

U25

V25

W25

Y25

A17

A18

A19

A20

A21

B17

B18

B19

B20

B21

C17

C18

C19

C20

C21

D17

D18

D19

D20

D21

E17

E18

E19

E20

E21

F17

F18

F19

F20

F21

A9

L17

M17

N17

AL7

AL8

AL9

AM6

AM7

AM8

AN5

AN6

AN7

AN8

AP5

AP6

AP7

AR4

AR5

AR6

AR7

AT4

AT5

AT6

AT7

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

NC

VDD3.3

VDD3.3

VDD3.3

NC/VDDM/VDDM

NC/VDDM/VDDM

NC/VDDM/VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

Modify 23

C670

4.7U_10V_0805

D D

C C

T13

+3V

VDDM_2.5

B B

+3V

www.sp860.com QQ:453100829

U28F

Y14

Y15

Y16

Y17

Y18

Y19

Y20

Y21

Y22

Y23

AA14

AA15

AA16

AA17

AA18

AA19

AA20

AA21

AA22

AA23

AB14

AB15

AB16

AB17

AB18

AB19

AB20

AB21

AB22

AB23

AC14

AC15

AC16

AC17

AC18

AC19

AC20

AC21

AC22

N21

N23

N24

P13

IVDD

IVDD

IVDD

IVDD

IVDD

1.8V_Main

NC/IVDD/IVDD

1.8VVDDQ_Main

NC/VDDQ/VDDQ

AUX1.8/AUX_IVDD

AUX

VDDM

VDDM

VDDM

VDDM

VDDM

AF11

AF12

AF25

AF26

N13

N14

P24

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

NC/IVDD

NC/IVDD

NC/IVDD

NC/IVDD

NC/IVDD

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

AUX3.3

NC/LSYNC

NC/RSYNC

NC/CSYNC

SiS648

V24

A3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL32

C306

0.1u

C356

0.1u

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

A22

A24

A26

A28

A30

A32

A34

C23

C283

0.1u

C353

0.1u

IVDD

NC

NC

NC

NC

NC

NC

NC

W13

Y24

AA24

AB13

AC24

AD13

AD15

AD17

AD19

AD21

AD23

AD24

R13

U13

AA13

T24

C16

B16

D16

E16

F15

AD3

AE1

AF3

AG1

AH3

AJ1

AK3

AM3

W11

W12

Y11

Y12

AA12

AA1

AA2

AA3

AA4

AA5

AA6

AB1

AB2

AB3

AB4

AB5

AB6

AC1

AC2

AC3

AC4

AC5

AC6

L11

L12

L13

M11

M12

M13

M14

M15

M16

N11

N12

R12

T12

U12

V12

P12

AB12

AC12

D4

D5

AM5

AM34

F13

F11

E11

D11

E12

D12

Z0802

Z0803

Z0804

Z0805

Z0806

Z0807

Z0808

Z0809

VDDZ_1.8

AGP_VDDQ

1.8V for sis661FX

+1.8VS +3VS

B62

QT1608RL060

T23

T19

T24

T18

T15

T20

T12

C355

0.1u

+1.8VS

+3VS

C348

0.1u

C1

C3

C5

G1

G5

H3

M3

N1

N5

R1

R5

U1

U5

W1

W5

AE5

AG5

AJ5

AL5

AC32

AC36

AD34

AE32

AE36

AF34

AG32

AG36

AH34

AJ32

AM10

AM12

AM14

AM16

AM18

AM20

AM22

AM24

AM26

AM28

AM30

AP9

AP11

AP13

AP15

AP17

U32

U36

V34

W32

SiS648

AGP_VDDQ

+

4.7U_10V_0805

VDDZ_1.8

+

VSS

A5

VSS

VSS

VSS

VSS

E1

VSS

E5

VSS

E7

VSS

E9

VSS

F3

VSS

VSS

VSS

VSS

J1

VSS

J5

VSS

K3

VSS

L1

VSS

L5

VSS

VSS

VSS

VSS

P3

VSS

VSS

VSS

T3

VSS

VSS

VSS

V3

VSS

VSS

VSS

Y3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C345

C346

4.7U_10V_0805

AP19

VSS

VSS

AP21

VSS

VSS

VSS

AP23

AP25

AP27

+

4.7U_10V_0805

+

VSS

VSS

VSS

VSS

VSS

AP29

AP31

AP33

AP35

AT8

C340

C357

4.7U_10V_0805

AT10

648

Ground

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AT20

AT22

AT24

AT26

C315

0.1u

C332

0.1u

AT28

AT30

AT32

VSS

AT34

AT12

AT14

AT16

C326

0.1u

C361

0.1u

AT18

AC23

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C25

C27

C29

C31

C34

C36

E22

E24

C303

C268

0.1u

0.1u

C308

C189

0.1u

0.1u

P14

P15

P16

P17

P18

P19

P20

P21

P22

W36

Y34

AA32

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AA36

VSS

AB34

VSS

P23

VSS

R14

VSS

R15

VSS

R16

VSS

R17

VSS

R18

VSS

R19

VSS

R20

VSS

R21

VSS

R22

VSS

R23

VSS

T14

VSS

T15

VSS

T16

VSS

T17

VSS

T18

VSS

T19

VSS

T20

VSS

T21

VSS

T22

VSS

T23

VSS

U14

VSS

U15

VSS

U16

VSS

U17

VSS

U18

VSS

U19

VSS

U20

VSS

U21

VSS

U22

VSS

U23

VSS

V14

VSS

V15

VSS

V16

VSS

V17

VSS

V18

VSS

V19

VSS

V20

VSS

V21

VSS

V22

VSS

V23

VSS

W14

VSS

W15

VSS

W16

VSS

W17

VSS

W18

VSS

W19

VSS

W20

VSS

W21

VSS

W22

VSS

W23

VSS

L32

VSS

L36

VSS

M34

VSS

N32

VSS

N36

VSS

P34

VSS

R32

VSS

R36

VSS/NC

T34

VSS

VSS

VSS

VSS

E26

E28

E30

E32

C270

0.1u

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E36

F34

G32

G36

H34

J32

J36

K34

C285

0.1u

Modify 23

C191

C349

0.1u

C668

4.7U_10V_0805

0.1u

C669

4.7U_10V_0805

Place to Bottom side

Place to Bottom side

A A

CPU_CORE

+

4.7U_10V_0805

C161

C156

+

4.7U_10V_0805

C163

1U_10V

C160

1U_10V

C155

0.1u

C158

0.1u

Place to Bottom side

C154

C152

0.1u

0.1u

C671

4.7U_10V_0805

VDDM_2.5

+

4.7U_10V_0805

C162

C166

+

4.7U_10V_0805

C369

0.1u

DDR_2.5

C373

0.1u

C334

0.1u

C174

0.1u

C225

0.1u

C347

0.1u

C202

0.1u

Modify 23

5

4

3

C208

0.1u

C350

+

4.7U_10V_0805

2

Place to Bottom side

4.7U_10V_0805

C672

C673

4.7U_10V_0805

Modify 23

Unwill International Corp.

Title

Size Document Number Rev

2410

Date: Sheet of

755SA1

SiS648 (POWER)

1

838Monday, December 08, 2003

A

Page 9

5

4

3

2

1

www.sp860.com QQ:453100829

DDR_2.5

D D

TP96

TP56

TP65

Z0911

184

82

VddID

VddSPD

VSS

176

TP67

TP98TP91

Z0912

102

167

Z0922

TP70

NC

NC, FETEN

Z0913

101

71

Z0923

TP68

NC

NC/CS2

TP95

Z0914

90

NC

NC/CS3

163

Z0924

TP97TP84

Z0915

10

TP66

Z0916

9

NC

92

SB_SM_CLK

Z0917

173

CON15

NC

NC

SDA

SCL

91

DDR_DIMM

SB_SM_DATA

Modify 21

TP90

TP86

Z0904

45

58

CB1

VSS

Z0905

49

66

Z0906

CB2

VSS

TP92

51

CB3

VSS

74

Z0907

134

81

CB4

VSS

TP85

Z0908

135

Z0909

CB5

VSS

TP83

142

CB6

VSS

Z0910

144

100

CB7

VSS

116

VSS

RSCAS#

RSWE#

RSRAS#

65

154

/CAS

/RAS

VSS

VSS

132

124

MVREF DDR_2.5

1

/WE

VREF

VSS

VSS

VSS

VSS

139

145

152

160

A1

TP93

TP94

RMA1

RMA0

RMA2

RMA1

RMA2

419343

48

202

201

A0

A2

A1

A1_L

A2_L

C C

/CS0

157

RCS#0

B B

RMA6

RMA7

RMA8

RMA3

RMA4

RMA4

37

130

200

A3

A4

A4_L

/CS1

/CS0_L(CS2)

/CS1_L(CS3)

158

191

192

RCS#1

RCS#3

RCS#2

RMA9

RMA5

RMA5

32

125

199

A6

A5

A5_L

CKE1

CKE0

21

111

188

CKE1

CKE0

CKE2

CKE0_L(CKE2)

122

187

CKE3

CKE1_L(CKE3)

Z0901

A11

DQS1

Z0902

RMA14

RMA11

RMA12

RMD0

RMD1

RMD2

RMD3

RMD4

2

456

DQS8

47

Z0918

8

94

DQ0

DQ1

DQ2

DQ3

DM0

DM1

DM2

DM3

107

119

129

149

RDQM1

RDQM4

RDQM2

RDQM0

RDQM3

DDRCLK0

DDRCLK#0

DDRCLK1

DDRCLK#1

DDRCLK2

DDRCLK#2

52

103

115

113

A13

A12

BA1

BA0

BA2

DQS4

DQS5

DQS6

DQS7

DQS2

DQS3

25

36

67

78

86

TP88

RDQS4

RDQS3

RDQS5

RDQS2

RDQS6

RDQS7

DDRCLK05

DDRCLK#05

DDRCLK15

DDRCLK#15

DDRCLK25

DDRCLK#25

RMA10

RMA13

272829

118

141

A9

A10

DQS0

14

RDQS0

RDQS1

RMD5

959798

DQ4

DM4

159

RDQM5

RMD6

DQ5

DM5

169

RDQM6

RMD7

99

DQ6

DM6

177

TP87

RDQM7

RMD8

12

DQ7

DM7

140

Z0919

RMD10

RMD9

13

19

DQ8

DQ9

DQ10

NC/DM8

CK0

137

RMD11

RMD12

RMD13

20

105

106

DQ12

DQ11

CK1

/CK0

138

16

17

DDRCLK0

DDRCLK#0

DDRCLK1

DDRCLK#1

DDRCLK2

DDRCLK#2

DDRCLK3

DDRCLK#3

DDRCLK4

DDRCLK#4

DDRCLK5

DDRCLK#5

RMD18

RMD20

185

DQ18A7DQ19

CK1_L(CK4)

RMD19

31

186

114

/CK1_L(CK4#)

195

DQ20

CK2_L(CK5)

RMD21

117

194

TP74

TP72

TP79

TP81

TP80

TP82

TP77

TP78

TP76

TP75

TP73

TP71

RMD22

DQ21

/CK2_L(CK5#)

RMD23

RMD25

RMD24

334235

121

123

DQ22A8DQ23

DQ24

SA0

SA1

181

182

183

DDRCLK#5

DDRCLK5

DDRCLK#4

DDRCLK4

DDRCLK#3

DDRCLK3

DQ25

SA2

RMD26

39

DQ26

SA0_L

196

RMD28

RMD27

RMD29

40

126

127

DQ28

DQ27

SA1_L

SA2_L

197

198

Z0920

TP69

R162 1K

RMD31

RMD30

13111133

DQ29

DQ30

DQ31

NC

193

Z0921

DDRCLK#5 5

DDRCLK5 5

DDRCLK#4 5

DDRCLK4 5

DDRCLK#3 5

DDRCLK3 5

RMD[0..63]10

RDQS[0..7]10

RDQM[0..7]10

RCS#[0..3]10

RMA[0..14]10

RSRAS#10

RSCAS#10

CKE[0..3]7,10

SB_SM_CLK5,19

SB_SM_DATA5,19

RMD32

RMD34

RMD33

53155556575960

DQ32

DQ33

VDD

VDD

7

38

46

RSWE#10

RMD35

RMD36

146

DQ34

DQ35

VDD

VDD

70

85

DDR_2.5

RMD38

RMD37

147

150

DQ36

DQ37

VDD

VDD

120

108

RMD41

RMD40

RMD42

RMD39

616364

68

151

DQ40

DQ41

DQ38

DQ39

VDD

VDD

VDD

148

168

DDR_2.5

RMD[0..63]

RDQS[0..7]

RDQM[0..7]

RCS#[0..3]

RMA[0..14]

RSRAS#

RSCAS#

RSWE#

CKE[0..3]

SB_SM_CLK

SB_SM_DATA

RMD45

RMD44

RMD43

RMD46

RMD48

RMD47

69

72

153

155

161

162

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

223054627796104

RMD49

DQ48

VDDQ

73

RMD50

DQ49

VDDQ

79

112

RMD51

80

DQ50

VDDQ

128

RMD17

RMD15

RMD14

RMD16

23

24

109

110

DQ13

DQ14

DQ15

DQ16

DQ17

/CK2

CK2

/CK1

CK0_L(CK3)

/CK0_L(CK3#)

75

76

189

190

RMD52

165

DQ51

VDDQ

136

RMD53

DQ52

VDDQ

166

143

RMD54

170

DQ53

VDDQ

156

RMD55

171

DQ54

VDDQ

164

RMD56

83

DQ55

VDDQ

172

RMD57

DQ56

VDDQ

84

180

RMD58

87

DQ57

VDDQ

RMD59

88

DQ58

DQ59

VSS

3

TP89

RMD61

RMD63

RMD62

RMD60

Z0903

44

174

17589178

179

CB0

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

34

50

26

18

R839

300_1

R483

75_1

R484

75_1

MVREF

MVREF_DIM

C482

0.1u

A A

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

Unwill International Corp.

755SA1

2410

DDR SLOT X 2

1

938Monday, December 08, 2003

A

Page 10

5

RSRAS#9

RSCAS#9

RSWE#9

RMA[0..14]9

RCS#[0..3]9

D D

RDQM[0..7]9

RDQS[0..7]9

RMD[0..63]9

CKE[0..3]7,9

C C

B B

RSRAS#

RSCAS#

RSWE#

RMA[0..14]

RCS#[0..3]

RDQM[0..7]

RDQS[0..7]

RMD[0..63] MD40

CKE[0..3]

DDR PULL HIGH

RMA6

RMA4

RMA3

RMA2

RMD30

RMD26

RMD31

RMD27

RMA9

RMA8

RMA7

RMA5

RMD23

RMD19

RMA11

RSRAS#

RSWE#

RSCAS#

RMD4

RMD0

RMD1

RMD5

RDQM0

RDQS0

RMD6

RMD2

RMD3

RMD7

RMD9

RMD8

RDQS1

RMD12

RDQM1

RMD13

RDQM2

RMD21

RMD22

RMD18

RP38 8P4RX33R

8

7

6

RP40 8P4RX33R

8

7

6

RP47 8P4RX33R

8

7

6

RP45 8P4RX33R

8

7

6

RP25 8P4RX33R

8

7

6

RP63

8

7

6

RP62 8P4RX33R

8

7

6

RP60 8P4RX33R

8

7

6

RP58 8P4RX33R

8

7

6

RP51 8P4RX33R

8

7

6

VTT_1.25V

www.sp860.com QQ:453100829

RP21 8P4RX33R

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

8P4RX33R

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

4 5

RP49 8P4RX33R

1

2

3

4 5

RP43 8P4RX33R

1

2

3

4 5

RP34 8P4RX33R

1

2

3

4 5

RP32 8P4RX33R

1

2

3

4 5

RP29 8P4RX33R

1

2

3

4 5

RP18 8P4RX33R

1

2

3

4 5

RP11 8P4RX33R

1

2

3

4 5

RP13 8P4RX33R

1

2

3

4 5

RP6 8P4RX33R

1

2

3

4 5

4

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

RMD45

RMD41

RDQM5

RDQS5

RMA13

RMA14

RMD28

RMD24

RMD29

RMD25

RDQM3

RDQS3

RMD36

RMD32

RMD37

RMD33

RMD34

RDQS4

RMD38

RDQM4

RMD35

RMD39

RMD44

RMD40

RMD43

RMD42

RMD47

RMD46

RMD51

RMD55

RMD56

RMD60

RMD54

RDQM6

RMD50

RDQS6

RMD58

RDQS7

RMD59

RMD63

DDR_2.5

RP8 8P4RX33R

1

2

3

4 5

RP56 8P4RX33R

1

2

3

4 5

RP16 8P4RX33R

1

2

3

4 5

RP52 8P4RX33R

1

2

3

4 5

RP23 8P4RX47R

1

2

3

4 5

RP37 8P4RX33R

1

2

3

4 5

RP54 8P4RX56R_OP

4 5

3

2

1

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

6

7

8

RMD57

RMD61

RMD62

RDQM7

RMD15

RMD14

RMD11

RMD10

RMD49

RMD48

RMD53

RMD52

RMD16

RMD20

RDQS2

RMD17

RCS#0

RCS#1

RCS#2

RCS#3

RMA1

RMA0

RMA10

RMA12

CKE0

CKE1

CKE2

CKE3

3

VTT_1.25V

DDR_2.5

DQM[0..7]7

MD[0..63]7

DQS[0..7]7

DQS4

MD34

DQM4

MD38

MD39

MD35

MD44

MD56

MD57

DQM7

MD62

MD48

MD49

MD52

MD53

DQS6

DQM6

MD50

MD54

MD26

MD30

MD27

MD31

DQS0

DQM0

MD6

MD2

C198

0.1u

MD[0..63]

DQS[0..7]

DQM[0..7]

RP31 8P4RX10R

8

7

6

RP30 8P4RX10R

8

7

6

RP9 8P4RX10R

8

7

6

RP14 8P4RX10R

8

7

6

RP12 8P4RX10R

8

7

6

RP42 8P4RX10R

8

7

6

RP61 8P4RX10R

8

7

6

C215

0.1u

4.7U_10V_0805

C265

0.1u

C374

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

RDQS4

RMD34

RDQM4

RMD38

RMD39

RMD35

RMD40

RMD44

RMD56

RMD57

RDQM7

RMD62

RMD48

RMD49

RMD52

RMD53

RDQS6

RDQM6

RMD50