Page 1

1

2

3

4

5

6

7

8

01

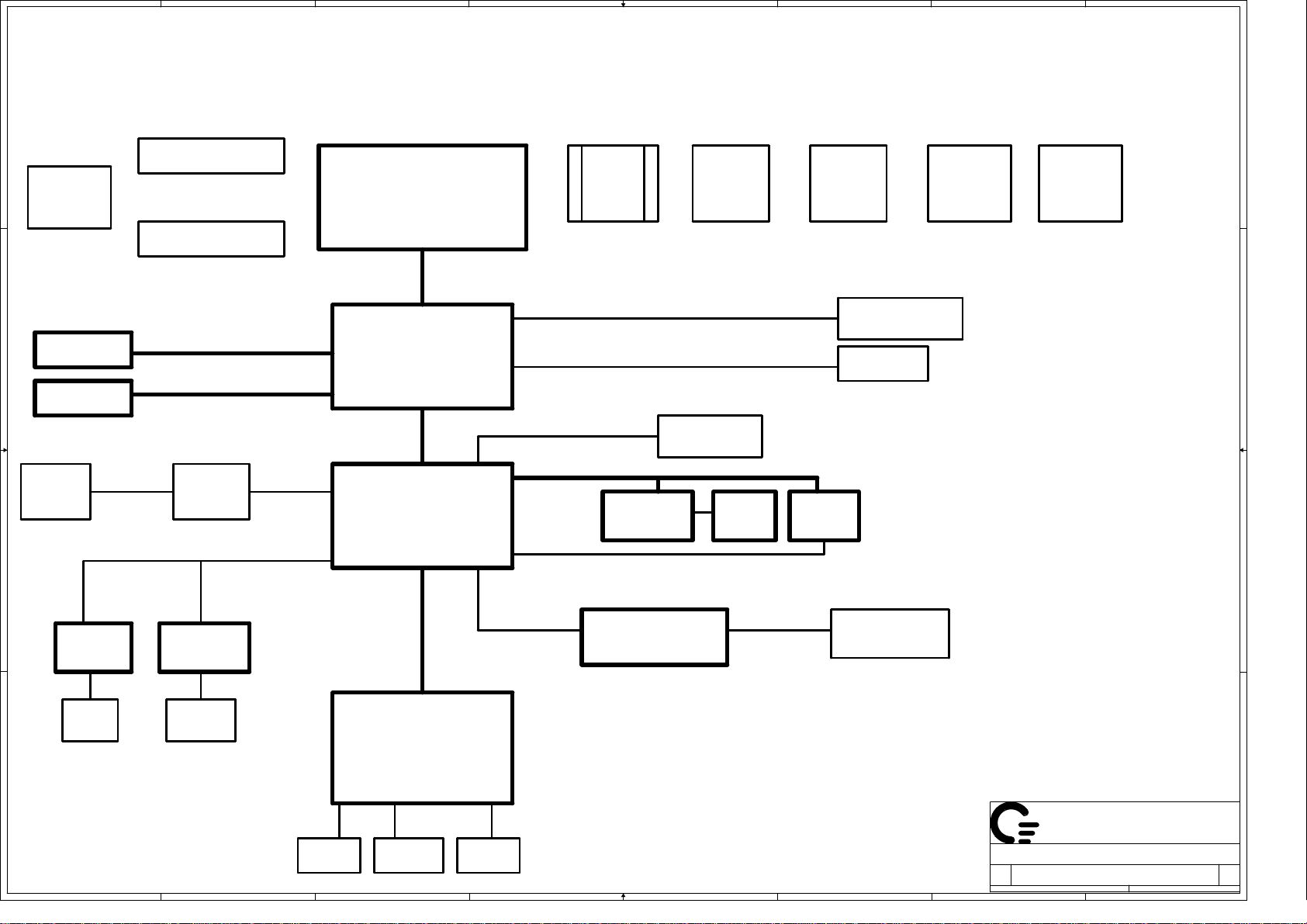

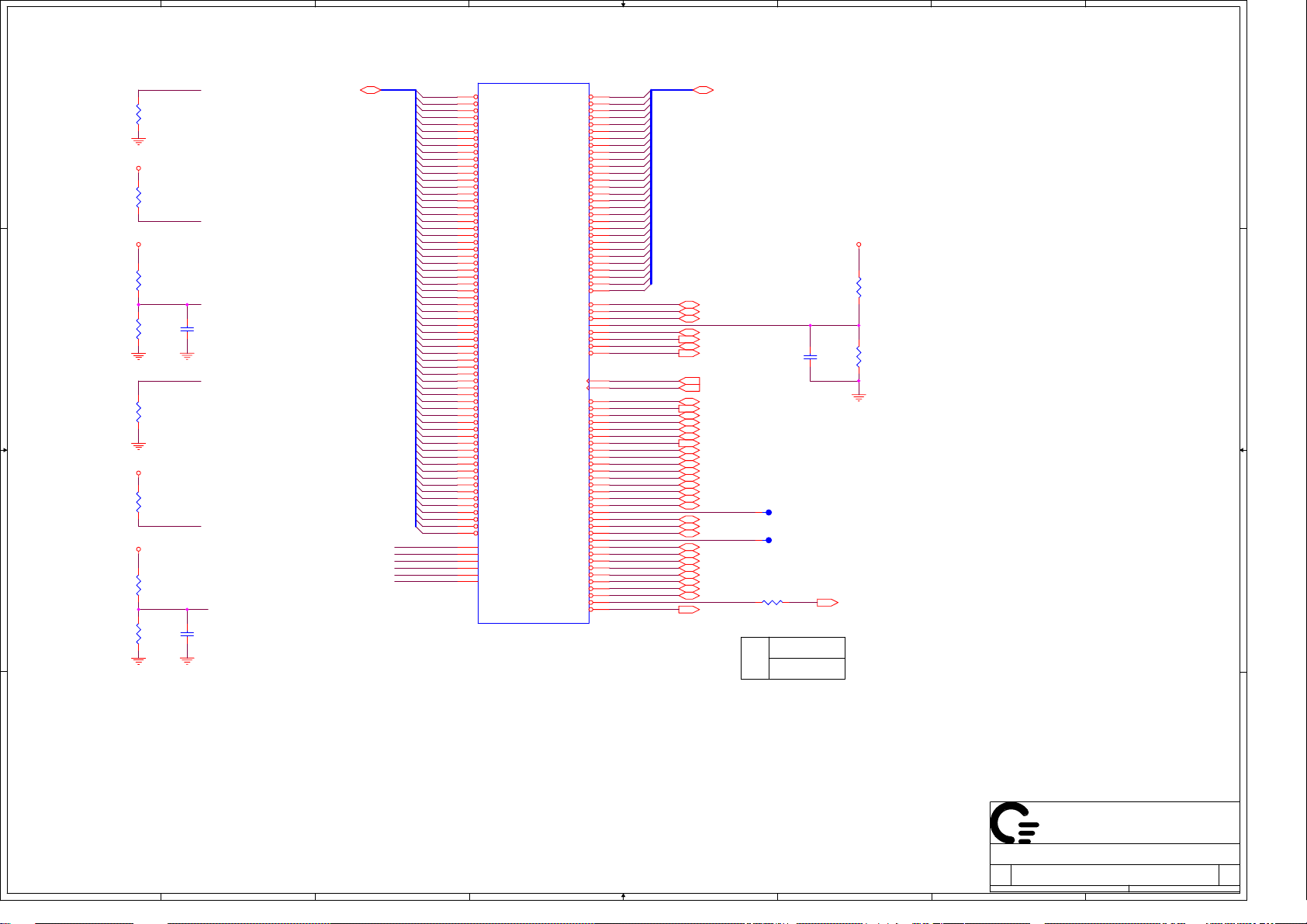

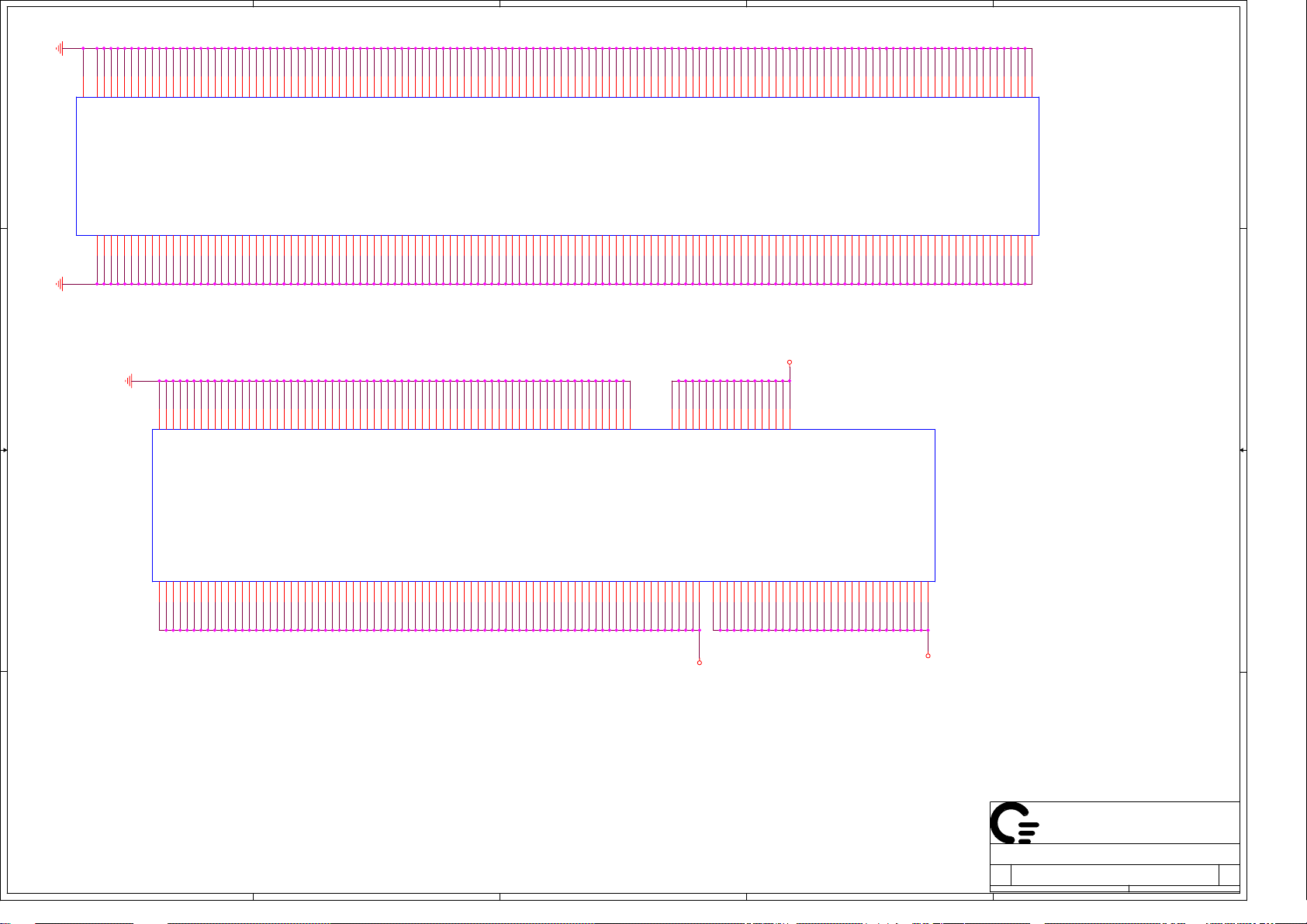

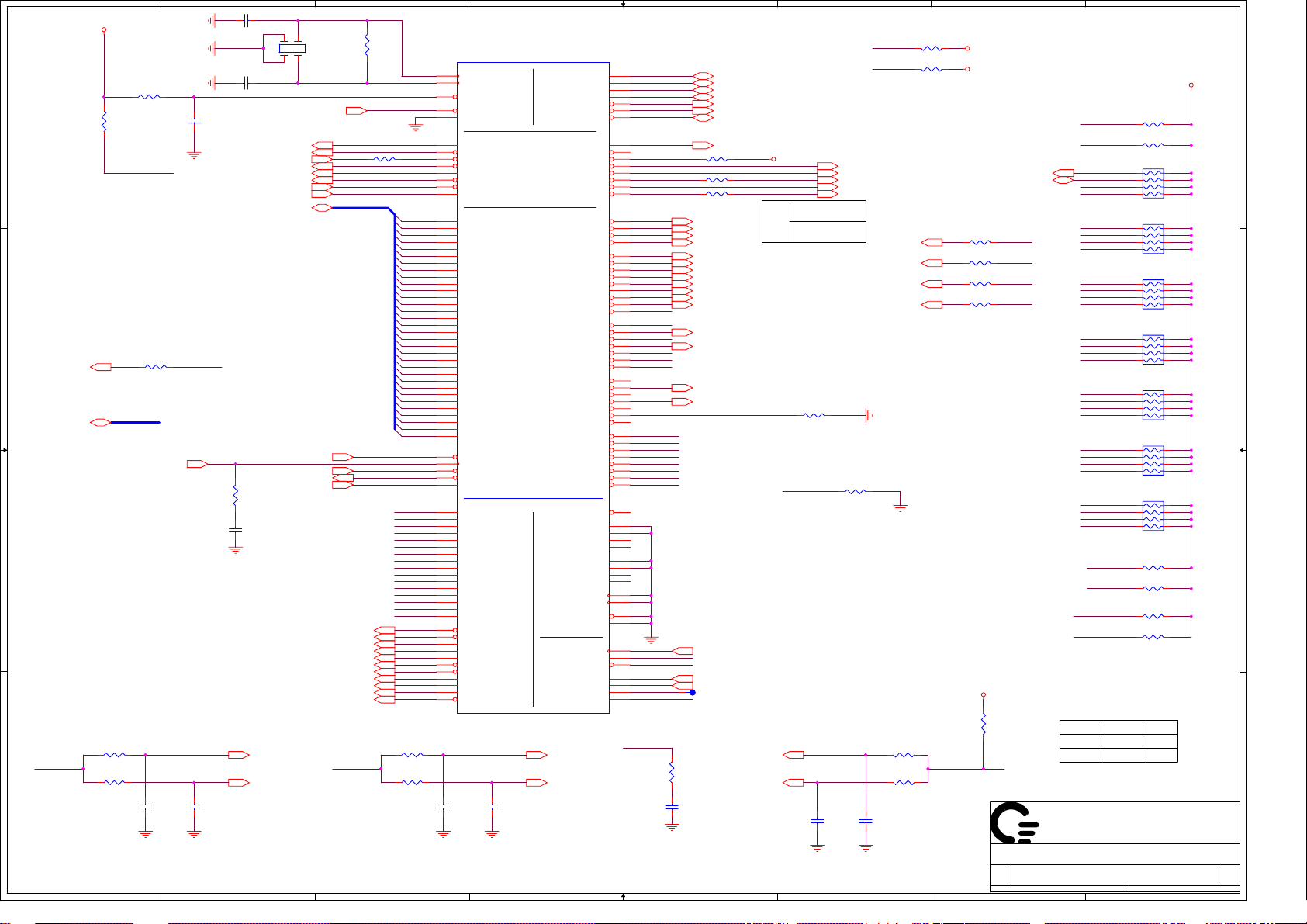

Tonga & Tyler (T2)

A A

VER : 3C

AC/BATT

CONNECTOR

RUN POWER

SW

PG 37

BATT CHARGER

B B

On Board DDR

333 MHZ DDR

333 MHZ DDR

DDR-SODIMM

PG 11

ODD

(Slave)

PG 25

C C

ATA 66/100

HDD

(Master)

PG 25

PG 32

PG 32

ATA 66/100

AC97

Dothan

(478 Micro-FCPGA)

Alviso

1257 PCBGA

PG 5,6,7,8,9

DMI interface

ICH6-M

609 BGA

PG 13,14,15

LPC

LPC

PG 3,4

4X100 / 4X133MHZ

USB2.0 (P0-P2)

USB2.0 (P3)

DC/DC

+3V_SRC

+5VSUS

PG 36

CARDBUS

PCI1510GVF

PG 18

CPU VR

PG 33

LVDS

VGAPG 10,12

3 port USB conn

PG 29

33MHz PCI

PCMCIA

Conn.

PG 19

RESET CKT

PG 31

MINI-PCI

PG 20

Panel Connector

PG 17

CRT Control

PG 17

CLOCKS

PG 16

Thermal

/FAN CTRL

PG 28

AUDIO

PG 21,22

Audio

Jacks

PG 20,21

D D

1

MDC

PG 20

Tip/Ring

Connector

PG 24

SIO(Macallan III)

256 Pins LBGA

PG 26,27

Flash

PG 27

X-Bus

4

PS/2

Keyboard

PG 27

2

Touchpad

PG 24

3

LAN Interface

82562ET

PG 23

5

RJ45 & Magnetic

PG 24

6

QUANTA

Title

Size Document Number Rev

Date: Sheet

COMPUTER

Schematic Block Diagram

VM7 3C

7

145Thursday, July 14, 2005

of

8

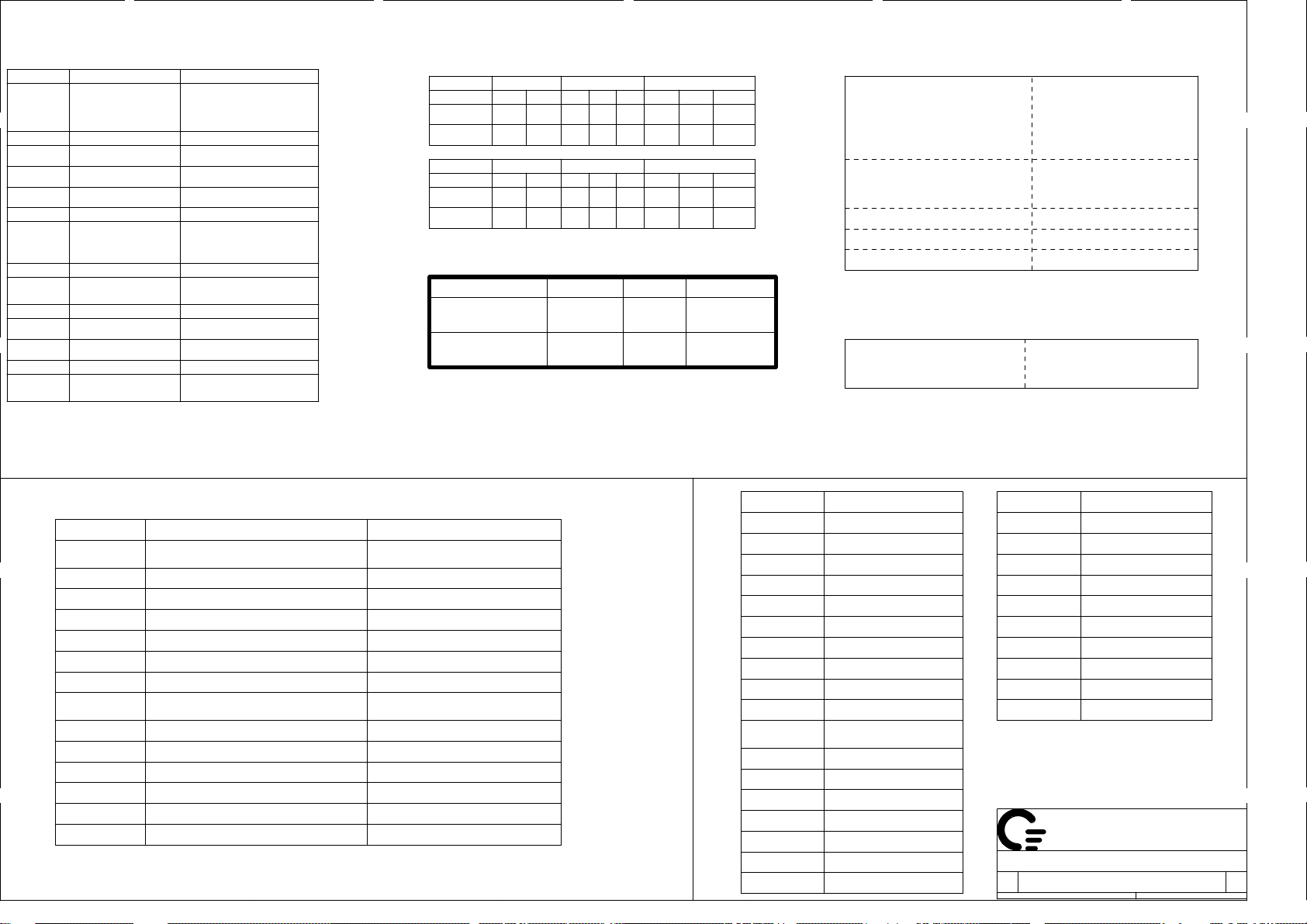

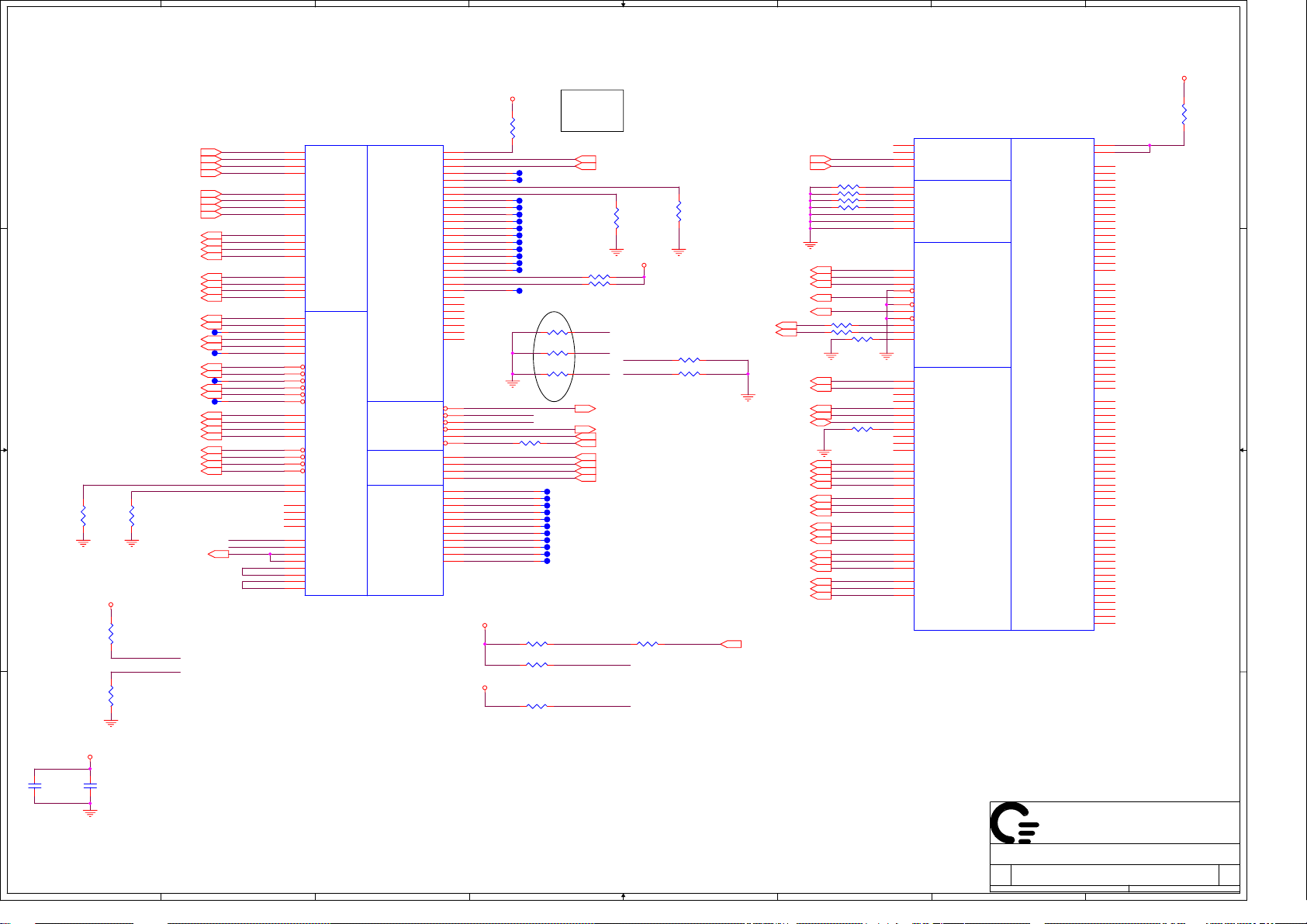

Page 2

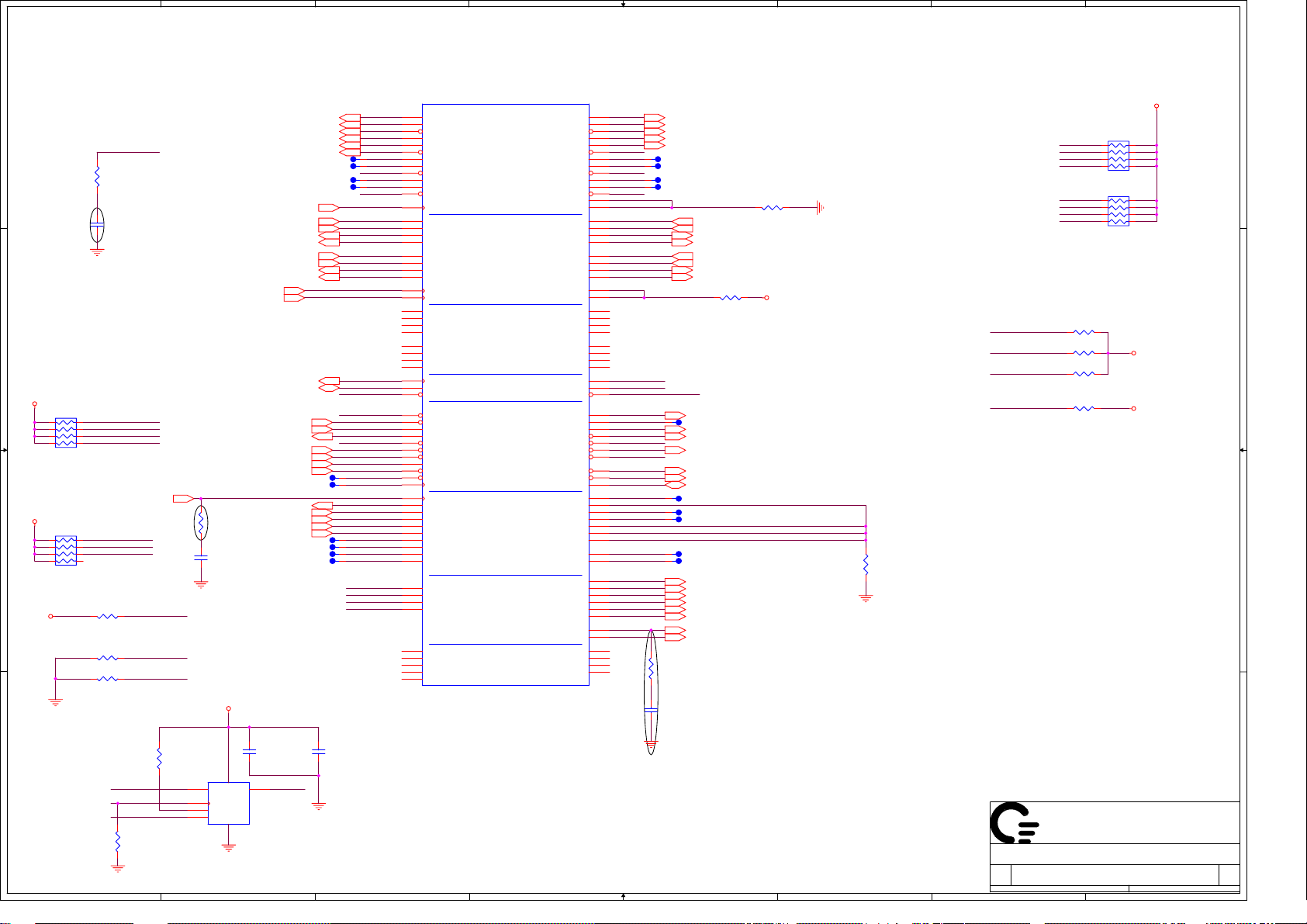

A

B

C

D

E

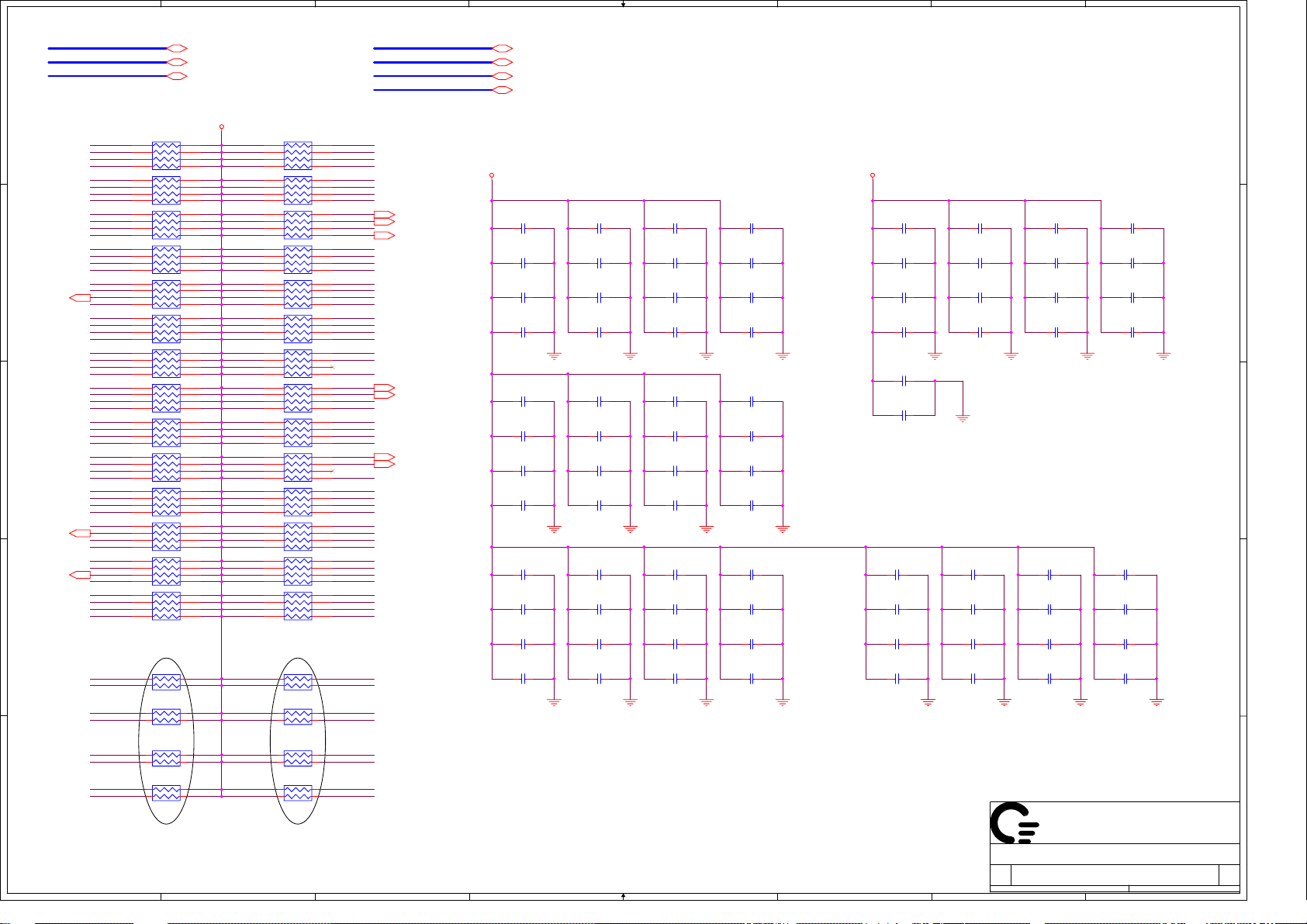

Alviso Strapping Signals and Configuration

Pin Name

CFG[2:0]

Strap Description

FSB Frequency Select

4 4

CFG[3:4]

CFG5

CFG6

CFG7

CFG[8:11]

CFG[12:13]

CFG[14:15]

CFG16

CFG17

CFG18

3 3

CFG19

CFG20

SDVOCRTL

_DATA

NOTE:

Reversed

DMI x2 Select

DDR I / DDR II

CPU Strap

Reversed

XOR/ALL Z test

straps

Reversed

FSB Dynamic ODT

Reversed

CPU core VCC

Select

CPU VTT Select

Reversed

SDVO Present

All strap signals are sampled with respect to the leading

edge of the Alviso GMCH PWORK In signal.

Configuration

000 = Reserved

001 = FSB533

010 = FSB800

011-100 = Reversed

101 = FSB400

110-111 = Reversed

0 = DMI x2

1 = DMI x4

0 = DDR II

1 = DDR I

0 = Prescott

1 = Dothan

00 = Reserved

01 = XOR mode enabled

10 = All Z mode enabled

11 = Normal Operation

(Default)

0 = Dynamic ODT Disabled

1 = Dynamic ODT Enabled

(Default)

0 = 1.05V

1 = 1.5V

0 = 1.05V

1 = 1.2V

0 = No SDVO device present

(Default)

1= SDVO device present

(Default)

(Default)

(Default)

(Default)

(Default)

Page.5

For Dothan A stepping

NB

CFG0

CFG1

1

0

1

01

1

00

FS_B

1

0

0

0

100MHZ

133MHZ

CPU CLOCK

BSEL0 FS_CCFG2

BSEL1

0

0

For Dothan B stepping

100MHZ

133MHZ

CPU

BSEL0BSEL1

001

NB

CFG0

CFG1CFG2

10

000

CLOCK

FS_C

FS_B

1

1

0

1

0

0

PCI TABLE

DEVICE

PCMCIA controller

MINIPCI SLOT REQ3#/GNT3#

IDSEL

AD17

AD19

IRQ

PIRQA#

PIRQC#

PIRQB#

PIRQD#

REQ# / GNT#

REQ1#/GNT1#

FS_A

1

1

FS_A

1

1

ICH6-M Integrated Pull-up

and Pull-down Resistors

EE_DOUT,

GNT[4]#/GPO[48], GNT[5]#/GPO[17],

GNT[6]#/GPO[16],

LAN_RXD[2:0],

LDRQ[0],

ACZ_BIT_CLK,

ACZ_SDOUT, ACZ_SYNC,

DPRSLPVR/TP[1],

USB[7:0][P,N]

DD[7],

LAN_CLK

GNT[3:0],

LDRQ[1]/GPI[41],

PWRBTN#,

ACZ_RST#,

EE_CS,

SDDREQ

GPIO[25],EE_DIN,

LAD[3:0]#/FB[3:0]#,

TP[3]

DPRSTP#/TP[4],

PME#,

ACZ_SDIN[2:0],

SPKR

ICH6 internal 20K pull-ups

ICH6 Internal 20K pull-downs

ICH6 internal 15K pull-downs

ICH6 internal 11.5K pull-downs

ICH6 internal 100K pull-downs

ICH6-M EDS 15825 1.5V2

ICH6-M IDE Integrated Series

Termination Resistors

DD[15:0],

DDACK#, IORDY,

IDEIRQ

DCS3#,

DIOR#, DREQ,DIOW#,

DA[2:0],

DCS1#,

approximately 33 ohm

02

ICH6-M Strapping Signals and Configuration

Pin Name

2 2

1 1

ACZ_SDOUT

ACZ_SYNC

DPRSLPVR

EE_CS

EE_DOUT Reserved

GNT[5]#/GPO[17]#

GNT(6)#/GPO(16)#

GPIO[25]

INTVRMEN

LINKALERT#

REQ[4:1]#

SATALED#

SPKR

TP[3]

All strap signals are sampled on the rising edge of the

NOTE:

ICH6-M's PWROK signal.

A

Strap Description

0=PCI Express Port Config bit 1(default)

1=XOR Chain Entrance Test mode

0=PCI Express Port Config bit 1(default)

1=Reserved

Reserved

Reserved

Boot BIOS Destination Selection

0="Top block swap" mode

1=Normal(default)

0=Enable Internal Vcc2_5V VRM(default)

1=Disable Internal Vcc2_5V VRM

0=Disable Internal VccSus 1.5V VRM(default)

1=Enable Internal VccSus 1.5V VRM

Reserved

XOR Test Chain Selection

Reserved

0=Normal(default)

1=NO Reboot

0=XOR Chain Entrance Test mode

1=Normal(default)

Note

This Signal should not be pulled high.

This Signal should not be pulled high.

This Signal should not be pulled low.

This functionality intended for

debug/testing only.

"Top block swap" ICH6 inverts A16 for

all cycles targeting FWH BIOS space

This Signal has a weak inernal PU

during RSMRST# and is disabled within

100ms after RSMRST# deasserts.

This Signal requires an external PU

This Signal should not be pulled low.

This Signal should not be pulled high.

This Signal should not be pulled low

unless using XOR Chain testing.

B

C

Power Name

+1_5V_LAN

+1_5V_PCIE

+1_5VRUN

+1_5VSUS

+2.5VRUN

+2.5VSUS

+3V562ET

+3VLAN

+3V_SRC

+3VALW

+3VRUN

+3VSUS

+5VRUN

+5VSUS

+15V

+AVDD

+DC_IN

Page#

P.15

P.15

P.4,8,14,15,30,37

P.15,20,30,31,35,37

P.6,8,15,17,37

P.6,8,9,10,11,12,34,37

P.23

P.14,15,20,23,24

P.15,23,36,37

P.3,17,20,24,26,27,28,30,

31,32,36,38

P.3,8,11,12,13,14,15,16,17,

18,20,21,22,24,25,26,27,28,

30,31,33,37

P.3,14,15,17,18,19,20,22,

24,26,28,31,34,35,36

P.15,17,36,37,38+5VALW

P.15,17,20,21,22,24,25,27,

28,30,33,37

P.15,19,20,28,29,34,35,36,

37

P.17,28,36,37

P.21

p.32

D

Power Name

+RTC_PWR3_3V

+VCCP

+VCCRTC

CRTVCC

DCIN+

DC_IN+

PBATT+

PWR_SRC

USBVCC0,USBVCC1,

USBVCC2

VHCORE P.4,33

Page#

P.26,36,38

P.3,4,5,6,8,9,13,15,16,

28,35,37

P.13,15,26,28

P.17

P.32

P.32

P.32,38

P.17,26,30,32,33,34,35,

36,37,38

P.29

QUANTA

Title

Size Document Number Rev

Date: Sheet

COMPUTER

Dothan Processor (Host BUS)

VM7 2A

E

245Thursday, July 14, 2005

of

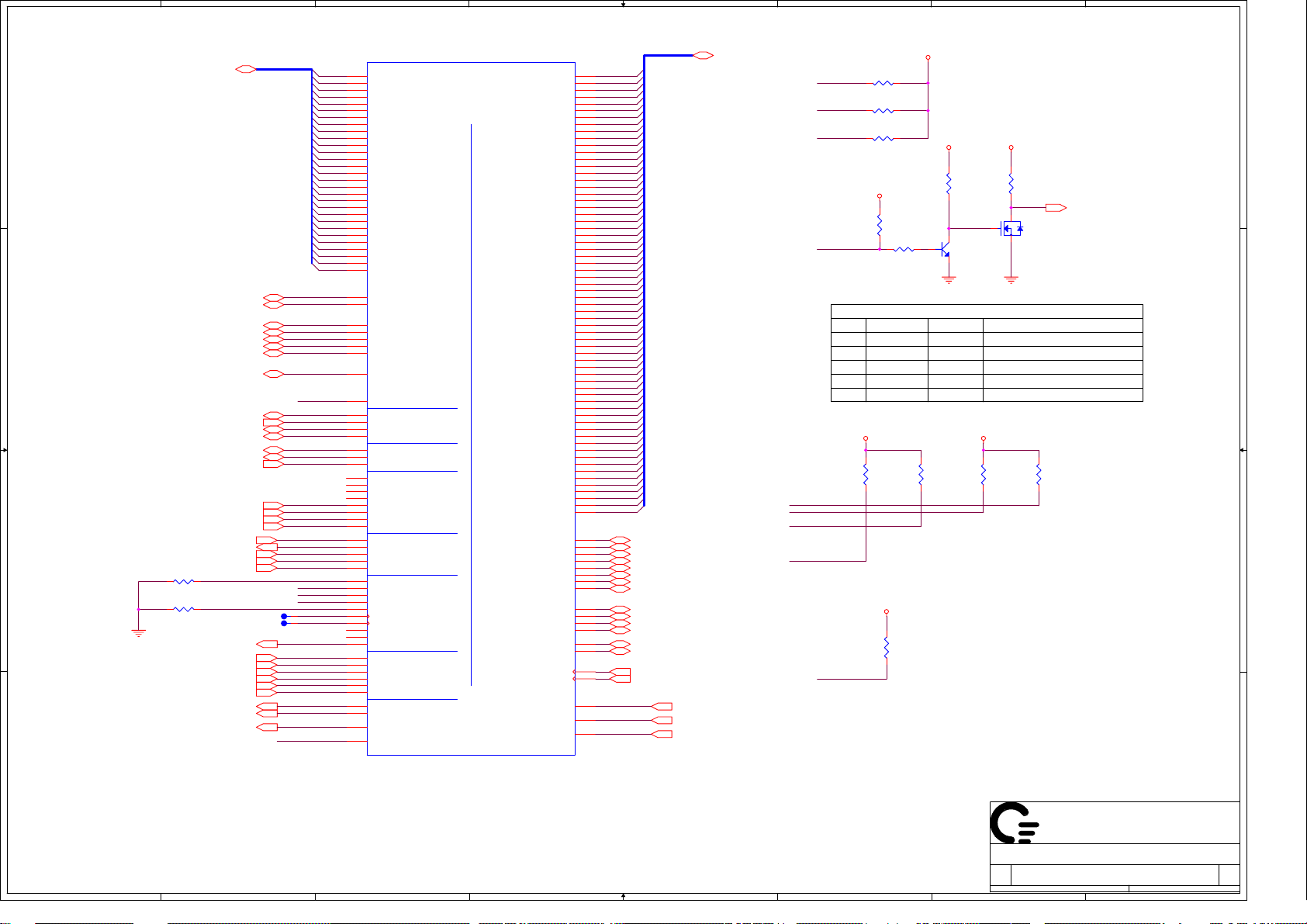

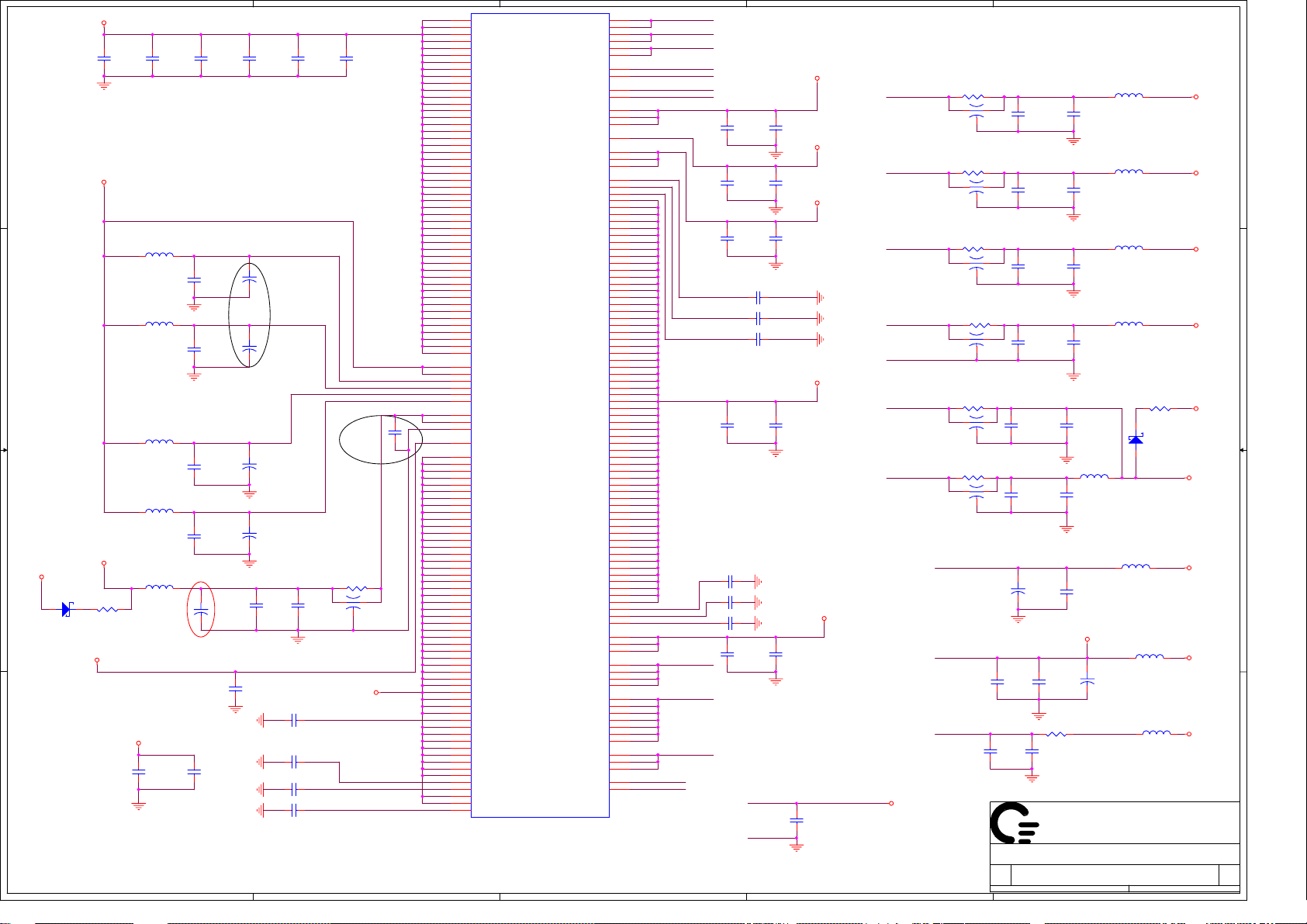

Page 3

1

2

3

4

5

6

7

8

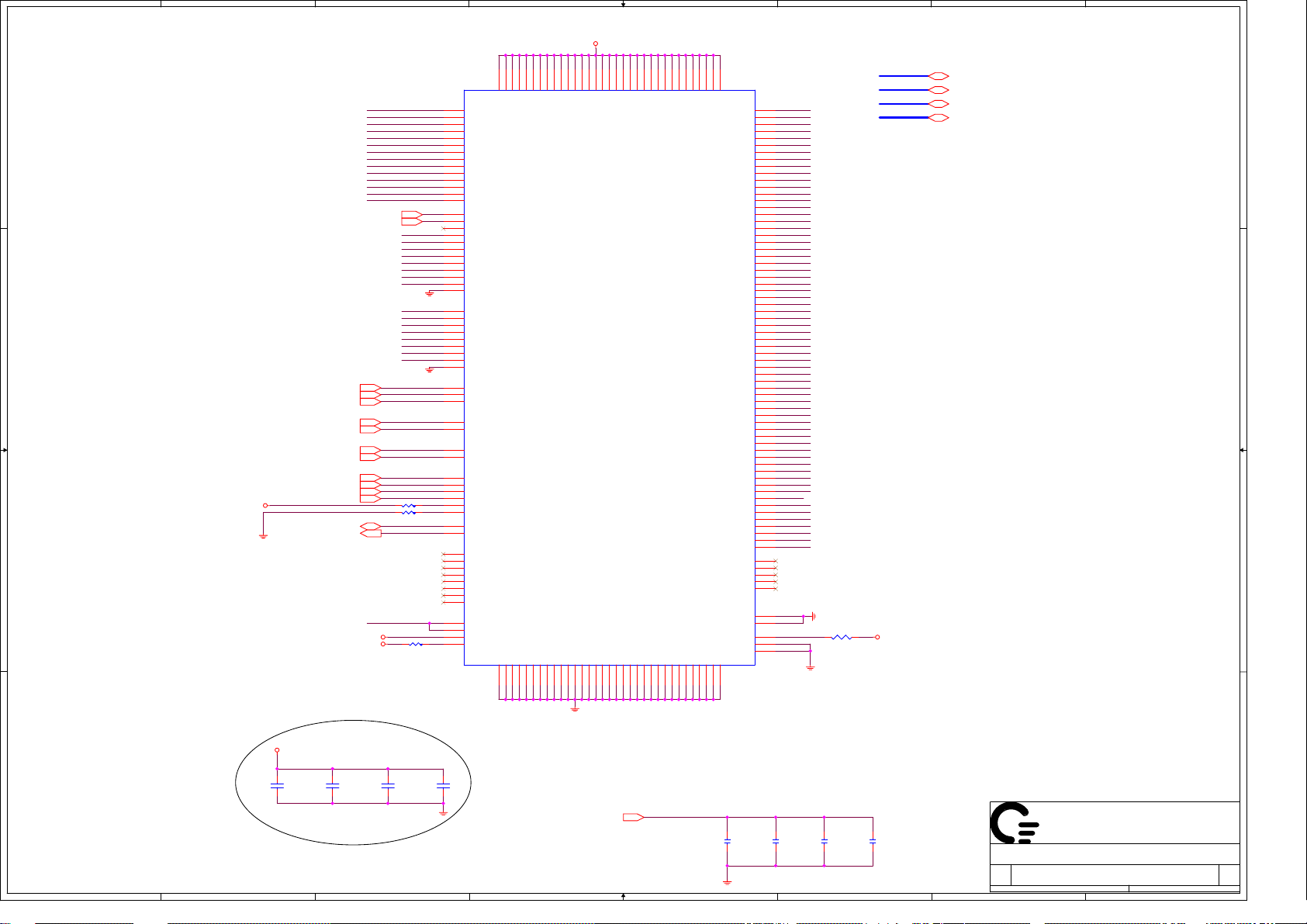

03

R60

56_0402

R71

56_0402

R52

200_0402

+VCCP

12

R59

56_0402

R58

330_NC

Resistor Value

150 ohm +/- 5%

39 ohm +/- 5%

680 ohm +/- 5%

27 ohm +/- 5%

Open

R68

54.9/F_0402

+3VSUS

12

R69

150_0402

+VCCP

12

12

+3VRUN

2

Connect To

VCCP

GND

GND

VCCP

R66

54.9/F_0402

1 2

1 3

R56

1.5K_NC

Q10

3904_NC

+VCCP

+3VALW

R72

330_NC

1 2

31

2

Q9

RHU002N06_NC

Resistor Placement

Within 2.0" of the CPU

Within 2.0" of the CPU

Within 2.0" of the CPU

Within 2.0" of the CPU

Within 2.0" of the CPU

12

R67

39.2/F_0402

12

R65

150_0402

PROCHOT# 27

HA#[3..31]5

A A

B B

C C

R63 27.4/F_0402

R64 680_0402

G1: NC for Dothan and

DPRSTP# for Yonah

CPUPWRGD13

12

12

CPUSLP#5,13

DPRSTP#13

THERMDA28

THERMDC28

-THERMTRIP28

HA#[3..31]

HADSTB0#5

HADSTB1#5

HREQ#05

HREQ#15

HREQ#25

HREQ#35

HREQ#45

ADS#5

HBREQ0#5

BPRI#5

BNR#5

HLOCK#5

HIT#5

HITM#5

DEFER#5

HTRDY#5

RS#05

RS#15

RS#25

SMI#13

T9 PAD

T6 PAD

A20M#

FERR#

IGNNE#

CPUPWRGD

SMI#

DBR#

STPCLK#

CPUSLP#

DPSLP#

THERMDA

THERMDC

-THERMTRIP

CPU_PROCHOT#

TCK

TDO

TDI

TMS

TRST#

A20M#13

FERR#13

IGNNE#13

DBR#31

INTR13

NMI13

STPCLK#13

DPSLP#13

U4A

HA#3

P4

A3#

HA#4

U4

A4#

HA#5

V3

A5#

HA#6

R3

A6#

HA#7 HD#4

V2

A7#

HA#8

W1

A8#

HA#9

T4

A9#

HA#10

W2

A10#

HA#11

Y4

A11#

HA#12

Y1

A12#

HA#13

U1

A13#

HA#14

AA3

A14#

HA#15

Y3

A15#

HA#16

AA2

A16#

HA#17

AF4

A17#

HA#18

AC4

A18#

HA#19

AC7

A19#

HA#20

AC3

A20#

HA#21

AD3

A21#

HA#22

AE4

A22#

HA#23

AD2

A23#

HA#24

AB4

A24#

HA#25

AC6

A25#

HA#26

AD5

A26#

HA#27

AE2

A27#

HA#28

AD6

A28#

HA#29

AF3

A29#

HA#30

AE1

A30#

HA#31

AF1

A31#

U3

ADSTB0#

AE5

ADSTB1#

R2

REQ0#

P3

REQ1#

T2

REQ2#

P1

REQ3#

T1

REQ4#

N2

ADS#

IERR#

A4

IERR#

N4

BREQ0#

J3

BPRI#

L1

BNR#

J2

LOCK#

K3

HIT#

K4

HITM#

L4

DEFER#

C8

BPM0#

B8

BPM1#

A9

BPM2#

C9

BPM3#

M3

TRDY#

H1

RS0#

K1

RS1#

L2

RS2#

C2

A20M#

D3

FERR#

A3

IGNNE#

E4

PWRGOOD

B4

SMI#

A13

TCK

A12

TDO

C12

TDI

C11

TMS

B13

TRST#

A16

ITP_CLK0

A15

ITP_CLK1

B10

PREQ#

A10

PRDY#

A7

DBR#

D1

LINT0

D4

LINT1

C6

STPCLK#

A6

SLP#

B7

DPSLP#

G1

DPRSTP#

B18

THERMDA

A18

THERMDC

C17

THERMTRIP#

B17

PROCHOT#

Dothan Processor

Dothan

REQUEST

PHASE

SIGNALS

ERROR

SIGNALS

ARBITRATION

PHASE

SIGNALS

SNOOP PHASE

SIGNALS

RESPONSE

PHASE

SIGNALS

PC

COMPATIBILITY

SIGNALS

DIAGNOSTIC

& TEST

SIGNALS

EXECUTION

CONTROL

SIGNALS

THERMAL DIODE

1 OF 3

DATA

PHASE

SIGNALS

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN0#

DSTBP0#

DSTBN1#

DSTBP1#

DSTBN2#

DSTBP2#

DSTBN3#

DSTBP3#

DINV0#

DINV1#

DINV2#

DINV3#

DBSY#

DRDY#

BCLK1

BCLK0

INIT#

RESET#

DPWR#

A19

D0#

A25

D1#

A22

D2#

B21

D3#

A24

D4#

B26

D5#

A21

D6#

B20

D7#

C20

D8#

B24

D9#

D24

E24

C26

B23

E23

C25

H23

G25

L23

M26

H24

F25

G24

J23

M23

J25

L26

N24

M25

H26

N25

K25

Y26

AA24

T25

U23

V23

R24

R26

R23

AA23

U26

V24

U25

V26

Y23

AA26

Y25

AB25

AC23

AB24

AC20

AC22

AC25

AD23

AE22

AF23

AD24

AF20

AE21

AD21

AF25

AF22

AF26

C23

C22

K24

L24

W25

W24

AE24

AE25

D25

J26

T24

AD20

M2

H2

B14

B15

CPUINIT#

B5

CPURST#

B11

C19

HD#0

HD#1

HD#2

HD#3

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HD#[0..63]

HDSTBN0# 5

HDSTBP0# 5

HDSTBN1# 5

HDSTBP1# 5

HDSTBN2# 5

HDSTBP2# 5

HDSTBN3# 5

HDSTBP3# 5

HDBI0# 5

HDBI1# 5

HDBI2# 5

HDBI3# 5

DBSY# 5

DRDY# 5

HCLK_CPU# 16

HCLK_CPU 16

CPUINIT# 13

CPURST# 5

DPWR# 5

HD#[0..63] 5

-THERMTRIP

IERR#

CPUPWRGD

CPU_PROCHOT#

TDI

TMS

TDO

CPURST#

1 2

1 2

1 2

ITP disable guidelines

Signal

TDI

TMS VCCP

TRST#

TCK

TDO

+VCCP

12

DBR#

D D

QUANTA

Title

Size Document Number Rev

1

2

3

4

5

6

Date: Sheet

COMPUTER

Dothan Processor (Host BUS)

VM7 2B

7

345Thursday, July 14, 2005

of

8

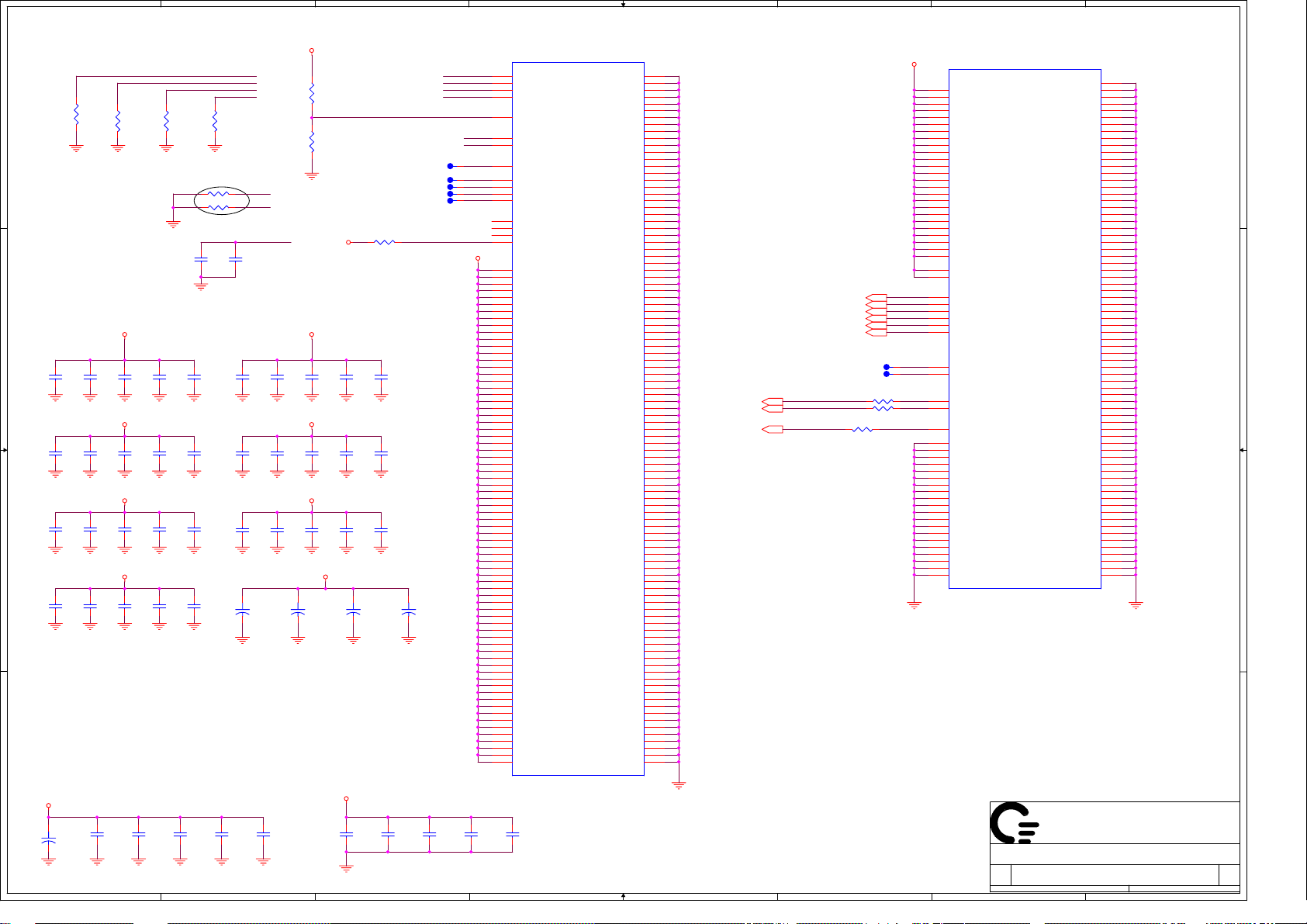

Page 4

1

2

3

4

5

6

7

8

+VCCP

T7 PAD

T8 PAD

T4 PAD

T2 PAD

T5 PAD

CPU_VCCA

+

C36

270U/4V_NC

COMP0

COMP1

COMP2

COMP3

GTLREF0

COMP0

COMP1

COMP2

COMP3

R214

54.9/F_0402

1 2

R51 1K_NC

R57 1K_NC

12

12

12

C358

10U/4V/0805

12

C392

10U/4V/0805

12

C395

10U/4V/0805

C375

10U/4V/0805

1 2

TEST1

TEST2

CPU_VCCA

C387

10U/4V/0805

12

C365

10U/4V/0805

12

C394

10U/4V/0805

C398

10U/4V/0805

1 2

+

C350

270U/4V_NC

C399

C370

C360

C377

R213

27.4/F_0402

1 2

C386

.01U/25V/0402

12

C354

10U/4V/0805

12

C373

10U/4V/0805

12

C49

10U/4V/0805

C47

10U/4V/0805

1 2

R39

R40

54.9/F_0402

A A

B B

C C

27.4/F_0402

1 2

1 2

Place pulldown resistors within 0.5" of COMP pins

VHCORE

12

12

C357

10U/4V/0805

VHCORE

12

C364

10U/4V/0805

12

C371

10U/4V/0805

VHCORE

C393

10U/4V/0805

1 2

12

10U/4V/0805

12

10U/4V/0805

12

10U/4V/0805

10U/4V/0805

1 2

C396

10U/4V/0805

12

C43

10U/4V/0805

12

C353

10U/4V/0805

C359

10U/4V/0805

1 2

VHCORE

12

C378

10U/4V/0805

VHCORE

12

C367

10U/4V/0805

VHCOREVHCORE

C391

10U/4V/0805

1 2

+

R37

1K/F_0402

1 2

R36

2K/F_0402

1 2

+1_5VRUN

12

C356

10U/4V/0805

12

C54

10U/4V/0805

C355

10U/4V/0805

1 2

VHCORE

C368

270U/4V_NC

Place voltage

divider within

0.5" of GTLREF

pin

R215

0_0603

12

C52

10U/4V/0805

12

C397

10U/4V/0805

C376

10U/4V/0805

1 2

+

C349

270U/4V_NC

12

12

C45

10U/4V/0805

12

C372

10U/4V/0805

C374

10U/4V/0805

1 2

Total caps = 2633 uF

ESR = 15m ohm/5 // 5m ohm/25 // 5m ohm/15

D D

+VCCP

12

12

+

C69

150U/6.3V/45mO

1

12

C383

.1U/10V/0402

12

C389

.1U/10V/0402

C385

.1U/10V/0402

12

C382

.1U/10V/0402

2

12

C390

.1U/10V/0402

+VCCP

12

C384

.1U/10V/0402

12

C379

.1U/10V/0402

3

12

C381

.1U/10V/0402

P25

P26

AB2

AB1

AD26

TEST1

TEST2

AF7

AC1

E26

AC26

VHCORE

D18

D20

D22

E17

E19

E21

G21

H22

K22

V22

W21

Y22

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC9

AC11

AC13

AC15

AC17

AC19

AD8

AD10

AD12

AD14

AD16

AD18

AE9

AE11

AE13

AE15

AE17

AE19

AF8

AF10

AF12

AF14

AF16

AF18

12

C380

.1U/10V/0402

U4B

COMP0

COMP1

COMP2

COMP3

GTLREF0

C5

TEST1

F23

TEST2

B2

NC1

C3

RSVD2

RSVD3

RSVD4

RSVD5

VCCA3

N1

VCCA2

B1

VCCA1

F26

VCCA0

D6

VCC00

D8

VCC01

VCC02

VCC03

VCC04

E5

VCC05

E7

VCC06

E9

VCC07

VCC08

VCC09

VCC10

F6

VCC11

F8

VCC12

F18

VCC13

F20

VCC14

F22

VCC15

G5

VCC16

VCC17

H6

VCC18

VCC19

J5

VCC20

J21

VCC21

VCC22

U5

VCC23

V6

VCC24

VCC25

W5

VCC26

VCC27

Y6

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

Dothan Processor

12

.1U/10V/0402

C388

Dothan

2 OF 3

POWER,

GROUND,

RESERVED

SIGNALS

4

VSS00

VSS01

VSS02

VSS03

VSS04

VSS05

VSS06

VSS07

VSS08

VSS09

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

A2

A5

A8

A11

A14

A17

A20

A23

A26

B3

B6

B9

B12

B16

B19

B22

B25

C1

C4

C7

C10

C13

C15

C18

C21

C24

D2

D5

D7

D9

D11

D13

D15

D17

D19

D21

D23

D26

E3

E6

E8

E10

E12

E14

E16

E18

E20

E22

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

M4

M5

M21

M24

N3

N6

N22

N23

N26

P2

P5

P21

P24

R1

R4

SELPSB2_CLK6,16

SELPSB1_CLK6,16

STP_CPU#14,16,33

5

CPU_VID033

CPU_VID133

CPU_VID233

CPU_VID333

CPU_VID433

CPU_VID533

T1 PAD

T3 PAD

SELPSB2_CLK

SELPSB1_CLK

R50 0_NC

Do not install R61 for

Dothan-A and install for

Dothan-B

6

R61

0_NC

R62

0_0402

1 2

1 2

12

+VCCP

BSEL0

BSEL1

U4C

D10

D12

D14

D16

E11

E13

E15

F10

F12

F14

F16

K6

L5

L21

M6

M22

N5

N21

P6

P22

R5

R21

T6

T22

U21

P23

W4

E2

F2

F3

G3

G4

H4

AE7

AF6

C16

C14

E1

R6

R22

R25

T3

T5

T21

T23

T26

U2

U6

U22

U24

V1

V4

V5

V21

V25

W3

W6

Dothan Processor

W23

VSS120

VCCP0

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

POWER, GROUND AND NC

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCP17

VCCP18

VCCP19

VCCP20

VCCP21

VCCP22

VCCP23

VCCP24

VCCQ0

VCCQ1

VID0

VID1

VID2

VID3

VID4

VID5

VCCSENSE

VSSSENSE

BSEL0

BSEL1

PSI

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

Dothan

3 OF 3

VID

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191VSS119

W26

Y2

Y5

Y21

Y24

AA1

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE3

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF2

AF5

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF24W22

QUANTA

Title

Size Document Number Rev

Date: Sheet

COMPUTER

Dothan Processor (POWER/NC)

VM7 2B

7

04

445Thursday, July 14, 2005

of

8

Page 5

1

2

3

4

5

6

7

8

05

HXRCOMP

12

R90

+VCCP

12

+VCCP

12

12

12

+VCCP

12

+VCCP

12

12

24.9/F_0402

R88

54.9/F_0402

HXSCOMP

R92

221/F_0402

HXSWING

R94

100/F_0402

HYRCOMP

R111

24.9/F_0402

R104

54.9/F_0402

HYSCOMP

R108

221/F_0402

HYSWING

R109

100/F_0402

C112

.1U/10V/0402

1 2

C136

.1U/10V/0402

1 2

A A

B B

C C

HD#[0..63]3

HD#[0..63]

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

W6

W8

W7

W1

W3

W2

E4

E1

F4

H7

E2

F1

E3

D3

K7

F2

J7

J8

H6

F3

K8

H5

H1

H2

K5

K6

J4

G3

H3

J1

L5

K4

J5

P7

L7

J3

P5

L3

U7

V6

R6

R5

P3

T8

R7

R8

U8

R4

T4

T5

R1

T3

V8

U6

U3

V5

U2

U1

Y5

Y2

V4

Y7

Y3

Y6

C1

C2

D1

T1

L1

P1

U8A

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

ALVISO

HADSTB0#

HADSTB1#

HCPURST#

HOST

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HCPUSLP#

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADS#

HVREF

HBNR#

HBPRI#

BREQ0#

HCLKINN

HCLKINP

HDBSY#

HDEFER#

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HDPWR#

HDRDY#

HEDRDY#

HHIT#

HHITM#

HLOCK#

HPCREQ#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HRS0#

HRS1#

HRS2#

HTRDY#

G9

C9

E9

B7

A10

F9

D8

B10

E10

G10

D9

E11

F10

G11

G13

C10

C11

D11

C12

B13

A12

F12

G12

E12

C13

B11

D13

A13

F13

F8

B9

E13

J11

A5

D5

E7

H10

AB1

AB2

C6

E6

H8

K3

T7

U5

G6

F7

G4

K1

R3

V3

G5

K2

R2

W4

F6

D4

D6

B3

A11

A7

D7

B8

C7

A8

A4

C5

B4

G8

B5

HA#[3..31]

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HCPUSLP#_GMCH

HA#[3..31] 3

ADS# 3

HADSTB0# 3

HADSTB1# 3

BNR# 3

BPRI# 3

HBREQ0# 3

CPURST# 3

HCLK_MCH# 16

HCLK_MCH 16

DBSY# 3

DEFER# 3

HDBI0# 3

HDBI1# 3

HDBI2# 3

HDBI3# 3

DPWR# 3

DRDY# 3

HDSTBN0# 3

HDSTBN1# 3

HDSTBN2# 3

HDSTBN3# 3

HDSTBP0# 3

HDSTBP1# 3

HDSTBP2# 3

HDSTBP3# 3

HIT# 3

HITM# 3

HLOCK# 3

HREQ#0 3

HREQ#1 3

HREQ#2 3

HREQ#3 3

HREQ#4 3

RS#0 3

RS#1 3

RS#2 3

HTRDY# 3

+VCCP

R283

100/F_0402

1 2

HVREF

12

C452

.1U/10V/0402

1 2

T81

PAD

T10

PAD

1 2

R79

0_NC

Do not install R79 for Dothan-A and install for Dothan-B

Populate for Dothen

R79

Depopuate for

Dothen-Celeron

R277

200/F_0402

CPUSLP# 3,13

D D

QUANTA

Title

Size Document Number Rev

1

2

3

4

5

6

Date: Sheet

COMPUTER

Alviso (Host)

VM7 2B

7

545Thursday, July 14, 2005

of

8

Page 6

1

2

3

4

5

6

7

8

06

VCC3G_PCIE

+VCCP

CFG0

SELPSB1_CLK

SELPSB2_CLK

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

DOT96#

DOT96

TP_NC1

TP_NC2

TP_NC3

TP_NC4

TP_NC5

TP_NC6

TP_NC7

TP_NC8

TP_NC9

TP_NC10

TP_NC11

+2.5VRUN

+VCCP

12

R287

10K_0402

1 2

R304

100_0402

1 2

1 2

1 2

A A

U8C

MCLK2+

MCLK5+

MCLK2-

MCLK5-

SMXSLEW

SMYSLEW

AA31

AB35

AC31

AD35

AA35

AB31

AC35

AA33

AB37

AC33

AD37

AA37

AB33

AC37

AM33

AE11

AJ34

AC10

AN33

AE10

AJ33

AD10

AP21

AM21

AH21

AK21

AN16

AM14

AH15

AG16

AF22

AF16

AP14

AL15

AM11

AN10

AK10

AK11

AF37

AE27

AE28

AF10

Y31

Y33

AL1

AF6

AK1

AF5

AD1

AF9

DMIRXN0

DMIRXN1

DMIRXN2

DMIRXN3

DMIRXP0

DMIRXP1

DMIRXP2

DMIRXP3

DMITXN0

DMITXN1

DMITXN2

DMITXN3

DMITXP0

DMITXP1

DMITXP2

DMITXP3

SM_CK0

SM_CK1

SM_CK2

SM_CK3

SM_CK4

SM_CK5

SM_CK0#

SM_CK1#

SM_CK2#

SM_CK3#

SM_CK4#

SM_CK5#

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

SM_OCDCOMP0

SM_OCDCOMP1

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

SMRCOMPN

SMRCOMPP

SMVREF0

SMVREF1

SMXSLEWIN

SMXSLEWOUT

SMYSLEWIN

SMYSLEWOUT

ALVISO

DMIDDR MUXING

CFG/RSVD

PM

DREF_SSCLKN

LCKNC

DREF_SSCLKP

DMI_TXN014

DMI_TXN114

DMI_TXN214

DMI_TXN314

DMI_TXP014

DMI_TXP114

DMI_TXP214

DMI_TXP314

DMI_RXN014

DMI_RXN114

DMI_RXN214

DMI_RXN314

DMI_RXP014

DMI_RXP114

DMI_RXP214

DMI_RXP314

T91PAD

T89PAD

T92

T90

MCLK0+

MCLK1+

MCLK3+

MCLK4+

MCLK0MCLK1-

MCLK3MCLK4-

CKE0

CKE1

CKE2

CKE3

-CSA0

-CSA1

-CSA2

-CSA3

M_OCDCOMP0

M_OCDCOMP1

M_RCOMPN

M_RCOMPP

MCLK0+12

MCLK1+12

12

R305

40.2/F_0402

M_RCOMPN

M_RCOMPP

MCLK3+11

MCLK4+11

MCLK0-12

MCLK1-12

PAD

MCLK3-11

MCLK4-11

PAD

CKE010,12

CKE110,12

CKE210,11

CKE310,11

-CSA010,12

-CSA110,12

-CSA210,11

-CSA310,11

MVREF11,12,34

B B

12

R306

40.2/F_0402

Route as short

C C

as possible.

+2.5VSUS

12

R311

80.6/F_0402

12

R309

80.6/F_0402

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

BM_BUSY#

EXT_TS0#

EXT_TS1#

THRMTRIP#

PWROK

RSTIN#

DREF_CLKN

DREF_CLKP

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

G16

H13

G14

F16

F15

G15

E16

D17

J16

D15

E15

D14

E14

H12

C14

H15

J15

H14

G22

G23

D23

G25

G24

J17

A31

A30

D26

D25

J23

J21

H22

F5

AD30

AE29

A24

A23

C37

D37

AP37

AN37

AP36

AP2

AP1

AN1

B1

A2

B37

A36

A37

PM_EXTTS#0

PM_EXTTS#1

PLTRST#_R

T79

PAD

T70

PAD

PAD

T78

T82 PAD

T80 PAD

T68 PAD

PAD

T69

T71 PAD

T84

PAD

T72 PAD

T83 PAD

T86

PAD

T85

PAD

T77 PAD

1 2

R267

150/F_NC

1 2

R258

150/F_NC

1 2

R259

150/F_NC

R285

10K_0402

R282

10K_0402

R96

56_0402

CFG[2:0]

001=FSB533

010=FSB800

101=FSB400

R273

1K_NC

R276

1K_NC

CRT_B

CRT_G

CRT_R

DOT96# 16

DOT96 16

DREFSSCLK# 16

DREFSSCLK 16

T95

PAD

T32

PAD

T33

PAD

T97

PAD

T96

PAD

T93

PAD

T12

PAD

T11

PAD

T15

PAD

T13

PAD

T14

PAD

PM_EXTTS#0

PM_EXTTS#1

THERMTRIP_GMCH#

SELPSB1_CLK 4,16

SELPSB2_CLK 4,16

12

R231

2.2K_NC

Low=DDR2

High=DDR(Default)

+2.5VRUN

BIA_PWM

FPBACK

PM_BMBUSY# 14

THERMTRIP_GMCH# 28

IMVP_PWRGD 14,31,33

PLTRST# 13,26

1 2

R286 0_NC

12

R280

2.2K_NC

Low=DMIx2

High=DMIx4(Default)

R274 100K/F_0402_NC

R275 100K/F_0402_NC

CLK_MCH_3GPLL#16

CLK_MCH_3GPLL16

VSYNC17

HSYNC17

TXLCLKOUT-17

TXLCLKOUT+17

TXUCLKOUT-17

TXUCLKOUT+17

EXTTS#0 26

CLK_DDC217

DAT_DDC217

CRT_B17

CRT_G17

CRT_R17

R278 39_0402

R279 39_0402

BIA_PWM26

FPBACK17

PNL_CLK17

PNL_DATA17

FPVCC17,27

TXLOUT0-17

TXLOUT1-17

TXLOUT2-17

TXLOUT0+17

TXLOUT1+17

TXLOUT2+17

TXUOUT0-17

TXUOUT1-17

TXUOUT2-17

TXUOUT0+17

TXUOUT1+17

TXUOUT2+17

R229 150_0402

R230 150_0402

R260 150_0402

1 2

R290 4.99K/F_0402

Refer chekc

list V1_601

P.30

1 2

1 2

1 2

R284

255/F_0402

1 2

R262

1.5K/F_0402

AB29

AC29

H24

H25

A15

C16

A17

J18

B15

B16

B17

E24

E23

E21

D21

C20

B20

A19

B19

H21

G21

J20

E25

F25

C23

C22

F23

F22

F26

C33

C31

F28

F27

B30

B29

C25

C24

B34

B33

B32

A34

A33

B31

C29

D28

C27

C28

D27

C26

U8F

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV_IRTNB

TV_IRTNC

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CTRL

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

ALVISO

MISC

TV VGA LVDS

EXP_COMPI

EXP_ICOMPO

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

EXP_TXN7

PCI-EXPRESS GRAPHICS

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

D36

D34

E30

F34

G30

H34

J30

K34

L30

M34

N30

P34

R30

T34

U30

V34

W30

Y34

D30

E34

F30

G34

H30

J34

K30

L34

M30

N34

P30

R34

T30

U34

V30

W34

E32

F36

G32

H36

J32

K36

L32

M36

N32

P36

R32

T36

U32

V36

W32

Y36

D32

E36

F32

G36

H32

J36

K32

L36

M32

N36

P32

R36

T32

U36

V32

W36

VCC3G_PCIE_R

R272

24.9/F_0402

1 2

SMDDR_VTERM

12

C169

D D

.1U/10V/0402

Need to place these caps

near Alviso SMVREF pins.

12

1

C168

.1U/10V/0402

QUANTA

Title

Custom

Size Document Number Rev

2

3

4

5

6

Date: Sheet

COMPUTER

Alviso (VGA,DMI)

VM7 2B

7

of

645Thursday, July 14, 2005

8

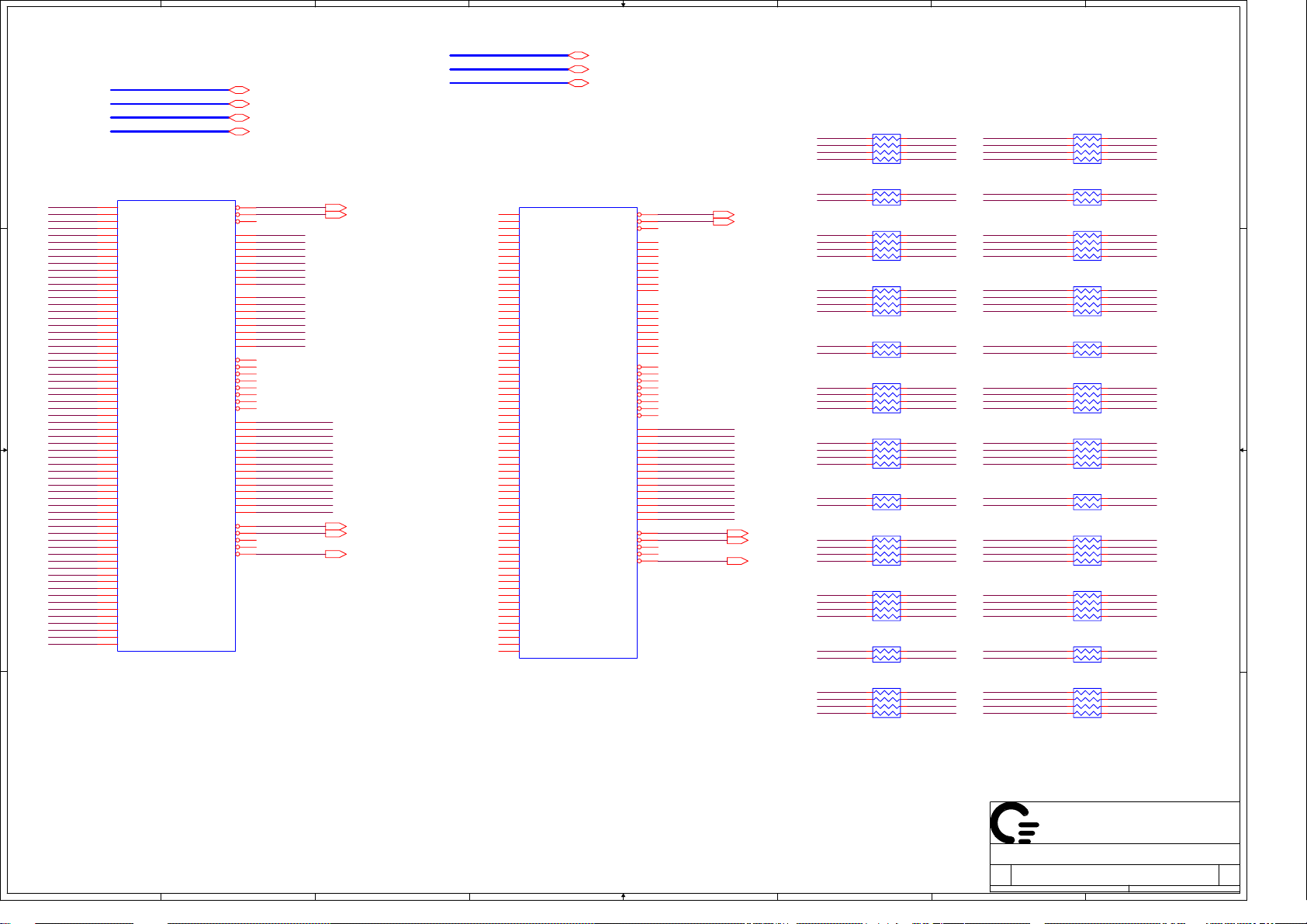

Page 7

1

2

3

4

5

6

7

8

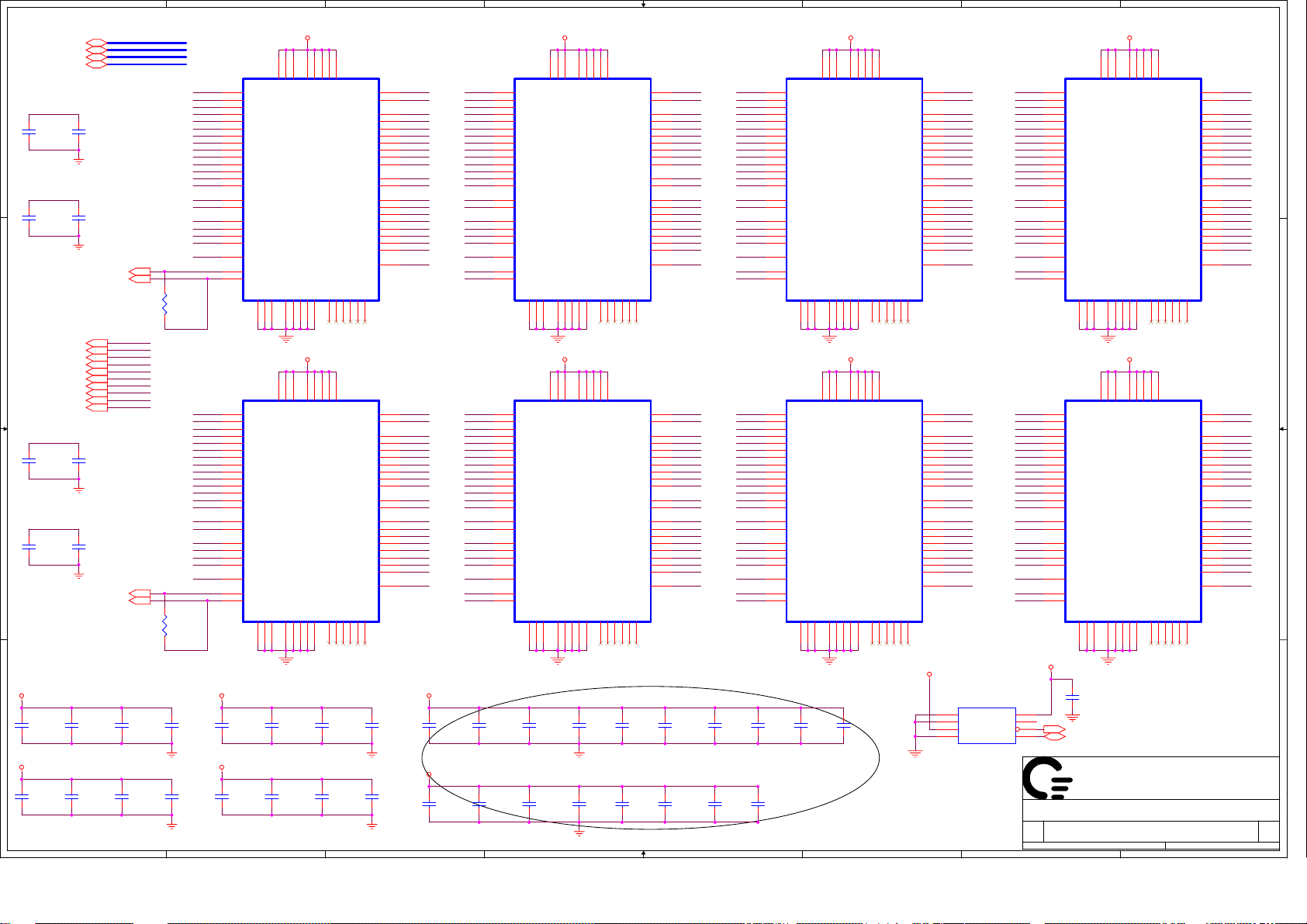

RMD[0..63]

RDQM[0..7]

MAB[0..13]

MAA[0..13]

AG35

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AM9

AP7

AP11

AP10

AM7

AN5

AN6

AN3

AP3

AP6

AM6

AM3

AK2

AK3

AG2

AG1

AM2

AH3

AG3

AE3

AD6

AC4

AD4

AD5

-CSA[0..3]

CKE[0..3]

U8B

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

AL9

SADQ33

AL6

SADQ34

SADQ35

SADQ36

SADQ37

AL7

SADQ38

SADQ39

SADQ40

SADQ41

SADQ42

SADQ43

SADQ44

SADQ45

AL4

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SADQ51

AL3

SADQ52

SADQ53

SADQ54

SADQ55

AF3

SADQ56

SADQ57

SADQ58

SADQ59

AF2

SADQ60

AF1

SADQ61

SADQ62

SADQ63

ALVISO

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

DDR SYSTEM MEMORY A

SA_RCVENIN#

SA_RCVENOUT#

A A

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

B B

C C

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

SA_BS0#

SA_BS1#

SA_BS2#

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

SA_WE#

MAB[0..13] 10,11

MAA[0..13] 10,12

-CSA[0..3] 6,10,11,12

CKE[0..3] 6,10,11,12

AK15

AK16

AL21

AJ37

AP35

AL29

AP24

AP9

AP4

AJ2

AD3

AK36

AP33

AN29

AP23

AM8

AM4

AJ1

AE5

AK35

AP34

AN30

AN23

AN8

AM5

AH1

AE4

MAA0

AL17

MAA1

AP17

MAA2

AP18

MAA3

AM17

MAA4

AN18

MAA5

AM18

MAA6

AL19

MAA7

AP20

MAA8

AM19

MAA9

AL20

MAA10

AM16

MAA11

AN20

MAA12

AM20

MAA13

AM15

AN15

AP16

AF29

AF28

AP15

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

A_BS0# 10,12

A_BS1# 10,12

-DCASA 10,12

-DRASA 10,12

-DMWA 10,12

RDQS[0..7]

AE31

AE32

AG32

AG36

AE34

AE33

AF31

AF30

AH33

AH32

AK31

AG30

AG34

AG33

AH31

AJ31

AK30

AJ30

AH29

AH28

AK29

AH30

AH27

AG28

AF24

AG23

AJ22

AK22

AH24

AH23

AG22

AJ21

AG10

AH11

AH10

AG9

AG8

AH8

AK9

AK6

AH5

AK8

AK4

AG5

AG4

AD8

AD9

AH4

AG6

AE8

AD7

AC5

AB8

AB6

AA8

AC8

AC7

AA4

AA5

U8G

SBDQ0

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

SBDQ15

SBDQ16

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQ32

SBDQ33

SBDQ34

SBDQ35

SBDQ36

SBDQ37

AJ9

SBDQ38

SBDQ39

AJ7

SBDQ40

SBDQ41

AJ4

SBDQ42

SBDQ43

SBDQ44

AJ8

SBDQ45

AJ5

SBDQ46

SBDQ47

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

SBDQ53

SBDQ54

SBDQ55

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

ALVISO

RMD[0..63] 10,11,12

RDQM[0..7] 10,11,12

RDQS[0..7] 10,11,12

SB_BS0#

SB_BS1#

SB_BS2#

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS0#

SB_DQS1#

SB_DQS2#

SB_DQS3#

SB_DQS4#

SB_DQS5#

SB_DQS6#

SB_DQS7#

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

DDR SYSTEM MEMORY B

SB_CAS#

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

SB_WE#

AJ15

AG17

AG21

AF32

AK34

AK27

AK24

AJ10

AK5

AE7

AB7

AF34

AK32

AJ28

AK23

AM10

AH6

AF8

AB4

AF35

AK33

AK28

AJ23

AL10

AH7

AF7

AB5

AH17

AK17

AH18

AJ18

AK18

AJ19

AK19

AH19

AJ20

AH20

AJ16

AG18

AG20

AG15

AH14

AK14

AF15

AF14

AH16

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MAB13

B_BS0# 10,11

B_BS1# 10,11

-DCASB 10,11

-DRASB 10,11

-DMWB 10,11

RMD59

RMD63

6

RMD58

4

RMD62

2

RDQS7

4

2

RMD57

6

RMD61

4

RMD56

2

RMD51

RMD55

6

RMD54

4

RMD50

2

RDQM6 DQM6

4

RDQS6

2

RMD48

RMD53

6

RMD52

4

RMD49

2

RMD43

RMD47

6

RMD42

4

RMD46

2

RDQM5

4

RDQS5

2

RMD45

RMD40

6

RMD41

4

RMD44

2

RMD38

RMD39

6

4

RMD34

2

RDQM4

4

RDQS4

2

RMD32

RMD33

6

RMD37

4

RMD36

2

MD59

78

MD63

5

MD58

3

MD62

1

RN3

10X4

DQS7

3

DQM7RDQM7 DQM3RDQM3

1

RN4

10X2

MD60RMD60

78

MD57

5

MD61

3

MD56

1

RN5

10X4

MD51

78

MD55

5

MD54

3

MD50

1

RN6

10X4

3

DQS6

1

RN7

10X2

MD48

78

MD53

5

MD52

3

MD49

1

RN8

10X4

MD43

78

MD47

5

MD42

3

MD46

1

RN9

10X4

DQM5

3

DQS5

1

RN10

10X2

MD45

78

MD40

5

MD41

3

MD44

1

RN11

10X4

MD38

78

MD39

5

MD35RMD35

3

MD34

1

RN12

10X4

DQM4

3

DQS4

1

RN13

10X2

MD32

78

MD33

5

MD37

3

MD36

1

RN14

10X4

RN17

10X4

RN18

10X2

RN19

10X4

RN20

10X4

RN21

10X2

RN22

10X4

RN23

10X4

RN24

10X2

RN25

10X4

RN26

10X4

RN27

10X2

RN28

10X4

MD26

78

MD31RMD31

5

MD30RMD30

3

MD27

1

DQS3

3

1

MD29

78

MD28

5

MD25RMD25

3

MD24

1

MD23

78

MD22

5

MD18

3

MD19RMD19

1

DQM2

3

1

MD20

78

MD21

5

MD16

3

MD17RMD17

1

MD11

78

MD14

5

MD10

3

MD15RMD15

1

DQM1

3

DQS1

1

MD12

78

MD13

5

MD9

3

MD8

1

MD7RMD7

78

MD2

5

MD3

3

MD6RMD6

1

DQS0

3

DQM0RDQM0

1

MD5

78

MD4

5

MD0

3

MD1

1

RMD26

RMD27

RDQS3

RMD29

RMD28

RMD24

RMD23

RMD22

RMD18

RDQM2

RDQS2 DQS2

RMD20

RMD21

RMD16

RMD11

RMD14

RMD10

RDQM1

RDQS1

RMD12

RMD13

RMD9

RMD8

RMD2

RMD3

RDQS0

RMD5

RMD4

RMD0

RMD1

6

4

2

4

2

6

4

2

6

4

2

4

2

6

4

2

6

4

2

4

2

6

4

2

6

4

2

4

2

6

4

2

07

D D

QUANTA

Title

Size Document Number Rev

1

2

3

4

5

6

Date: Sheet

COMPUTER

Alviso (DDR)

VM7 2B

7

745Thursday, July 14, 2005

of

8

Page 8

5

+VCCP

C470

L17

BLM11A121S

L18

BLM11A121S

L28

BLM18PG181SN1

12

+VCCP

12

2.2U/10V/0805

5

12

.1U/10V/0402

L24

10uH

L27

10uH

C474

12

.1U/10V/0402

D D

+1_5VRUN

C C

2 1

D8

RB751V

+2.5VRUN

R82

10_0402

+2.5VRUN

B B

+VCCP

A A

C454

12

12

.1U/10V/0402

12

12

.1U/10V/0402

12

12

.1U/10V/0402

12

12

.1U/10V/0402

12

Place it closed

to U8.E19&U8.G19

12

4.7U/10V/0805

12

C458

.1U/10V/0402

C437

C436

C151

C154

12

C578

+

150U/6.3V/7343

C81

12

C131

10U/4V/0805

12

+

C411

470U/4V/15mO

Change

material

12

+

C420

470U/4V/15mO

12

C133

+

150U/2V/15mO

VCCA_MPLL

12

C161

+

150U/2V/15mO

12

.1U/10V/0402

12

C450

.1U/10V/0402

VCCA_DPLLA

VCCA_DPLLB

VCCA_CRTDAC

C414

1 2

C89

.47U/10V/0603

1 2

C88

.47U/10V/0603

1 2

C147

.22U/10V/0603

1 2

C117

.22U/10V/0603

12

C123

10U/4V/0805

VCCA_HPLL

12

C413

.022U/16V/0402

4

12

C462

10U/4V/0805

Place it

close to

U8.E19 and

U8.G19

R247

0_0402

1 2

123

C431

22nF/3P_NC

+VCCP

VCCP_GMCH_CAP1

VCCP_GMCH_CAP2

VCCP_GMCH_CAP3

VCCP_GMCH_CAP4

4

VCCA_CRTDAC_R

12

C581

.1U/10V/0402

M29

K29

V28

U28

R28

P28

N28

M28

K28

H28

G28

V27

U27

R27

P27

N27

M27

K27

H27

K26

H26

K25

K24

K23

K22

K21

W20

U20

K20

V19

U19

K19

W18

V18

K18

K17

AC2

AC1

B23

C35

AA1

AA2

E19

G19

H20

K13

K12

W11

V11

U11

R11

P11

N11

M11

K11

W10

V10

U10

R10

P10

N10

M10

K10

T29

R29

N29

J29

T28

L28

J28

T27

L27

J27

J25

T20

T18

F19

J13

T11

L11

T10

J10

Y9

W9

U9

R9

P9

N9

M9

L9

J9

N8

M8

N7

M7

N6

M6

A6

N5

M5

N4

M4

N3

M3

N2

M2

B2

V1

N1

M1

G1

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCCH_MPLL1

VCCH_MPLL0

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_MPLL

VCCA_CRTDAC0

VCCA_CRTDAC1

VSSA_CRTDAC

VCC_SYNC

VTT0

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

VTT32

VTT33

VTT34

VTT35

VTT36

VTT37

VTT38

VTT39

VTT40

VTT41

VTT42

VTT43

VTT44

VTT45

VTT46

VTT47

VTT48

VTT49

VTT50

VTT51

U8H

ALVISO

POWER

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

VCCA_TVBG

VSSA_TVBG

VCCD_TVDAC

VCCDQ_TVDAC

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

VCCA_LVDS

VCCHV0

VCCHV1

VCCHV2

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCSM52

VCCSM53

VCCSM54

VCCSM55

VCCSM56

VCCSM57

VCCSM58

VCCSM59

VCCSM60

VCCSM61

VCCSM62

VCCSM63

VCCSM64

VCCTX_LVDS0

VCCTX_LVDS1

VCCTX_LVDS2

VCCA_SM0

VCCA_SM1

VCCA_SM2

VCCA_SM3

VCC3G0

VCC3G1

VCC3G2

VCC3G3

VCC3G4

VCC3G5

VCC3G6

VCCA_3GPLL0

VCCA_3GPLL1

VCCA_3GPLL2

VCCA_3GBG

VSSA_3GBG

F17

E17

D18

C18

F18

E18

H18

G18

D19

H17

B26

B25

A25

A35

B22

B21

A21

AM37

AH37

AP29

AD28

AD27

AC27

AP26

AN26

AM26

AL26

AK26

AJ26

AH26

AG26

AF26

AE26

AP25

AN25

AM25

AL25

AK25

AJ25

AH25

AG25

AF25

AE25

AE24

AE23

AE22

AE21

AE20

AE19

AE18

AE17

AE16

AE15

AE14

AP13

AN13

AM13

AL13

AK13

AJ13

AH13

AG13

AF13

AE13

AP12

AN12

AM12

AL12

AK12

AJ12

AH12

AG12

AF12

AE12

AD11

AC11

AB11

AB10

AB9

AP8

AM1

AE1

B28

A28

A27

AF20

AP19

AF19

AF18

AE37

W37

U37

R37

N37

L37

J37

Y29

Y28

Y27

F37

G37

3

3

VCC_TVDACA_R

VCC_TVDACB_R

VCC_TVDACC_R

VCC_TVBG_R

VSS_TVBG

VCCD_TVDAC_R

VCCQ_TVDAC_R

V1.8_DDR_CAP6

V1.8_DDR_CAP3

V1.8_DDR_CAP4

VCC_DDRDLL

VCC3G_PCIE

VCCA_3GPLL

VCCA_3GBG

VSSA_3GBG

V1.8_DDR_CAP1

V1.8_DDR_CAP2

V1.8_DDR_CAP5

Note: All VCCSM

pins shorted

internally.

Note: All VCCSM

pins shorted

internally.

1 2

C502

.1U/10V/0402

1 2

C495

.1U/10V/0402

1 2

C482

.1U/10V/0402

12

C96

.1U/10V/0402

12

C434

.01U/25V/0402

12

C95

.1U/10V/0402

1 2

1 2

1 2

12

C197

10U/4V/0805

12

C97

.1U/10V/0402

VCCA_3GBG

VSSA_3GBG

+1_5VRUN

12

C85

10U/4V/0805

+2.5VRUN

12

C435

.1U/10V/0402

+2.5VRUN

12

C84

10U/4V/0805

C497

.1U/10V/0402

C489

.1U/10V/0402

C501

.1U/10V/0402

+2.5VSUS

12

C196

10U/4V/0805

Refer chekc list V1_601 P.33

+2.5VRUN

12

C86

4.7U/10V/0805

12

C446

.1U/10V/0402

2

R246

0_0402

1 2

1

3

C433

22nF/3P_NC

22nF/3P_NC

VCC_TVDACC_R VCC_TVDACC

22nF/3P_NC

22nF/3P_NC

VSS_TVBG

VCCD_TVDAC_R

22nF/3P_NC

VCCQ_TVDAC_R

22nF/3P_NC

+2.5VRUN

2

R81 0_0402

1 2

3

C91

R237 0_0402

1 2

3

C430

R78 0_0402

1 2

3

C87

1 2

3

C432

1 2

3

C90

VCC_DDRDLL

VCC3G_PCIE

VCCA_3GPLL

2

1

2

1

2

1

2

R236

0_0402

1

2

R80

0_0402

1

2

12

C472

10U/4V/0805

12

C475

.1U/10V/0402

Title

Size Document Number Rev

Date: Sheet

1

08

VCC_TVDACAVCC_TVDACA_R

12

C417

.022U/16V/0402

VCC_TVDACBVCC_TVDACB_R

12

C94

.022U/16V/0402

12

C415

.022U/16V/0402

VCC_TVBGVCC_TVBG_R

12

C79

.022U/16V/0402

VCCD_TVDAC

12

C419

.022U/16V/0402

VCCQ_TVDAC

12

C93

.022U/16V/0402

12

+

C504

100U/2V_18mO

12

C456

10U/4V/0805

1 2

12

C453

10U/4V/0805

12

C418

.1U/10V/0402

12

C82

.1U/10V/0402

12

C416

.1U/10V/0402

12

C78

2.2U/6.3V/0603

12

C412

.1U/10V/0402

12

C92

.1U/10V/0402

12

C485

.1U/10V/0402

VCC3G_PCIE

12

+

VCCA_3GPLL_R

R289

0.5/F_0603

C159

150U/2V/15mO

QUANTA

COMPUTER

Alviso (Power)

VM7 2B

12

L26

BLM18PG181SN1

12

L14

BLM18PG181SN1

12

L25

BLM18PG181SN1

12

L13

BLM18PG181SN1

D7

RB751V

2 1

12

L15

BLM18PG181SN1

L39

BLM18PG330SN1

L32

BLM18PG330SN1

L31

BLM18PG181SN1

1

+3VRUN

+3VRUN

+3VRUN

+3VRUN

12

+3VRUN

R77

10_0402

+1_5VRUN

12

+1_5VRUN

12

+1_5VRUN

12

+1_5VRUN

845Thursday, July 14, 2005

of

Page 9

5

4

3

2

1

09

AF23

H23

AL22

AH22

J22

E22

D22

A22

AN21

AF21

F21

C21

AK20

V20

G20

F20

E20

D20

A20

AN19

AG19

W19

T19

J19

H19

C19

AL18

U18

B18

A18

AN17

AJ17

AF17

G17

C17

AL16

K16

H16

D16

A16

K15

C15

AN14

AL14

AJ14

AG14

K14

J14

F14

B14

A14

J12

D12

B12

AN11

AL11

AJ11

AG11

AF11

AA11

Y11

H11

F11

AA10

Y10

L10

D10

AN9

AH9

AE9

AC9

AL5W5E5

AN4

AJ3

AC3

AB3

AA3C3A3

AN2

AL2

AH2

AE2

AD2V2T2P2L2

B27

J26

G26

E26

A26

AN24

AL24J2G2D2Y1

B36

AF4Y4U4P4L4H4C4

AA6T6P6L6J6B6AP5

AK7

AG7

AA7V7G7

AJ6

AE6

AC6

AA9V9T9K9H9A9AL8Y8P8L8E8C8AN7

D D

VSSALVDS

VSS269

VSS270

VSS271

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

U8E

ALVISO

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

AF27

AB27

AA27

W27

G27

E27

AJ24

AG24

J24

F24

D24

B24

C C

Y13

AA12

Y12

VSS_NCTF66

VSS_NCTF67

VSS_NCTF68

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

AA28

W28

E28

AN27

AL27

AJ27

AG27

T14

R14

P14

N14

M14

L14

AA13

VSS_NCTF59

VSS_NCTF60

VSS_NCTF61

VSS_NCTF62

VSS_NCTF63

VSS_NCTF64

VSS_NCTF65

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

G29

F29

E29

D29

A29

AC28

AB28

L15

AB14

AA14

Y14

W14

V14

U14

VSS_NCTF52

VSS_NCTF53

VSS_NCTF54

VSS_NCTF55

VSS_NCTF56

VSS_NCTF57

VSS_NCTF58

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

AA29

W29

V29

U29

P29

L29

H29

V15

U15

T15

R15

P15

N15

M15

VSS_NCTF45

VSS_NCTF46

VSS_NCTF47

VSS_NCTF48

VSS_NCTF49

VSS_NCTF50

VSS_NCTF51

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

AA30

Y30

C30

AM29

AJ29

AG29

AD29

N16

M16

L16

AB15

AA15

Y15

W15

VSS_NCTF38

VSS_NCTF39

VSS_NCTF40

VSS_NCTF41

VSS_NCTF42

VSS_NCTF43

VSS_NCTF44

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

F31

E31

D31

AP30

AE30

AC30

AB30

Y16

W16

V16

U16

T16

R16

P16

VSS_NCTF31

VSS_NCTF32

VSS_NCTF33

VSS_NCTF34

VSS_NCTF35

VSS_NCTF36

VSS_NCTF37

U8D

ALVISO

B B

VCC_NCTF73

VCC_NCTF74

VCC_NCTF75

VCC_NCTF76

VCC_NCTF77

VCC_NCTF78

N17

M17

L17

VCC_NCTF69

VCC_NCTF70

VCC_NCTF71

VCC_NCTF72

M18

L18

W17

V17

U17

T17

P17

VCC_NCTF62

VCC_NCTF63

VCC_NCTF64

VCC_NCTF65

VCC_NCTF66

VCC_NCTF67

VCC_NCTF68

N19

M19

L19

Y18

R18

P18

N18

VCC_NCTF55

VCC_NCTF56

VCC_NCTF57

VCC_NCTF58

VCC_NCTF59

VCC_NCTF60

VCC_NCTF61

P20

N20

M20

L20

Y19

R19

P19

VCC_NCTF48

VCC_NCTF49

VCC_NCTF50

VCC_NCTF51

VCC_NCTF52

VCC_NCTF53

VCC_NCTF54

T21

P21

N21

M21

L21

Y20

R20

VCC_NCTF41

VCC_NCTF42

VCC_NCTF43

VCC_NCTF44

VCC_NCTF45

VCC_NCTF46

VCC_NCTF47

P22

N22

M22

L22

W21

V21

U21

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

P31

N31

M31

L31

K31

J31

H31

G31

AB18

AA18

AB17

AA17

Y17

R17

AB16

AA16

VSS_NCTF24

VSS_NCTF25

VSS_NCTF26

VSS_NCTF27

VSS_NCTF28

VSS_NCTF29

VSS_NCTF30

NCTF

VCC_NCTF34

VCC_NCTF35

VCC_NCTF36

VCC_NCTF37

VCC_NCTF38

VCC_NCTF39

VCC_NCTF40

N23

M23

L23

W22

V22

U22

T22

R22

VSS

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

AG37

Y37

V37

T37

P37

M37

K37

H37

E37

AN36

AL36

AJ36

AF36

AE36

AD36

AC36

AB36

AA36

C36

AE35

Y35

W35

V35

U35

T35

R35

P35

N35

M35

L35

K35

J35

H35

G35

F35

E35

D35

B35

AN34

AH34

AD34

AC34

AB34

AA34

C34

AL33

AF33

AD33

W33

V33

U33

T33

R33

P33

N33

M33

L33

K33

J33

H33

G33

F33

E33

D33

AN32

AJ32

AD32

AC32

AB32

AA32

Y32

C32

A32

AL31

AG31

AD31

W31

V31

U31

T31

R31

+VCCP

W13

V13

U13

T13

R13

P13

N13

M13

L13

W12

V12

U12

T12

R12

P12

N12

M12

L12

AB26

AA26

Y26

AB25

AA25

Y25

AB24

AA24

Y24

AB23

AA23

Y23

AB22

AA22

Y22

AB21

AA21

Y21

R21

AB20

AA20

AB19

AA19

VTT_NCTF0

VTT_NCTF1

VTT_NCTF2

VTT_NCTF3

VTT_NCTF4

VTT_NCTF5

VTT_NCTF6

VTT_NCTF7

VTT_NCTF8

VSS_NCTF9

VSS_NCTF10

VSS_NCTF11

VSS_NCTF12

VSS_NCTF13

VSS_NCTF14

VSS_NCTF15

VSS_NCTF16

VSS_NCTF17

VSS_NCTF18

VSS_NCTF19

VSS_NCTF20

VSS_NCTF21

VSS_NCTF22

VSS_NCTF23

VCC_NCTF10

VCC_NCTF11

VCC_NCTF12

VCC_NCTF13

VCC_NCTF14

VCC_NCTF15

VCC_NCTF16

VCC_NCTF17

VCC_NCTF18

VCC_NCTF19

VCC_NCTF20

VCC_NCTF21

VCC_NCTF22

VCC_NCTF23

VCC_NCTF24

VCC_NCTF25

VCC_NCTF26

VCC_NCTF27

VCC_NCTF28

VCC_NCTF29

VCC_NCTF30

VCC_NCTF31

VCC_NCTF32

VCC_NCTF33

V25

U25

T25

R25

P25

N25

M25

L25

W24

V24

U24

T24

R24

P24

N24

M24

L24

W23

V23

U23

T23

R23

P23

VTT_NCTF16

VTT_NCTF17

VCC_NCTF3

VCC_NCTF4

VCC_NCTF5

VCC_NCTF6

VCC_NCTF7

VCC_NCTF8

VCC_NCTF9

T26

R26

P26

N26

M26

L26

W25

VSS_NCTF0

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

VSS_NCTF8

VTT_NCTF9

VTT_NCTF10

VTT_NCTF11

VTT_NCTF12

VTT_NCTF13

VTT_NCTF14

VTT_NCTF15

VCCSM_NCTF0

VCCSM_NCTF1

VCCSM_NCTF2

VCCSM_NCTF3

VCCSM_NCTF4

VCCSM_NCTF5

VCCSM_NCTF6

VCCSM_NCTF7

VCCSM_NCTF8

VCCSM_NCTF9

VCCSM_NCTF10

VCCSM_NCTF11

VCCSM_NCTF12

VCCSM_NCTF13

VCCSM_NCTF14

VCCSM_NCTF15

VCCSM_NCTF16

VCCSM_NCTF17

VCCSM_NCTF18

VCCSM_NCTF19

VCCSM_NCTF20

VCCSM_NCTF21

VCCSM_NCTF22

VCCSM_NCTF23

VCCSM_NCTF24

VCCSM_NCTF25

VCCSM_NCTF26

VCCSM_NCTF27

VCCSM_NCTF28

VCCSM_NCTF29

VCCSM_NCTF30

VCCSM_NCTF31

VCC_NCTF0

VCC_NCTF1

VCC_NCTF2

AD26

AC26

AD25