Page 1

DATA SHEET

BIPOLAR ANALOG INTEGRATED CIRCUIT

µ

PC8101GR

150 MHz SILICON QUADRATURE MODULATOR IC

FOR DIGITAL MOBILE COMMUNICATIONS

DESCRIPTION

µ

PC8101GR is a silicon monolithic integrated circuit designed as up-to-150 MHz quadrature modulator for digital mobile

communications, mainly CT2. This modulator consists of digital 90° phase shifter, dual mixers and various buffer amplifiers

which are packaged in 20 pin SSOP. Up/down converter IC (µPC8100GR) is also available as for kit-use with this IC. So,

these pair devices contribute to make RF block small, high-performance and low power-consumption.

This product is manufactured using NEC’s 20 GHz f

passivation film and gold electrodes. These materials can protect chip surface from external pollution and prevent corrosion

and migration. Thus, this product has excellent performance, uniformity and reliability.

T NESAT

III silicon bipolar process. This process uses silicon nitride

FEATURES

• Operating frequency: fIF = 50 MHz to 150 MHz, Local input frequency: fLo = 100 MHz to 300 MHz, fI/Q = DC to 500 kHz

• Digital 90° phase shifter is incorporated. (Due to the flip flop phase shifter, fIF = fLo/2 + fI/Q.)

• 20 pin SSOP suitable for high-density surface mounting.

• Supply voltage V

• Equipped with Power Save Function.

APPLICATIONS

• Typical application – Digital cordless phone CT2. (In the case of I/Q method)

• Further application – Digital communication equipments.

ORDERING INFORMATION

PART NUMBER PACKAGE SUPPLYING FORM

µ

PC8101GR-E2 20 pin plastic SSOP Embossed tape 12 mm wide. QTY 2.5 kp/Reel.

Remark To order evaluation samples, please contact your local NEC sales office. (Order number: µPC8101GR)

CC = 2.7 to 5.5 V

(225 mil) Pin 1 indicates roll-in direction of tape.

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for availability

and additional information.

Document No. P10818EJ3V0DS00 (3rd edition)

Date Published October 1999 N CP(K)

Printed in Japan

Caution electro-static sensitive devices

The mark shows major revised points.

©

1995,1999

Page 2

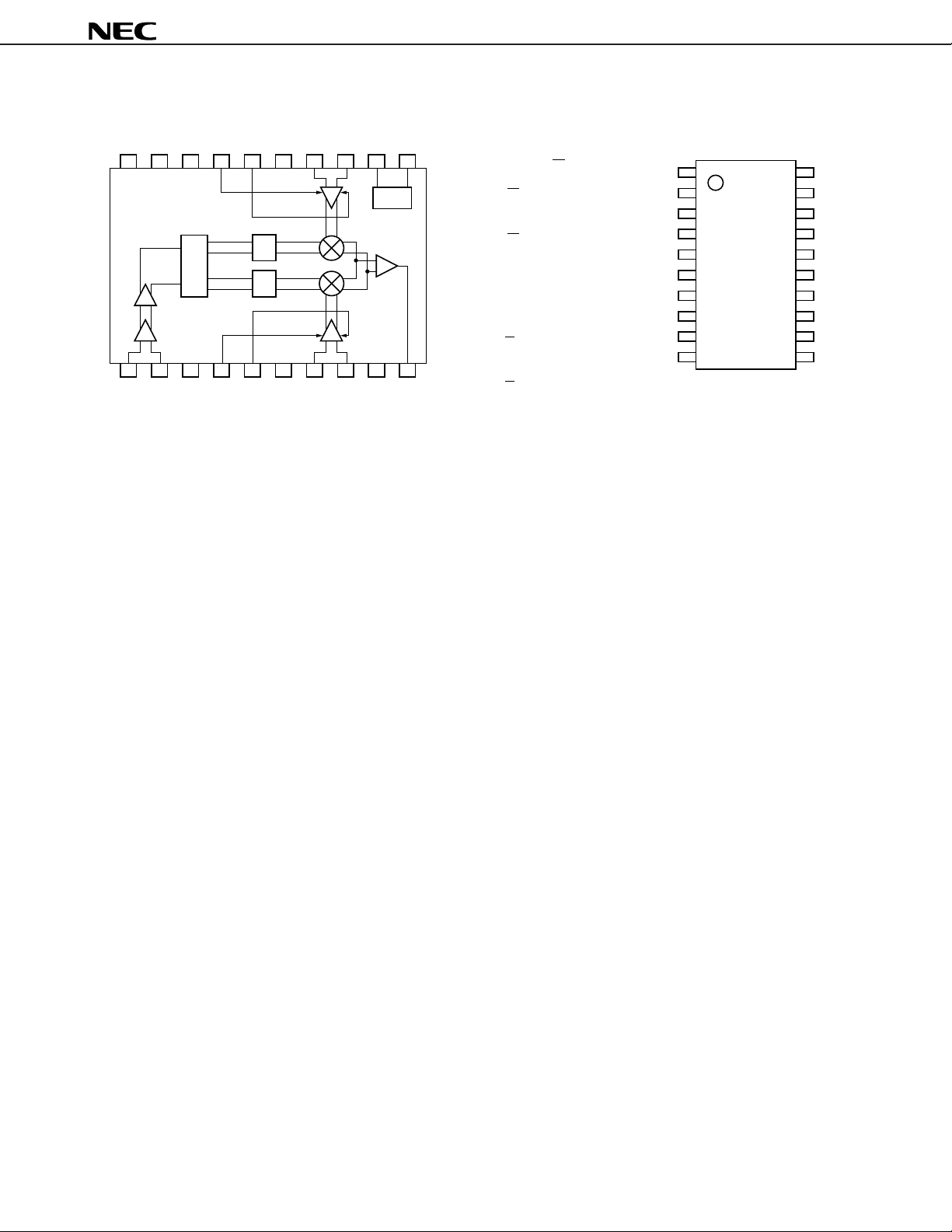

INTERNAL BLOCK DIAGRAM AND PIN CONNECTIONS

µ

PC8101GR

20 19 18 17 16 15 14 13 12

90°

LPF

270°

F / F

0°

180°

LPF

12345678910

11

REG.

1. LOCAL IN

2. LOCAL IN

3. GND

4. Q – BIAS

5. Q – BIAS

6. GND

7. Q – INPUT

8. Q – INPUT

9. GND

10. IF OUTPUT

11. V

CC

12. POWER SAVE

13. I – INPUT

14. I – INPUT

15. GND

16. I – BIAS

17. I – BIAS

18. GND

19. N.C.

20. GND

10

1

2

3

4

5

6

7

8

9

(Top View)

20

19

18

17

16

15

14

13

12

11

2

Data Sheet P10818EJ3V0DS00

Page 3

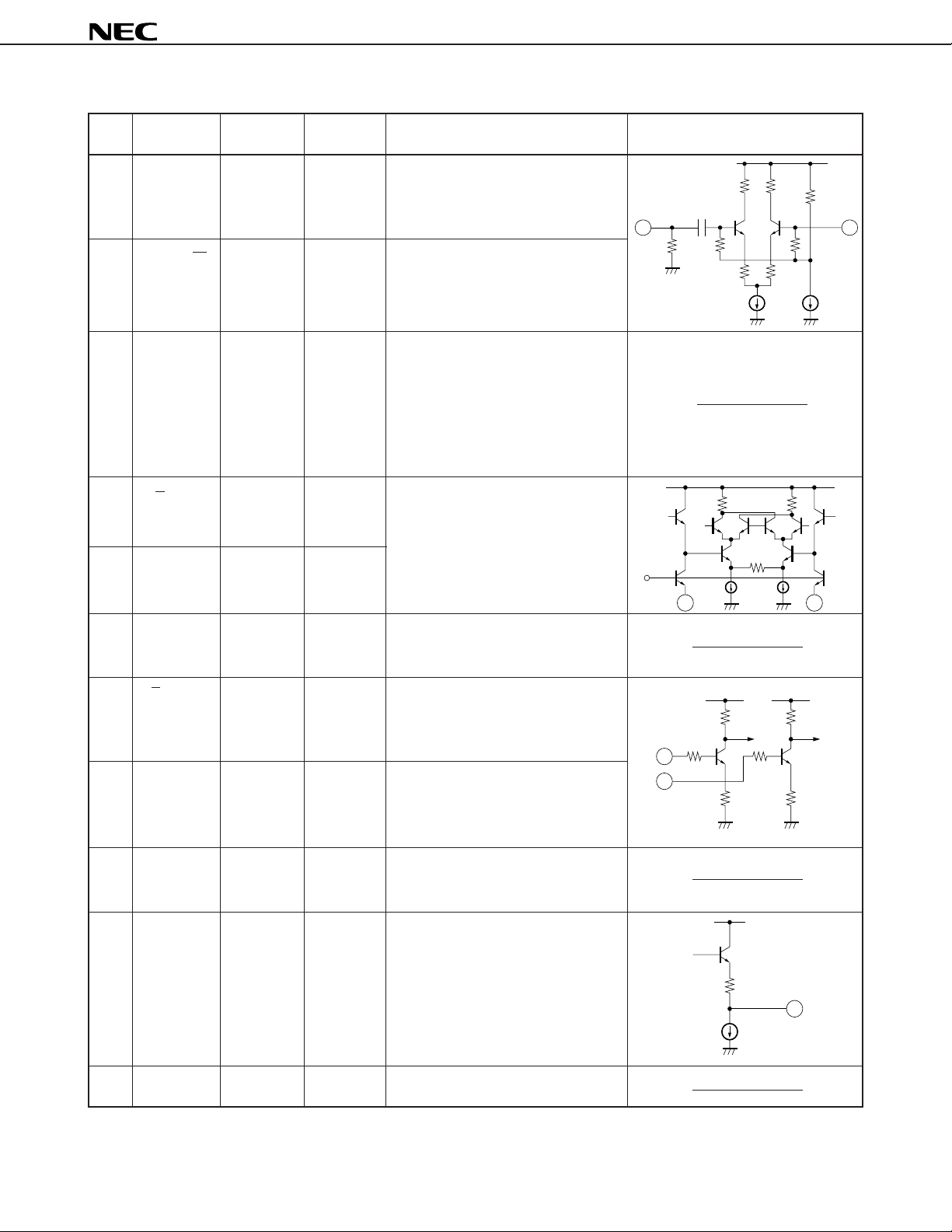

PIN EXPLANATION

µ

PC8101GR

PIN

ASSIGNMENT

NO.

1 LOCAL IN – –

2 LOCAL IN – 2.0

3 GND 0 –

4 Q-BIAS – 0.175

5 Q-BIAS – 0.175

APPLIED

VOLTAGE (V)

PIN VOLTAGE

(V)

FUNCTION AND APPLICATION EQUIVALENT CIRCUIT

Local input for phase shifter.

This input impedance is 50 Ω matched

internally.

Bypass of local buffer amplifier input.

Grounded through capacitor.

It must be connected to the system ground

with minimum inductance. Ground pattern on the board should be formed as

wide as possible.

(Track length should be kept as short as

possible.)

These pins are to adjust local leakage

level.

These pins should be grounded through

register 1 kΩ adjustable 30 mV offset.

1

V

CC

2

6 GND 0 –

7 Q-INPUT VCC/2 –

8 Q-INPUT VCC/2 –

9 GND 0 –

10 IF OUTPUT – 1.4

Track length should be kept as short as

possible.

Input for Q signal. This input impedance

is larger than 500 kΩ. As Q signal, VCC/

2 bias DC signal should be input.

Input for Q signal. This input impedance

is larger than 500 kΩ. As Q signal, VCC/

2 biased 1VP–P signal should be input.

Track length should be kept as short as

possible.

IF output from modulator. This output is

emitter follower as 50 Ω impedance. IF

output frequency is provided as fIF = fLo/

2 + fI/Q.

5

4

7

8

10

11 VCC 2.7 to 5.5 –

Supply voltage pin.

Data Sheet P10818EJ3V0DS00

3

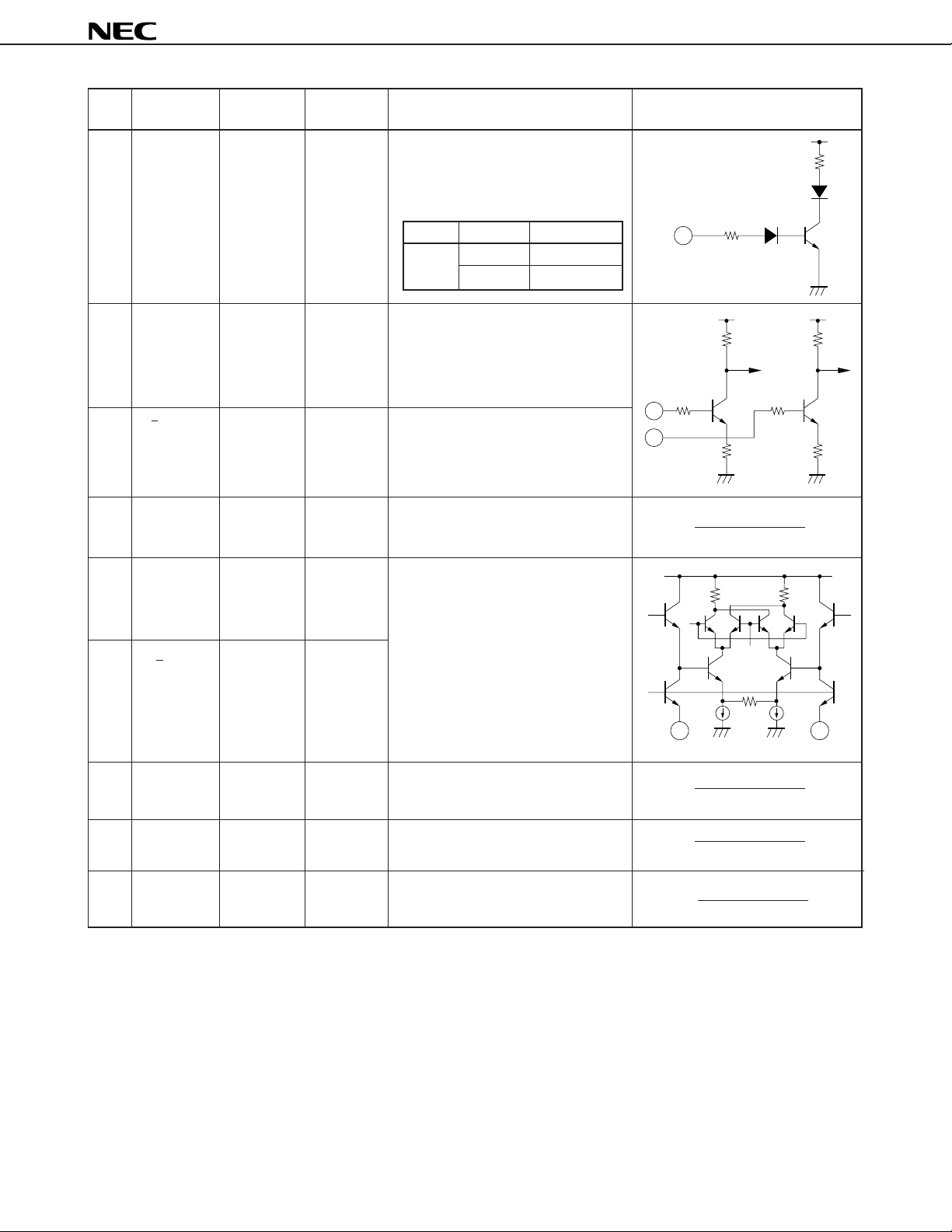

Page 4

µ

PC8101GR

PIN

ASSIGNMENT

NO.

12 POWER 0 to 5.5 –

SAVE

13 I-INPUT VCC/2 –

14 I-INPUT VCC/2 –

15 GND 0 –

APPLIED

VOLTAGE (V)

PIN VOLTAGE

(V)

FUNCTION AND APPLICATION EQUIVALENT CIRCUIT

Power save control pin. This pin can

control ON/OFF operation with bias as

follows;

Bias: V Operation

PS

V

Input for I signal. This input impedance is larger than 500 kΩ. As I signal,

VCC/2 biased 1 VP–P MAX. signal should

be input.

Input for I signal. This input impedance is larger than 500 kΩ. As I signal,

VCC/2 bias DC signal should be input.

Track length should be kept as short

as possible.

≥1.8 ON

0 to 1.0 OFF

12

13

14

16 I-BIAS – 0.175

17 I-BIAS – 0.175

18 GND 0 –

19 N.C – –

20 GND 0 –

* Pin voltage at VCC = 2.7 V

These pins are to adjust local leakage

level.

These pins should be grounded through

register 1 kΩ adjustable 30 mV offset.

Track length should be kept as short

as possible.

Non connection

Track length should be kept as short

as possible.

16

17

4

Data Sheet P10818EJ3V0DS00

Page 5

µ

PC8101GR

ABSOLUTE MAXIMUM RATINGS

Supply Voltage VCC TA = +25 °C 6.0 V

Power Dissipation PD Mounted on 50 × 50 × 1.6 mm double copper 530 mW

clad epoxy glass board at TA = +70 °C

Operating Temperature Topt –20 to +70 °C

Storage Temperature T

stg –65 to +150 °C

RECOMMENDED OPERATING CONDITIONS

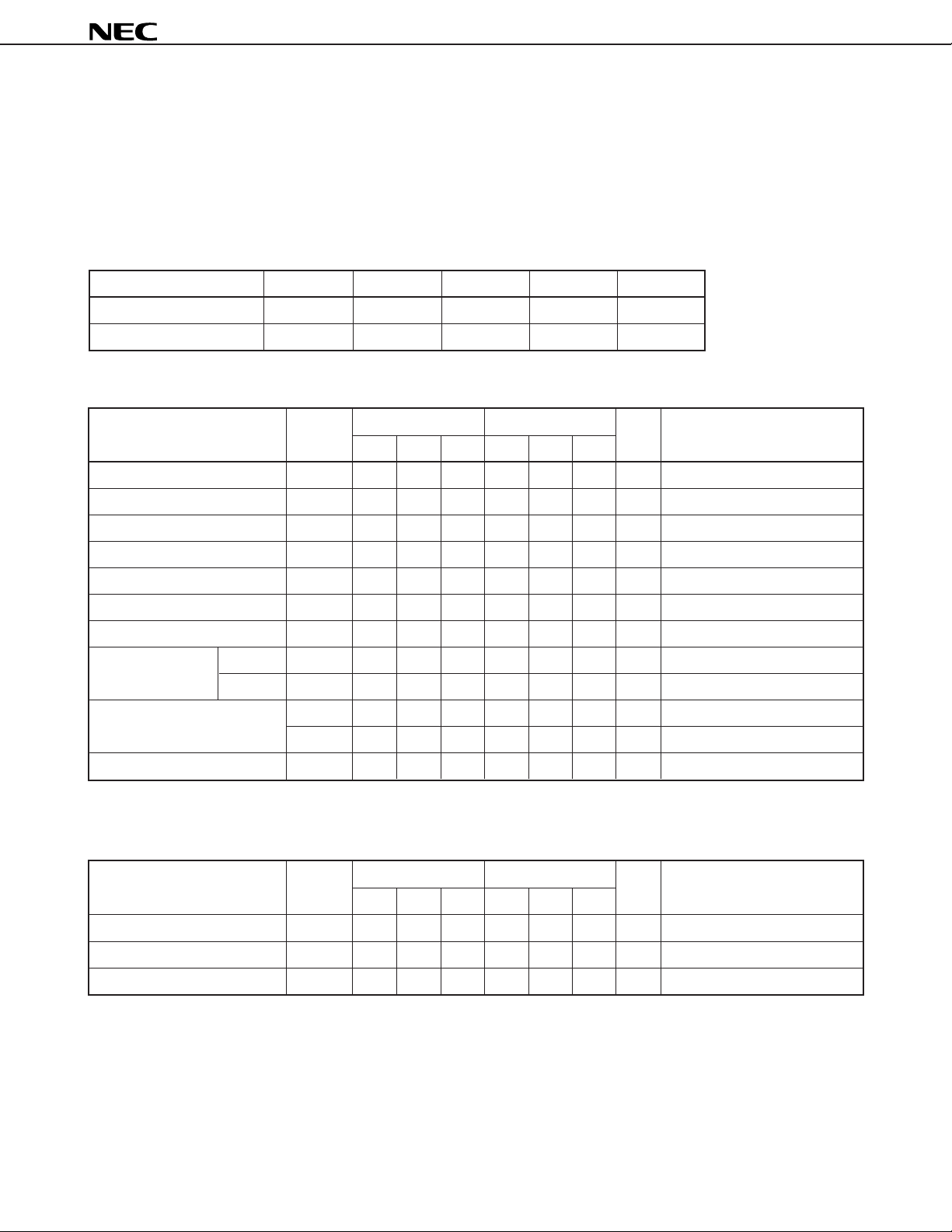

PARAMETER SYMBOL MIN. TYP. MAX. UNIT

Supply Voltage VCC 2.7 3.0 5.5 V

Operating Temperature Topt –20 +25 +70 °C

ELECTRICAL CHARACTERISTICS (TA = +25 °C, UNLESS OTHERWISE SPECIFIED VP/S ≥ 1.8 V)

PARAMETER SYMBOL

Circuit current ICC 10.0 15.0 22.0 17.0 24.5 32.0 mA No input signal

Circuit current power-save mode ICC(P/S) 330 480 1050 1500µAVP/S ≤ 1.0 V

IF output level PIFout –15 –11 –7.0 –12.5 –7.7 –4.5 dBm 50 Ω load, f = fLo/2 + fI/Q*

Local leakage (carrier) ISO(Lo) 26.0 35.0 30.6 dBc f = fLo/2*

Local leak level at IFout pin Loif –49 –37 –39.4 –28 dBm I/Qinput : DC = VCC /2

Image rejection (side band leak) ImR 28.5 37.5 28.5 38.2 dBc f = fLo/2 – fI/Q*

I/Q input impedance ZI/Q 500 1 000 500 700 kΩ I/Qbias = 2.75 V

Power-save

response time

Power-save control voltage VP/S(ON) 1.8 5.5 1.8 5.5 V Normal operation

Local input level PLoin –17 –7 –17 –7 dBm

rise time TP/S(RISE) 1.0 5.0 1.0 5.0

fall time TP/S(FALL) 1.0 3.0 1.0 3.0

VP/S(OFF) 1.0 1.0 V Power-save mode

VCC = 2.7 V VCC = 5.5 V

MIN. TYP. MAX. MIN. TYP. MAX.

UNIT TEST CONDITION

1

1

µ

sVP/S(OFF) → VP/S(ON)

µ

sVP/S(ON) → VP/S(OFF)

STANDARD CHARACTERISTICS FOR REFERENCE

(TA = +25 °C, UNLESS OTHERWISE SPECIFIED VP/S ≥ 1.8 V)

1

PARAMETER SYMBOL

3rd order distortion of I/Q

Local input VSWR VSWRLoin 1.1 1.1 X : 1

IF output VSWR VSWRIFout 1.2 1.2 X : 1

IM3I/Q –37.3 –56.5 dBc f = fLo/2 – 3fI/Q*

VCC = 2.7 V VCC = 5.5 V

MIN. TYP. MAX. MIN. TYP. MAX.

*1 :fLoin = 300.1 MHz PLoin = –10 dBm

f

I/Q = 36 kHz 1 VP-P DC = VCC/2

Data Sheet P10818EJ3V0DS00

UNIT TEST CONDITION

1

5

Page 6

TEST CIRCUIT

33 nF

I signal

µ

PC8101GR

1 000 pF

50 Ω

P/S

GND

10 nF

CC

V

OUT

IF

1 000 pF

50 Ω

1 kΩ 1 kΩ

20 19 18 17 16 15 14 13 12 11

I

I

GND

LoIN

12345678910

(N.C.)

LoIN

30 pF

50 Ω

GND

GND

I – BIAS

I – BIAS

PC8101GR

µ

Q – BIAS

Q – BIAS

1 kΩ 1 kΩ

GND

GND

33 nF

Q

Q signal

Q

2 000 pF

5 F

µ

Signal Generator Spectrum Analyzer

SIGNAL f(MHz) PIN

Lo 300.1 MHz –10 dBm

I signal 36 kHz 1 VP-P

Q signal 36 kHz 1 VP-P

SYMBOL Applied voltage (V)

VCC = VP/S 2.7 to 5.5 V

VI = VIb = VO = VOb 0.5 × VCC

6

Data Sheet P10818EJ3V0DS00

I/Q phase difference = 90°

In the case of local leak level measurement,

I/Q signal is applied as only DC.

Page 7

TYPICAL CHARACTERISTICS (Unless otherwise specified TA = +25 ˚C)

y

)

Output spectrum at IF out pin

–5

–25

–45

–65

–85

–105

I/Q 3d

PI/Q

PIm

ImR

PLO

LoL

Pout

VCC = 2.7 V

µ

PC8101GR

V

CC = 2.7 V fLO vs. Pout, PLO,PIm, PI/Q

0

–10

Pout

–20

–30

–40

–50

Output Level (dBm)

PI/Q

PLO

–60

–70

Im

–80

P

10 50 100 500

Input LO frequency f

V

CC vs. ICC

LO (MHz)

40

VP/S = VCC, No signals

I/Q = VCC/2

V

30

= –30 ˚C

A

T

0

VCC = 5.5 V fLO vs. Pout, PLO,PIm, PI/Q

–10

Pout

–20

–30

–40

PLO

–50

–60

PI/Q

P

Im

Output Level (dBm)

– 70

–80

10 50 100 500

Input LO frequency f

LO (MHz)

Pout, PIm and PI/Q3rd vs. Supply Voltage

Lo: f

CC

P/S = V

I/Q = VCC/2

LO = 300.1MHz

P

in = –10 dBm

I/Q = 450 kHz

I/Q: F

1V

p-p

0

PLOin is measued on I/Q bias Without signals

–10

–20

Pout

P

LO

PIm

PI/Q3rd

= +25 ˚C

A

T

20

= +80 ˚C

A

T

Circuit Current ICC (mA)

10

Recommended operating range

0

2.0 3.0 4.0 5.0 6.0

Supply Voltage V

CC (V)

–30

–40

–50

Output Level (dBm)

–60

–70

–80

2.7 3 3.5 4 4.5 5 5.5

Data Sheet P10818EJ3V0DS00

Suppl

Voltage VCC (V

7

Page 8

)

CC = 2.7 V TA vs. Pout, PLO, PIm, PI/Q

V

fLO = 300.1 MHz, PLO = – 10dBm

0

–10

Pout

PLO

PIm

PL/Q3d

I = Ib = Q = Qb = GND

30

20

P/S vs. Circuit Current

V

µ

PC8101GR

VCC = 5.5 V

–20

–30

–40

–50

Output Level (dBm)

–60

–70

–80

–30–20–100 1020304050607080

Ambrent Temperature TA (˚C

PLO

250

Circuit Curent ICC (mA)

200

100

50

10

µ

µ

µ

µ

1 1.21.41.6 2 3 4 5 6

in appliod Voltage P/S (V)

P

V

CC = 2.7 V

8

Data Sheet P10818EJ3V0DS00

Page 9

TEST CIRCUIT ASSEMBLED ON EVALUATION BOARD

IC MOUNTED SIDE

µ

PC8101GR

C IN1

LO IN

C IN2

NEC

µ

PC8101

COMPONENT MOUNTED SIDE

V

CC

10 000 pF

I IN

RF OUT

Q IN

DC

I

b

I

IF

0 Ω

10 nF

1 000 pF

0 Ω

33 nF

1 kΩ

1 kΩ

141617

13

PS

12

2 000 pF

11

V

CC

200 pF

20 pF

19

20

1 000 pF

5

4

1 kΩ

1

30 pF

2

1 kΩ

10

8

7

0 Ω

50 Ω

0 Ω

0 Ω

0 Ω

Lo

f

Lo

= 300 MHz

in (Lo)

= –10 dBm

P

Q

DC

Q

b

33 nF

Data Sheet P10818EJ3V0DS00

9

Page 10

TYPICAL APPLICATION

CT2 BLOCK DIAGRAM

µ

PC8101GR

RX

PLL

SW

µ

PG131GR

0°

TX

µ

PC8100GR

The application circuits and their parameters are for references only and are not intended for use in actual design-in's.

F/F

90°

PC8101GR

µ

DEMO

PLL

I

Q

I

Q

10

Data Sheet P10818EJ3V0DS00

Page 11

PACKAGE DIMENSIONS

20 PIN PLASTIC SSOP (225 mil) (UNIT: mm)

µ

PC8101GR

20

11

110

6.7 ± 0.3

1.8 MAX.

1.5 ± 0.1

detail of lead end

3˚

6.4 ± 0.2

4.4 ± 0.1

+7˚

–3˚

1.0 ± 0.2

0.5 ± 0.2

0.65

0.22

+0.10

–0.05

0.10

0.15

M

0.575 MAX.

0.15

+0.10

–0.05

0.1 ± 0.1

NOTE Each lead centerline is located within 0.10 mm of its true position (T.P.) at maximum material condition.

Data Sheet P10818EJ3V0DS00

11

Page 12

µ

PC8101GR

NOTE ON CORRECT USE

(1) Observe precautions for handling because of electrostatic sensitive devices.

(2) Form a ground pattern as wide as possible to minimize ground impedance (to prevent undesired operation).

(3) Keep the track length of the ground pins as short as possible.

(4) Connect a bypass capacitor (e.q. 1 000 pF) to the V

CC pin.

RECOMMENDED SOLDERING CONDITIONS

This product should be soldered in the following recommended conditions. Other soldering method and conditions than

the recommended conditions are to be consulted with our sales representatives.

µ

PC8101GR

Soldering

process

Infrared ray reflow

VPS

Wave soldering

Partial heating method

Peak package’s surface temperature: 235 °C or below,

Reflow time: 30 seconds or below (210 °C or higher),

Number of reflow process: 2, Exposure limit*: None

Peak package’s surface temperature: 215 °C or below,

Reflow time: 40 seconds or below (200 °C or higher),

Number of reflow process: 2, Exposure limit*: None

Solder temperature: 260 °C or below,

Flow time: 10 seconds or below

Number of flow process: 1, Exposure limit*: None

Terminal temperature: 300 °C or below,

Flow time: 10 seconds or below,

Exposure limit*: None

Soldering conditions

*: Exposure limit before soldering after dry-pack package is opened.

Storage conditions: 25 °C and relative humidity at 65 % or less.

Note: Apply only a single process at once, except for “Partial heating method”.

For details of recommended soldering conditions for surface mounting, refer to information document SEMICONDUCTOR

DEVICE MOUNTING TECHNOLOGY MANUAL (C10535E).

Symbol

IR35–00-2

VP15–00-2

WS60–00-1

12

Data Sheet P10818EJ3V0DS00

Page 13

[MEMO]

µ

PC8101GR

Data Sheet P10818EJ3V0DS00

13

Page 14

[MEMO]

µ

PC8101GR

14

Data Sheet P10818EJ3V0DS00

Page 15

[MEMO]

µ

PC8101GR

Data Sheet P10818EJ3V0DS00

15

Page 16

µ

PC8101GR

ATTENTION

OBSERVE PRECAUTIONS

FOR HANDLING

ELECTROSTATIC

SENSITIVE

DEVICES

NESAT (NEC Silicon Advanced Technology) is a trademark of NEC Corporation.

• The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

• No part of this document may be copied or reproduced in any form or by any means without the prior written

consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in

this document.

• NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual

property rights of third parties by or arising from use of a device described herein or any other liability arising

from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights

or other intellectual property rights of NEC Corporation or others.

• Descriptions of circuits, software, and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these circuits,

software, and information in the design of the customer's equipment shall be done under the full responsibility

of the customer. NEC Corporation assumes no responsibility for any losses incurred by the customer or third

parties arising from the use of these circuits, software, and information.

• While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices,

the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or

property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety

measures in its design, such as redundancy, fire-containment, and anti-failure features.

• NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a

customer designated “quality assurance program“ for a specific application. The recommended applications of

a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device

before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment,

audio and visual equipment, home electronic appliances, machine tools, personal electronic

equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster

systems, anti-crime systems, safety equipment and medical equipment (not specifically designed

for life support)

Specific: Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life

support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books.

If customers intend to use NEC devices for applications other than those specified for Standard quality grade,

they should contact an NEC sales representative in advance.

M7 98.8

Loading...

Loading...