Page 1

STLC7550

LOW POWE R LO W VO LTAGE ANALOG FRONT E ND

.

GENERAL PURPOSE SIGNAL PROCESSING

ANALOG FRONT END (AFE)

.

TARGETED FOR V.34bis MODEM AND

56Kbps MODEM APPLICATIONS

.

16-BIT OVERSAMPLING Σ∆ A/D AND D/A

CONVERTERS

.

83dB SIGNAL TO NOISE RATIO FOR SAMPLING FREQUENCY UP TO 9.6kHz @ 3V

.

87dB DYNAMIC RANGE @ 3V

.

FILT ER BAND W IDTHS :

0.425 x THE SAMPLING FREQUENCY

.

ON-CHIP REFERENCE VOLTAGE

.

SINGLE POWER SUPPLY RANGE :

2.7 TO 5.5V

.

LOW POWER CONSUMPTION LESS THAN

30mW OPERATING POWER 3V

.

STAND-BY MODE POWER CONSUMPTION

LESS T HAN 3µW at 3V

.

PROGR AM MI N G SA MPLING FREQ U E N CY

.

MAX. SAMPLING FREQUENCY : 45kHz

.

SYNCHRONOUS SERIAL INTERFACE FOR

PROCESSO R DATAS EXCHANGE. MAS TER

OR SLAVE OPERA TIONS

.

0.50µm CMOS PROCESS

.

TQFP44 PACKAGE

.

STLC7546 MODE OF OPERATION COMP A TIBLE

Maximum Power Dissipation 30mW is well suited

for Battery operations.

In case of battery low, STLC7550 will continue to

work even at a 2.7V level.

STLC7550 also provides clock generator for all

sampling frequencies requested for V.34bis and

56Kbps applications.

This new AFE can also be used for PC mother

boards or add-on cards or stand alone MODEMs.

It can be used in a master mode or slave mode.

The slave mode eases multi AFE architecture design in saving external logical glue.

TQFP44 (10 x 10 x 1.40 mm)

(Full Plastic Quad Flat Pack)

ORDER CODE : STLC7550TQFP

DESCRIPTION

The STLC7550 is a single chip Analog Front-end

(AFE) designed to implement modems up to

56Kbps.

It has been espec ially des igned fo r hos t proc ess ing

application in which the modulation software

(V .34bi s, 56Kbps) is perf ormed by the main app lication proces s or : Pentium, Risc or D S P pr oc es s or s .

The main target of this device is stand alone appliances as Hand Held PC (HPC), Personnal Digital

Assistants (PDA), Webphones, Network Computers, Set Top Boxes for Digital Television (Satellite

and Cable).

To comply with such applications STLC7550 is

powered nominally at 3V only.

November 1998

TQFP48 (7 x 7 x 1.40mm)

(Full Plastic Quad Flat Pack)

ORDER CODE : STLC7550TQF7

1/17

Page 2

STLC7550

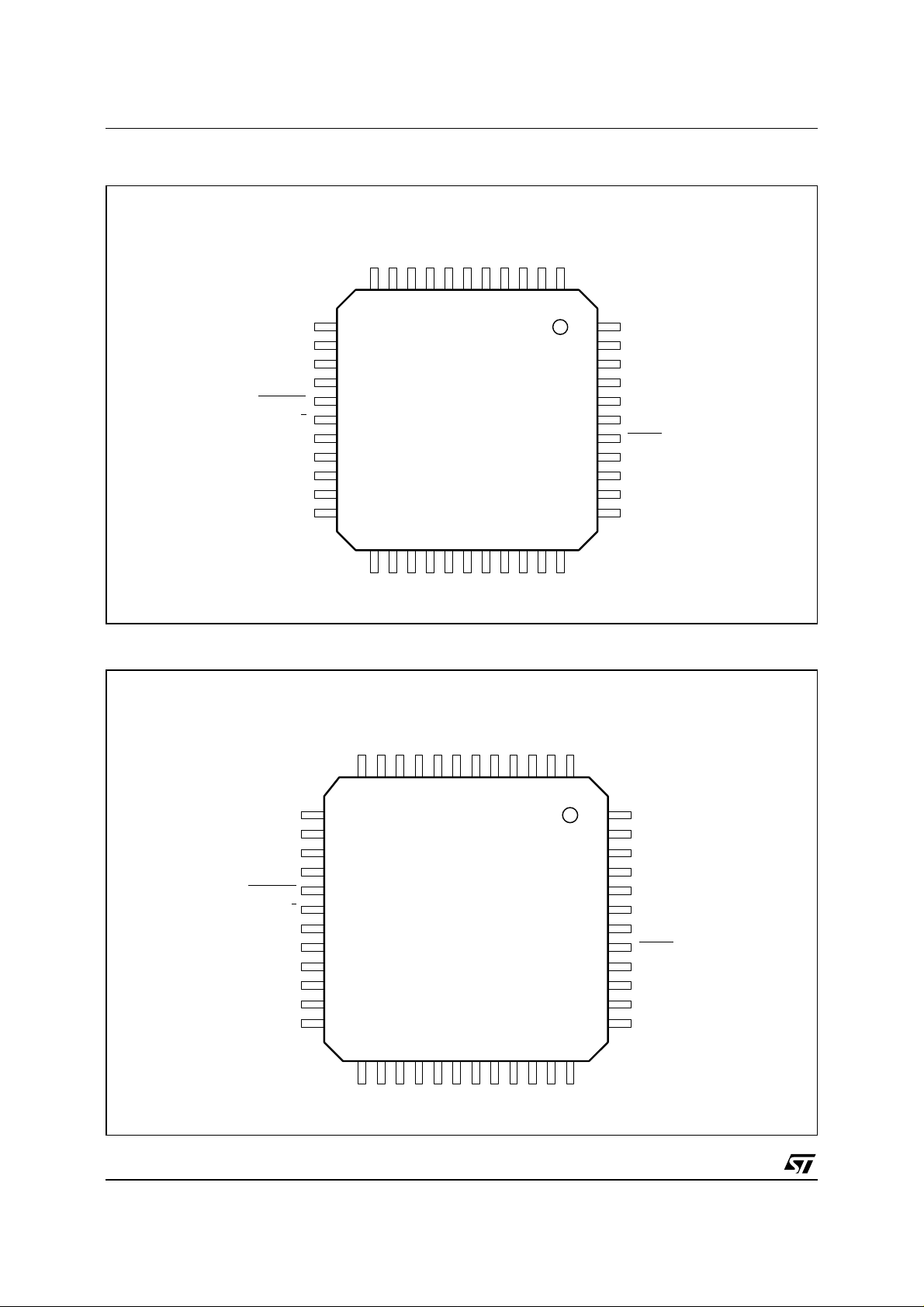

PIN CONNECTIONS

(TQFP44)

HC1

HC0

PWRDWN

M/S

V

REFP

V

REFN

AGND1

XTALIN/MCLK

XTALOUT

MCM

DGND

DVDDFS

12

13

14

15

16

17

18

19

20

21

22

23 24 25 26 27 28 29 30 31 32 33

DD

IN-

IN+

AUXIN-

AUXIN+

AV

CM

V

SCLK

AGND2

1234567891011

44

43

42

41

40

39

38

37

36

DOUT

DIN

TSTD1

TS

RESET

OUT-

OUT+

35

34

7550-01.EPS

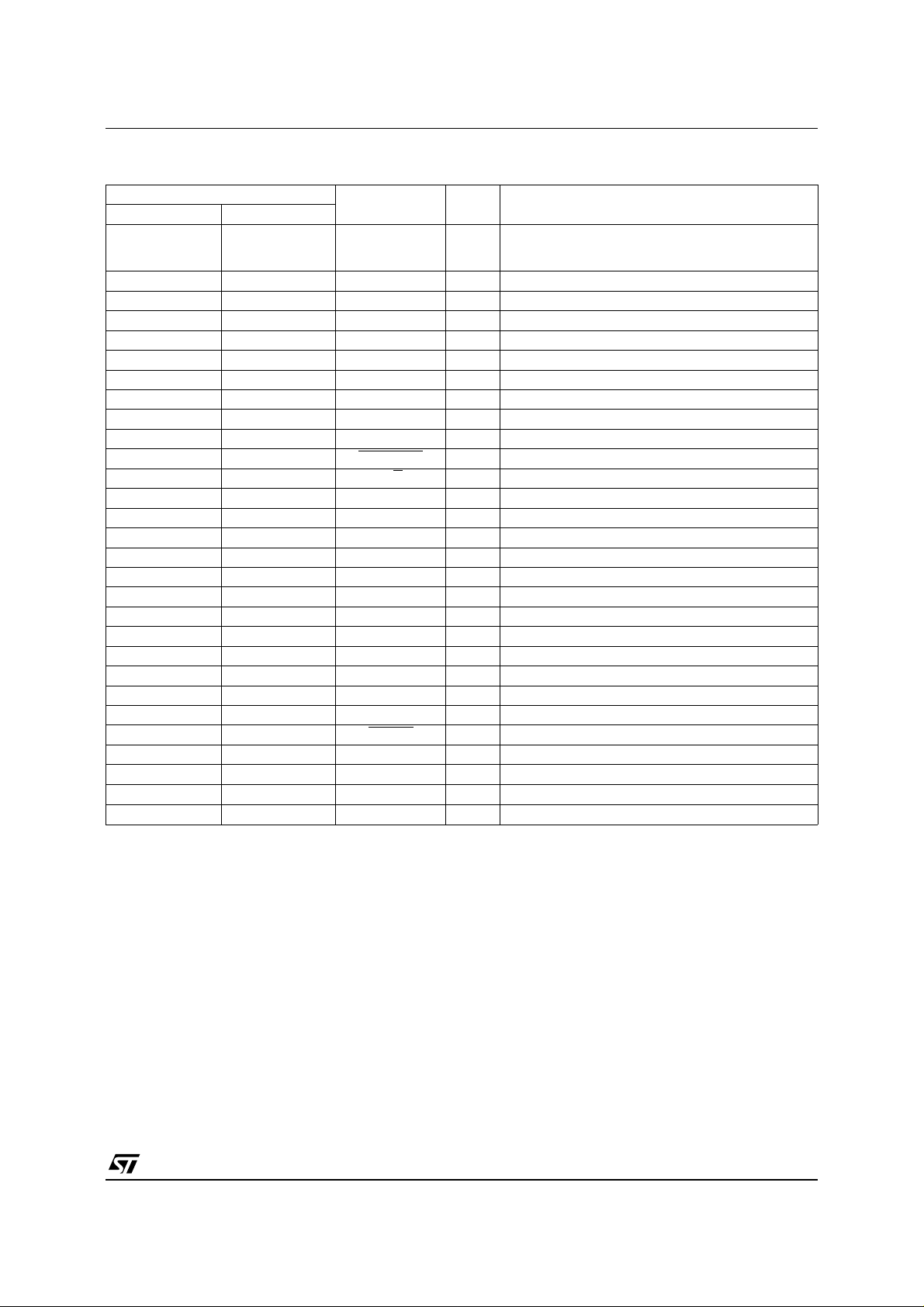

PIN CONNECTIONS

(TQFP48)

HC1

HC0

PWRDWN

M/S

V

REFP

V

REFN

AGND1

MCM

DGND

DD

DV

XTALOUT

13

14

15

16

17

18

19

20

21

22

23

24

25 26 27 28 29 30 31 32 331234 35 36

DD

CM

IN-

AV

V

IN+

AUXIN- XTALIN/MCLK

AUXIN+

FS

SCLK

AGND2

1234567891011

48

47

46

45

44

43

42

41

40

39

DOUT

DIN

TSTD1

TS

RESET

OUT-

OUT+

38

37

7550-01.EPS

2/17

Page 3

PIN LIST

Pin Number

TQFP44 TQFP48

1 - 2, 10 to 13,

21 to 24, 32 to

35, 43 - 44

3 3 SCLK O Shift Clock Output

4 4 FS I/O Frame Synchronization Input (slave)/Output (master)

55DV

6 6 DGND I Digital Ground

7 7 MCM I Master Clock Mode

8 8 XTALOUT O Crystal Output

9 9 XTALIN/MCLK I Crystal Input (MCM = 1) / External Clock (MCM = 0)

14 15 HC1 I Hardware Control Input

15 16 HC0 I Hardware Control Input

16 17

17 18 M/

18 19 V

19 20 V

20 21 AGND1 I Analog Ground

25 27 AUXIN+ I Non-inverting Input to Auxiliary Analog Input

26 28 AUXIN- I Inverting Input to Auxiliary Analog Input

27 29 IN+ I Non-inverting Input to Analog Input Amplifier

28 30 IN- I Inverting Input to Analog Input Amplifier

29 31 AV

30 32 V

31 33 AGND2 I Analog Ground

36 39 OUT+ O Non-inverting Smoothing Filter Output

37 40 OUT- O Inverting Smoothing Filter Output

38 41

39 42 TS I Timeslot Control Input

40 43 TSTD1 I/O Digital Input/Output reserved for test

41 44 DIN I Serial Data Input

42 45 DOUT O Serial Data Output

1 - 2, 10 to 14,

22 to 26, 34 to

38, 46 to 48

STLC7550

Name Type Description

NC - Not connected

DD

PWRDWN I Power down Input

S I Master/Slave Mode Control Pin Input

REFP

REFN

DD

CM

RESET I Reset Function to initialize the internal counters

I Positive Digital Power Supply (2.7V TO 5.5V)

O 16-bit D/A and A/D Positive Reference Voltage

O 16-bit D/A and A/D Negative Reference Voltage

I Positive Analog Power Supply (2.7V to 5.5V)

O Common Mode Voltage Output (AVDD/2)

7550-01.TBL

PIN DESCRIPTION

Supply

DD

(5 pins)

(AV

DD

1.2 - Digital V

)

This pin is the positive digital power s upply for DAC

Supply

DD

and ADC digital internal circuitry.

1.3 - Analog Ground

supply

DD

These pins are the ground return of the analog DAC

(ADC) section.

1.4 - Digital Ground

This pin is the ground for DAC and ADC internal

digital circuitry.

and Digital VDD shoul d be d ecoup led wit h re sp ect to An alo g Gro u nd an d Dig ita l

DD

1 - POWER SUPPLY

1.1 - Analog V

This pin is the positive analog power supply

voltage for the DAC and the ADC sect ion.

It is not internally connected to digital V

(DV

).

DD

In any case the voltage on this pin must be higher

or equal to the voltage of the Digital power supply

).

(DV

DD

Notes :

1. To obtain published performance, the analog V

Ground, respecti vely. The decoupling is intended to isolate digital no i se from the ana l og sectio n ; dec oupling capaci tors sho uld

be as clo se as possi ble to the respective analog and dig i tal suppl y pins.

2. All the ground pins m ust b e tied toget her. In the following sec tion, the ground and s upply pins are referred t o as GND and V

respectively.

(DV

(AGND1, AGND2)

(DGND)

DD

)

DD

3/17

,

Page 4

STLC7550

PIN DESCRIPTION

2 - HOST INTERFACE

2.1 - Data In

(DIN)

(continued)

(10 pins)

In Data Mode, the data word is the input of the DAC

channel. In software, the data word is followed by

the control register word.

2.2 - Data Out

(DOUT)

In Data Mode, the data word is the ADC conversion

result. In software, the data word is followed by t he

register read.

2.3 - Frame Synchronization

(FS)

In master mode, the frame synchronization signal

is used to indicate that the device is ready to send

and receive data. The data trans fer begins on the

falling edge of the frame-sync signal. The framesync is generated internally and goes low on the

rising edge of SCLK in master mode. In slave mode

the frame is generated externally.

2.4 - Serial Bit Clock

(SCLK)

SCLK clocks the digital data into DIN and out of

DOUT during the frame synchronization interval.

The Serial bit clock is generated internally .

RESET)

2.5 - Reset Function

(

The reset function is to initialize the internal counters and control register. A minimum low pulse of

100ns is required to reset the chip. This reset

function initiates the serial data communications.

The reset function will initialize all t he registers to

their default value and will put the device in a

pre-programmed state. After a low-going pulse on

RESET, the device registers will be initialized to

provide an over-sampling ratio equal to 160, the

serial interface will be in data mode, the DAC

attenuation will be set to infinite, the ADC gain will

be set to 0dB, the Differential i nput mode on the

ADC converter will be selected, and the multiplexor

will be set on the main inputs IN+ and IN-. After a

reset condition, the first frame synchronization corresponds to the primary channel.

(

2.6 - Power Down

PWRDWN)

The Power-Down input powers down the entire

chip (< 50µW). When

PWRDWN Pin is taken low,

the device powers down such that the existing

internally programmed state is maintained. When

PWRDWN is driven high, full operation resumes

after 1ms. If the

should be tied to V

2.7 - Hardware Control

PWRDWN input is not used, it

.

DD

(HC0, HC1)

These two pins are used for Hardware/Software

Control of the device. The data on HC0 and HC1

will be latched on to the device on the rising edge

of the Frame Synchronization Pulse. If these two

pins are low, Software Control Mode is selected.

When in Software Control Mode, the LSB of the

16-bit word will select the Data Mode (LSB = 0) or

the Control Mode (LSB = 1). Other combinations of

HC0/HC1 are for Hardware Control. These inputs

should be tied low if not used.

S)

2.8 - Master/Slave Control

When M/

S is high, the device is in master mode

and Fs is gen erate d internal ly. When M/

(M/

S is low,

the device is in slave mode and Fs must be

generat ed externall y.

2.9 - Master Clock Mode

(MCM)

When MCM is high, XTALIN is provide d external ly

and must be equal to 36.864MHz. When MCM is low,

XTALIN is provided externally and must be equal to

oversampling frequency : Fs x Over (see Clock Block

Diagram and §4 Modes of Operation).

2.10 - Timeslot Control

(TS)

When TS = 0 the data are assigned to the first

16 bits after falling edge of FS (7546 mode) otherwise the data are bits 17 to 32.

The case M/

S = 1 with TS = 1 is reserved for life-test

(transmit gain fixed to 0dB).

3 - CLOCK SIGNALS

(2 pins)

Depending on MCM value, these pins have different function.

3.1 - MCM = 1

(XTALIN, XTA LOUT)

These pins must be tied to external crystal. For the

value of crystal see Functional Description Chapter

Part 3.

3.2 - MCM = 0

(MCLK, XTALOUT)

MCLK Pin must be connected to an external c lock.

XT A LOUT is not used.

4/17

Page 5

STLC7550

PIN DESCRIPTION

4 - ANALOG INTERFACE

(continued)

(9 pins)

4.1 - DAC and ADC Positive Reference

)

Voltage Output

(V

REFP

This pin provides the Positive Reference Voltage

used by the 16-bit conv erters. The reference voltage, V

V

REFP

1.25V. V

resp e ct to V

, is the voltage difference between the

REF

and V

REFP

outputs, and its nominal value is

REFN

should be externally decoupled with

.

CM

4.2 - DAC and ADC Negative Reference

Voltage Output

(V

REFN

)

This pin provides the Negative Reference Voltage

used by the 16-bit converters, and should be externally decoupled with respect to V

4.3 - Common Mode V oltage Output

CM

.

)

(V

CM

This output pin is the common mode voltage

(AV

- AGND)/2. This output must be decoupled

DD

with re s p e ct to GN D .

4.4 - Non- inverting Sm oothing Filter Outpu t

(OUT+)

This pin is the non-inverting output of the fully

differential analog smoothing filter.

4.5 - Inverting Smoothing Filter Output

(OUT-)

This pin is the inverting output of the fully differential

analog smoothing filter. Outputs OUT+ and OUTprovide analog signals with maximum peak-topeak amplitude 2 x V

, and must be followed by

REF

an external two pole smoothing filter. The external

filter follows the internal single pole switch capaci-

tor filter. The cutoff frequency of the external filter

must be greater than two times the sampling frequency (FS), so that the combined frequency response of both the internal and external filters is flat

in the passband . The attenuator of the last output

stage can be programmed to 0dB, 6dB or infinite.

4.6 - Non-inverting Analog Input (IN+)

This pin is the differential non-inverting ADC input .

4.7 - Inverting Analog Input

(IN-)

This pin is the differential inverting ADC input.

These analog inputs (IN+, IN-) are presented to the

Sigma-Delta modulator. The analog input peak-topeak differential signal range must be less than

2 x V

, and must be preceded by an external

REF

single pole anti-aliasing filter. The cut-off frequency

of the filter must be lower than one half the oversampling frequency. These filters should be set as

close as possible to the IN+ and IN- pins. The gain

of the first stage is programmable (see Table 3).

4.8 - Non-inverting Auxiliary Analog

Input

(AUX IN+)

This p in is th e dif ferentia l non-i nverti ng au xiliary ADC

input. The characteristics are same as the IN+ input.

4.9 - Inverting Auxiliary Analog Input

(AUX IN-)

This pin is the differential inverting auxiliary ADC

input. The characteristics are same as the IN- input.

The input pair (IN+/IN- or AUX IN+/AUX IN-) are

software selectable.

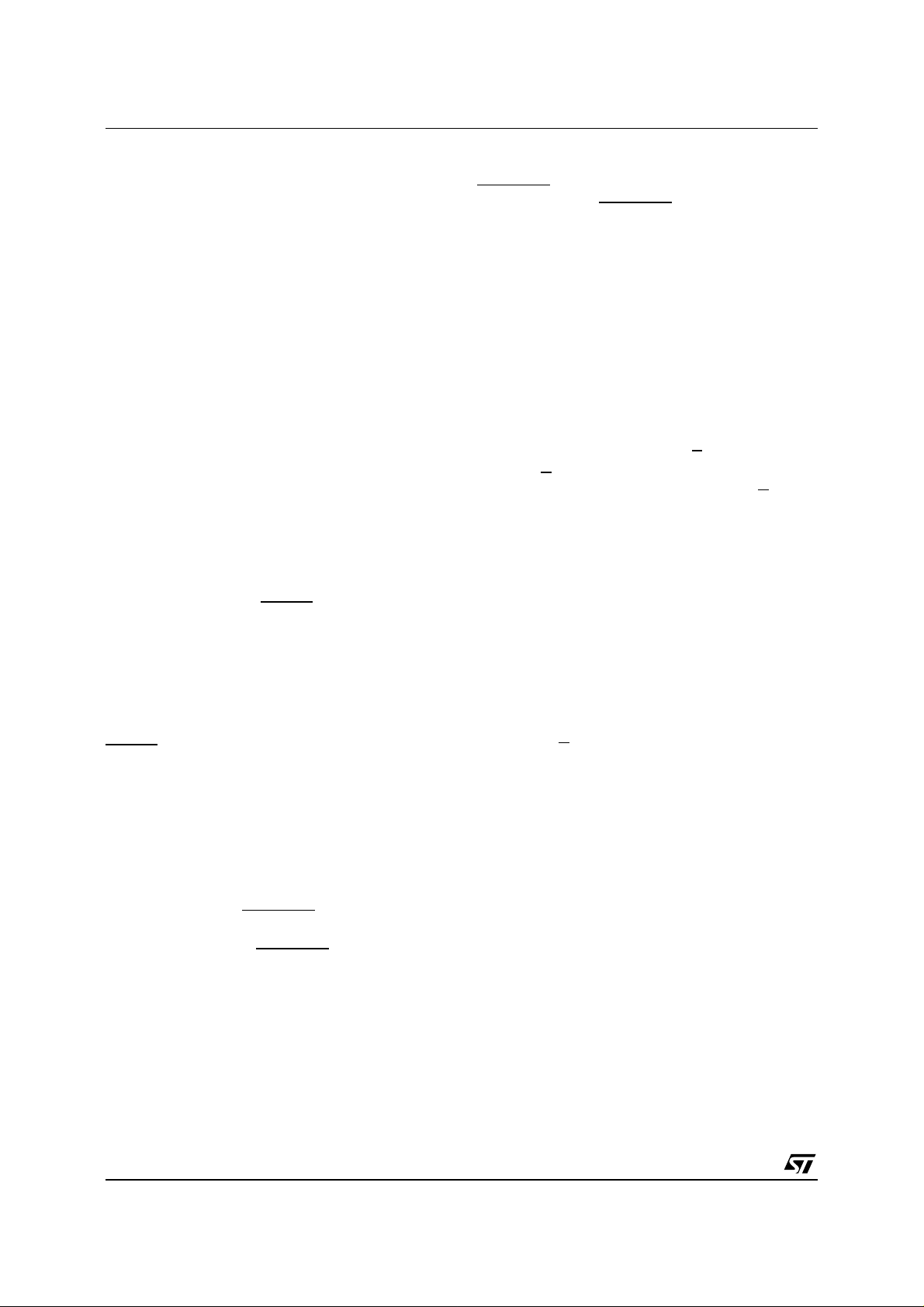

BLOCK DIAGRAM

27

IN+

28

IN-

REFP

REFN

V

25

26

(0 + 6dB in

diff. input)

36

37

18

19

30

CM

ATTEN.

0dB/+6dB/

INFINITE

DD

AUXIN+

AUXIN-

OUT+

OUT-

V

V

(TQFP44)

MUX

MODULATOR

DAC 1 BIT

First order

differential

switched

capacitor

filter

ANALOG

CLOCK

GENERATOR

HC1

HC0

15

14

7

LOW-PASS

(0.425 x sampling

frequency)

SERIAL PORTS

2nd ORDER

MODULATOR

XTALINXTALOUTAGND2AGND1AV

DVDDDGND

LOW-PASS

(0.425 x sampling

frequency)

38 166598312029

RESET PWRDWN

STLC7550

42

41

40

39

17

AND CONTROL REGISTER

MCM

DOUT

DIN

TSTD1

TS

M/S

4

FS

3

SCLK

7550-02.EPS

5/17

Page 6

STLC7550

FUNCTIONAL DESCRIPTION

1 - TRANSMIT D/A SECTION

The functions included in the Tx D/A section are

detailed hereafter. 16-bit 2’s complement data format is used in the DAC channel.

1.1 - Transmit Low Pass Filters

The transmit low pass filter is basically an interpolating filter including a sinx/x correction. It is a

combination of Finite Impulse Res ponse filter (FIR)

and an Infinite Impulse Response filter (IIR). The

digital signal from the serial interface gets interpolated by 2, 3, 4, 5 or 6 x Sampling Frequency (FS)

through the IIR filter. The signal is further interpolated by 32 x FS x n (with n equal to 2, 3, 4, 5, 6)

through the IIR and FIR filter. The low pass filter is

followed by the DAC. The DAC is oversampled at

64, 96, 128, 160, 192 x FS. The oversampling ratio

is user selectable.

1.2 - D/A Converter

The oversampled D/A converter includes a second

order digital noise shaper, a one bit D/A converter

and a single pole analog low-pass filter.

The attenuation of the last output stage can be

programmed to 0dB, +6dB or infinite. The cut-off

frequency of the single pole switch-capacitor lowpass filter is :

fc

with OCLK = Oversampling Clock frequency.

Continuous-time filtering of the analog differential

output is necessary using an off-chip amplifier and

a few external passive components.

At least 79dB signal to noise plus distortion ratio can

be obtained in the frequency band of 0.425 x 9.6kHz

(with an oversampling ratio equal to 160).

2 - RECEIVE A/D SECTION

The different functions included in the ADC channel

section are described below . 16-bit 2’ s complement

data format is used in the ADC.

2.1 - A/D Converter

The oversampled A/D converter is based on a

second order sigma-delta modulator. To produce

excellent common-mode rejection of unwanted signals, the analog signal is processed differentially

until it is converted to digital data. Single-ended

mode can also be used. The ADC is oversampled

at 64, 96, 128, 160 or 192 x FS. The oversampling

ratio is user selectable. At least -85dB SNDR can

be expected in the 0.425 x 9.6kHz bandwidth with

a -6dBr differential input signal and an oversampling ratio equal to 160.

OCLK

=

−

3dB

2

⋅ π ⋅ 10

2.2 - Receive Low Pass Filter

It is a decimation filter . The decimation is performed

by two decimation digital filters : one decimation

FIR filter and one decimation IIR filter.

The purpose of the FIR filter is to decimate 32 times

the digital signal coming from the ADC modulator.

The IIR is a cascade of 5 biquads. It provides the

low-pass filtering needed to remove the noise remaining above half the sampling frequency. The

output of the IIR will be processed by the DSP .

3 - CLOCK GENERA TOR

The master clock, MCLK is provided by the user

thanks to a crystal or e xternal clock generat or (see

Figur e 1) .

The MCLK could be equal to 36.864MHz

(MCM = 1). In that case thanks to the divider M x Q,

the STLC7550 is able to generate all V.34bis and

56 Kbps sampling frequencies (see Table 1).

When MCM = 0, the MCLK mu st be equal to the

oversampling frequency : Fs x OVER (7546 mode).

The ADC and DAC are oversampled at the OCLK

frequency. O CLK is equal to t he s hift clock used in

the serial interface.

The MCLK frequency should be :

MCLK = K x Sampling frequency

Combination of M, Q and oversampling ratios allows to generate several sampling frequencies.

Recommended values for classical modem applications are as follow :

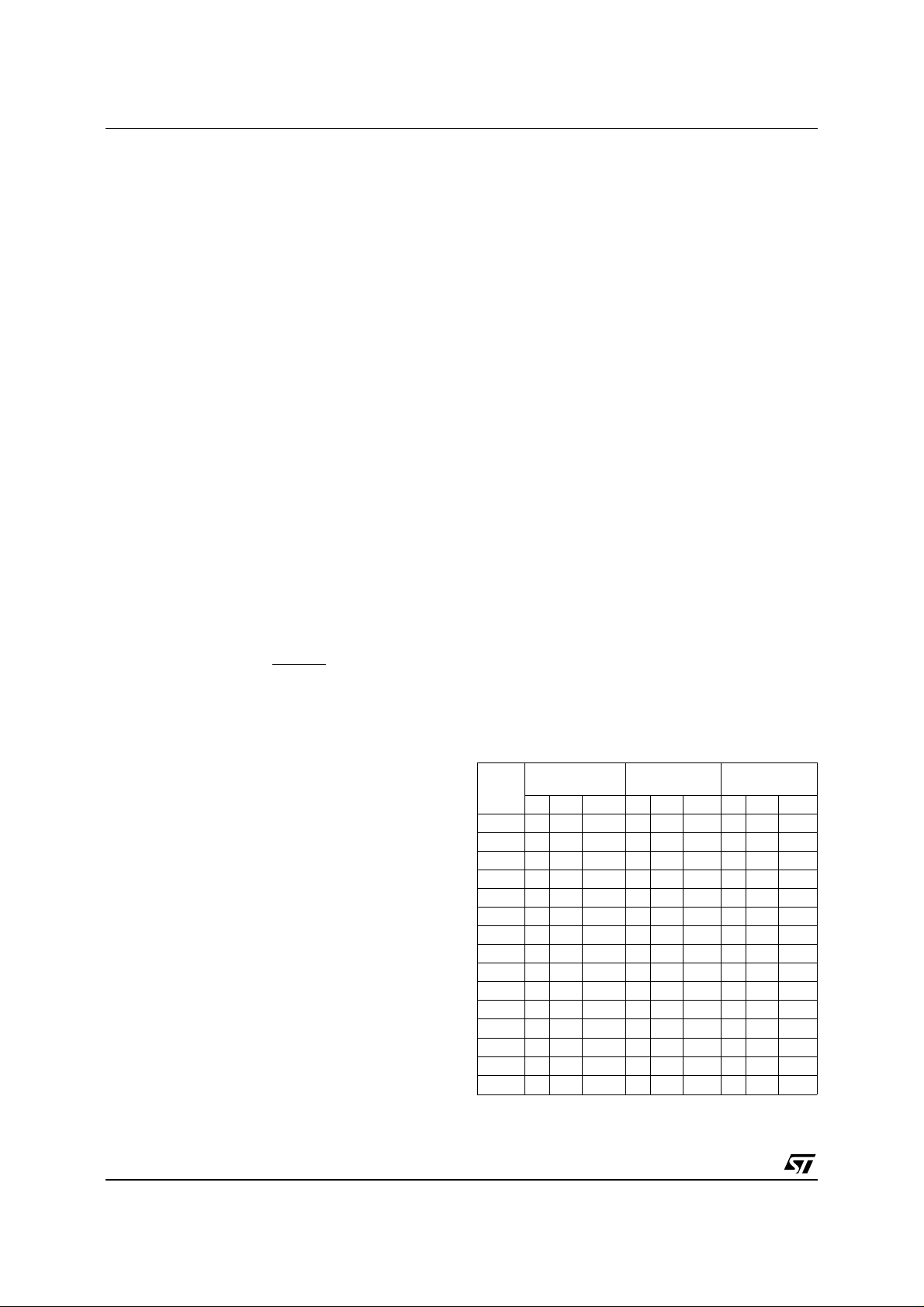

Table 1 :

(kHz)

16.00 3 6 128 2 4.5 128 1 6 96

13.96 3 5.5 160 - - - - - -

13.71 3 7 128 1 7 192 1 7 96

12.80 3 6 160 2 4.5 160 1 4.5 160

12.00 3 8 128 2 6 128 1 6 128

11.82 3 6.5 160 - - - - - -

10.97 3 7 160 - - - - - -

10.47 4 5.5 160 2 5.5 160 1 5.5 160

10.29 4 7 128 2 7 128 1 7 128

9.60 4 6 160 2 6 160 1 6 160

9.00 4 8 128 2 8 128 1 8 128

8.86 4 6.5 160 2 6.5 160 1 6.5 160

8.23 4 7 160 2 7 160 1 7 160

8.00 4 6 192 2 6 192 1 6 192

7.20 4 8 160 2 8 160 1 8 160

Note :

Sampling Frequencies Generation

F

FQ =

36.864MHz (1)

M Q over M Q over M Q over

1. Recommended value.

FQ =

18.432MHz

FQ =

9.216MHz

6/17

Page 7

STLC7550

DD

(continued)

XTALOUT

÷ M ÷ Q

MCM

FUNCTIONAL DESCRIPTION

Figure 1 :

Clock Block Diagram

XTALIN

(MCLK)

V

Cont. Reg. : Bit 8-9-10-11-12-13

4 - MODES OF OPERATION

Thanks to MCM and M/

S programmation pins we

can get the following configuration.

Configuration 1 :

MCM = 1, M/

S = 1

The STLC7550 is in master mode and we have :

Fs = XTAL IN / (M x Q x OVER)

Fs and SCLK are output pins.

Figure 2 :

PROCESSOR

Configuration 1

BCLK

FS

DO

DI

fQ = 36.864MHz

XTALIN

SCLK

FS

DIN

DOUT

M/S

MCM

TS GND

STLC7550

V

DD

V

DD

SCLK

(OCLK)

Sync

% OVER

Bit 3-4-5

M/S

FS

Internal

Sampling

The configuration 4 is equivalent to configuration 3

but the Fs is generated and phase controlled by the

processor .

Figure 3 :

PROCESSOR

Figure 4 :

7550-04.EPS

Configuration 2

fQ = 36.864MHz

XTALIN

BCLK

FS

DO

DI

SCLK

FS

DIN

DOUT

M/S

MCM

TS GND

STLC7550

Configuration 3 (7546 mode)

= K x Fs

f

Q

GND

V

DD

7550-03.EPS

7550-05.EPS

Configuration 2 :

MCM = 1, M/

S = 0

The STLC7550 is in slave mode. SCLK is provided

by the STLC7550, the processor generates the Fs

and controls the phase of the sampling frequency.

Fs must be the result of a division of a number of

cycles of SLCK (Fs = SCLK % OVER).

Configuration 3 :

MCM = 0, M/

S = 1

The STLC7550 is in master mode and the pr ocessor provides the XTAL IN = MCLK = OCLK.

The STLC7550 generates the Fs from OCLK. In

this mode the configuration 3 is equivalent to the

STLC7546 mode.

Configuration 4 :

MCM = 0, M/

S = 0

The STLC7550 is in slave mode.

XTALIN

BCLK

FS

DO

DI

PROCESSOR

Configuration 5 :

MCM = 1, M/

SCLK

FS

DIN

DOUT

STLC7550

MCM = 0, M /

M/S

MCM

TS GND

V

DD

GND

S = 1 (master codec)

S = 0 (sl ave cod ec)

This is dual codec application.

The master codec has his data in timeslot 0 and

the slave codec has his data in timeslot 1 thanks to

the programmation of TS.

7/17

7550-06.EPS

Page 8

STLC7550

FUNCTIONAL DESCRIPTION

Figure 5 :

Figure 6 :

Configuration 4

Configuration 5

PROCESSOR

(continued)

BCLK

DO

PROCESSOR

BCLK

FS

DO

DI

FS

f

= K x Fs

Q

XTALIN

SCLK

FS

M/S

MCM

GND

GND

DIN

DI

DOUT

TS GND

STLC7550

7550-07.EPS

fQ = 36.864MHz

XTALIN

SCLK

FS

DIN

DOUT

M/S

MCM

TS GND

V

DD

V

DD

STLC7550

HC0

HC1

8/17

HC0

XTAKIN

V

DD

TS

FS

DIN

DOUT

HC1

M/S

MCM

GND

GND

STLC7550

7550-08.EPS

Page 9

STLC7550

FUNCTIONAL DESCRIPTION

(continued)

5 - HOST INTERFACE

The Host interface consist of the shift clock,

the frame synchronization signal, the ADCchannel data output, and the DAC-channel

data input.

Two modes of serial transfer are available :

- First : Software mode for 15-bit transmit data

transfer and 16-bit receive data transfer

- Second : hardware mode for 16-bit data transfer.

Both modes are selected by the Hardware Control

pins (HC0, HC1).

T ab le 2 :

HC1 HC0 LSB Useful Data

Figure 7 :

Mode Selection

Secondary

FSYNC

0 0 0 15bits No Software Mode for Data Transfer only.

0 0 1 15bits (+16bits reg.) Yes Software Mode for Data Transfer + Control Register Transfer.

0 1 X 16bits No Hardware Mode for Data Transfer only.

1 X X 16bits (+16bits reg.) Yes Hardware Mode for Data Transfer + Control Register Transfer.

Data Mode

The data to the device, input/output are MSB-first

in 2’s complement format (see Table 2).

When Control Mode is selected, the device will

internally generate an additional Frame Synchronization Pulse (Secondary Frame Synchronization

Pulse) at the midpoint of the original Frame Period.

If the device is in slave mode the additional f rame

sync (secondary frame sync pulse) must be generated by the processor. The Original Frame Synchronization Pulse will also be referred to as the

Primary Frame Synchronization Pulse.

Description

Sampling period

SCLK

TxDI

TxDO

HC1, HC0

Figure 8 :

SCLK

TxDI

TxDO

HC1, HC0

FS

Mixed Mode

FS

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 -

--

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 -

--

00 or 01

Sampling Period

1/2 Sampling Period (see Note)

Data Word Input Control Word

Data Word Output Register Word

1X

D15 D14--

D15 D14--

7550-09.EPS

01

Note :

In slave mode, this 1/2 Sampling Period is not mandatory. If 1/2 Sampling Period is not provided, one sample is lost.

7550-10.EPS

9/17

Page 10

STLC7550

FUNCTIONAL DESCRIPTION

(continued)

6 - CONTROL REGISTER

This section defines the control and device status

information. The register programming occurs only

during Secondary Frame Synchronization. After a

reset condition, the device is always in data mode.

T ab le 3 :

Bits Name Function

10 Q1 Q1 Divider 0

11 Q2 Q2 Divider 0

12 T0 M Divider and Test mode bit 0 0

13 T1 M Divider and Test mode bit 1 0

14 TEST2 Test mode bit 2 0

15 TEST3 Test mode bit 3 0

T ab le 4 :

T ab le 5 :

DIFFERENTIAL INPUT

SINGLE ENDED (one input used, other at V

Note 1 :

Bits Assignment

Reset

Value

0-- 0

1 D1 Aux/Main Input 0

2 D2 Receive Gain 0

3 D3 Oversampling bit 0 0

4 D4 Oversampling bit 1 0

5 D5 Oversampling bit 2 0

6 D6 Attenuator transmit bit 0 0

7 D7 Attenuator transmit bit1 0

8 M M Divider 1

9 Q0 Q0 Divider 1

Aux/Main Input

D1 Function

0 Main Receive Input

1 Auxiliary Receive Input

Receive Gain

D2 Function

0 0dB gain (commun mode fixed)

1 +6dB gain (commun mode non-fixed)

)

CM

0 -6dB gain (see Note 1)

1 0dB gain

Not recommended case. Performan ces coul d be reduced.

Table 6 :

Table 7 :

Table 8 :

D11 D10 D9 Function

Table 9 :

D13 D12 D8 Function

Table 10 :

D15 D14 Function

Oversampling Ratio

D5 D4 D3 Function

0 0 0 160

0 0 1 192

0 1 0 Reserved

0 1 1 Reserved

1 0 0 Reserved

10164

11096

1 1 1 128

Transmit Attenuation

D7 D6 Function

0 0 Inf inite

0 1 Reser ved

1 0 - 6dB

110dB

Q Divider Clock Generator

0 0 0 Q divider = 5

0 0 1 Q divider = 6

0 1 0 Q divider = 7

0 1 1 Q divider = 8

1 0 0 Q divider = 4.5

1 0 1 Q divider = 5.5

1 1 0 Q divider = 6.5

1 1 1 Q divider = 7.5

M Divider Clock Generator

0 0 0 M divider = 3

0 0 1 M divider = 4

0 1 X Reserved

1 0 X Reserved

1 1 0 M divider = 1

1 1 1 M divider = 2

Reserved Mode

X X Reserved for test

This two bits must be set to 0 for normal operation.

10/17

Page 11

ELECTRICAL SPECIFICATIONS

Unless otherwise noted, Electrical Characteristics are specified over the operating range.

Typical values are given for V

= 3V, T

DD

= 25°C and for nominal Master clock frequency

amb

MCLK = 1.536MHz and oversampling ratio = 160.

STLC7550

Absolute Maximum Ratings

(referenced to GND)

Symbol Parameter Value Unit

V

V

I,VIN

I

I,IIN

I

I

OUT

T

oper

T

P

DMAX

DC Supply Voltage -0.3, 7.0 V

DD

Digital or Analog Input Voltage -0.3, VDD+0.3 V

Digital or Analog Input Current ±1mA

Digital Output Current ±20 mA

O

Analog Output Current ±10 mA

Operating Temperature 0, 70 °C

Storage Temperature -40, 125 °C

stg

Maximum Power Dissipation 200 mW

ESD Electrostatic Discharge 2000 V

= 3V ± 5%, GND = 0V, TA = 0 to 70°C unless otherwise specified)

Nominal DC Characteristics

(V

DD

Symbol Parameter Min. Typ. Max. Unit

V

DD

Supply Voltage Range 2.70 3 5.5 V

POWER SUPPLY AND COMMON MODE VOLTAGE

SINGLE POWER SUPPLY (DV

I

DDA

I

DDD

I

-LP Supply Current in Low Power Mode MCLK Stopped

DD

V

CM

Analog Supply Current 6 mA

Digital Supply Current 4 mA

Output Common Mode Voltage

VCM Output Voltage Load Current (see Note 1)

= AVDD)

DD

MCLK Running

1

10 µA

200

VDD/2-5% VDD/2 VDD/2+5% V

DIGITAL INTERFACE

V

IL

V

IH

I

I

V

OH

V

OL

Low Level Input Voltage -0.3 0.5 V

High Level Input Voltage DVDD-0.5 V

Input Current VI = VDD or VI = GND -10 ±110µA

High Level Output Voltage (I

Low Level Output Voltage (I

= -600µA) DVDD-0.5 V

LOAD

= 800µA) 0.3 V

LOAD

ANALOG INTERFACE

V

REF

Tempco (V

V

CMO IN

V

DIF IN

V

OFF IN

V

CMO OUT

V

DIF OUT

V

OFF OUT

R

IN

R

OUT

R

L

C

L

V

ADO OUT

Note :

1. Device is very sensitive to noise on V

Differential Reference Voltage Output

V

= (V

REF

)V

REF

Temperature Coefficient 200 ppm/°C

REF

Input Common Mode Offset Voltage = [(IN+)+(IN-)]/2 -V

Differential Input Voltage : [(IN+)-(IN-)] ≤ 2 x V

Differential Input DC Offset Voltage -100 100 mV

Output Common Mode Voltage Offset :

(OUT+ + OUT-)/2 - V

Differential Output Voltage : OUT+ - OUT- ≤ 2 x V

Differe ntial O utput DC Offset V oltage : (OUT+ - OUT- ) (0000x) -100 100 mV

Input Resistance IN+, IN- (id. AUX IN) 100 kΩ

Output Resistance (OUT+, OUT-) 50 Ω

Load Resistance (OUT+, OUT-) 10 kΩ

Load Capacitance (OUT+, OUT-) 20 pF

Output A/D Modulator Voltage Offset : IN+ = IN- = V

VCM must be buffered. AC variation in VCM current magnitude decrease A/D and D/A performance.

REFP

- V

REFN

)

CM

REF

(see Note 1)

CM

REF

CM

Pin. VCM output voltage load current must be DC (<10µA). in order to drive dynamic load,

CM

1.15 1.25 1.35 V

-100 100 mV

2 x V

REF

-20 20 mV

2 x V

REF

-1000 +1000 LSB

µA

Vpp

V

11/17

Page 12

STLC7550

ELECTRICAL SPECIFICATIONS

(continued)

Nominal AC Electrical Characteristics

(Reference level V

= 0.5V, VIH = DVDD - 0.5V, VOL = 0.3V , VOH = DVDD - 0.5V, DVDD = 3V,

IL

Output load = 50pF unless otherwise)

Symbol N° Parameter Min. Typ. Max. Unit

SERIAL CHANNEL TIMING (see Figure 9 for Parameter numbers)

1 SCLK Period 300 ns

2 SCLK Width Low 150 ns

3 SCLK Width High 150 ns

4 SCLK Rise Time 10 ns

5 SCLK Fall Time 10 ns

6 FS Setup 100 ns

7 FS Hold 100 ns

8 DIN Setup 50 ns

9 DIN Hold 0 ns

10 DOUT Valid 20 ns

11 HC0,HC1 Set-up 20 ns

12 0 50 ns

MASTER CLOCK INTERFACE (MCLK) (MCM = 0)

MCLK Master Clock Input 0.92 1.54 2.8 MHz

Master Clock Duty Cycle 45 55 %

Figure 9 :

Serial Interface Timing Diagram

SCLK

FS

DIN

DOUT

HC0

12

67

11

MSB

10

MSB

1

2.4

89

35

7550-11.EPS

12/17

Page 13

STLC7550

ELECTRICAL SPECIFICATIONS

(continued)

Transmit Characteristics

Performance of the Tx channel

Typical values are given for AV

= 3V, T

DD

= 25°C and for nominal master clock MCLK = 1.536MHz,

amb

differential mode and oversampling ratio = 160. Measurement band = 100Hz to 0.425 x Sampling frequency.

Symbol Parameter Min. Typ. Max. Unit

Gabs Absolute Gain at 1kHz -0.5 0 0.5 dB

Ripple Ripple in Band : 0 to 0.425 x FS ±0.2 dB

THD Total Harmonic Distortion (differential Tx signal : V

DR

CRxTx Crosstalk (transmit channel to receive channel) 85 dB

Dynamic Range (f = 1kHz) (measured over the full 0 to FS/2 with a -20dBr

output signal and extrapolated to full scale) (see Note 2)

= 1.25VPP, f = 1kHz) -85 -92 dB

OUT

87 dB

Smoothing filter transfer characteristics

The cut-off frequency of the single pole switch-capacitor low-pass filter following the DAC is :

−

3dB

n ⋅ 32 ⋅ FS

=

2 ⋅ π ⋅ 10

with n = 2, 3, 4, 5, 6 (see paragraph Functional Description 1.2).

fc

Receive Characteristics

Performance of the Rx channel

Typical values are given for AV

=3V, T

DD

= 25°C and for nominal master clock MCLK = 1.536MHz,

amb

differentia l mode and oversam pling ratio = 16 0. Measurem ent band = 100Hz to 0.425 x Sampl ing Frequency .

Symbol Parameter Min. Typ. Max. Unit

Gabs Absolute Gain at 1kHz -0.5 0 0.5 dB

Ripple Ripple in Band : 0 to 0.425 x FS ±0.2 dB

THD Total Harmonic Distortion (differential Rx signal : V

DR

PSRR Power Supply Rejection Ratio (f = 1kHz, V

CTxRx Crosstalk (transmit channel to receive channel) 85 dB

Note 2 : The dynamic range can be measured in bit with : N

Dynamic Range (f = 1kHz) (measured over the full 0 to FS/2 with a -20dBr

input and extrapolated to full scale) (see Note 2)

AC

DR −

=

bit

6.02

= 1.25VPP, f = 1kHz) -92 dB

IN

87 dB

= 200mVPP)50dB

1.76

with DR in dB.

13/17

Page 14

STLC7550

TYPICAL APPLICATION

Line Interface - Differential Duplexor

Figure 10

22k

13.2k

OUT+

680pF

13.2k

OUT-

IN+

22k

W

W

22k

22k

1.2k

W

100pF

W

W

W

100pF

W

C : Improve the low frequency response.

Its value depends on the transformer inductance.

C' : Reduces the DC offset gain.

Z0 : Nominal line impedance

Z0/2

C

VCM

2R

Z0/2

C

2R

R

Phone

Line

1.2k

R'

r

C'

R'

W

R

2.2nF

VCM

2.2nF

IN-

All capacitor, resistor and impedance values are provided for indication only. These values must be

readjusted according to line transformer characteristics and also telecommunication regulations in force in

individual countries.

Refer to Application Note AN930 for more detailed information. Contact your local representative.

7550-12.EPS

14/17

Page 15

DEFINITION AND TERMINOLOGY

Data Transfer Interval

Signal Data

Data Mode

Control Mode

Frame Sync.

Frame Sync and

Sampling Period

ADC Channel

DAC Channel

OverSampling Ratio

Resolution

Dynamic Range

Signal-to-(Noise+Distortion)

Crosstalk

Power Supply Rejection Ratio

STLC7550

The time during which data is transfered from D

interval is 16 shift clocks provides by the chip.

This refers to the input signal and all the converted representations

through the ADC channel and the DAC channel.

This refers to the data transfer. Since the device is synchronous, the

signal data words from the ADC channel and to the DAC channel occur

simultaneously .

This refers to the digital control data transfer into DIN and the register

read data from D

. The control mode interval occurs when

OUT

requested by hardware or software.

Frame sync refers only to the falling edge of the s ignal whic h initiates

the data transfer interval. The primary frame sync starts the Data Mode

and the secondary frame sync starts the Control Mode.

The time between falling edges of successive primary frame sync

signals.

This term refers to all signal processing circuits between the analog

input and the digital conversion result at D

OUT

This term refers to all signal processing circuits between the digital

data word applied to D

and the differential output analog signal

IN

available at OUT+ and OUT- pins.

This term refer to the ratio between the master clock MCLK

corresponding to the oversampling frequency and the sampling

frequency FS.

The number of bits in the input words to the DAC, and t he output words

in the ADC.

The S/(N+D) with a 1kHz, -20dBr input signal and extrapolated to full

scale. Use of a small input signal reduces the harmonic distortion

components of the noise to insignificance. Units in dB or in N

explained before.

S/(THD+N) is the ratio of the rms of the input signal to the rms of all

other spectral components within the measurement bandwidth

(0.425 x Sampling Frequency). Units in dB.

The amount of 1kHz signal present on the output of t he grounded input

channel with 1kHz 0dB signal present on the other channel. Units

in dB.

PSRR. The amount of 1kHz signal present on the output of the

grounded input channel with 1kHz 200mVPP signal present on the

power supply.

and to DIN. This

OUT

.

as

bit

15/17

Page 16

STLC7550

PACKAGE MECHANICAL DATA

(continued)

44 PINS - PLASTIC QUAD FLA T P AC K (THIN)

A

A2

A1

B

c

D3

D1

e

33

E3

E1

23

D

L1

K

0,10 mm

.004 inch

SEATING PLANE

E

L

0,25 mm

.010 inch

GAGE PLANE

Dimensions

44 34

1

11

12 22

Millimeters Inches

Min. Typ. Max. Min. Typ. Max.

A 1.60 0.063

A1 0.05 0.15 0.002 0.006

A2 1.35 1.40 1.45 0.053 0.055 0.057

B 0.30 0.37 0.40 0.012 0.015 0.016

C 0.09 0.20 0.004 0.008

D 12.00 0.472

D1 10.00 0.394

D3 8.00 0.315

e 0.80 0.031

E 12.00 0.472

E1 10.00 0.394

E3 8.00 0.315

L 0.45 0.60 0.75 0.018 0.024 0.030

L1 1.00 0.039

K0

o

(Min.), 7o (Max.)

PM-4Y.EPS

4Y.TBL

16/17

Page 17

STLC7550

PACKAGE MECHANICAL DATA

(continued)

48 PINS - PLASTIC QUAD FLA T P AC K (THIN)

A

A2

A1

B

c

17/17

D3

D1

D

e

0,10 mm

.004 inch

E1

L1

E

L

K

SEATING PLANE

0,25 mm

.010 inch

GAGE PLANE

36

E3

25

Dimensions

48 37

1

12

13 24

Millimeters Inches

Min. Typ. Max. Min. Typ. Max.

A 1.60 0.063

A1 0.05 0.15 0.002 0.006

A2 1.35 1.40 1.45 0.053 0.055 0.057

B 0.17 0.22 0.27 0.007 0.009 0.011

C 0.09 0.20 0.004 0.008

D 9.00 0.354

D1 7.00 0.276

D3 5.50 0.216

e 0.50 0.0197

E 9.00 0.354

E1 7.00 0.276

E3 5.50 0.216

L 0.45 0.60 0.75 0.018 0.024 0.030

L1 1.00 0.039

K0

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the

consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from

its use. No licence is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications

mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information

previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or sys tem s

without express written approv al of STMi cr oelec troni cs.

Purchase of I

Rights to use these components in a I

Australia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Neth erlands

Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

The ST logo is a registered trademark of STMicroelectronics

© 1998 STMicroelectronics - All Rights Reserved

2

C Components of STMicroelectronics, conveys a license under the Philips I2C Pate n t .

2

the I

C Standard Specifications as defined by Phili ps.

STMicroelectronics GROUP OF COMPANIES

2

C system, is granted provided that the system conforms to

http://www.st.com

o

(Min.), 7o (Max.)

PM-5B.EPS

5B.TBL

Loading...

Loading...