Page 1

STB100NF04L

N-CHANNEL 40V - 0.0036 Ω - 100A D2PAK

STripFET™ II POWER MOSFET

TYPE

V

DSS

STB100NF04L 40 V <0.0042

■ TYPICAL R

■ LOW THRESHOLD DRIVE

■ 100% AVALANCHE TESTED

■ LOGIC LEVEL DEVICE

(on) = 0.0036 Ω

DS

R

DS(on)

I

D

100 A

Ω

DESCRIPTION

This Power MOSFET is the latest dev elo pment of

STMicroelectronis unique "Single Feature Size™"

strip-based process. The resulting transistor

shows extremely high packing density for low onresistance, rugged avalanche characteristics and

less critical alignment steps therefore a remarkable manufacturing reproducibility.

APPLICATIONS

■ HIGH CURRENT, HIGH SWITCHING SPEED

■ MOTOR CONTROL, AUDIO AMPLIFIERS

■ DC-DC & DC-AC CONVERTERS

■ SOLENOID AND RELAY DRIVERS

3

1

D2PAK

TO-263

(Suffix “T4”)

ADD SUFFIX “T4” FOR ORDERING IN TAPE & REEL

INTERNAL SCHEMATIC DIAGRAM

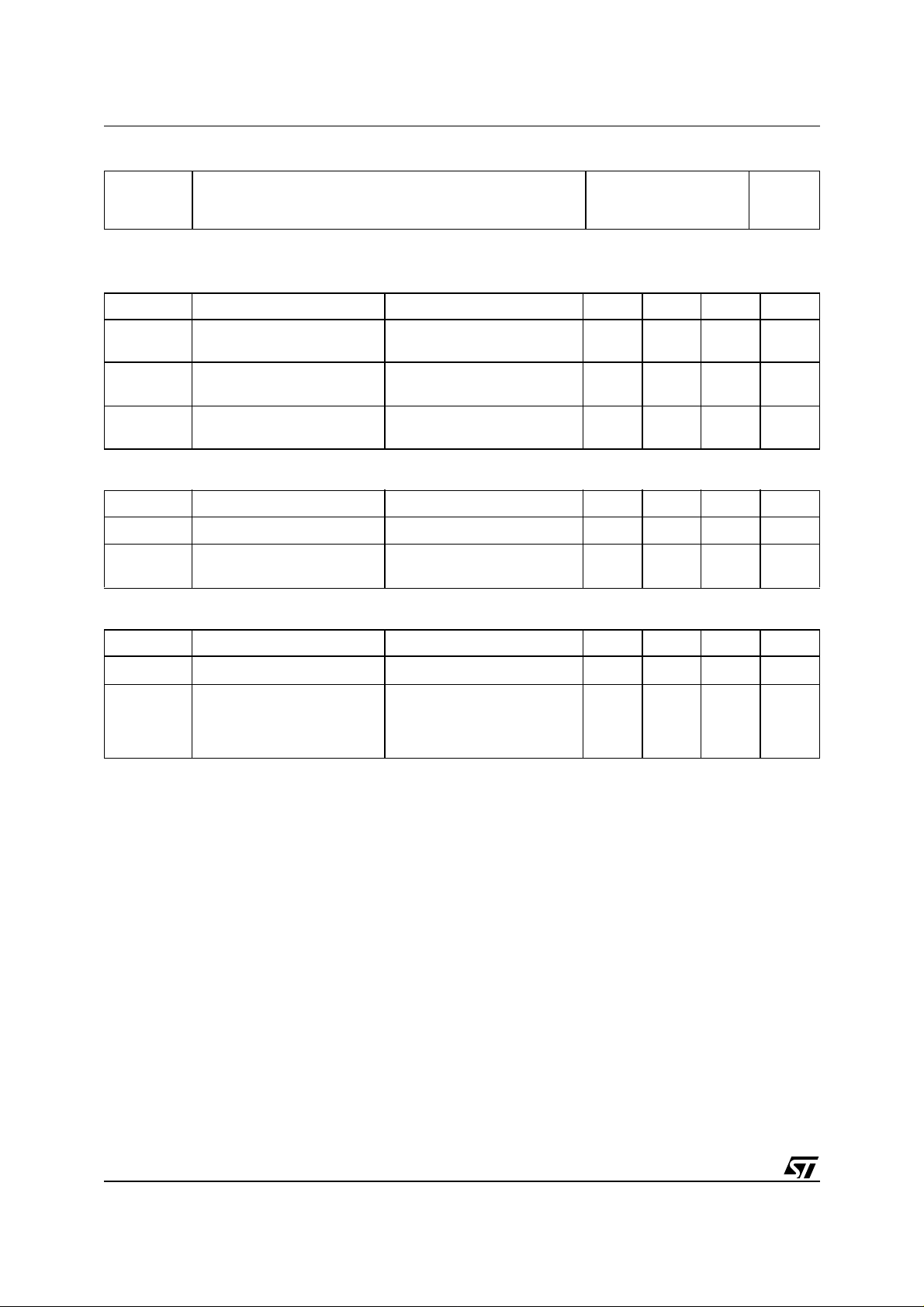

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

DS

V

DGR

V

GS

(*) Drain Current (continuos) at TC = 25°C

I

D

I

D

(

I

DM

P

tot

dv/dt

E

AS

T

stg

T

j

(

Pulse widt h l i m i ted by safe operating area.

•)

(*) Curren t Lim i ted by package

.

Drain-source Voltage (VGS = 0)

Drain-gate Voltage (RGS = 20 kΩ)

40 V

40 V

Gate- source Voltage ± 16 V

100 A

Drain Current (continuos) at TC = 100°C

•)

Drain Current (pulsed) 400 A

Total Dissipation at TC = 25°C

70 A

300 W

Derating Factor 2 W/°C

(1)

Peak Diode Recovery voltage slope 3.6 V/ns

(2)

Single Pulse Avalanche Energy 1.4 J

Storage Temperature -65 to 175 °C

Max. Operating Junction Temperature 175 °C

(1) ISD ≤100A, di/dt ≤240A/µs, VDD ≤ 32V, Tj ≤ T

(2) Starting Tj = 25 oC, IAR = 50A, VDD= 30V

JMAX

1/9February 2002

Page 2

STB100NF04L

THERMA L D ATA

Rthj-case

Rthj-amb

T

Thermal Resistance Junction-case

Thermal Resistance Junction-ambient

Maximum Lead Temperature For Soldering Purpose

j

Max

Max

Typ

0.5

62.5

300

°C/W

°C/W

°C

ELECTRICAL CHARACTERISTICS (T

= 25 °C unless otherwise specified)

case

OFF

Symbol Parameter Test Conditions Min. Typ. Max. Unit

I

= 250 µA, VGS = 0

D

V

= Max Rating

DS

V

= Max Rating TC = 125°C

DS

V

= ± 16 V

GS

40 V

1

10

±100 nA

ON

V

(BR)DSS

I

DSS

I

GSS

(*)

Drain-source

Breakdown Voltage

Zero Gate Voltage

Drain Current (V

GS

Gate-body Leakage

Current (V

DS

= 0)

= 0)

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

V

GS(th)

R

DS(on)

Gate Threshold Voltage

Static Drain-source On

Resistance

= VGS I

DS

= 10 V ID = 50 A

V

GS

V

= 4.5 V ID = 50 A

GS

= 250 µA

D

1V

0.0036

0.0040

0.0042

0.0065

DYNAMIC

Symbol Parameter Test Conditions Min. Typ. Max. Unit

(*)

g

fs

C

iss

C

oss

C

rss

Forward Transconductance

Input Capacitance

Output Capacitance

Reverse Transfer

Capacitance

V

= 15 V ID= 20 A

DS

= 25V, f = 1 MHz, VGS = 0

V

DS

50 S

6400

1300

190

µA

µA

Ω

Ω

pF

pF

pF

2/9

Page 3

STB100NF04L

ELECTRICAL CHARACTERISTICS (continued)

SWITCHING ON

Symbol Parameter Test Conditions Min. Typ. Max. Unit

t

d(on)

Turn-on Delay Time

t

r

Rise Time

V

DD

R

= 4.7 Ω VGS = 4.5 V

G

37

270

= 20 V ID = 50 A

(Resistive Load, Figure 3)

Q

g

Q

gs

Q

gd

Total Gate Charge

Gate-Source Charge

Gate-Drain Charge

= 32V ID= 100A VGS= 4.5V

V

DD

72

20

28.5

90 nC

SWITCHING OFF

Symbol Parameter Test Conditions Min. Typ. Max. Unit

t

d(off)

= 20 V

Turn-off Delay Time

t

f

Fall Time

V

DD

R

= 4.7Ω, V

G

(Resistive Load, Figure 3)

D

GS

= 50 A

= 4.5 V

90

80

ns

ns

nC

nC

ns

ns

t

r(Voff)

t

t

f

c

Fall Time

Cross-over Time

Off-voltage Rise Time

= 32 V ID = 100 A

V

clamp

R

= 4.7Ω, V

G

GS

= 4.5 V

(Inductive Load, Figure 5)

85

125

160

SOURCE DRAIN DIODE

Symbol Parameter Test Conditions Min. Typ. Max. Unit

I

SD

I

SDM

V

SD

t

rr

Q

rr

I

RRM

(*)

Pulsed: P ul se duration = 300 µs, duty cycle 1.5 %.

(

•)Pulse width limited by s afe operating area.

Source-drain Current

(•)

Source-drain Current (pulsed)

(*)

Forward On Voltage

Reverse Recovery Time

Reverse Recovery Charge

Reverse Recovery Current

I

= 100A VGS = 0

SD

= 100 A di/dt = 100A/µs

I

SD

V

= 20 V Tj = 150°C

DD

(see test circuit, Figure 5)

Thermal ImpedanceSaf e Operating Area

100

400

1.3 V

88

240

5.5

ns

ns

ns

A

A

ns

nC

A

3/9

Page 4

STB100NF04L

Output Characteristics Transfer Characteristics

Transconductance Static Drain-source On Resistance

Gate Charge vs Gate-source Voltage Capacitance Variations

4/9

Page 5

STB100NF04L

Normalized Gate Threshold Voltage vs Temperature Normalized on Resistance vs Temperature

Source-drain Diode Forward Characteristics Normalized Breakdown Voltage Temperature.

. .

5/9

Page 6

STB100NF04L

Fig. 1: Unclamped Inductive Load Test CircuitFig. 1: Unclamped Inductive Load Test Circuit Fig. 2: Unclamped Inductive Waveform

Fig. 3: Switching Times Test Circuits For Resistive

Load

Fig. 5: Test Circuit For Inductive Load Switching

And Diode Recovery Times

Fig. 4: Gate Charge test Circuit

6/9

Page 7

D2PAK MECHANICAL DATA

STB100NF04L

DIM.

MIN. TYP. MAX. MIN. TYP. TYP.

mm. inch.

A 4.4 4.6 0.173 0.181

A1 2.49 2.69 0.098

0.106

A2 0.03 0.23 0.001 0.009

B 0.7 0.93 0.028 0.037

B2 1.14 1.7 0.045 0.067

C 0.45 0.6 0.018 0.024

C2 1.21 1.36 0.048 0.054

D 8.95 9.35 0.352 0.368

D1 8 0.315

E 10 10.4 0.394 0.409

E1 8.5 0.334

G 4.88 5.28 0.192 0.208

L 15 15.85 0.591 0.624

L2 1.27 1.4 0.050 0.055

L3 1.4 1.75 0.055 0.069

M 2.4 3.2 0.094 0.126

R 0.4 0.016

V2 0° 8° 0° 8°

7/9

Page 8

STB100NF04L

D2PAK FOOTPRINT

TAPE AND REEL SHIPMENT (suffix ”T4”)*

TUBE SHIPMENT (no suffix)*

REEL MECHANICAL DATA

DIM.

A 330 12.992

B 1.5 0.059

C 12.8 13.2 0.504 0.520

D 20.2 0.795

G 24.4 26.4 0.960 1. 039

N 100 3.937

T 30.4 1.197

mm inch

MIN. MAX. MIN. MAX.

TAPE MECHANICAL DATA

DIM.

A0 10.5 10.7 0.413 0.421

B0 15.7 15.9 0.618 0.626

D 1.5 1.6 0.059 0.063

D1 1.59 1.61 0.062 0.063

E 1.65 1.85 0.065 0.073

F 11.4 11.6 0.449 0.456

K0 4.8 5.0 0.189 0.197

P0 3.9 4.1 0.153 0.161

P1 11.9 12.1 0.468 0.476

P2 1.9 2.1 0075 0.082

R50 1.574

T0.25 0.35 .0.0098 0.0137

W 23.7 24.3 0.933 0.956

mm inch

MIN. MAX. MIN. MAX.

* on sales type

8/9

BASE QTY BULK QTY

1000 1000

Page 9

STB100NF04L

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted

by implic ation or otherwise under any patent or patent r i ght s of STMi croelectr oni cs. Spec i fications mentioned i n this publication are subject

to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics product s are not

authorized for use as cri tical comp onents in lif e support devi ces or systems without express written approva l of STMicroe l ectronics.

The ST logo is registered trademark of STMicroelectronics

2002 STMi croelectronics - All Ri ghts Rese rved

All other na m es are the property of their respective owners.

Australi a - Brazil - Canada - Chin a - F i nland - France - German y - Hong Kong - I ndia - Israel - It al y - Japan - Malaysia - Mal ta - Morocco -

Singap ore - Spain - Sw eden - Switzerland - Uni ted Kingdom - United St at es.

STMicroelectronics GROUP OF COMPANIES

http:// www.st.com

9/9

Loading...

Loading...