Page 1

Y

-DSR

S

-

GENERAL DESCRIPTION

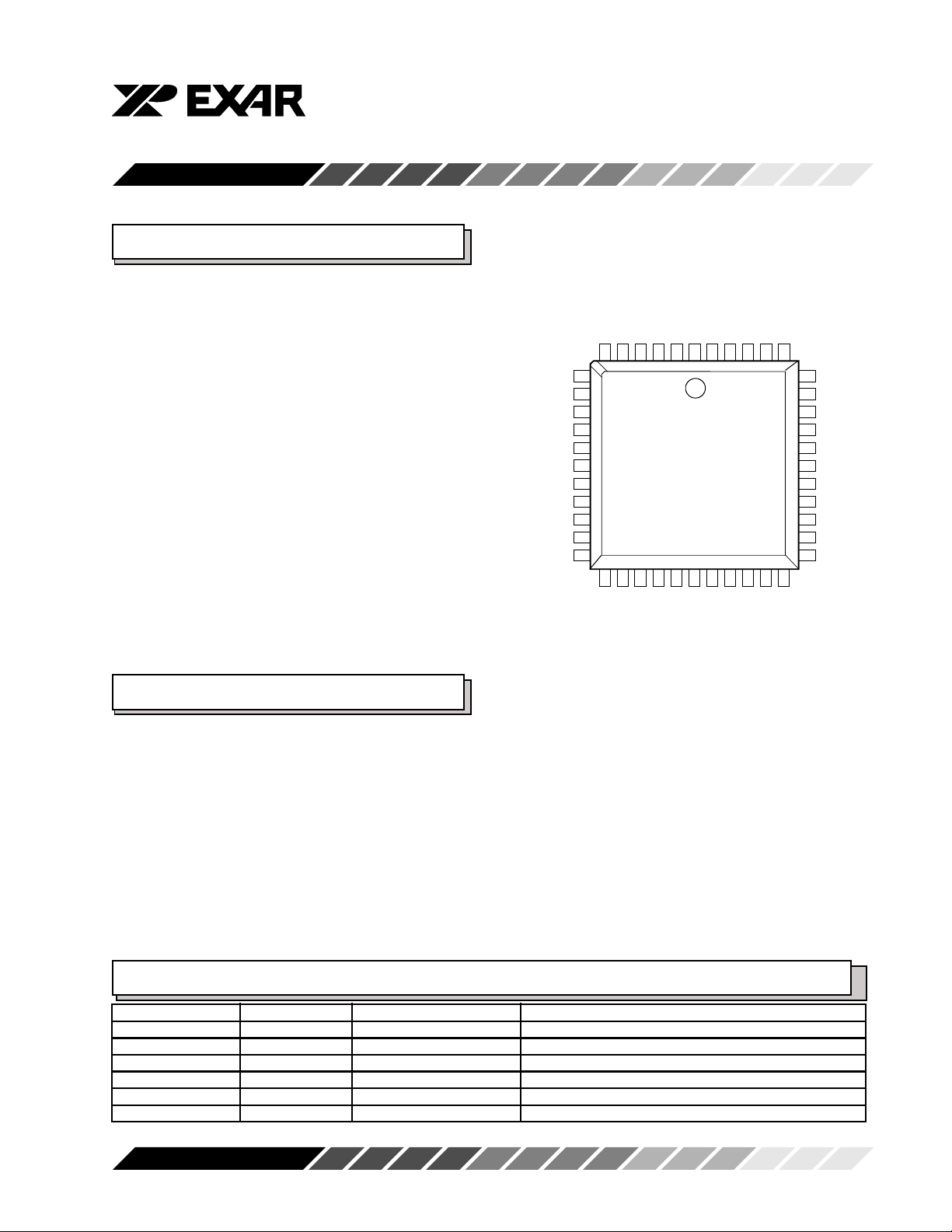

ST16C550

UART WITH 16-BYTE FIFO’s

April 2005

The ST16C550 (550) is a universal asynchronous receiver and transmitter with 16 byte transmit and receive

FIFO. It operates at 2.97 to 5.5 volts. A programmable

baud rate generator can select transmit and receive

clock rates from 50 bps to 1.5 Mbps.

The ST16C550 is an improved version of the NS16C550

UART with higher operating speed and lower access

time. The ST16C550 on board status registers provides

the error conditions, type and status of the transfer

operation being performed. Included is complete MODEM control capability, and a processor interrupt

system that may be software tailored to the user’s

requirements. The ST16C550 provides internal loopback capability for on board diagnostic testing.

The ST16C550 is available in 40 pin PDIP, 44 pin PLCC,

and 48 pin TQFP packages. It is fabricated in an

advanced CMOS process to achieve low drain power

and high speed requirements.

FEATURES

RCLK

N.C.

CS0

CS1

-CS2

-BAUDOUT

PLCC Package

D4D3D2D1D0

6

5

4

7

D5

8

D6

9

D7

10

11

RX

12

13

TX

14

15

16

17

1819202122232425262728

-IOW

XTAL1

XTAL2

N.C.VCC

3

2

1

4443424140

ST16C550CJ44

N.C.

-IOR

GND

IOW

-RI

IOR

-CD

-CT

39

RESET

38

-OP1

37

-DTR

36

-RTS

35

-OP2

34

N.C.

33

INT

32

-RXRD

31

A0

30

A1

29

A2

-AS

-DDIS

TXRDY

• Pin to pin and functionally compatible to the Industry

Standard 16C550

• 2.97 to 5.5 volt operation

• 24MHz clock operation at 5V

• Standard modem interface

• Compatible with ST16C450

• Low operating current ( 1.2mA typ.)

• 16MHz clock operation at 3.3V

• 16 byte transmit FIFO

• 16 byte receive FIFO with error flags

• Full duplex operation

• Transmit and receive control

• Four selectable receive FIFO interrupt trigger levels

ORDERING INFORMATION

Part number Package Operating temperature Device Status

ST16C550CP40 40-Lead PDIP 0° C to + 70° C Active. See the ST16C550CQ48 for new designs.

ST16C550CJ44 44-Lead PLCC 0° C to + 70° C Active

ST16C550CQ48 48-Lead TQFP 0° C to + 70° C Active

ST16C550IP40 40-Lead PDIP -40° C to + 85° C Active. See the ST16C550IQ48 for new designs.

ST16C550IJ44 44-Lead PLCC -40° C to + 85° C Active

ST16C550IQ48 48-Lead TQFP -40° C to + 85° C Active

Rev. 5.01

EXAR Corporation, 48720 Kato Road, Fremont, CA 94538 • (510) 668-7000 • FAX (510) 668-7017

Page 2

ST16C550

-

Y

.

-

Y

Y

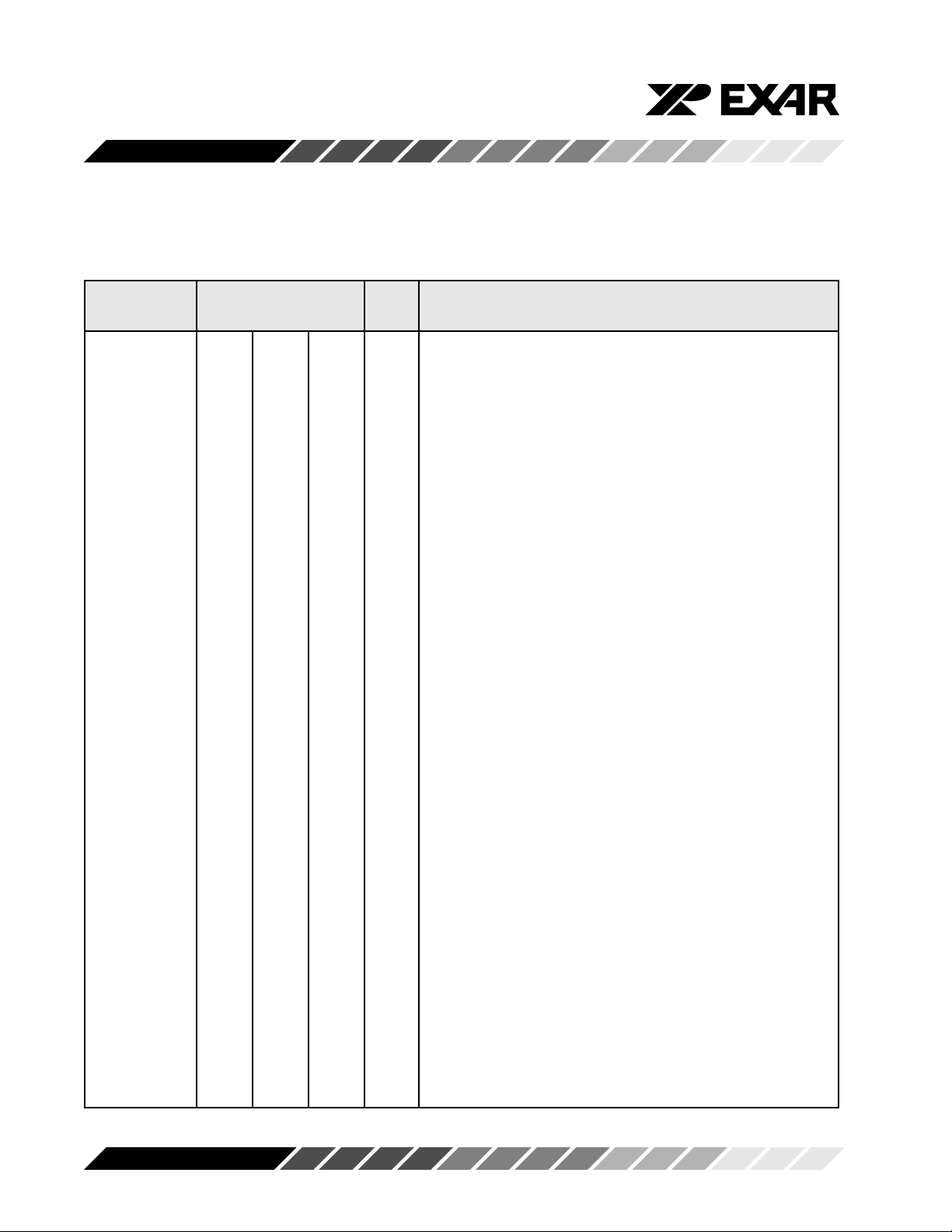

Figure 1, PACKAGE DESCRIPTION, ST16C550

48 Pin TQFP Package 40 Pin DIP Package

N.C.

RCLK

N.C.

CS0

CS1

-CS2

BAUDOUT

N.C.D4D3D2D1D0

4847464544434241403938

1

2

D5

3

D6

4

D7

5

6

7

RX

8

TX

9

10

11

12

1314151617181920212223

N.C.

XTAL1

XTAL2

ST16C550CQ48

-IOW

VCC

-RI

-CD

-DSR-CTSN.C

37

24

N.C.

IOR

-IOR

GND

IOW

-AS

-DDIS

-TXRDY

VCC

1

D0

2

D1

3

RCLK

RX

CS0

CS1

-CS2

BAUDOUT

XTAL1

XTAL2

-IOW

IOW

GND

D2

4

D3

5

D4

6

D5

7

D6

8

D7

9

10

11

TX

12

ST16C550CP40

13

14

15

16

17

18

19

20

N.C.

36

RESET

35

-OP1

34

-DTR

33

-RTS

32

-OP2

31

INT

30

-RXRD

29

A0

28

A1

27

A2

26

N.C.

25

40

-RI

39

-CD

38

-DSR

37

-CTS

36

RESET

35

-OP1

34

-DTR

33

-RTS

32

-OP2

31

INT

30

-RXRD

29

A0

28

A1

27

A2

26

-AS

25

-TXRD

24

-DDIS

23

IOR

22

-IOR

21

Rev. 5.01

2

Page 3

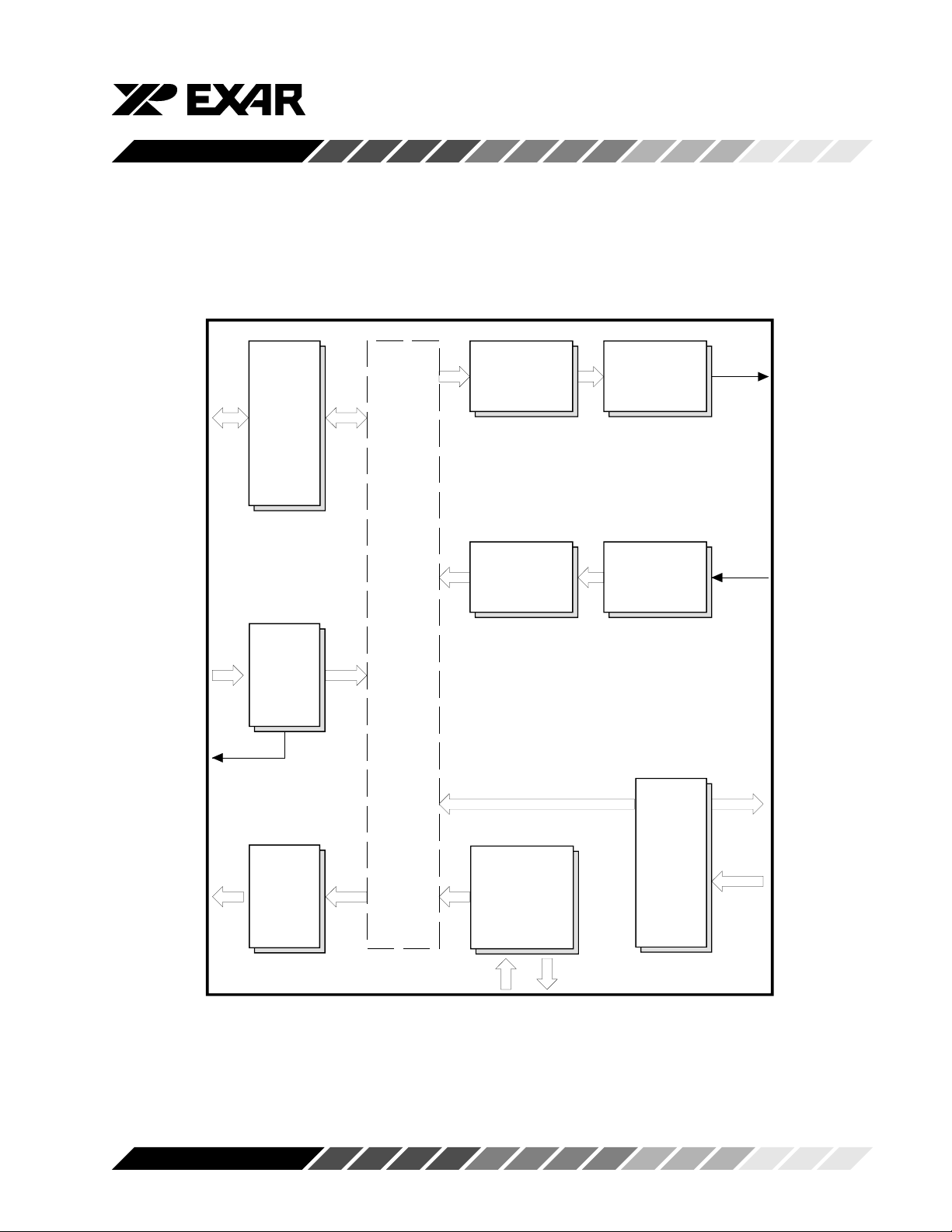

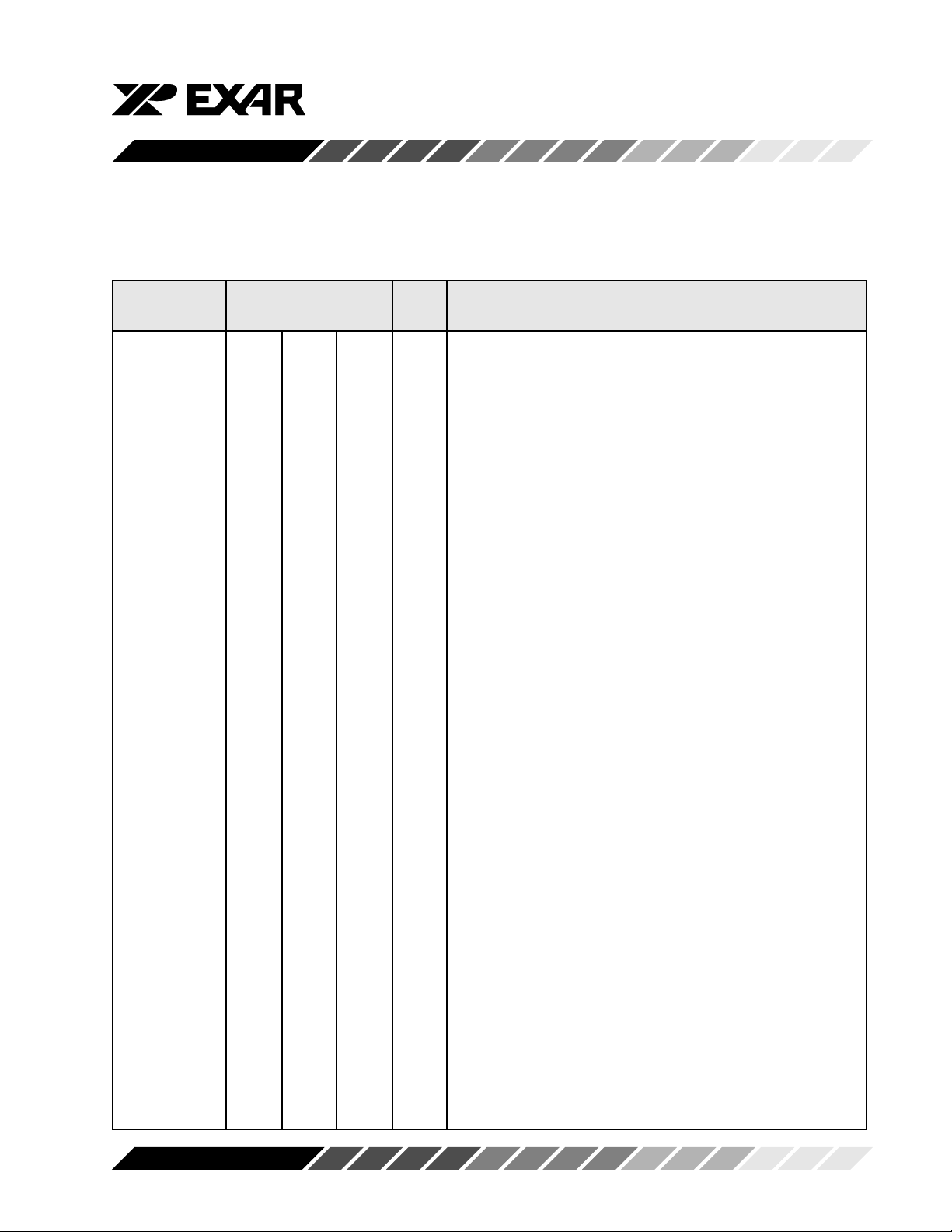

Figure 2, BLOCK DIAGRAM

-

-DTR,-RTS

2

-

ST16C550

Transmit

D0-D7

-IOR,IOR

IOW,IOW

RESET

A0-A2

-AS

CS0,CS1

-CS2

-DDIS

&

Data bus

Control Logic

&

Logic

Select

Register

Control signals

Inter Connec t Bus Li nes

FIFO

Registers

Receive

FIFO

Registers

Transmit

Shift

Register

Receive

Shift

Register

TX

RX

INT

-RXRDY

-TXRDY

Rev. 5.01

-OP1,-OP

Modem

Clock

&

Logic

Control

Interrupt

Baud Rate

Generator

3

RCLK

XTAL1

XTAL2

BAUDOUT

Control

Logic

-CTS

-RI

-CD

-DSR

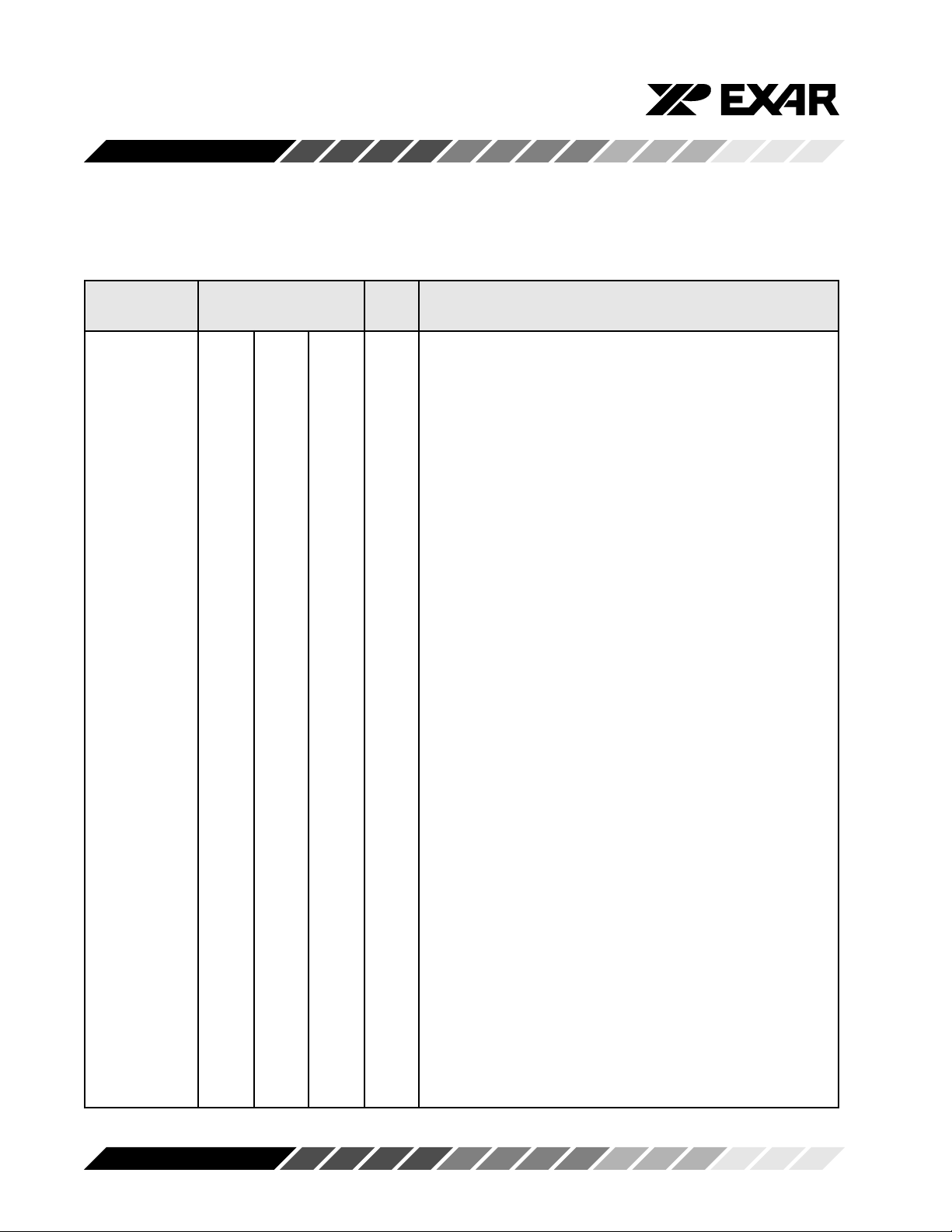

Page 4

ST16C550

SYMBOL DESCRIPTION

Symbol Pin Signal Pin Description

40 44 48 type

A0 28 31 28 I Address-0 Select Bit Internal registers address selection.

A1 27 30 27 I Address-1 Select Bit Internal registers address selection.

A2 26 29 26 I Address-2 Select Bit Internal registers address selection.

IOR 22 25 20 I Read data strobe. Its function is the same as -IOR (see -

IOR), except it is active high. Either an active -IOR or IOR

is required to transfer data from 16C550 to CPU during a

read operation. Connect to logic 0 when using -IOR.

CS0 12 14 9 I Chip Select-0. Logical 1 on this pin provides the chip select-

0 function. Connect CS0 to logic 1 if using CS1 or -CS2.

CS1 13 15 10 I Chip Select-1. Logical 1 on this pin provides the chip select-

1 function. Connect CS1 to logic 1 if using CS0 or -CS2.

-CS2 14 16 11 I Chip Select -2. Logical 0 on this pin provides the chip select2 function. Connect to logic 0 if using CS0 or CS1.

IO W 19 21 17 I Write data strobe. Its function is the same as -IOW (see -

IOW), but it acts as an active high input signal. Either -IOW

or IOW is required to transfer data from the CPU to

ST16C550 during a write operation. Connect to logic 0 when

using -IOW.

-AS 2 5 2 8 2 4 I Address Strobe. A logic 1 transition on -AS latches the state

of the chip selects and the register select bits, A0-A2. This

input is used when address and chip selects are not stable

for the duration of a read or write operation, i.e., a microprocessor that needs to de-multiplex the address and data bits.

If not required, the -AS input can be permanently tied to a

logic 0.

D0-D7 1-8 2-9 43-47

2-4 I/O Data Bus (Bi-directional) - These pins are the eight bit, tri-

state data bus for transferring information to or from the

controlling CPU. D0 is the least significant bit and the first

data bit in a transmit or receive serial data stream.

GN D 2 0 22 18 Pw r Signal and Power Ground.

Rev. 5.01

4

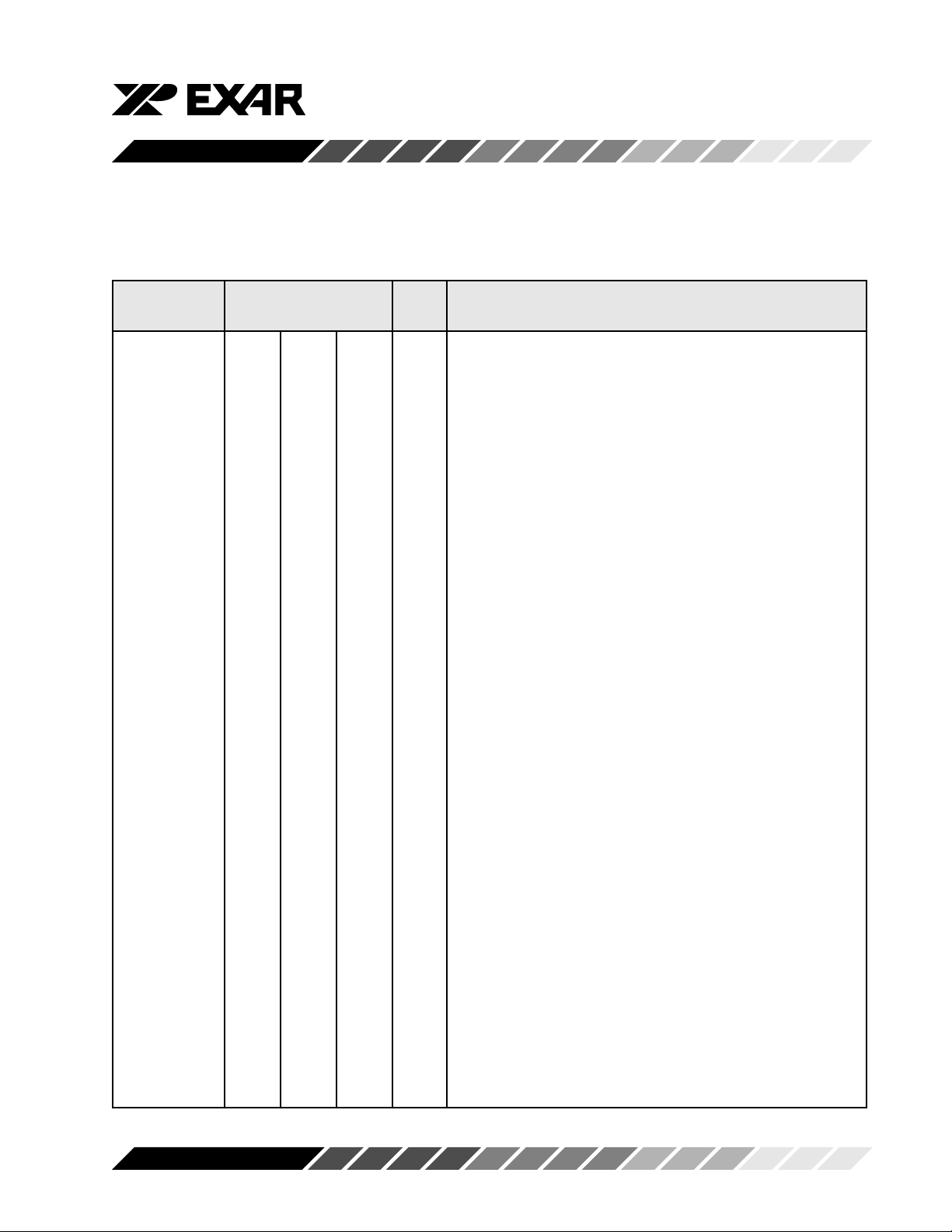

Page 5

ST16C550

SYMBOL DESCRIPTION

Symbol Pin Signal Pin Description

40 44 48 type

-IOR 21 24 19 I Read data strobe (active low strobe). A logic 0 on this pin

transfers the contents of the ST16C550 data bus to the CPU.

Connect to logic 1 when using IOR.

-IOW 18 20 16 I Write data strobe (active low strobe). A logic 0 on this pin

transfers the contents of the CPU data bus to the addressed

internal register. Connect to logic 1 when using IOW.

INT 30 33 30 O Interrupt Request (active high). Interrupts are enabled in the

interrupt enable register (IER), and when an interrupt condition exists. Interrupt conditions include: receiver errors,

available receiver buffer data, transmit buffer empty, or

when a modem status flag is detected.

-RXRDY 29 32 29 O Receive Ready. When operating in the FIFO mode, one of

two types of DMA signaling can be selected using the FIFO

control register bit-3. When operating in the ST16C450

mode, only DMA mode “0” is allowed. Mode “0” supports

single transfer DMA in which a transfer is made between

CPU bus cycles. Mode “1” supports multi-transfer DMA in

which multiple transfers are made continuously until the

receiver FIFO has been emptied. In DMA mode “0” -RXRDY

is low, when there is at least one character in the receiver

FIFO or receive holding register. In DMA mode “1”, -RXRDY

is low, when the trigger level or the time-out has been

reached.

-TXRDY 24 27 23 O Transmit Ready. When operating in the FIFO mode, one of

two types of DMA signaling can be selected using the FIFO

control register bit-3. When operating in the ST16C450

mode, only DMA mode “0” is allowed. Mode “0” supports

single transfer DMA in which a transfer is made between

CPU bus cycles. Mode “1” supports multi-transfer DMA in

which multiple transfers are made continuously until the

transmit FIFO has been filled.

-BAUDOUT 15 17 12 O Baud Rate Generator Output. This pin provides the 16X

clock of the selected data rate from the baud rate generator.

The RCLK pin must be connected externally to -BAUDOUT

when the receiver is operating at the same data rate.

Rev. 5.01

5

Page 6

ST16C550

SYMBOL DESCRIPTION

Symbol Pin Signal Pin Description

40 44 48 type

-DDIS 23 26 22 O Drive Disable. This pin goes to a logic 0 when the external

CPU is reading data from the ST16C550. This signal can be

used to disable external transceivers or other logic functions.

-OP1 34 38 34 O Output-1 (User Defined) - See bit-2 of modem control

register (MCR bit-2).

RESET 35 39 35 I Reset. (active high) - A logic 1 on this pin will reset the

internal registers and all the outputs. The UART transmitter

output and the receiver input will be disabled during reset

time. (See ST16C550 External Reset Conditions for initialization details.)

RCLK 9 10 5 I Receive Clock Input. This pin is used as external 16X clock

input to the receiver section. External connection to Baudout pin is required in order to utilize the internal baud

rate generator.

-OP2 31 35 31 O Output-2 (User Defined). This pin provides the user a

general purpose output. See bit-3 modem control register

(MCR bit-3).

VCC 40 44 42 Pwr Power Supply Input.

XTAL1 16 18 14 I Crystal or External Clock Input - Functions as a crystal input

or as an external clock input. A crystal can be connected

between this pin and XTAL2 to form an internal oscillator

circuit. An external 1 MΩ resistor is required between the

XTAL1 and XTAL2 pins (see figure 3). Alternatively, an

external clock can be connected to this pin to provide

custom data rates (Programming Baud Rate Generator

section).

XTAL2 17 19 15 O Output of the Crystal Oscillator or Buffered Clock - (See also

XTAL1). Crystal oscillator output or buffered clock output.

-CD 38 42 40 I Carrier Detect (active low) - A logic 0 on this pin indicates

that a carrier has been detected by the modem.

Rev. 5.01

6

Page 7

ST16C550

SYMBOL DESCRIPTION

Symbol Pin Signal Pin Description

40 44 48 type

-CTS 36 40 38 I Clear to Send (active low) - A logic 0 on the -CTS pin

indicates the modem or data set is ready to accept transmit

data from the ST16C550. Status can be tested by reading

MSR bit-4. This pin has no effect on the UART’s transmit or

receive operation.

-DSR 37 41 39 I Data Set Ready (active low) - A logic 0 on this pin indicates

the modem or data set is powered-on and is ready for data

exchange with the UART. This pin has no effect on the

UART’s transmit or receive operation.

-DTR 33 37 33 O Data Terminal Ready (active low) - A logic 0 on this pin

indicates that the ST16C550 is powered-on and ready. This

pin can be controlled via the modem control register.

Writing a logic 1 to MCR bit-0 will set the -DTR output to

logic 0, enabling the modem. This pin will be a logic 1 after

writing a logic 0 to MCR bit-0, or after a reset. This pin has

no effect on the UART’s transmit or receive operation.

-RI 39 43 41 I Ring Indicator (active low) - A logic 0 on this pin indicates the

modem has received a ringing signal from the telephone

line. A logic 1 transition on this input pin will generate an

interrupt.

-RTS 32 36 32 O Request to Send (active low) - A logic 0 on the -RTS pin

indicates the transmitter has data ready and waiting to send.

Writing a logic 1 in the modem control register (MCR bit-1)

will set this pin to a logic 0 indicating data is available. After

a reset this pin will be set to a logic 1. This pin has no effect

on the UART’s transmit or receive operation.

RX 10 11 7 I Receive Data - This pin provides the serial receive data

input to the ST16C550. A logic 1 indicates no data or an idle

channel. During the local loop-back mode, the RX input pin is

disabled and TX data is internally connected to the UART RX

Input, internally, see figure 12.

TX 11 13 8 O Transmit Data - This pin provides the serial transmit data

from the ST16C550, the TX signal will be a logic 1 during

reset, idle (no data). During the local loop-back mode, the

TX pin is set to a logic 1 and TX data is internally connected

to the UART RX Input, see figure 12.

Rev. 5.01

7

Page 8

ST16C550

GENERAL DESCRIPTION

The ST16C550 provides serial asynchronous receive

data synchronization, parallel-to-serial and serial-toparallel data conversions for both the transmitter and

receiver sections. These functions are necessary for

converting the serial data stream into parallel data that

is required with digital data systems. Synchronization

for the serial data stream is accomplished by adding

start and stops bits to the transmit data to form a data

character (character orientated protocol). Data integrity is insured by attaching a parity bit to the data

character. The parity bit is checked by the receiver for

any transmission bit errors. The electronic circuitry to

provide all these functions is fairly complex especially

when manufactured on a single integrated silicon

chip. The ST16C550 represents such an integration

with greatly enhanced features. The ST16C550 is

fabricated with an advanced CMOS process.

The ST16C550 is an upward solution that provides 16

bytes of transmit and receive FIFO memory, instead

of 1 byte provided in the 16C450. The ST16C550 is

designed to work with high speed modems and shared

network environments, that require fast data processing time. Increased performance is realized in the

ST16C550 by the larger transmit and receive FIFO’s.

This allows the external processor to handle more

networking tasks within a given time. The 4 selectable

levels of FIFO trigger provided for maximum data

throughput performance especially when operating in

a multi-channel environment. The combination of the

above greatly reduces the bandwidth requirement of

the external controlling CPU, increases performance,

and reduces power consumption.

FUNCTIONAL DESCRIPTIONS

Internal Registers

The ST16C550 provides 12 internal registers for

monitoring and control. These registers are shown in

Table 3 below. These registers function as data holding registers (THR/RHR), interrupt status and control

registers (IER/ISR), a FIFO control register (FCR),

line status and control registers, (LCR/LSR), modem

status and control registers (MCR/MSR), programmable data rate (clock) control registers (DLL/DLM),

and a user assessable scratchpad register (SPR).

The ST16C550 is capable of operation to 1.5Mbps

with a 24 MHz crystal or external clock input.

With a crystal of 14.7464 MHz and through a software

option, the user can select data rates up to 460.8Kbps

or 921.6Kbps.

Rev. 5.01

8

Page 9

ST16C550

9

Page 10

ST16C550

ample: T = [(programmed word length = 7) + (stop bit

= 1) + (start bit = 1) = 9]. 40 (bit times divided by 9) =

4.4 characters.

Example -B: If the user programs the word length = 7,

with parity and one stop bit, the time out will be:

T = 4 X 7(programmed word length) + 12 = 40 bit times.

Character time = 40 / 10 [ (programmed word length

= 7) + (parity = 1) + (stop bit = 1) + (start bit = 1) = 4

characters.

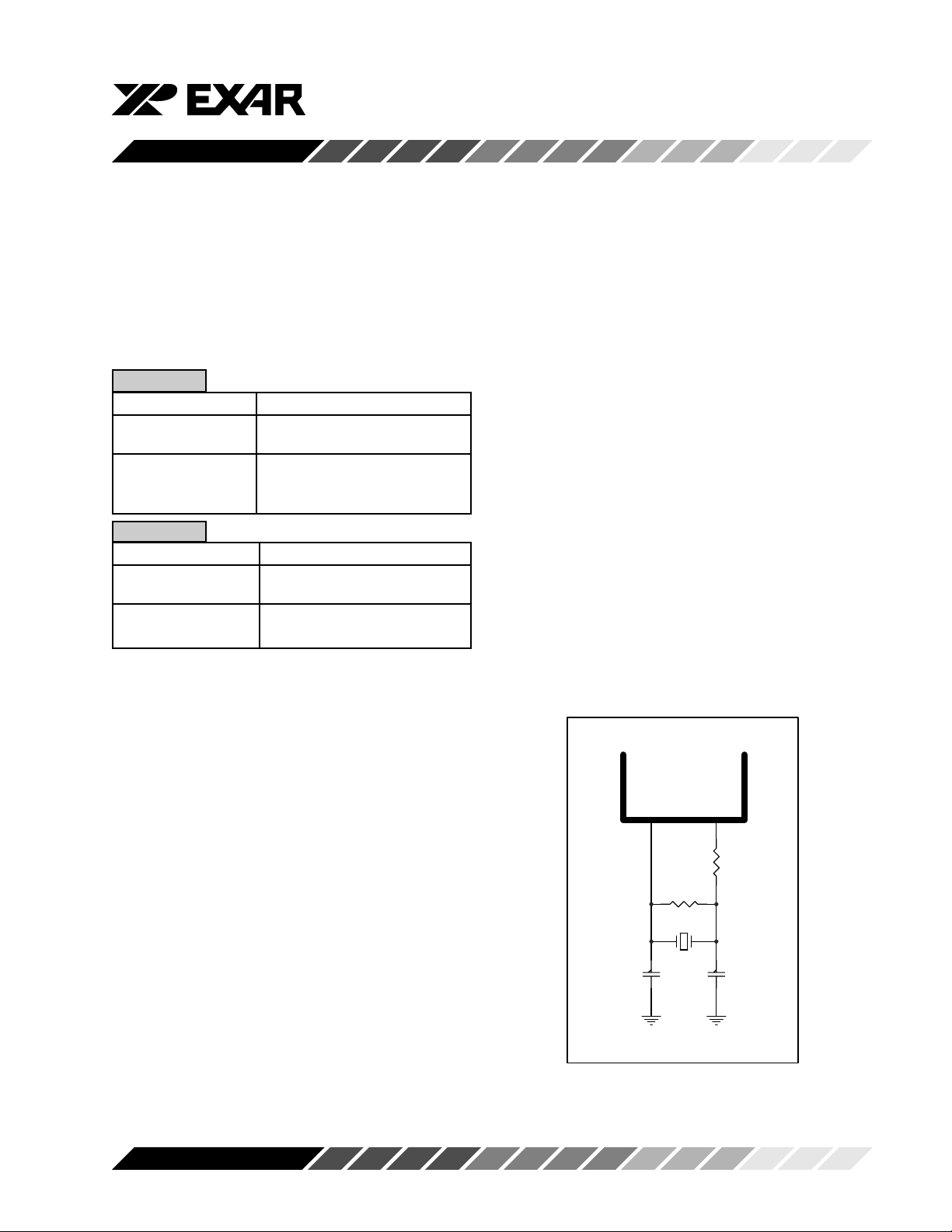

Programmable Baud Rate Generator

The ST16C550 supports high speed modem technologies that have increased input data rates by

employing data compression schemes. For example

a 33.6Kbps modem that employs data compression

may require a 115.2Kbps input data rate. A 128.0Kbps

ISDN modem that supports data compression may

need an input data rate of 460.8Kbps. The ST16C550

can support a standard data rate of 921.6Kbps.

The programmable Baud Rate Generator is capable

of accepting an input clock up to 24 MHz, as required

for supporting a 1.5Mbps data rate. The ST16C550 can

be configured for internal or external clock operation.

For internal clock oscillator operation, an industry

standard microprocessor crystal (parallel resonant/

22 pF load) is connected externally between the

XTAL1 and XTAL2 pins, with an external 1 MΩ resistor

across it. Alternatively, an external clock can be

connected to the XTAL1 pin to clock the internal baud

rate generator for standard or custom rates. See

figure 3 for crystal oscillator connection.

The generator divides the input 16X clock by any

divisor from 1 to 216 -1. The ST16C550 divides the

basic crystal or external clock by 16. The frequency of

the -BAUDOUT output pin is exactly 16X (16 times) of

the selected baud rate (-BAUDOUT =16 x Baud Rate).

Customized Baud Rates can be achieved by selecting

the proper divisor values for the MSB and LSB sections of baud rate generator.

Programming the Baud Rate Generator Registers

DLM (MSB) and DLL (LSB) provides a user capability

for selecting the desired final baud rate. The example

in Table 3 below shows selectable baud rates when

using a 1.8432 MHz crystal.

For custom baud rates, the divisor value can be calculated using the following equation:

Divisor (in decimal) = (XTAL1 clock frequency) / (serial data rate x 16)

Table 3, BAUD RATE GENERATOR PROGRAMMING TABLE (1.8432 MHz CLOCK):

Output User User DLM DLL

Baud Rate 16 x Clock 16 x Clock Program Program

Divisor Divisor Value Value

(Decimal) (HEX) (HEX) (HEX)

50 2304 900 09 00

75 1536 600 06 00

150 768 300 03 00

300 384 180 01 80

600 192 C0 00 C0

1200 96 60 00 60

2400 48 30 00 30

4800 24 18 00 18

7200 16 10 00 10

9600 12 0C 00 0C

19.2k 6 0 6 00 06

38.4k 3 0 3 00 03

57.6k 2 0 2 00 02

115.2k 1 01 0 0 01

Rev. 5.01

10

Page 11

ST16C550

DMA Operation

The ST16C550 FIFO trigger level provides additional

flexibility to the user for block mode operation. The user

can optionally operate the transmit and receive FIFO’s

in the DMA mode (FCR bit-3). The DMA mode affects

the state of the -RXRDY and -TXRDY output pins. The

following tables show this:

-RXRDY pin:

Non-DMA mode DMA mode

1 = FIFO empty 0 to 1 transition when FIFO

empties

0 = at least 1 byte 1 to 0 transition when FIFO

in FIFO reaches trigger level, or

timeout occurs

-TXRDY pin:

Non-DMA mode DMA mode

1 = at least 1 byte 1 = FIFO is full

in FIFO

0 = FIFO empty 0 = FIFO has at least 1

empty location

Loop-back Mode

D0-D7. The user optionally compares the received

data to the initial transmitted data for verifying error

free operation of the UART TX/RX circuits.

In this mode , the receiver and transmitter interrupts are

fully operational. The Modem Control Interrupts are also

operational. The interrupts are still controlled by the

IER.

Figure 3, TYPICAL EXTERNAL CRYSTAL OSCILLATOR CONNECTION

The internal loop-back capability allows onboard diagnostics. In the loop-back mode the normal modem

interface pins are disconnected and reconfigured for

loop-back internally. In this mode MSR bits 4-7 are

also disconnected. However, MCR register bits 0-3

can be used for controlling loop-back diagnostic testing. In the loop-back mode -OP1 and -OP2 in the MCR

register (bits 0-1) control the modem -RI and -CD

inputs respectively. MCR signals -DTR and -RTS (bits

0-1) are used to control the modem -CTS and -DSR

inputs respectively. The transmitter output (TX) and the

receiver input (RX) are disconnected from their associated interface pins, and instead are connected together

internally (See Figure 4). The -CTS, -DSR, -CD, and -RI

are disconnected from their normal modem control

inputs pins, and instead are connected internally to DTR, -RTS, -OP1 and -OP2. Loop-back test data is

entered into the transmit holding register via the user

data bus interface, D0-D7. The transmit UART serializes the data and passes the serial data to the receive

UART via the internal loop-back connection. The receive

UART converts the serial data back into parallel data

that is then made available at the user data interface,

Rev. 5.01

XTAL1 XTAL2

R2

1M

Y1

C1

22-47pF

R1

0-120

(Optional)

1.8432 - 24 MHz

C2

22-47pF

11

Page 12

ST16C550

-

Figure 4, INTERNAL LOOP-BACK MODE DIAGRAM

Transmit

FIFO

D0-D7

-IOR,IOR

IOW,IOW

RESET

A0-A2

-AS

CS0,CS1

-CS2

Data bus

Register

&

Select

Control Logic

Logic

&

Control signals

Inter Connect Bus Lines

Registers

Receive

FIFO

Registers

Transmit

Shift

Register

Receive

Shift

Register

TX

MCR Bit-4=1

RX

-RTS

-CTS

-TXRDY

-RXRDY

Rev. 5.01

INT

-DTR

Logic

Control

Interrupt

-DSR

-OP1

Clock

&

Baud Rate

Generator

RCLK

XTAL1

12

Modem Control Logic

XTAL2

-RI

-OP2

-CD

Page 13

ST16C550

REGISTER FUNCTIONAL DESCRIPTIONS

The following table delineates the assigned bit functions for the twelve ST16C550 internal registers. The assigned

bit functions are more fully defined in the following paragraphs.

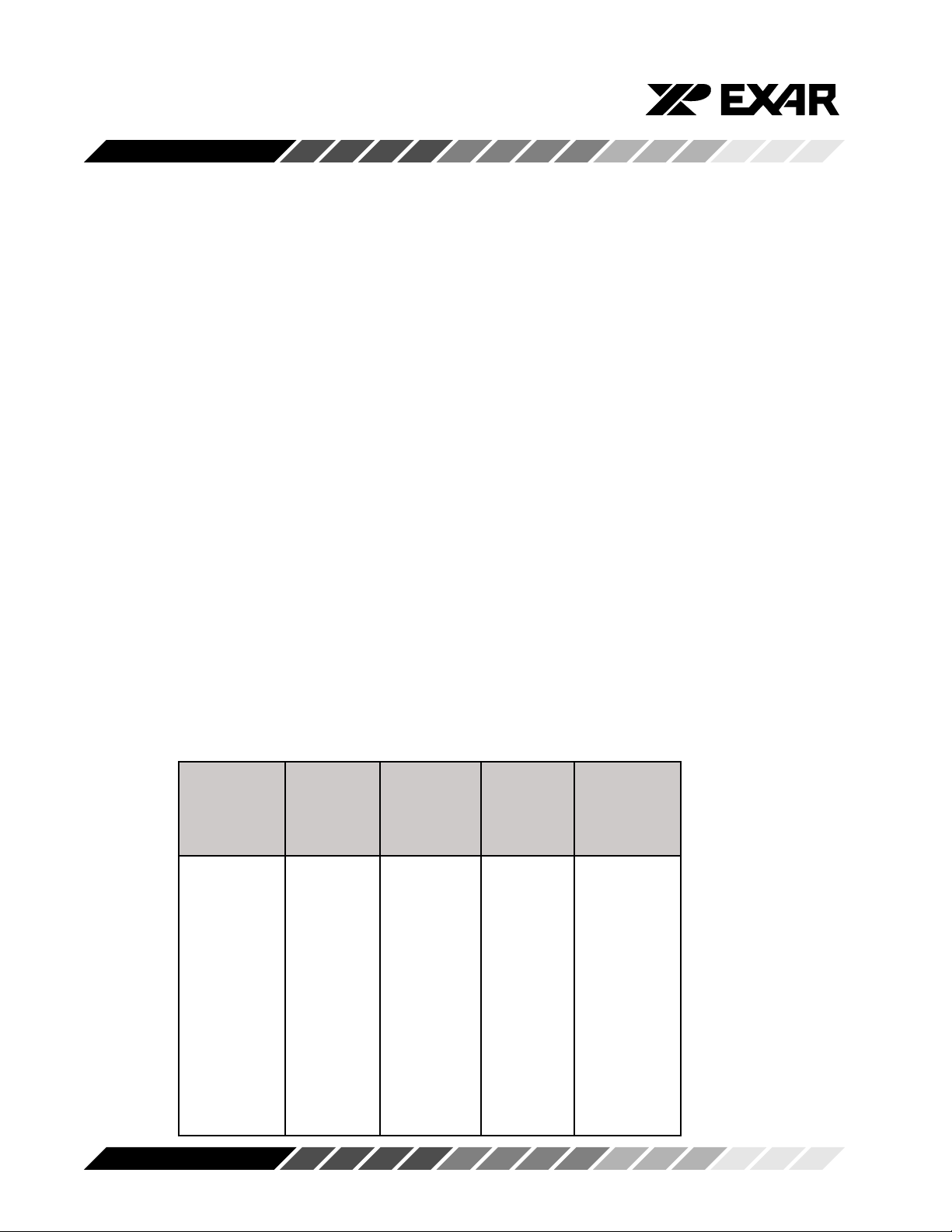

Table 4, ST16C550 INTERNAL REGISTERS

A2 A1 A0 Register BIT-7 BIT-6 BIT-5 BIT-4 BIT-3 BIT-2 BIT-1 BIT-0

[Default]

Note *2

General Register Set

0 0 0 RHR [XX] bit-7 bit-6 bit-5 bit-4 bit-3 bit-2 bit-1 bit-0

0 0 0 THR [XX] bit-7 bit-6 bit-5 bit-4 bit-3 bit-2 bit-1 bit-0

0 0 1 IER [00] 0000modem receive transmit receive

0 1 0 FCR [00] RCVR RCVR 0 0 DMA XMIT RCVR FIFO

trigger trigger mode FIFO FIFO enable

(MSB) (LSB) select reset reset

0 1 0 ISR [01] FIFO’s FIFO’s 0 0 INT INT INT INT

enabled enabled priority priority priority status

0 1 1 LCR [00] divisor set set even parity stop word word

latch break parity parity enable bits length length

enable bit-1 bit-0

1 0 0 MCR [00] 0 0 0 loopback -OP2 -OP1 -RTS -DTR

enable

status line holding holding

interrupt status register register

interrupt

bit-2 bit-1 bit-0

1 0 1 LSR [60] FIFO trans. trans. break framing parity overrun receive

1 1 0 MSR [X0] CD RI DSR CTS delta delta delta delta

1 1 1 SPR [FF] bit-7 bit-6 bit-5 bit-4 bit-3 bit-2 bit-1 bit-0

data empty holding interrupt error error error data

error empt y ready

-CD -RI -DSR -CTS

Baud Rate Generator Divisor Registers. Accessible when LCR bit-7 is set to logic 1. Note 1*

0 0 0 DLL [XX] bit-7 bit-6 bit-5 bit-4 bit-3 bit-2 bit-1 bit-0

0 0 1 DLM [XX] bit-15 bit-14 bit-13 bit-12 bit-11 bit-10 bit-9 bit-8

Note *1: The BRG registers are accessible only when LCR bit-7 is set to a logic 1.

Note *2: The value represents the register’s initialized HEX value. An “X” signifies a 4-bit un-initialized nibble.

Rev. 5.01

13

Page 14

ST16C550

Transmit and Receive Holding Register

The serial transmitter section consists of an 8-bit

Transmit Hold Register (THR) and Transmit Shift

Register (TSR). The status of the THR is provided in

the Line Status Register (LSR). Writing to the THR

transfers the contents of the data bus (D7-D0) to the

THR, providing that the THR or TSR is empty. The

THR empty flag in the LSR register will be set to a logic

1 when the transmitter is empty or when data is

transferred to the TSR. Note that a write operation can

be performed when the transmit holding register

empty flag is set (logic 0 = at least one byte in FIFO /

THR, logic 1= FIFO/THR empty).

The serial receive section also contains an 8-bit

Receive Holding Register, RHR. Receive data is

removed from the ST16C550 and receive FIFO by

reading the RHR register. The receive section provides a mechanism to prevent false starts. On the

falling edge of a start or false start bit, an internal

receiver counter starts counting clocks at 16x clock

rate. After 7 1/2 clocks the start bit time should be

shifted to the center of the start bit. At this time the start

bit is sampled and if it is still a logic 0 it is validated.

Evaluating the start bit in this manner prevents the

receiver from assembling a false character. Receiver

status codes will be posted in the LSR.

B) FIFO status will also be reflected in the user

accessible ISR register when the FIFO trigger level is

reached. Both the ISR register status bit and the

interrupt will be cleared when the FIFO drops below

the trigger level.

C) The data ready bit (LSR BIT-0) is set as soon as a

character is transferred from the shift register to the

receive FIFO. It is reset when the FIFO is empty.

IER Vs Receive/Transmit FIFO Polled Mode Operation

When FCR BIT-0 equals a logic 1; resetting IER bits

0-3 enables the ST16C550 in the FIFO polled mode of

operation. Since the receiver and transmitter have

separate bits in the LSR either or both can be used in

the polled mode by selecting respective transmit or

receive control bit(s).

A) LSR BIT-0 will be a logic 1 as long as there is one

byte in the receive FIFO.

B) LSR BIT 1-4 will indicate if an overrun error

occurred.

C) LSR BIT-5 will indicate when the transmit FIFO is

empty.

Interrupt Enable Register (IER)

The Interrupt Enable Register (IER) masks the interrupts from receiver ready, transmitter empty, line

status and modem status registers. These interrupts

would normally be seen on the ST16C550 INT output

pin.

IER Vs Receive FIFO Interrupt Mode Operation

When the receive FIFO (FCR BIT-0 = a logic 1) and

receive interrupts (IER BIT-0 = logic 1) are enabled,

the receive interrupts and register status will reflect

the following:

A) The receive data available interrupts are issued to

the external CPU when the FIFO has reached the

programmed trigger level. It will be cleared when the

FIFO drops below the programmed trigger level.

Rev. 5.01

D) LSR BIT-6 will indicate when both the transmit

FIFO and transmit shift register are empty.

E) LSR BIT-7 will indicate any FIFO data errors.

IER BIT-0:

Logic 0 = Disable the receiver ready interrupt. (normal

default condition)

Logic 1 = Enable the receiver ready interrupt.

IER BIT-1:

Logic 0 = Disable the transmitter empty interrupt.

(normal default condition)

Logic 1 = Enable the transmitter empty interrupt.

IER BIT-2:

Logic 0 = Disable the receiver line status interrupt.

(normal default condition)

Logic 1 = Enable the receiver line status interrupt.

14

Page 15

ST16C550

IER BIT-3:

Logic 0 = Disable the modem status register interrupt.

(normal default condition)

Logic 1 = Enable the modem status register interrupt.

IER BIT 4-7: Not used and set to “0”.

FIFO Control Register (FCR)

This register is used to enable the FIFO’s, clear the

FIFO’s, set the transmit/receive FIFO trigger levels,

and select the DMA mode. The DMA, and FIFO

modes are defined as follows:

DMA MODE:

See description and DMA tables on page 11.

FCR BIT-0:

Logic 0 = Disable the transmit and receive FIFO.

(normal default condition)

Logic 1 = Enable the transmit and receive FIFO. This

bit must be a “1” when other FCR bits are written to or

they will not be programmed.

FCR BIT-1:

Logic 0 = No FIFO receive reset. (normal default

condition)

Logic 1 = Clears the contents of the receive FIFO and

resets the FIFO counter logic (the receive shift register is not cleared or altered). This bit will return to a

logic 0 after clearing the FIFO.

3 = logic 0) and when there are no characters in the

transmit FIFO or transmit holding register, the TXRDY pin will be a logic 0. Once active the -TXRDY

pin will go to a logic 1 after the first character is loaded

into the transmit holding register.

Receive operation in mode “0”:

When the ST16C550 is in mode “0” (FCR bit-0 = logic

0) or in the FIFO mode (FCR bit-0 = logic 1, FCR bit3 = logic 0) and there is at least one character in the

receive FIFO, the -RXRDY pin will be a logic 0. Once

active the -RXRDY pin will go to a logic 1 when there

are no more characters in the receiver.

Transmit operation in mode “1”:

When the ST16C550 is in FIFO mode ( FCR bit-0 =

logic 1, FCR bit-3 = logic 1 ), the -TXRDY pin will be

a logic 1 when the transmit FIFO is completely full. It

will be a logic 0 if one or more FIFO locations are

empty.

Receive operation in mode “1”:

When the ST16C550 is in FIFO mode (FCR bit-0 =

logic 1, FCR bit-3 = logic 1) and the trigger level has

been reached, or a Receive Time Out has occurred,

the -RXRDY pin will go to a logic 0. Once activated, it

will go to a logic 1 after there are no more characters

in the FIFO.

FCR BIT 4-5: Not used.

FCR BIT-2:

Logic 0 = No FIFO transmit reset. (normal default

condition)

Logic 1 = Clears the contents of the transmit FIFO and

resets the FIFO counter logic (the transmit shift register is not cleared or altered). This bit will return to a

logic 0 after clearing the FIFO.

FCR BIT-3:

Logic 0 = Set DMA mode “0”. (normal default condition)

Logic 1 = Set DMA mode “1.”

Transmit operation in mode “0”:

When the ST16C550 is in the ST16C450 mode

(FIFO’s disabled, FCR bit-0 = logic 0) or in the FIFO

mode (FIFO’s enabled, FCR bit-0 = logic 1, FCR bit-

Rev. 5.01

FCR BIT 6-7: These bits are used to set the trigger level

for the receive FIFO interrupt.

An interrupt is generated when the number of characters

in the FIFO equals the programmed trigger level. However the FIFO will continue to be loaded until it is full.

BIT-7 BIT-6 R X F I F O t r i g g e r l e v e l

00 1

01 4

10 8

11 14

15

Page 16

ST16C550

Interrupt Status Register (ISR)

The ST16C550 provides four levels of prioritized interrupts to minimize external software interaction. The

Interrupt Status Register (ISR) provides the user with six

interrupt status bits. Performing a read cycle on the ISR

will provide the user with the highest pending interrupt

level to be serviced. No other interrupts are acknowledged until the pending interrupt is serviced. Whenever

the interrupt status register is read, the interrupt status

is cleared. However it should be noted that only the

current pending interrupt is cleared by the read. A lower

level interrupt may be seen after rereading the interrupt

status bits. The Interrupt Source Table 5 (below) shows

the data values (bit 0-3) for the four prioritized interrupt

levels and the interrupt sources associated with each

of these interrupt levels:

Table 5, INTERRUPT SOURCE TABLE

Priority [ISR]

Level Bit-3 Bit-2 Bit-1 Bit-0 Source of the interrupt

X 0001No interrupt pending

1 0110LSR (Receiver Line Status Register)

2 0100RXRDY (Received Data Ready)

2 1100RXRDY (Receive Data time out)

3 0010TXRDY ( Transmitter Holding Register Empty)

4 0000MSR (Modem Status Register)

Rev. 5.01

16

Page 17

ISR BIT-0:

Logic 0 = An interrupt is pending and the ISR contents

may be used as a pointer to the appropriate interrupt

service routine.

Logic 1 = No interrupt pending. (normal default condition)

ISR BIT 1-3: (logic 0 or cleared is the default condition)

These bits indicate the source for a pending interrupt at

interrupt priority levels 1, 2, and 3 (See Interrupt Source

Table).

ISR BIT 4-5: Not used and set to “0”.

ISR BIT 6-7: (logic 0 or cleared is the default condition)

These bits are set to a logic 0 when the FIFO is not being

used. They are set to a logic 1 when the FIFO’s are

enabled

Line Control Register (LCR)

The Line Control Register is used to specify the

asynchronous data communication format. The word

length, the number of stop bits, and the parity are

selected by writing the appropriate bits in this register.

LCR BIT 0-1: (logic 0 or cleared is the default condition)

These two bits specify the word length to be transmitted or received.

BIT-1 BIT-0 Word length

00 5

01 6

10 7

11 8

ST16C550

BIT-2 Word length Stop bit

length

(Bit time(s))

0 5,6,7,8 1

1 5 1-1/2

1 6,7,8 2

LCR BIT-3:

Parity or no parity can be selected via this bit.

Logic 0 = No parity (normal default condition)

Logic 1 = A parity bit is generated during the transmission, receiver checks the data and parity for transmission errors.

LCR BIT-4:

If the parity bit is enabled with LCR bit-3 set to a logic

1, LCR BIT-4 selects the even or odd parity format.

Logic 0 = ODD Parity is generated by forcing an odd

number of logic 1’s in the transmitted data. The

receiver must be programmed to check the same

format. (normal default condition)

Logic 1 = EVEN Parity is generated by forcing an even

the number of logic 1’s in the transmitted. The receiver

must be programmed to check the same format.

LCR BIT-5:

If the parity bit is enabled, LCR BIT-5 selects the

forced parity format.

LCR BIT-5 = logic 0, parity is not forced (normal

default condition)

LCR BIT-5 = logic 1 and LCR BIT-4 = logic 0, parity bit

is forced to a logical 1 for the transmit and receive

data.

LCR BIT-5 = logic 1 and LCR BIT-4 = logic 1, parity bit

is forced to a logical 0 for the transmit and receive

data.

LCR BIT-2: (logic 0 or cleared is the default condition)

The length of stop bit is specified by this bit in

conjunction with the programmed word length.

Rev. 5.01

LCR LCR LCR Parity selection

Bit-5 Bit-4 Bit-3

X X 0 No parity

0 0 1 Odd parity

0 1 1 Even parity

1 0 1 Force parity “1”

1 1 1 Forced “0”

17

Page 18

ST16C550

LCR BIT-6:

When enabled the Break control bit causes a break

condition to be transmitted (the TX output is forced to a

logic 0 state). This condition exists until disabled by

setting LCR bit-6 to a logic 0.

Logic 0 = No TX break condition. (normal default

condition)

Logic 1 = Forces the transmitter output (TX) to a logic

0 for alerting the remote receiver to a line break

condition.

LCR BIT-7:

The internal baud rate counter latch and Enhance

Feature mode enable.

Logic 0 = Divisor latch disabled. (normal default condition)

Logic 1 = Divisor latch and enhanced feature register

enabled.

Modem Control Register (MCR)

This register controls the interface with the modem or

a peripheral device.

MCR BIT-0:

Logic 0 = Force -DTR output to a logic 1. (normal

default condition)

Logic 1 = Force -DTR output to a logic 0.

MCR BIT-1:

Logic 0 = Force -RTS output to a logic 1. (normal

default condition)

Logic 1 = Force -RTS output to a logic 0.

MCR BIT-2:

Logic 0 = Set -OP1 output to a logic 1. (normal default

condition)

Logic 1 = Set -OP1 output to a logic 0.

MCR BIT-3:

Logic 0 = Set -OP2 output to a logic 1. (normal default

condition)

Logic 1 = Set -OP2 output to a logic 0.

MCR BIT-4:

Logic 0 = Disable loop-back mode. (normal default

condition)

Logic 1 = Enable local loop-back mode (diagnostics).

MCR BIT 5-7: Not used and set to “0”.

Line Status Register (LSR)

This register provides the status of data transfers

between. the ST16C550 and the CPU.

LSR BIT-0:

Logic 0 = No data in receive holding register or FIFO.

(normal default condition)

Logic 1 = Data has been received and is saved in the

receive holding register or FIFO.

LSR BIT-1:

Logic 0 = No overrun error. (normal default condition)

Logic 1 = Overrun error. A data overrun error occurred

in the receive shift register. This happens when additional data arrives while the FIFO is full. In this case

the previous data in the shift register is overwritten.

Note that under this condition the data byte in the

receive shift register is not transfer into the FIFO,

therefore the data in the FIFO is not corrupted by the

error.

LSR BIT-2:

Logic 0 = No parity error (normal default condition)

Logic 1 = Parity error. The receive character does not

have correct parity information and is suspect. In the

FIFO mode, this error is associated with the character

at the top of the FIFO.

LSR BIT-3:

Logic 0 = No framing error (normal default condition).

Logic 1 = Framing error. The receive character did not

have a valid stop bit(s). In the FIFO mode this error is

associated with the character at the top of the FIFO.

LSR BIT-4:

Logic 0 = No break condition (normal default condition)

Logic 1 = The receiver received a break signal (RX

was a logic 0 for one character frame time). In the

FIFO mode, only one break character is loaded into

the FIFO.

LSR BIT-5:

This bit is the Transmit Holding Register Empty indicator. This bit indicates that the UART is ready to

accept a new character for transmission. In addition,

Rev. 5.01

18

Page 19

this bit causes the UART to issue an interrupt to CPU

when the THR interrupt enable is set. The THR bit is

set to a logic 1 when a character is transferred from

the transmit holding register into the transmitter shift

register. The bit is reset to logic 0 concurrently with

the loading of the transmitter holding register by the

CPU. In the FIFO mode this bit is set when the transmit

FIFO is empty; it is cleared when at least 1 byte is

written to the transmit FIFO.

LSR BIT-6:

This bit is the Transmit Empty indicator. This bit is set

to a logic 1 whenever the transmit holding register and

the transmit shift register are both empty. It is reset to

logic 0 whenever either the THR or TSR contains a

data character. In the FIFO mode this bit is set to one

whenever the transmit FIFO and transmit shift register

are both empty.

LSR BIT-7:

Logic 0 = No Error (normal default condition)

Logic 1 = At least one parity error, framing error or

break indication is in the current FIFO data. This bit is

cleared when there are no remaining LSR errors in the

RX FIFO.

Modem Status Register (MSR)

ST16C550

MSR BIT-2:

Logic 0 = No -RI Change (normal default condition)

Logic 1 = The -RI input to the ST16C550 has changed

from a logic 0 to a logic 1. A modem Status Interrupt

will be generated.

MSR BIT-3:

Logic 0 = No -CD Change (normal default condition)

Logic 1 = Indicates that the -CD input to the has

changed state since the last time it was read. A

modem Status Interrupt will be generated.

MSR BIT-4:

CTS (active high, logical 1). Normally this bit is the

compliment of the -CTS input. In the loop-back mode,

this bit is equivalent to the RTS bit in the MCR register.

MSR BIT-5:

DSR (active high, logical 1). Normally this bit is the

compliment of the -DSR input. In the loop-back mode,

this bit is equivalent to the DTR bit in the MCR register.

MSR BIT-6:

RI (active high, logical 1). Normally this bit is the

compliment of the -RI input. In the loop-back mode

this bit is equivalent to the OP1 bit in the MCR register.

This register provides the current state of the control

interface signals from the modem, or other peripheral

device that the ST16C550 is connected to. Four bits

of this register are used to indicate the changed

information. These bits are set to a logic 1 whenever

a control input from the modem changes state. These

bits are set to a logic 0 whenever the CPU reads this

register.

MSR BIT-0:

Logic 0 = No -CTS Change (normal default condition)

Logic 1 = The -CTS input to the ST16C550 has

changed state since the last time it was read. A

modem Status Interrupt will be generated.

MSR BIT-1:

Logic 0 = No -DSR Change (normal default condition)

Logic 1 = The -DSR input to the ST16C550 has

changed state since the last time it was read. A

modem Status Interrupt will be generated.

Rev. 5.01

MSR BIT-7:

CD (active high, logical 1). Normally this bit is the

compliment of the -CD input. In the loop-back mode

this bit is equivalent to the OP2 bit in the MCR register.

Scratchpad Register (SPR)

The ST16C550 provides a temporary data register to

store 8 bits of user information.

19

Page 20

ST16C550

ST16C550 EXTERNAL RESET CONDITIONS

REGISTERS RESET STATE

IE R IER BITS 0-7 = logic 0

ISR ISR BIT-0=1, ISR BITS 1-7 = logic

0

LCR, MCR BITS 0-7 = logic 0

LSR LSR BITS 0-4 = logic 0,

LSR BITS 5-6 = logic 1 LSR, BIT

7 = logic 0

MSR MSR BITS 0-3 = logic 0,

MSR BITS 4-7 = logic levels of the

input signals

FCR BITS 0-7 = logic 0

SIGNALS RESET STATE

TX Logic 1

-OP1 Logic 1

-OP2 Logic 1

-RTS Logic 1

-DTR Logic 1

-RXRDY Logic 1

-TXRDY Logic 0

I N T Logic 0

Rev. 5.01

20

Page 21

ST16C550

AC ELECTRICAL CHARACTERISTICS

TA=0° - 70°C (-40° - +85°C for Industrial grade packages), Vcc=3.3 - 5.0 V ± 10% unless otherwise specified.

Symbol Parameter Limits Limits Units Conditions

3.3 5.0

Min Max Min Max

T1w,T

2w

T

3w

T4w Address strobe width 3 5 2 5 ns

T5s Address setup time 5 0 ns

T5h Address hold time 5 5 ns

T

6s

T6h Chip select hold time 0 0 ns

T

6s'

T

7d

T

7w

T

7w'

T

7h

T

7h'

T

8d

T

9d

T

11d

T

12d

T

12h

T

13d

T

13w

T

13w'

T

13h

T

14d

T

15d

T

16s

T

16h

T

17d

T

18d

T

19d

T

20d

T

21d

T

22d

T

23d

T

24d

T

25d

T

26d

T

27d

T

28d

T

R

N Baud rate divisor 1 216-1 1 216-1 Rclk

Clock pulse duration 17 17 ns

Oscillator/Clock frequency 16 24 MHz

Chip select setup time 5 0 ns

Address setup time 10 5 ns see Note 1

-IOR delay from chip select 10 10 ns

-IOR strobe width 77 38 ns

Chip select width 77 38 ns

Chip select hold time from -IOR 0 0 ns

Address hold time 5 5 ns see Note 1

-IOR delay from address 10 10 ns

Read cycle delay 77 38 ns

-IOR to -DDIS delay 1 5 10 ns 100 pF load

Delay from -IOR to data 3 5 25 ns

Data disable time 2 5 15 ns

-IOW delay from chip select 1 0 10 ns

-IOW strobe width 27 15 ns

Chip select width 77 38 ns

Chip select hold time from -IOW 0 0 ns

-IOW delay from address 10 10 ns

Write cycle delay 77 38 ns

Data setup time 20 15 ns

Data hold time 5 5 ns

Delay from -IOW to output 5 0 40 ns 100 pF load

Delay to set interrupt from MODEM input 4 0 3 5 ns 100 pF load

Delay to reset interrupt from -IOR 4 0 35 ns 100 pF load

Delay from stop to set interrupt 1 1 Rclk

Delay from -IOR to reset interrupt 4 5 40 ns 100 pF load

Delay from stop to interrupt 4 5 40 ns

Delay from initial INT reset to transmit 8 24 8 2 4 Rclk

start

Delay from -IOW to reset interrupt 4 5 40 ns

Delay from stop to set -RxRdy 1 1 Rclk

Delay from -IOR to reset -RxRdy 4 5 40 ns

Delay from -IOW to set -TxRdy 4 5 40 ns

Delay from start to reset -TxRdy 8 8 Rclk

Reset pulse width 40 40 ns

Note 1: Applicable only when -AS is tied low.

Rev. 5.01

21

Page 22

ST16C550

ABSOLUTE MAXIMUM RATINGS

Supply range 7 Volts

Voltage at any pin GND - 0.3 V to VCC +0.3 V

Operating temperature -40° C to +85° C

Storage temperature -65° C to 150° C

Package dissipation 500 mW

DC ELECTRICAL CHARACTERISTICS

TA=0° - 70°C (-40° - +85°C for Industrial grade packages), Vcc=3.3 - 5.0 V ± 10% unless otherwise specified.

Symbol Parameter Limits Limits Units Conditions

3.3 5.0

Min Max Min Max

V

ILCK

V

IHCK

V

IL

V

IH

V

OL

V

OL

V

OH

V

OH

I

IL

I

CL

I

CC

C

P

Clock input low level -0.3 0.6 -0.5 0.6 V

Clock input high level 2.4 VCC 3.0 VCC V

Input low level -0.3 0.8 -0.5 0.8 V

Input high level 2.0 VCC 2 . 2 VCC V

Output low level on all outputs 0.4 V IOL= 5 mA

Output low level on all outputs 0.4 V IOL= 4 mA

Output high level 2.4 V IOH= -5 mA

Output high level 2.0 V IOH= -1 mA

Input leakage ±10 ±10 µA

Clock leakage ±10 ±10 µA

Avg power supply current 1.3 3 m A

Input capacitance 5 5 pF

Rev. 5.01

22

Page 23

-

1

1

1

T1w

E

XTERNAL

1

CLOCK

BAUDOUT

ST16C550

T2w

T3w

/2 -BAUDOUT

/3 -BAUDOUT

/3> -BAUDOUT

X450-CK-

Clock timing

Rev. 5.01

23

Page 24

ST16C550

-

A

C

I

D

T4w

1

-

D

-

A

C

I

T4w

AS

0-A2

CS2

S1-CS0

IO R

OR

DDIS

0-D7

T8d

T5s

Valid

Address

T6s

Valid

T7d T7h

T11d

T12d

T7w

Active

Active

Data

General Read Timing when using -AS signal

T5h

T6h

T9d

T11d

T12h

X550-RD-1

AS

T5s

0-A2

CS2

S1-CS0

IOW

OW

0-D7

T13d T13h

T14d

Valid

Address

T6s

Valid

T13w

Active

T16s

Data

General Write Timing when using -AS signal.

T5h

T6h

T15d

T16h

X550-W D-

Rev. 5.01

24

Page 25

ST16C550

A0-A2

-CS

-IOR

D0-D7

Valid

Address

T6s'

T12d

Active

T7w

Active

T7h'

T9d

T12h

Data

T6s'

General Read Timing when -AS is tied to GND

Valid

Address

T7w’

Active

T12d

T7h'

T12h

A0-A2

-CS

-IOW

D0-D7

Rev. 5.01

Valid

Address

T6s'

Active

T13w

Active

T16s

Data

T7h'

T15d

T16h

T6s'

General Write Timing when -AS is tied to GND

Valid

Address

T7h'

Active

T16s

25

Page 26

ST16C550

I

-

-

-

-

-

I

I

-

1

IOW

OW

RTS

DTR

CD

CTS

DSR

NT

IOR

OR

RI

Active

Change of state

T17d

Change of state

Change of state

T18d T18d

Active Active

T19d

Active

Change of state

Active

Active Active

T18d

Change of state

X450-MD-

Modem input/output timing

Rev. 5.01

26

Page 27

ST16C550

STOP

START

R

I

I

X

NT

IOR

OR

BIT

D0 D1 D2 D3 D4 D5 D6 D7

DATA BITS (5-8)

5 DATA BITS

6 DATA BITS

7 DATA BITS

16 BAUD RATE CLOCK

PARITY

BIT

BIT

NEXT

DATA

START

BIT

T20d

Active

T21d

X450-RX-1

Receive timing

Rev. 5.01

27

Page 28

ST16C550

STOP

START

R

-

I

X

RXRDY

IOR

OR

BIT

D0 D1 D2 D3 D4 D5 D6 D7

DATA BITS (5-8)

Receive ready timing in non FIFO mode

PARITY

BIT

BIT

NEXT

DATA

START

BIT

T25d

Active

Data

Ready

T26d

Active

X550-RX-2

Rev. 5.01

28

Page 29

ST16C550

STOP

START

R

-

I

X

RXRDY

IOR

OR

BIT

D0 D1 D2 D3 D4 D5 D6 D7

DATA BITS (5-8)

Receive ready timing in FIFO mode

PARITY

BIT

BIT

First byte

that reaches

the trigger

level

T25d

Active

Data

Ready

T26d

Active

X550-RX-3

Rev. 5.01

29

Page 30

ST16C550

T

I

X

NT

IOW/

-IOW

T22d

Active

START

BIT

DATA BITS (5-8)

D0 D1 D2 D3 D4 D5 D6 D7

5 DATA BITS

6 DATA BITS

7 DATA BITS

Active TX Ready

T23d

STOP

BIT

PARITY

BIT

T24d

Active

16 BAUD RATE CLOCK

Transmit timing

Rev. 5.01

30

Page 31

ST16C550

STOP

START

T

-

2

X

-IOW

IOW

TXRDY

Active

BYTE #1

BIT

D0 D1 D2 D3 D4 D5 D6 D7

DATA BITS (5-8)

T27d

Active

Transmitter ready

PARITY

BIT

BIT

NEXT

DATA

START

BIT

T28d

Transmitter

not ready

X550-TX-

Transmit ready timing in non FIFO mode

Rev. 5.01

31

Page 32

ST16C550

START BIT

T

I

D

-

X

IOW

OW

0-D7

TXRDY

Active

BYTE #16

T27d

DATA BITS (5-8)

D0 D1 D2 D3 D4 D5 D6 D7

5 DATA BITS

6 DATA BITS

7 DATA BITS

T28d

FIFO Full

STOP BIT

PARITY BIT

X550-TX-3

Transmit ready timing in FIFO mode

Rev. 5.01

32

Page 33

PACKAGE OUTLINE DRAWING

ST16C550

D D

44LEAD PLASTIC LEADED CHIP CARRIER

(PLCC)

D

D

1

1

244

1

D

3

D

3

45° x H

45° x H

2

C

1

A

A

1

Seating Plane

A

2

B

1

B

e

R

D

2

Note: The control dimension is t he i nch column

SYMBOL

A

A

1

A

2

B

B

1

C

D

D

1

D

2

D

3

e

H

1

H

2

R

INCHES MILLIMETERS

MIN MAX MIN MAX

0.165

0.090

0.020

0.013

0.026

0.008

0.685

0.650

0.590

0.042

0.042

0.025

0.500 typ

0.50 BSC

0.180

0.120

-----

0.021

0.032

0.013

0.695

0.656

0.630

0.056

0.048

0.045

4.19

2.29

0.51

0.33

0.66

0.19

17.40

16.51

14.99

12.70 typ

1.07

1.07

0.64

4.57

3.05

------

0.53

0.81

0.32

17.65

16.66

16.00

1.27BSC

1.42

1.22

1.14

Rev. 5.01

33

Page 34

ST16C550

PACKAGE OUTLINE DRAWING

48 LEAD THIN QUAD FLAT PACK

(TQFP)

D

D

36 25

1

Seating

Plane

37

48

1

B

e

A

2

A

A

1

1

2

Note: The control dimension is the millimeter column

SYMBOL

A

A

1

A

2

B

C

D

D

1

e

L

α

INCHES MILLIMETERS

MIN MAX MIN MAX

0.039

0.002

0.037

0.007

0.004

0.346

0.272

0.047

0.006

0.041

0.011

0.008

0.362

0.280

1.00

0.05

0.95

0.17

0.09

8.80

6.90

0.20 BSC

0.018

0°

0.030

7°

0.45

0°

C

L

0.50BSC

24

13

D

1.20

0.15

1.05

0.27

0.20

9.20

7.10

0.75

7°

D

1

α

Rev. 5.01

34

Page 35

ST16C550

EXPLANATION OF DATA SHEET REVISIONS:

FROM TO CHANGES DATE

4.20 4.30 Added revision history. Added Device Status to front page. Sept 2003

4.30 5.00 Updated AC Timing values for IOW, CS and IOR pulse widths and

Read/Write cycle delays. This applies to devices with top mark date Feb 2005

code of "B2 YYWW" and newer.

5.00 5.01 Corrected the AC Timing values. Added Chip Select Width for Apr 2005

clarification.

NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to

improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits

described herein, conveys no license under any patent or other right, and makes no representation that the circuits

are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may

vary depending upon a user's specific application. While the information in this publication has been carefully

checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure

of the product can reasonably be expected to cause failure of the life support system or to significantly affect its

safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives,

in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user

assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 2005 EXAR Corporation

Datasheet April 2005

Send your UART technical inquiry with technical details to hotline: uarttechsupport@exar.com

Reproduction, in part or whole, without prior written consent of EXAR Corporation is prohibited.

Rev. 5.01

35

Loading...

Loading...