Page 1

SL74HC161

Semiconductor

Presettable Counters

High-Performance Silicon-Gate CMOS

The SL74HC161 is identical in pinout to the LS/ALS161. The device

inputs are compatible with standard CMOS outputs; with pullup

resistors, they are compatible with LS/ALSTTL outputs.

The SL74HC161 is programmable 4-bit synchronous counter that

feature parallel Load, asynchronous Reset, a Carry Output for

cascading and count-enable controls.

The SL74HC161 is binary counter with asynchronous Reset.

• Outputs Directly Interface to CMOS, NMOS, and TTL

• Operating Voltage Range: 2.0 to 6.0 V

• Low Input Current: 1.0 µA

• High Noise Immunity Characteristic of CMOS Devices ORDERING INFORMATION

SL74HC161N Plastic

SL74HC161D SOIC

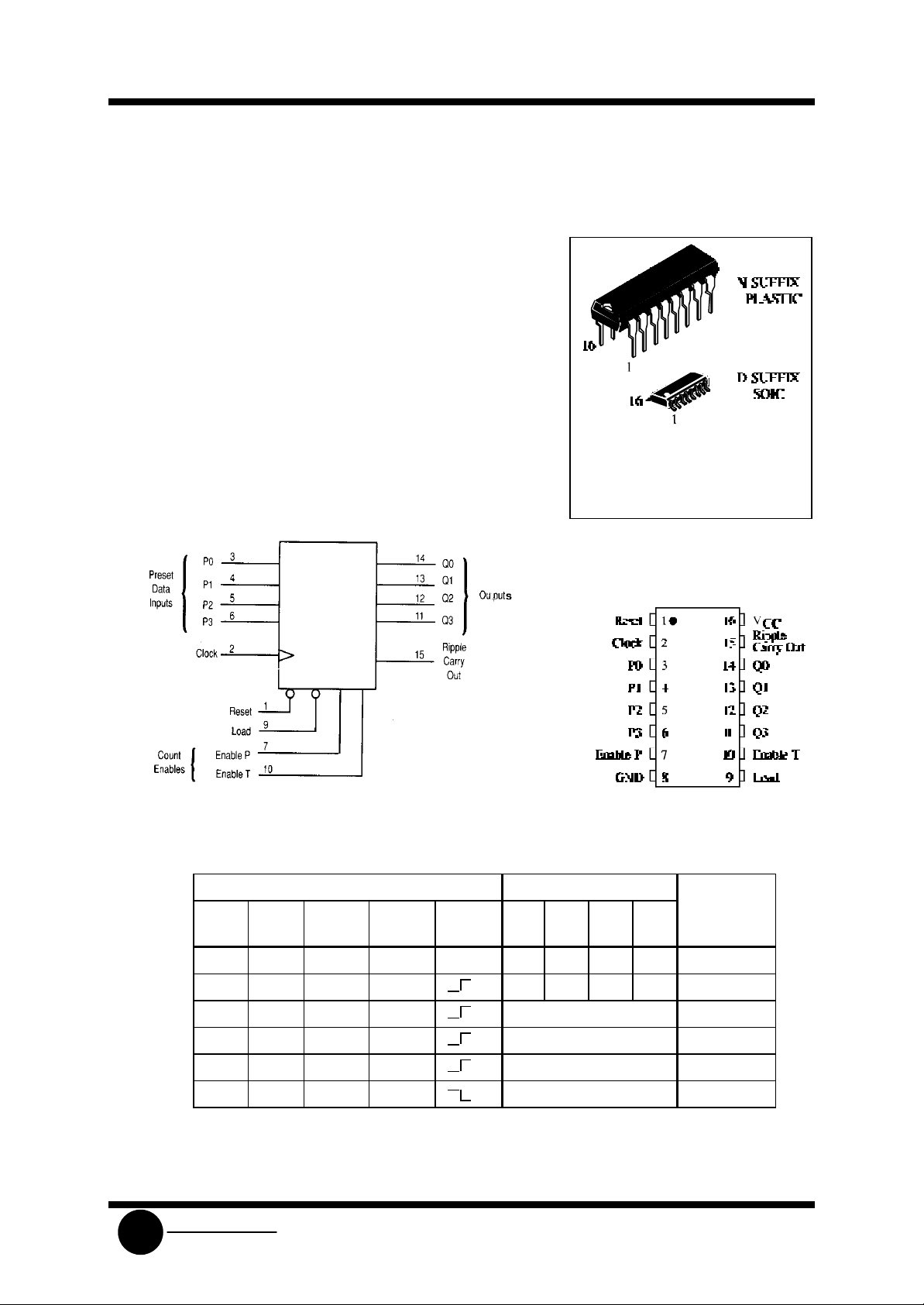

LOGIC DIAGRAM

TA = -55° to 125° C for all packages

PIN ASSIGNMENT

PIN 16 =VCC

PIN 8 = GND

FUNCTION TABLE

Inputs Outputs

Reset Load Enable P Enable T Clock Q0 Q1 Q2 Q3 Function

L X X X X L L L L Reset to “0”

H L X X P0 P1 P2 P3 Preset Data

H H X L No change No count

SLS

H H L X No change No count

H H H H Count up Count

H X X X No change No count

X=don’t care

P0,P1,P2,P3 = logic level of Data inputs

Ripple Carry Out = Enable T • Q0 • Q1 • Q2 • Q3

System Logic

Page 2

SL74HC161

Semiconductor

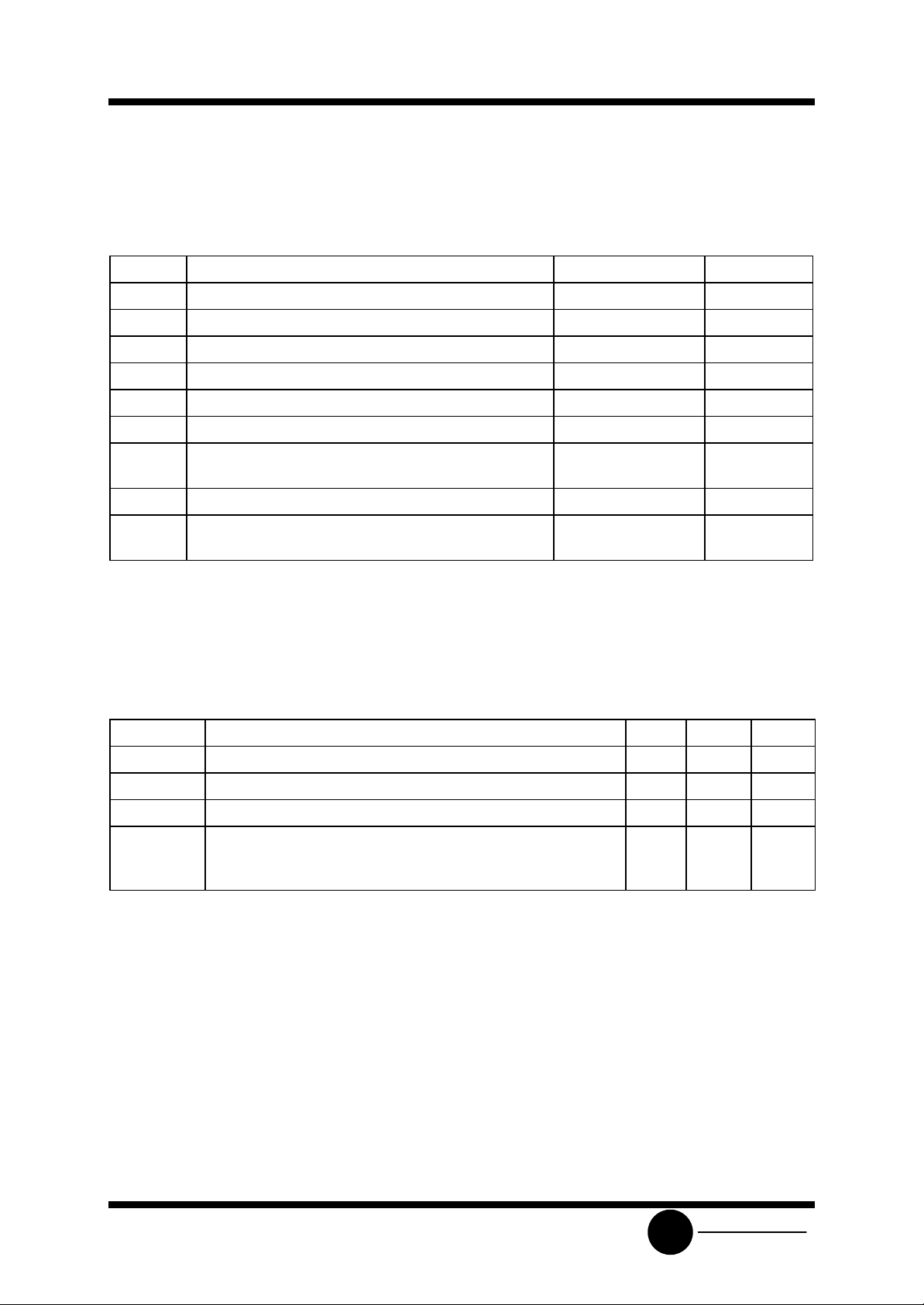

MAXIMUM RATINGS*

Symbol Parameter Value Unit

VCC DC Supply Voltage (Referenced to G ND) -0.5 to +7.0 V

VIN DC Input Voltage (Referenced to GND) -1.5 to VCC +1.5 V

V

DC Output Voltage (Referenced to GND) -0.5 to VCC +0.5 V

OUT

IIN DC Input Current, per Pin ±20 mA

I

DC Output Current, per Pin ±25 mA

OUT

ICC DC Supply Current, VCC and GND Pins ±50 mA

PD Power Dissipation in Still Air, Plastic DIP+

SOIC Package+

750

500

Tstg Storage Temperature -65 to +150 °C

TL Lead Temperature, 1 mm from Case for 10 Seconds

260 °C

(Plastic DIP or SOIC Package)

*

Maximum Ratings are those values beyond which damage to the device may occur.

Functional operation should be restricted to the Recommended Operating Conditions.

+Derating - Plastic DIP: - 10 mW/°C from 65° to 125°C

SOIC Package: : - 7 mW/°C from 65° to 125°C

RECOMMENDED OPERATING CONDITIONS

Symbol Parameter Min Max Unit

VCC DC Supply Voltage (Referenced to GND) 2.0 6.0 V

VIN, V

DC Input Voltage, Output Voltage (Referenced to GND) 0 VCC V

OUT

TA Operating Temperature, All Package Types -55 +125 °C

tr, tf Input Rise and Fall Time (Figure 1) VCC =2.0 V

VCC =4.5 V

V

=6.0 V

CC

0

0

0

1000

500

400

mW

ns

This device contains protection circuitry to guard against damage due to high static voltages or electric

fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated

voltages to this high-impedance circuit. For proper operation, VIN and V

GND≤(VIN or V

OUT

)≤VCC.

should be constrained to the range

OUT

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or VCC).

Unused outputs must be left open.

System Logic

SLS

Page 3

SL74HC161

Semiconductor

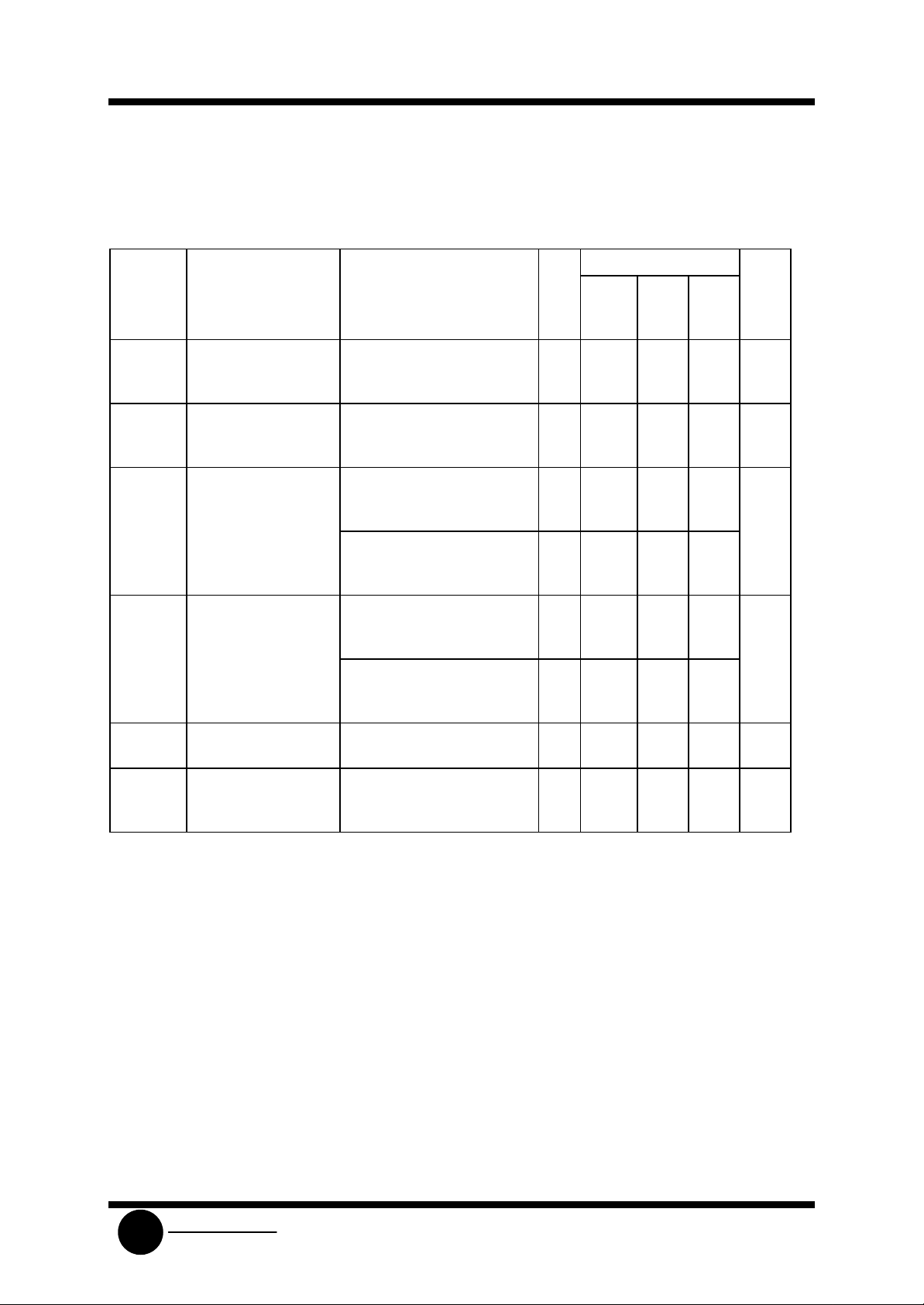

DC ELECTRICAL CHARACTERISTICS(Voltages Referenced to GND)

VCC Guaranteed Limit

Symbol Parameter Test Conditions V 25 °C

to

-55°C

VIH Minimum High-Level

Input Voltage

VIL Maximum Low -Level

Input Voltage

VOH Minimum High-Level

Output Voltage

VIN=VIH or VIL

VOL Maximum Low -Level

Output Voltage

VIN=VIH or VIL

IIN Maximum Input

V

=0.1 V or VCC-0.1 V

OUT

I

≤ 20 µA

OUT

V

=0.1 V or VCC-0.1 V

OUT

I

≤ 20 µA

OUT

VIN=VIH or VIL

I

≤ 20 µA

OUT

I

≤ 6.0 mA

OUT

I

≤ 7.8 mA

OUT

VIN=VIH or VIL

I

≤ 20 µA

OUT

I

≤ 6.0 mA

OUT

I

≤ 7.8 mA

OUT

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

4.5

6.0

2.0

4.5

6.0

4.5

6.0

1.5

3.15

4.2

0.5

1.35

1.8

1.9

4.4

5.9

3.98

5.48

0.1

0.1

0.1

0.26

0.26

VIN=VCC or GND 6.0 ±0.1 ±1.0 ±1.0 µA

Leakage Current

≤85

°C

1.5

3.15

4.2

0.5

1.35

1.8

1.9

4.4

5.9

3.84

5.34

0.1

0.1

0.1

0.33

0.33

≤125

°C

1.5

3.15

4.2

0.5

1.35

1.8

1.9

4.4

5.9

3.7

5.2

0.1

0.1

0.1

0.4

0.4

Unit

V

V

V

V

ICC Maximum Quiescent

Supply Current

(per Package)

System Logic

SLS

VIN=VCC or GND

I

=0µA

OUT

6.0 4.0 40 160 µA

Page 4

SL74HC161

Semiconductor

AC ELECTRICAL CHARACTERISTICS(C

=50pF,Input tr=tf=6.0 ns)

L

VCC Guaranteed Limit

Symbol Parameter V 25 °C to

≤85°C ≤125°C Unit

-55°C

f

Maximum Clock Frequency (Figures 1,6) 2.0

max

t

PLH

Maximum Propagation Delay Clock to Q

t

(Figures 1,6) 2.0

PHL

t

Maximum Propagation Delay Reset to Q

PHL

(Figures 2 and 6)

t

PLH

Maximum Propagation Delay Enable T to Ripple

4.5

6.0

2.0

4.5

6.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

6

30

35

120

20

16

145

22

18

145

20

17

110

16

14

5

24

28

160

23

20

185

25

20

185

22

19

150

18

15

Carry Out

t

(Figures 3,6) 2.0

PHL

4.5

6.0

135

18

15

175

20

16

4

20

24

200

28

22

320

30

23

220

25

21

190

20

17

210

22

20

MHz

ns

ns

ns

ns

ns

t

PLH

Maximum Propagation Delay Clock to Ripple

t

Carry Out (Figures 1,6) 2.0

PHL

t

Maximum Propagation Delay Reset to Ripple Carry

PHL

Out (Figures 2,6)

t

, t

TLH

Maximum Output Transition Time, Any Output

THL

(Figures 1 and 6)

2.0

4.5

6.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

120

22

18

145

22

20

155

22

18

75

15

13

160

27

22

185

28

24

190

26

22

95

19

16

200

30

25

220

35

28

230

30

25

110

22

19

CIN Maximum Input Capacitance - 10 10 10 pF

Power Dissipation Capacitance (Per Gate) Typical @25°C,VCC=5.0 V

CPD Used to determine the no-load dynamic power

consumption:

PD=CPDV

2

f+ICCVCC

CC

30 pF

ns

ns

ns

ns

SLS

System Logic

Page 5

SL74HC161

Semiconductor

TIMING REQUIREMENTS (C

VCC Guaranteed Limit

Symbol Parameter V 25 °C to

tSU Minimum Setup Time, Preset Data Inputs to Clock

(Figure 4)

tSU Minimum Setup Time, Load to Clock

(Figure 4)

tSU Minimum Setup Time, Enable T or Enable P to

Clock (Figure 5)

th Minimum Hold Time, Clock to Load or Preset Data

Inputs (Figure 4)

th Minimum Hold Time, Clock to Enable T or Enable

P (Figure 5)

t

Minimum Recovery Time, Reset Inactive to Clock

rec

(Figure 2)

=50pF,Input tr=tf=6.0 ns)

L

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

-55°C

40

15

12

60

15

12

80

20

17

3

3

3

3

3

3

80

15

12

≤85°C ≤125°C Unit

60

20

18

75

20

18

95

25

23

3

3

3

3

3

3

95

20

17

80

30

20

90

30

20

110

35

25

3

3

3

3

3

3

110

26

23

ns

ns

ns

ns

ns

ns

t

Minimum Recovery Time, Load Inactive to Clock

rec

(Figure 4)

tw Minimum Pulse Width, Clock (Figure 1) 2.0

tw Minimum Pulse Width, Reset (Figure 2) 2.0

t

Maximum Input Rise and Fall Times

r, tf

(Figure 1)

2.0

4.5

6.0

4.5

6.0

4.5

6.0

2.0

4.5

6.0

80

15

12

60

12

10

60

12

10

1000

500

400

95

20

17

75

15

13

75

15

13

1000

500

400

110

26

23

90

18

15

90

18

15

1000

500

400

ns

ns

ns

ns

SLS

System Logic

Page 6

SL74HC161

Semiconductor

Figure 1. Switching Waveforms Figure 2. Switching Waveforms

Figure 3. Switching Waveforms Figure 4. Switching Waveforms

Figure 5. Switching Waveforms Figure 6. Test Circuit

SLS

System Logic

Page 7

SL74HC161

Semiconductor

VCC=Pin 16

GND=Pin 8

The flip-flops shown in the circuit diagrams are Toggle-Enable flip-flops. A Toggle-Enable flip-flop is a

combination of a D flip-flop and a T flip-flop. When loading data from Preset inputs P0, P1, P2, and P3, the Load

signal is used to disable the Toggle input (Tn) of the flip-flop. The logic level at the Pn input is then clocked to

the Q output of the flip-flop on the next rising edge of the clock.

A logic zero on the Reset device input forces the internal clock (C) high and resets the Q output of the flipflop low.

Figure 7.Expanded logic diagram

System Logic

SLS

Page 8

SL74HC161

Semiconductor

Sequence illustrated in waveforms:

1. Reset outputs to zero.

2. Preset to binary twelve.

3. Count to thirteen, four teen, fifteen, zero, one, and two.

4. Inhibit.

Figure 8. Timing Diagram

SLS

System Logic

Page 9

SL74HC161

Semiconductor

TYPICAL APPLICATIONS CASCADING

Note:When used in these cascaded configurations the clock f

Actual performance will depend on number of stages. This limitation is due to set up times

between Enable (Port) and clock.

Figure 9. N-Bit Synchronous Counters

guaranteed limits may not apply.

max

SLS

Figure 10. Nibble Ripple Counter

System Logic

Loading...

Loading...