Datasheet SAA5290PS-092, SAA5290PS-107, SAA5290PS-108, SAA5290PS-128, SAA5290PS-129 Datasheet (Philips)

...Page 1

DATA SH EET

Preliminary specification

Supersedes data of 1997 Jul 07

File under Integrated Circuits, IC02

1998 Dec 14

INTEGRATED CIRCUITS

SAA5x9x family

Economy teletext and TV

microcontrollers

Page 2

1998 Dec 14 2

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

CONTENTS

1 FEATURES

1.1 General

1.2 Microcontroller

1.3 Teletext acquisition

1.4 Teletext Display

1.5 Additional features of SAA529xA devices

1.6 Additional features of SAA549x devices

2 GENERAL DESCRIPTION

2.1 Device masking history

3 ORDERING INFORMATION

4 QUICK REFERENCE DATA

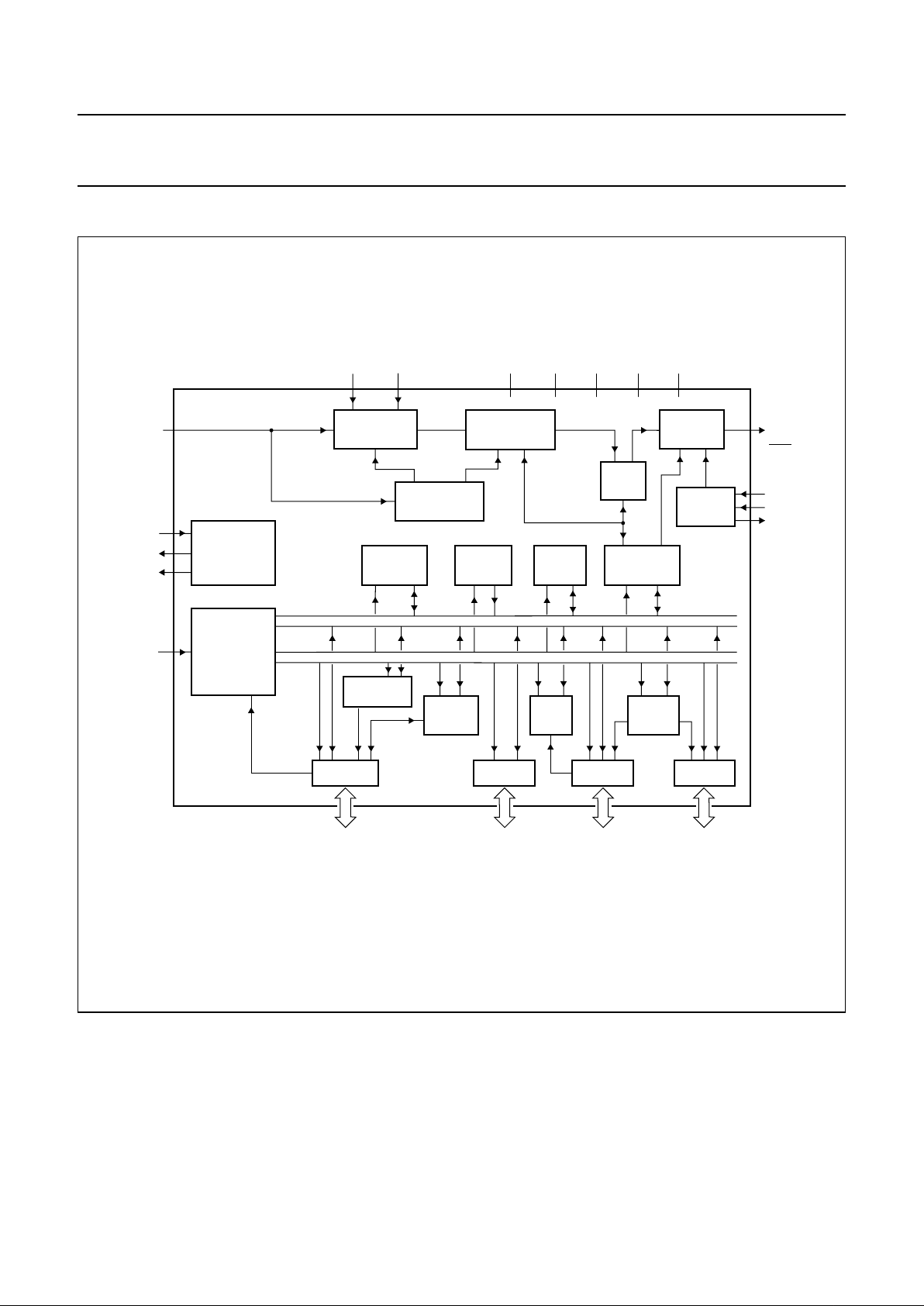

5 BLOCK DIAGRAM

6 PINNING INFORMATION

6.1 Pinning

6.2 Pin description

7 FUNCTIONAL DESCRIPTION

7.1 Microcontroller

7.2 80C51 features not supported

7.3 Additional features

7.4 Microcontroller interfacing

8 TELETEXT DECODER

8.1 Data slicer

8.2 Acquisition timing

8.3 Teletext acquisition

8.4 Rolling headers and time

8.5 Error checking

8.6 Memory organisation of SAA5296/7,

SAA5296/7A and SAA5496/7

8.7 Inventory page

8.8 Memory organisation of SAA5290, SAA5290A,

SAA5291, SAA5291A and SAA5491

8.9 Packet 26 processing

8.10 VPS

8.11 Wide Screen Signalling (SAA529xA and

SAA549x only)

8.12 525-line world system teletext

8.13 Fastext detection

8.14 Page clearing

8.15 Full channel operation

8.16 Independent data services (SAA5290,

SAA5290A, SAA5291, SAA5291A and

SAA5491 only)

9 THE DISPLAY

9.1 Introduction

9.2 Character matrix

9.3 East/West selection

9.4 National option characters

9.5 The twist attribute

9.6 Language group identification

9.7 525-line operation

9.8 On-Screen Display characters

9.9 Control characters

9.10 Quadruple width display (SAA549x)

9.11 Page attributes

9.12 Display modes

9.13 On-Screen Display boxes

9.14 Screen colour

9.15 Redefinable colours (SAA549x)

9.16 Cursor

9.17 Other display features

9.18 Display timing

9.19 Horizontal timing

9.20 Vertical timing

9.21 Display position

9.22 Clock generator

9.23 Reset signal

10 CHARACTER SETS

10.1 Pan-European

10.2 Cyrillic

10.3 Greek/Turkish

10.4 Arabic/English/French

10.5 Thai

10.6 Arabic/Hebrew

10.7 Iranian

11 LIMITING VALUES

12 CHARACTERISTICS

13 CHARACTERISTICS FOR THE I2C-BUS

INTERFACE

14 QUALITY AND RELIABILITY

15 APPLICATION INFORMATION

16 EMC GUIDELINES

17 PACKAGE OUTLINES

18 SOLDERING

18.1 Introduction

18.2 Through-hole mount packages

18.3 Surface mount packages

18.4 Suitability of IC packages for wave, reflow and

dipping soldering methods

19 DEFINITIONS

20 LIFE SUPPORT APPLICATIONS

21 PURCHASE OF PHILIPS I2C COMPONENTS

Page 3

1998 Dec 14 3

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

1 FEATURES

1.1 General

• Single chip microcontroller with integrated teletext

decoder

• Single +5 V power supply

• Single crystal oscillator for teletext decoder, display and

microcontroller

• Teletext function can be powered-down independently

of microcontroller function for reduced power

consumption in standby

• Pin compatibility throughout family.

1.2 Microcontroller

• 80C51 microcontroller core

• 16/32/64 kbyte mask programmed ROM

• 256/768/1280 bytes of microcontroller RAM

• Eight 6-bit Pulse Width Modulator (PWM) outputs for

control of TV analog signals

• One 14-bit PWM for Voltage Synthesis Tuner control

• Four 8-bit Analog-to-Digital converters

• 2 high current open-drain outputs for directly driving

LEDs etc.

• I

2

C-bus interface

• External ROM and RAM capability on QFP80 package

version.

1.3 Teletext acquisition

• 1 page and 10 page Teletext version

• Acquisition of 525-line and 625-line World System

Teletext, with automatic selection

• Acquisition and decoding of VPS data (PDC system A)

• Page clearing in under 64 µs (1 TV line)

• Separate storage of extension packets

(SAA5296/7, SAA5296/7A and SAA5496/7)

• Inventory of transmitted Teletext pages stored in the

Transmitted Page Table (TPT) and Subtitle Page Table

(SPT) (SAA5296/7, SAA5296/7A and SAA5496/7)

• Automatic detection of FASTEXT transmission

• Real-time packet 26 engine for processing accented

(and other) characters

• Comprehensive Teletext language coverage

• Video signal quality detector.

1.4 Teletext Display

• 525-line and 625-line display

• 12 × 10 character matrix

• Double height, width and size On-Screen Display (OSD)

• Definable border colour

• Enhanced display features including meshing and

shadowing

• 260 characters in mask programmed ROM

• Automatic FRAME output control with manual override

• RGB push-pull output to standard decoder ICs

• Stable display via slave synchronisation to horizontal

sync and vertical sync.

1.5 Additional features of SAA529xA devices

• Wide Screen Signalling (WSS) bit decoding (line 23).

1.6 Additional features of SAA549x devices

• Wide Screen Signalling bit decoding (line 23)

• Quad width OSD capability

• 32 additional OSD characters in mask programmed

ROM

• 8 foreground and 8 background colours definable from a

palette of 64.

Page 4

1998 Dec 14 4

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

2 GENERAL DESCRIPTION

The SAA529x, SAA529xA and SAA549x family of

microcontrollers are a derivative of the Philips’

industry-standard 80C51 microcontroller and are intended

for use as the central control mechanism in a television

receiver. They provide control functions for the television

system and include an integrated teletext function.

The teletext hardware has the capability of decoding and

displaying both 525-line and 625-line World System

Teletext. The same display hardware is used both for

Teletext and On-Screen Display, which means that the

display features give greater flexibility to differentiate the

TV set.

The family offers both 1 page and 10 page Teletext

capability, in a range of ROM sizes. Increasing display

capability is offered from the SAA5290 to the SAA5497.

2.1 Device masking history

A number of mask variants have been produced for the

ETT family of devices. The current mask variants available

are:

• SAA5x90 M5A

• SAA5x91 M1A

• SAA5x96 M5A

• SAA5x97 M1A.

There have been two design issues with the M1 mask,

which required resolving, these brought about the

introduction of the M1A mask:

• Spanish G3 arrows

• OSD twist effect.

The Spanish G3 arrows issue was only encountered on

the Pan-European device, it became apparent that an

up arrow and a right arrow were missing from the Spanish

character map.

The OSD twist effect was inherent on all devices, although

not visible on the Pan-European version. Essentially, OSD

characters had the ability to set and reset the serial

attribute “twist”. This effect is described in detail in

Application note

“SPG/AN97004 Version 1.0”

.

Page 5

1998 Dec 14 5

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

3 ORDERING INFORMATION

Note

1. ‘nnn’ is a three-digit number uniquely referencing the microcontroller program mask and OSD mask.

4 QUICK REFERENCE DATA

TYPE NUMBER

(1)

PACKAGE

PROGRAM

MEMORY (ROM)

NAME DESCRIPTION VERSION

SAA5290PS/nnn SDIP52 plastic shrink dual in-line package; 52 leads

(600 mil)

SOT247-1 16 kbytes

SAA5291PS/nnn SDIP52 plastic shrink dual in-line package; 52 leads

(600 mil)

SOT247-1 32 kbytes

SAA5296PS/nnn

SAA5296APS/nnn

SAA5491PS/nnn

SAA5496PS/nnn

SAA5491H/nnn QFP80 plastic quad flat package; 80 leads (lead length

1.95 mm); body 14 × 20 × 2.8 mm

SOT318-2 32 kbytes and external

SAA5297PS/nnn SDIP52 plastic shrink dual in-line package; 52 leads

(600 mil)

SOT247-1 64 kbytes

SAA5297APS/nnn

SAA5497PS/nnn

SAA5297AH/nnn QFP80 plastic quad flat package; 80 leads (lead length

1.95 mm); body 14 × 20 × 2.8 mm

SOT318-2 64 kbytes or external

SAA5497H/nnn

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V

DDA

supply voltages 4.5 5.0 5.5 V

V

DDM

V

DDT

f

xtal

crystal frequency − 12 − MHz

T

amb

operating ambient temperature −20 − +70 °C

I

DDM

microcontroller supply current − 20 35 mA

SAA5290, SAA5290A, SAA5291, SAA5291A and SAA5491

I

DDA

analog supply current − 35 50 mA

I

DDT

teletext supply current − 40 65 mA

SAA5296, SAA5296A, SAA5297, SAA5297A, SAA5496 and SAA5497

I

DDA

analog supply current − 35 50 mA

I

DDT

teletext supply current − 50 80 mA

Page 6

1998 Dec 14 6

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

5 BLOCK DIAGRAM

Fig.1 Block diagram.

handbook, full pagewidth

MGK462

PORT 1 PORT 0 PORT 3 PORT 2

TIMER/

CTRS

I

2

C-BUS

INTERFACE

ADC

SAA5x9x

PWM

8051

MICRO-

CONTROLLER

OSCILLATOR

TEXT

INTERFACE

512 × 8

AUX RAM

256 × 8

RAM

32K × 8

ROM

ACQUISITION

TIMING

PAGE

RAM

DISPLAY

TIMING

DATA SLICER

DISPLAY

TELETEXT

ACQUISITION

BLACK IREF

V

DDAVDDMVDDTVSSAVSSD

CVBS0,

CVBS1

RESET

P1.0 to P1.7 P0.0 to P0.7 P3.0 to P3.7 P2.0 to P2.7

XTALIN

XTALOUT

OSCGND

VSYNC

HSYNC

FRAME

R, G, B,

VDS,

COR

data

address

int

Page 7

1998 Dec 14 7

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

6 PINNING INFORMATION

6.1 Pinning

Fig.2 Pin configuration (SDIP52).

handbook, halfpage

1

2

3

4

5

6

7

8

9

10

11

12

13

40

39

38

37

36

35

34

33

32

31

30

29

28

27

14

15

16

17

18

19

20

22

23

24

25

26

21

42

41

43

44

45

46

47

48

49

50

51

52

MGK461

SAA5x9x

P2.0/TPWM

P2.1/PWM0

P2.2/PWM1

P2.3/PWM2

P2.4/PWM3

P2.5/PWM4

P2.6/PWM5

P2.7/PWM6

P3.0/ADC0

P3.1/ADC1

P3.2/ADC2

P3.3/ADC3

P0.0

P0.1

P0.2

P0.3

P0.4

P0.5

P0.6

P0.7

CVBS0

CVBS1

BLACK

IREF

V

SSD

DDM

V

DDT

V

DDA

V

V

SSD

SSA

V

P1.5

P1.4

P1.7/SDA

P1.6/SCL

P1.3/T1

P1.2/INT0

P1.1/T0

P1.0/INT1

RESET

XTALOUT

XTALIN

OSCGND

VSYNC

HSYNC

VDS

R

G

B

RGBREF

P3.4/PWM7

COR

FRAME

Page 8

1998 Dec 14 8

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

Fig.3 Pin configuration (QFP80).

handbook, full pagewidth

SAA5x9x

MGL157

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

P2.6/PWM5

P2.7/PWM6

P3.0/ADC0

n.c.

P3.1/ADC1

P3.2/ADC2

P3.3/ADC3

P2.5/PWM4

P2.4/PWM3

RD

WR

V

SSD

EA

P0.0

P0.1

P0.2

PSEN

ALE

REF−

P0.3

P1.2/INT0

RESET

XTALOUT

XTALIN

OSCGND

A8

A9

A10

A11

V

DDT

REF+

V

DDA

P3.6

VSYNC

P3.5

HSYNC

P3.4/PWM7

VDS

R

G

60

59

58

57

56

P1.1/T0

P1.0/INT1

V

DDM

P1.3/T1

64

63

62

61

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

P0.6

P0.7

V

SSA

CVBS0

CVBS1

BLACK

IREF

A15

A14

A13

A12

FRAME

V

SSD

COR

RGBREF

B

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

P2.3/PWM2

P2.2/PWM1

P2.1/PWM0

P2.0/TPWM

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

P1.5

P1.4

P1.7/SDA

P1.6/SCL

21

22

23

24

P0.4

P3.7

n.c.

P0.5

Page 9

1998 Dec 14 9

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

6.2 Pin description

Table 1 SDIP52 and QFP80 packages

SYMBOL

PIN

DESCRIPTION

SDIP52 QFP80

P2.0/TPWM 1 77 Port 2: 8-bit open-drain bidirectional port with alternative functions.

P2.0/TPWM is the output for the 14-bit high precision PWM.

P2.1/PWM0 to P2.7/PWM6 are the outputs for the 6-bit PWMs 0 to 6.

P2.1/PWM0 2 78

P2.2/PWM1 3 79

P2.3/PWM2 4 80

P2.4/PWM3 5 9

P2.5/PWM4 6 8

P2.6/PWM5 7 1

P2.7/PWM6 8 2

P3.0/ADC0 9 3 Port 3: 8-bit open-drain bidirectional port with alternative functions.

P3.0/ADC0 to P3.3/ADC3 are the inputs for the software ADC facility.

P3.4/PWM7 is the output for the 6-bit PWM7.

P3.1/ADC1 10 5

P3.2/ADC2 11 6

P3.3/ADC3 12 7

P3.4/PWM7 30 44

P3.5 − 46

P3.6 − 48

P3.7 − 22

V

SSD

13 12 Digital ground.

P0.0 14 14 Port 0: 8-bit open-drain bidirectional port.

P0.5 and P0.6 have 10 mA current sinking capability for direct drive of LEDs.

P0.1 15 15

P0.2 16 16

P0.3 17 20

P0.4 18 21

P0.5 19 24

P0.6 20 25

P0.7 21 26

V

SSA

22 27 Analog ground.

CVBS0 23 28 Composite video inputs; a positive-going 1 V (peak-to-peak) input is required,

connected via a 100 nF capacitor.

CVBS1 24 29

BLACK 25 30 Video black level storage input: this pin should be connected to V

SSA

via a

100 nF capacitor.

IREF 26 31 Reference current input for analog circuits, connected to V

SSA

via a 27 kΩ

resistor.

FRAME 27 36 De-interlace output synchronised with the VSYNC pulse to produce a

non-interlaced display by adjustment of the vertical deflection circuits.

V

SSD

28 37 Internally connected; this pin should be connected to digital ground.

COR 29 38 Open-drain, active LOW output which allows selective contrast reduction of

the TV picture to enhance a mixed mode display.

Page 10

1998 Dec 14 10

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

RGBREF 31 39 DC input voltage to define the output HIGH level on the RGB pins.

B 32 40 Pixel rate output of the BLUE colour information.

G 33 41 Pixel rate output of the GREEN colour information.

R 34 42 Pixel rate output of the RED colour information.

VDS 35 43 Video/data switch push-pull output for dot rate fast blanking.

HSYNC 36 45 Schmitt trigger input for a TTL level version of the horizontal sync pulse; the

polarity of this pulse is programmable by register bit TXT1.H POLARITY.

VSYNC 37 47 Schmitt trigger input for a TTL level version of the vertical sync pulse;

the polarity of this pulse is programmable by register bit TXT1.V POLARITY.

V

DDA

38 49 +5 V analog power supply.

V

DDT

39 51 +5 V teletext power supply.

OSCGND 40 56 Crystal oscillator ground.

XTALIN 41 57 12 MHz crystal oscillator input.

XTALOUT 42 58 12 MHz crystal oscillator output.

RESET 43 59 For a recommended reset circuit refer to the application diagram shown in

Fig.29.

V

DDM

44 62 +5 V microcontroller power supply.

P1.0/INT1 45 63 Port 1: 8-bit open-drain bidirectional port with alternate functions.

P1.0/INT1 is external interrupt 1 which can be triggered on the rising and

falling edge of the pulse.

P1.1/T0 is the counter/timer 0.

P1.2/INT0 is external interrupt 0.

P1.3/T1 is the counter/timer 1.

P1.6/SCL is the serial clock input for the I

2

C-bus.

P1.7/SDA is the serial data port for the I2C-bus.

P1.1/T0 46 64

P1.2/INT0 47 60

P1.3/T1 48 61

P1.6/SCL 49 65

P1.7/SDA 50 66

P1.4 51 67

P1.5 52 68

REF+ − 50 Positive reference voltage for software driven ADC.

REF−−19 Negative reference voltage for software driven ADC.

RD − 10 Read control signal to external Data Memory.

WR − 11 Write control signal to external Data Memory.

PSEN − 17 Enable signal for external Program Memory.

ALE − 18 External latch enable signal; active HIGH.

EA − 13 Control signal used to select external (LOW) or internal (HIGH) Program

Memory.

AD0 to AD7 − 69 to 76 Address lines A0 to A7 multiplexed with data lines D0 to D7.

A8 to A15 − 55 to 52,

35 to 32

Address lines A8 to A15.

SYMBOL

PIN

DESCRIPTION

SDIP52 QFP80

Page 11

1998 Dec 14 11

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

7 FUNCTIONAL DESCRIPTION

7.1 Microcontroller

The functionality of the microcontroller used in this family

is described here with reference to the industry-standard

80C51 microcontroller. A full description of its functionality

can be found in the

“80C51-Based 8-Bit Microcontrollers;

Data Handbook IC20”

. Using the 80C51 as a reference,

the changes made to this family fall into two categories:

• Features not supported by the SAA529x, SAA529xA or

SAA549x devices

• Features found on the SAA529x, SAA529xA or

SAA549x devices but not supported by the 80C51.

7.2 80C51 features not supported

7.2.1 INTERRUPT PRIORITY

The IP SFR is not implemented and all interrupts are

treated with the same priority level. The normal

prioritisation of interrupts is maintained within the level.

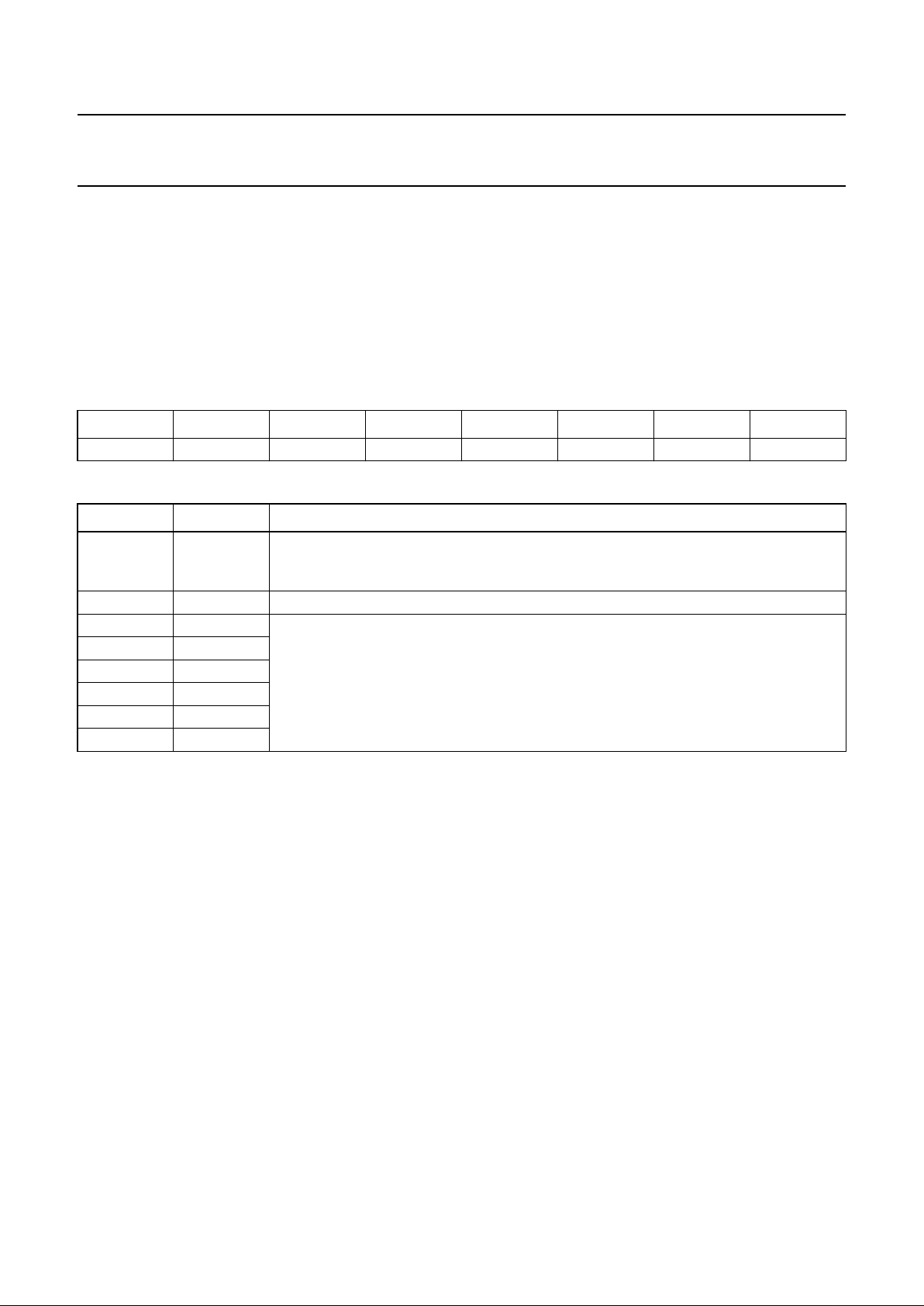

Table 2 Interrupts and vectors address

Note

1. SAA5290, SAA5290A, SAA5291, SAA5291A and

SAA5491 only.

7.2.2 O

FF-CHIP MEMORY

The SDIP52 version does not support the use of off-chip

program memory or off-chip data memory.

7.2.3 I

DLE AND POWER-DOWN MODES

As Idle and Power-down modes are not supported, their

respective bits in PCON are not available.

7.2.4 UART F

UNCTION

The 80C51 UART is not available. As a consequence the

SCON and SBUF SFRs are removed and the ES bit in the

IE SFR is unavailable.

INTERRUPT SOURCE VECTOR ADDRESS

Reset 000H

External INT0 003H

Timer 0 00BH

External INT1 013H

Timer 1 01BH

Byte I

2

C-bus 02BH

Bit I

2

C-bus; note 1 053H

7.3 Additional features

The following features are provided in addition to the

standard 80C51 features.

7.3.1 I

NTERRUPTS

The external INT1 interrupt is modified to generate an

interrupt on both the rising and falling edges of the INT1

pin, when EX1 bit is set. This facility allows for software

pulse width measurement for handling of a remote control.

7.3.2 B

IT LEVEL I

2

C-BUS INTERFACE

For reasons of compatibility with SAA5290 and

SAA5290A, the SAA5291, SAA5291A and SAA5491

contain a bit level serial I/O which supports the I2C-bus.

P1.6/SCL and P1.7/SDA are the serial I/O pins. These two

pins meet the I2C-bus specification

“The I2C-bus and how

to use it (including specifications)”

concerning the input

levels and output drive capability. Consequently, these two

pins have an open-drain output configuration. All the four

following modes of the I2C-bus are supported.

• Master transmitter

• Master receiver

• Slave transmitter

• Slave receiver.

Three SFRs support the function of the bit-level I2C-bus

hardware: S1INT, S1BIT and S1SCS and are enabled by

setting register bit TXT8.I2C SELECT to logic 0.

7.3.3 B

YTE LEVEL I

2

C-BUS INTERFACE

The byte level serial I/O supports the I2C-bus protocol.

P1.6/SCL and P1.7/SDA are the serial I/O pins. These two

pins meet the I2C-bus specification concerning the input

levels and output drive capability. Consequently, these two

pins have an open-drain output configuration.

The byte level I2C-bus serial port is identical to the I2C-bus

serial port on the 8xC552. The operation of the subsystem

is described in detail in the 8xC552 data sheet found in

“80C51-Based 8-Bit Microcontrollers; Data Handbook

IC20”

.

Four SFRs support the function of the byte level I2C-bus

hardware, they are S1CON, S1STA, S1DAT and S1ADR

and are enabled by setting register bit TXT8.I2C SELECT

to logic 1.

7.3.4 LED

SUPPORT

Port pins P0.5 and P0.6 have a 10 mA current sinking

capability to enable LEDs to be driven directly.

Page 12

1998 Dec 14 12

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

7.3.5 6-BIT PWM DACS

Eight 6-bit DACs are available to allow direct control of analog parts of the television.

Each low resolution 6-bit DAC is controlled by its associated Special Function Register (PWM0 to PWM7). The PWM

outputs are alternative functions of Port 2 and Port 3.4. The PWE bit in the SFR for the port corresponding to the PWM

output should be set to logic 1 for correct operation of the PWM output, e.g. if PWM0 is to be used, P2.1 should be set

to logic 1 setting the port pin to high-impedance.

7.3.5.1 Pulse Width Modulator Registers (PWM0 to PWM7)

Table 3 Pulse Width Modulator Registers (see Table 10 for addresses)

Table 4 Description of PWMn bits (n=0to7)

76543210

PWE − PV5 PV4 PV3 PV2 PV1 PV0

BIT SYMBOL DESCRIPTION

7 PWE If PWE is set to a logic 1, the corresponding PWM is active and controls its assigned

port pin. If PWE is set to a logic 0, the port pin is controlled by the corresponding bit in

the port SFR.

6 − Not used.

5 PV5 The output of the PWM is a pulse of period 21.33 µs with a pulse HIGH time determined

by the binary value of these 6-bits multiplied by 0.33 µs. PV5 is the most significant bit.

4 PV4

3 PV3

2 PV2

1 PV1

0 PV0

Page 13

1998 Dec 14 13

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

7.3.6 14-BIT PWM DAC

One 14-bit DAC is available to allow direct control of

analog sections of the television. The 14-bit PWM is

controlled using Special Function Registers TDACL and

TDACH.

The output of the TPWM is a pulse of period 42.66 µs.

The 7 most significant bits, TDACH.TD13 (MSB) to

TDACH.TD8 and TDACL.TD7, alter the pulse width

between 0 and 42.33 µs, in much the same way as in the

6-bit PWMs.

The 7 least significant bits, TDACL.TD6 to TDACL.TD0

(LSB), extend certain pulses by a further 0.33 µs, e.g. if the

7 least significant bits are given the value 01H, then

1 in 128 cycles is extended. If the 7 least significant bits

are given the value 02H, then 2 in 128 cycles is extended,

and so forth.

The TPWM will not start to output a new value until after

writing a value to TDACH. Therefore, if the value is to be

changed, TDACL should be written to before TDACH.

7.3.6.1 TPWM High Byte Register (TDACH)

Table 5 TPWM High Byte Register (SFR address D3H)

Table 6 Description of TDACH bits

7.3.6.2 TPWM Low Byte Register (TDACL)

Table 7 TPWM Low Byte Register (SFR address D2H)

Table 8 Description of TDACL bits

76543210

PWE − TD13 TD12 TD11 TD10 TD9 TD8

BIT SYMBOL DESCRIPTION

7 PWE If PWE is set to a logic 1, the TPWM is active and controls port line P2.0. If PWE is set

to a logic 0, the port pin is controlled by the corresponding bit in the port SFR.

6 − Not used.

5 TD13 These 6-bits along with bit TD7 in the TDACL register control the pulse width period.

TD13 is the most significant bit.

4 TD12

3 TD11

2 TD10

1 TD9

0 TD8

76543210

TD7 TD6 TD5 TD4 TD3 TD2 TD1 TD0

BIT SYMBOL DESCRIPTION

7 TD7 This bit is used with bits TD13 to TD8 in the TDACH register to control the pulse width

period.

6 to 0 TD6 to TD0 These 7-bits extend certain pulses by a further 0.33 µs.

Page 14

1998 Dec 14 14

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

7.3.7 SOFTWARE ADC

Up to 4 successive approximation ADCs can be

implemented in software by making use of the on-chip 8-bit

DAC and multiplexed voltage comparator. The software

ADC uses 4 analog inputs which are multiplexed with

P3.0 to P3.3.

Table 9 ADC input channel selection

The control of the ADC is achieved using the Special

Function Registers SAD and SADB.

SAD.CH1 and SAD.CH0 select one of the four inputs to

pass to the comparator. The other comparator input

comes from the DAC, whose value is set by SAD.SAD7

(MSB) to SAD.SAD4 and SADB.SAD3 to SADB.SAD0

(LSB).

CH1 CH0 INPUT PIN

0 0 P3.3/ADC3

0 1 P3.0/ADC0

1 0 P3.1/ADC1

1 1 P3.2/ADC2

The setting of the value SAD.SAD7 to SAD.SAD4 must be

performed at least 1 instruction cycle before the setting of

SAD.ST to ensure comparison is made using the correct

SAD.SAD7 to SAD.SAD4 value.

The output of the comparator is SAD.VHI, and is valid

after 1 instruction cycle following the setting of SAD.ST to

a logic 1.

handbook, halfpage

MULTIPLEXER

P3.0

P3.1

VH1

MGL115

P3.2

P3.3

CH1, CH0

SAD7 to SAD0

REF+REF−

1D

ST C1

8-BIT DAC

Fig.4 SAD block diagram.

Page 15

1998 Dec 14 15

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

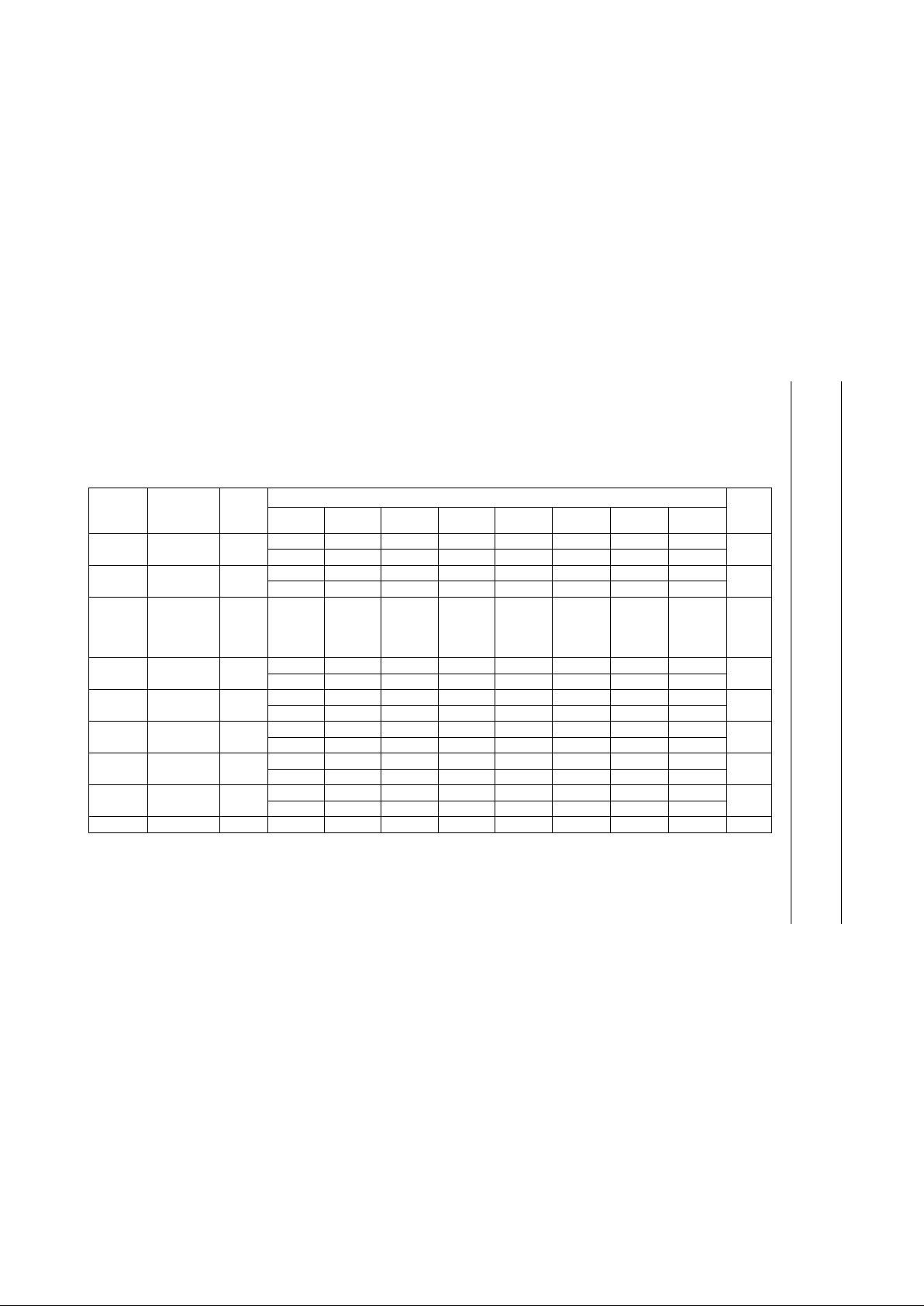

7.4 Microcontroller interfacing

The 80C51 communicates with the peripheral functions using Special Function Registers (SFRs) which are addressed as RAM locations. The registers

in the teletext decoder appear as normal SFRs in the microcontroller memory map, but are written to using an internal serial bus. The SFR map is given

in Table 10.

7.4.1 SPECIAL FUNCTION REGISTER MAP

Table 10 Special Function Register map; note 1

SYMBOL NAME

DIRECT

ADDR.

(HEX)

BIT ADDRESS, SYMBOL OR ALTERNATIVE PORT FUNCTION RESET

VALUE

(HEX)

76543210

ACC

(2)

Accumulator E0 E7 E6 E5 E4 E3 E2 E1 E0 00

−−−−−−−−

B

(2)

B register F0 F7 F6 F5 F4 F3 F2 F1 F0 00

−−−−−−−−

DPTR Data Pointer

(2 bytes)

DPH High byte

83 −−−−−−−−00

DPL Low byte

82 −−−−−−−−00

IE

(2)(3)

Interrupt

Enable

A8 AF AE AD AC AB AA A9 A8 00

EA ES1 ES2 −

(1)

ET1 EX1 ET0 EX0

P0

(2)

Port 0 80 87 86 85 84 83 82 81 80 FF

−−−−−−−−

P1

(2)

Port 1 90 97 96 95 94 93 92 91 90 FF

−−−−−−−−

P2

(2)

Port 2 A0 A7 A6 A5 A4 A3 A2 A1 A0 FF

−−−−−−−−

P3

(2)(3)

Port 3 B0 B7 B6 B5 B4 B3 B2 B1 B0 FF

−−−−−−−−

PCON

(3)

Power Control 87 − ARD −−

(1)

GF1 GF0 −−10

Page 16

1998 Dec 14 16

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

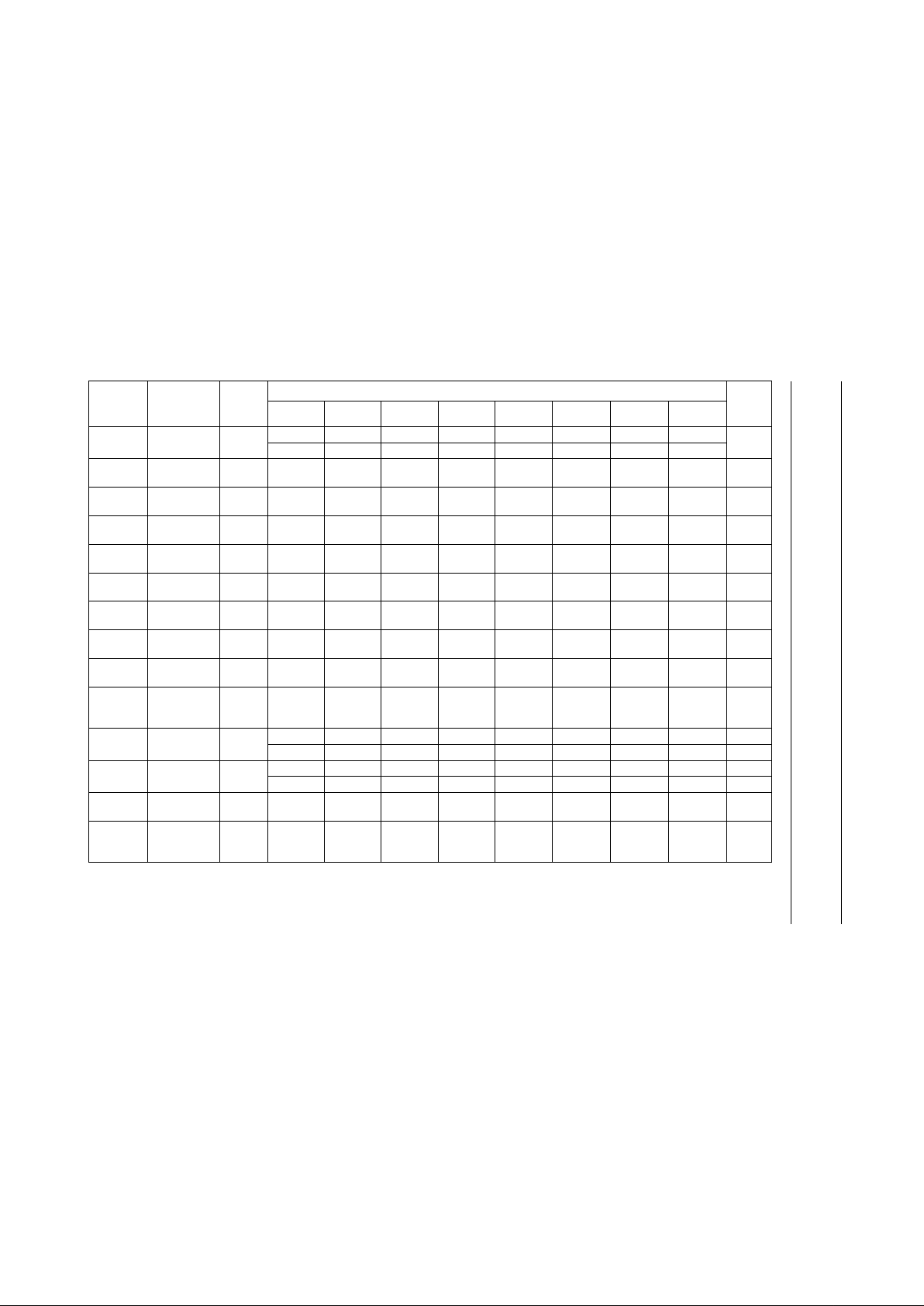

PSW

(2)

Program

Status Word

D0 D7 D6 D5 D4 D3 D2 D1 D0 00

CY AC F0 RS1 RS0 OV −

(1)

P

PWM0

(3)

Pulse Width

Modulator 0

D5 PWE −

(1)

PV5 PV4 PV3 PV2 PV1 PV0 40

PWM1

(3)

Pulse Width

Modulator 1

D6 PWE −

(1)

PV5 PV4 PV3 PV2 PV1 PV0 40

PWM2

(3)

Pulse Width

Modulator 2

D7 PWE −

(1)

PV5 PV4 PV3 PV2 PV1 PV0 40

PWM3

(3)

Pulse Width

Modulator 3

DC PWE −

(1)

PV5 PV4 PV3 PV2 PV1 PV0 40

PWM4

(3)

Pulse Width

Modulator 4

DD PWE −

(1)

PV5 PV4 PV3 PV2 PV1 PV0 40

PWM5

(3)

Pulse Width

Modulator 5

DE PWE −

(1)

PV5 PV4 PV3 PV2 PV1 PV0 40

PWM6

(3)

Pulse Width

Modulator 6

DF PWE −

(1)

PV5 PV4 PV3 PV2 PV1 PV0 40

PWM7

(3)

Pulse Width

Modulator 7

D4 PWE −

(1)

PV5 PV4 PV3 PV2 PV1 PV0 40

S1ADR

(3)

Serial

I

2

C-bus

address

DB ADR6 ADR5 ADR4 ADR3 ADR2 ADR1 ADR0 GC 00

S1CON

(2)(3)(4)

Serial

I

2

C-bus

D8 DF DE DD DC DB DA D9 D8

CR2 ENSI STA STO SI AA CR1 CR0 00

S1SCS

(2)(3)(5)

Serial

I

2

C-bus

D8 DF DE DD DC DB DA D9 D8

SDI SCI CLH BB RBF WBF STR ENS E0

S1DAT

(3)(4)

Serial

I

2

C-bus data

DA DAT7 DAT6 DAT5 DAT4 DAT3 DAT2 DAT1 DAT0 00

S1INT

(3)(5)

Serial

I

2

C-bus

Interrupt

DA SI −−−−−−−7F

SYMBOL NAME

DIRECT

ADDR.

(HEX)

BIT ADDRESS, SYMBOL OR ALTERNATIVE PORT FUNCTION RESET

VALUE

(HEX)

7654321 0

Page 17

1998 Dec 14 17

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

S1STA

(3)(4)

Serial

I

2

C-bus status

D9 STAT4 STAT3 STAT2 STAT1 STAT0 0 0 0 F8

S1BIT

(3)(5)

Serial

I

2

C-bus data

D9 SDO/SDI −−−−−−−7F

SAD

(2)(3)

Software

ADC (MSB)

E8 EF EE ED EC EB EA E9 E8 00

VHI CH1 CH0 ST SAD7 SAD6 SAD5 SAD4

SADB

(2)(3)

Software

ADC (LSB)

98 9F 9E 9D 9C 9B 9A 99 98 00

−−−−SAD3 SAD2 SAD1 SAD0

SP Stack Pointer 81 8F 8E 8D 8C 8B 8A 89 88 07

TCON

(2)

Timer/counter

control

88 TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0 00

TDACH

TPWM

High byte

D3 PWE −

(1)

TD13 TD12 TD11 TD10 TD9 TD8 40

TDACL TPWM

Low byte

D2 TD7 TD6 TD5 TD4 TD3 TD2 TD1 TD0 00

TH0 Timer 0

High byte

8C TH07 TH06 TH05 TH04 TH03 TH02 TH01 TH00 00

TH1 Timer 1

High byte

8D TH17 TH16 TH15 TH14 TH13 TH12 TH11 TH10 00

TL0 Timer 0

Low byte

8A TL07 TL06 TL05 TL04 TL03 TL02 TL01 TL00 00

TL1 Timer 1

Low byte

8B TL17 TL16 TL15 TL14 TL13 TL12 TL11 TL10 00

TMOD Timer/counter

mode

89 GATE C/

TM1M0GATEC/TM1M000

Timer 1 Timer 0

TXT0

(3)(6)

Teletext

Register 0

C0 X24 POSN DISPLAY

X24

AUTO

FRAME

DISABLE

HDR

ROLL

DISPLAY

STATUS

ROW

ONLY

DISABLE

FRAME

VPS ON INV ON 00

TXT1

(3)(6)

Teletext

Register 1

C1 EXT PKT

OFF

8−BIT ACQ OFF X26

OFF

FULL

FIELD

FIELD

POLARITYHPOLARITYVPOLARITY

00

SYMBOL NAME

DIRECT

ADDR.

(HEX)

BIT ADDRESS, SYMBOL OR ALTERNATIVE PORT FUNCTION RESET

VALUE

(HEX)

7654321 0

Page 18

1998 Dec 14 18

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

TXT2

(3)(6)

T eletext

Register 2

C2 −

(1)

REQ3 REQ2 REQ1 REQ0 SC2 SC1 SC0 00

TXT3

(3)(6)

T eletext

Register 3

C3 −

(1)

−

(1)

−

(1)

PRD4 PRD3 PRD2 PRD1 PRD0 00

TXT4

(3)(6)

T eletext

Register 4

C4 OSD

BANK

ENABLE

QUAD

WIDTH

ENABLE

EAST/

WEST

DISABLE

DBL HT

B MESH

ENABLE

C MESH

ENABLE

TRANS

ENABLE

SHADOW

ENABLE

00

TXT5

(3)(6)

Teletext

Register 5

C5 BKGND

OUT

BKGND IN COR OUT COR IN TEXT

OUT

TEXT IN PICTURE

ON OUT

PICTURE

ON IN

03

TXT6

(3)(6)

Teletext

Register 6

C6 BKGND

OUT

BKGND IN COR OUT COR IN TEXT

OUT

TEXT IN PICTURE

ON OUT

PICTURE

ON IN

03

TXT7

(3)(6)

Teletext

Register 7

C7 STATUS

ROW TOP

CURSORONREVEAL TOP/

BOTTOM

DOUBLE

HEIGHT

BOX ON24BOX ON

1-23

BOX ON000

TXT8

(3)(6)

T eletext

Register 8

C8 I2C

SELECT

IDS

ENABLE

−

(1)

DISABLE

SPANISH

PKT26

RECEIVE

D

WSS

RECEIVE

D

WSS ON

CVBS0/

CVBS1

00

TXT9

(3)(6)

Teletext

Register 9

C9 CURSOR

FREEZE

CLEAR

MEMORY.

A0 R4 R3 R2 R1 R0 00

TXT10

(3)(6)

Teletext

Register 10

CA −

(1)

−

(1)

C5 C4 C3 C2 C1 C0 00

TXT11

(3)(6)

Teletext

Register 11

CB D7 D6 D5 D4 D3 D2 D1 D0 00

TXT12

(3)(6)

Teletext

Register 12

CC 625/525

SYNC

ROM

VER R4

ROM

VER R3

ROM

VER R2

ROM

VER R1

ROM VERR0TXT ON VIDEO

SIGNAL

QUALITY

0XXXX

X00B

TXT13

(2)(3)

(6)

Teletext

Register 13

B8 BF BE BD BC BB BA B9 B8 00

VPS

RECEIVE

D

PAGE

CLEARIN

G

525

DISPLAY

525 TEXT 625

TEXT

PKT

8/30

FASTEXT TIB

TXT14

(3)(6)

Teletext

Register 14

CD −− −PAGE3 PAGE2 PAGE1 PAGE0 00

SYMBOL NAME

DIRECT

ADDR.

(HEX)

BIT ADDRESS, SYMBOL OR ALTERNATIVE PORT FUNCTION RESET

VALUE

(HEX)

7654321 0

Page 19

1998 Dec 14 19

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

Notes

1. These bits are inactive and must be written to logic 0 for future compatibility.

2. SFRs are bit addressable.

3. SFRs are modified or added to the 80C51 SFRs.

4. This register used for Byte Orientated I

2

C-bus, TXT8.I2C SELECT = 1.

5. This register used for Bit Orientated I2C-bus, TXT8.I2C SELECT = 0.

6. Although the Teletext, WSS and CLUT registers are reset internally by hardware, it is advisable that these registers are explicitly reset by the

software following initial power-up and returning from the standby condition.

TXT15

(3)(6)

Teletext

Register 15

CE −−−−BLOCK3 BLOCK2 BLOCK1 BLOCK0 00

TXT16

(3)(6)

Teletext

Register 16

CF − Y2 Y1 Y0 −−X1 X0 00

TXT17

(3)(6)

Teletext

Register 17

B9 − FORCE

ACQ 1

FORCE

ACQ 0

FORCE

625

FORCE

525

SCREEN

COL2

SCREEN

COL1

SCREEN

COL0

00

WSS1

(3)(6)

WSS

Register 1

BA −−−WSS0 to

WSS3

ERROR

WSS3 WSS2 WSS1 WSS0 00

WSS2

(3)(6)

WSS

Register 2

BB −−−WSS4 to

WSS7

ERROR

WSS7 WSS6 WSS5 WSS4 00

WSS3

(3)(6)

WSS

Register 3

BC WSS11 to

WSS13

ERROR

WSS13 WSS12 WSS11 WSS8 to

WSS10

ERROR

WSS10 WSS9 WSS8 00

CLUT

(3)(6)

CLUT

Register

BD CLUT

ENABLE

CLUT

ADDRESS

B1 or − B0 or − G1 or

ENTRY 3

G0 or

ENTRY 2

R1 or

ENTRY 1

R0 or

ENTRY 0

00

SYMBOL NAME

DIRECT

ADDR.

(HEX)

BIT ADDRESS, SYMBOL OR ALTERNATIVE PORT FUNCTION RESET

VALUE

(HEX)

7654321 0

Page 20

1998 Dec 14 20

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

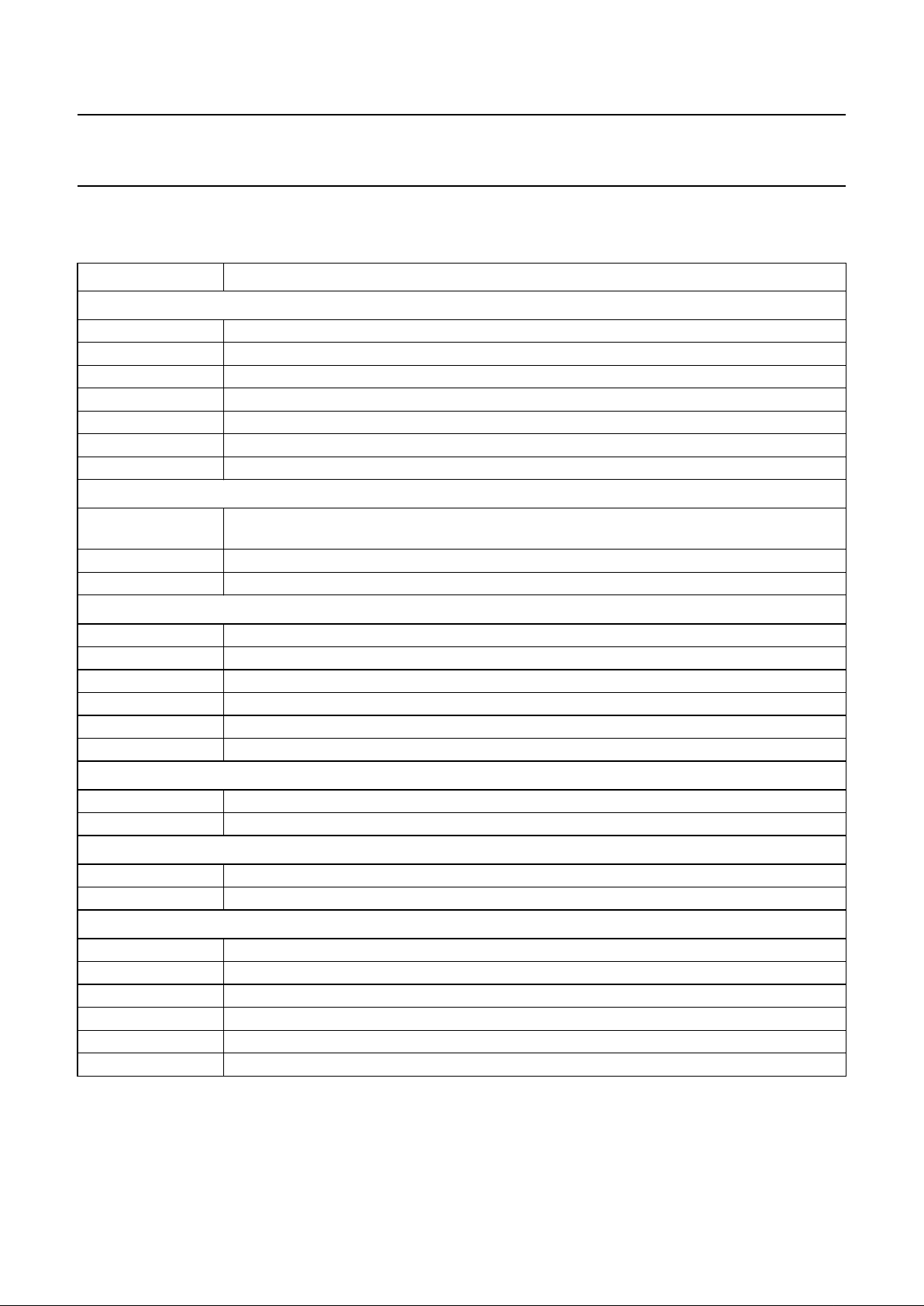

7.4.2 SPECIAL FUNCTION REGISTERS

Table 11 SFRs bit description

REGISTER FUNCTION

Interrupt Enable Register (IE)

EA disable all interrupts (logic 0) or use individual interrupt enable bits (logic 1)

ES1 bit I

2

C-bus interrupt enable (logic 1)

ES2 byte I

2

C-bus interrupt enable (logic 1)

ET1 enable timer 1 overflow interrupt (logic 1)

EX1 enable external interrupt 1 (logic 1)

ET0 enable timer 0 overflow interrupt (logic 1)

EX0 enable external interrupt 0 (logic 1)

Power Control Register (PCON)

ARD AUX-RAM disable bit. Disables the 512 bytes of internal AUX-RAM (logic 1);

all MOVX-instructions access the external data memory

GF1 general purpose flag 1

GF0 general purpose flag 0

Program Status Word (PSW)

CY carry flag

AC auxiliary carry flag

F0 flag 0

RS1,RS0 register bank select control bits

OV overflow flag

P parity flag

6-bit Pulse Width Modulator Control Registers (PWM0 to PWM7)

PWE activate this PWM and take control of respective port pin (logic 1)

PV5 to PV0 binary value sets high time of PWM output

Serial Interface Slave Address Register (S1ADR); note 1

ADR6 to ADR0 I

2

C-bus slave address to which the device will respond

GC enables response to the I

2

C-bus general call address

Serial Interface Control Register (S1CON); note 1

CR2 to CR0 clock rate bits

ENSI I

2

C-bus interface enable

STA start condition flag

STO stop condition flag

SI interrupt flag

AA assert acknowledge flag

Page 21

1998 Dec 14 21

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

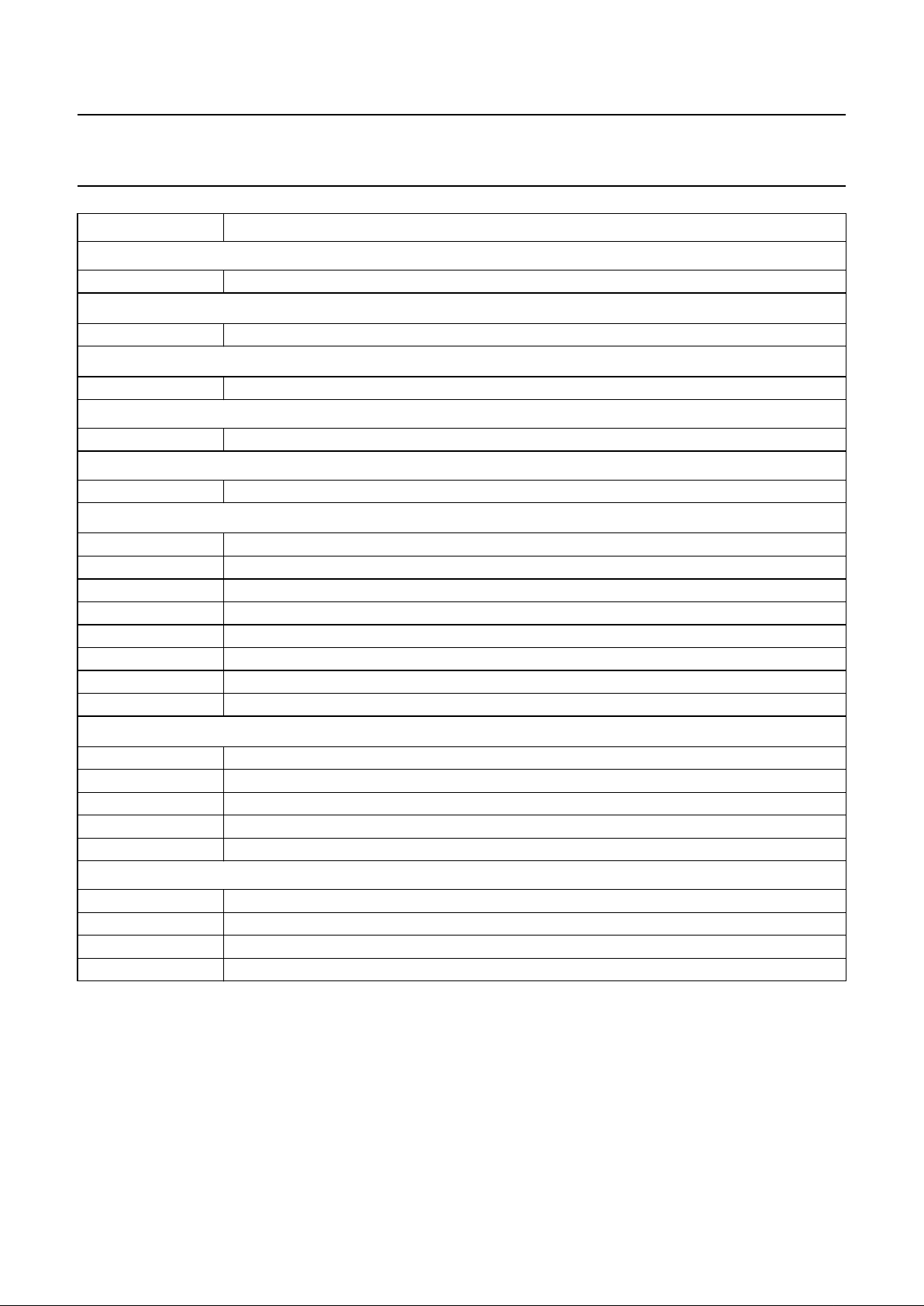

Serial Interface Data Register (S1DAT); note 1

DAT7 to DAT0 I

2

C-bus data

Serial Interface Status Register (S1STA) - READ only; note 1

STAT4 to STAT0 I

2

C-bus interface status

Serial Interface Data Register (S1BIT) - READ; note 2

SDI I

2

C-bus data bit input

Serial Interface Data Register (S1BIT) - WRITE; note 2

SDO I

2

C-bus data bit output

Serial Interface Interrupt Register (S1INT); note 2

SI I2C-bus interrupt flag

Serial Interface Control Register (S1SCS) - READ; note 2

SDI serial data input at SDA

SCI serial clock input at SCL

CLH clock LOW-to-HIGH transition flag

BB bus busy flag

RBF read bit finished flag

WBF write bit finished flag

STR clock stretching enable (logic 1)

ENS enable serial I/O (logic 1)

Serial Interface Control Register (S1SCS) - WRITE; note 2

SDO serial data output at SDA

SCO serial clock output at SCL

CLH clock LOW-to-HIGH transition flag

STR clock stretching enable (logic 1)

ENS enable serial I/O (logic 1)

Software ADC Control Register (SAD)

VHI comparator output indicating that analog input voltage greater than DAC voltage (logic 1)

CH1 and CH0 ADC input channel selection bits; see Table 11

ST initiate voltage comparison (logic 1); this bit is automatically reset to logic 0

SAD7 to SAD4 4 MSBs of DAC input value

REGISTER FUNCTION

Page 22

1998 Dec 14 22

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

Software ADC Control Register (SADB)

SAD3 to SAD0 4 LSBs of DAC input value

Timer/Counter Control Register (TCON)

TF1 Timer 1 overflow flag

TR1 Timer 1 run control bit

TF0 Timer 0 overflow flag

TR0 Timer 0 run control bit

IE1 interrupt 1 edge flag

IT1 interrupt 1 type control bit

IE0 interrupt 0 edge flag

IT0 interrupt 0 type control bit

14-bit PWM MSB Register (TDACH)

PWE activate this 14-bit PWM and take over port pin (logic 1)

TD13 to TD8 6 MSBs of 14-bit number to be output by the 14-bit PWM

14-bit PWM LSB Register (TDACL)

TD7 to TD0 8 LSBs of 14-bit number to be output by the 14-bit PWM

Timer 0 High byte (TH0)

TH07 to TH00 8 MSBs of Timer 0 16-bit counter

Timer 1 High byte (TH1)

TH17 to TH10 8 MSBs of Timer 1 16-bit counter

Timer 0 Low byte (TL0)

TL07 to TL00 8 LSBs of Timer 0 16-bit counter

Timer 1 Low byte (TL1)

TL17 to TL10 8 LSBs of Timer 1 16-bit counter

Timer/Counter Mode Control Register (TMOD)

GATE gating control

C/

T counter or timer selector

M1, M0 mode control bits

REGISTER FUNCTION

Page 23

1998 Dec 14 23

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

Teletext Register 0 (TXT0) - WRITE only

X24 POSN store packet 24 in extension packet memory (logic 0) or page memory (logic 1)

DISPLAY X24 display X24 from page memory (logic 0) or extension packet memory (logic 1)

AUTO FRAME FRAME output switched off automatically if any video displayed (logic 1)

DISABLE HDR

ROLL

disable writing of rolling headers and time into memory (logic 1)

DISPLAY STATUS

ROW ONLY

display row 24 only (logic 1)

DISABLE FRAME FRAME output always LOW (logic 1)

VPS ON enable capture of VPS data (logic 1)

INV ON

(3)

enable capture of inventory page in block 8 (logic 1)

Teletext Register 1 (TXT1) - WRITE only

EXT PKT OFF

(3)

disable decoding of extension packets (logic 1)

8-BIT data in packets 0 to 24 written into memory without error checking (logic 1)

ACQ OFF prevent teletext acquisition section writing to memory (logic 1)

X26 OFF disable automatic processing of packet 26 data (logic 1)

FULL FIELD decode teletext on VBI lines only (logic 0) or decode teletext on any line (logic 1)

FIELD POLARITY VSYNC in first half of the line (logic 0) or second half of the line (logic 1) at start of even field

H POLARITY HSYNC input positive-going (logic 0) or negative-going (logic 1)

V POLARITY VSYNC input positive-going (logic 0) or negative-going (logic 1)

Teletext Register 2 (TXT2) - WRITE only

REQ3 to REQ0

(3)

selects which page is modified by TXT3 page request data

SC2 to SC0 start column at which page request data written to TXT3, page request data is placed

Teletext Register 3 (TXT3) - WRITE only

PRD4 to PRD0 page request data

Teletext Register 4 (TXT4) - WRITE only

OSD BANK

ENABLE

(4)

bank switching of OSD enabled (logic 1)

QUAD WIDTH

ENABLE

(4)

enable quad width characters (logic 1)

EAST/

WEST western languages selected (logic 0) or Eastern languages selected (logic 1)

DISABLE DBL

HGHT

disable display of double height teletext control codes (logic 1) in OSD boxes

B MESH ENABLE enable meshing of area with black background (logic 1)

C MESH ENABLE enable meshing of area with other background colours (logic 1)

TRANS ENABLE set black background to transparent i.e. video is displayed (logic 1)

SHADOW ENABLE enable south-east shadowing (logic 1)

REGISTER FUNCTION

Page 24

1998 Dec 14 24

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

Teletext Register 5 (TXT5) - WRITE only

BKGND OUT background colour displayed outside teletext boxes (logic 1)

BKGND IN background colour displayed inside teletext boxes (logic 1)

COR OUT COR output active outside teletext boxes (logic 1)

COR IN COR output active inside teletext boxes (logic 1)

TEXT OUT text displayed outside teletext boxes (logic 1)

TEXT IN text displayed inside teletext boxes (logic 1)

PICTURE ON OUT video picture displayed outside teletext boxes (logic 1)

PICTURE ON IN video picture displayed inside teletext boxes (logic 1)

Teletext Register 6 (TXT6) - WRITE only

See TXT5 this register has the same meaning as TXT5 but is only invoked if either newsflash (C5) or

subtitle (C6) bit in row 25 of the basic page memory is set

Teletext Register 7 (TXT7) - WRITE only

STATUS ROW TOP display row 24 below (logic 0) or above (logic 1) teletext page

CURSOR ON display cursor at location pointed to by TXT9 and TXT10 (logic 1)

REVEAL display characters in areas with the conceal attribute set (logic 1)

TOP/BOTTOM display rows 0 to 11 (logic 0) or 12 to 23 (logic 1) when the double height bit is set

DOUBLE HEIGHT display each character as twice normal height (logic 1)

BOX ON 24 enable teletext boxes in memory row 24 (logic 1)

BOX ON 1-23 enable teletext boxes in memory rows 1 to 23 (logic 1)

BOX ON 0 enable teletext boxes in memory row0 (logic 1)

Teletext Register 8 (TXT8)

I

2

C SELECT

(2)

select bit I2C-bus (logic 0) or byte I2C-bus (logic 1)

IDS ENABLE

(2)

capture teletext Independent Date Services (logic 1)

DISABLE

SPANISH

(2)

disable special treatment of Spanish packet 26 decoding

PKT 26 RECEIVED set to logic 1 when packet 26 teletext data processed

WSS RECEIVED

(5)

set to logic 1 when wide screen signalling data received

WSS ON

(5)

enable acquisition of wide screen signalling data

CVBS0/CVBS1 select CVBS0 (logic 0) or CVBS1 (logic 1) input to the device

Teletext Register 9 (TXT9) - WRITE only

CURSOR FREEZE locks current cursor position (logic 1)

CLEAR MEMORY write 20H into every location in teletext memory (logic 1)

A0 TXT11 accesses the basic page memory, selected by TXT15 on the 10 page device, (logic 0)

or extension packet memory (logic 1)

R4 to R0 memory row to be accessed by TXT11

REGISTER FUNCTION

Page 25

1998 Dec 14 25

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

Teletext Register 10 (TXT10) - WRITE only

C5 to C0 memory column to be accessed by TXT11

Teletext Register 11 (TXT11)

D7 to D0 data byte written to, or read from teletext memory

Teletext Register 12 (TXT12) - READ only

625/525 SYNC a 625-line CVBS signal (logic 0), or a 525-line CVBS signal (logic 1) is being input

ROM VER R4 to R0 mask programmable identification for character set

TXT ON power has been applied to the teletext hardware (logic 1)

VIDEO SIGNAL

QUALITY

CVBS input can be locked on by the teletext decoder (logic 1)

Teletext Register 13 (TXT13)

VPS RECEIVED set to logic 1 when VPS data is received

PAGE CLEARING set when software requested page clear in progress

525 DISPLAY set to logic 1 when 525-line syncs are driving the display

525 TEXT set to logic 1 when 525-line teletext is received

625 TEXT set to logic 1 when 625-line teletext is received

PKT 8/30 set to logic 1 when packet 8/30 is detected

FASTEXT set to logic 1 when packet X27/0 is detected

TIB text interface busy; logic 1 indicates that TXT registers 0 to 16 cannot currently be accessed

Teletext Register 14 (TXT 14) - WRITE only; note 3

PAGE3 to PAGE0 selects which page to display

Teletext Register 15 (TXT15) - WRITE only; note 3

BLOCK3 to BLOCK0 selects which memory block accessed by TXT9, 10 and 11

Teletext Register 16 (TXT16) - WRITE only

Y2 to Y0 sets vertical position of display area

X1 to X0 sets horizontal position of display area

Teletext Register 17 (TXT17) - Write only

FORCE ACQ0,1 force acquisition mode

FORCE 625 force display to 625-line mode

FORCE 525 force display to 525-line mode

SCREEN COL 2 to 0 defines colour displayed instead of TV picture and black background

REGISTER FUNCTION

Page 26

1998 Dec 14 26

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

Notes

1. Available on SAA5296, SAA5296A, SAA5297, SAA5297A, SAA5496, SAA5497 permanently and SAA5290,

SAA5290A, SAA5291, SAA5291A, SAA5491 when TXT8.I2C SELECT set to logic 1.

2. Available on SAA5290, SAA5290A, SAA5291, SAA5291A and SAA5491.

3. Available on SAA5296, SAA5296A, SAA5297, SAA5297A, SAA5496, SAA5497.

4. Available on SAA5491, SAA5496, SAA5497.

5. Available on SAA5290A, SAA5291A, SAA5296A, SAA5297A, SAA5491, SAA5496, SAA5497.

Wide Screen Signalling Register 1 (WSS1) - READ only; note 5

WSS 0-3 ERROR error flag for bits WSS0 to WSS3

WSS3 to WSS0 signalling bits to define aspect ratio (group 1)

Wide Screen Signalling Register 2 (WSS2) - READ only; note 5

WSS 4-7 ERROR error flag for bits WSS4 to WSS7

WSS7 to WSS4 signalling bits to define enhanced services (group 2)

Wide Screen Signalling Register 3 (WSS3) - READ only; note 5

WSS11-13 ERROR error flag for bits WSS11 to WSS13

WSS13 to WSS11 signalling bits to define reserved elements (group 4)

WSS8-10 ERROR error flag for bits WSS8 to WSS10

WSS10 to WSS8 signalling bits to define subtitles (group 3)

Colour Look-Up Table Register (CLUT) - WRITE only; note 4

CLUT ENABLE enable the colour look-up table (logic 1)

CLUT ADDRESS load CLUT address (logic 1) or CLUT data (logic 0)

B1 most significant BLUE component data

B0 least significant BLUE component data

G1 or ENTRY3 most significant GREEN component data or most significant bit of CLUT address

G0 or ENTRY2 least significant GREEN component data or CLUT address

R1 or ENTRY1 most significant RED component data or CLUT address

R0 or ENTRY0 least significant RED component data or least significant bit of CLUT address

REGISTER FUNCTION

Page 27

1998 Dec 14 27

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

8 TELETEXT DECODER

8.1 Data slicer

The data slicer extracts the digital teletext data from the

incoming analog waveform. This is performed by sampling

the CVBS waveform and processing the samples to

extract the teletext data and clock.

8.2 Acquisition timing

The acquisition timing is generated from a logic level

positive-going composite sync signal VCS. This signal is

generated by a sync separator circuit which adaptively

slices the sync pulses. The acquisition clocking and timing

are locked to the VCS signal using a digital

phase-locked-loop. The phase error in the acquisition

phase-locked-loop is detected by a signal quality circuit

which disables acquisition if poor signal quality is detected.

8.3 Teletext acquisition

This family is capable of acquiring 625-line and 525-line

World System Teletext see

“World System Teletext and

Data Broadcasting System”

. Teletext pages are identified

by seven numbers: magazine (page hundreds), page tens,

page units, hours tens, hours units, minutes tens and

minutes units. The last four digits, hours and minutes, are

known as the subcode, and were originally intended to be

time related, hence their names. A page is requested by

writing a series of bytes into the TXT3 SFR which

corresponds to the number of the page required.

The bytes written into TXT3 are put into a small RAM with

an auto-incrementing address. The start address for the

RAM is set using the TXT2 SFR. Table 12 shows the

contents of the page request RAM.

TXT2.REQ0 to TXT2.REQ3 determine which of the

10 page requests is being modified for a 10 page teletext

decoder. If TXT2.REQ is given a value greater than 09H,

then data written into TXT3 is ignored.

Up to 10 pages of teletext can be acquired on the 10 page

device, when TXT1.EXT PKT OFF is set to logic 1, and up

to 9 pages can be acquired when this bit is set to logic 0.

If the ‘DO CARE’ bit for part of the page number is set to a

logic 0 then that part of the page number is ignored when

the teletext decoder is deciding whether a page being

received off air should be stored or not. For example, if the

‘DO CARE’ bits for the 4 subcode digits are all set to

logic 0s then every subcode version of the page will be

captured.

When the HOLD bit is set to a logic 0 the teletext decoder

will not recognise any page as having the correct page

number and no pages will be captured. In addition to

providing the user requested hold function this bit should

be used to prevent the inadvertent capture of an unwanted

page when a new page request is being made. For

example, if the previous page request was for page 100

and this was being changed to page 234, it would be

possible to capture page 200 if this arrived after only the

requested magazine number had been changed.

The E1 and E0 bits control the error checking which should

be carried out on packets 1 to 23 when the page being

requested is captured. This is described in more detail in

Section 8.5.

For the ten page device, each packet can only be written

into one place in the teletext RAM so if a page matches

more than one of the page requests the data is written into

the area of memory corresponding to the lowest numbered

matching page request.

At power-up each page request defaults to any page, hold

on and error check Mode 0.

Table 12 The contents of the Page request RAM

START

COLUMN

PRD4 PRD3 PRD2 PRD1 PRD0

0 DO CARE

Magazine

HOLD MAG2 MAG1 MAG0

1 DO CARE

Page Tens

PT3 PT2 PT1 PT0

2 DO CARE

Page Units

PU3 PU2 PU1 PU0

3 DO CARE

Hours

Tens

X X HT1 HT0

4 DO CARE

Hours

Units

HU3 HU2 HU1 HU0

5 DO CARE

Minutes

Tens

X MT2 MT1 MT0

6 DO CARE

Minutes

Units

MU3 MU2 MU1 MU0

7X XXE1E0

Page 28

1998 Dec 14 28

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

Table 13 Notation used in Table 12

8.4 Rolling headers and time

When a new page has been requested it is conventional

for the decoder to turn the header row of the display green

and to display each page header as it arrives until the

correct page has been found.

When a page request is changed (i.e. when the TXT3 SFR

is written to) a flag (PBLF) is written into bit 5, column 9,

row 25 of the corresponding block of the page memory.

The state of the flag for each block is updated every TV

line, if it is set for the current display block, the acquisition

section writes all valid page headers which arrive into the

display block and automatically writes an alphanumeric

green character into column 7 of row 0 of the display block

every TV line.

When a requested page header is acquired for the first

time, rows 1 to 23 of the relevant memory block are

cleared to space, i.e. have 20H written into every column,

before the rest of the page arrives. Row 24 is also cleared

if the TXT0.X24 POSN bit is set. If the

TXT1.EXT PKT OFF bit is set the extension packets

corresponding to the page are also cleared.

MNEMONIC DESCRIPTION

MAG Magazine

PT Page Tens

PU Page Units

HT Hours Tens

HU Hours Units

MT Minutes Tens

MU Minutes Units

E Error check mode

The last 8 characters of the page header are used to

provide a time display and are always extracted from every

valid page header as it arrives and written into the display

block.

The TXT0.DISABLE HEADER ROLL bit prevents any data

being written into row 0 of the page memory except when

a page is acquired off air i.e. rolling headers and time are

not written into the memory. The TXT1.ACQ OFF bit

prevents any data being written into the memory by the

teletext acquisition section.

When a parallel magazine mode transmission is being

received only headers in the magazine of the page

requested are considered valid for the purposes of rolling

headers and time. Only one magazine is used even if don’t

care magazine is requested. When a serial magazine

mode transmission is being received all page headers are

considered to be valid.

8.5 Error checking

Before teletext packets are written into the page memory

they are error checked. The error checking carried out

depends on the packet number, the byte number, the error

check mode bits in the page request data and the

TXT1.8 BIT bit.

If an uncorrectable error occurs in one of the Hamming

checked addressing and control bytes in the page header

or in the Hamming checked bytes in packet 8/30, bit 4 of

the byte written into the memory is set, to act as an error

flag to the software. If uncorrectable errors are detected in

any other Hamming checked data the byte is not written

into the memory.

Page 29

1998 Dec 14 29

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

Fig.5 Error checking.

handbook, full pagewidth

MGK465

3938373635343332313029282726252423222120191817161514131211109876543210

'8-bit' bit = 0

3938373635343332313029282726252423222120191817161514131211109876543210

'8-bit' bit = 1

Packet X/0

3938373635343332313029282726252423222120191817161514131211109876543210

'8-bit' bit = 0, error check mode = 0

3938373635343332313029282726252423222120191817161514131211109876543210

'8-bit' bit = 0, error check mode = 1

3938373635343332313029282726252423222120191817161514131211109876543210

'8-bit' bit = 0, error check mode = 2

3938373635343332313029282726252423222120191817161514131211109876543210

'8-bit' bit = 0, error check mode = 3

3938373635343332313029282726252423222120191817161514131211109876543210

'8-bit' bit = 1

Packet X/1-23

3938373635343332313029282726252423222120191817161514131211109876543210

'8-bit' bit = 0

3938373635343332313029282726252423222120191817161514131211109876543210

'8-bit' bit = 1

Packet X/24

3938373635343332313029282726252423222120191817161514131211109876543210

Packet X/27/0

3938373635343332313029282726252423222120191817161514131211109876543210

Packet 8/30/0,1

3938373635343332313029282726252423222120191817161514131211109876543210

8-bit

data

Packet 8/30/2,3,4-15

odd parity

checked

8/4 Hamming

checked

Page 30

1998 Dec 14 30

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

8.6 Memory organisation of SAA5296/7,

SAA5296/7A and SAA5496/7

The teletext memory is divided into 10 blocks. Normally,

when the TXT1.EXT PKT OFF bit is logic 0, each of blocks

0 to 8 contains a teletext page arranged in the same way

as the basic page memory (see Fig.6) of the page device

and block 9 contains extension packets (see Fig.7).

When the TXT1.EXT PKT OFF bit is logic 1, no extension

packets are captured and block 9 of the memory is used to

store another page.

The number of the memory block into which a page is

written corresponds to the page request number which

resulted in the capture of the page.

Packet 0, the page header, is split into 2 parts when it is

written into the text memory. The first 8 bytes of the header

contain control and addressing information. They are

Hamming decoded and written into columns 0 to 7 of

row 25 (see Table 15). Row 25 also contains the

magazine number of the acquired page and the PBLF flag

but the last 14 bytes are unused and may be used by the

software, if necessary. The Hamming error flags are set if

the on-board 8/4 Hamming checker detects that there has

been an uncorrectable (2 bit) error in the associated byte.

It is possible for the page to still be acquired if some of the

page address information contains uncorrectable errors if

that part of the page request was a ‘don’t care’. There is no

error flag for the magazine number as an uncorrectable

error in this information prevents the page being acquired.

The interrupted sequence (C9) bit is automatically dealt

with by the acquisition section so that rolling headers do

not contain discontinuities in the page number sequence.

The magazine serial (C11) bit indicates whether the

transmission is a serial or a parallel magazine

transmission. This affects the way the acquisition section

operates and is dealt with automatically.

The newsflash (C5), subtitle (C6), suppress header (C7),

inhibit display (C10) and language control (C12 to 14) bits

are dealt with automatically by the display section,

described below.

The update (C8) bit has no effect on the hardware. The

remaining 32 bytes of the page header are parity checked

and written into columns 8 to 39 of row 0. Bytes which

pass the parity check have the MSB set to a logic 0 and

are written into the page memory. Bytes with parity errors

are not written into the memory.

Table 14 Notation used in Table 15

MNEMONIC DESCRIPTION

MAG Magazine

PT Page Tens

PU Page Units

HT Hours Tens

HU Hours Units

MT Minutes Tens

MU Minutes Units

Table 15 The data in row 25 of the basic page memory

COL BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

0000Hamming error PU3 PU2 PU1 PU0

1000Hamming error PT3 PT2 PT1 PT0

2000Hamming error MU3 MU2 MU1 MU0

3000Hamming error C4 MT2 MT1 MT0

4000Hamming error HU3 HU2 HU1 HU0

5000Hamming error C6 C5 HT1 HT0

6000Hamming error C10 C9 C8 C7

7000Hamming error C14 C13 C12 C11

8000

FOUND 0 MAG2 MAG1 MAG0

9 0 0 PBLF 0 0000

10 to 23 −−−unused −−−−

Page 31

1998 Dec 14 31

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

Fig.6 Packet storage locations.

(1) If ‘X24 Posn’ bit = 1.

(2) VPS data block 9, unused in blocks 0 to 8.

handbook, full pagewidth

Row 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

0678

9023

39

Packet X/0

Basic Page Blocks (0 to 8/9)

OSD only

Packet X/1

Packet X/2

Packet X/3

Packet X/4

Packet X/5

Packet X/6

Packet X/7

Packet X/8

Packet X/9

Packet X/10

Packet X/11

Packet X/12

Packet X/13

Packet X/14

Packet X/15

Packet X/16

Packet X/17

Packet X/18

Packet X/19

Packet X/20

Packet X/21

Packet X/22

Packet X/23

Packet X/24

(1)

MGK466

Control Data VPS Data

(2)

Page 32

1998 Dec 14 32

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

Fig.7 Extension packet storage locations.

(1) If ‘X24 Position’ bit = 0.

handbook, full pagewidth

MGD163

0

1

2

3

4

5

6

7

8

9

9230

10

11

12

13

14

15

20

21

22

23

24

25

16

17

18

19

Row

Packet X/24 for page in block 0

(1)

Packet X/24 for page in block 1

(1)

Packet X/27/0 for page in block 0

Packet X/27/0 for page in block 1

Packet X/24 for page in block 2

(1)

Packet X/27/0 for page in block 2

Packet X/24 for page in block 3

(1)

Packet X/27/0 for page in block 3

Packet X/24 for page in block 4

(1)

Packet X/27/0 for page in block 4

Packet X/24 for page in block 5

(1)

Packet X/27/0 for page in block 5

Packet X/24 for page in block 6

(1)

Packet X/27/0 for page in block 6

Packet X/24 for page in block 7

(1)

Packet X/27/0 for page in block 7

Packet X/24 for page in block 8

(1)

Packet X/27/0 for page in block 8

Packet 8/30/0.1

Packet 8/30/2.3

Packet 8/30/4-15

VPS Data

Extension Packet Block (9)

Page 33

1998 Dec 14 33

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

8.7 Inventory page

If the TXT0.INV ON bit is a logic 1, memory block 8 is used

as an inventory page.The inventory page consists of two

tables: the Transmitted Page Table (TPT) and the Subtitle

Page Table (SPT).

In each table, every possible combination of the page tens

and units digit, 00H to FFH, is represented by a byte.

Each bit of these bytes corresponds to a magazine number

so each page number, from 100 to 8FF, is represented by

a bit in the table.

The bit for a particular page in the TPT is set when a page

header is received for that page. The bit in the SPT is set

when a page header for the page is received which has the

‘subtitle’ page header control bit (C6) set.

Before the inventory page is enabled the software must

ensure that page request 8 is put on hold.

Fig.8 Table organisation.

handbook, full pagewidth

x00

x01

x02

x03

x04

x05

x06

x07

x08

x09

x0a

x0b

x0c

x0d

x0e

x0f

x10

x11

x12

x13

x14

x15

x16

x17

x18

x19

x1a

x1b

x1c

x1d

x1e

x1f

x20

x21

x22

x23

x24

x25

x26

x27

x28

x29

x2a

x2b

x2c

x2d

x2e

x2f

x30

x31

x32

x33

x34

x35

x36

x37

x38

x39

x3a

x3b

x3c

x3d

x3e

x3f

xc0

xc1

xc2

xc3

xc4

xc5

xc6

xc7

xc8

xc9

xca

xcb

xcc

xcd

xce

xcf

xd0

xd1

xd2

xd3

xd4

xd5

xd6

xd7

xd8

xd9

xda

xdb

xdc

xdd

xde

xdf

xe0

xe1

xe2

xe3

xe4

xe5

xe6

xe7

xe8

xe9

xea

xeb

xec

xed

xee

xfef

xf0

xf1

xf2

xf3

xf4

xf5

xf6

xf7

xf8

xf9

xfa

xfb

xfc

xfd

xfe

xff

7xx

bit

7

Bytes in the table

Bytes in each byte

column

row n

n + 1

n + 6

n + 7

0

0

MGD160

81624 3239

6xx

5xx

4xx

3xx

2xx 1xx

8xx

Page 34

1998 Dec 14 34

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

Fig.9 Inventory page organisation.

handbook, full pagewidth

MGD165

0

1

2

3

4

5

6

7

8

9

230

039

10

11

12

13

14

15

20

21

22

23

24

25

16

17

18

19

Row

Unused

Unused

Unused

Unused

Unused

Unused

Unused

Unused

Unused

Transmitted

Pages

Table

Subtitle

Pages

Table

Page 35

1998 Dec 14 35

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

8.8 Memory organisation of SAA5290, SAA5290A, SAA5291, SAA5291A and SAA5491

Teletext packets each contain 40 bytes of data and one packet is stored in each row of the text memory, the row used

being dependent on the packet number.

Packet 0, the page header, is split into 2 parts when it is written into the text memory. The first 8 bytes of the header

contain control and addressing information. They are Hamming decoded and written into columns 0 to 7 of row 25.

handbook, full pagewidth

Row 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

0678

9023

39

Packet X/0

Basic Page Block

OSD only

Packet X/1

Packet X/2

Packet X/3

Packet X/4

Packet X/5

Packet X/6

Packet X/7

Packet X/8

Packet X/9

Packet X/10

Packet X/11

Packet X/12

Packet X/13

Packet X/14

Packet X/15

Packet X/16

Packet X/17

Packet X/18

Packet X/19

Packet X/20

Packet X/21

Packet X/22

Packet X/23

Packet X/24

(1)

MGK467

Control Data VPS Data

aw/ag

Row 0

1

2

Packet X/24

(2)

Extension Packet Memory

Packet X/27/0

Packet 8/30

Fig.10 Packet storage locations.

(1) If X24 Position bit = 1.

(2) If X24 Position bit = 0.

Page 36

1998 Dec 14 36

Philips Semiconductors Preliminary specification

Economy teletext and TV microcontrollers SAA5x9x family

8.9 Packet 26 processing

One of the uses of packet 26 is to transmit characters

which are not in the basic teletext character set. The family

automatically decodes packet 26 data and, if a character

corresponding to that being transmitted is available in the

character set, automatically writes the appropriate

character code into the correct location in the teletext

memory. This is not a full implementation of the packet 26

specification allowed for in level 2 teletext, and so is often

referred to as level 1.5.

By convention, the packets 26 for a page are transmitted

before the normal packets. To prevent the default

character data overwriting the packet 26 data the device

incorporates a mechanism which prevents packet 26 data

from being overwritten. On the SAA5291,SAA5291A and

SAA5491 devices this mechanism is disabled when the

Spanish national option is detected as the Spanish

transmission system sends even parity (i.e. incorrect)

characters in the basic page locations corresponding to

the characters sent via packet 26 and these will not

overwrite the packet 26 characters anyway. The special

treatment of Spanish national option is prevented if

TXT12.ROM VER R4 is logic 0 or if the TXT8.DISABLE

SPANISH is set.

Packet 26 data is processed regardless of the

TXT1.EXT PKT OFF bit, but setting theTXT1.X26 OFF

disables packet 26 processing.

The TXT8.Pkt 26 received bit is set by the hardware

whenever a character is written into the page memory by

the packet 26 decoding hardware. The flag can be reset by

writing a logic 0 into the SFR bit.

8.10 VPS

When the TXT0. VPS ON bit is set, any VPS data present

on line 16, field 0 of the CVBS signal at the input of the

teletext decoder is error checked and stored in row 25,

block 0 for SAA5291, SAA5291A, SAA5491 and row 25,

block 9 for SAA5296/7, SAA5296/7A, SAA5496/7 of the

basic page memory. The device automatically detects

whether teletext or VPS is being transmitted on this line

and decodes the data appropriately.

Each VPS byte in the memory consists of 4 bi-phase

decoded data bits (bits 0 to 3), a bi-phase error flag (bit 4)

and three 0s (bits 5 to 7).

The TXT13.VPS Received bit is set by the hardware

whenever VPS data is acquired. The flag can be reset by

writing a logic 0 into the SFR bit. Full details of the VPS

system can be found in

“Specification of the Domestic

Video Programme Delivery Control System (PDC); EBU

Tech. 3262-E”

.

Table 16 VPS data storage

ROW

COLUMN