Page 1

INTEGRATED CIRCUITS

DATA SH EET

SAA4700T

VPS dataline processor

Preliminary specification

File under Integrated Circuits, IC02

March 1991

Page 2

Philips Semiconductors Preliminary specification

VPS dataline processor SAA4700T

FEATURES

• Adaptive sync slicer with buffered composite sync

output VCS

• Adaptive data slicer

• Data rate clock regenerator

• Field selection and line 16 decoding

• Startcode and biphase check

• Data valid output

• Storage of data line information in a 40 bit register bank

• I2C-bus transmission

GENERAL DESCRIPTION

The SAA4700T is a bipolar integrated circuit designed for

use in dataline receivers and incorporates a dataline slicer

and decoder. The slicer extracts the dataline signal from

the video signal and regenerates the data clock. It also

provides signals for the decoder in order to decode the

binary data that is transmitted in line 16 of every first field

of the composite video signal (video programming signal

and video recording programming by Teletext, VPS and

VPT systems). The decoded information out of words 5

and 11 to 14 is accessed via the built-in I2C-bus interface.

This information then can be used for programming a

video cassette recorder in order to start and stop a

recording of a television program at the correct aligned

time, regardless of a delay or extension in the transmission

time of the required program.

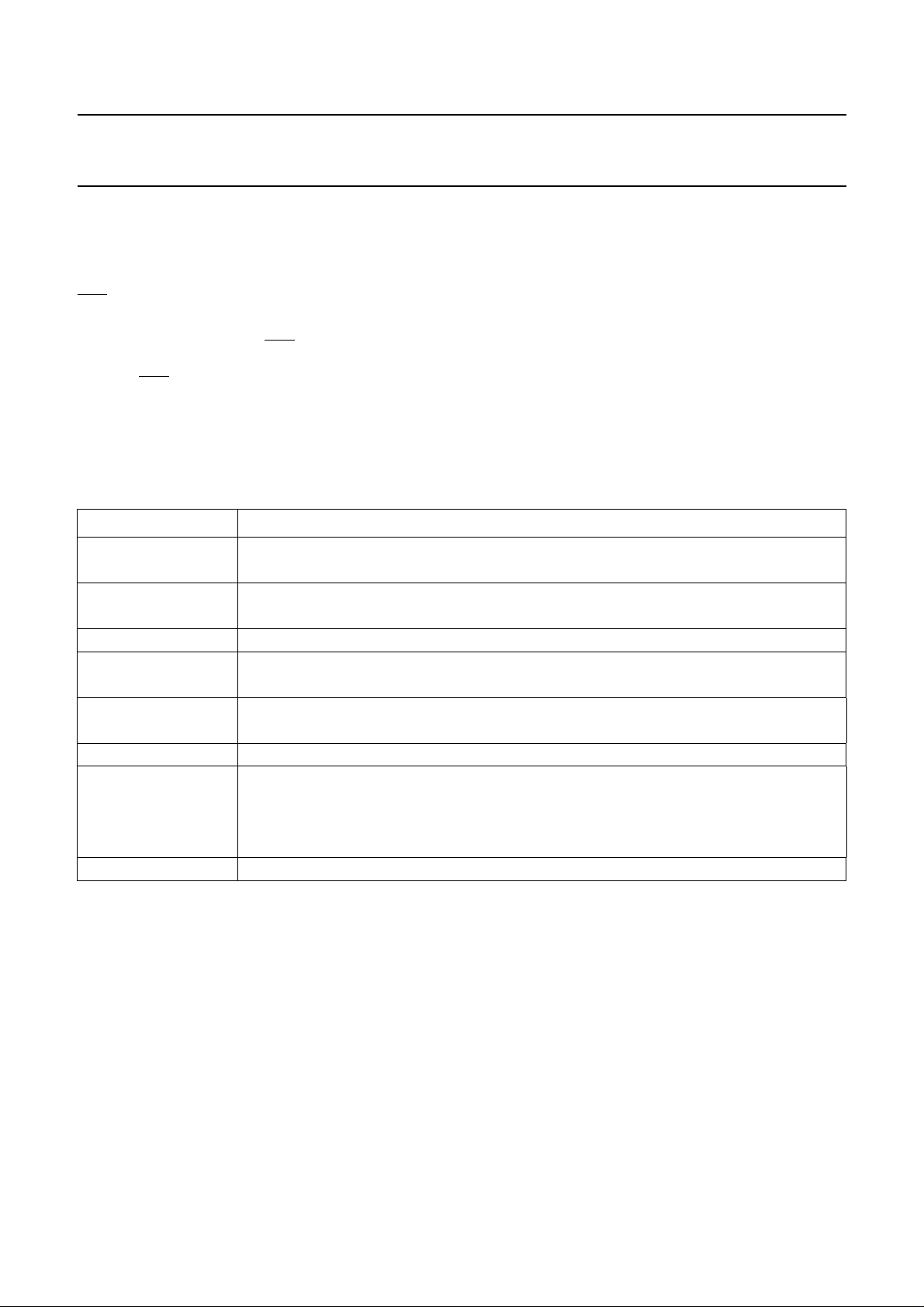

QUICK REFERENCE DATA

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V

P

I

P

V

i CVBS

supply voltage (pins 17 and 18) 4.5 5 5.5 V

total supply current − 18 23 mA

CVBS input signal sync-to-white

0.5 1 1.4 V

(peak-to-peak value)

T

amb

operating ambient temperature 0 −+70 °C

ORDERING AND PACKAGE INFORMATION

EXTENDED

TYPE NUMBER

PINS PIN POSITION MATERIAL CODE

PACKAGE

SAA4700T 20 mini-pack plastic SOT163A

Note

1. SOT163-1; 1996 November 13.

March 1991 2

(1)

Page 3

Philips Semiconductors Preliminary specification

VPS dataline processor SAA4700T

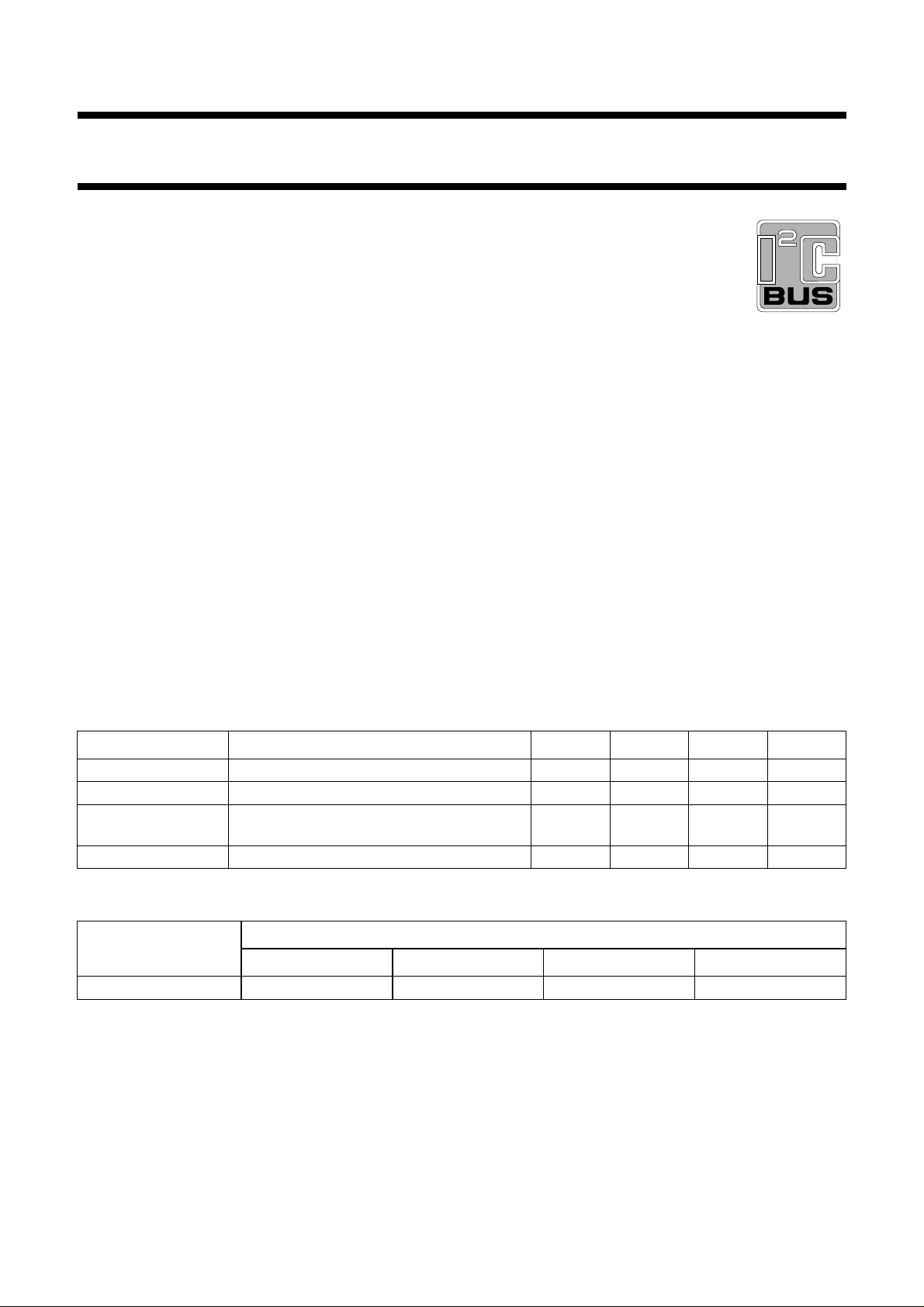

handbook, full pagewidth

4.7 nF

CVBS

470 pF

1 nF

4.7

kΩ

75 kΩ

(2%)

to V

P

4.7 nF

22

nF

2

SYNC

SEPARATOR

SAA4700T

1

15

19

DATA

SLICER

REGENERATOR

PLL WITH

5 MHz VCO AND

PHASE DETECTOR

CSO

0.1

µF

5 6 12 13 8

FIELD SELECTOR

LINE 16 DECODER

line 16

data

CLOCK

VCS

16 3 4 17 18 11

(test line 16)

INPUT

CONTROLLER

TIME BASE

DAV

OUTPUT

CONTROLLER

data

4

6

REFERENCE

POWER-ON RESET

I2C-BUS

CONTROL

5

40 BIT DATA

REGISTER

40 BIT

DATA LATCH

MULTIPLEXER

VOLTAGES

8

AD = LOW

external

reset

9

SCL

10

SDA

7

n.c.

14

n.c.

20

n.c.

8.2 kΩ

clock pulse

Fig.1 Block diagram and test circuit.

FUNCTIONAL DESCRIPTION

Dataline 16

The information in dataline 16 consists of fifteen 8-bit

words; the total information content is shown in Table 1;

and the organization of transmitted bytes is shown in

Table 2.

Out of the fifteen possible 8-bit words the SAA4700T

extracts words 5 and 11 to 14. The contents of these words

2

can be read via the built-in I

C-bus interface. The circuit is

fully transparent, thus each bit is transferred without

modification with only the sequence of words being

changed. Words 11 to 14 are transmitted first followed by

word 5.

By evaluating the sliced sync signal the circuit can identify

the beginning of dataline 16 in the first field. The dataline

decoder stage releases the start code detector. When a

0.1 µF

+5 V

MGH128

V

P

correct start code is detected (for timing of start code

detection see Fig.3) words 5 and 11 to 14 are decoded,

checked for biphase errors and stored in a register bank. If

no biphase error has occurred, the contents of the register

bank are transferred to a second register bank by the data

valid control signal. If the system has been addressed, this

transfer will be delayed until the next start or stop condition

of the I2C-bus has been received.

The last bit of correct information on the dataline remains

available until it is read via the I2C-bus. Once the stored

information has been read it is considered to be no longer

valid and the internal new data flag is reset. Subsequently,

if the circuit is addressed, the only VPS data that will be

sent back is “FFF to F”. The same conditions apply after

power-up when no data can be read out. New data is

available after reception of another error-free dataline 16.

March 1991 3

Page 4

Philips Semiconductors Preliminary specification

VPS dataline processor SAA4700T

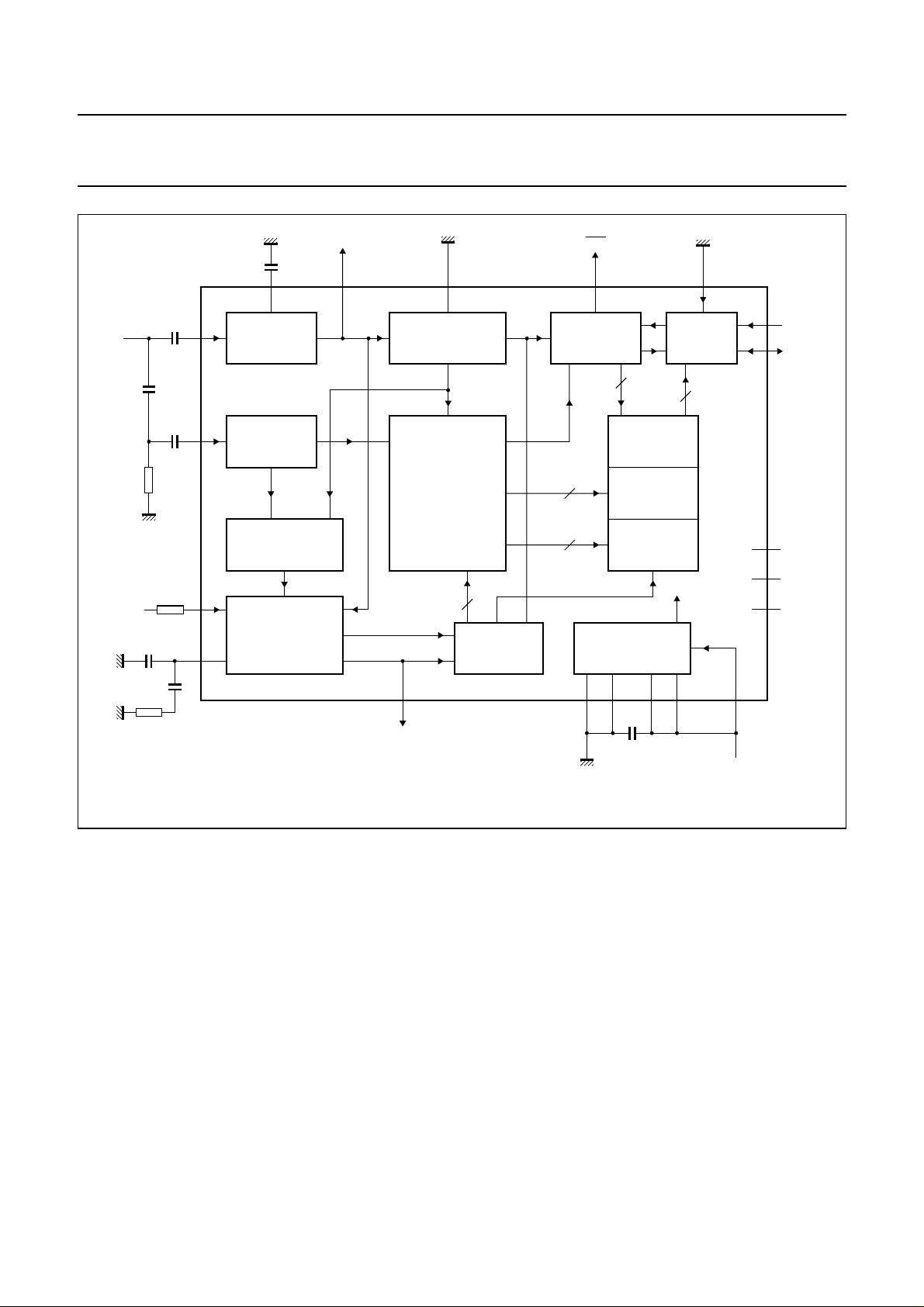

PINNING

SYMBOL PIN DESCRIPTION

CVBS 1 video signal input (CVBS from TV)

SYNC 2 sync amplitude input (CVBS from TV)

GND1 3 analog ground (0 V)

GND2 4 digital ground (0 V)

C

black

5 capacitor for black level

CSO 6 composite sync output

n.c. 7 not connected

AD 8 address set input

2

SCL 9 I

SDA 10 I

C-bus clock line

2

C-bus data line

RS 11 reset input active LOW

TP 12 test point for line 16 decoder

DAV 13 data available output active LOW

n.c. 14 not connected

R

osc

15 oscillator resistor for frequency

adjustment

CP 16 test point clock pulse

V

P1

V

P2

C

ph

17 +5 V supply voltage (digital part)

18 +5 V supply voltage (analog part)

19 capacitor of phase detector

n.c. 20 not connected

PIN CONFIGURATION

handbook, halfpage

CVBS

SYNC

GND1

GND2

C

black

CSO

SCL

SDA

n.c.

AD

1

2

3

4

5

6

7

8

9

10

Fig.2 Pin configuration.

SAA4700T

MBH797

n.c.

20

C

19

ph

V

18

P2

V

17

P1

CP

16

R

15

osc

n.c.

14

DAV

13

TP

12

RS

11

External reset

The circuit provides an internal power-on reset. When

using this facility pin 11 should be connected to VP or, if

external reset (RESET = LOW) is to be used pin 11 should

be prepared by connecting pin 11 via a 10 kΩ pull-up

resistor to VP.

Reset forces the following:

• I2C-bus not to acknowledge

• DAV output to go HIGH (pin 13)

• I2C-bus transfer register to “FFF”

March 1991 4

CVBS input

The CVBS signal is applied to the sync separator (pin 2)

via a decoupling capacitor and to the data slicer (pin 1) via

an RC high-pass filter. To enable proper storage of the

sync value in the decoupling capacitor, the sync generator

output resistance should not exceed 1 kΩ.

Black level

The capacitor connected to pin 5 stores the black level

value for the adaptive sync slicer.

Page 5

Philips Semiconductors Preliminary specification

VPS dataline processor SAA4700T

Composite sync output (CSO)

A composite sync output signal for customer application is

provided (pin 6).

DAV output

The data available output pin 13 is set LOW after an error

free data line 16 is received. DAV returnes to HIGH after

the beginning of the next first field. If no valid data is

available DAV remains HIGH.

A short duration pulse of 1 µs (Fig.5) is inserted at the

beginning of dataline 16; it will ensure that a HIGH-to-LOW

transmission occurs which can then be used for triggering.

Table 1 Information per word in dataline 16

WORD NUMBER CONTENT

1 run in

2 start code

3 program source identification (binary coded)

4 program source identification (ASCII sequential)

5 sound and VTR control information

6 program/test picture identification

7 internal information exchange

8

9

10 messages/commands

11

12

13

14

15 reserve

address assignment of signal distribution

VTR control / information

5 MHz VCO and phase detector

The resistor connected between pin 15 and V

determines the current into the voltage controlled

oscillator. The RC network connected to pin 19 acts as a

low-pass filter for the phase detector.

Power supply

To prevent crosscoupling the circuit is provided with

separate ground and supply pins for analog and digital

parts (pins 3, 4, 17 and 18).

P2

March 1991 5

Page 6

Philips Semiconductors Preliminary specification

VPS dataline processor SAA4700T

Table 2 VTR control information of dataline 16

VTR CONTROL INFORMATION

Word

number

Bit number X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X

Label binary

Word 5: AD

Bit1 Bit2 Status

0 0 2-channel Special system code

0 1 Mono

System

status code

1 0 Stereo 1 X 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 NC...NC PC...PC

1 1 2-channel

511121314

180781516232431

Day Month Hour Minute Nation Progr.

(1)

source

Pause

code

Interrupt

code

Note

1. address range; NC = nation code; PC = program source code; X = 0 or 1 (bit)

Bit3 Bit4 Status 1 X 0 0 0 0 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 NC...NC PC...PC

1 0 free

0 1 free

1 X 0 0 0 0 0 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 NC...NC PC...PC

March 1991 6

Page 7

Philips Semiconductors Preliminary specification

VPS dataline processor SAA4700T

handbook, full pagewidth

data to controller

start code pulse

biphase error pulse

(ignored in word 2)

clock signal

to time base

0.2

µs

101001011011010101010

error

Fig.3 Timing diagram of start code detection.

word 3start code (word 2)run in (word 1)

1

0

MEH097

handbook, full pagewidth

white level

sync level

1 V

0.7 V

12.5 ±1.5

µs

Fig.4 Timing diagram of dataline 16; modulation depth 71.4%.

March 1991 7

48 µs

0.5 V ±5%

MEH098

Page 8

Philips Semiconductors Preliminary specification

VPS dataline processor SAA4700T

handbook, full pagewidth

DAV output

start code

latch pulse

word 11

latch pulse

word 14

latch pulse

CVBS

input

line 16

pulse

word 5

12.5 µs

1 µs

word 1

word 2

word 3

word 4

word 5

64 µs

word 6

word 7

48 µs

word 8

word 9

word 10

word 11

word 12

word 13

word 14

word 15

MEH096

Fig.5 Timing diagram of the data available output and word latch pulses.

March 1991 8

Page 9

Philips Semiconductors Preliminary specification

VPS dataline processor SAA4700T

LIMITING VALUES

In accordance with the Absolute Maximum System (IEC 134).

Ground pins 3 and 4 as well as supply pins 17 and 18 tied together.

SYMBOL PARAMETER MIN. MAX. UNIT

V

P1

V

P2

T

stg

T

amb

THERMAL RESISTANCE

SYMBOL PARAMETER MIN. MAX. UNIT

R

th j-a

CHARACTERISTICS

V

P1=VP2

=5V; T

unless otherwise specified.

supply voltage (pin 17) −0.5 6.0 V

supply voltage (pin 18) −0.5 6.0 V

storage temperature range −20 125 °C

operating ambient temperature range 0 +70 °C

from junction to ambient in free air − 130 K/W

=25°C; CVBS signal according to VPS and VPT standard and measurements taken in Fig.1,

amb

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

, V

V

P1

P2

I

P

supply voltages (pins 17 and 18) 4.5 5 5.5 V

total supply current I17+ I

18

− 18 23 mA

CVBS and sync inputs (pins 1 and 2)

V

i CVBS

CVBS input signal (peak-to-peak value) sync-to-white

0.5 1 1.4 V

note 1; Fig.4

V

i data

data input signal

line 16; Fig.4 250 500 700 mV

(peak-to-peak value, pin 1)

V

i sync

sync input signal

100 − 600 mV

(peak-to-peak value, pin 2)

R

S

source resistance −−1kΩ

Composite sync output (pin 6)

V

OL

V

OH

I

OL

I

OH

t

d

DAV output (pin 13)

V

OL

V

OH

I

OL

I

OH

output voltage LOW −−0.4 V

output voltage HIGH 2.4 −−V

output current LOW −−200 µA

output current HIGH −−−500 µA

sync separator delay time − 0.3 −µs

note 2

output voltage LOW −−0.4 V

output voltage HIGH 2.4 −−V

output current LOW −−500 µA

output current HIGH − 0.01 1 µA

March 1991 9

Page 10

Philips Semiconductors Preliminary specification

VPS dataline processor SAA4700T

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

SCL and SDA (pins 9 and 10)

V

IL

V

IH

I

I

C

I

V

O ACK

t

r

t

f

t

p L

t

p H

SCL clock frequency −−100 kHz

AD set input (pin 8)

V

IL

V

IH

RESET input (pin 11)

V

IL

V

IH

I

IL

I

IH

Notes

1. With standard sync and data amplitude of 68% to 75% black-white.

2. If the open collector output DAV is used, a pull-up resistor to VP1 is necessary.

input voltage LOW −−1.5 V

input voltage HIGH 3 −−V

input current 0.9V

P

−−±10 µA

input capacitance −−10 pF

output voltage during acknowledge

IOL= 3 mA −−0.4 V

on pin 10

rise time −−1µs

fall time −−0.3 µs

pulse duration LOW 4.7 −−µs

pulse duration HIGH 4.0 −−µs

note 2

input voltage LOW address 23H 0 − 0.4 V

input voltage HIGH address 21H 2.4 − V

P

V

note 2

input voltage LOW reset active −−0.4 V

input voltage HIGH reset non-active 2.4 −−V

input current LOW −−−10 µA

input current HIGH − 0.01 1 µA

March 1991 10

Page 11

Philips Semiconductors Preliminary specification

VPS dataline processor SAA4700T

handbook, full pagewidth

I2C-BUS FORMAT

V

CVBS

P

+5 V

75 kΩ

(2%)

DAV

n.c.

13

7910

8

0.1

µF

n.c.

CSO SCL SDA

470

pF

4.7

nF

4.7

nF

0.1 µF

SAA4700T

22

nF

8.2 kΩ

n.c.

20 19 18 17 16 15 14 12 11

123456

1 nF

4.7 kΩ

Fig.6 Application circuit.

MEH136

S SLAVE ADDRESS A DATA A DATA A DATA A DATA A DATA P

S = start condition

SLA VE ADDRESS = 0010 0001 or 0010 0011 for set input AD = HIGH respectively LOW on pin 8

(the circuit is only a slave transmitter)

A = acknowledge, generated by the slave or the master

DATA = five data bytes, see words in Table 1

P = stop condition respectively non-acknowledge by the microcontroller

2

Remarks to I

C-bus transmission

• the MSB of each word is transmitted first

• there is no restriction on the number of words to be transmitted, but if more than five words are requested, the following

content will be “FF” continuously.

• Normally every dataline transmission has to be ended with STOP condition by non-acknowledge of the controller.

March 1991 11

Page 12

Philips Semiconductors Preliminary specification

VPS dataline processor SAA4700T

PACKAGE OUTLINE

SO20: plastic small outline package; 20 leads; body width 7.5 mm

D

c

y

Z

20

pin 1 index

1

e

11

A

2

10

w M

b

p

SOT163-1

E

H

E

Q

A

1

L

p

L

detail X

(A )

A

X

v M

A

A

3

θ

0 5 10 mm

scale

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

mm

OUTLINE

VERSION

SOT163-1

A

max.

2.65

0.10

A

0.30

0.10

0.012

0.004

A

1

A3b

2

2.45

0.25

2.25

0.096

0.01

0.089

IEC JEDEC EIAJ

075E04 MS-013AC

0.49

0.36

0.019

0.014

p

0.32

0.23

0.013

0.009

UNIT

inches

Note

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

(1)E(1) (1)

cD

13.0

7.6

7.4

0.30

0.29

1.27

0.050

12.6

0.51

0.49

REFERENCES

March 1991 12

eHELLpQ

10.65

10.00

0.419

0.394

1.4

0.055

1.1

0.4

0.043

0.016

1.1

1.0

0.043

0.039

PROJECTION

0.25

0.25 0.1

0.01

0.01

EUROPEAN

ywv θ

Z

0.9

0.4

8

0.004

ISSUE DATE

0.035

0.016

95-01-24

97-05-22

0

o

o

Page 13

Philips Semiconductors Preliminary specification

VPS dataline processor SAA4700T

SOLDERING

Introduction

There is no soldering method that is ideal for all IC

packages. Wave soldering is often preferred when

through-hole and surface mounted components are mixed

on one printed-circuit board. However, wave soldering is

not always suitable for surface mounted ICs, or for

printed-circuits with high population densities. In these

situations reflow soldering is often used.

This text gives a very brief insight to a complex technology.

A more in-depth account of soldering ICs can be found in

“IC Package Databook”

our

Reflow soldering

Reflow soldering techniques are suitable for all SO

packages.

Reflow soldering requires solder paste (a suspension of

fine solder particles, flux and binding agent) to be applied

to the printed-circuit board by screen printing, stencilling or

pressure-syringe dispensing before package placement.

Several techniques exist for reflowing; for example,

thermal conduction by heated belt. Dwell times vary

between 50 and 300 seconds depending on heating

method. Typical reflow temperatures range from

215 to 250 °C.

Preheating is necessary to dry the paste and evaporate

the binding agent. Preheating duration: 45 minutes at

45 °C.

(order code 9398 652 90011).

Wave soldering

Wave soldering techniques can be used for all SO

packages if the following conditions are observed:

• A double-wave (a turbulent wave with high upward

pressure followed by a smooth laminar wave) soldering

technique should be used.

• The longitudinal axis of the package footprint must be

parallel to the solder flow.

• The package footprint must incorporate solder thieves at

the downstream end.

During placement and before soldering, the package must

be fixed with a droplet of adhesive. The adhesive can be

applied by screen printing, pin transfer or syringe

dispensing. The package can be soldered after the

adhesive is cured.

Maximum permissible solder temperature is 260 °C, and

maximum duration of package immersion in solder is

10 seconds, if cooled to less than 150 °C within

6 seconds. Typical dwell time is 4 seconds at 250 °C.

A mildly-activated flux will eliminate the need for removal

of corrosive residues in most applications.

Repairing soldered joints

Fix the component by first soldering two diagonallyopposite end leads. Use only a low voltage soldering iron

(less than 24 V) applied to the flat part of the lead. Contact

time must be limited to 10 seconds at up to 300 °C. When

using a dedicated tool, all other leads can be soldered in

one operation within 2 to 5 seconds between

270 and 320 °C.

March 1991 13

Page 14

Philips Semiconductors Preliminary specification

VPS dataline processor SAA4700T

DEFINITIONS

Data sheet status

Objective specification This data sheet contains target or goal specifications for product development.

Preliminary specification This data sheet contains preliminary data; supplementary data may be published later.

Product specification This data sheet contains final product specifications.

Limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or

more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation

of the device at these or at any other conditions above those given in the Characteristics sections of the specification

is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information

Where application information is given, it is advisory and does not form part of the specification.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these

products can reasonably be expected to result in personal injury. Philips customers using or selling these products for

use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such

improper use or sale.

2

PURCHASE OF PHILIPS I

C COMPONENTS

2

Purchase of Philips I

components in the I2C system provided the system conforms to the I2C specification defined by

Philips. This specification can be ordered using the code 9398 393 40011.

C components conveys a license under the Philips’ I2C patent to use the

March 1991 14

Loading...

Loading...