Page 1

S3C70F2/C70F4/P70F4 PRODUCT OVERVIEW

1 PRODUCT OVERVIEW

OVERVIEW

The S3C70F2/C70F4 single-chip CMOS microcontroller has been designed for high-performance using

Samsung's newest 4-bit CPU core, SAM47 (Samsung Arrangeable Microcontrollers).

The S3P70F4 is the microcontroller which has 4 Kbyte one-time-programmable ROM and the functions are the

same to S3C70F2/C70F4. With a four-channel comparator, eight LED direct drive pins, serial I/O interface, and

its versatile 8-bit timer/counter, the S3C70F2/C70F4 offers an excellent design solution for a wide variety of

general-purpose applications.

Up to 24 pins of the 30-pin SDIP package can be dedicated to I/O. Five vectored interrupts provide fast response

to internal and external events. In addition, the S3C70F2/C70F4's advanced CMOS technology provides for very

low power consumption and a wide operating voltage range — all at a very low cost.

1-1

Page 2

PRODUCT OVERVIEW S3C70F2/C70F4/P70F4

FEATURES SUMMARY

Memory

• 512 × 4-bit data memory (RAM)

• 2048 × 8-bit program memory (ROM):S3C70F2

4096 × 8-bit program memory (ROM):S3C70F4

24 I/O Pins

•• I/O: 18 pins, including 8 high current pins

• Input only: 6 pins

Comparator

• 4-channel mode:

Internal reference (4-bit resolution)

16-step variable reference voltage

• 3-channel mode:

External reference

150 mV resolution (worst case)

8-bit Basic Timer

• Programmable interval timer

• Watch-dog timer

8-bit Timer/Counter 0

Bit Sequential Carrier

• Supports 16-bit serial data transfer in arbitrary

format

Interrupts

• Two external interrupt vectors

• Three internal interrupt vectors

• Two quasi-interrupts

Memory-Mapped I/O Structure

• Data memory bank 15

Two Power-Down Modes

• Idle mode: Only CPU clock stops

• Stop mode: System clock stops

OSCILLATION SOURCES

• Crystal, Ceramic for system clock

• Crystal/ceramic: 0.4 - 6.0 MHz

• CPU clock divider circuit (by 4. 8, or 64)

• Programmable interval timer

• External event counter function

Timer/counter clock output to TCLO0 pin

Watch Timer

• Time interval generation: 0.5 s, 3.9 ms at 4.19

MHz

• 4 frequency outputs to BUZ pin

8-bit Serial I/O Interface

• 8-bit transmit/receive mode

• 8-bit receive-only mode

• LSB-first or MSB-first transmission selectable

• Internal or external clock source

Instruction Execution Times

• 0.95, 1.91, 15.3 µs at 4.19 MHz

• 0.67, 1.33, 10.7 µs at 6.0 MHz

Operating Temperature

• – 40

°

C to 85 °C

Operating Voltage Range

• 1.8 V to 5.5 V

Package Type

• 30 SDIP, 32 SOP

1-2

Page 3

S3C70F2/C70F4/P70F4 PRODUCT OVERVIEW

FUNCTION OVERVIEW

SAM47 CPU

All S3C7-series microcontrollers have the advanced SAM47 CPU core. The SAM47 CPU can directly address up

to 32 K bytes of program memory. The arithmetic logic unit (ALU) performs 4-bit addition, subtraction, logical,

and shift-and-rotate operations in one instruction cycle and most 8-bit arithmetic and logical operations in two

cycles.

CPU REGISTERS

Program Counter

A 11-bit program counter (PC) stores addresses for instruction fetch during program execution. Usually, the PC is

incremented by the number of bytes of the instruction being fetched. An exception is the 1-byte instruction REF

which is used to reference instructions stored in a look-up table in the ROM. Whenever a reset operation or an

interrupt occurs, bits PC11 through PC0 are set to the vector address. Bit PC13–12 is reserved to support future

expansion of the device's ROM size.

Stack Pointer

An 8-bit stack pointer (SP) stores addresses for stack operations. The stack area is located in the generalpurpose data memory bank 0. The SP is read or written by 8-bit instructions and SP bit 0 must always be set to

logic zero.

During an interrupt or a subroutine call, the PC value and the program status word (PSW) are saved to the stack

area in RAM. When the service routine has completed, the values referenced by the stack pointer are restored.

Then, the next instruction is executed.

The stack pointer can access the stack regardless of data memory access enable flag status. Since the reset

value of the stack pointer is not defined in firmware, it is recommended that the stack pointer be initialized to 00H

by program code. This sets the first register of the stack area to data memory location 0FFH.

PROGRAM MEMORY

In its standard configuration, the 4096 × 8-bit ROM is divided into three functional areas:

— 16-byte area for vector addresses

— 96-byte instruction reference area

— 1920-byte general purpose area (S3C70F2)

— 3968-byte general purpose area (S3C70F4)

The vector address area is used mostly during reset operations and interrupts. These 16 bytes can also be used

as general-purpose ROM.

The REF instruction references 2 × 1-byte and 2-byte instructions stored in locations 0020H–007FH. The REF

instruction can also reference 3-byte instructions such as JP or CALL. In order for REF to be able to reference

these instructions, however, JP or CALL must be shortened to a 2-byte format. To do this, JP or CALL is written

to the reference area with the format TJP or TCALL instead of the normal instruction name. Unused locations in

the instruction reference area can be allocated to general-purpose use.

1-3

Page 4

PRODUCT OVERVIEW S3C70F2/C70F4/P70F4

DATA MEMORY

Overview

Data memory is organized into three areas:

— 32 × 4-bit working registers

— 224 × 4-bit general-purpose area in bank 0

— 256 × 4-bit general-purpose area in bank 1

— 128 × 4-bit area in bank 15 for memory-mapped I/O addresses

Data stored in data memory can be manipulated by 1-, 4-, and 8-bit instructions.

Data memory is organized into two memory banks — bank 0, bank 1 and bank 15. The select memory bank in-

struction (SMB) selects the bank to be used as working data memory. After power-on reset operation,

initialization values for data memory must be redefined by code.

Data Memory Addressing Modes

The enable memory bank (EMB) flag controls the addressing mode for data memory banks 0, 1 or 15.

When the EMB flag is logic zero, restricted area can be accessed. When the EMB flag is set to logic one, all two

data memory banks can be accessed according to the current SMB value. The EMB = "0" addressing mode is

used for normal program execution, whereas the EMB = "1" mode is commonly used for interrupts, subroutines,

mapped I/O, and repetitive access of specific RAM addresses.

Working Registers

The RAM's working register area in data memory bank 0 is further divided into four register banks. Each register

bank has eight 4-bit registers that are addressable either by 1-bit or 4-bit instructions. Paired 4-bit registers can

be addressed as double registers by 8-bit instructions.

Register A is the 4-bit accumulator and double register EA is the 8-bit extended accumulator. Double registers

WX, WL, and HL are used as data pointers for indirect addressing. Unused working registers can be used as

general-purpose memory.

To limit the possibility of data corruption due to incorrect register bank addressing, register bank 0 is usually used

for the main program and banks 1, 2, and 3 for interrupt service routines.

1-4

Page 5

S3C70F2/C70F4/P70F4 PRODUCT OVERVIEW

CONTROL REGISTERS

Program Status Word

The 8-bit program status word (PSW) controls ALU operations and instruction execution sequencing. It is also

used to restore a program's execution environment when an interrupt has been serviced. Program instructions

can always address the PSW regardless of the current value of data memory enable flags.

Before an interrupt or subroutine is processed, the PSW values are pushed onto the stack in data memory bank

0. When the service routine is completed, the PSW values are restored.

IS1 IS0 EMB ERB

C SC2 SC1 SC0

Interrupt status flags (IS1, IS0), the enable memory bank and enable register bank flags (EMB, ERB), and the

carry flag (C) are 1- and 4-bit read/write or 8-bit read-only addressable. You can address the skip condition flags

(SC0–SC2) using 8-bit read instructions only.

Select Bank (SB) Register

Two 4-bit registers store address values used to access specific memory and register banks: the select memory

bank register, SMB, and the select register bank register, SRB.

'SMB n' instruction selects a data memory bank (0 or 15) and stores the upper four bits of the 12-bit data memory

address in the SMB register. To select register bank 0, 1, 2, or 3, and store the address data in the SRB, you can

use the instruction 'SRB n'.

The instructions "PUSH SB" and "POP SB" move SRB and SMB values to and from the stack for interrupts and

subroutines.

CLOCK CIRCUITS

System oscillation circuit generates the internal clock signals for the CPU and peripheral hardware.

The system clock can use a crystal, or ceramic oscillation source, or an externally-generated clock signal. To

drive S3C70F2/C70F4 using an external clock source, the external clock signal should be input to Xin, and its

inverted signal to X

out

.

4-bit power control register controls the oscillation on/off, and select the CPU clock. The internal system clock

signal (fx) can be divided internally to produce three CPU clock frequencies — fx/4, fx/8, or fx/64.

INTERRUPTS

Interrupt requests may be generated internally by on-chip processes (INTB, INTT0, and INTS) or externally by

peripheral devices (INT0 and INT1). There are two quasi-interrupts: INTK and INTW. INTK (KS0–KS2) detects

falling edges of incoming signals and INTW detects time intervals of 0.5 seconds or 3.91 milliseconds. The

following components support interrupt processing:

— Interrupt enable flags

— Interrupt request flags

— Interrupt priority registers

— Power-down termination circuit

1-5

Page 6

PRODUCT OVERVIEW S3C70F2/C70F4/P70F4

POWER-DOWN

To reduce power consumption, there are two power-down modes: idle and stop. The IDLE instruction initiates idle

mode; the STOP instruction initiates stop mode.

In idle mode, the CPU clock stops while peripherals continue to operate normally. In stop mode, system clock

oscillation stops completely, halts all operations except for a few basic peripheral functions. A power-down is

terminated either by a RESET or by an interrupt (with exception of the external interrupt INT0).

RESETRESET

When RESET is input during normal operation or during power-down mode, a reset operation is initiated and the

CPU enters idle mode. When the standard oscillation stabilization time interval (31.3 ms at 4.19 MHz) has

elapsed, normal CPU operation resumes.

I/O PORTS

The S3C70F2/C70F4 has seven I/O ports. Pin addresses for all I/O ports are mapped to locations FF0H–FF6H

in bank 15 of the RAM. There are 6 input pins and 18 configurable I/O pins including 8 high current I/O pins for a

total of 24 I/O pins. The contents of I/O port pin latches can be read, written, or tested at the corresponding

address using bit manipulation instructions.

TIMERS and TIMER/COUNTER

The timer function has three main components: an 8-bit basic timer, an 8-bit timer/counter, and a watch timer.

The 8-bit basic timer generates interrupt requests at precise intervals, based on the selected internal clock

frequency.

The programmable 8-bit timer/counter is used for counting events, modifying internal clock frequencies, and

dividing external clock signals. The 8-bit timer/counter generates a clock signal (SCK) for the serial I/O interface.

The watch timer consists of an 8-bit watch timer mode register, a clock selector, and a frequency divider circuit.

Its functions include real-time, watch-time measurement, and clock generation for frequency output for buzzer

sound.

SERIAL I/O INTERFACE

The serial I/O interface supports the transmission or reception of 8-bit serial data with an external device. The

serial interface has the following functional components:

— 8-bit mode register

— Clock selector circuit

— 8-bit buffer register

— 3-bit serial clock counter

The serial I/O circuit can be set to transmit-and-receive, or to receive-only mode. MSB-first or LSB-first

transmission is also selectable.

The serial interface can operate with an internal or an external clock source, or using the clock signal generated

by the 8-bit timer/counter. Transmission frequency can be modified by setting the appropriate bits in the SIO

mode register.

1-6

Page 7

S3C70F2/C70F4/P70F4 PRODUCT OVERVIEW

BIT SEQUENTIAL CARRIER

The bit sequential carrier (BSC) is a 16-bit register that can be manipulated using 1-, 4-, and 8-bit instructions.

Using 1-bit indirect addressing, addresses and bit locations can be specified sequentially. In this way, programs

can process 16-bit data by moving the bit location sequentially and then incrementing or decrementing the value

of the L register. BSC data can also be manipulated using direct addressing.

COMPARATOR

The S3C70F2/C70F4 contains a 4-channel comparator which can be multiplexed to normal input port.

— Conversion time: 15.2 µs, 121.6 µs at 4.19 MHz

— Two operation modes:

Three channels for analog input and one channel for external reference voltage input

Four channels for analog input and internal reference voltage level

— 16-level internal reference voltage generator

— 150 mV accuracy for input voltage level difference detection (maximum)

— Comparator enable and disable

The comparison results are read from the 4-bit CMPREG register after the specified conversion time.

1-7

Page 8

PRODUCT OVERVIEW S3C70F2/C70F4/P70F4

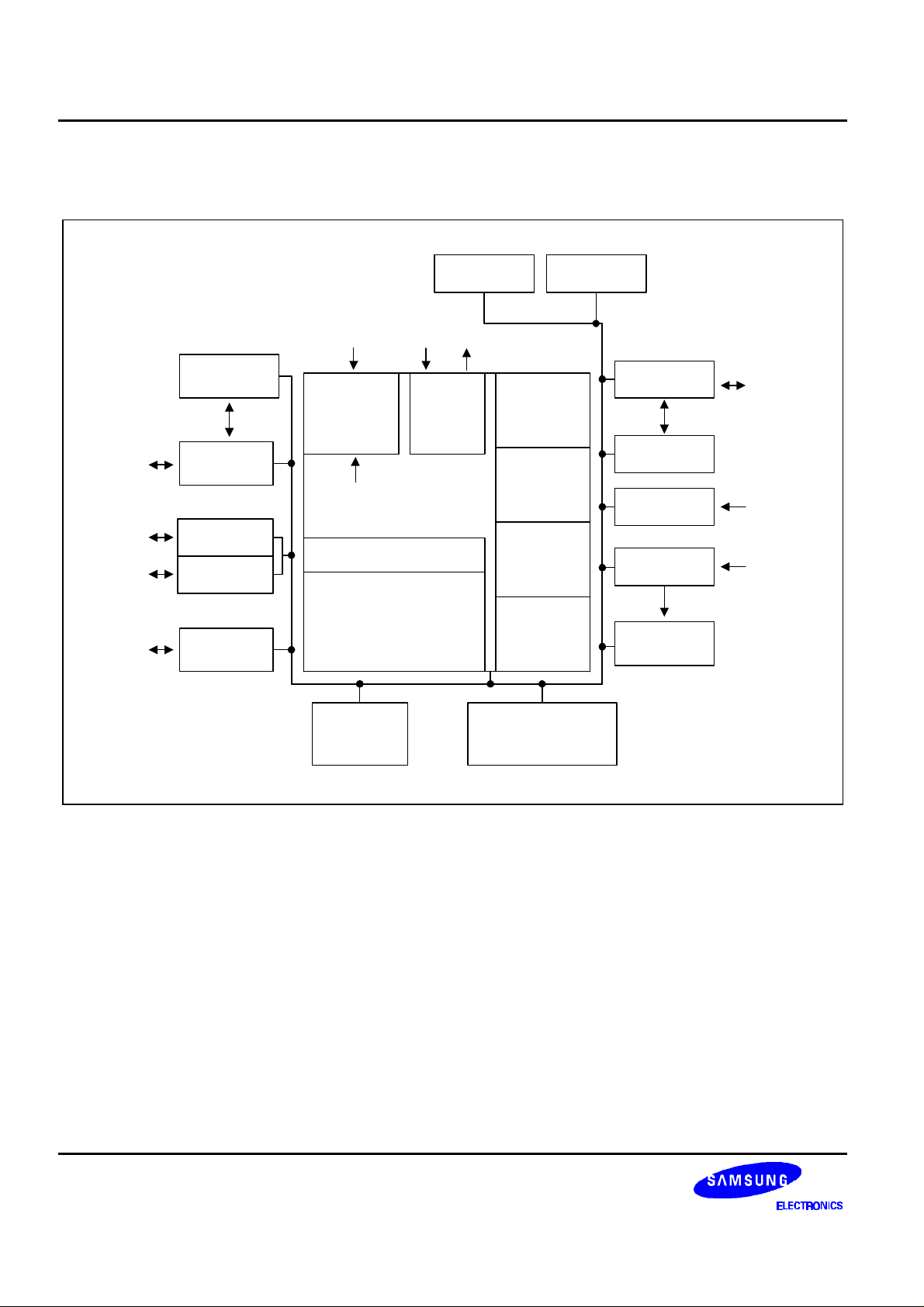

BLOCK DIAGRAM

Basic Timer Watch Timer

X

RESET

X

OUT

IN

P3.0/TCL0

P3.1/TCLO0

P3.2/CLO

P4.0 - P4.3

P5.0 - P5.3

P6.0/KS0

P6.1/KS1

P6.2/KS2

P6.3/KS3

8-Bit

Timer/Counter

I/O Port 3

I/O Port 4

I/O Port 5

I/O Port 6

Interrupt

Control

Block

Internal

Interrupts

Instruction Decoder

Arithmetic

and

Logic Unit

512 x 4-Bit

Data

Memory

Clock

Stack

Pointer

Program

Counter

Program

Status Word

Flags

Program Memory

KS57C01502: 2 KByte

KS57C01504: 4 KByte

I/O Port 0

Serial I/O Port

Input Port 1

Input Port 2

Comparator

P0.0/CLO

P0.1/TIO

P0.2/INT1

P0.0/SCK

P0.1/SO

P0.2/SI

P2.0/KS0/CIN0

P2.1/KS1/CIN1

P2.2/KS2/CIN2

P2.3/KS3/CIN3

1-8

Figure 1-1. S3C70F2/C70F4 Simplified Block Diagram

Page 9

S3C70F2/C70F4/P70F4 PRODUCT OVERVIEW

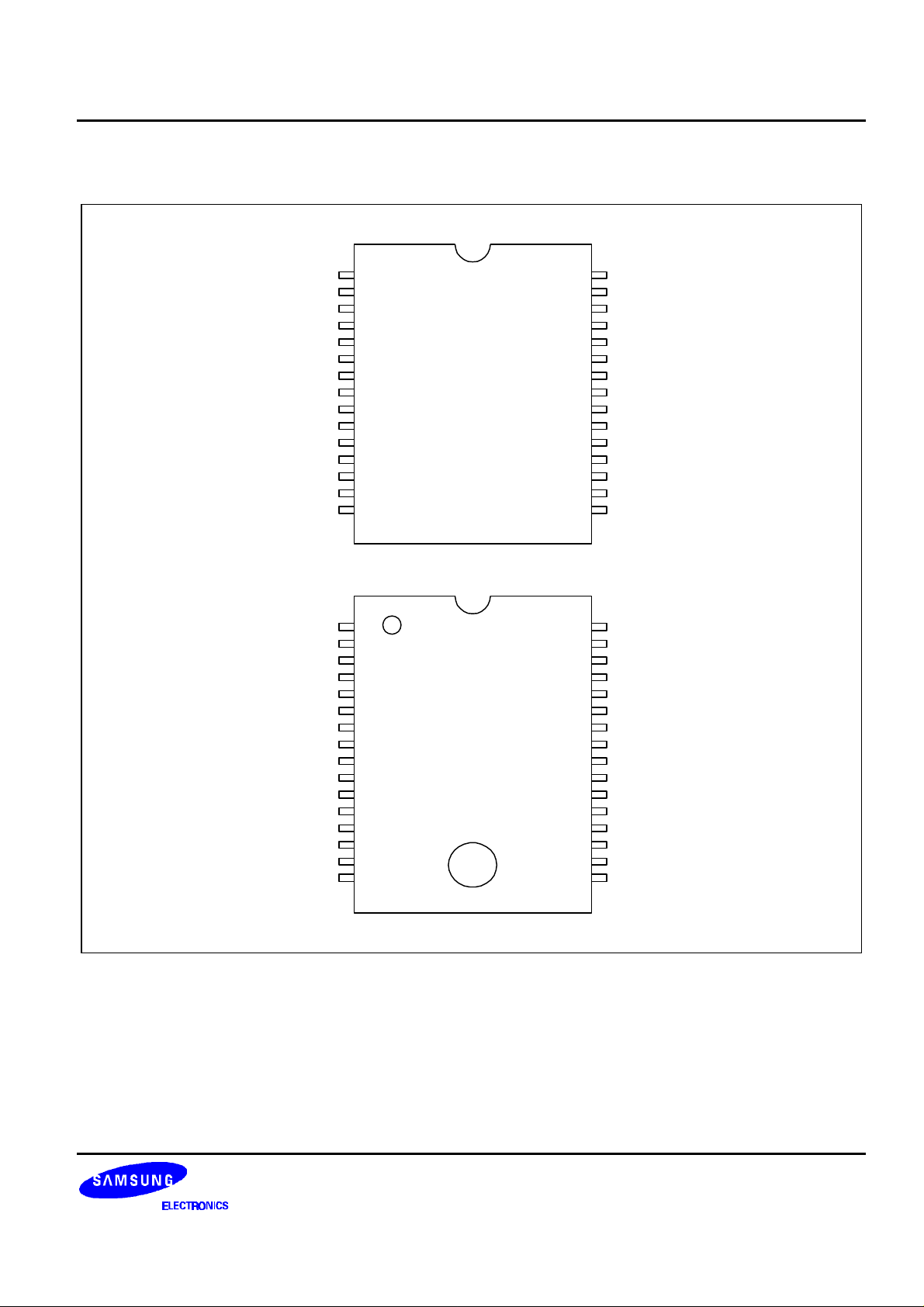

PIN ASSIGNMENTS

VSS

Xout

Xin

TEST

P1.0/INT0

P1.1/INT1

RESET

P0.0/SCK

P0.1./SO

P0.2/SI

P2.0/CIN0

P2.1/CIN1

P2.2/CIN2

P2.3/CIN3

P3.0/TCL0

VSS

Xout

Xin

TEST

P1.0/INT0

P1.1/INT1

RESET

NC

P0.0/SCK

P0.1./SO

P0.2/SI

P2.0/CIN0

P2.1/CIN1

P2.2/CIN2

P2.3/CIN3

P3.0/TCL0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

S3C70F2

S3C70F4

(Top View)

30-SDIP

S3C70F2

S3C70F4

(Top View)

30-SDIP

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

VDD

P6.3/BUZ

P6.2/KS2

P6.1/KS1

P6.0/KS0

P5.3

P5.2

P5.1

P5.0

P4.3

P4.2

P4.1

P4.0

P3.2/CLO

P3.1/TCLO0

VDD

P6.3/BUZ

P6.2/KS2

P6.1/KS1

P6.0/KS0

P5.3

P5.2

P5.1

P5.0

P4.3

P4.2

P4.1

P4.0

NC

P3.2/CLO

P3.1/TCLO0

Figure 1-2. S3C70F2/C70F4 Pin Assignment Diagram

1-9

Page 10

PRODUCT OVERVIEW S3C70F2/C70F4/P70F4

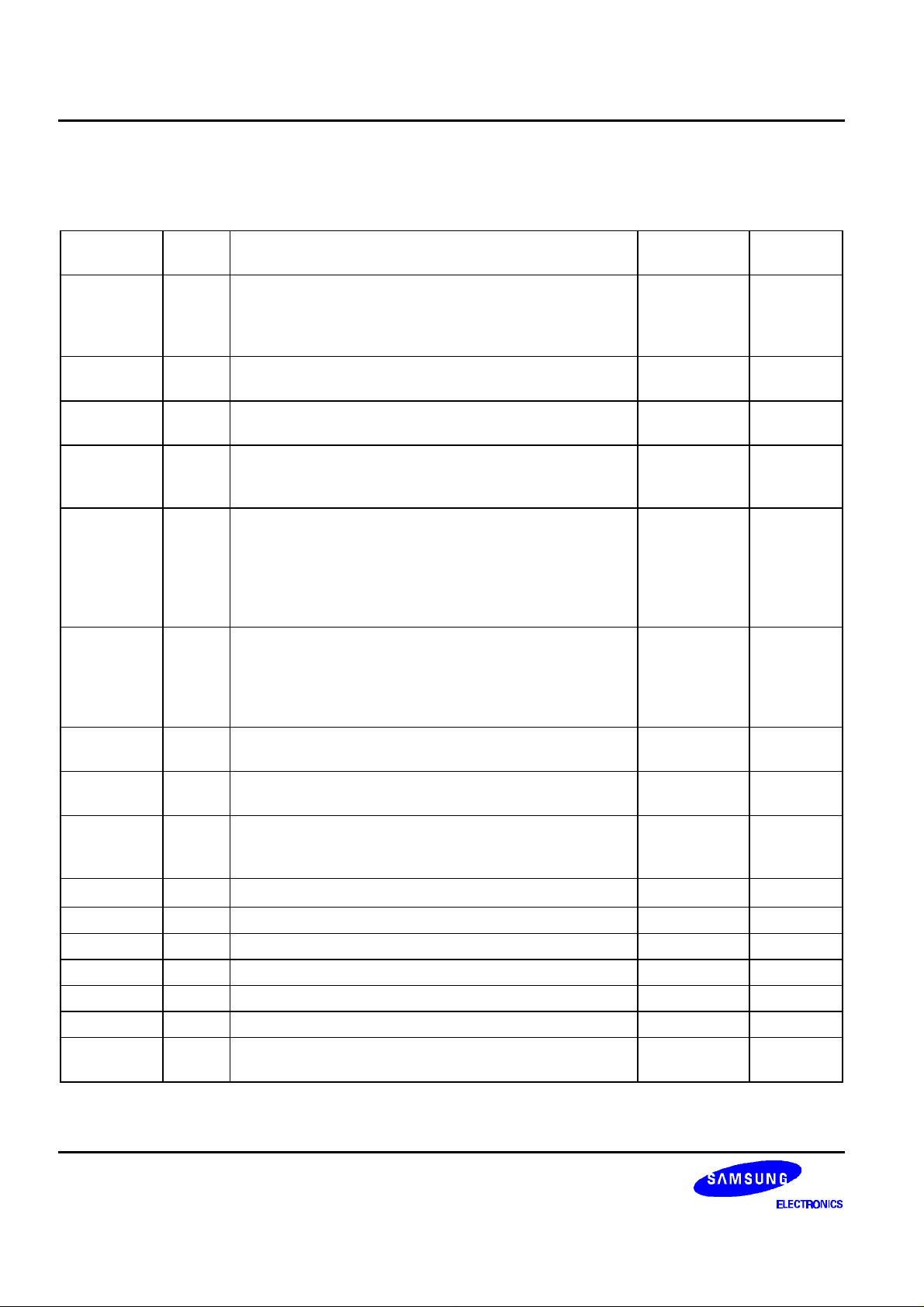

PIN DESCRIPTIONS

Table 1-1. S3C70F2/C70F4 Pin Descriptions

Pin Name Pin

Description Number Share Pin

Type

P0.0

P0.1

P0.2

I/O 3-bit I/O port. 1-bit or 3-bit read/write and test are

possible. Pull-up resistors are assignable to input pins by

software and are automatically disabled for output pins.

8(9)

9(10)

10(11)

Pins are individually configurable as input or output.

P1.0

P1.1

P2.0–P2.3 I 4-bit input port. 1-bit or 4-bit read and test are possible. 11-14

I 2-bit input port. 1-bit or 2-bit read and test are possible.

Pull-up resistors are assignable by software.

5(5)

6(6)

CIN0–CIN3

(12-15)

P3.0

P3.1

P3.2

P4.0–P4.3

P5.0–P5.3

I/O Same as port 0 15(16)

16(17)

17(18)

I/O 4-bit I/O ports. 1-, 4-, or 8-bit read/write and test are

possible. Pins are individually configurable as input or

18-21(20-23)

22-25(24-27)

output. 4-bit pull-up resistors are assignable to input pins

by software and are automatically disabled for output

pins. The N-channel open-drain or push-pull output can

be selected by software (1-bit unit)

P6.0

P6.1

P6.2

P6.3

I/O 4-bit I/O port.

1-bit or 4-bit read/write and test are possible.

Pull-up resistors are assignable to input pins by software

and are automatically disabled for output pins. Pins are

26(28)

27(29)

28(30)

29(31)

individually configurable as input or output.

INT0 I External interrupts with detection of rising and falling

5(5) P1.0

edges

INT1 I External interrupts with detection of rising or falling

6(6) P1.1

edges

CIN0–CIN3 I 4-channel comparator input.

11-14(12-15) P2.0–P2.3

CIN0–CIN2: comparator input only.

CIN3: comparator input or external reference input

SCK

I/O Serial interface clock signal

8(9)

SO I/O Serial data output 9(10) P0.1

SI I/O Serial data input 10(11) P0.2

TCL0 I/O External clock input for timer/counter 15(16) P3.0

TCLO0 I/O Timer/counter clock output 16(17) P3.1

CLO I/O CPU clock output 17(18) P3.2

BUZ I/O 2 kHz, 4 kHz, 8 kHz, or 16 kHz frequency output at 4.19

29(31) P6.3

MHz for buzzer sound

SCK

SO

SI

INT0

INT1

TCL0

TCLO0

CLO

–

KS0

KS1

KS2

BUZ

P0.0

NOTE: Pn numbers shown in parentheses '( )' are for 32-pin SOP package; other pin numbers are for the 30-pin SDIP.

1-10

Page 11

S3C70F2/C70F4/P70F4 PRODUCT OVERVIEW

Table 1-1. S3C70F2/C70F4 Pin Descriptions (Continued)

Pin Name Pin

Description Number Share Pin

Type

Quasi-interrupt input with falling edge detection 26-28(28-30) P6.0–P6.2

V

DD

V

SS

RESET

TEST I

Xin, X

out

NOTE: Pin numbers shown in parentheses '( )' are for 32-pin SOP package; other pin numbers are for the 30-pin SDIP.

— Main power supply 30(32) —

— Ground 1(1) —

I Reset signal 7(7) —

Test signal input (must be connected to VSS)

4(4) —

— Crystal or ceramic oscillator signal for system clock 3,2(3,2) —

Table 1-2. Overview of S3C70F2/C70F4 Pin Data

SDIP Pin

Numbers

1

2,3 Xout, Xin

4 TEST

Pin

Names

V

SS

Share

Pins

I/O

Type

Reset

Value

I

Circuit

Type

5,6 P1.0, P1.1 INT0, INT1 I Input A-3

7

RESET

8-10 P0.0 - P0.2

SCK, SO, SI

11-14 P2.0 - P2.3 CIN0 - CIN3 I Input

15-17 P3.0 - P3.2 TCL0, TCLO0,

I

B

I/O Input D-1

F-1, F-2

I/O Input D-1

(note)

CLO

18-21 P4.0 - P4.3

22-25 P5.0 - P5.3

26-29 P6.0 - P6.3 KS0, KS1, KS2,

I/O Input E

I/O Input E

I/O Input D-1

BUZ

30

V

DD

NOTE: I/O circuit type F-2 is implemented for P2.3 only.

1-11

Page 12

PRODUCT OVERVIEW S3C70F2/C70F4/P70F4

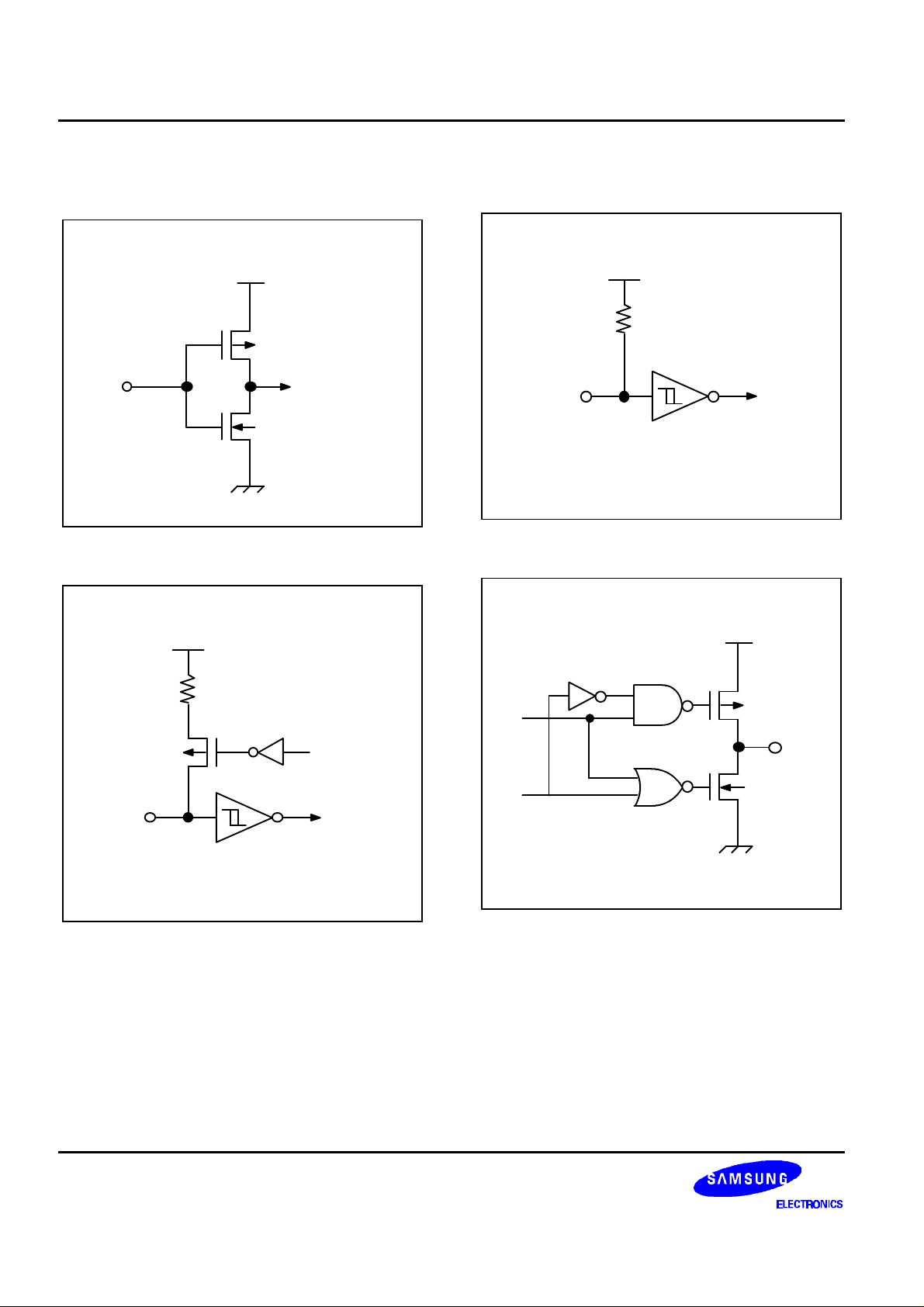

PIN CIRCUIT DIAGRAMS

VDD

P-CHANNEL

IN

N-CHANNEL

Figure 1-3. Pin Circuit Type A

VDD

PULL-UP

RESISTOR

P-CHANNEL

RESISTOR

ENABLE

VDD

PULL-UP

RESISTOR

IN

SCHMITT TRIGGER

Figure 1-5. Pin Circuit Type B

VDD

P-CHANNEL

DATA

OUT

1-12

IN

SCHMITT TRIGGER

Figure 1-4. Pin Circuit Type A-3

N-CHANNEL

OUTPUT

DISABLE

Figure 1-6. Pin Circuit Type C

Page 13

KS57C01502/C01504/P01504 PRODUCT OVERVIEW

VDD

PULL-UP

RESISTOR

RESISTOR

ENABLE

DATA

OUTPUT

CIRCUIT

TYPE 4

DISABLE

SCHMITT TRIGER

Figure 1-7. Pin Circuit Type D-1

PNE

DATA

P-CHANNEL

VDD

P-CHANNEL

VDD

PULL-UP

RESISTOR

I/O

I/O

PULL-UP

RESISTOR

ENABLE

DIGITAL INPUT

ANALOG INPUT

Figure 1-9. Pin Circuit Type F-1

DIGITAL INPUT

ANALOG INPUT

OUTPUT

DISABLE

N-CHANNEL

Figure 1-8. Pin Circuit Type E

EXTERNAL V

Figure 1-10. Pin Circuit Type F-2

REF

1-13

Page 14

PRODUCT OVERVIEW KS57C01502/C01504/P01504

NOTES

1-14

Page 15

S3C70F2/C70F4/P70F4 ELECTRICAL DATA

14 ELECTRICAL DATA

Table 14-1. Absolute Maximum Ratings

(TA = 25 °C)

Parameter Symbol Conditions Rating Units

Supply Voltage

Input Voltage

Output Voltage

Output Current High

Output Current Low

Operating Temperature

Storage Temperature

V

DD

I

V

V

OH

I

O

All I/O ports

One I/O port active – 5 mA

– – 0.3 to + 6.5 V

– 0.3 to V

–

– 0.3 to VDD + 0.3

DD

+ 0.3

V

V

All I/O ports active – 15

I

OL

Ports 0, 3, and 6 5 mA

Ports 4 and 5 30

All ports, total + 100

T

A

T

stg

– – 40 to + 85

– – 65 to + 150

°

C

°

C

Table 14-2. D.C. Electrical Characteristics

(T

= – 40 °C to + 85 °C, VDD = 1.8 V to 5.5 V)

A

Parameter Symbol Conditions Min Typ Max Units

Input High

V

IH1

Ports 4 and 5

0.7V

DD

–

V

DD

Voltage

Input Low

V

IH2

V

IH3

V

IL1

Ports 0, 1, 2, 3, 6, and RESET

XIN and X

OUT

Ports 4 and 5 – –

0.8V

V

DD

DD

– 0.1

–

–

V

V

0.3V

DD

DD

DD

Voltage

Output High

Voltage

V

IL2

V

IL3

V

OH

Ports 0, 1, 2, 3, 6, and RESET

XIN and X

V

DD

OUT

= 4.5 V to 5.5 V

V

DD

- 1.0

– – V

IOH = – 1 mA

0.2V

0.1

DD

Ports 0, 3, 4, 5, 6

V

V

14-1

Page 16

ELECTRICAL DATA S3C70F2/C70F4/P70F4

Table 14-2. D.C. Electrical Characteristics (Continued)

(T

= – 40 °C to + 85 °C, VDD = 1.8 V to 5.5 V)

A

Parameter Symbol Conditions Min Typ Max Units

Output Low

Voltage

V

OL

V

= 4.5 V to 5.5 V

DD

IOL = 15 mA

– – 2 V

Ports 4, 5

VDD = 4.5V to 5.5 V

I

= 4.0mA

OL

– 2

All output pins except Ports 4, 5

Input High

Leakage

Current

Input Low

Leakage

Current

Output High

Leakage

I

LIH1

I

LIH2

I

LIL1

I

LIL2

I

LOH

VIN = V

DD

All input pins except XIN and X

VIN = V

XIN and X

V

All input pins except X

= 0 V

IN

DD

OUT

, X

IN

OUT

and RESET

V

= 0 V

IN

XIN and X

V

O

= V

OUT

DD

All output pins

OUT

– – 3

20

– – – 3

– 20

– – 3

µA

µA

µA

Current

Output Low

I

LOL

V

O

= 0 V

– – – 3

µA

Leakage

Current

Pull-Up

Resistor

R

L1

R

L2

V

= 0 V; V

I

DD

= 5 V

Port 0, 1, 3, 4, 5, 6

V

= 3 V

DD

V

DD

V

DD

= 5 V; V

= 3 V

= 0 V; RESET

I

25 50 100

50 100 200

100 250 400

200 500 800

kΩ

14-2

Page 17

S3C70F2/C70F4/P70F4 ELECTRICAL DATA

Table 14-2. D.C. Electrical Characteristics (Concluded)

(T

= – 40 °C to + 85 °C, VDD = 1.8 V to 5.5 V)

A

Parameter Symbol Conditions Min Typ Max Units

Supply

Current

(1)

I

DD1

Run mode; V

= 5.0 V ± 10%

DD

6.0MHz – 3.0 8.0

Crystal oscillator; C1=C2=22pF 4.19MHz 2.0 5.5

V

= 3 V ± 10%

DD

6.0MHz 1.3 4.0

mA

4.19MHz 1.0 3.0

I

DD2

Idle mode; V

= 5.0 V ± 10%

DD

6.0MHz – 0.8 2.5

mA

Crystal oscillator; C1=C2=22pF 4.19MHz 0.6 1.8

V

= 3 V ± 10%

DD

6.0MHz 0.6 1.5

4.19MHz 0.4 1.0

I

DD3

NOTES:

1. D.C. electrical values for Supply current (I

output port drive currents and comparator.

2. The supply current assumes a CPU clock of fx/4.

Stop mode; V

Stop mode; V

= 5.0 V ± 10%

DD

= 3.0 V ± 10%

DD

to I

DD1

) do not include current drawn through internal pull-up resistor,

DD3

– 0.5 3.0

0.3 2.0

µA

CPU CLOCK

1.5 MHz

1.05 MHz

15.625 kHz

Main Osc. Freq. ( Divided by 4 )

6 MHz

4.2 MHz

400 kHz

1 2

CPU CLOCK = 1/n x oscillator frequency (n = 4, 8 or 64)

2.7

3 4 5 6 7

SUPPLY VOLTAGE (V)

Figure 14-1. Standard Operating Voltage Range

14-3

Page 18

ELECTRICAL DATA S3C70F2/C70F4/P70F4

Table 14-3. Oscillators Characteristics

(TA = – 40 °C + 85 °C, VDD = 1.8 V to 5.5 V)

Oscillator Clock

Configuration

Ceramic

Xin Xout

Oscillator

C1 C2

Crystal

Xin Xout

Oscillator

C1 C2

External

Xin Xout

Clock

Parameter Test Condition Min Typ Max Units

Oscillation frequency

Stabilization time

(2)

Oscillation frequency

Stabilization time

(2)

XIN input frequency

(1)

VDD = 2.7 V to 5.5 V

VDD = 1.8 V to 5.5 V

VDD = 3.0 V

(1)

VDD = 2.7 V to 5.5 V

VDD = 1.8 V to 5.5 V

VDD = 3.0 V

(1)

VDD = 2.7 V to 5.5 V

0.4 – 6.0 MHz

0.4 – 4.2

– – 4 ms

0.4 – 6.0 MHz

0.4 – 4.2

– – 10 ms

0.4 – 6.0 MHz

XIN input high and low

VDD = 1.8 V to 5.5 V

– 83.3 – 1250 ns

0.4 – 4.2

level width (tXH, tXL)

NOTES:

1. Oscillation frequency and XIN input frequency data are for oscillator characteristics only.

2. Stabilization time is the interval required for oscillating stabilization after a power-on occurs, or when stop mode is

terminated.

14-4

Page 19

S3C70F2/C70F4/P70F4 ELECTRICAL DATA

Table 14-4. Input/Output Capacitance

(TA = 25 °C, V

DD

= 0 V )

Parameter Symbol Condition Min Typ Max Units

C

C

OUT

IN

f = 1 MHz; Unmeasured pins

are returned to V

SS

– – 15 pF

15 pF

Input

Capacitance

Output

Capacitance

I/O Capacitance

C

IO

15 pF

Table 14-5. Comparator Electrical Characteristics

(T

= – 40 °C to + 85 °C, VDD = 4.0 V to 5.5V, VSS = 0 V)

A

Parameter Symbol Condition Min Typ Max Units

Input Voltage Range – – 0 –

Reference Voltage

V

REF

– 0 –

V

DD

V

DD

Range

I

CIN

V

CIN

I

,

REF

– – –

±150

– – 3 – 3

Input Voltage Accuracy

Input Leakage Current

V

V

mV

µA

Table 14-6. A.C. Electrical Characteristics

(T

= – 40 °C to + 85 °C, V

A

= 1.8 V to 5.5 V)

DD

Parameter Symbol Conditions Min Typ Max Units

Instruction Cycle

Time

TCL0 Input

Frequency

TCL0 Input High,

Low Width

SCK Cycle Time

t

TIH

t

t

CY

f

TI

, t

KCY

V

= 2.7 V to 5.5 V

DD

VDD = 1.8 V to 5.5 V

V

= 2.7 V to 5.5 V

DD

VDD = 1.8 V to 5.5 V

V

= 2.7 V to 5.5 V

TIL

DD

VDD = 1.8 V to 5.5 V

VDD = 2.7 V to 5.5 V

0.67 – 64

0.95

0 – 1.5 MHz

1 MHz

0.48 – –

1.8

800 – – ns

External SCK source

Internal SCK source

VDD = 1.8 V to 5.5 V

670

3200

External SCK source

Internal SCK source

3800

µs

µs

14-5

Page 20

ELECTRICAL DATA S3C70F2/C70F4/P70F4

Table 14-6. A.C. Electrical Characteristics ( Concluded)

(T

= – 40 °C to + 85 °C, V

A

= 1.8 V to 5.5 V)

DD

Parameter Symbol Conditions Min Typ Max Units

SCK High, Low

Width

tKH, t

VDD = 2.7 V to 5.5 V

KL

External SCK source

Internal SCK source

VDD = 1.8 V to 5.5 V

335 – – ns

t

/2 – 50

KCY

1600

External SCK source

t

/2 – 150

KCY

100 – – ns

150

150

SI Setup Time to

SCK High

t

SIK

Internal SCK source

VDD = 2.7 V to 5.5 V

External SCK source

Internal SCK source

VDD = 1.8 V to 5.5 V

External SCK source

500

400 – – ns

400

600

SI Hold Time to

SCK High

t

KSI

Internal SCK source

VDD = 2.7 V to 5.5 V

External SCK source

Internal SCK source

VDD = 1.8 V to 5.5 V

External SCK source

500

– – 300 ns

250

1000

Output Delay for

SCK to SO

t

KSO

Internal SCK source

(1)

VDD = 2.7 V to 5.5 V

External SCK source

Internal SCK source

VDD = 1.8 V to 5.5 V

External SCK source

1000

µs

Interrupt Input

High, Low Width

t

INTH

t

INTL

Internal SCK source

,

INT0

(2)

– –

INT1, KS0–KS2 10

RESET Input

t

RSL

Input 10 – –

µs

Low Width

NOTES:

1. R (1 Kohm) and C (100 pF) are the load resistance and load capacitance of the SO output line.

2. Minimum value for INT0 is based on a clock of 2t

14-6

or 128 / fx as assigned by the IMOD0 register setting.

CY

Page 21

S3C70F2/C70F4/P70F4 ELECTRICAL DATA

Table 14-7. RAM Data Retention Supply Voltage in Stop Mode

(TA = – 40 °C to + 85 °C)

Parameter Symbol Conditions Min Typ Max Unit

Data retention supply voltage

Data retention supply current

V

DDDR

I

DDDR

V

DDDR

– 1.8 – 5.5 V

= 1.8 V

– 0.1 10

µA

Release signal set time

Oscillator stabilization wait

(1)

time

NOTES:

1. During oscillator stabilization wait time, all CPU operations must be stopped to avoid instability during oscillator startup.

2. Use the basic timer mode register (BMOD) interval timer to delay execution of CPU instructions during the wait time.

t

SREL

t

WAIT

– 0 – –

Released by RESET

Released by interrupt –

µs

–

217 / fx

(2)

– ms

– ms

TIMING WAVEFORMS

INTERNAL RESET

OPERATION

IDLE MODE

OPERATING

MODE

V

DD

RESET

EXECUTION OF

STOP INSTRUCTION

STOP MODE

DATA RETENTION MODE

V

DDDR

t

WAIT

t

SREL

Figure 14-2. Stop Mode Release Timing When Initiated by RESETRESET

14-7

Page 22

ELECTRICAL DATA S3C70F2/C70F4/P70F4

DATA RETENTION MODE

DD

V

EXECUTION OF

STOP INSTRUCTION

POWER-DOWN MODE TERMINATING SIGNAL

(INTERRUPT REQUEST)

Figure 14-3. Stop Mode Release Timing When Initiated By Interrupt Request

0.8 VDD

0.2 VDD

STOP MODE

DDDR

V

MEASUREMENT

POINTS

SREL

t

0.8 VDD

0.2 VDD

IDLE MODE

WAIT

t

NORMAL

OPERATING

MODE

Xin

Figure 14-4. A.C. Timing Measurement Points (Except for XIN)

1 / fx

tXL tXH

Figure 14-5. Clock Timing Measurement at X

IN

VDD - 0.2 V

0.2 V

14-8

Page 23

S3C70F2/C70F4/P70F4 ELECTRICAL DATA

TI

1 / f

TCL

RESET

TIL

t

TIH

t

Figure 14-6. TCL Timing

t

RSL

0.2 V

Figure 14-7. Input Timing for RESETRESET Signal

0.8 VDD

0.2 VDD

DD

INT0, 1

KS0 to KS2

tINTL tINTH

0.8 VDD

0.2 VDD

Figure 14-8. Input Timing for External Interrupts

14-9

Page 24

ELECTRICAL DATA S3C70F2/C70F4/P70F4

t

CKY

SCK

SO

SI

t

KSO

t

KL

t

SIK

INPUT DATA

OUTPUT DATA

t

t

KSI

Figure 14-9. Serial Data Transfer Timing

KH

0.8 V

0.2 V

DD

DD

0.8 V

0.2

DD

V

DD

14-10

Page 25

S3C70F2/C70F4/P70F4 MECHANICAL DATA

15 MECHANICAL DATA

OVERVIEW

The S3C70F2/C70F4/P70F4microcontroller is available in a 30-pin SDIP package (Samsung part number 30SDIP-400) and a 32-SOP package (Samsung part number 30-SOP-450A).

(1.30)

8.94 ± 0.20

#30

#1

30-SDIP-400

27.88 MAX

27.48 ± 0.20

0.56 ± 0.10

1.12 ± 0.10

#16

#15

1.778

10.16

3.81 ± 0.20

0.51 MIN

5.21 MAX

3.30 ± 0.30

0-15

+ 0.10

0.25

- 0.05

NOTE: Dimensions are in millimeters.

Figure 15-1. 30-SDIP-400 Package Dimensions

15-1

Page 26

MECHANICAL DATA S3C70F2/C70F4/P70F4

0-8

#32

#17

12.00 ± 0.30

(0.43)

32-SOP-450A

#1

20.30 MAX

19.90 ± 0.20

0.40 ± 0.10

NOTE: Dimensions are in millimeters.

#16

1.27

8.34 ± 0.20

+ 0.10

0.25

- 0.05

2.00 ± 0.10

0.05 MIN

11.43

0.90 ± 0.20

2.20 MAX

0.10 MAX

15-2

Figure 15-2. 30-SOP-450A Package Dimensions

Page 27

S3C70F2/C70F4/P70F4 S3P70F4 OTP

16 S3P70F4 OTP

OVERVIEW

The S3P70F4 single-chip CMOS microcontroller is the OTP (One Time Programmable) version of the

S3C70F2/C70F4 microcontroller. It has an on-chip OTP ROM instead of masked ROM. The EPROM is accessed

by serial data format.

The S3P70F4 is fully compatible with the S3C70F2/C70F4, both in function and in pin configuration. Because of

its simple programming requirements, the S3P70F4 is ideal for use as an evaluation chip for the

S3C70F2/C70F4.

VSS/VSS

Xout

Xin

VPP/TEST

P1.0/INT0

P1.1/INT1

RESETRESET/RESET

P0.0/SCK

P0.1./SO

P0.2/SI

P2.0/CIN0

P2.1/CIN1

P2.2/CIN2

P2.3/CIN3

P3.0/TCL0

NOTE: The bolds indicate an OTP pin name.

Figure 16-1. S3P70F4 Pin Assignments (30-SDIP Package)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

S3C70F4

(30-SDIP)

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

VDD/VDD

P6.3/BUZ/SCLK

P6.2/KS2/SDAT

P6.1/KS1

P6.0/KS0

P5.3

P5.2

P5.1

P5.0

P4.3

P4.2

P4.1

P4.0

P3.2/CLO

P3.1/TCLO0

16-1

Page 28

S3P70F4 OTP S3C70F2/C70F4/P70F4

VSS/VSS

Xout

Xin

VPP/TEST

P1.0/INT0

P1.1/INT1

RESETRESET/RESET

NC

P0.0/SCK

P0.1./SO

P0.2/SI

P2.0/CIN0

P2.1/CIN1

P2.2/CIN2

P2.3/CIN3

P3.0/TCL0

NOTE: The bolds indicate an OTP pin name.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

S3P70F4

(32-SOP)

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

Figure 16-2. S3P70F4 Pin Assignments (32-SOP Package)

VDD/VDD

P6.3/BUZ/SCLK

P6.2/KS2/SDAT

P6.1/KS1

P6.0/KS0

P5.3

P5.2

P5.1

P5.0

P4.3

P4.2

P4.1

P4.0

NC

P3.2/CLO

P3.1/TCLO0

16-2

Page 29

S3C70F2/C70F4/P70F4 S3P70F4 OTP

Table 16-1. Descriptions of Pins Used to Read/Write the EPROM

Main Chip During Programming

Pin Name Pin Name Pin No. I/O Function

P6.2 SDAT 28 (30) I/O Serial data pin. Output port when reading and input

port when writing. Can be assigned as a Input /

push-pull output port.

P6.3 SCLK 29 (31) I/O Serial clock pin. Input only pin.

TEST

VPP(TEST)

4 (4) I Power supply pin for EPROM cell writing (indicates

that OTP enters into the writing mode). When 12.5

V is applied, OTP is in writing mode and when 5 V

is applied, OTP is in reading mode. (Option)

RESET RESET

VDD / V

SS

VDD / V

SS

7 (7) I Chip initialization

30/1 (32/1) I

Logic power supply pin. VDD should be tied to +5 V

during programming.

NOTE: ( ) means the 32-SOP OTP pin number.

Table 16-2. Comparison of S3P70F4 and S3C70F2/C70F4 Features

Characteristic S3P70F4 S3C70F2/C70F4

Program Memory 4 K-byte EPROM 2 K-byte mask ROM: S3C70F2

4 K-byte mask ROM: S3C70F4

Operating Voltage (VDD)

OTP Programming Mode

2.0 V to 5.5 V 1.8 V to 5.5V

VDD = 5 V, VPP(TEST)=12.5V

–

Pin Configuration 30 SDIP, 32 SOP 30 SDIP, 32 SOP

EPROM Programmability User Program one time Programmed at the factory

OPERATING MODE CHARACTERISTICS

When 12.5 V is supplied to the VPP(TEST) pin of the S3P70F4, the EPROM programming mode is entered. The

operating mode (read, write, or read protection) is selected according to the input signals to the pins listed in

Table 16–3 below.

Table 16-3. Operating Mode Selection Criteria

V

DD

Vpp(TEST) REG/MEM ADDRESS(A15-A0) R/W MODE

5 V 5 V 0 0000H 1 EPROM read

12.5 V 0 0000H 0 EPROM program

12.5 V 0 0000H 1 EPROM verify

12.5 V 1 0E3FH 0 EPROM read protection

NOTE: "0" means Low level; "1" means High level.

16-3

Page 30

S3P70F4 OTP S3C70F2/C70F4/P70F4

OTP ELECTRICAL DATA

Table 16-4. Absolute Maximum Ratings

(TA = 25 °C)

Parameter Symbol Conditions Rating Units

Supply Voltage

Input Voltage

Output Voltage

Output Current High

V

DD

V

I

V

O

I

OH

All I/O ports

One I/O port active – 5 mA

– – 0.3 to + 6.5 V

– 0.3 to V

–

– 0.3 to VDD + 0.3

DD

+ 0.3

V

V

All I/O ports active – 15

Output Current Low

I

OL

Ports 0, 3, and 6 5 mA

Ports 4 and 5 30

All ports, total + 100

Operating Temperature

Storage Temperature

T

A

T

stg

– – 40 to + 85

– – 65 to + 150

°

C

°

C

Table 16-5. D.C. Electrical Characteristics

(T

= – 40 °C to + 85 °C, VDD = 2.0 V to 5.5 V)

A

Parameter Symbol Conditions Min Typ Max Units

Input High

V

IH1

Ports 4 and 5

0.7V

DD

–

V

DD

Voltage

Input Low

V

IH2

V

IH3

V

IL1

Ports 0, 1, 2, 3, 6, and RESET

XIN and X

OUT

Ports 4 and 5 – –

0.8V

V

DD

DD

– 0.1

–

–

V

V

0.3V

DD

DD

DD

Voltage

Output High

Voltage

V

IL2

V

IL3

V

OH

Ports 0, 1, 2, 3, 6, and RESET

X

and X

IN

V

DD

OUT

= 4.5 V to 5.5 V

V

DD

- 1.0

– – V

IOH = – 1 mA

0.2V

0.1

DD

Ports 0, 3, 4, 5, 6

V

V

16-4

Page 31

S3C70F2/C70F4/P70F4 S3P70F4 OTP

Table 16-5. D.C. Electrical Characteristics (Continued)

(T

= – 40 °C to + 85 °C, VDD = 2.0 V to 5.5 V)

A

Parameter Symbol Conditions Min Typ Max Units

Output Low

Voltage

V

OL

V

= 4.5 V to 5.5 V

DD

IOL = 15 mA

– – 2 V

Ports 4, 5

VDD = 4.5 V to 5.5 V

I

= 4.0mA

OL

– 2

All output pins except Ports 4, 5

Input High

Leakage

Current

Input Low

Leakage

Current

Output High

Leakage

I

LIH1

I

LIH2

I

LIL1

I

LIL2

I

LOH

VIN = V

DD

All input pins except XIN and X

VIN = V

XIN and X

V

All input pins except X

IN

DD

= 0 V

OUT

, X

IN

OUT

and RESET

V

= 0 V

IN

XIN and X

V

O

= V

OUT

DD

All output pins

OUT

– – 3

20

– – – 3

– 20

– – 3

µA

µA

µA

Current

Output Low

I

LOL

V

O

= 0 V

– – – 3

µA

Leakage

Current

Pull-Up

Resistor

R

L1

R

L2

V

= 0 V; V

I

DD

= 5 V

Port 0, 1, 3, 4, 5, 6

V

= 3 V

DD

V

DD

V

DD

= 5 V; V

= 3 V

= 0 V; RESET

I

25 50 100

50 100 200

100 250 400

200 500 800

kΩ

16–5

Page 32

S3P70F4 OTP S3C70F2/C70F4/P70F4

Table 16-5. D.C. Electrical Characteristics (Concluded)

(T

= – 40 °C to + 85 °C, VDD = 2.0 V to 5.5 V)

A

Parameter Symbol Conditions Min Typ Max Units

Supply

Current

(1)

I

DD1

Run mode; V

= 5.0 V ± 10%

DD

6.0MHz – 3.0 8.0

Crystal oscillator; C1=C2=22pF 4.19MHz 2.0 5.5

mA

V

= 3 V ± 10%

DD

I

DD2

Idle mode; V

= 5.0 V ± 10%

DD

Crystal oscillator; C1=C2=22pF 4.19MHz 0.6 1.8

V

= 3 V ± 10%

DD

I

DD3

NOTES:

1. D.C. electrical values for Supply current (I

output port drive currents and comparator.

2. The supply current assumes a CPU clock of fx/4.

CPU CLOCK

Stop mode; V

Stop mode; V

1.5 MHz

= 5.0 V ± 10%

DD

= 3.0 V ± 10%

DD

to I

DD1

6.0MHz 1.3 4.0

4.19MHz 1.0 3.0

6.0MHz – 0.8 2.5

6.0MHz 0.6 1.5

4.19MHz 0.4 1.0

– 0.5 3.0

0.3 2.0

) do not include current drawn through internal pull-up registers,

DD3

Main Osc. Freq. ( Divided by 4 )

6 MHz

mA

µA

16–6

1.05 MHz

15.625 kHz

4.2 MHz

400 kHz

1 2

CPU CLOCK = 1/n x oscillator frequency (n = 4, 8 or 64)

2.7

3 4 5 6 7

SUPPLY VOLTAGE (V)

Figure 16-3. Standard Operating Voltage Range

Page 33

S3C70F2/C70F4/P70F4 S3P70F4 OTP

Table 16-6. Oscillators Characteristics

(T

= – 40 °C + 85 °C, VDD = 2.0 V to 5.5 V)

A

Oscillator Clock

Configuration

Ceramic

Xin Xout

Oscillator

C1 C2

Crystal

Xin Xout

Oscillator

C1 C2

External

Xin Xout

Clock

Parameter Test Condition Min Typ Max Units

Oscillation frequency

Stabilization time

(2)

Oscillation frequency

Stabilization time

(2)

Xin input frequency

(1)

VDD = 2.7 V to 5.5 V

VDD = 2.0 V to 5.5 V

VDD = 3.0 V

(1)

VDD = 2.7 V to 5.5 V

VDD = 2.0 V to 5.5 V

VDD = 3.0 V

(1)

VDD = 2.7 V to 5.5 V

0.4 – 6.0 MHz

0.4 – 4.2

– – 4 ms

0.4 – 6.0 MHz

0.4 – 4.2

– – 10 ms

0.4 – 6.0 MHz

XIN input high and low

VDD = 2.0 V to 5.5 V

– 83.3 – 1250 ns

0.4 – 4.2

level width (tXH, tXL)

NOTES:

1. Oscillation frequency and XIN input frequency data are for oscillator characteristics only.

2. Stabilization time is the interval required for oscillating stabilization after a power-on occurs, or when stop mode is

terminated.

16–7

Page 34

S3P70F4 OTP S3C70F2/C70F4/P70F4

Table 16-7. Input/Output Capacitance

(TA = 25 °C, V

DD

= 0 V )

Parameter Symbol Condition Min Typ Max Units

C

C

OUT

IN

f = 1 MHz; Unmeasured pins

are returned to V

SS

– – 15 pF

15 pF

Input

Capacitance

Output

Capacitance

I/O Capacitance

C

IO

15 pF

Table 16-8. Comparator Electrical Characteristics

(T

= – 40 °C to + 85 °C, VDD = 4.0 V to 5.5V, VSS = 0 V)

A

Parameter Symbol Condition Min Typ Max Units

Input Voltage Range – – 0 –

Reference Voltage

V

REF

– 0 –

V

DD

V

DD

Range

I

CIN

V

CIN

I

,

REF

– – –

±150

– – 3 – 3

Input Voltage Accuracy

Input Leakage Current

V

V

mV

µA

Table 16-9. A.C. Electrical Characteristics

(T

= – 40 °C to + 85 °C, V

A

= 2.0 V to 5.5 V)

DD

Parameter Symbol Conditions Min Typ Max Units

Instruction Cycle

t

CY

V

= 2.7 V to 5.5 V

DD

0.67 – 64

Time

TCL0 Input

VDD = 2.0 V to 5.5 V

f

TI

V

= 2.7 V to 5.5 V

DD

0.95

0 – 1.5 MHz

Frequency

TCL0 Input High,

t

TIH

, t

VDD = 2.0 V to 5.5 V

V

= 2.7 V to 5.5 V

TIL

DD

0.48 – –

1 MHz

Low Width

SCK Cycle Time

t

KCY

VDD = 2.0 V to 5.5 V

VDD = 2.7 V to 5.5 V

1.8

800 – – ns

External SCK source

Internal SCK source

VDD = 2.0 V to 5.5 V

670

3200

External SCK source

Internal SCK source

3800

µs

µs

16–8

Page 35

S3C70F2/C70F4/P70F4 S3P70F4 OTP

Table 16-9. A.C. Electrical Characteristics ( Concluded)

(T

= – 40 °C to + 85 °C, V

A

= 2.0 V to 5.5 V)

DD

Parameter Symbol Conditions Min Typ Max Units

SCK High, Low

Width

tKH, t

VDD = 2.7 V to 5.5 V

KL

External SCK source

Internal SCK source

VDD = 2.0 V to 5.5 V

335 – – ns

t

/2 - 50

KCY

1600

External SCK source

t

/2 - 150

KCY

100 – – ns

150

150

SI Setup Time to

SCK High

t

SIK

Internal SCK source

VDD = 2.7 V to 5.5 V

External SCK source

Internal SCK source

VDD = 2.0 V to 5.5 V

External SCK source

500

400 – – ns

400

600

SI Hold Time to

SCK High

t

KSI

Internal SCK source

VDD = 2.7 V to 5.5 V

External SCK source

Internal SCK source

VDD = 2.0 V to 5.5 V

External SCK source

500

– – 300 ns

250

1000

Output Delay for

SCK to SO

t

KSO

Internal SCK source

(1)

VDD = 2.7 V to 5.5 V

External SCK source

Internal SCK source

VDD = 2.0 V to 5.5 V

External SCK source

1000

µs

Interrupt Input

High, Low Width

t

INTH

t

INTL

Internal SCK source

,

INT0

(2)

– –

INT1, KS0–KS2 10

RESET Input

t

RSL

Input 10 – –

µs

Low Width

NOTES:

1. R(1Kohm) and C (100pF) are the load resistance and load capacitance of the SO output line.

2. Minimum value for INT0 is based on a clock of 2t

or 128 / fx as assigned by the IMOD0 register setting.

CY

16–9

Page 36

S3P70F4 OTP S3C70F2/C70F4/P70F4

Table 16-10. RAM Data Retention Supply Voltage in Stop Mode

(TA = – 40 °C to + 85 °C)

Parameter Symbol Conditions Min Typ Max Unit

Data retention supply voltage

Data retention supply current

V

DDDR

I

DDDR

– 2.0 – 5.5 V

V

DDDR

= 2.0 V

– 0.1 10

µA

Release signal set time

Oscillator stabilization wait

(1)

time

NOTES:

1. During oscillator stabilization wait time, all CPU operations must be stopped to avoid instability during oscillator start-up.

2. Use the basic timer mode register (BMOD) interval timer to delay execution of CPU instructions during the wait time.

t

SREL

t

WAIT

– 0 – –

Released by RESET

Released by interrupt –

µs

–

217 / fx

(2)

– ms

– ms

16–10

Page 37

S3C70F2/C70F4/P70F4 S3P70F4 OTP

START

Address= First Location

VDD=5V, VPP=12.5V

x = 0

Program One 1ms Pulse

Increment X

YES

x = 10

NO

FAIL

Device Failed

Verify Byte

FAIL

Verify 1 Byte

Last Address

V

= VPP= 5 V

DD

Compare All Byte

PASS

Device Passed

FAIL

NO

Increment Address

Figure 16-4. OTP Programming Algorithm

16–11

Page 38

S3P70F4 OTP S3C70F2/C70F4/P70F4

NOTES

16–12

Loading...

Loading...