Datasheet PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H, PIC32MX575F512H Datasheet

...

PIC32MX5XX/6XX/7XX

Family Data Sheet

High-Performance, USB, CAN and Ethernet

32-bit Flash Microcontrollers

© 2009-2011 Microchip Technology Inc. DS61156G

Note the following details of the code protection feature on Microchip devices:

• Microchip products meet the specification contained in their particular Microchip Data Sheet.

• Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device

applications and the like is provided only for your convenience

and may be superseded by updates. It is your responsibility to

ensure that your application meets with your specifications.

MICROCHIP MAKES NO REPRESENTATIONS OR

WARRANTIES OF ANY KIND WHETHER EXPRESS OR

IMPLIED, WRITTEN OR ORAL, STATUTORY OR

OTHERWISE, RELATED TO THE INFORMATION,

INCLUDING BUT NOT LIMITED TO ITS CONDITION,

QUALITY, PERFORMANCE, MERCHANTABILITY OR

FITNESS FOR PURPOSE. Microchip disclaims all liability

arising from this information and its use. Use of Microchip

devices in life support and/or safety applications is entirely at

the buyer’s risk, and the buyer agrees to defend, indemnify and

hold harmless Microchip from any and all damages, claims,

suits, or expenses resulting from such use. No licenses are

conveyed, implicitly or otherwise, under any Microchip

intellectual property rights.

Trademarks

The Microchip name and logo, the Microchip logo, dsPIC,

K

EELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART,

32

PIC

logo, rfPIC and UNI/O are registered trademarks of

Microchip Technology Incorporated in the U.S.A. and other

countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor,

MXDEV, MXLAB, SEEVAL and The Embedded Control

Solutions Company are registered trademarks of Microchip

Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard,

dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN,

ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial

Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified

logo, MPLIB, MPLINK, mTouch, Omniscient Code

Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit,

PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance,

TSHARC, UniWinDriver, WiperLock and ZENA are

trademarks of Microchip Technology Incorporated in the

U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated

in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

© 2009-2011, Microchip Technology Incorporated, Printed in

the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-61341-150-6

Microchip received ISO/TS-16949:2002 certification for its worldwide

headquarters, design and wafer fabrication facilities in Chandler and

Tempe, Arizona; Gresham, Oregon and design centers in California

and India. The Company’s quality system processes and procedures

are for its PIC

devices, Serial EEPROMs, microperipherals, nonvolatile memory and

analog products. In addition, Microchip’s quality system for the design

and manufacture of development systems is ISO 9001:2000 certified.

®

MCUs and dsPIC® DSCs, KEELOQ

®

code hopping

DS61156G-page 2 © 2009-2011 Microchip Technology Inc.

PIC32MX5XX/6XX/7XX

High-Performance, USB, CAN and Ethernet

32-bit Flash Microcontrollers

High-Performance 32-bit RISC CPU:

•MIPS32® M4K® 32-bit core with 5-stage pipeline

• 80 MHz maximum frequency

• 1.56 DMIPS/MHz (Dhrystone 2.1) performance

at zero Wait state Flash access

• Single-cycle multiply and high-performance divide

unit

• MIPS16e

• Two sets of 32 core register files (32-bit) to reduce

interrupt latency

• Prefetch Cache module to speed execution from

Flash

®

mode for up to 40% smaller code size

Microcontroller Features:

• Operating voltage range of 2.3V to 3.6V

• 64K to 512K Flash memory (plus an

additional 12 KB of Boot Flash)

• 16K to 128K SRAM memory

• Pin-compatible with most PIC24/dsPIC

devices

• Multiple power management modes

• Multiple interrupt vectors with individually

programmable priority

• Fail-Safe Clock Monitor mode

• Configurable Watchdog Timer with on-chip

Low-Power RC oscillator for reliable operation

®

DSC

Peripheral Features:

• Atomic SET, CLEAR and INVERT operation on

select peripheral registers

• Up to 8-channels of hardware DMA with automatic

data size detection

• USB 2.0-compliant full-speed device and

On-The-Go (OTG) controller:

- Dedicated DMA channels

• 10/100 Mbps Ethernet MAC with MII and RMII

interface:

- Dedicated DMA channels

• CAN module:

- 2.0B Active with DeviceNet™ addressing

support

- Dedicated DMA channels

• 3 MHz to 25 MHz crystal oscillator

Peripheral Features (Continued):

• Internal 8 MHz and 32 kHz oscillators

• Six UART modules with:

- RS-232, RS-485 and LIN support

-IrDA

• Up to four SPI modules

• Up to five I

• Separate PLLs for CPU and USB clocks

• Parallel Master and Slave Port (PMP/PSP) with

8-bit and 16-bit data, and up to 16 address lines

• Hardware Real-Time Clock and Calendar (RTCC)

• Five 16-bit Timers/Counters (two 16-bit pairs

combine to create two 32-bit timers)

• Five Capture inputs

• Five Compare/PWM outputs

• Five external interrupt pins

• High-speed I/O pins capable of toggling at up

to 80 MHz

• High-current sink/source (18 mA/18 mA) on

all I/O pins

• Configurable open-drain output on digital I/O pins

®

with on-chip hardware encoder and

decoder

2

C™ modules

Debug Features:

• Two programming and debugging Interfaces:

- 2-wire interface with unintrusive access and

real-time data exchange with application

- 4-wire MIPS

Action Group (JTAG) interface

• Unintrusive hardware-based instruction trace

• IEEE Standard 1149.2 compatible (JTAG)

boundary scan

®

standard enhanced Joint Test

Analog Features:

• Up to 16-channel, 10-bit Analog-to-Digital

Converter:

- 1 Msps conversion rate

- Conversion available during Sleep and Idle

• Two Analog Comparators

© 2009-2011 Microchip Technology Inc. DS61156G-page 3

PIC32MX5XX/6XX/7XX

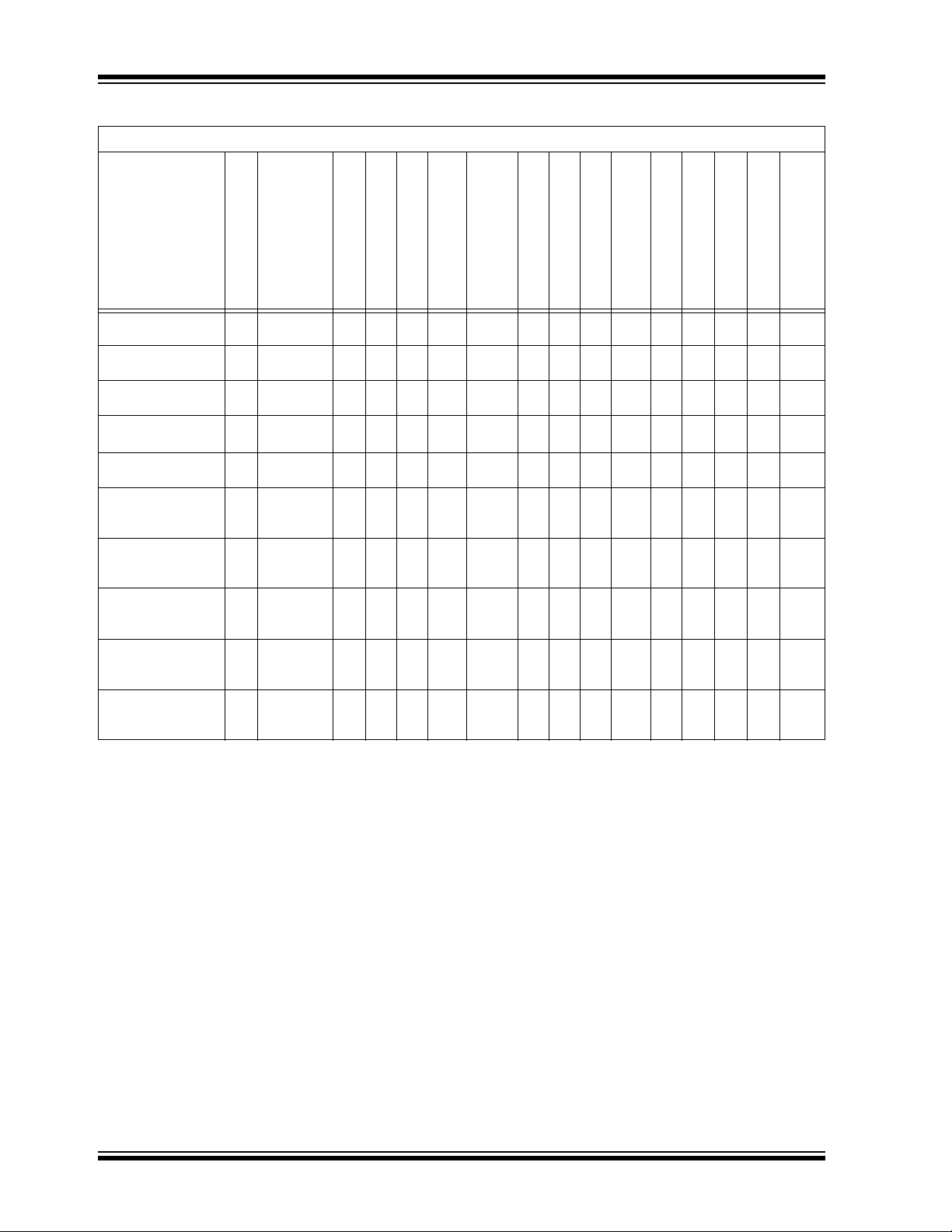

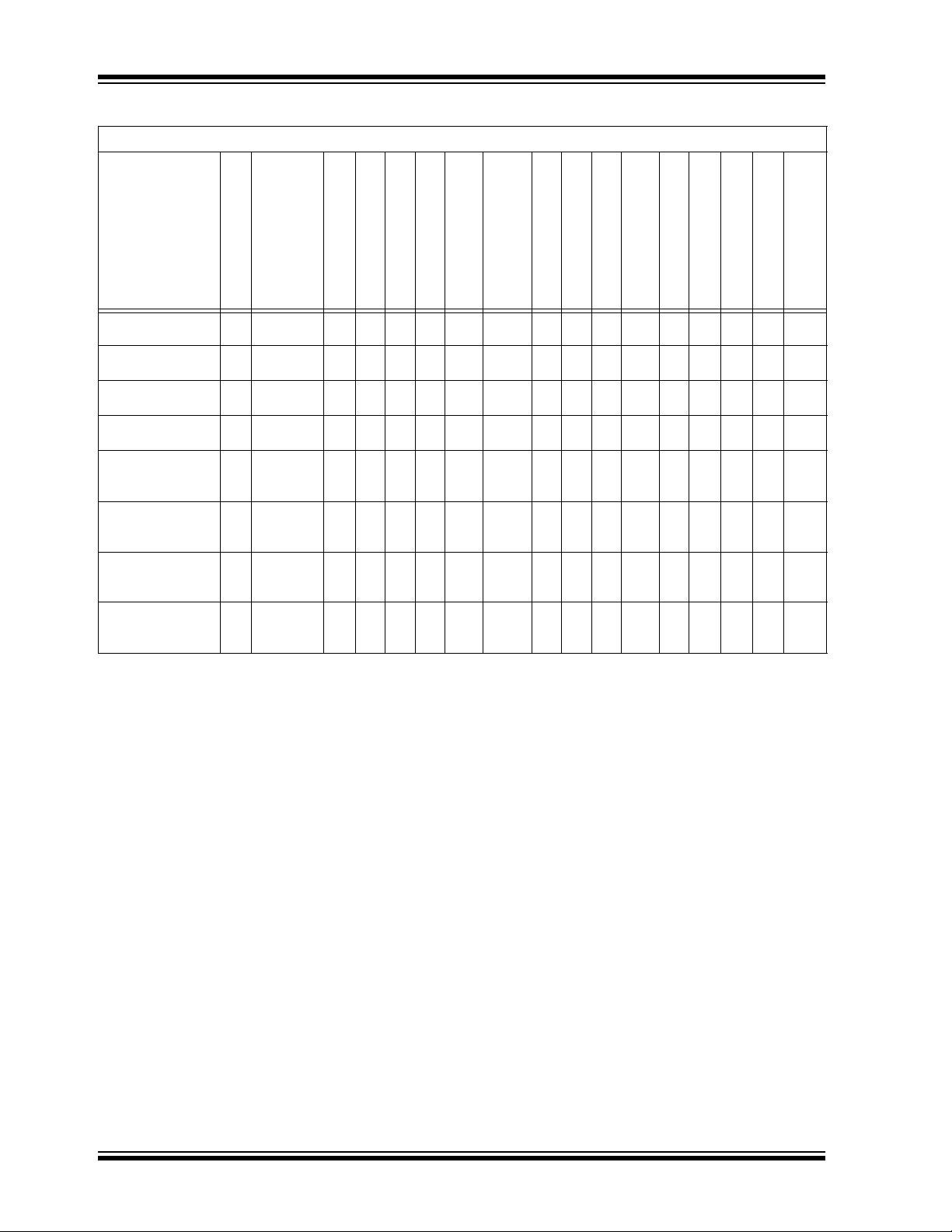

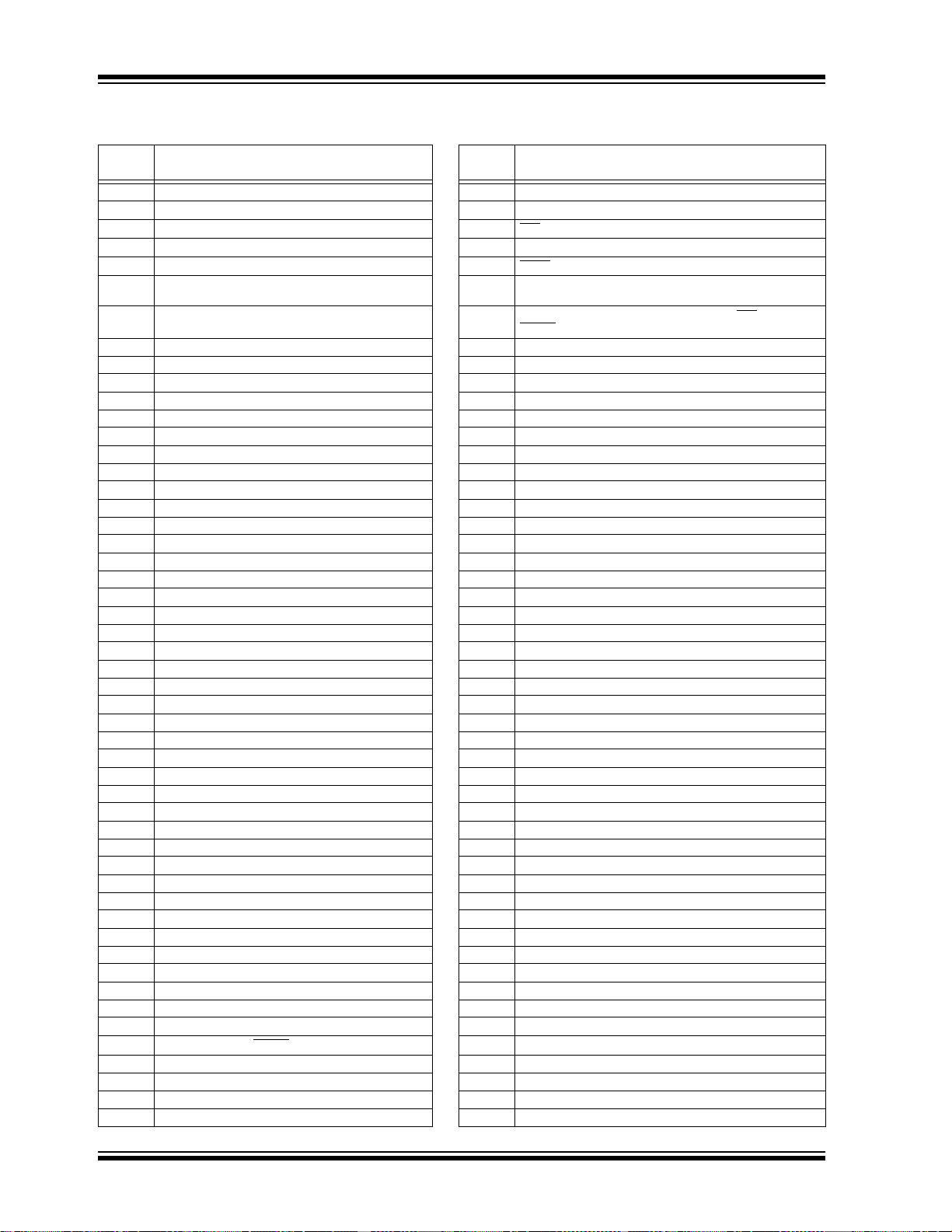

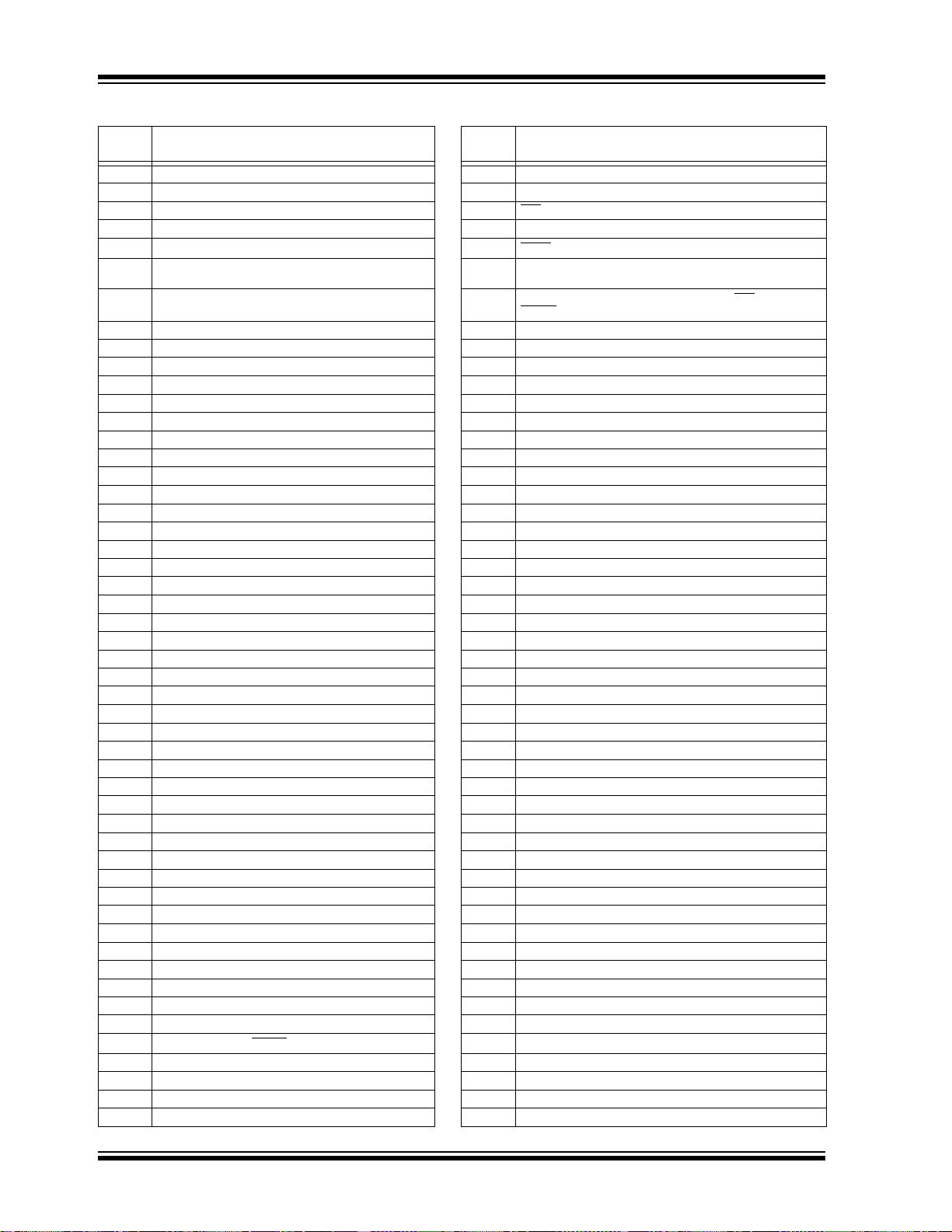

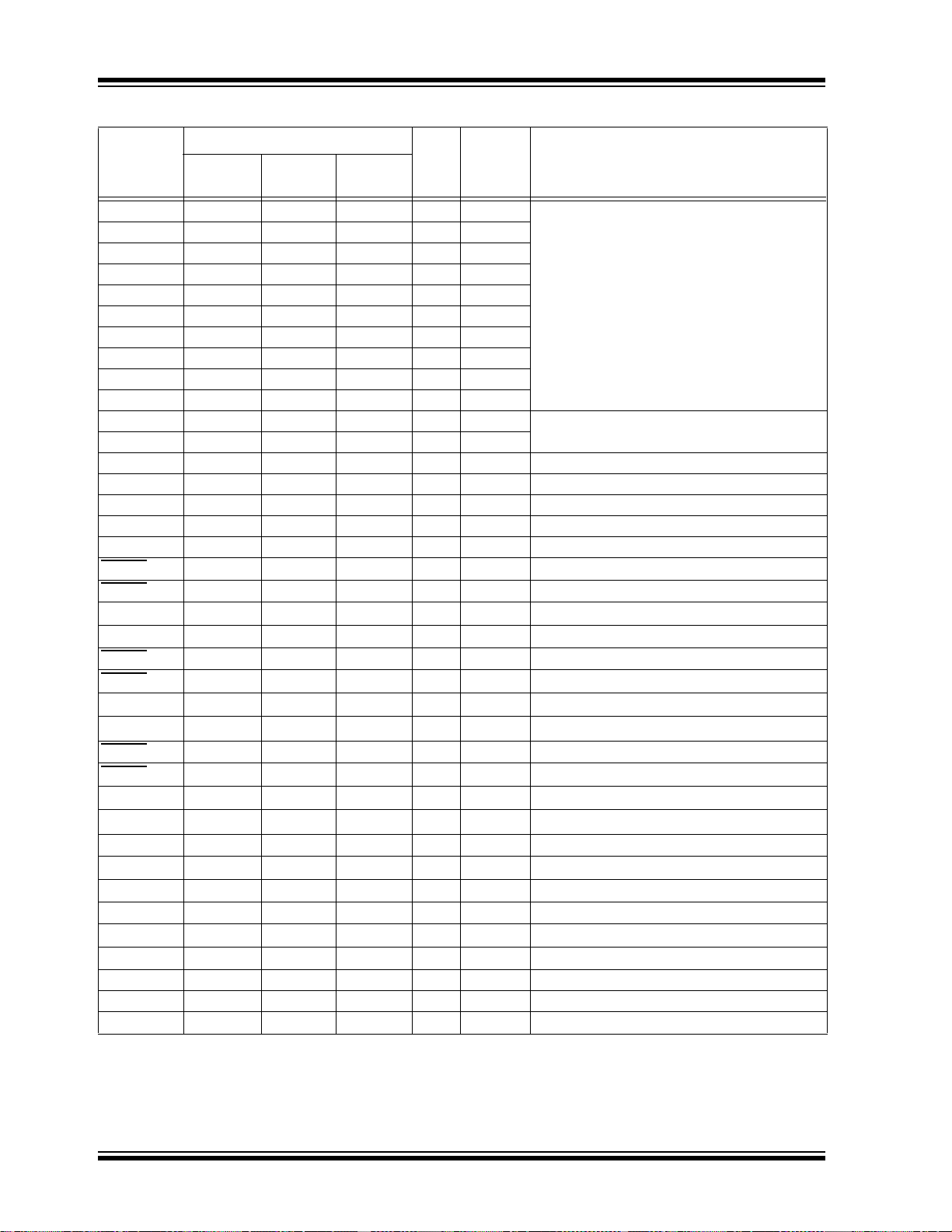

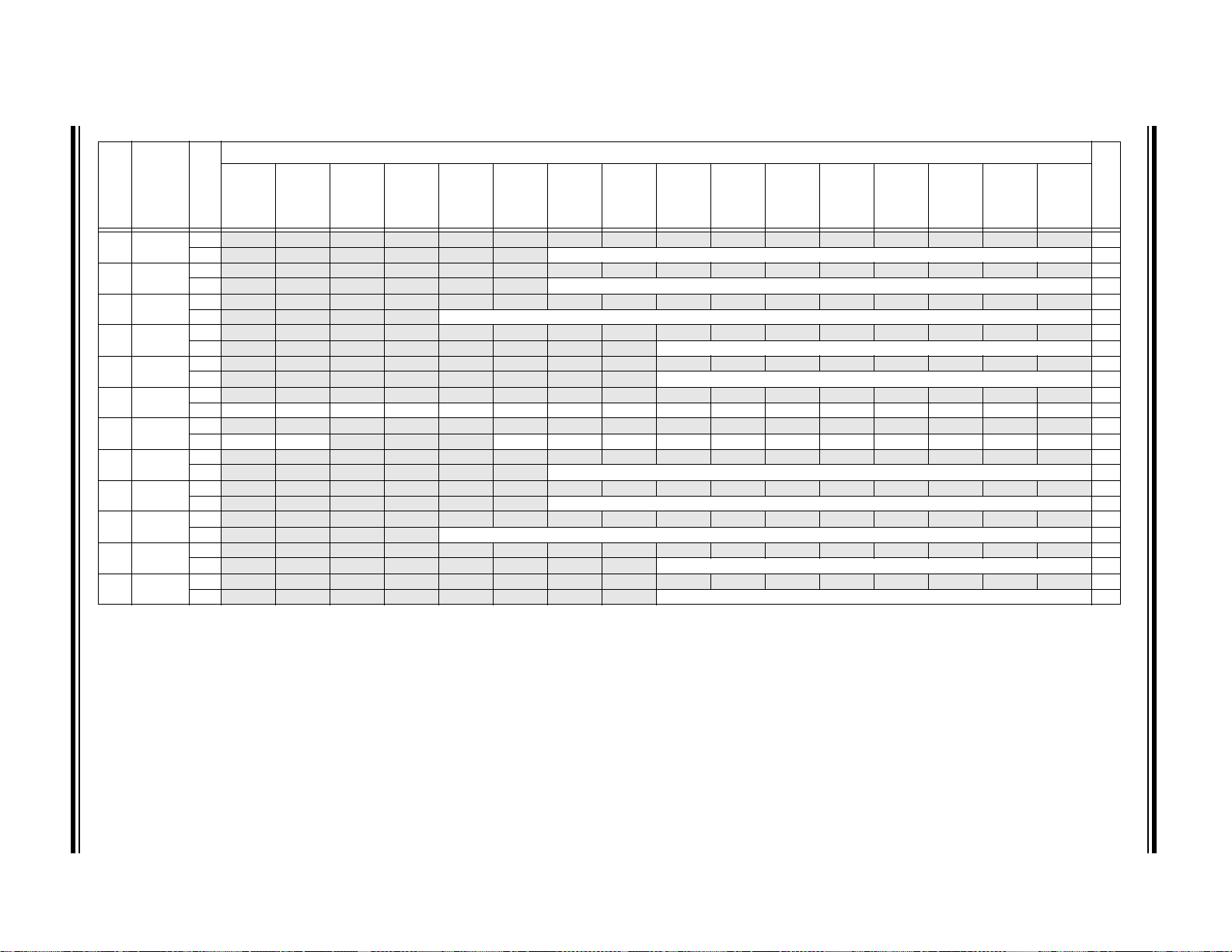

TABLE 1: PIC32 USB AND CAN – FEATURES

USB and CAN

(3)

SPI

(3)

2

C™

I

(Channels)

Comparators

10-bit 1 Msps ADC

Device

Pins

Program Memory (KB)

PIC32MX534F064H 64 64 + 12

PIC32MX564F064H 64 64 + 12

PIC32MX564F128H 64 128 + 12

PIC32MX575F256H 64 256 + 12

PIC32MX575F512H 64 512 + 12

PIC32MX534F064L 100 64 + 12

PIC32MX564F064L 100 64 + 12

PIC32MX564F128L 100 128 + 12

PIC32MX575F256L 100 256 + 12

PIC32MX575F512L 100 512 + 12

(2,3)

USB

Data Memory (KB)

CAN

DMA Channels

UART

Dedicated)

(Programmable/

Timers/Capture/Compare

(1)

16 1 1 5/5/5 4/4 6 3 4 16 2 Yes Yes No

(1)

32 1 1 5/5/5 4/4 6 3 4 16 2 Yes Yes No

(1)

32 1 1 5/5/5 4/4 6 3 4 16 2 Yes Yes No

(1)

64 1 1 5/5/5 8/4 6 3 4 16 2 Yes Yes No

(1)

64 1 1 5/5/5 8/4 6 3 4 16 2 Yes Yes No

(1)

16 1 1 5/5/5 4/4 6 4 5 16 2 Yes Yes Yes

(1)

32 1 1 5/5/5 4/4 6 4 5 16 2 Yes Yes Yes

(1)

32 1 1 5/5/5 4/4 6 4 5 16 2 Yes Yes Yes

(1)

64 1 1 5/5/5 8/4 6 4 5 16 2 Yes Yes Yes

(1)

64 1 1 5/5/5 8/4 6 4 5 16 2 Yes Yes Yes

Legend: PF, PT = TQFP MR = QFN BG = XBGA

Note 1: This device features 12 KB boot Flash memory.

2: CTS and RTS pins may not be available for all UART modules. Refer to the “Pin Diagrams” section for more

information.

3: Some pins between the UART, SPI and I

2

C modules may be shared. Refer to the “Pin Diagrams” section for more

information.

4: Refer to Section 32.0 “Packaging Information” for more information.

PMP/PSP

JTAG

(4)

Trace

Packages

PT,

MR

PT,

MR

PT,

MR

PT,

MR

PT,

MR

PT,

PF,

BG

PT,

PF,

BG

PT,

PF,

BG

PT,

PF,

BG

PT,

PF,

BG

DS61156G-page 4 © 2009-2011 Microchip Technology Inc.

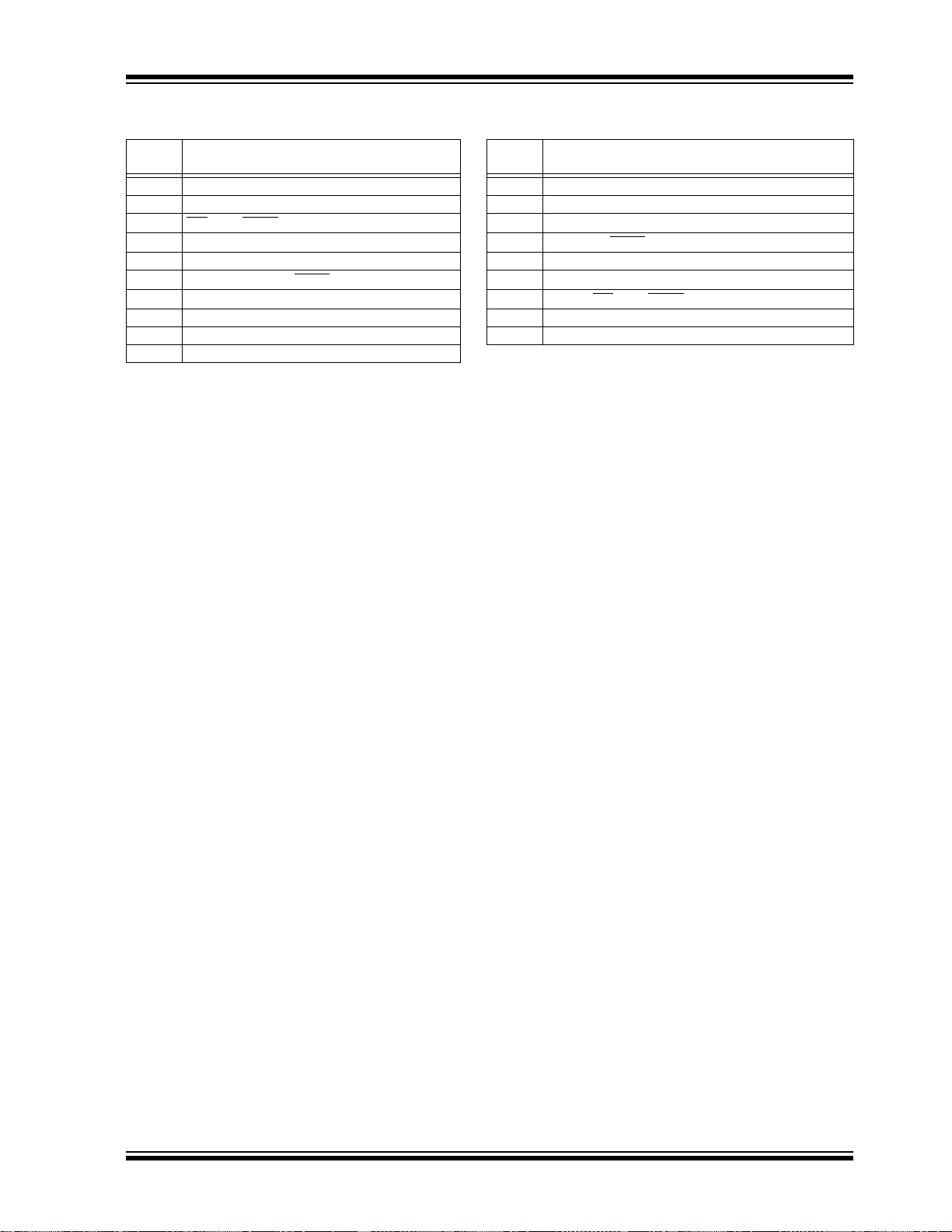

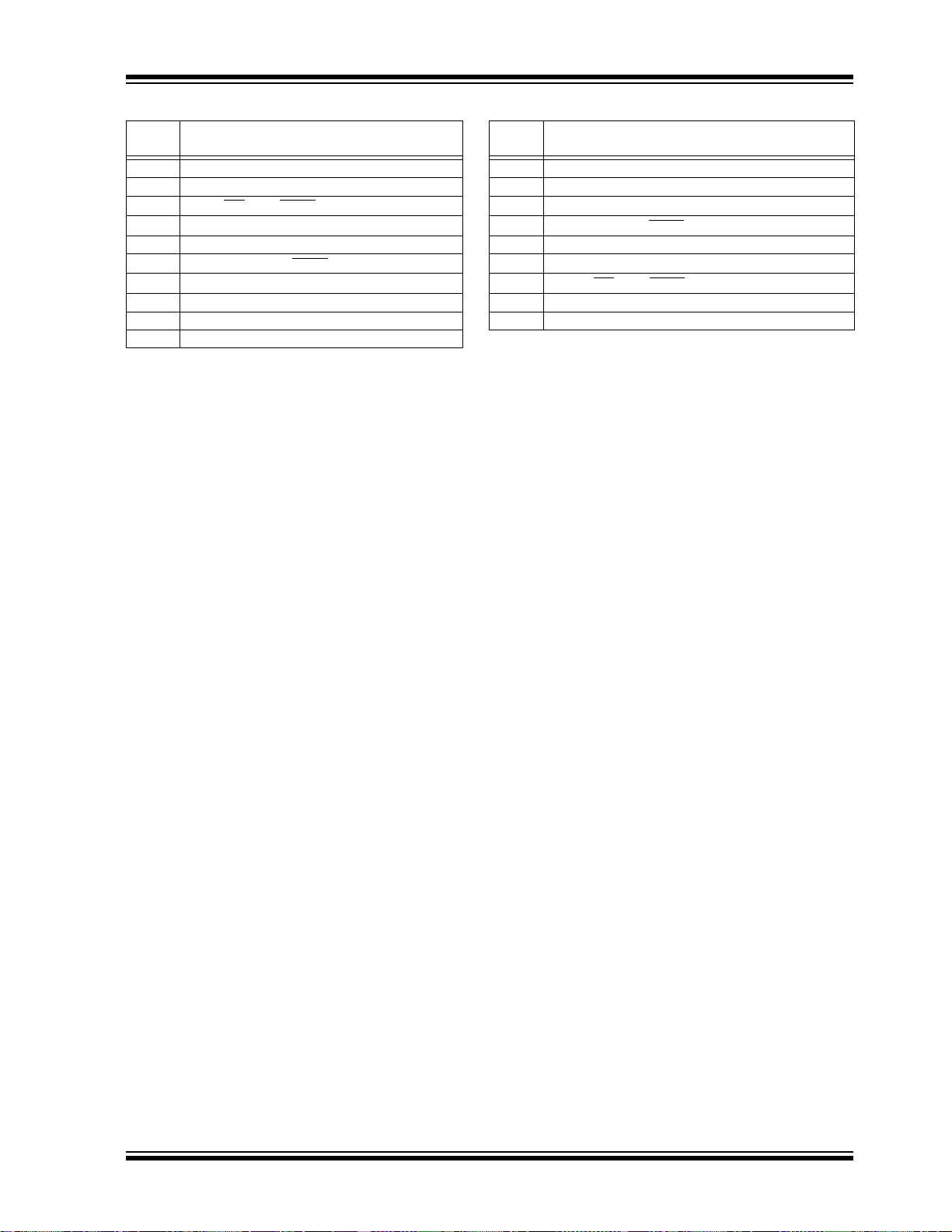

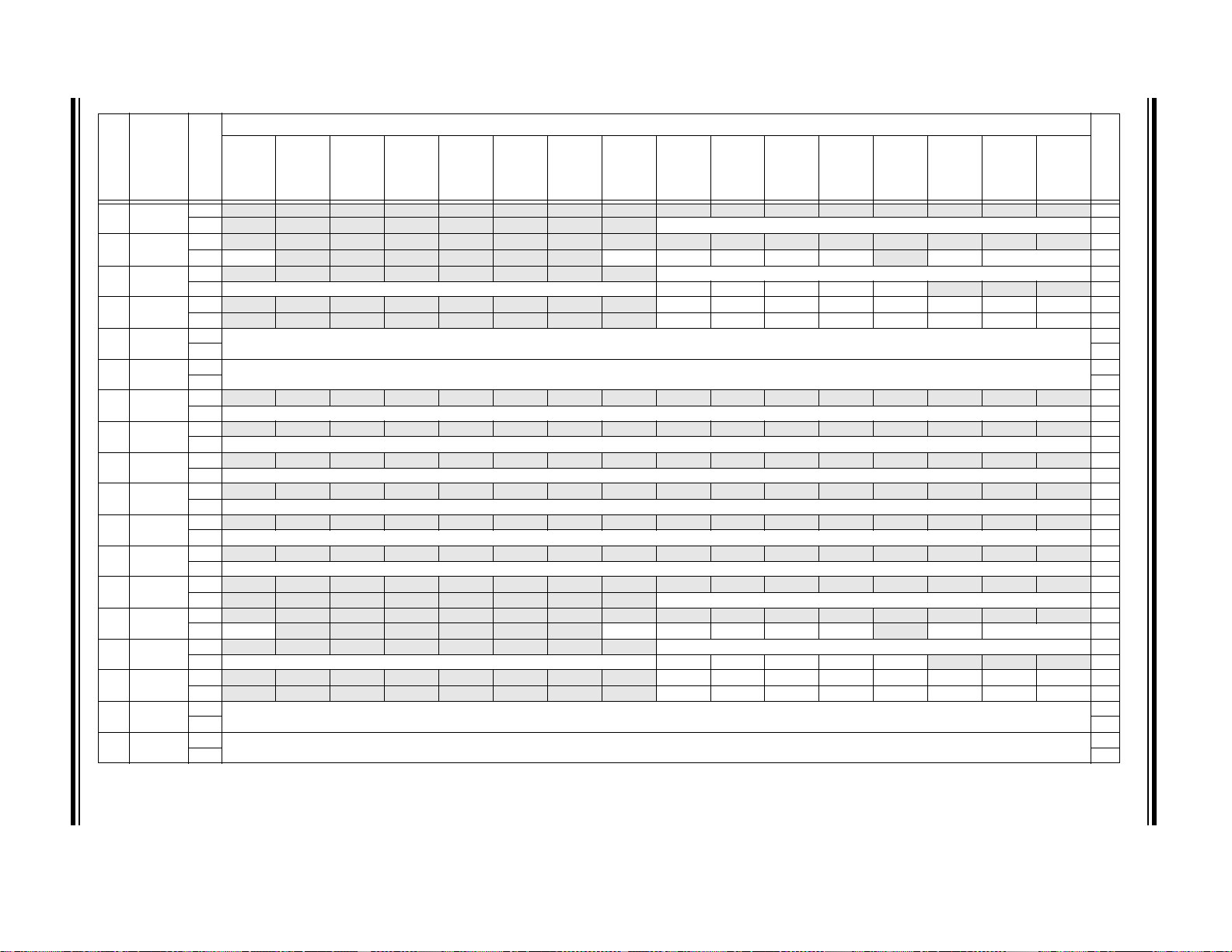

TABLE 2: PIC32 USB AND ETHERNET – FEATURES

USB and Ethernet

PIC32MX5XX/6XX/7XX

(3)

SPI

(3)

2

C™

I

(Channels)

10-bit 1 Msps ADC

Comparators

Device

Pins

Program Memory (KB)

PIC32MX664F064H 64 64 + 12

PIC32MX664F128H 64 128 + 12

PIC32MX675F256H 64 256 + 12

PIC32MX675F512H 64 512 + 12

PIC32MX695F512H 64 512 + 12

PIC32MX664F064L 100 64 + 12

PIC32MX664F128L 100 128 + 12

PIC32MX675F256L 100 256 + 12

PIC32MX675F512L 100 512 + 12

PIC32MX695F512L 100

512 + 12

(2,3)

USB

Ethernet

Data Memory (KB)

DMA Channels

UART

Dedicated)

(Programmable/

Timers/Capture/Compare

(1)

32 1 1 5/5/5 4/4 6 3 4 16 2 Yes Yes No

(1)

32 1 1 5/5/5 4/4 6 3 4 16 2 Yes Yes No

(1)

64 1 1 5/5/5 8/4 6 3 4 16 2 Yes Yes No

(1)

64 1 1 5/5/5 8/4 6 3 4 16 2 Yes Yes No

(1)

128 1 1 5/5/5 8/4 6 3 4 16 2 Yes Yes No

(1)

32 1 1 5/5/5 4/4 6 4 5 16 2 Yes Yes Yes

(1)

32 1 1 5/5/5 4/4 6 4 5 16 2 Yes Yes Yes

(1)

64 1 1 5/5/5 8/4 6 4 5 16 2 Yes Yes Yes

(1)

64 1 1 5/5/5 8/4 6 4 5 16 2 Yes Yes Yes

(1)

128 1 1 5/5/5 8/4 6 4 5 16 2 Yes Yes Yes

Legend: PF, PT = TQFP MR = QFN BG = XBGA

Note 1: This device features 12 KB boot Flash memory.

2: CTS and RTS pins may not be available for all UART modules. Refer to the “Pin Diagrams” section for more

information.

3: Some pins between the UART, SPI and I

2

C modules may be shared. Refer to the “Pin Diagrams” section for more

information.

4: Refer to Section 32.0 “Packaging Information” for more information.

JTAG

PMP/PSP

(4)

Trace

Packages

PT,

MR

PT,

MR

PT,

MR

PT,

MR

PT,

MR

PT,

PF,

BG

PT,

PF,

BG

PT,

PF,

BG

PT,

PF,

BG

PT,

PF,

BG

© 2009-2011 Microchip Technology Inc. DS61156G-page 5

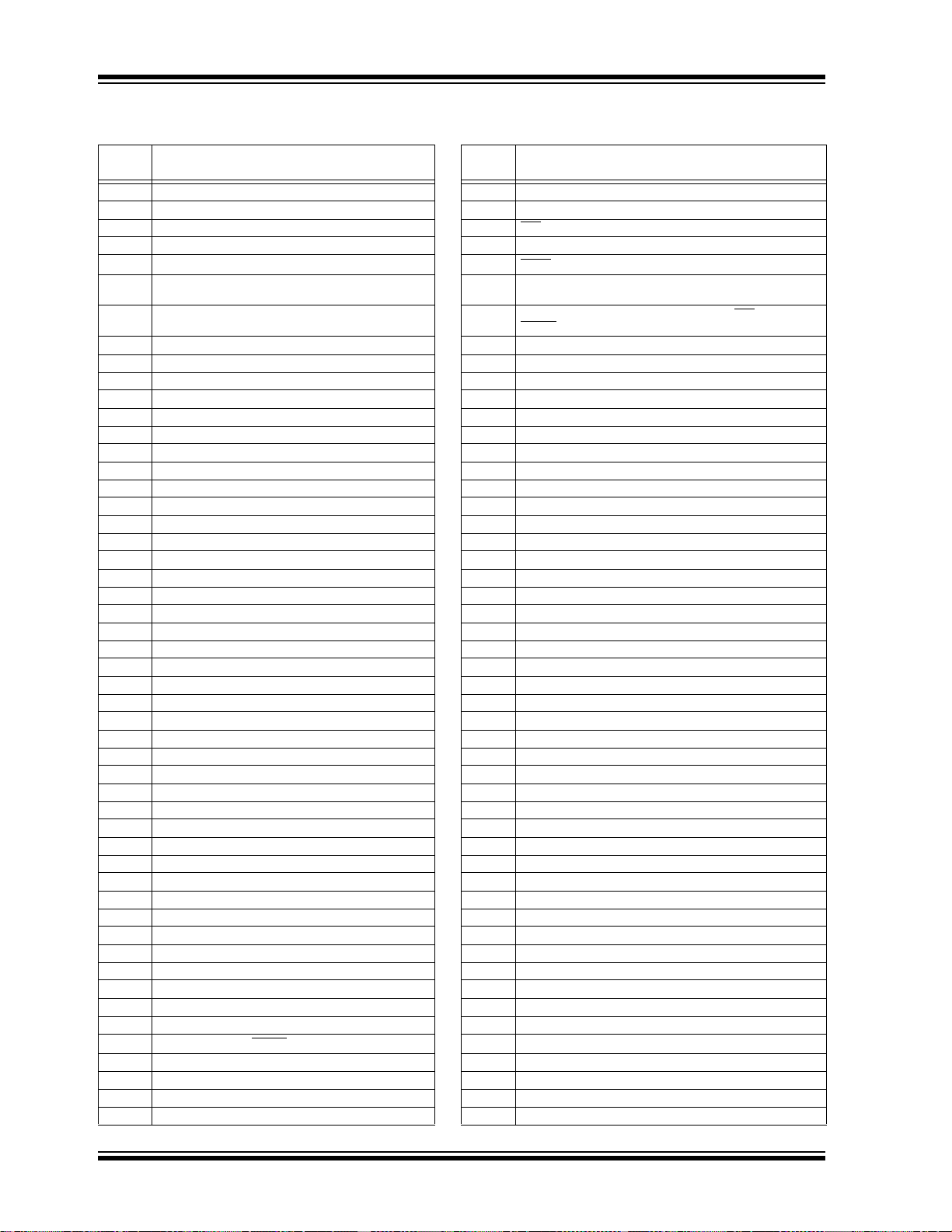

PIC32MX5XX/6XX/7XX

TABLE 3: PIC32 USB, ETHERNET AND CAN – FEATURES

USB, Ethernet and CAN

(3)

SPI

(3)

2

C™

I

(Channels)

Comparators

10-bit 1 Msps ADC

Device

Pins

Program Memory (KB)

PIC32MX764F128H 64 128 + 12

PIC32MX775F256H 64 256 + 12

PIC32MX775F512H 64 512 + 12

PIC32MX795F512H 64 512 + 12

PIC32MX764F128L 100 128 + 12

PIC32MX775F256L 100 256 + 12

PIC32MX775F512L 100 512 + 12

PIC32MX795F512L 100 512 + 12

(2,3)

USB

Data Memory (KB)

CAN

Ethernet

DMA Channels

UART

Dedicated)

(Programmable/

Timers/Capture/Compare

(1)

32 1 1 1 5/5/5 4/6 6 3 4 16 2 Yes Yes No

(1)

64 1 1 2 5/5/5 8/8 6 3 4 16 2 Yes Yes No

(1)

64 1 1 2 5/5/5 8/8 6 3 4 16 2 Yes Yes No

(1)

128 1 1 2 5/5/5 8/8 6 3 4 16 2 Yes Yes No

(1)

32 1 1 1 5/5/5 4/6 6 4 5 16 2 Yes Yes Yes

(1)

64 1 1 2 5/5/5 8/8 6 4 5 16 2 Yes Yes Yes

(1)

64 1 1 2 5/5/5 8/8 6 4 5 16 2 Yes Yes Yes

(1)

128 1 1 2 5/5/5 8/8 6 4 5 16 2 Yes Yes Yes

Legend: PF, PT = TQFP MR = QFN BG = XBGA

Note 1: This device features 12 KB boot Flash memory.

2: CTS and RTS pins may not be available for all UART modules. Refer to the “Pin Diagrams” section for more

information.

3: Some pins between the UART, SPI and I

2

C modules may be shared. Refer to the “Pin Diagrams” section for more

information.

4: Refer to Section 32.0 “Packaging Information” for more information.

PMP/PSP

JTAG

(4)

Trace

Packages

PT,

MR

PT,

MR

PT,

MR

PT,

MR

PT,

PF,

BG

PT,

PF,

BG

PT,

PF,

BG

PT,

PF,

BG

DS61156G-page 6 © 2009-2011 Microchip Technology Inc.

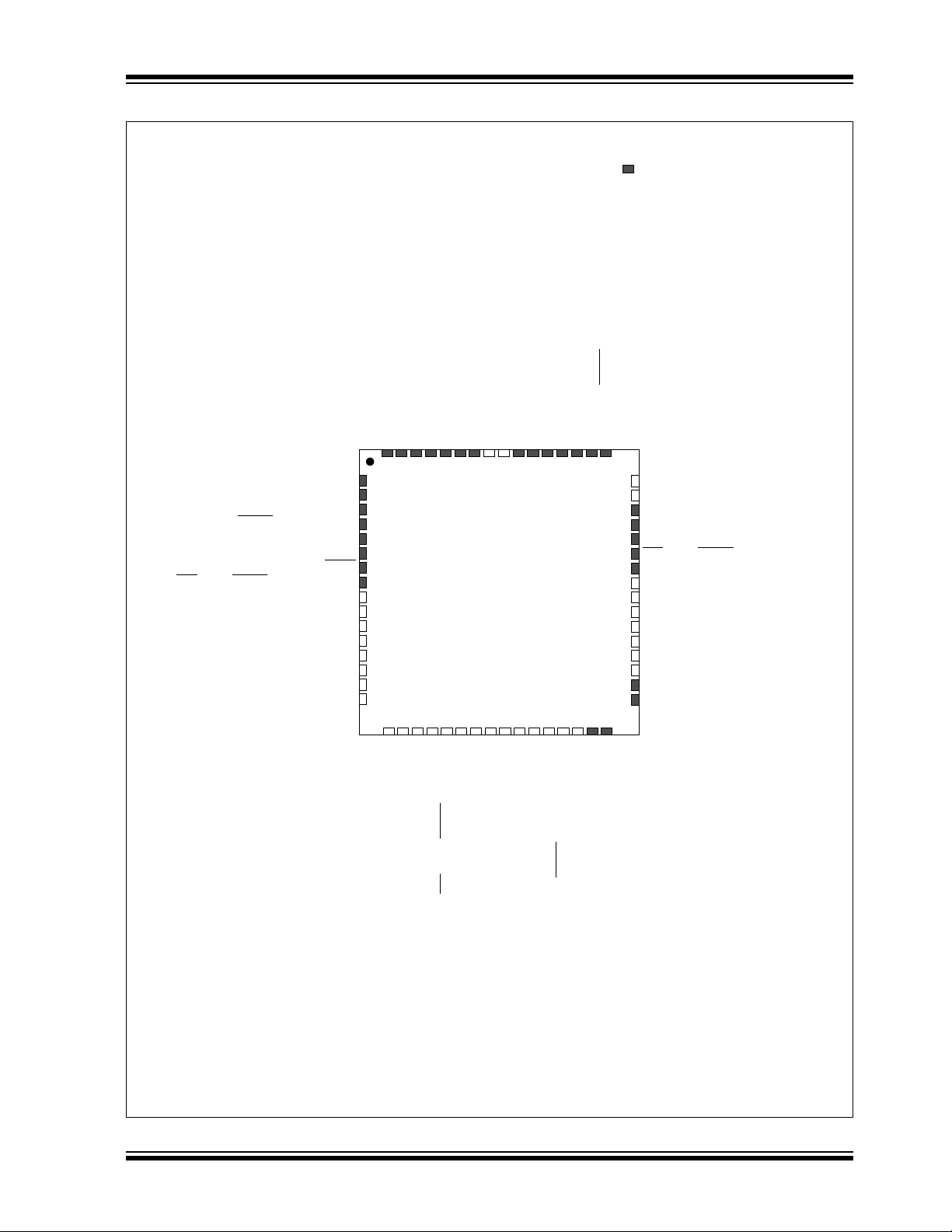

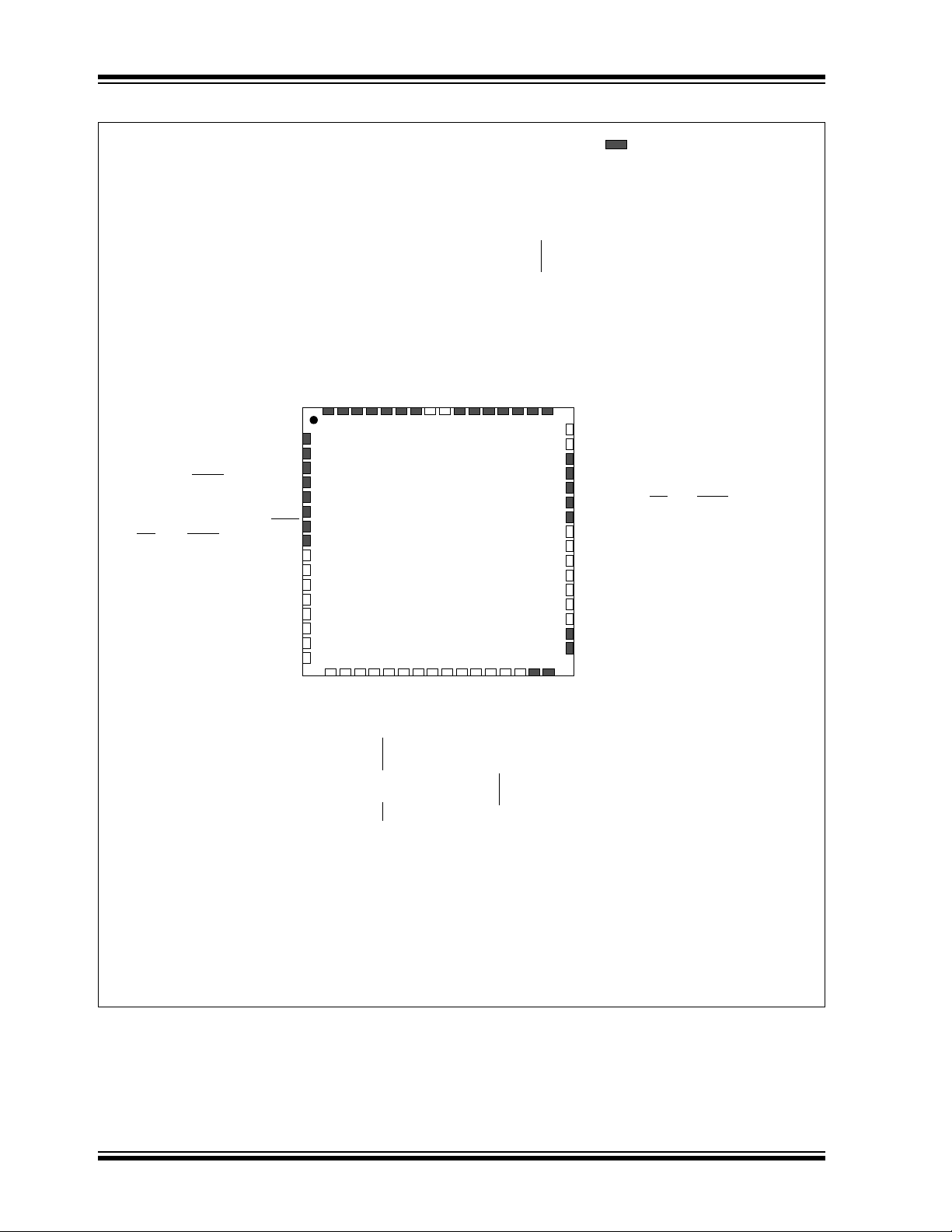

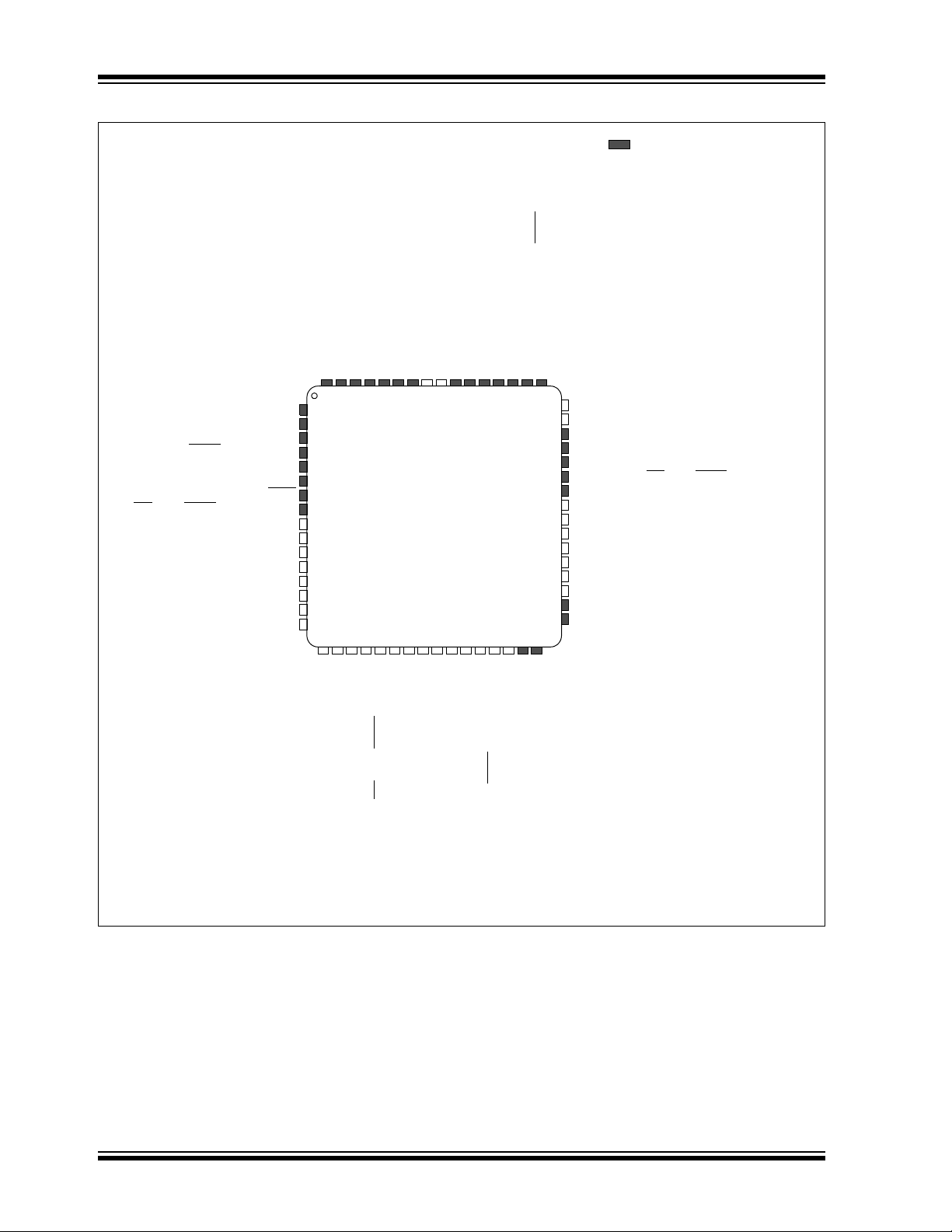

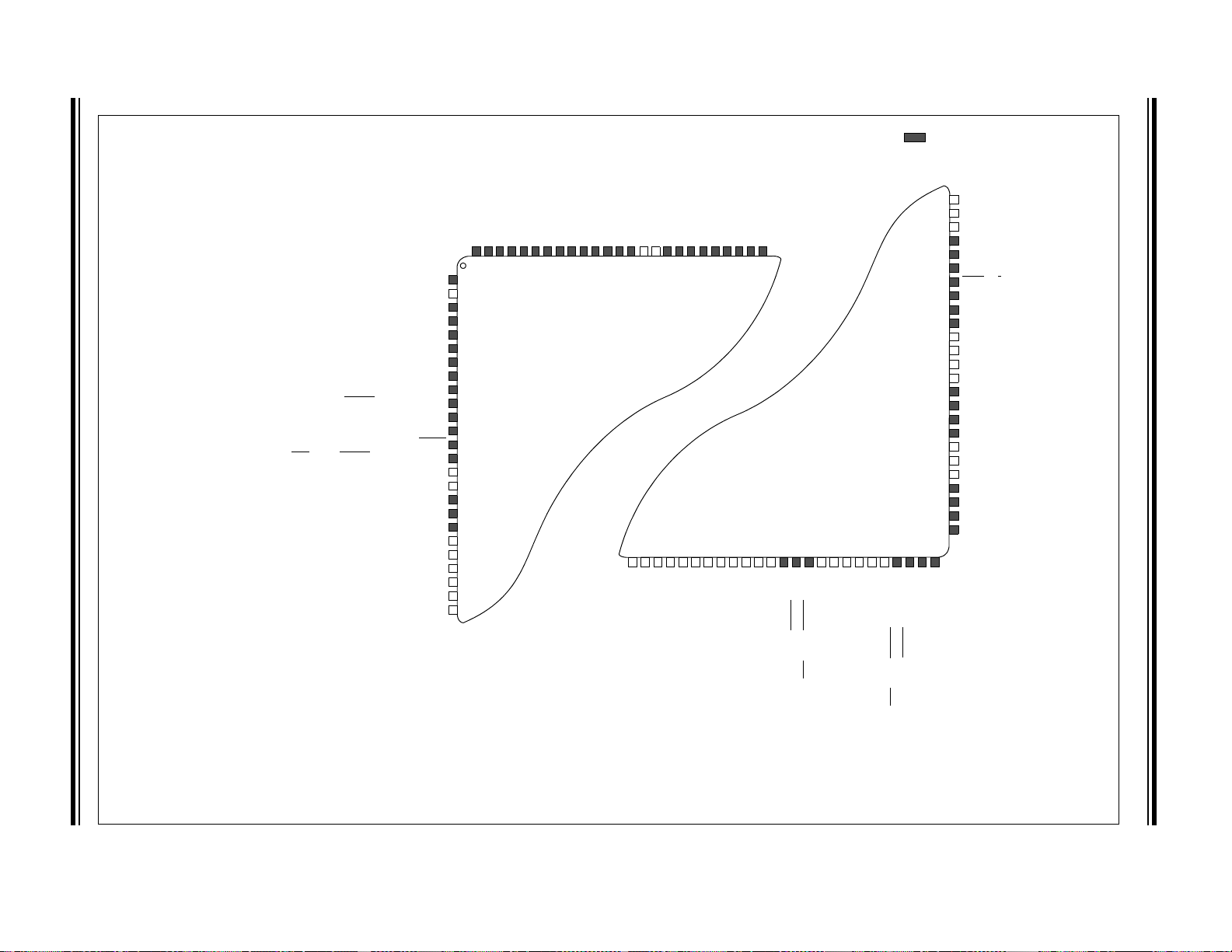

Pin Diagrams

64-Pin QFN

(1)

= Pins are up to 5V tolerant

Note 1: The metal plane at the bottom of the device is not connected to any pins and is recommended to be

connected to V

SS externally.

PIC32MX575F256H

PMD5/RE5

PMD6/RE6

PMD7/RE7

SCK2/U6TX/U3RTS

/PMA5/CN8/RG6

V

DD

AN5/C1IN+/VBUSON/CN7/RB5

AN4/C1IN-/CN6/RB4

AN3/C2IN+/CN5/RB3

AN2/C2IN-/CN4/RB2

SDA4/SDI2/U3RX/PMA4/CN9/RG7

SCL4/SDO2/U3TX/PMA3/CN10/RG8

PGEC1/AN1/V

REF-/CVREF-/CN3/RB1

PGED1/AN0/V

REF+/CVREF+/PMA6/CN2/RB0

SS2

/U6RX/U3CTS/PMA2/CN11/RG9

MCLR

VSS

64 63 62 61 60 59 58 57 56 55

22 23 24 25 26 27 28 29 30 31

3

40

39

38

37

36

35

34

33

4

5

7

8

9

10

11

1

2

42

41

6

32

43

54

14

15

16

12

13

17

18 19 20 21

45

44

47

46

48

53

52 51 50 49

AVDD

AN8/SS4/U5RX/U2CTS/C1OUT/RB8

AN9/C2OUT/PMA7/RB9

TMS/AN10/CV

REFOUT/PMA13/RB10

TDO/AN11/PMA12/RB11

V

DD

PGEC2/AN6/OCFA/RB6

PGED2/AN7/RB7

AC1RX/SCL5/SDO4/U2TX/PMA8/CN18/RF5

AC1TX/SDA5/SDI4/U2RX/PMA9/CN17/RF4

TCK/AN12/PMA11/RB12

TDI/AN13/PMA10/RB13

AN14/SCK4/U5TX/U2RTS

/PMALH/PMA1/RB14

AN15/OCFB/PMALL/PMA0/CN12/RB15

V

SS

AVSS

CN15/RD6

PMRD/CN14/RD5

OC5/IC5/PMWR/CN13/RD4

SCL3/SDO3/U1TX/OC4/RD3

SDA3/SDI3/U1RX/OC3/RD2

SCK3/U4TX/U1RTS

/OC2/RD1

PMD4/RE4

PMD3/RE3

PMD2/RE2

PMD1/RE1

C1RX/RF0

V

CAP/VCORE

PMD0/RE0

C1TX/RF1

CN16/RD7

V

DD

SOSCI/CN1/RC13

OC1/INT0/RD0

SCL1/IC3/PMCS2/PMA15/INT3/RD10

SS3

/U4RX/U1CTS/SDA1/IC2/INT2/RD9

RTCC/IC1/INT1/RD8

IC4/PMCS1/PMA14/INT4/RD11

OSC2/CLKO/RC15

OSC1/CLKI/RC12

V

DD

D+/RG2

V

USB

VBUS

USBID/RF3

D-/RG3

SOSCO/T1CK/CN0/RC14

Vss

PIC32MX575F512H

PIC32MX534F064H

PIC32MX564F064H

PIC32MX564F128H

PIC32MX5XX/6XX/7XX

© 2009-2011 Microchip Technology Inc. DS61156G-page 7

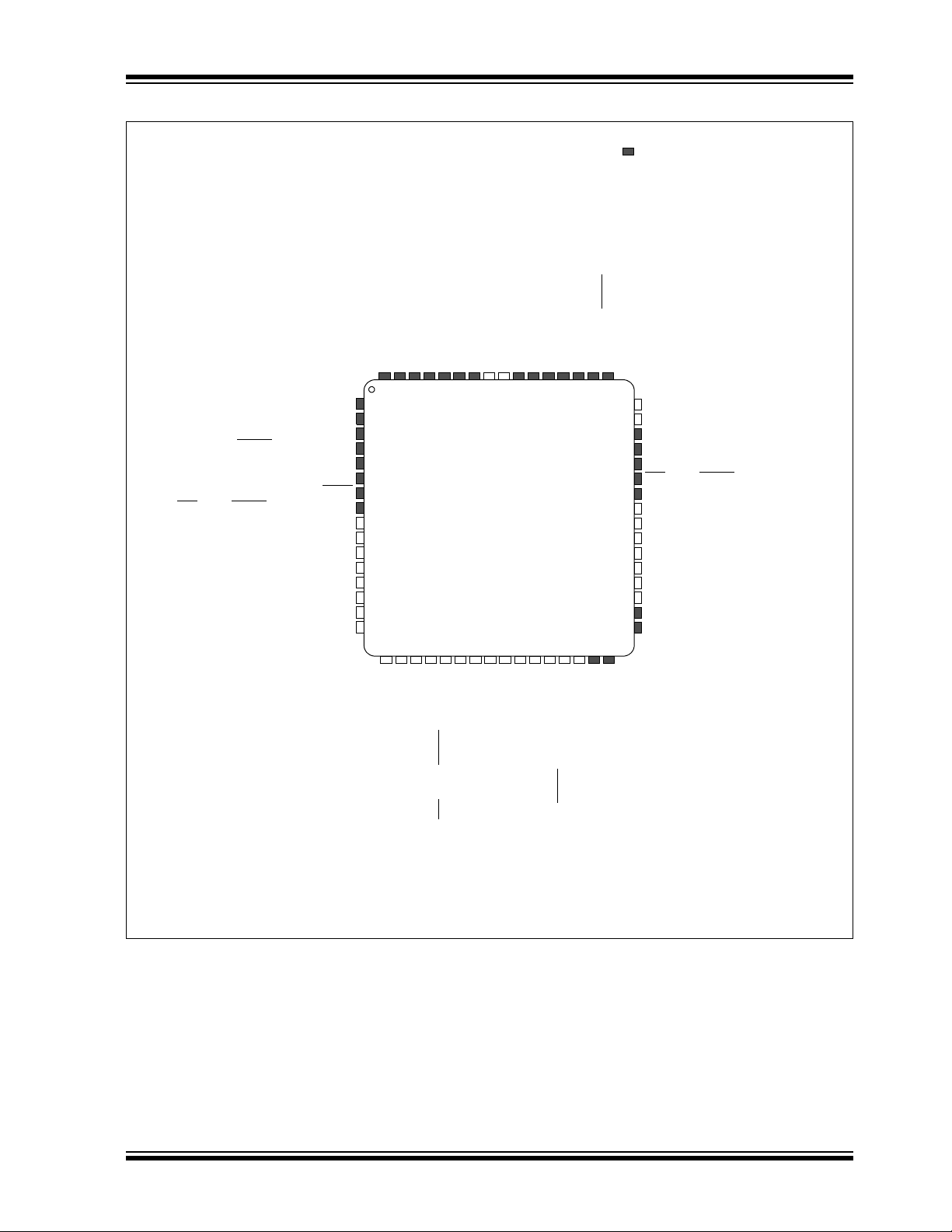

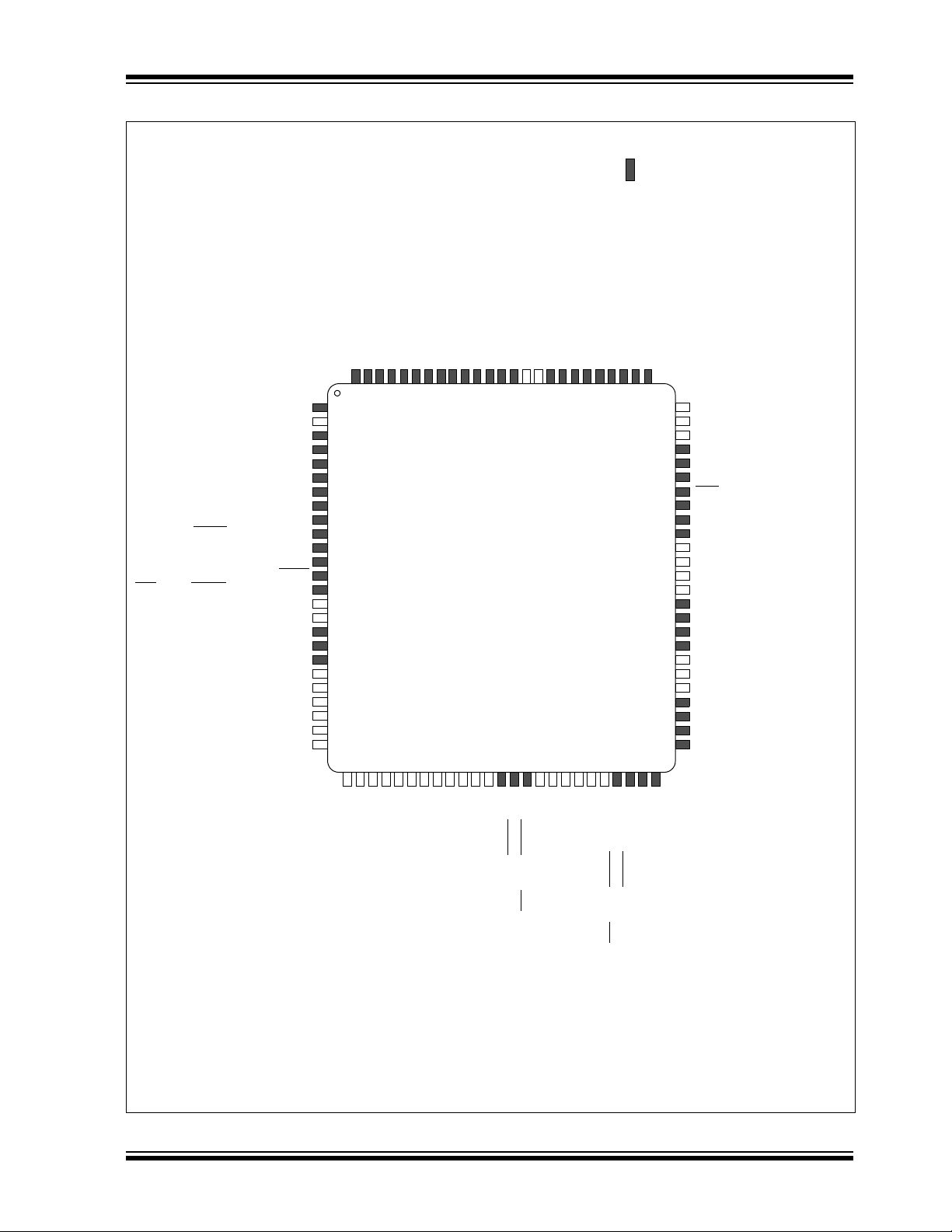

PIC32MX5XX/6XX/7XX

64-Pin QFN

(1)

= Pins are up to 5V tolerant

PIC32MX675F512H

PIC32MX695F512H

PIC32MX675F256H

22 23 24 25 26 27 28 29 30 31

40

39

38

37

36

35

34

33

42

41

32

43

17

18 19 20 21

45

44

47

46

48

AV

DD

AN8/SS4/U5RX/U2CTS/C1OUT/RB8

AN9/C2OUT/PMA7/RB9

TMS/AN10/CV

REFOUT

/PMA13/RB10

TDO/AN11/PMA12/RB11

V

DD

PGEC2/AN6/OCFA/RB6

PGED2/AN7/RB7

SCL5/SDO4/U2TX/PMA8/CN18/RF5

SDA5/SDI4/U2RX/PMA9/CN17/RF4

TCK/AN12/PMA11/RB12

TDI/AN13/PMA10/ RB13

AN14/SCK4/U5TX/U2RTSU2RTS

/PMALH/PMA1/RB14

AN15/EMDC/AEMDC/OCFB/PMALL/PMA0/CN12/RB15

V

SS

AV

SS

SOSCI/CN1/RC13

OC1/INT0/RD0

ECOL/AECRSDV/SCL1/IC3/PMCS2/PMA15/INT3/RD10

AERXD0/ETXD2/SS3

/U4RX/U1CTS/SDA1/IC2/INT2/RD9

RTCC/AERXD1/ETXD3/IC1/INT1/RD8

ECRS/AEREFCLK/IC4/PMCS1/PMA14/INT4/RD11

OSC2/CLKO/RC15

OSC1/CLKI/RC12

V

DD

D+/RG2

V

USB

V

BUS

USBID/RF3

D-/RG3

SOSCO/T1CK/CN0/RC14

Vss

ETXEN/PMD5/RE5

ETXD0/PMD6/RE6

ETXD1/PMD7/RE7

SCK2/U6TX/U3RTS

/PMA5/CN8/RG6

V

DD

AN5/C1IN+/V

BUSON

/CN7/RB5

AN4/C1IN-/CN6/RB4

AN3/C2IN+/CN5/ RB3

AN2/C2IN-/CN4/RB2

SDA4/SDI2/U3RX/PMA4/CN9/RG7

SCL4/SDO2/U3TX/PMA3/CN10/RG8

PGEC1/AN1/V

REF

-/CV

REF

-/CN3/RB1

PGED1/AN0/V

REF

+/CV

REF

+/PMA6/CN2/RB0

SS2

/U6RX/U3CTS/PMA2/CN11/RG9

MCLR

V

SS

64 63 62 61 60 59 58 57 56 55

3

4

5

7

8

9

10

11

1

2

6

54

14

15

16

12

13

53

52 51 50 49

AETXEN/ETXERR/CN15/RD6

PMRD/CN14/RD5

OC5/IC5/PMWR/CN13/RD4

SCL3/SDO3/U1TX/OC4/RD3

SDA3/SDI3/U1RX/OC3/RD2

EMDIO/AEMDIO/SCK3/U4TX/U1RTS

/OC2/RD1

ERXERR/PMD4/RE4

ERXCLK/EREFCLK/PMD3/RE3

ERXDV/ECRSDV/PMD2/RE2

ERXD0/PMD1/RE1

AETXD1/ERXD3/RF0

V

CAP

/V

CORE

ERXD1/PMD0/RE0

AETXD0/ERXD2/RF1

ETXCLK/AERXERR/CN16/RD7

V

DD

Note 1: The metal plane at the bottom of the device is not connected to any pins and is recommended to be

connected to VSS externally.

PIC32MX664F064H

PIC32MX664F128H

Pin Diagrams (Continued)

DS61156G-page 8 © 2009-2011 Microchip Technology Inc.

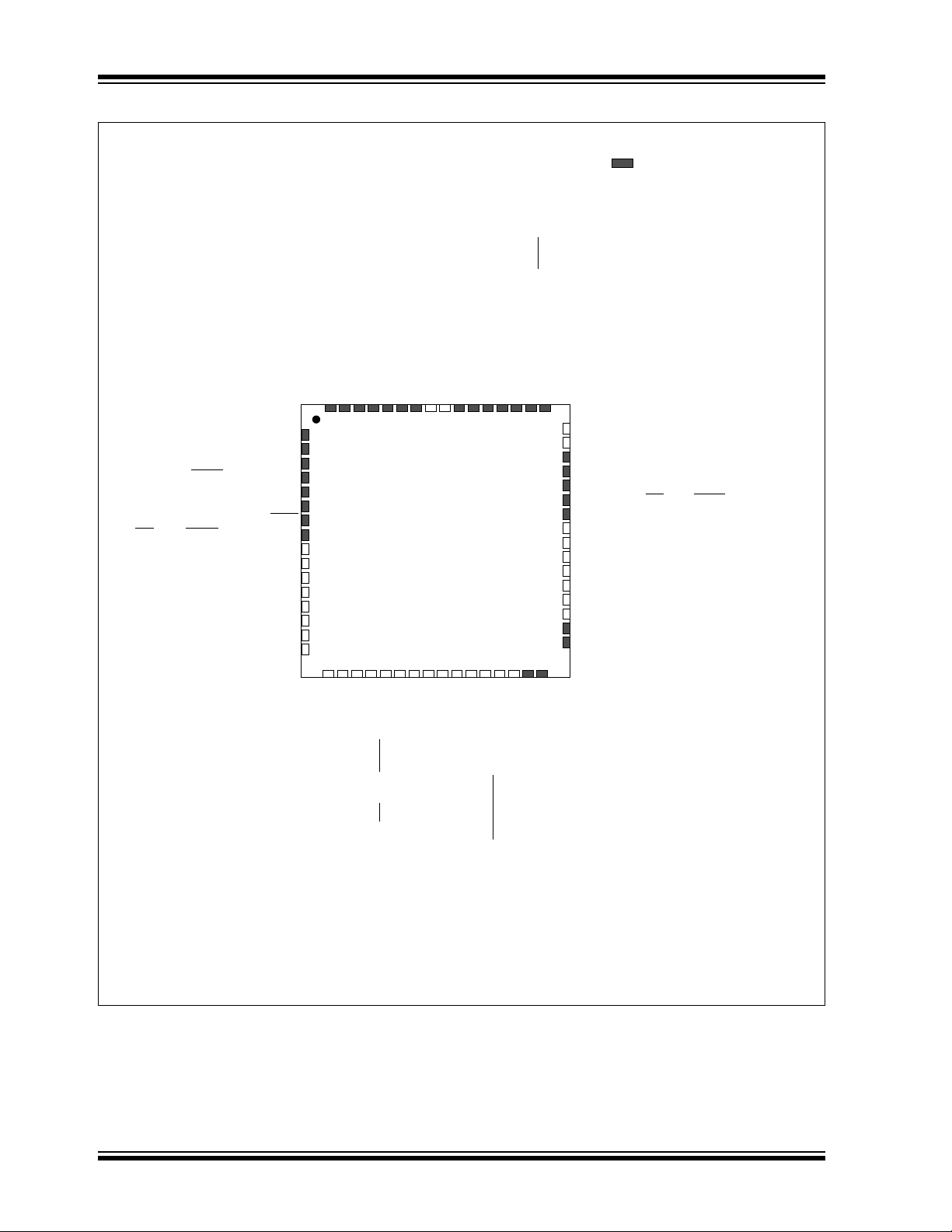

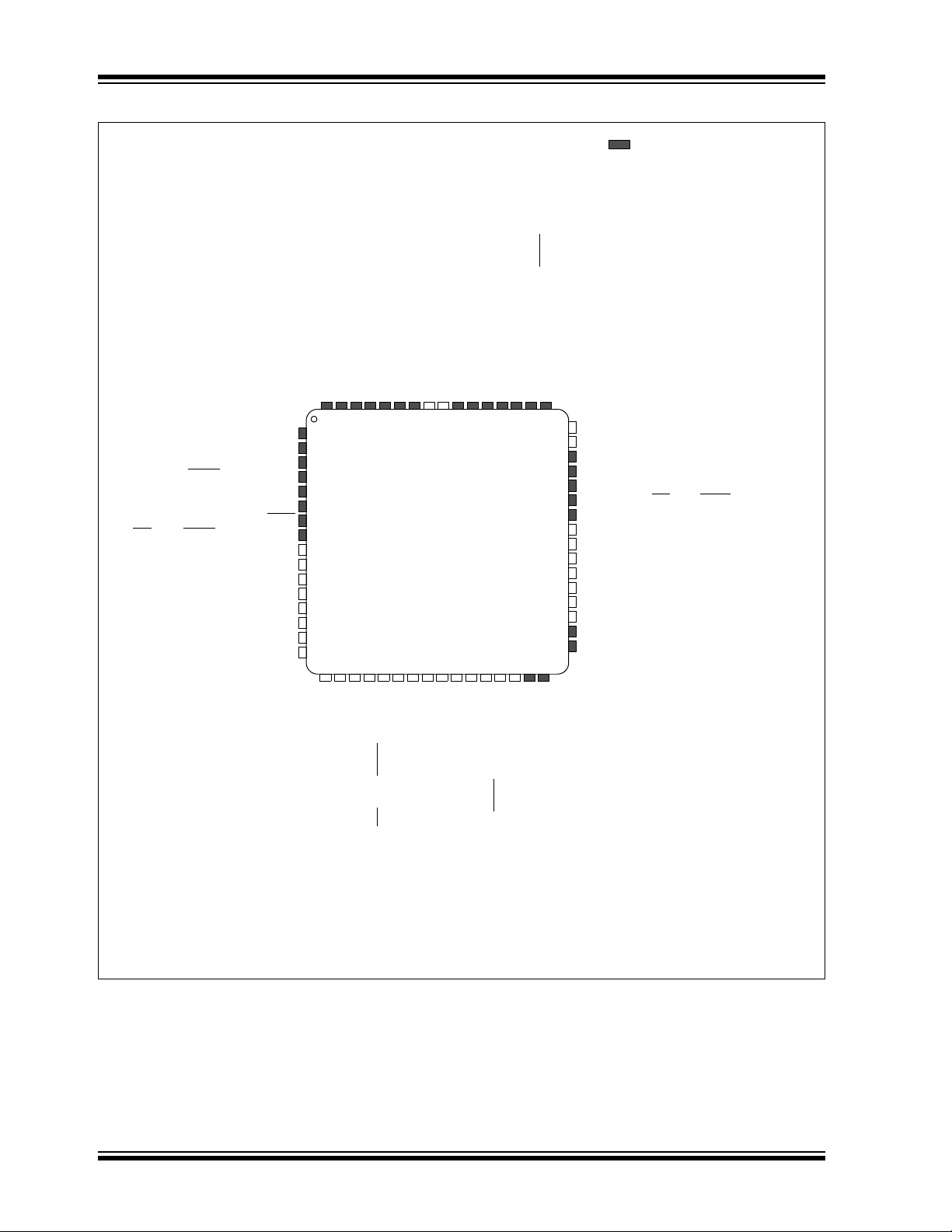

Pin Diagrams (Continued)

64-Pin QFN

(1)

= Pins are up to 5V tolerant

ETXEN/PMD5/RE5

ETXD0/PMD6/RE6

ETXD1/PMD7/RE7

SCK2/U6TX/U3RTS/PMA5/CN8/RG6

V

DD

AN5/C1IN+/V

BUSON

/CN7/RB5

AN4/C1IN-/CN6/RB4

AN3/C2IN+/CN5/ RB3

AN2/C2IN-/CN4/RB2

SDA4/SDI2/U3RX/PMA4/CN9/RG7

SCL4/SDO2/U3TX/PMA3/CN10/RG8

PGEC1/AN1/V

REF

-/CV

REF

-/CN3/RB1

PGED1/AN0/V

REF

+/CV

REF

+/PMA6/CN2/RB0

SS2

/U6RX/U3CTS/PMA2/CN11/RG9

MCLR

V

SS

64 63 62 61 60 59 58 57 56 55

3

4

5

7

8

9

10

11

1

2

6

54

14

15

16

12

13

53

52 51 50 49

AETXEN/ETXERR/CN15/RD6

PMRD/CN14/RD5

OC5/IC5/PMWR/CN13/RD4

SCL3/SDO3/U1TX/OC4/RD3

SDA3/SDI3/U1RX/ OC3/RD2

EMDIO/AEMDIO/SCK3/U4TX/U1RTS

/OC2/RD1

ERXERR/PMD4/RE4

ERXCLK/EREFCLKPMD3/RE3

ERXDV/ECRSDV/PMD2/RE2

ERXD0/PMD1/RE1

C1RX/AETXD1/ERXD3/RF0

V

CAP

/V

CORE

ERXD1/PMD0/RE0

C1TX/AETXD0/ERXD2/RF1

ETXCLK/AERXERR/CN16/RD7

V

DD

PIC32MX795F512H

PIC32MX775F256H

PIC32MX775F512H

22 23 24 25 26 27 28 29 30 31

40

39

38

37

36

35

34

33

42

41

32

43

17

18 19 20 21

45

44

47

46

48

AV

DD

AN8/C2TX/SS4/U5RX/U2CTS/C1OUT/RB8

AN9/C2OUT/PMA7/RB9

TMS/AN10/CV

REFOUT

/PMA13/RB10

TD O/A N11 /PM A12 /R B11

V

DD

PGEC2/AN6/OCFA/RB6

PGED2/AN7/RB7

AC1RX/SCL5/SDO4/U2TX/PMA8/CN18/RF5

AC1TX/SDA5/SDI4/U2RX/PMA9/CN17/RF4

TCK/AN12/PMA11/RB12

TDI/AN13/PMA10/RB13

AN14/C2RX/SCK4/U5TX/U2RTS

/PMALH/PMA1/RB14

AN15/EMDC/AEMDC/OCFB/PMALL/PMA0/CN12/RB15

V

SS

AV

SS

SOSCI/CN1/RC13

OC1/INT0/RD0

ECOL/AECRSDV/SCL1/IC3/PMCS2/PMA15/INT3/RD10

AERXD0/ETXD2/SS3

/U4RX/U1CTS/SDA1/IC2/INT2/RD9

RTCC/AERXD1/ETXD3/I C1/INT1/RD8

ECRS/AEREFCLK/IC4/PMCS1/PMA14/INT4/RD11

OSC2/CLKO/RC15

OSC1/CLKI/RC12

V

DD

D+/RG2

V

USB

V

BUS

USBID/RF3

D-/RG3

SOSCO/T1CK/CN0/RC14

Vss

Note 1: The metal plane at the bottom of the device is not connected to any pins and is recommended to be

connected to V

SS externally.

PIC32MX5XX/6XX/7XX

© 2009-2011 Microchip Technology Inc. DS61156G-page 9

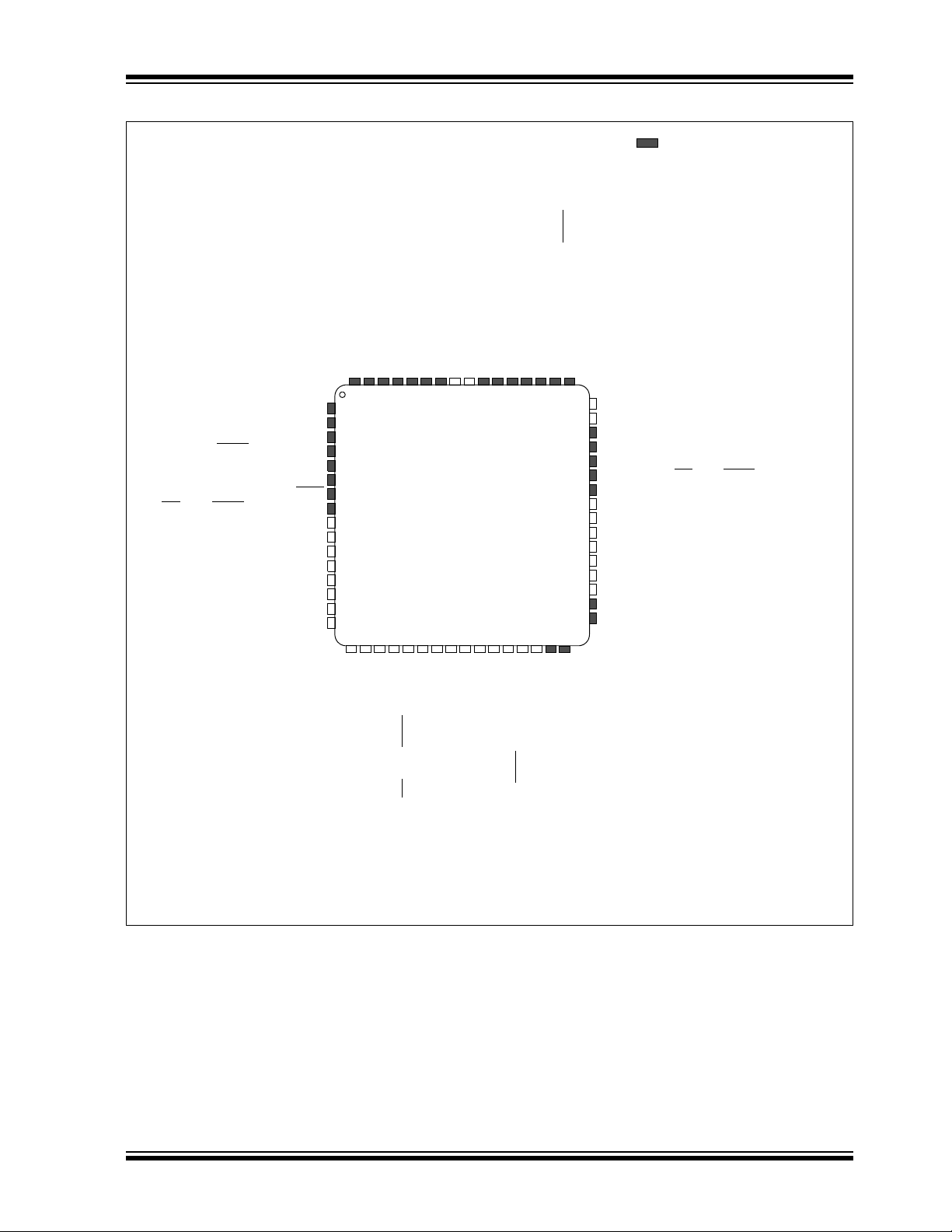

PIC32MX5XX/6XX/7XX

64-Pin QFN

(1)

= Pins are up to 5V tolerant

ETXEN/PMD5/RE5

ETXD0/PMD6/RE6

ETXD1/PMD7/RE7

SCK2/U6TX/U3RTS/PMA5/CN8/RG6

V

DD

AN5/C1IN+/V

BUSON

/CN7/RB5

AN4/C1IN-/CN6/RB4

AN3/C2IN+/CN5/ RB3

AN2/C2IN-/CN4/RB2

SDA4/SDI2/U3RX/PMA4/CN9/RG7

SCL4/SDO2/U3TX/PMA3/CN10/RG8

PGEC1/AN1/V

REF

-/CV

REF

-/CN3/RB1

PGED1/AN0/V

REF

+/CV

REF

+/PMA6/CN2/RB0

SS2

/U6RX/U3CTS/PMA2/CN11/RG9

MCLR

V

SS

64 63 62 61 60 59 58 57 56 55

3

4

5

7

8

9

10

11

1

2

6

54

14

15

16

12

13

53

52 51 50 49

AETXEN/ETXERR/CN15/RD6

PMRD/CN14/RD5

OC5/IC5/PMWR/CN13/RD4

SCL3/SDO3/U1TX/OC4/RD3

SDA3/SDI3/U1RX/OC3/RD2

EMDIO/AEMDIO/SCK3/U4TX/U1RTS

/OC2/RD1

ERXERR/PMD4/RE4

ERXCLK/EREFCLKPMD3/RE3

ERXDV/ECRSDV/PMD2/RE2

ERXD0/PMD1/RE1

C1RX/AETXD1/ERXD3/RF0

V

CAP

/V

CORE

ERXD1/PMD0/RE0

C1TX/AETXD0/ERXD2/RF1

ETXCLK/AERXERR/CN16/RD7

V

DD

PIC32MX764F128H

22 23 24 25 26 27 28 29 30 31

40

39

38

37

36

35

34

33

42

41

32

43

17

18 19 20 21

45

44

47

46

48

AV

DD

AN8/SS4/U5RX/U2CTS/C1OUT/RB8

AN9/C2OUT/PMA7/RB9

TMS/AN10/CV

REFOUT

/PMA13/RB10

TDO/AN11/PMA12/RB11

V

DD

PGEC2/AN6/OCFA/RB6

PGED2/AN7/RB7

AC1RX/SCL5/SDO4/U2TX/PMA8/CN18/RF5

AC1TX/SDA5/SDI4/U2RX/PMA9/CN17/RF4

TCK/AN12/PMA11/RB12

TDI/AN13/PMA10/RB13

AN14/SCK4/U5TX/U2RTS

/PMALH/PMA1/RB14

AN15/EMDC/AEMDC/OCFB/PMALL/PMA0/CN12/RB15

V

SS

AV

SS

SOSCI/CN1/RC13

OC1/INT0/RD0

ECOL/AECRSDV/SCL1/IC3/PMCS2/PMA15/INT3/RD10

AERXD0/ETXD2/SS3

/U4RX/U1CTS/SDA1/IC2/INT2/RD9

RTCC/AERXD1/ETXD3/IC1/INT1/RD8

ECRS/AEREFCLK/IC4/PMCS1/PMA14/INT4/RD11

OSC2/CLKO/RC15

OSC1/CLKI/RC12

V

DD

D+/RG2

V

USB

V

BUS

USBID/RF3

D-/RG3

SOSCO/T1CK/CN0/RC14

Vss

Note 1: The metal plane at the bottom of the device is not connected to any pins and is recommended to be

connected to VSS externally.

Pin Diagrams (Continued)

DS61156G-page 10 © 2009-2011 Microchip Technology Inc.

Pin Diagrams (Continued)

64-Pin TQFP

= Pins are up to 5V tolerant

PIC32MX575F256H

PMD5/RE5

PMD6/RE6

PMD7/RE7

SCK2/U6TX/U3RTS

/PMA5/CN8/RG6

V

DD

AN5/C1IN+/V

BUSON

/CN7/RB5

AN4/C1IN-/CN6/RB4

AN3/C2IN+/CN5/RB3

AN2/C2IN-/CN4/RB2

SDA4/SDI2/U3RX/PMA4/CN9/RG7

SCL4/SDO2/U3TX/PMA3/CN10/RG8

PGEC1/AN1/V

REF

-/CV

REF

-/CN3/RB1

PGED1/AN0/V

REF

+/CV

REF

+/PMA6/CN2/RB0

SS2

/U6RX/U3CTS/PMA2/CN11/RG9

MCLR

V

SS

64 63 62 61 60 59 58 57 56 55

22 23 24 25 26 27 28 29 30 31

3

40

39

38

37

36

35

34

33

4

5

7

8

9

10

11

1

2

42

41

6

32

43

54

14

15

16

12

13

17

18 19 20 21

45

44

47

46

48

53

52 51 50 49

AV

DD

AN8/SS4/U5RX/U2CTS/C1OUT/RB8

AN9/C2OUT/PMA7/RB9

TMS/AN10/CV

REFOUT

/PMA13/RB10

TDO/AN11/PMA12/RB11

V

DD

PGEC2/AN6/OCFA/RB6

PGED2/AN7/RB7

AC1RX/SCL5/SDO4/U2TX/PMA8/CN18/RF5

AC1TX/SDA5/SDI4/U2RX/PMA9/CN17/RF4

TCK/AN12/PMA11/RB12

TDI/AN13/PMA10/RB13

AN14/SCK4/U5TX/U2RTS

/PMALH/PMA1/RB14

AN15/OCFB/PMALL/PMA0/CN12/RB15

V

SS

AV

SS

CN15/RD6

PMRD/CN14/RD5

OC5/IC5/PMWR/CN13/RD4

SCL3/SDO3/U1TX/OC4/RD3

SDA3/SDI3/U1RX/OC3/RD2

SCK3/U4TX/U1RTS

/OC2/RD1

PMD4/RE4

PMD3/RE3

PMD2/RE2

PMD1/RE1

C1RX/RF0

V

CAP

/V

CORE

PMD0/RE0

C1TX/RF1

CN16/RD7

V

DD

SOSCI/CN1/RC13

OC1/INT0/RD0

SCL1/IC3/PMCS2/PMA15/INT3/RD10

SS3

/U4RX/U1CTS/SDA1/IC2/INT2/RD9

RTCC/IC1/INT1/RD8

IC4/PMCS1/PMA14/INT4/RD11

OSC2/CLKO/RC15

OSC1/CLKI/RC12

V

DD

D+/RG2

V

USB

V

BUS

USBID/RF3

D-/RG3

SOSCO/T1CK/CN0/RC14

Vss

PIC32MX575F512H

PIC32MX534F064H

PIC32MX564F064H

PIC32MX564F128H

PIC32MX5XX/6XX/7XX

© 2009-2011 Microchip Technology Inc. DS61156G-page 11

PIC32MX5XX/6XX/7XX

64-Pin TQFP

= Pins are up to 5V tolerant

PIC32MX675F512H

PIC32MX695F512H

PIC32MX675F256H

ETXEN/PMD5/RE5

ETXD0/PMD6/RE6

ETXD1/PMD7/RE7

SCK2/U6TX/U3RTS

/PMA5/CN8/RG6

V

DD

AN5/C1IN+/V

BUSON

/CN7/RB5

AN4/C1IN-/CN6/RB4

AN3/C2IN+/CN5/RB3

AN2/C2IN-/CN4/RB2

SDA4/SDI2/U3RX/PMA4/CN9/RG7

SCL4/SDO2/U3TX/PMA3/CN10/RG8

PGEC1/AN1/V

REF

-/CV

REF

-/CN3/RB1

PGED1/AN0/V

REF

+/CV

REF

+/PMA6/CN2/RB0

SS2

/U6RX/U3CTS/PMA2/CN11/RG9

MCLR

V

SS

64 63 62 61 60 59 58 57 56 55

3

4

5

7

8

9

10

11

1

2

6

54

14

15

16

12

13

53

52 51 50 49

AETXEN/ETXERR/CN15/RD6

PMRD/CN14/RD5

OC5/IC5/PMWR/CN13/RD4

SCL3/SDO3/U1TX/OC4/RD3

SDA3/SDI3/U1RX/ OC3/RD2

EMDIO/AEMDIO/SCK3/U4TX/U1RTS

/OC2/RD1

ERXERR/PMD4/RE4

ERXCLK/EREFCLK/PMD3/RE3

ERXDV/ECRSDV/PMD2/RE2

ERXD0/PMD1/RE1

AETXD1/ERXD3/RF0

V

CAP

/V

CORE

ERXD1/PMD0/RE0

AETXD0/ERXD2/RF1

ETXCLK/AERXERR/CN16/RD7

V

DD

22 23 24 25 26 27 28 29 30 31

40

39

38

37

36

35

34

33

42

41

32

43

17

18 19 20 21

45

44

47

46

48

AV

DD

AN8/SS4/U5RX/U2CTS/C1OUT/RB8

AN9/C2OUT/PMA7/RB9

TMS/AN10/CV

REFOUT

/PMA13/RB10

TDO/AN11/PMA12/RB11

V

DD

PGEC2/AN6/OCFA/RB6

PGED2/AN7/RB7

SCL5/SDO4/U2TX/PMA8/CN18/RF5

SDA5/SDI4/U2RX/PMA9/CN17/RF4

TCK/AN12/PMA11/RB12

TDI/AN13/PMA10/RB13

AN14/SCK4/U5TX/ U2RTS

/PMALH/PMA1/RB14

AN15/EMDC/AEMDC/OCFB/PMALL/PMA0/CN12/RB15

V

SS

AV

SS

SOSCI/CN1/RC13

OC1/INT0/RD0

ECOL/AECRSDV/SCL1/IC3/PMCS2/PMA15/INT3/RD10

AERXD0/ETXD2/SS3

/U4RX/U1CTS/SDA1/IC2/INT2/RD9

RTCC/AERXD1/ETXD3/I C1/INT1/RD8

ECRS/AEREFCLK/IC4/PMCS1/PMA14/INT4/RD11

OSC2/CLKO/RC15

OSC1/CLKI/RC12

V

DD

D+/RG2

V

USB

V

BUS

USBID/RF3

D-/RG3

SOSCO/T1CK/CN0/RC14

Vss

PIC32MX664F064H

PIC32MX664F128H

Pin Diagrams (Continued)

DS61156G-page 12 © 2009-2011 Microchip Technology Inc.

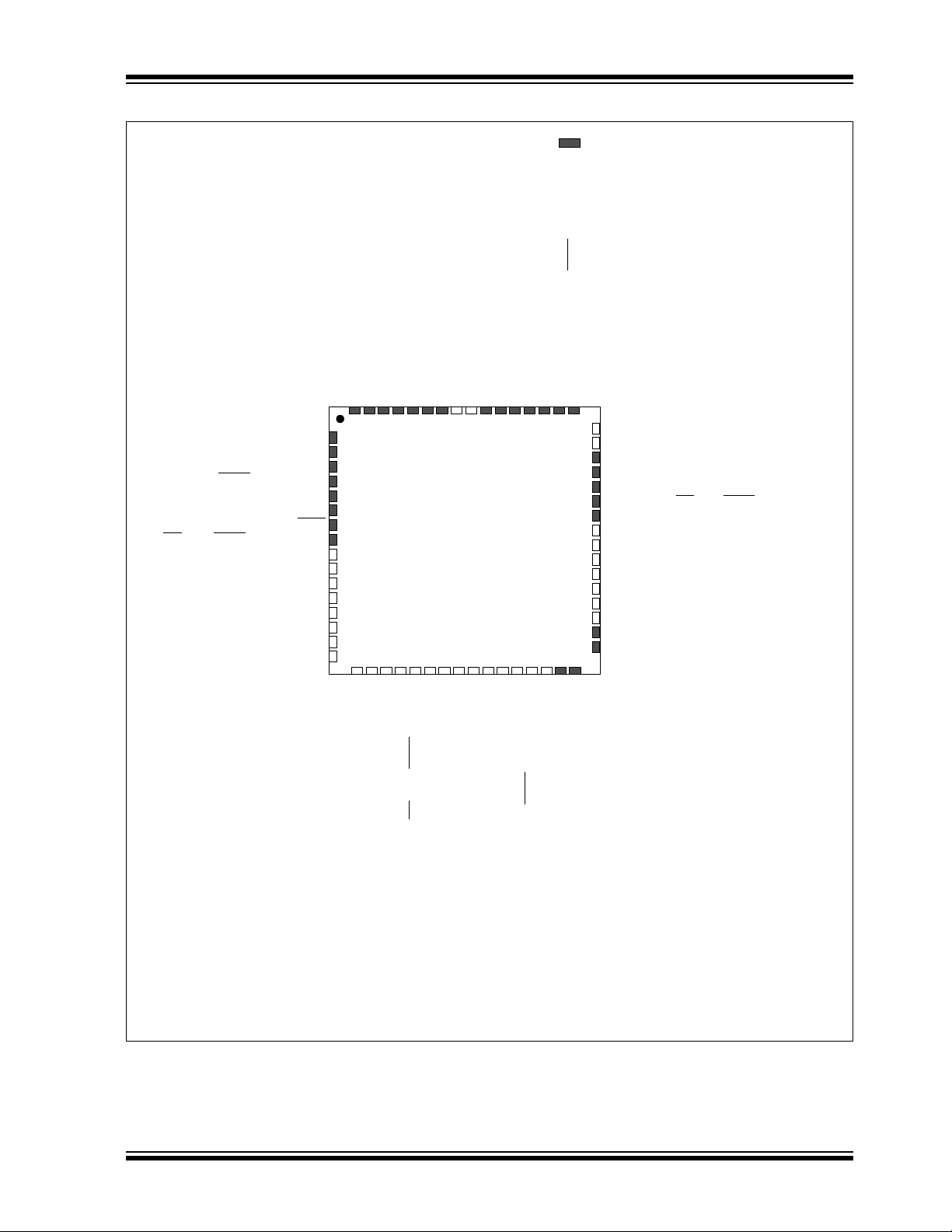

Pin Diagrams (Continued)

64-Pin TQFP

= Pins are up to 5V tolerant

PIC32MX795F512H

PIC32MX775F256H

PIC32MX775F512H

ETXEN/PMD5/RE5

ETXD0/PMD6/RE6

ETXD1/PMD7/RE7

SCK2/U6TX/U3RTS

/PMA5/CN8/RG6

V

DD

AN5/C1IN+/V

BUSON

/CN7/RB5

AN4/C1IN-/CN6/RB4

AN3/C2IN+/CN5/RB3

AN2/C2IN-/CN4/RB2

SDA4/SDI2/U3RX/PMA4/CN9/RG7

SCL4/SDO2/U3TX/PMA3/CN10/RG8

PGEC1/AN1/V

REF

-/CV

REF

-/CN3/RB1

PGED1/AN0/V

REF

+/CV

REF

+/PMA6/CN2/RB0

SS2

/U6RX/U3CTS/PMA2/CN11/RG9

MCLR

V

SS

64 63 62 61 60 59 58 57 56 55

3

4

5

7

8

9

10

11

1

2

6

54

14

15

16

12

13

53

52 51 50 49

AETXEN/ETXERR/CN15/RD6

PMRD/CN14/RD5

OC5/IC5/PMWR/CN13/RD4

SCL3/SDO3/U1TX/OC4/RD3

SDA3/SDI3/U1RX/OC3/RD2

EMDIO/AEMDIO/SCK3/U4TX/U1RTS

/OC2/RD1

ERXERR/PMD4/RE4

ERXCLK/EREFCLK/PMD3/RE3

ERXDV/ECRSDV/PMD2/RE2

ERXD0/PMD1/RE1

C1RX/AETXD1/ERXD3/RF0

V

CAP

/V

CORE

ERXD1/PMD0/RE0

C1TX/AETXD0/ERXD2/RF1

ETXCLK/AERXERR/CN16/RD7

V

DD

22 23 24 25 26 27 28 29 30 31

40

39

38

37

36

35

34

33

42

41

32

43

17

18 19 20 21

45

44

47

46

48

AV

DD

AN8/C2TX/SS4/U5RX/U2CTS/C1OUT/RB8

AN9/C2OUT/PMA7/RB9

TMS/AN10/CV

REFOUT

/PMA13/RB10

TDO/AN11/PMA12/RB11

V

DD

PGEC2/AN6/OCFA/RB6

PGED2/AN7/RB7

AC1RX/SCL5/SDO4/U2TX/PMA8/CN18/RF5

AC1TX/SDA5/SDI4/U2RX/PMA9/CN17/RF4

TCK/AN12/PMA11/RB12

TDI/AN13/PMA10/RB13

AN14/C2RX/SCK4/U5TX/U2RTS

/PMALH/PMA1/RB14

AN15/EMDC/AEMDC/OCFB/PMALL/PMA0/CN12/RB15

V

SS

AV

SS

SOSCI/CN1/RC13

OC1/INT0/RD0

ECOL/AECRSDV/SCL1/IC3/PMCS2/PMA15/INT3/RD10

AERXD0/ETXD2/SS3/U4RX/U1CTS/SDA1/IC2/INT2/RD9

RTCC/AERXD1/ETXD3/I C1/INT1/RD8

ECRS/AEREFCLK/IC4/PMCS1/PMA14/I NT4/RD11

OSC2/CLKO/RC15

OSC1/CLKI/RC12

V

DD

D+/RG2

V

USB

V

BUS

USBID/RF3

D-/RG3

SOSCO/T1CK/CN0/RC14

Vss

PIC32MX5XX/6XX/7XX

© 2009-2011 Microchip Technology Inc. DS61156G-page 13

PIC32MX5XX/6XX/7XX

64-Pin TQFP

= Pins are up to 5V tolerant

PIC32MX764F128H

ETXEN/PMD5/RE5

ETXD0/PMD6/RE6

ETXD1/PMD7/RE7

SCK2/U6TX/U3RTS

/PMA5/CN8/RG6

V

DD

AN5/C1IN+/V

BUSON

/CN7/RB5

AN4/C1IN-/CN6/RB4

AN3/C2IN+/CN5/RB3

AN2/C2IN-/CN4/RB2

SDA4/SDI2/U3RX/PMA4/CN9/RG7

SCL4/SDO2/U3TX/PMA3/CN10/RG8

PGEC1/AN1/V

REF

-/CV

REF

-/CN3/RB1

PGED1/AN0/V

REF

+/CV

REF

+/PMA6/CN2/RB0

SS2

/U6RX/U3CTS/PMA2/CN11/RG9

MCLR

V

SS

64 63 62 61 60 59 58 57 56 55

3

4

5

7

8

9

10

11

1

2

6

54

14

15

16

12

13

53

52 51 50 49

AETXEN/ETXERR/CN15/RD6

PMRD/CN14/RD5

OC5/IC5/PMWR/CN13/RD4

SCL3/SDO3/U1TX/OC4/RD3

SDA3/SDI3/U1RXU1RX/OC3/RD2

EMDIO/AEMDIO/SCK3/U4TX/U1RTS

/OC2/RD1

ERXERR/PMD4/RE4

ERXCLK/EREFCLK/PMD3/RE3

ERXDV/ECRSDV/PMD2/RE2

ERXD0/PMD1/RE1

C1RX/AETXD1/ERXD3/RF0

V

CAP

/V

CORE

ERXD1/PMD0/RE0

C1TX/AETXD0/ERXD2/RF1

ETXCLK/AERXERR/CN16/RD7

V

DD

22 23 24 25 26 27 28 29 30 31

40

39

38

37

36

35

34

33

42

41

32

43

17

18 19 20 21

45

44

47

46

48

AV

DD

AN8/SS4/U5RX/U2CTS/C1OUT/RB8

AN9/C2OUT/PMA7/RB9

TMS/AN10/CV

REFOUT

/PMA13/RB10

TDO/AN11/PMA12/RB11

V

DD

PGEC2/AN6/OCFA/RB6

PGED2/AN7/RB7

AC1RX/SCL5/SDO4/U2TX/PMA8/CN18/RF5

AC1TX/SDA5/SDI4/U2RX/PMA9/CN17/RF4

TCK/AN12/PMA11/RB12

TDI/AN13/PMA10/RB13

AN14/SCK4/U5TX/U2RTS

/PMALH/PMA1/RB14

AN15/EMDC/AEMDC/OCFB/PMALL/PMA0/CN12/RB15

V

SS

AV

SS

SOSCI/CN1/RC13

OC1/INT0/RD0

ECOL/AECRSDV/SCL1/IC3/PMCS2/PMA15/INT3/RD10

AERXD0/ETXD2/SS3/U4RX/U1CTS/SDA1/IC2/INT2/RD9

RTCC/AERXD1/ETXD3/I C1/INT1/RD8

ECRS/AEREFCLK/IC4/PMCS1/PMA14/I NT4/RD11

OSC2/CLKO/RC15

OSC1/CLKI/RC12

V

DD

D+/RG2

V

USB

V

BUS

USBID/RF3

D-/RG3

SOSCO/T1CK/CN0/RC14

Vss

Pin Diagrams (Continued)

DS61156G-page 14 © 2009-2011 Microchip Technology Inc.

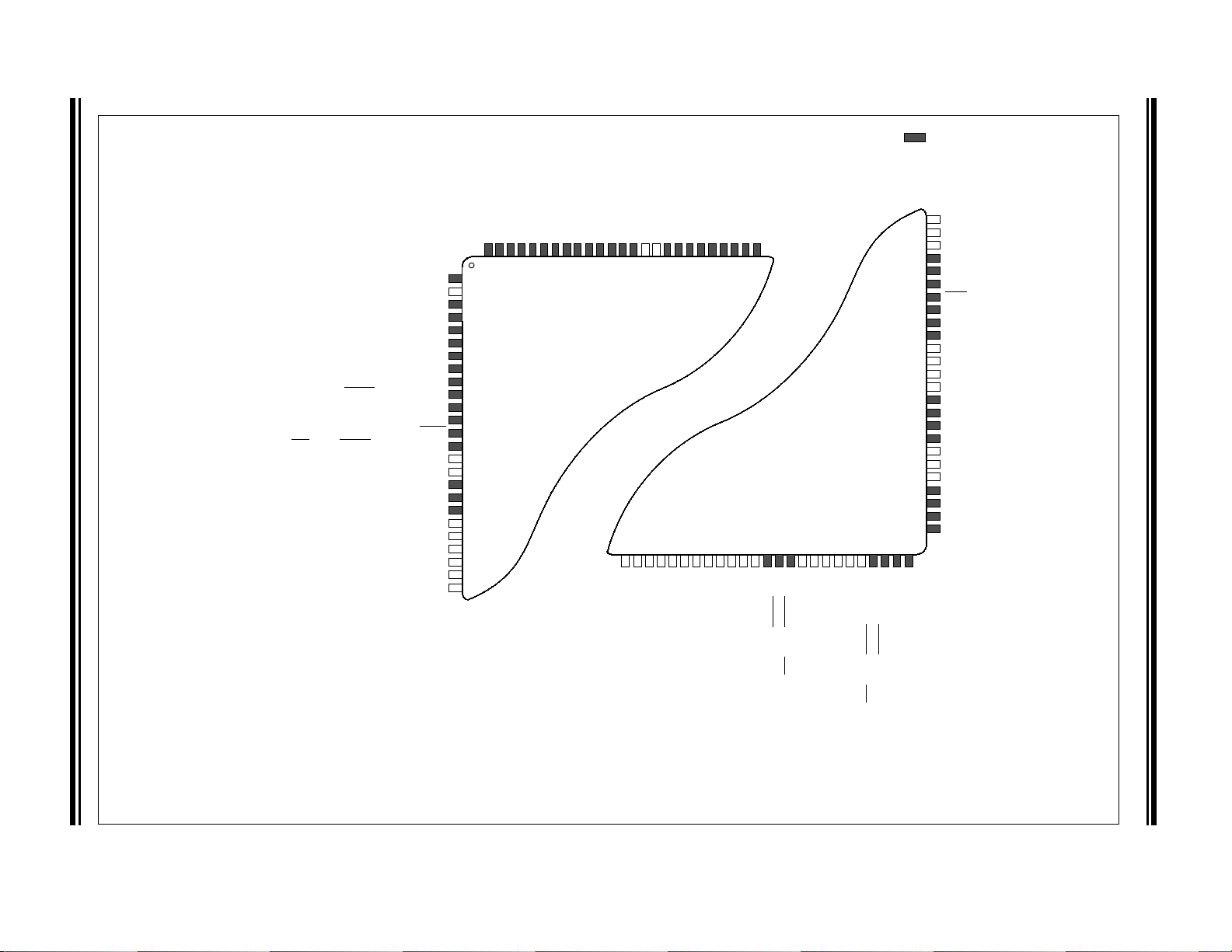

Pin Diagrams (Continued)

PMRD/CN14/RD5

OC5/PMWR/CN13/RD4

PMD13/CN19/RD13

IC5/PMD12/RD12

OC4/RD3

OC3/RD2

OC2/RD1

TRD3/RA7

TRCLK/RA6

PMD2/RE2

TRD0/RG13

TRD1/RG12

TRD2/RG14

PMD1/RE1

PMD0/RE0

PMD8/RG0

PMD4/RE4

PMD3/RE3

C1RX/PMD11/RF0

SOSCI/CN1/RC13

SDO1/OC1/INT0/RD0

SCK1/IC3/PMCS2/PMA15/RD10

SS1/

IC2

/RD9

RTCC/IC1/RD8

IC4/PMCS1/PMA14/RD11

SDA1/INT4/RA15

SCL1/INT3/RA14

OSC2/CLKO/RC15

OSC1/CLKI/RC12

V

DD

D+/RG2

V

USB

V

BUS

SCL3/SDO3/U1TX/RF8

D-/RG3

SDA3/SDI3/U1RX/RF2

USBID/RF3

V

SS

SOSCO/T1CK/CN0/RC14

V

REF

+/CV

REF

+/PMA6/RA10

V

REF

-/CV

REF

-/PMA7/RA9

AV

DD

AV

SS

AN8/C1OUT/RB8

AN9/C2OUT/RB9

AN10/CV

REFOUT

/PMA13/RB10

AN11/PMA12/RB11

V

DD

AC1RX/SS4/U5RX/U2CTS/RF12

AC1TX/SCK4/U5TX/U2RTS

/RF13

SS3

/U4RX/U1CTS/CN20/RD14

SCK3/U4TX/U1RTS

/CN21/RD15

V

DD

V

SS

PGEC2/AN6/OCFA/RB6

PGED2/AN7/RB7

SCL5/SDO4/U2TX/PMA8/CN18/RF5

SDA5/SDI4/U2RX/PMA9/CN17/RF4

PMD5/RE5

PMD6/RE6

PMD7/RE7

T2CK/RC1

T3CK/RC2

T4CK/RC3

T5CK/SDI1/RC4

SCK2/U6TX/U3RTS

/PMA5/CN8/RG6

V

DD

TMS/RA0

INT1/RE8

INT2/RE9

AN5/C1IN+/V

BUSON

/CN7/RB5

AN4/C1IN-/CN6/RB4

AN3/C2IN+/CN5/RB3

AN2/C2IN-/CN4/RB2

SDA4/SDI2/U3RX/PMA4/CN9/RG7

SCL4/SDO2/U3TX/PMA3/CN10/RG8

PGEC1/AN1/CN3/RB1

PGED1/AN0/CN2/RB0

V

DD

RG15

SS2

/U6RX/U3CTS

/PMA2/CN11/RG9

MCLR

AN12/PMA11/RB12

AN13/PMA10/RB13

AN14/PMALH/PMA1/RB14

AN15/OCFB/PMALL/PMA0/CN12/RB15

PMD9/RG1

C1TX/PMD10/RF1

V

DD

PMD14/CN15/RD6

TDO/RA5

SDA2/RA3

SCL2/RA2

V

SS

V

SS

V

SS

V

CAP

/V

CORE

TDI/RA4

TCK/RA1

100-Pin TQFP

PMD15/CN16/RD7

= Pins are up to 5V tolerant

20

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

65

64

63

62

61

60

59

56

45

44

43

42

41

40

39

2829303132333435363738

17

18

19

21

22

1

72

71

70

69

68

67

66

75

74

73

58

57

24

23

25

27

464748

49

55

54

53

52

51

50

26

PIC32MX575F512L

92949391908988878685848382818079789576

77

969897

99

100

PIC32MX575F256L

PIC32MX534F064L

PIC32MX564F064L

PIC32MX564F128L

PIC32MX5XX/6XX/7XX

© 2009-2011 Microchip Technology Inc. DS61156G-page 15

DS61156G-page 16 © 2009-2011 Microchip Technology Inc.

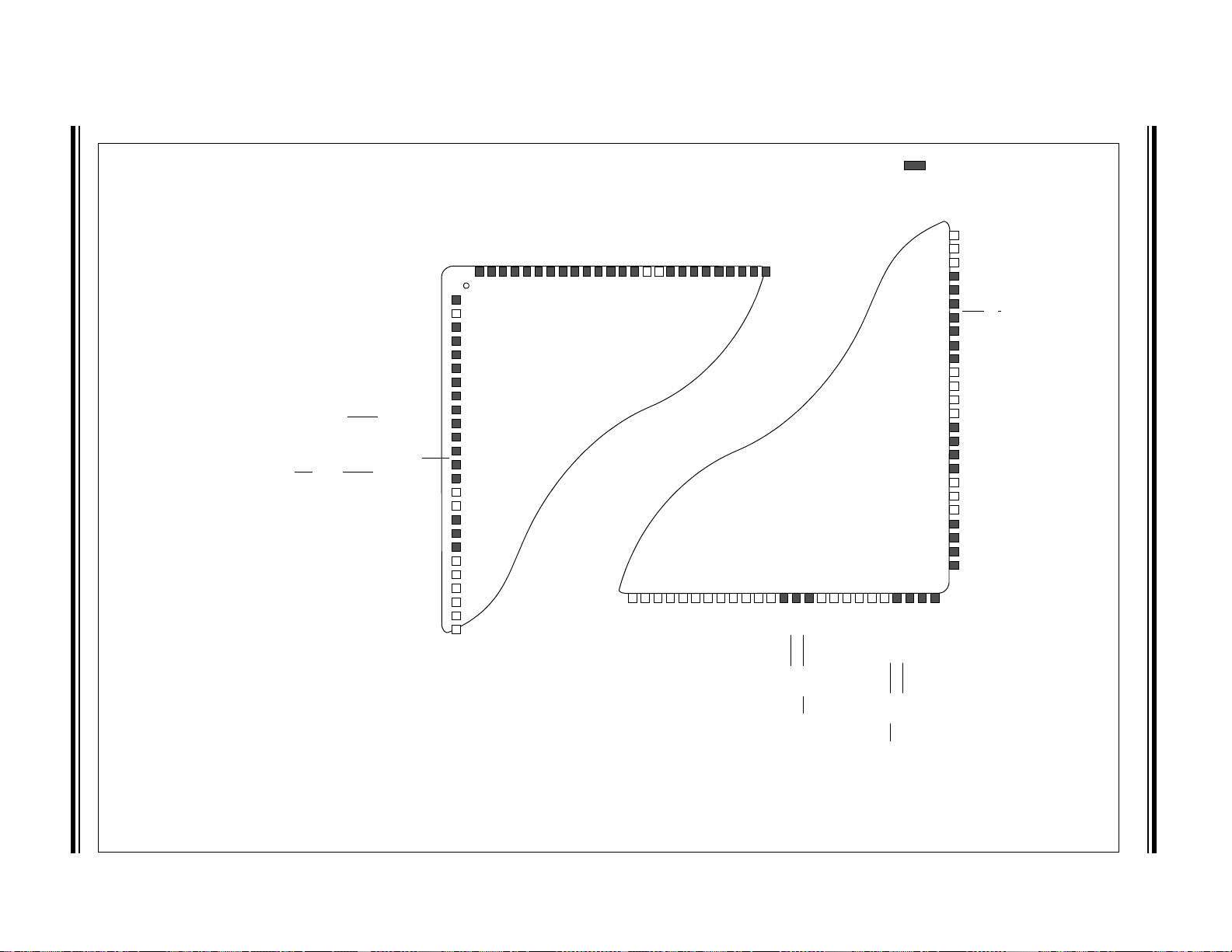

100-Pin TQFP

PIC32MX675F512L

PIC32MX695F512L

PIC32MX675F256L

= Pins are up to 5V tolerant

PMRD/CN14/RD5

OC5/PMWR/CN13/RD4

ETXD3/PMD13/CN19/RD13

ETXD2/IC5/PMD12/RD12

OC4/RD3

OC3/RD2

OC2/RD1

TRD3/RA7

TRCLK/RA6

PMD2/RE2

TRD0/RG13

TRD1/RG12

TRD2/RG14

PMD1/RE1

PMD0/RE0

PMD8/RG0

PMD4/RE4

PMD3/RE3

ETXD1/PMD11/RF0

PMD5/RE5

PMD6/RE6

PMD7/RE7

T2CK/RC1

T3CK/RC2

T4CK/RC3

T5CK/SDI1/RC4

ECOL/SCK2/U6TX/U3RTS

/PMA5/CN8/RG6

V

DD

TMS/RA0

AERXD0/INT1/RE8

AERXD1/INT2/RE9

AN5/C1IN+/V

BUSON

/CN7/RB5

AN4/C1IN-/CN6/RB4

AN3/C2IN+/CN5/RB3

AN2/C2IN-/CN4/RB2

ECRS/SDA4/SDI2/U3RX/PMA4/CN9/RG7

ERXDV/AERXDV/ECRSDV/AECRSDV/SCL4/SDO2/U3TX/PMA3/CN10/RG8

PGEC1/AN1/CN3/RB1

PGED1/AN0/CN2/RB0

V

DD

AERXERR/RG15

ERXCLK/AERXCLK/EREFCLK/AEREFCLK/SS2

/U6RX/U3CTS/PMA2/CN11/RG9

MCLR

ETXERR/PMD9/RG1

ETXD0/PMD10/RF1

VDDETXEN/PMD14/CN15/RD6

V

SS

V

CAP

/V

DDCORE

ETXCLK/PMD15/CN16/RD7

20

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

21

22

1

24

23

25

92949391908988878685848382818079789576

77

969897

99

100

SOSCI/CN1/RC13

SDO1/OC1/INT0/RD0

SS1/

IC2/RD9

RTCC/EMDIO/AEMDIO/IC1/RD8

EMDC/AEMDC/IC4/PMCS1/PMA14/RD11

AETXEN/SDA1/INT4/RA15

AETXCLK/SCL1/INT3/RA14

OSC2/CLKO/RC15

OSC1/CLKI/RC12

V

DD

D+/RG2

V

USB

V

BUS

SCL3/SDO3/U1TX/RF8

D-/RG3

SDA3/SDI3/U1RX/RF2

USBID/RF3

V

SS

SOSCO/T1CK/CN0/RC14

V

REF

+/CV

REF

+/AERXD3/PMA6/RA10

V

REF

-/CV

REF

-/AERXD2/PMA7/RA9

AV

DD

AV

SS

AN8/C1OUT/RB8

AN9/C2OUT/RB9

AN10/CV

REFOUT

/PMA13/RB10

AN11/ERXERR/AETXERR/PMA12/RB11

V

DD

SS4/U5RX/U2CTS/RF12

SCK4/U5TX/U2RTS

/RF13

AETXD0/SS3

/U4RX/U1CTS/CN20/RD14

AETXD1/SCK3/U4TX/U1RTS

/CN21/RD15

V

DD

V

SS

PGED2/AN7/RB7

SCL5/SDO4/U2TX/PMA8/CN18/RF5

SDA5/SDI4/U2RX/PMA9/CN17/RF4

AN12/ERXD0/AECRS/PMA11/RB12

AN13/ERXD1/AECOL/PMA10/RB13

AN14/ERXD2/AETXD3/PMALH/PMA1/RB14

AN15/ERXD3/AETXD2/OCFB/PMALL/PMA0/CN12/RB15

TDO/RA5

SDA2/RA3

SCL2/RA2

V

SS

V

SS

TDI/RA4

TCK/RA1

65

64

63

62

61

60

59

56

45

44

43

42

41

40

39

2829303132333435363738

72

71

70

69

68

67

66

75

74

73

58

57

27

464748

49

55

54

53

52

51

50

SCK1/IC3/PMCS2/PMA15/RD10

PIC32MX664F064L

PIC32MX664F128L

PGEC2/AN6/OCFA/RB6

26

Pin Diagrams (Continued)

PIC32MX5XX/6XX/7XX

© 2009-2011 Microchip Technology Inc. DS61156G-page 17

100-Pin TQFP

= Pins are up to 5V tolerant

PIC32MX795F512L

PIC32MX775F256L

PIC32MX775F512L

PMRD/CN14/RD5

OC5/PMWR/CN13/RD4

ETXD3/PMD13/CN19/RD13

ETXD2/IC5/PMD12/RD12

OC4/RD3

OC3/RD2

OC2/RD1

TRD3/RA7

TRCLK/RA6

PMD2/RE2

TRD0/RG13

TRD1/RG12

TRD2/RG14

PMD1/RE1

PMD0/RE0

C2RX/PMD8/RG0

PMD4/RE4

PMD3/RE3

C1RX/ETXD1/PMD11/RF0

PMD5/RE5

PMD6/RE6

PMD7/RE7

T2CK/RC1

T3CK/AC2TX/RC2

T4CK/AC2RX/RC3

T5CK/SDI1/RC4

ECOL/SCK2/U6TX/U3RTS

/PMA5/CN8/RG6

V

DD

TMS/RA0

AERXD0/INT1/RE8

AERXD1/INT2/RE9

AN5/C1IN+/V

BUSON

/CN7/RB5

AN4/C1IN-/CN6/RB4

AN3/C2IN+/CN5/RB3

AN2/C2IN-/CN4/RB2

ECRS/SDA4/SDI2/U3RX/PMA4/CN9/RG7

ERXDV/AERXDV/ECRSDV/AECRSDV/SCL4/SDO2/U3TX/PMA3/CN10/RG8

PGEC1/AN1/CN3/RB1

PGED1/AN0/CN2/RB0

V

DD

AERXERR/RG15

ERXCLK/AERXCLK/EREFCLK/AEREFCLK/SS2

/U6RX/U3CTS/PMA2/CN11/RG9

MCLR

C2TX/ETXERR/PMD9/RG1

C1TX/ETXD0/PMD10/RF1

VDDETXEN/PMD14/CN15/RD6

V

SS

V

CAP

/V

DDCORE

ETXCLK/PMD15/CN16/RD7

20

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

21

22

1

24

23

25

92949391908988878685848382818079789576

77

969897

99

100

SOSCI/CN1/RC13

SDO1/OC1/INT0/RD0

SCK1/IC3/PMCS2/PMA15/RD10

SS1/

IC2/RD9

RTCC/EMDIO/AEMDIO/IC1/RD8

EMDC/AEMDC/IC4/PMCS1/PMA14/RD1

AETXEN/SDA1/INT4/RA15

AETXCLK/SCL1/INT3/RA14

OSC2/CLKO/RC15

OSC1/CLKI/RC12

V

DD

D+/RG2

V

USB

V

BUS

SCL3/SDO3/U1TX/RF8

D-/RG3

SDA3/SDI3/U1RX/RF2

USBID/RF3

V

SS

SOSCO/T1CK/CN0/RC14

V

REF

+/CV

REF

+/AERXD3/PMA6/RA10

V

REF

-/CV

REF

-/AERXD2/PMA7/RA9

AV

DD

AV

SS

AN8/C1OUT/RB8

AN9/C2OUT/RB9

AN10/CV

REFOUT

/PMA13/RB10

AN11/ERXERR/AETXERR/PMA12/RB11

V

DD

AC1RX/SS4/U5RX/U2CTS/RF12

AC1TX/SCK4/U5TX/U2RTS

/RF13

AETXD0/SS3

/U4RX/U1CTS/CN20/RD14

AETXD1/SCK3/U4TX/U1RTS

/CN21/RD15

V

DD

V

SS

PGEC2/AN6/OCFA/RB6

PGED2/AN7/RB7

SCL5/SDO4/U2TX/PMA8/CN18/RF5

SDA5/SDI4/U2RX/PMA9/CN17/RF4

AN12/ERXD0/AECRS/PMA11/RB12

AN13/ERXD1/AECOL/PMA10/RB13

AN14/ERXD2/AETXD3/PMALH/PMA1/RB14

AN15/ERXD3/AETXD2/OCFB/PMALL/PMA0/CN12/RB15

TDO/RA5

SDA2/RA3

SCL2/RA2

V

SS

V

SS

TDI/RA4

TCK/RA1

65

64

63

62

61

60

59

56

45

44

43

42

41

40

39

2829303132333435363738

72

71

70

69

68

67

66

75

74

73

58

57

27

464748

49

55

54

53

52

51

50

26

Pin Diagrams (Continued)

PIC32MX5XX/6XX/7XX

DS61156G-page 18 © 2009-2011 Microchip Technology Inc.

100-Pin TQFP

= Pins are up to 5V tolerant

PIC32MX764F128L

PMRD/CN14/RD5

OC5/PMWR/CN13/RD4

ETXD3/PMD13/CN19/RD13

ETXD2/IC5/PMD12/RD12

OC4/RD3

OC3/RD2

OC2/RD1

TRD3/RA7

TRCLK/RA6

PMD2/RE2

TRD0/RG13

TRD1/RG12

TRD2/RG14

PMD1/RE1

PMD0/RE0

PMD8/RG0

PMD4/RE4

PMD3/RE3

C1RX/ETXD1/PMD11/RF0

PMD5/RE5

PMD6/RE6

PMD7/RE7

T2CK/RC1

T3CK/RC2

T4CK/RC3

T5CK/SDI1/RC4

ECOL/SCK2/U6TX/U3RTS

/PMA5/CN8/RG6

V

DD

TMS/RA0

AERXD0/INT1/RE8

AERXD1/INT2/RE9

AN5/C1IN+/V

BUSON

/CN7/RB5

AN4/C1IN-/CN6/RB4

AN3/C2IN+/CN5/RB3

AN2/C2IN-/CN4/RB2

ECRS/SDA4/SDI2/U3RX/PMA4/CN9/RG7

ERXDV/AERXDV/ECRSDV/AECRSDV/SCL4/SDO2/U3TX/PMA3/CN10/RG8

PGEC1/AN1/CN3/RB1

PGED1/AN0/CN2/RB0

V

DD

AERXERR/RG15

ERXCLK/AERXCLK/EREFCLK/AEREFCLK/SS2

/U6RX/U3CTS/PMA2/CN11/RG9

MCLR

ETXERR/PMD9/RG1

C1TX/ETXD0/PMD10/RF1

VDDETXEN/PMD14/CN15/RD6

V

SS

V

CAP

/V

DDCORE

ETXCLK/PMD15/CN16/RD7

20

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

21

22

1

24

23

25

92949391908988878685848382818079789576

77

969897

99

100

SOSCI/CN1/RC13

SDO1/OC1/INT0/RD0

SCK1/IC3/PMCS2/PMA15/RD10

SS1/

IC2/RD9

RTCC/EMDIO/AEMDIO/IC1/RD8

EMDC/AEMDC/IC4/PMCS1/PMA14/RD1

AETXEN/SDA1/INT4/RA15

AETXCLK/SCL1/INT3/RA14

OSC2/CLKO/RC15

OSC1/CLKI/RC12

V

DD

D+/RG2

V

USB

V

BUS

SCL3/SDO3/U1TX/RF8

D-/RG3

SDA3/SDI3/U1RX/RF2

USBID/RF3

V

SS

SOSCO/T1CK/CN0/RC14

V

REF

+/CV

REF

+/AERXD3/PMA6/RA10

V

REF

-/CV

REF

-/AERXD2/PMA7/RA9

AV

DD

AV

SS

AN8/C1OUT/RB8

AN9/C2OUT/RB9

AN10/CV

REFOUT

/PMA13/RB10

AN11/ERXERR/AETXERR/PMA12/RB11

V

DD

AC1RX/SS4/U5RX/U2CTS/RF12

AC1TX/SCK4/U5TX/U2RTS

/RF13

AETXD0/SS3

/U4RX/U1CTS/CN20/RD14

AETXD1/SCK3/U4TX/U1RTS

/CN21/RD15

V

DD

V

SS

PGEC2/AN6/OCFA/RB6

PGED2/AN7/RB7

SCL5/SDO4/U2TX/PMA8/CN18/RF5

SDA5/SDI4/U2RX/PMA9/CN17/RF4

AN12/ERXD0/AECRS/PMA11/RB12

AN13/ERXD1/AECOL/PMA10/RB13

AN14/ERXD2/AETXD3/PMALH/PMA1/RB14

AN15/ERXD3/AETXD2/OCFB/PMALL/PMA0/CN12/RB15

TDO/RA5

SDA2/RA3

SCL2/RA2

V

SS

V

SS

TDI/RA4

TCK/RA1

65

64

63

62

61

60

59

56

45

44

43

42

41

40

39

2829303132333435363738

72

71

70

69

68

67

66

75

74

73

58

57

27

464748

49

55

54

53

52

51

50

26

Pin Diagrams (Continued)

PIC32MX5XX/6XX/7XX

Pin Diagrams (Continued)

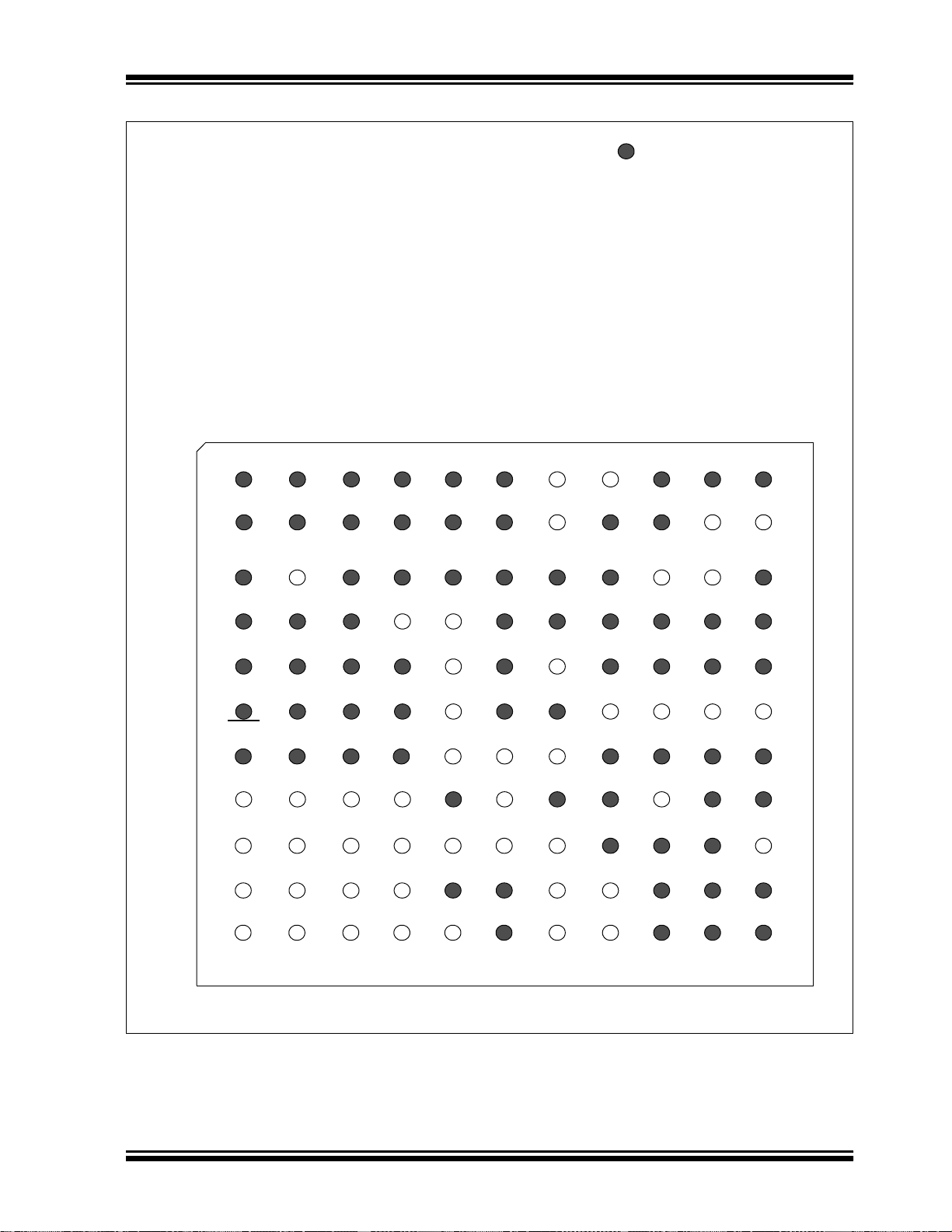

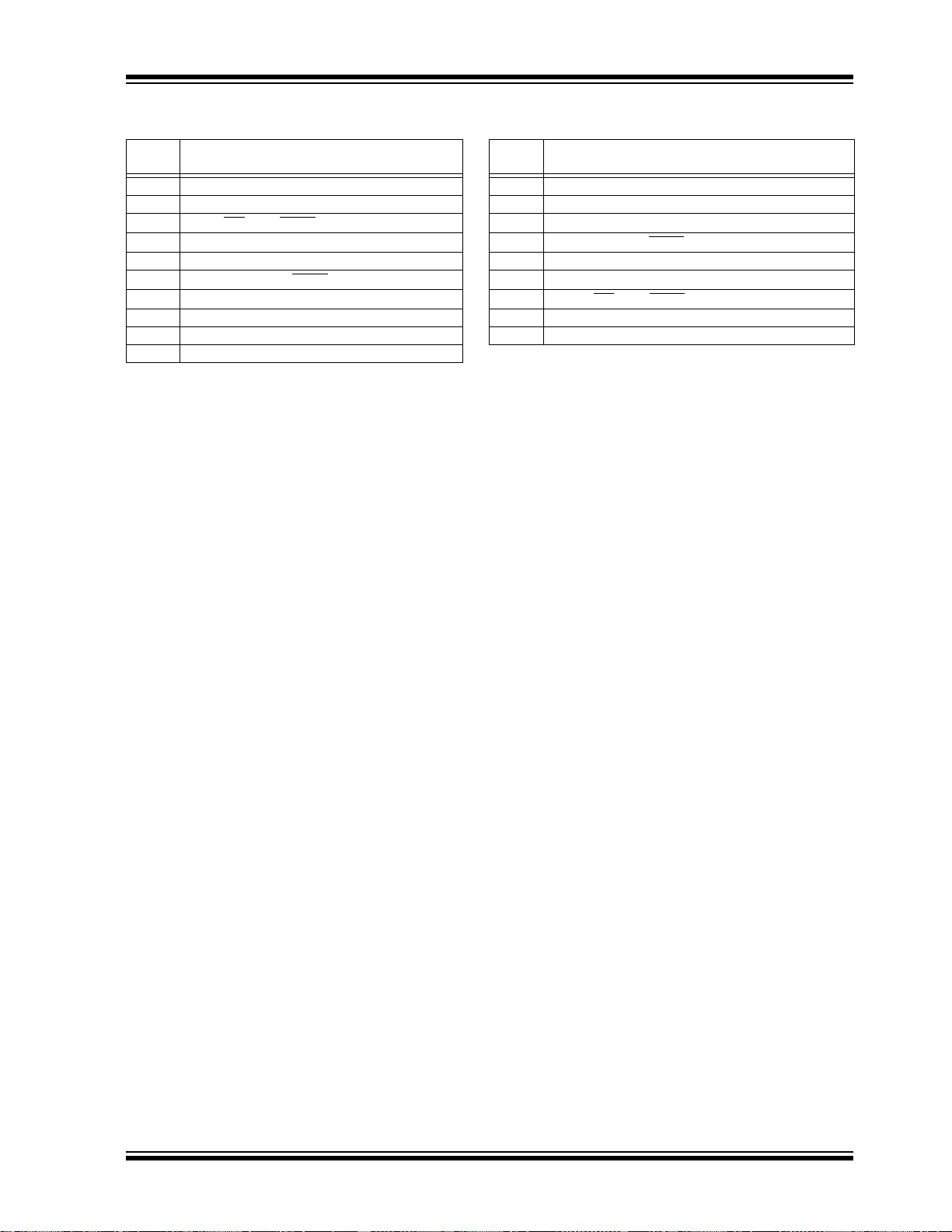

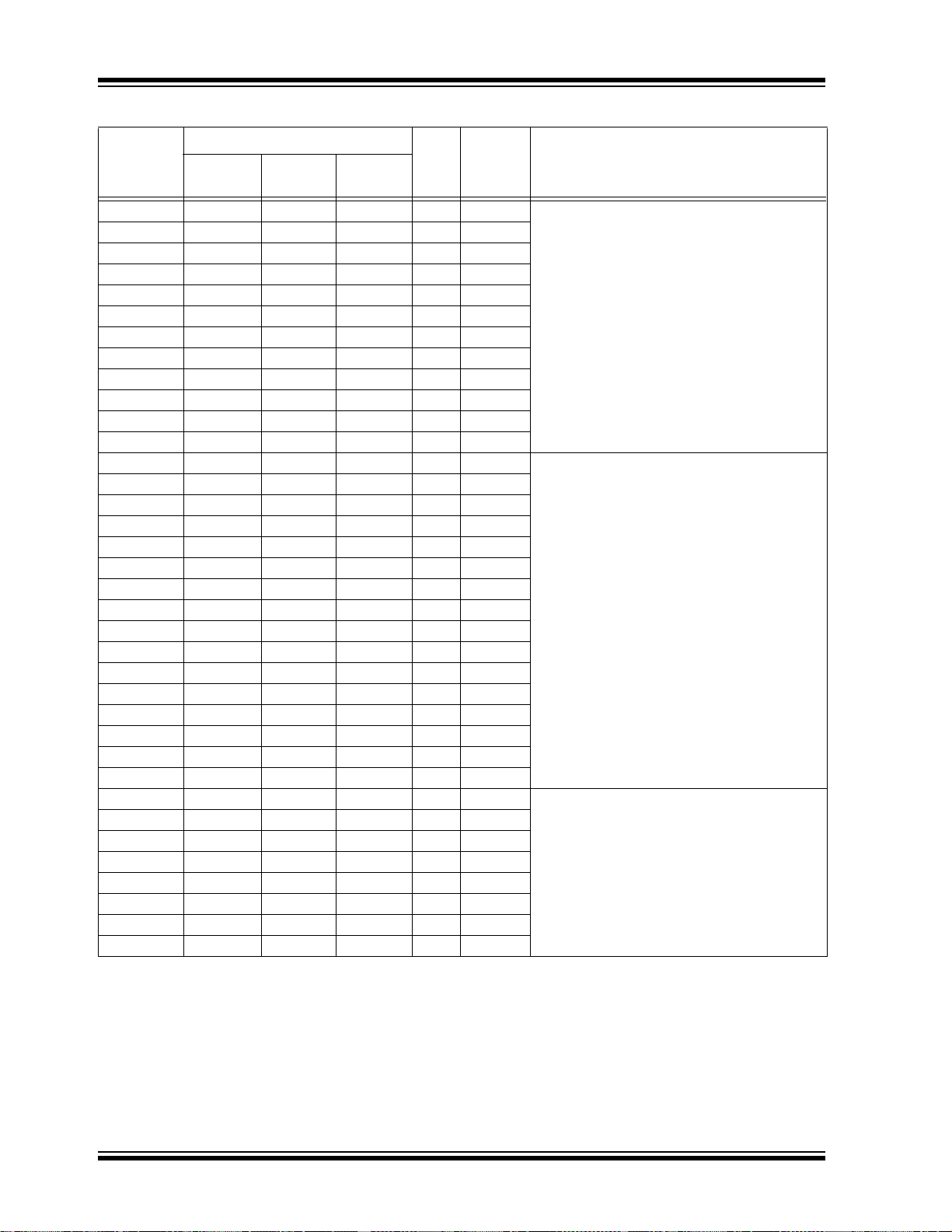

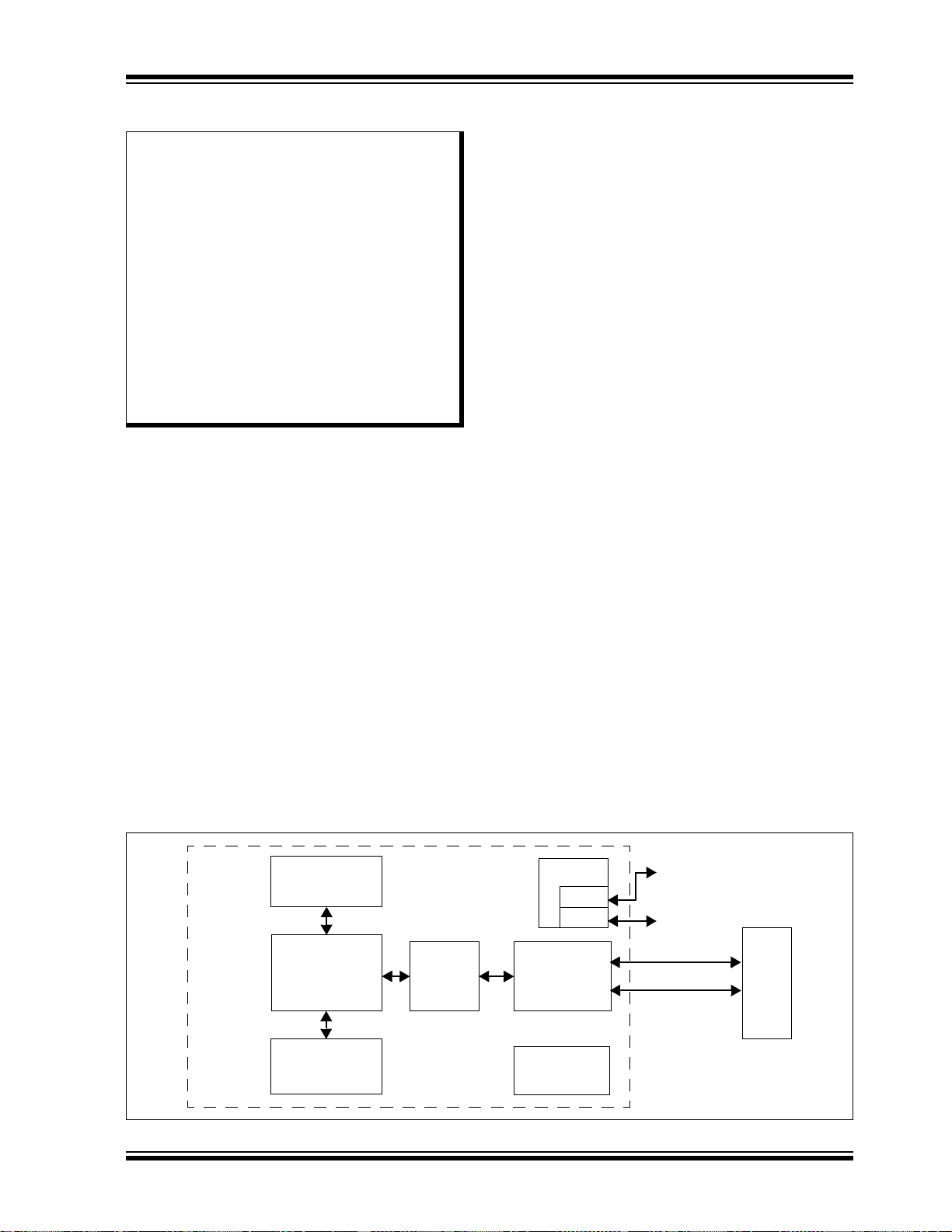

121-Pin XBGA

(1)

1234567891011

A

RE4 RE3 RG13 RE0 RG0 RF1 VDD VSS RD12 RD2 RD1

B

NC RG15 RE2 RE1 RA7 RF0 VCAP/

V

CORE

RD5 RD3 VSS RC14

C

RE6 VDD RG12 RG14 RA6 NC RD7 RD4 VDD RC13 RD11

D

RC1 RE7 RE5 VSS VSS NC RD6 RD13 RD0 NC RD10

E

RC4 RC3 RG6 RC2 VDD RG1 VSS RA15 RD8 RD9 RA14

F

MCLR RG8 RG9 RG7 VSS NC NC VDD RC12 VSS RC15

G

RE8 RE9 RA0 NC VDD VSS VSS NC RA5 RA3 RA4

H

RB5 RB4 VSS VDD NC VDD NC VBUS VUSB RG2 RA2

J

RB3 RB2 RB7 AVDD RB11 RA1 RB12 NC NC RF8 RG3

K

RB1 RB0 RA10 RB8 NC RF12 RB14 VDD RD15 RF3 RF2

L

RB6 RA9 AVSS RB9 RB10

RF13

RB13 RB15 RD14 RF4 RF5

PIC32MX575F256L

Note 1: Refer to Table 4, Tab l e 5 and Ta bl e 6 for full pin names.

= Pins are up to 5V tolerant

PIC32MX795F512L

PIC32MX575F512L

PIC32MX675F512L

PIC32MX695F512L

PIC32MX675F256L

PIC32MX775F256L

PIC32MX775F512L

PIC32MX534F064L

PIC32MX564F064L

PIC32MX564F128L

PIC32MX664F064L

PIC32MX664F128L

PIC32MX764F128L

PIC32MX5XX/6XX/7XX

© 2009-2011 Microchip Technology Inc. DS61156G-page 19

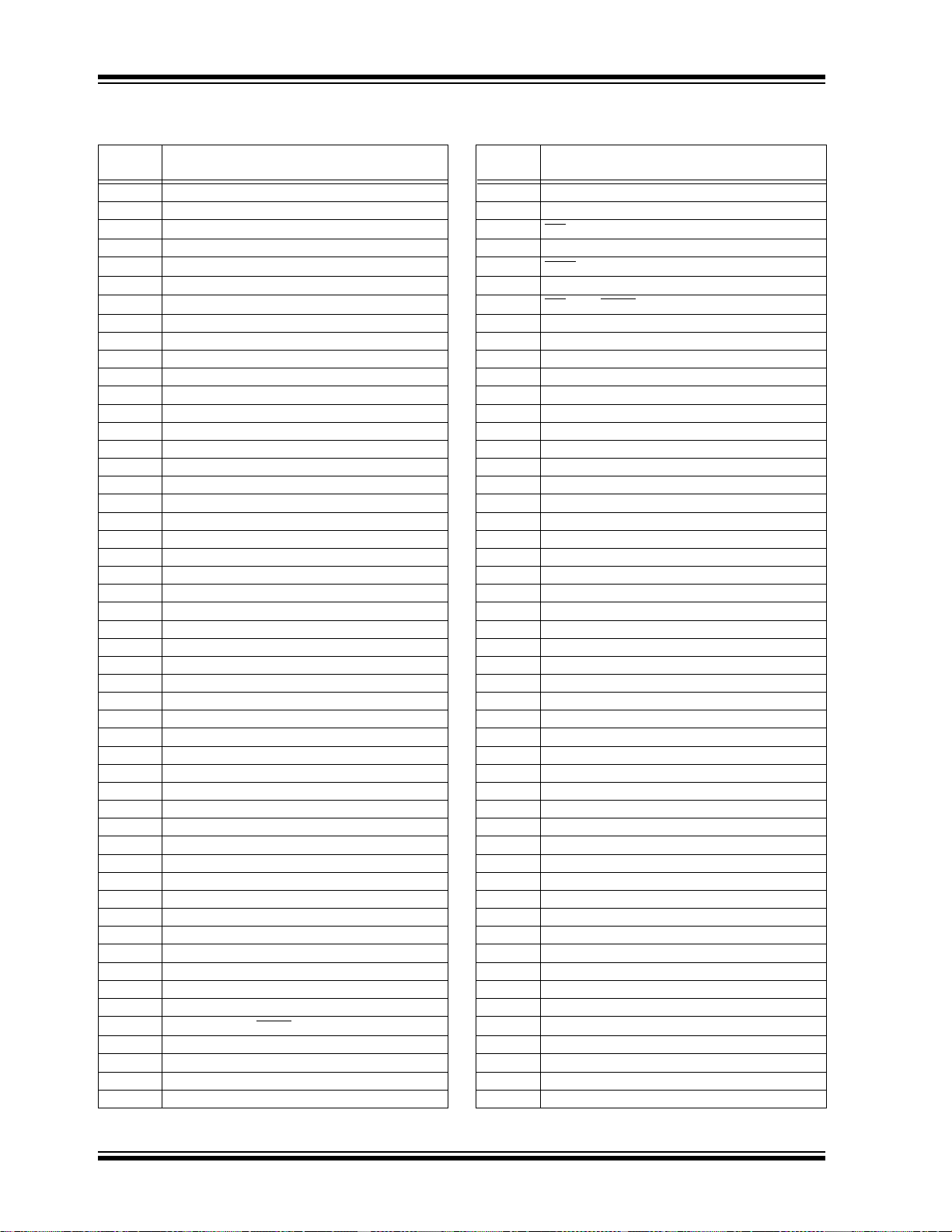

PIC32MX5XX/6XX/7XX

TABLE 4: PIN NAMES: PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L,

PIC32MX575F256L AND PIC32MX575F512L DEVICES

Pin

Number

Full Pin Name

A1 PMD4/RE4 E8 SDA1/INT4/RA15

A2 PMD3/RE3 E9 RTCC/IC1/RD8

A3 TRD0/RG13 E10 SS1

A4 PMD0/RE0 E11 SCL1/INT3/RA14

A5 PMD8/RG0 F1 MCLR

A6 C1TX/PMD10/RF1 F2 SCL4/SDO2/U3TX/PMA3/CN10/RG8

A7 V

A8 V

DD F3 SS2/U6RX/U3CTS/PMA2/CN11/RG9

SS F4 SDA4/SDI2/U3RX/PMA4/CN9/RG7

A9 IC5/PMD12/RD12 F5 V

A10 OC3/RD2 F6 No Connect (NC)

A11 OC2/RD1 F7 No Connect (NC)

B1 No Connect (NC) F8 V

B2 RG15 F9 OSC1/CLKI/RC12

B3 PMD2/RE2 F10 V

B4 PMD1/RE1 F11 OSC2/CLKO/RC15

B5 TRD3/RA7 G1 INT1/RE8

B6 C1RX/PMD11/RF0 G2 INT2/RE9

B7 V

CAP/VCORE G3 TMS/RA0

B8 PMRD/CN14/RD5 G4 No Connect (NC)

B9 OC4/RD3 G5 V

B10 VSS G6 VSS

B11 SOSCO/T1CK/CN0/RC14 G7 VSS

C1 PMD6/RE6 G8 No Connect (NC)

C2 V

DD G9 TDO/RA5

C3 TRD1/RG12 G10 SDA2/RA3

C4 TRD2/RG14 G11 TDI/RA4

C5 TRCLK/RA6 H1 AN5/C1IN+/V

C6 No Connect (NC) H2 AN4/C1IN-/CN6/RB4

C7 PMD15/CN16/RD7 H3 V

C8 OC5/PMWR/CN13/RD4 H4 VDD

C9 VDD H5 No Connect (NC)

C10 SOSCI/CN1/RC13 H6 V

C11 IC4/PMCS1/PMA14/RD11 H7 No Connect (NC)

D1 T2CK/RC1 H8 V

D2 PMD7/RE7 H9 VUSB

D3 PMD5/RE5 H10 D+/RG2

D4 V

D5 V

SS H11 SCL2/RA2

SS J1 AN3/C2IN+/CN5/RB3

D6 No Connect (NC) J2 AN2/C2IN-/CN4/RB2

D7 PMD14/CN15/RD6 J3 PGED2/AN7/RB7

D8 PMD13/CN19/RD13 J4 AV

D9 SDO1/OC1/INT0/RD0 J5 AN11/PMA12/RB11

D10 No Connect (NC) J6 TCK/RA1

D11 SCK1/IC3/PMCS2/PMA15/RD10 J7 AN12/PMA11/RB12

E1 T5CK/SDI1/RC4 J8 No Connect (NC)

E2 T4CK/RC3 J9 No Connect (NC)

E3 SCK2/U6TXU6TX/U3RTS

/PMA5/CN8/RG6 J10 SCL3/SDO3/U1TX/RF8

E4 T3CK/RC2 J11 D-/RG3

E5 V

DD K1 PGEC1/AN1/CN3/RB1

E6 PMD9/RG1 K2 PGED1/AN0/CN2/RB0

E7 V

SS K3 VREF+/CVREF+/PMA6/RA10

Pin

Number

Full Pin Name

/IC2/RD9

SS

DD

SS

DD

BUSON/CN7/RB5

SS

DD

BUS

DD

DS61156G-page 20 © 2009-2011 Microchip Technology Inc.

PIC32MX5XX/6XX/7XX

TABLE 4: PIN NAMES: PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L,

PIC32MX575F256L AND PIC32MX575F512L DEVICES (CONTINUED)

Pin

Number

K4 AN8/C1OUT/RB8 L3 AVSS

K5 No Connect (NC) L4 AN9/C2OUT/RB9

K6 AC1RX/SS4

K7 AN14/PMALH/PMA1/RB14 L6 AC1TX/SCK4/U5TX/U2RTS

K8 V

K9 SCK3/U4TX/U1RTS

K10 USBID/RF3 L9 SS3

K11 SDA3/SDI3/U1RX/RF2 L10 SDA5/SDI4/U2RX/PMA9/CN17/RF4

L1 PGEC2/AN6/OCFA/RB6 L11 SCL5/SDO4/U2TX/PMA8/CN18/RF5

L2 V

DD L7 AN13/PMA10/RB13

REF-/CVREF-/PMA7/RA9

Full Pin Name

/U5RX/U2CTS/RF12 L5 AN10/CVREFOUT/PMA13/RB10

/CN21/RD15 L8 AN15/OCFB/PMALL/PMA0/CN12/RB15

Pin

Number

Full Pin Name

/RF13

/U4RX/U1CTS/CN20/RD14

© 2009-2011 Microchip Technology Inc. DS61156G-page 21

PIC32MX5XX/6XX/7XX

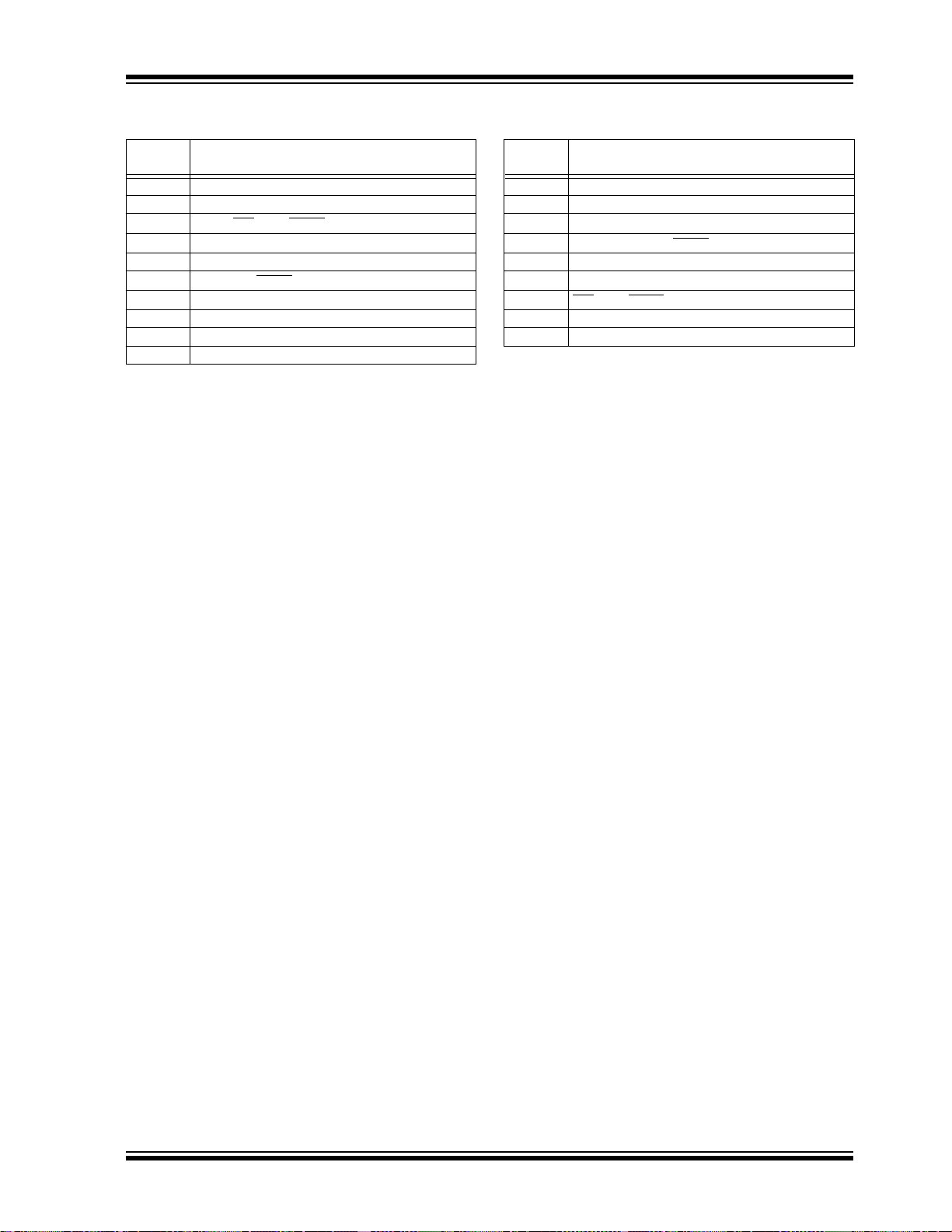

TABLE 5: PIN NAMES: PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L,

PIC32MX675F512L AND PIC32MX695F512L DEVICES

Pin

Number

Full Pin Name

A1 PMD4/RE4 E8 AETXEN/SDA1/INT4/RA15

A2 PMD3/RE3 E9 RTCC/EMDIO/AEMDIO/IC1/RD8

A3 TRD0/RG13 E10 SS1

A4 PMD0/RE0 E11 AETXCLK/SCL1/INT3/RA14

A5 PMD8/RG0 F1 MCLR

A6 ETXD0/PMD10/RF1 F2 ERXDV/AERXDV/ECRSDV/AECRSDV//SCL4/SDO2/

DD F3 ERXCLK/AERXCLK/EREFCLK/AEREFCLK//SS2/U6RX/

A7 V

SS F4 ECRS/SDA4/SDI2/U3RX/PMA4/CN9/RG7

A8 V

A9 ETXD2/IC5/PMD12/RD12 F5 V

A10 OC3/RD2 F6 No Connect (NC)

A11 OC2/RD1 F7 No Connect (NC)

B1 No Connect (NC) F8 V

B2 AERXERR/RG15 F9 OSC1/CLKI/RC12

B3 PMD2/RE2 F10 V

B4 PMD1/RE1 F11 OSC2/CLKO/RC15

B5 TRD3/RA7 G1 AERXD0/INT1/RE8

B6 ETXD1/PMD11/RF0 G2 AERXD1/INT2/RE9

CAP/VCORE G3 TMS/RA0

B7 V

B8 PMRD/CN14/RD5 G4 No Connect (NC)

B9 OC4/RD3 G5 V

B10 VSS G6 VSS

B11 SOSCO/T1CK/CN0/RC14 G7 VSS

C1 PMD6/RE6 G8 No Connect (NC)

DD G9 TDO/RA5

C2 V

C3 TRD1/RG12 G10 SDA2/RA3

C4 TRD2/RG14 G11 TDI/RA4

C5 TRCLK/RA6 H1 AN5/C1IN+/V

C6 No Connect (NC) H2 AN4/C1IN-/CN6/RB4

C7 ETXCLK/PMD15/CN16/RD7 H3 V

C8 OC5/PMWR/CN13/RD4 H4 VDD

C9 VDD H5 No Connect (NC)

C10 SOSCI/CN1/RC13 H6 V

C11 EMDC/AEMDC/IC4/PMCS1/PMA14/RD11 H7 No Connect (NC)

D1 T2CK/RC1 H8 V

D2 PMD7/RE7 H9 VUSB

D3 PMD5/RE5 H10 D+/RG2

SS H11 SCL2/RA2

D4 V

SS J1 AN3/C2IN+/CN5/RB3

D5 V

D6 No Connect (NC) J2 AN2/C2IN-/CN4/RB2

D7 ETXEN/PMD14/CN15/RD6 J3 PGED2/AN7/RB7

D8 ETXD3/PMD13/CN19/RD13 J4 AV

D9 SDO1/OC1/INT0/RD0 J5 AN11/ERXERR/AETXERR/PMA12/RB11

D10 No Connect (NC) J6 TCK/RA1

D11 SCK1/IC3/PMCS2/PMA15/RD10 J7 AN12/ERXD0/AECRS/PMA11/RB12

E1 T5CK/SDI1/RC4 J8 No Connect (NC)

E2 T4CK/RC3 J9 No Connect (NC)

E3 ECOL/SCK2/U6TX/U3RTS

/PMA5/CN8/RG6 J10 SCL3/SDO3/U1TX/RF8

E4 T3CK/RC2 J11 D-/RG3

DD K1 PGEC1/AN1/CN3/RB1

E5 V

E6 ETXERR/PMD9/RG1 K2 PGED1/AN0/CN2/RB0

SS K3 VREF+/CVREF+/AERXD3/PMA6/RA10

E7 V

Pin

Number

/IC2/RD9

U3TX/PMA3/CN10/RG8

/PMA2/CN11/RG9

U3CTS

SS

DD

SS

DD

BUSON/CN7/RB5

SS

DD

BUS

DD

Full Pin Name

DS61156G-page 22 © 2009-2011 Microchip Technology Inc.

PIC32MX5XX/6XX/7XX

TABLE 5: PIN NAMES: PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L,

PIC32MX675F512L AND PIC32MX695F512L DEVICES (CONTINUED)

Pin

Number

K4 AN8/C1OUT/RB8 L3 AVSS

K5 No Connect (NC) L4 AN9/C2OUT/RB9

K6 SS4

K7 AN14/ERXD2/AETXD3/PMALH/PMA1/RB14 L6 SCK4/U5TX/U2RTS

K8 V

K9 AETXD1/SCK3/U4TX/U1RTS

K10 USBID/RF3 L9 AETXD0/SS3

K11 SDA3/SDI3/U1RX/RF2 L10 SDA5/SDI4/U2RX/PMA9/CN17/RF4

L1 PGEC2/AN6/OCFA/RB6 L11 SCL5/SDO4/U2TX/PMA8/CN18/RF5

L2 V

/U5RX/U2CTS/RF12 L5 AN10/CVREFOUT/PMA13/RB10

DD L7 AN13/ERXD1/AECOL/PMA10/RB13

REF-/CVREF-/AERXD2/PMA7/RA9

Full Pin Name

/CN21/RD15 L8 AN15/ERXD3/AETXD2/OCFB/PMALL/PMA0/CN12/RB15

Pin

Number

Full Pin Name

/RF13

/U4RX/U1CTS/CN20/RD14

© 2009-2011 Microchip Technology Inc. DS61156G-page 23

PIC32MX5XX/6XX/7XX

TABLE 6: PIN NAMES: PIC32MX775F256L, PIC32MX775F512L AND

PIC32MX795F512L DEVICES

Pin

Number

Full Pin Name

A1 PMD4/RE4 E8 AETXEN/SDA1/INT4/RA15

A2 PMD3/RE3 E9 RTCC/EMDIO/AEMDIO/IC1/RD8

A3 TRD0/RG13 E10 SS1

A4 PMD0/RE0 E11 AETXCLK/SCL1/INT3/RA14

A5 C2RX/PMD8/RG0 F1 MCLR

A6 C1TX/ETXD0/PMD10/RF1 F2 ERXDV/AERXDV/ECRSDV/AECRSDV/SCL4/SDO2/

DD F3 ERXCLK/AERXCLK/EREFCLK/AEREFCLK/SS2/U6RX/

A7 V

SS F4 ECRS/SDA4/SDI2/U3RX/PMA4/CN9/RG7

A8 V

A9 ETXD2/IC5/PMD12/RD12 F5 V

A10 OC3/RD2 F6 No Connect (NC)

A11 OC2/RD1 F7 No Connect (NC)

B1 No Connect (NC) F8 V

B2 AERXERR/RG15 F9 OSC1/CLKI/RC12

B3 PMD2/RE2 F10 V

B4 PMD1/RE1 F11 OSC2/CLKO/RC15

B5 TRD3/RA7 G1 AERXD0/INT1/RE8

B6 C1RX/ETXD1/PMD11/RF0 G2 AERXD1/INT2/RE9

CAP/VCORE G3 TMS/RA0

B7 V

B8 PMRD/CN14/RD5 G4 No Connect (NC)

B9 OC4/RD3 G5 V

B10 VSS G6 VSS

B11 SOSCO/T1CK/CN0/RC14 G7 VSS

C1 PMD6/RE6 G8 No Connect (NC)

DD G9 TDO/RA5

C2 V

C3 TRD1/RG12 G10 SDA2/RA3

C4 TRD2/RG14 G11 TDI/RA4

C5 TRCLK/RA6 H1 AN5/C1IN+/V

C6 No Connect (NC) H2 AN4/C1IN-/CN6/RB4

C7 ETXCLK/PMD15/CN16/RD7 H3 V

C8 OC5/PMWR/CN13/RD4 H4 VDD

C9 VDD H5 No Connect (NC)

C10 SOSCI/CN1/RC13 H6 V

C11 EMDC/AEMDC/IC4/PMCS1/PMA14/RD11 H7 No Connect (NC)

D1 T2CK/RC1 H8 V

D2 PMD7/RE7 H9 VUSB

D3 PMD5/RE5 H10 D+/RG2

SS H11 SCL2/RA2

D4 V

SS J1 AN3/C2IN+/CN5/RB3

D5 V

D6 No Connect (NC) J2 AN2/C2IN-/CN4/RB2

D7 ETXEN/PMD14/CN15/RD6 J3 PGED2/AN7/RB7

D8 ETXD3/PMD13/CN19/RD13 J4 AV

D9 SDO1/OC1/INT0/RD0 J5 AN11/ERXERR/AETXERR/PMA12/RB11

D10 No Connect (NC) J6 TCK/RA1

D11 SCK1/IC3/PMCS2/PMA15/RD10 J7 AN12/ERXD0/AECRS/PMA11/RB12

E1 T5CK/SDI1/RC4 J8 No Connect (NC)

E2 T4CK/AC2RX/RC3 J9 No Connect (NC)

E3 ECOL/SCK2/U6TX/U3RTS

/PMA5/CN8/RG6 J10 SCL3/SDO3/U1TX/RF8

E4 T3CK/AC2TX/RC2 J11 D-/RG3

DD K1 PGEC1/AN1/CN3/RB1

E5 V

E6 C2TX/ETXERR/PMD9/RG1 K2 PGED1/AN0/CN2/RB0

SS K3 VREF+/CVREF+/AERXD3/PMA6/RA10

E7 V

Pin

Number

/IC2/RD9

U3TX/PMA3/CN10/RG8

/PMA2/CN11/RG9

U3CTS

SS

DD

SS

DD

BUSON/CN7/RB5

SS

DD

BUS

DD

Full Pin Name

DS61156G-page 24 © 2009-2011 Microchip Technology Inc.

PIC32MX5XX/6XX/7XX

TABLE 6: PIN NAMES: PIC32MX775F256L, PIC32MX775F512L AND

PIC32MX795F512L DEVICES (CONTINUED)

Pin

Number

K4 AN8/C1OUT/RB8 L3 AVSS

K5 No Connect (NC) L4 AN9/C2OUT/RB9

K6 AC1RX/SS4

K7 AN14/ERXD2/AETXD3/PMALH/PMA1/RB14 L6 AC1TX/SCK4/U5TX/U2RTS

DD L7 AN13/ERXD1/AECOL/PMA10/RB13

K8 V

K9 AETXD1/SCK3/U4TX/U1RTS

K10 USBID/RF3 L9 AETXD0/SS3

K11 SDA3/SDI3/U1RX/RF2 L10 SDA5/SDI4/U2RX/PMA9/CN17/RF4

L1 PGEC2/AN6/OCFA/RB6 L11 SCL5/SDO4/U2TX/PMA8/CN18/RF5

REF-/CVREF-/AERXD2/PMA7/RA9

L2 V

Full Pin Name

/U5RX/U2CTS/RF12 L5 AN10/CVREFOUT/PMA13/RB10

/CN21/RD15 L8 AN15/ERXD3/AETXD2/OCFB/PMALL/PMA0/CN12/RB15

Pin

Number

Full Pin Name

/U4RX/U1CTS/CN20/RD14

/RF13

© 2009-2011 Microchip Technology Inc. DS61156G-page 25

PIC32MX5XX/6XX/7XX

TABLE 7: PIN NAME: PIC32MX764F128L DEVICE

Pin

Number

Full Pin Name

A1 PMD4/RE4 E8 AETXEN/SDA1/INT4/RA15

A2 PMD3/RE3 E9 RTCC/EMDIO/AEMDIO/IC1/RD8

A3 TRD0/RG13 E10 SS1

A4 PMD0/RE0 E11 AETXCLK/SCL1/INT3/RA14

A5 PMD8/RG0 F1 MCLR

A6 C1TX/ETXD0/PMD10/RF1 F2 ERXDV/AERXDV/ECRSDV/AECRSDV/SCL4/SDO2/

A7 V

DD F3 ERXCLK/AERXCLK/EREFCLK/AEREFCLK/SS2/U6RX/

SS F4 ECRS/SDA4/SDI2/U3RX/PMA4/CN9/RG7

A8 V

A9 ETXD2/IC5/PMD12/RD12 F5 V

A10 OC3/RD2 F6 No Connect (NC)

A11 OC2/RD1 F7 No Connect (NC)

B1 No Connect (NC) F8 V

B2 AERXERR/RG15 F9 OSC1/CLKI/RC12

B3 PMD2/RE2 F10 V

B4 PMD1/RE1 F11 OSC2/CLKO/RC15

B5 TRD3/RA7 G1 AERXD0/INT1/RE8

B6 C1RX/ETXD1/PMD11/RF0 G2 AERXD1/INT2/RE9

CAP/VCORE G3 TMS/RA0

B7 V

B8 PMRD/CN14/RD5 G4 No Connect (NC)

B9 OC4/RD3 G5 V

B10 VSS G6 VSS

B11 SOSCO/T1CK/CN0/RC14 G7 VSS

C1 PMD6/RE6 G8 No Connect (NC)

DD G9 TDO/RA5

C2 V

C3 TRD1/RG12 G10 SDA2/RA3

C4 TRD2/RG14 G11 TDI/RA4

C5 TRCLK/RA6 H1 AN5/C1IN+/V

C6 No Connect (NC) H2 AN4/C1IN-/CN6/RB4

C7 ETXCLK/PMD15/CN16/RD7 H3 V

C8 OC5/PMWR/CN13/RD4 H4 VDD

C9 VDD H5 No Connect (NC)

C10 SOSCI/CN1/RC13 H6 V

C11 EMDC/AEMDC/IC4/PMCS1/PMA14/RD11 H7 No Connect (NC)

D1 T2CK/RC1 H8 V

D2 PMD7/RE7 H9 VUSB

D3 PMD5/RE5 H10 D+/RG2

SS H11 SCL2/RA2

D4 V

SS J1 AN3/C2IN+/CN5/RB3

D5 V

D6 No Connect (NC) J2 AN2/C2IN-/CN4/RB2

D7 ETXEN/PMD14/CN15/RD6 J3 PGED2/AN7/RB7

D8 ETXD3/PMD13/CN19/RD13 J4 AV

D9 SDO1/OC1/INT0/RD0 J5 AN11/ERXERR/AETXERR/PMA12/RB11

D10 No Connect (NC) J6 TCK/RA1

D11 SCK1/IC3/PMCS2/PMA15/RD10 J7 AN12/ERXD0/AECRS/PMA11/RB12

E1 T5CK/SDI1/RC4 J8 No Connect (NC)

E2 T4CK/RC3 J9 No Connect (NC)

E3 ECOL/SCK2/U6TX/U3RTS

/PMA5/CN8/RG6 J10 SCL3/SDO3/U1TX/RF8

E4 T3CK/RC2 J11 D-/RG3

DD K1 PGEC1/AN1/CN3/RB1

E5 V

E6 ETXERR/PMD9/RG1 K2 PGED1/AN0/CN2/RB0

SS K3 VREF+/CVREF+/AERXD3/PMA6/RA10

E7 V

Pin

Number

/IC2/RD9

U3TX/PMA3/CN10/RG8

/PMA2/CN11/RG9

U3CTS

SS

DD

SS

DD

BUSON/CN7/RB5

SS

DD

BUS

DD

Full Pin Name

DS61156G-page 26 © 2009-2011 Microchip Technology Inc.

PIC32MX5XX/6XX/7XX

TABLE 7: PIN NAME: PIC32MX764F128L DEVICE (CONTINUED)

Pin

Number

K4 AN8/C1OUT/RB8 L3 AVSS

K5 No Connect (NC) L4 AN9/C2OUT/RB9

K6 AC1RX/SS4

K7 AN14/ERXD2/AETXD3/PMALH/PMA1/RB14 L6 AC1TX/SCK4/U5TX/U2RTS/RF13

DD L7 AN13/ERXD1/AECOL/PMA10/RB13

K8 V

K9 AETXD1/SCK3/U4TX/U1RTS

K10 USBID/RF3 L9 AETXD0/SS3

K11 SDA3/SDI3/U1RX/RF2 L10 SDA5/SDI4/U2RX/PMA9/CN17/RF4

L1 PGEC2/AN6/OCFA/RB6 L11 SCL5/SDO4/U2TX/PMA8/CN18/RF5

REF-/CVREF-/AERXD2/PMA7/RA9

L2 V

Full Pin Name

/U5RX/U2CTS/RF12 L5 AN10/CVREFOUT/PMA13/RB10

/CN21/RD15 L8 AN15/ERXD3/AETXD2/OCFB/PMALL/PMA0/CN12/RB15

Pin

Number

Full Pin Name

/U4RX/U1CTS/CN20/RD14

© 2009-2011 Microchip Technology Inc. DS61156G-page 27

PIC32MX5XX/6XX/7XX

Table of Contents

1.0 Device Overview ........................................................................................................................................................................ 31

2.0 Guidelines for Getting Started with 32-bit Microcontrollers ........................................................................................................ 43

3.0 CPU............................................................................................................................................................................................ 49

4.0 Memory Organization ................................................................................................................................................................. 55

5.0 Flash Program Memory............................................................................................................................................................ 117

6.0 Resets ...................................................................................................................................................................................... 119

7.0 Interrupt Controller ................................................................................................................................................................... 121

8.0 Oscillator Configuration ............................................................................................................................................................ 125

9.0 Prefetch Cache......................................................................................................................................................................... 127

10.0 Direct Memory Access (DMA) Controller ................................................................................................................................. 129

11.0 USB On-The-Go (OTG)............................................................................................................................................................ 131

12.0 I/O Ports ................................................................................................................................................................................... 133

13.0 Timer1 ...................................................................................................................................................................................... 135

14.0 Timer2/3, Timer4/5 ................................................................................................................................................................... 137

15.0 Input Capture............................................................................................................................................................................ 139

16.0 Output Compare ....................................................................................................................................................................... 141

17.0 Serial Peripheral Interface (SPI)............................................................................................................................................... 143

18.0 Inter-Integrated Circuit™ (I

19.0 Universal Asynchronous Receiver Transmitter (UART) ........................................................................................................... 147

20.0 Parallel Master Port (PMP)....................................................................................................................................................... 149

21.0 Real-Time Clock and Calendar (RTCC) ................................................................................................................................... 151

22.0 10-bit Analog-to-Digital Converter (ADC) ................................................................................................................................. 153

23.0 Controller Area Network (CAN) ................................................................................................................................................ 155

24.0 Ethernet Controller ................................................................................................................................................................... 157

25.0 Comparator .............................................................................................................................................................................. 159

26.0 Comparator Voltage Reference (CV

27.0 Power-Saving Features ........................................................................................................................................................... 163

28.0 Special Features ...................................................................................................................................................................... 165

29.0 Instruction Set .......................................................................................................................................................................... 177

30.0 Development Support............................................................................................................................................................... 179

31.0 Electrical Characteristics .......................................................................................................................................................... 183

32.0 Packaging Information.............................................................................................................................................................. 225

The Microchip Web Site ..................................................................................................................................................................... 253

Customer Change Notification Service .............................................................................................................................................. 253

Customer Support .............................................................................................................................................................................. 253

Reader Response .............................................................................................................................................................................. 254

Product Identification System............................................................................................................................................................. 255

2

C™).............................................................................................................................................. 145

REF).................................................................................................................................. 161

DS61156G-page 28 © 2009-2011 Microchip Technology Inc.

PIC32MX5XX/6XX/7XX

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of

your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications

Department via E-mail at docerrors@microchip.com or fax the Reader Response Form in the back of this data

sheet to (480) 792-4150. We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner

of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may

exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The

errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

© 2009-2011 Microchip Technology Inc. DS61156G-page 29

PIC32MX5XX/6XX/7XX

NOTES:

DS61156G-page 30 © 2009-2011 Microchip Technology Inc.

PIC32MX5XX/6XX/7XX

Note 1: Some features are not available on all device variants.

2: BOR functionality is provided when the on-board voltage regulator is enabled.

UART1-6

Comparators

PORTA

PORTD

PORTE

PORTF

PORTG

PORTB

CN1-22

JTAG

Priority

DMAC

ICD

MIPS32® M4K

®

IS DS

EJTAG INT

Bus Matrix

Prefetch

Data RAM

Peripheral Bridge

128

128-bit Wide

Flash

32

32 32

32

32

Peripheral Bus Clocked by PBCLK

Program Flash Memory

Controller

32

Module

32

32

Interrupt

Controller

BSCAN

PORTC

PMP

I2C1-5

SPI1-4

IC1-5

PWM

OC1-5

OSC1/CLKI

OSC2/CLKO

V

DD, VSS

Timing

Generation

MCLR

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

Brown-out

Reset

Precision

Reference

Band Gap

FRC/LPRC

Oscillators

Regulator

Voltage

VCAP/VCORE

OSC/SOSC

Oscillators

PLL

Dividers

SYSCLK

PBCLK

Peripheral Bus Clocked by SYSCLK

USB

PLL-USB

USBCLK

32

RTCC

10-bit ADC

Timer1-5

32

32

CAN1, CAN2

ETHERNET

32

32

CPU Core

1.0 DEVICE OVERVIEW

Note 1: This data sheet summarizes the features

of the PIC32MX5XX/6XX/7XX family of

devices. It is not intended to be a

comprehensive reference source. To

complement the information in this data

sheet, refer to the related section of the

“PIC32 Family Reference Manual”, which

is available from the Microchip web site

(www.microchip.com/PIC32).

2: Some registers and associated bits

described in this section may not be

available on all devices. Refer to

Section 4.0 “Memory Organization” in

this data sheet for device-specific register

and bit information.

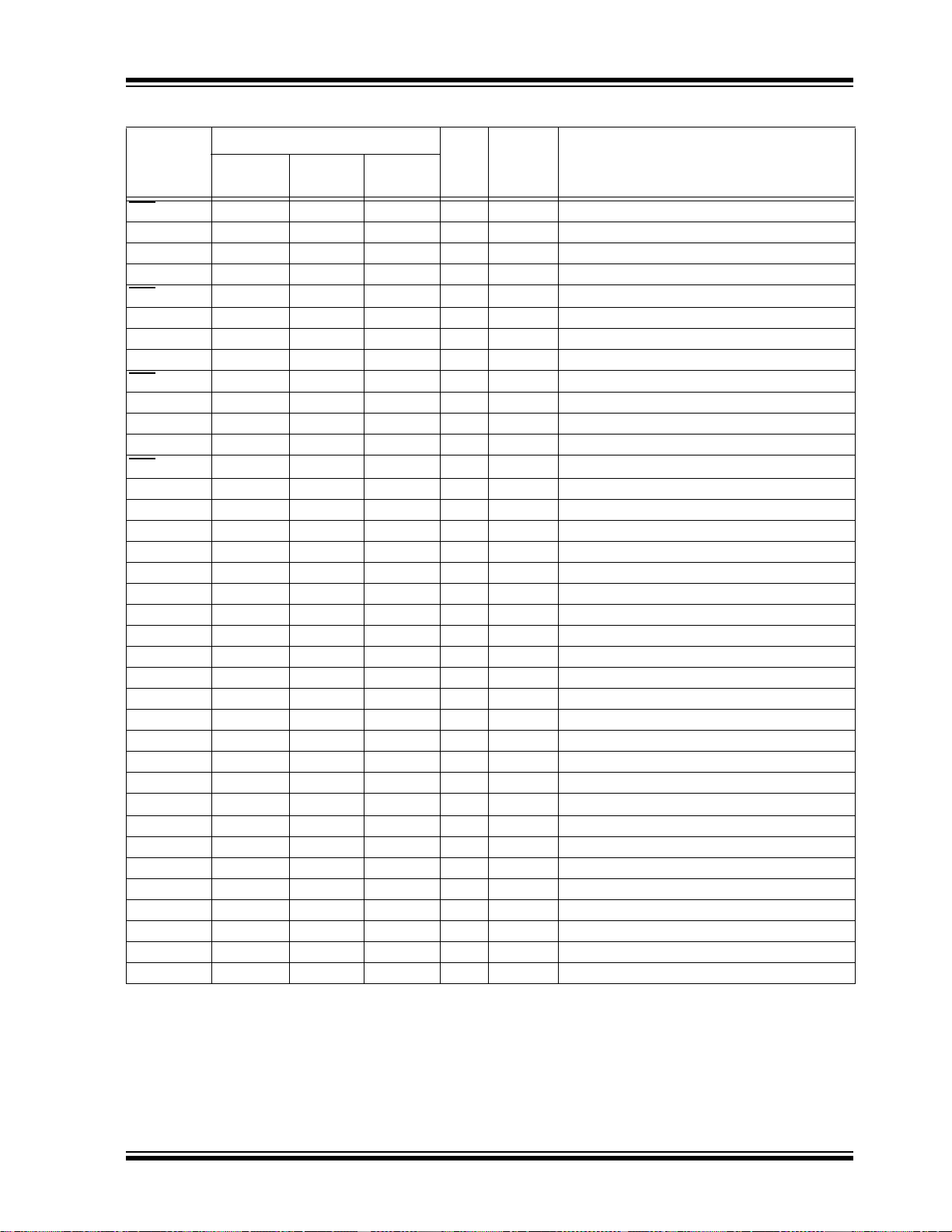

FIGURE 1-1: BLOCK DIAGRAM

(1,2)

This document contains device-specific information for

PIC32MX5XX/6XX/7XX devices.

Figure 1-1 illustrates a general block diagram of the

core and peripheral modules in the

PIC32MX5XX/6XX/7XX family of devices.

Table 1-1 lists the functions of the various pins shown

in the pinout diagrams.

© 2009-2011 Microchip Technology Inc. DS61156G-page 31

PIC32MX5XX/6XX/7XX

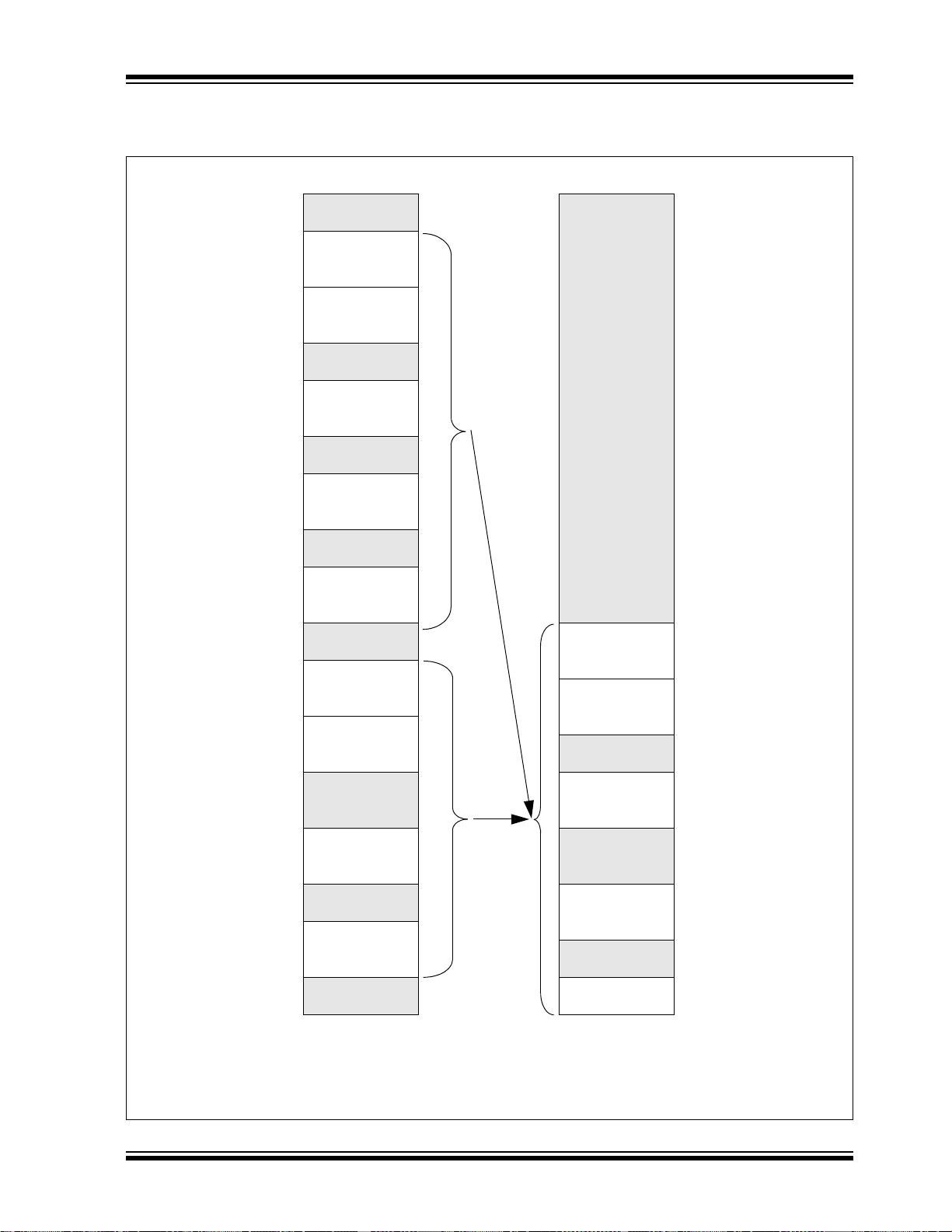

TABLE 1-1: PINOUT I/O DESCRIPTIONS

Pin Number

Pin Name

AN0 16 25 K2 I Analog Analog input channels.

AN1 15 24 K1 I Analog

AN2 14 23 J2 I Analog

AN3 13 22 J1 I Analog

AN4 12 21 H2 I Analog

AN5 11 20 H1 I Analog

AN6 17 26 L1 I Analog

AN7 18 27 J3 I Analog

AN8 21 32 K4 I Analog

AN9 22 33 L4 I Analog

AN10 23 34 L5 I Analog

AN11 24 35 J5 I Analog

AN12 27 41 J7 I Analog

AN13 28 42 L7 I Analog

AN14 29 43 K7 I Analog

AN15 30 44 L8 I Analog

CLKI 39 63 F9 I ST/CMOS External clock source input. Always associated

CLKO 40 64 F11 O — Oscillator crystal output. Connects to crystal or

OSC1 39 63 F9 I ST/CMOS Oscillator crystal input. ST buffer when

OSC2 40 64 F11 I/O — Oscillator crystal output. Connects to crystal or

SOSCI 47 73 C10 I ST/CMOS 32.768 kHz low-power oscillator crystal input;

SOSCO 48 74 B11 O — 32.768 kHz low-power oscillator crystal output.

Legend: CMOS = CMOS compatible input or output Analog = Analog input P = Power

Note 1: Pin numbers are provided for reference only. See the “Pin Diagrams” section for device pin availability.

2: See Section 24.0 “Ethernet Controller” for more information.

64-Pin

QFN/TQFP

ST = Schmitt Trigger input with CMOS levels O = Output I = Input

TTL = TTL input buffer

100-Pin

TQFP

(1)

121-Pin

XBGA

Pin

Type

Buffer

Type

Description

with OSC1 pin function.

resonator in Crystal Oscillator mode. Optionally

functions as CLKO in RC and EC modes.

Always associated with OSC2 pin function.

configured in RC mode; CMOS otherwise.

resonator in Crystal Oscillator mode. Optionally

functions as CLKO in RC and EC modes.

CMOS otherwise.

DS61156G-page 32 © 2009-2011 Microchip Technology Inc.

PIC32MX5XX/6XX/7XX

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

Pin Name

CN0 48 74 B11 I ST Change notification inputs.

CN1 47 73 C10 I ST

CN2 16 25 K2 I ST

CN3 15 24 K1 I ST

CN4 14 23 J2 I ST

CN5 13 22 J1 I ST

CN6 12 21 H2 I ST

CN7 11 20 H1 I ST

CN8 4 10 E3 I ST

CN9 5 11 F4 I ST

CN10 6 12 F2 I ST

CN11 8 14 F3 I ST

CN12 30 44 L8 I ST

CN13 52 81 C8 I ST

CN14 53 82 B8 I ST

CN15 54 83 D7 I ST

CN16 55 84 C7 I ST

CN17 31 49 L10 I ST

CN18 32 50 L11 I ST

CN19 — 80 D8 I ST

CN20 — 47 L9 I ST

CN21 — 48 K9 I ST

IC1 42 68 E9 I ST Capture Inputs 1-5

IC2 43 69 E10 I ST

IC3 44 70 D11 I ST

IC4 45 71 C11 I ST

IC5 52 79 A9 I ST

OCFA 17 26 L1 I ST Output Compare Fault A Input

OC1 46 72 D9 O — Output Compare Output 1

OC2 49 76 A11 O — Output Compare Output 2

OC3 50 77 A10 O — Output Compare Output 3

OC4 51 78 B9 O — Output Compare Output 4

OC5 52 81 C8 O — Output Compare Output 5

OCFB 30 44 L8 I ST Output Compare Fault B Input

INT0 46 72 D9 I ST External Interrupt 0

INT1 42 18 G1 I ST External Interrupt 1

INT2 43 19 G2 I ST External Interrupt 2

INT3 44 66 E11 I ST External Interrupt 3

INT4 45 67 E8 I ST External Interrupt 4

Legend: CMOS = CMOS compatible input or output Analog = Analog input P = Power