Page 1

E2B0031-27-Y2

¡ Semiconductor MSM6778

¡ Semiconductor

This version: Nov. 1997

Previous version: Mar. 1996

MSM6778

120-DOT COMMON DRIVER (TAB)

GENERAL DESCRIPTION

The MSM6778 is a dot-matrix LCD common driver. Fabricated in CMOS technology, the device

contains two 60-bit bidirectional shift registers, two 60-bit level shifters, and two 60-bit 4-level

drivers.

The MSM6778 has 120 LCD outputs. The number of LCD outputs can be increased by cascading

MSM6778 devices, using cascade-connected I/O pins. The bias voltage which specifies a drive

level can optionally be supplied externally. The MSM6778 is suitable for various types of LCD

panel.

FEATURES

• Logic supply voltage : 2.7 V to 5.5 V

• LCD drive voltage : A wide range from 18 V to 28 V

• Applicable LCD duty : 1/100 to 1/256

• The bias voltage can be externally supplied.

• Structure:

35mm-wide Tape Automated Bonding (TAB) film (Product name: MSM6778AV-Z-01)

Tin-plating

1/7

Page 2

¡ Semiconductor MSM6778

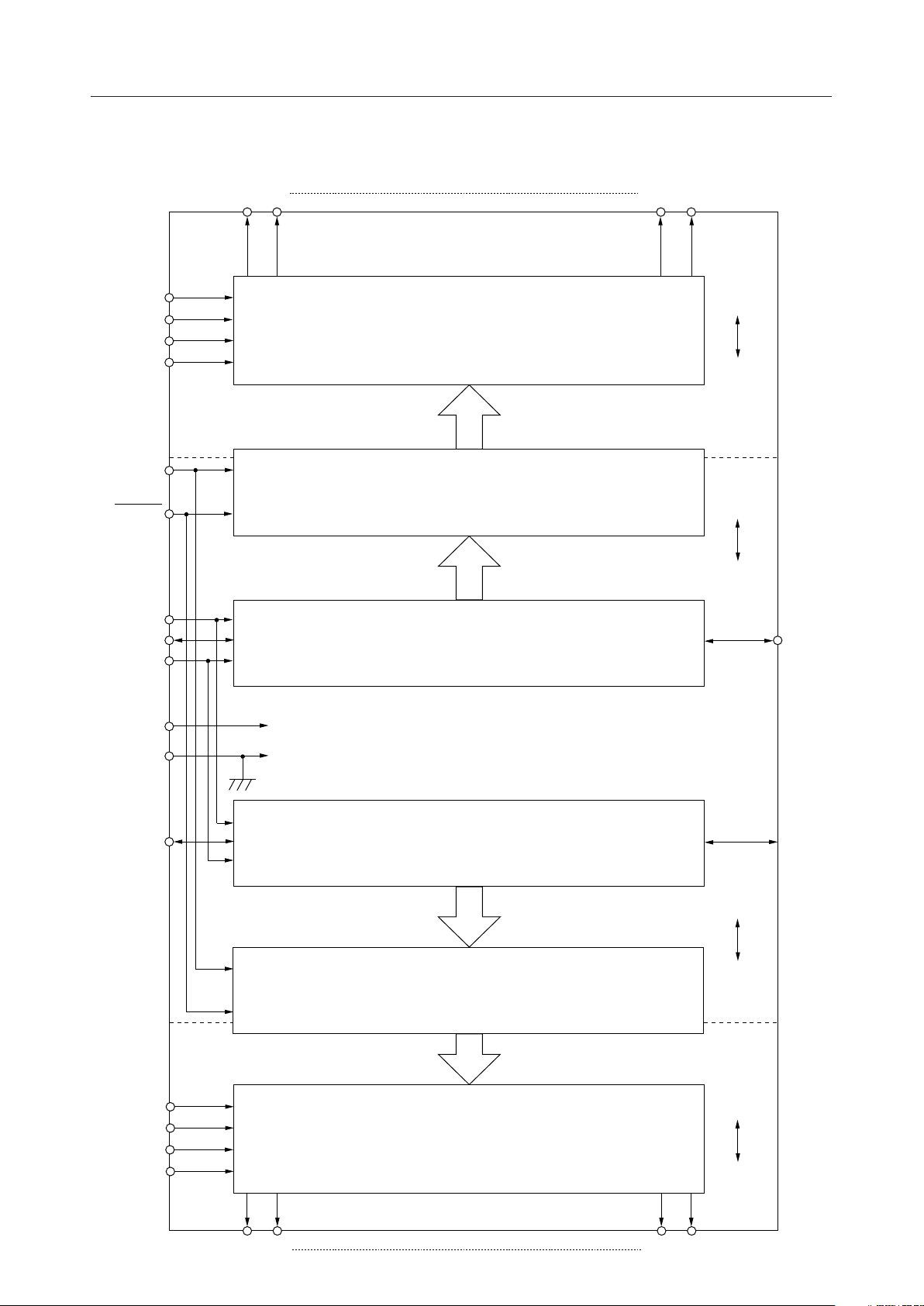

BLOCK DIAGRAM

V

1L

V

2L

V

5L

V

EEL

DF

DISPOFF

SHL

IO

1

CP

O

1O2

60-BIT 4-LEVEL DRIVER

60-BIT LEVEL SHIFTER

60-BIT BI-DIRECTIONAL SHIFT REGISTER

O59O

60

V

DD

V

EE

V

DD

V

SS

IO

60

V

,

V

DDL

DDR

V

SS

IO

61

60-BIT BI-DIRECTIONAL SHIFT REGISTER

V

DD

V

SS

IO

120

60-BIT LEVEL SHIFTER

V

1R

V

2R

V

5R

V

EER

60-BIT 4-LEVEL DRIVER

V

DD

V

EE

O

O

O

62

61

O

120

119

2/7

Page 3

¡ Semiconductor MSM6778

(Inp

)

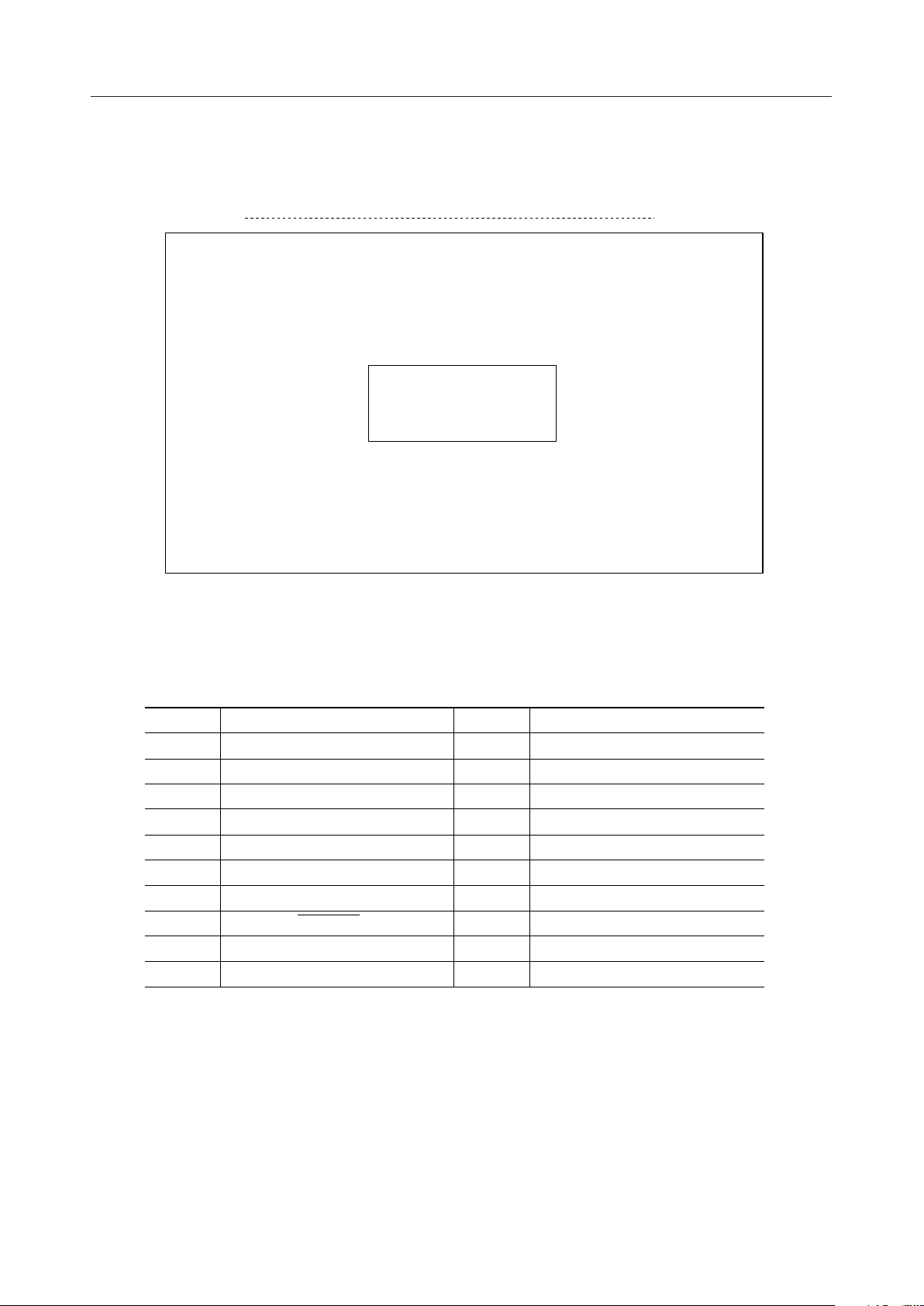

PIN CONFIGURATION (TOP VIEW)

(LCD output side)

O

O

1

2

O

119

O

120

Chip surface

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19

Input Pin Name

Pin Symbol Pin Symbol

1

2

3

4

5

6

7

8

9

10

V

1L

V

2L

V

5L

V

EEL

V

DDL

SHL

V

SS

DISPOFF

IO

1

IO

60

ut pin side

11

12

13

14

15

16

17

18

19

V

V

IO

IO

V

V

V

61

120

DF

CP

DDR

EER

5R

2R

1R

3/7

Page 4

¡ Semiconductor MSM6778

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Condition Rating Unit

Power Supply Voltage (1) V

Power Supply Voltage (2) V

Input Voltage V

Storage Temperature T

* V1>V2>V5>VEE, VDD V1>V2 VDD–10V, VEE+10V V5>V

VDD=V

DDL=VDDR

>

=

, V1=V1L=V1R, V2=V2L=V2R, V5=V5L=V5R, VEE=V

DD

* Ta=25˚C 0 to 30 V

DD–VEE

I

STG

>

=

Ta=25˚C –0.3 to +6.5 V

Ta=25˚C –0.3 to VDD+0.3 V

— –30 to +85 ˚C

>

=

EE

EEL=VEER

RECOMMENDED OPERATING CONDITIONS

Parameter Symbol Condition Range Unit

Power Supply Voltage (1) V

Power Supply Voltage (2) V

DD–VEE

Operating temperature T

DD —

* No load 14 to 28 V

During liquid crystal driving 18 to 28 V

op —

2.7 to 5.5 V

–20 to +75 ˚C

* V1>V2>V5>VEE, VDD V1>V2 VDD–7V, VEE+7V V5>V

VDD=V

DDL=VDDR

>

=

, V1=V1L=V1R, V2=V2L=V2R, V5=V5L=V5R, VEE=V

>

=

>

=

EE

EEL=VEER

Note: Unlike mold packages, The Tape Carrier Package (TCP) cannot shield a light. Please

shield a light to secure the electrical characteristics.

ELECTRICAL CHARACTERISTICS

DC Characteristics

(V

=2.7 to 5.5 V, Ta= –20 to +75˚C)

DD

Parameter

"H" Input Voltage

"L" Input Voltage

"H" Input Current

"L" Input Current

"H" Output Voltage

"L" Output Voltage

ON Resistance

Supply Current

Input Capacitance

Symbol

*1

V

IH

*1

V

IL

I

*1

IH

*1

I

IL

*2

V

OH

*2

V

OL

R

*4

ON

*5

I

DD

*5

I

EE

C

I

Condition

—

—

V

, VDD=5.5 V

I=VDD

=0 V, VDD=5.5 V

V

I

=–0.2 mA, VDD=2.7 V

I

O

=0.2 mA, VDD=2.7 V

I

O

V

I V

CP=28 kHz, V

V

DD–VEE

N–VO I

DD–VEE

=25 V, *3

=0.25 V

=3.0 V

DD

=25 V, No load

f=1 MHz

Min.

0.8 V

—

—

—

V

DD

—

—

—

—

—

DD

–0.4

Typ.

—

—

—

—

—

—

—

—

—

—

Max.

—

0.2 V

1

–1

0.4

2.0

60

400

—

DD

Unit

V

V

mA

mA

V

V

kW

mA

mA

pF

*1 Applicable to pins CP, IO1,IO60,IO61, IO

*2 Applicable to pins IO1, IO60, IO61, IO

, SHL, DF, DISPOFF

120

120

*3 VN=V1, V2, V5, VEE, V2=1/16 (VDD–VEE), V5=15/16 (VDD–VEE)

*4 Applicable to pins O1 to O

120

*5 IDD shows the supply current between VDD and VSS. IEE shows the supply current between

V

and VEE.

DD

Note: The above values are guaranteed when TCP is protected from light.

4/7

Page 5

¡ Semiconductor MSM6778

Switching Characteristics

=2.7 to 5.5 V, Ta= –20 to +75˚C, CL=15 pF)

(V

DD

Parameter Symbol Condition Min. Typ. Max. Unit

, IO61 (IO60, IO

IO

1

120

)

"H", "L" Propagation Delay Time

Clock Frequency

CP Pulse Width

Data Setup Time

, IO

IO

1

(IO60, IO

61 Æ

120 Æ

CP

CP)

t

PLH

t

PHL

f

CP

t

WCP

t

SETUP

—

—

—

—

*1

—

63

100

—

—

—

—

—

—

3

1

ms

MHz

ns

ns

Data Hold Time

Æ

Æ

, IO

IO

1

IO60, IO

61

120

)

CP

(CP

CP Rise, Fall Time

*1 The relationship between t

t

HOLD

t

r (CP)

t

f (CP)

PLH

(t

PLH

—

—

) Min. and t

100

—

Min. satisfies the operation in a cascade

HOLD

—

—

—

20

connection state.

Note 1: When display is controlled by DISPOFF pin, CP rise and fall time must be £ 1 ms.

Note 2: The above values are guaranteed when TCP is protected from light.

IO1 (IO60)

(IO

IO

61

120

CP

t

f (CP)

t

HOLD

t

WCP

t

WCP

0.8V

DD

0.2V

DD

t

SETUP

0.8V

DD

)

0.2V

DD

0.2V

t

r (CP)

0.8V

DD

DD

ns

ns

IO60 (IO1)

(IO61)

IO

120

t

PLH (tPHL)

0.8V

0.2V

DD

DD

5/7

Page 6

¡ Semiconductor MSM6778

FUNCTIONAL DESCRIPTION

Pin Functional Description

• IO1, IO60, IO61, IO

120

These are I/O pins of the two 60-bit bidirectional shift registers.

• SHL

This pin selects the shift direction of the two 60-bit bidirectional shift registers.

Set this pin to "H" or "L" level during power-on.

SHL

Shift Direction

L

O

O

O

1

Æ

60

O

61

Æ

120

I/O pins Function

and IO61 are data input pins for the shift

IO

1

register. The entered data is read in at the falling

IO

IO

60

IO

1

,

61

IO

,

120

Input

Output

edge of a clock pulse. The data is output from

IO

and IO

60

behind the number of bits (60) of

120

the shift register.

and IO

H

O

O

120

60

Æ

Æ

O

1

O

61

IO

IO

60

IO

,

120

IO

1

,

61

Input

Output

IO

60

register. The entered data is read in at the falling

edge of a clock pulse. The data is output from IO

and IO

61

are data input pins for the shift

120

behind the number of bits (60) of the

1

shift register.

• CP

This is a clock pulse input for the two 60-bit bidirectional shift registers. Scan data is shifted at

the falling edge of a clock pulse.

• DF

This is a synchronous signal input for alternate signal for LCD driving.

• DISPOFF

This is an input used to control the output levels of O1 to O

level is output from the output pins O1 to O

independently of the data of the shift register. See

120

. During low level input, the V

120

the truth table.

• O1 to O

120

These are outputs for the 4-level drivers, which correspond directly to each bit of the shift

register. One of the four levels V1, V2, V5, and VEE is selected and output depending on the

combination of the shift register data and a DF signal. See the Truth Table.

• V1L, V2L, V5L, V

, V1R, V2R, V5R, V

EEL

EER

These are LCD drive bias voltage inputs.

• V

DDL

, V

DDR

, V

SS

These are power supply pins for the device. VDD is usually from 2.7 V to 5.5 V and VSS is 0 V.

1

6/7

Page 7

¡ Semiconductor MSM6778

Truth Table

DF

L

L

H

H

X

SHIFT REGISTER DATA

L

H

L

H

X

DISPOFF

H

H

H

H

L

DRIVER OUTPUT (O

V

2

V

EE

V

5

V

1

V

1

to O

1

120

)

X : Don't care

NOTES ON USE (when turning the power ON or OFF)

The LCD drivers of this IC require a high voltage. For this reason, if a high voltage is applied to

the LCD drivers with the logic power supply floating, excess current flows. This may damage

the IC.

Be sure to follow the sequence below when turning the power ON or OFF.

Power ON : Logic circuits ON Æ LCD drivers ON, or both ON at a time

Power OFF : LCD drivers OFF Æ logic circuits OFF, or both OFF at a time

7/7

Loading...

Loading...