Page 1

MITSUMI

Video Amplifier

Monolithic IC MM1002

Outline

This IC is a video amplifier that can perform superimpose. It has a built-in 75Ω driver.

Features

1. Built-in superimpose function

2. Built-in Y-C mix circuit

3. Vertical/horizontal sync signal output pin

4. Built-in clamp circuit (for Y signal only)

5. 75Ω driver built in

6. EVF driver built in

7. External pin (Pin 14) allows fine tuning of character level

8. Frequency response 5MHz

9. Power supply voltage 4.7V~5.3V

Video Amplifier MM1002

Package

SOP-16A (MM1002F)

Applications

1. TV

2. VCR

3. VCR with camera

4. Other video equipment

Block Diagram

Page 2

MITSUMI

Video Amplifier MM1002

Pin Description

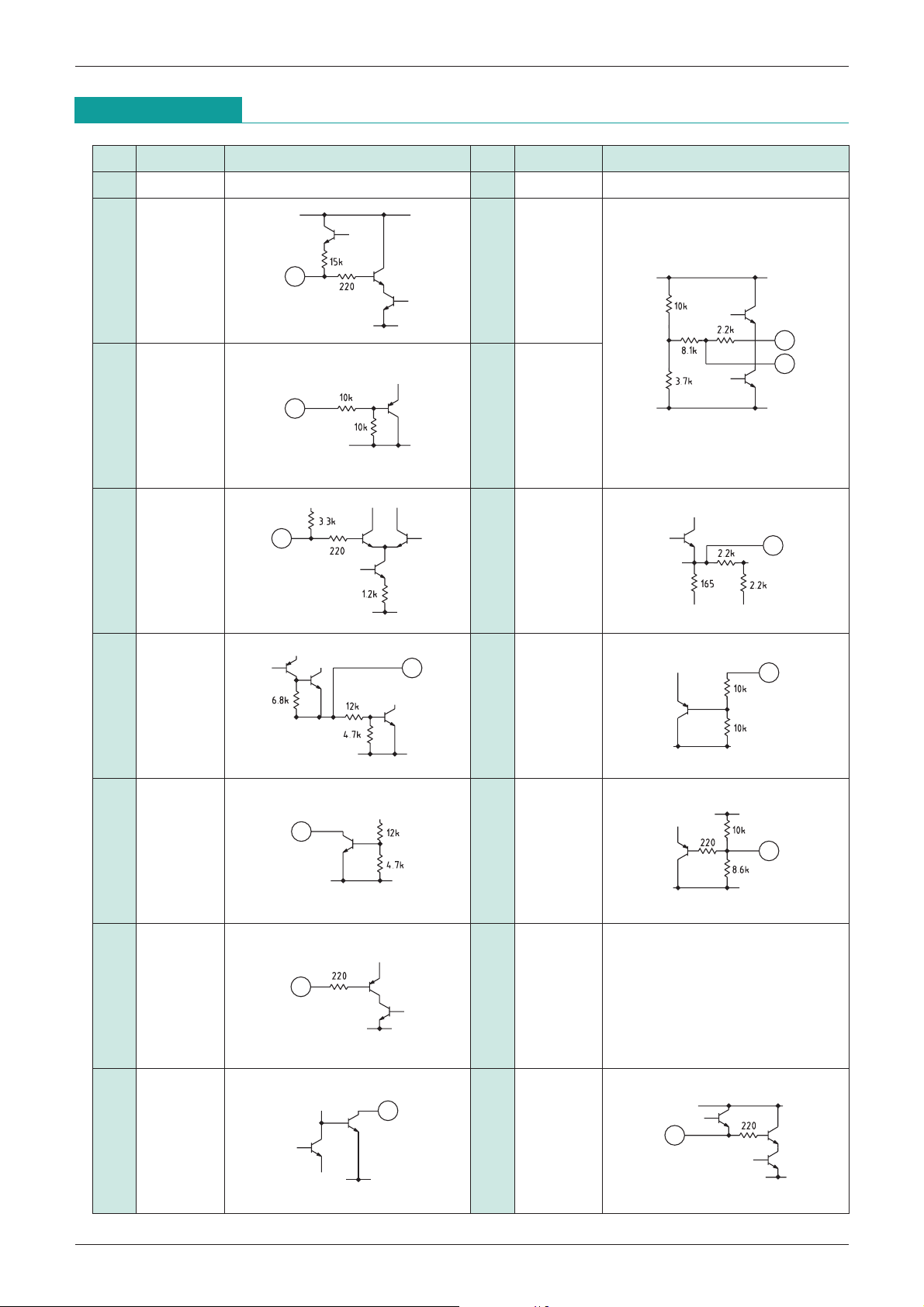

Pin no. Pin name Internal equivalent circuit diagram Pin no. Pin name Internal equivalent circuit diagram

1 NC

2

CHROMA IN

3 MIX

4 C1 12 EVF

9 GND

10

VIDEO OUT

11

Anti-sag

pin

5 R

6 H-SYNC

7 C2

8 V-SYNC 16 VIDEO IN

Character

13

14

15 V

signal

Character

signal level

CC

Page 3

MITSUMI

Video Amplifier MM1002

Absolute Maximum Ratings

(Ta=25°C)

Item Symbol Ratings Units

Storage temperature T

Operating temperature T

Power supply voltage V

STG

OPR

CC 7V

-

40~+125 °C

-

20~+75 °C

Allowable loss Pd 350 mW

Electrical Characteristics

Item

Operating power supply voltage

(Except where noted otherwise, Ta=25°C, VCC=5.0V, pulse level 0V, short between V

Symbo

Measurement

l

circuit

Measurement conditions Min. Typ. Max. Units

VCC VCC 4.7 5.0 5.3 V

Consumption current Id Id 18.0 25.0 mA

EVF output

Voltage gain G

Differential gain DG1 Buf

Differential phase DP1 Buf

Frequency characteristic fc1 TP3

Video amp output

Voltage gain G

Differential gain DG2 Buf

Differential phase DP2 Buf

Frequency characteristic fc2 TP4

Character addition

U1 TP3 SG

U2 TP4 SG

SG-1 staircase wave (no chroma signal) 1V

-

1 sweep signal 1VP

-

P, 0.1MHz

SG-1 staircase wave 1V

APL=10, 50, 90%, SW 1

SG-1 staircase signal 1V

APL=10, 50, 90%, SW 1

SG-1 sweep signal 1V

5MHz/0.1MHz

-

1 sweep wave 1VP

SG

-

1 staircase wave 1VP

*

-

P, 0.1MHz 5.5 6.0 6.5 dB

APL=10, 50, 90%, SW 2

SG-1 staircase signal 1V

APL=10, 50, 90%, SW 2

SG

-

1 sweep signal 1VP

5MHz/0.1MHz

*

-

0.5 0.0 +0.5 dB

P-P

P-P

P-P

1

-

P

P-P

-

P

1

P-P

13%

1 3 deg

-

10 1dB

13%

1 3 deg

-

10 1dB

Character level VCL TP4 HD horizontal sync signal 115 120 125 IRE

TP7 pulse level 5V

SG-1 staircase wave (no chroma signal) 1V

P-P

Input threshold voltage VTH13 TP7 HD horizontal sync signal 0.7 1.4 2.1 V

Chroma amp

Voltage gain G

U3 TP4 SG

Frequency characteristic fc3 TP4

Crosstalk C TP4

Input threshold voltage V

TH3 TP8

Sync separation

Sync separation level V

7PIN threshold voltage

Horizontal sync output voltage

Vertical sync output voltage

SEPA TP1

V

TH7H

TH7L TP9 DC voltage 5V L

V

VOH6

OL6 (no chroma signal) 1VP

V

V

OH8

V

OL8

TP9

TP10

TP11

TP7 pulse level L H

-

2 sine wave 0.1VP

SG-2 sine wave 0.1V

5MHz/0.1MHz

SG

-

2 sine wave 0.1VP

TP8 pulse level 5V

SG

-

2 sine wave 0.1VP

TP8 pulse level L H

SG-1 staircase wave (no chroma signal) 1V

SG-1 SYNC level max min *5

TP9 DC voltage 0V H

SG-1 staircase wave 4.8 5.0 V

SG-1 staircase wave 4.8 5.0 V

(no chroma signal) 1V

2

*

-

P, 0.1MHz 13.5 15.0 16.5 dB

P-P

1

*

-

P, 4MHz

3

*

-

P, 4MHz

4

*

6 1.9 2.1 2.3 V

*

6 1.1 1.3 1.5 V

*

-

P

7 0.2 0.4 V

*

P-P

8

*

-

10 1dB

-

60-40 dB

0.7 1.4 2.1 V

P-P

55 110 165 mV

0.2 0.4 V

CC

-Id pin)

Page 4

MITSUMI

Video Amplifier MM1002

Notes :

1 Frequency response fc1, fc2, fc3

*

For the same conditions as the G

5MHz as V2, F

f

C1=20LOG dB

2 Character addition ······· input threshold voltage VTH13

*

C1 is obtained as follows. The same applies for fC2 and fC3.

V2

V1

For the same conditions as the V

TP7 pulse level when a character signal is output on TP4 is V

3 Chroma amp ······ crosstalk C

*

U1 measurement, given video output for 0.1MHz as V2, and for

CL measurement, adjust VR1 to raise pulse level gradually, and

TH13.

Given TP4 level when there is no pulse input as V3, and the level when pulse input exists as V4, C

is obtained as follows.

C=20LOG dB

4 Chroma amp ······ input threshold voltage VTH3

*

V4

V3

For the same conditions as C measurement, adjust VR2 to raise TP8 level from 0V. The TP8 level

when TP4 level changes at pulse input is V

5 Sync separation ······ sync separation level VSEPA

*

Input a 1VP

-

P staircase signal (no chroma signal) to SG-1, and gradually shrink the sync signal.

TP1 sync level when TP10 horizontal sync signal starts to disappear is V

TH3.

SEPA.

6 Sync separation ······ Pin 7 threshold voltage VTH7H, VTH7L

*

Impress external DC voltage on TP9 and raise gradually from 0V. TP9 level when TP11 level goes

from high to low is V

high is V

7 Sync separation ······· horizontal sync output voltage VOH6, VOL6

*

TH7L.

TP10 high level when a 1V

level is V

8 Sync separation ······ vertical sync output voltage VOH8, VOL8

*

OL6.

TP10 high level when a 1V

level is V

OL8.

TH7H. Lower gradually from 5V. TP9 level when TP11 level goes from low to

P

-

P staircase signal (no chroma signal) is input to SG-1 is VOH6, and low

P

-

P staircase signal (no chroma signal) is input to SG-1 is VOH8, and low

Page 5

MITSUMI

Measuring Circuit

Video Amplifier MM1002

Page 6

MITSUMI

Application Circuits

Video Amplifier MM1002

Loading...

Loading...