Page 1

May 1997

ML4823

High Frequency Power Supply Controller

GENERAL DESCRIPTION

The ML4823 High Frequency PWM Controller is an IC

controller optimized for use in Switch Mode Power

Supply designs running at frequencies to 1MHz.

Propagation delays are minimal through the comparators

and logic for reliable high frequency operation while slew

rate and bandwidth are maximized on the error amplifier.

This controller is designed for single-ended applications

using voltage or current mode and provides for input

voltage feed forward.

A 1V threshold current limit comparator provides cycleby-cycle current limit and exceeding a 1.4V threshold

initiates a soft-start cycle. The soft start pin doubles as a

maximum duty cycle clamp. All logic is fully latched to

provide jitter-free operation and prevent multiple pulsing.

An under-voltage lockout circuit with 800mV of hysteresis

assures low startup current and drives the outputs low

during fault conditions.

FEATURES

■ Practical operation at switching frequencies to 1.0MHz

■ High current (2A peak) totem pole output

■ Wide bandwidth error amplifier

■ Fully latched logic with double pulse suppression

■ Pulse-by-pulse current limiting

■ Soft start and max. duty cycle control

■ Under voltage lockout with hysteresis

■ 5.1V trimmed bandgap reference

■ Low start-up current (1.1mA)

■ Pin compatible improved replacement for UC3823

■ Fast shut down path from current limit to output

■ Soft start latch ensures full soft start cycle

■ Outputs pull low for undervoltage lockout

This controller is an improved second source for the

UC3823 controller; however, the ML4823 includes

features not found on the 3823. These features are set in

italics.

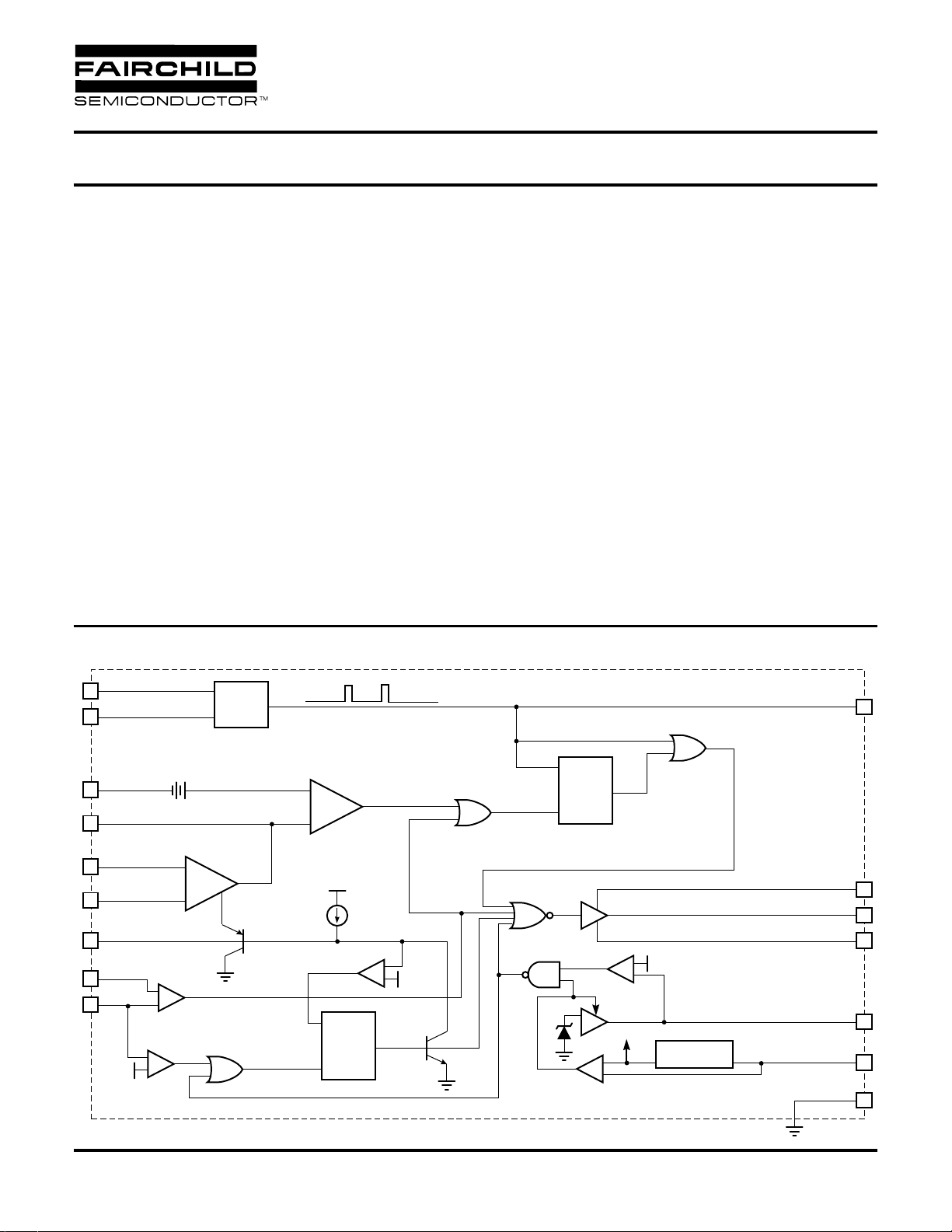

BLOCK DIAGRAM (Pin Configuration Shown for 16-Pin Version)

R

5

C

6

RAMP

7

E/A OUT

3

NI

2

INV

1

SOFT START

8

I

LIM

11

I

LIM

9

1.4V

T

+

+

ERROR

AMP

–

OSC

+

COMP

–

R

S

V+

R

Q

S

–

–

+

1V

5.1V

Q

UNDER

VOLTAGE

LOCKOUT

–

+

+

ENABLE

V

REF

V

REF

9V

4V

GEN

INTERNAL

BIAS

T

1.25V

REF

–

/S.D.

+

+

–

CLOCK OUT

POWER V

OUTPUT

POWER GND

5.1V V

REF

V

CC

SIGNAL GND

4

C

13

14

12

16

15

10

REV. 1.0 10/12/2000

Page 2

ML4823

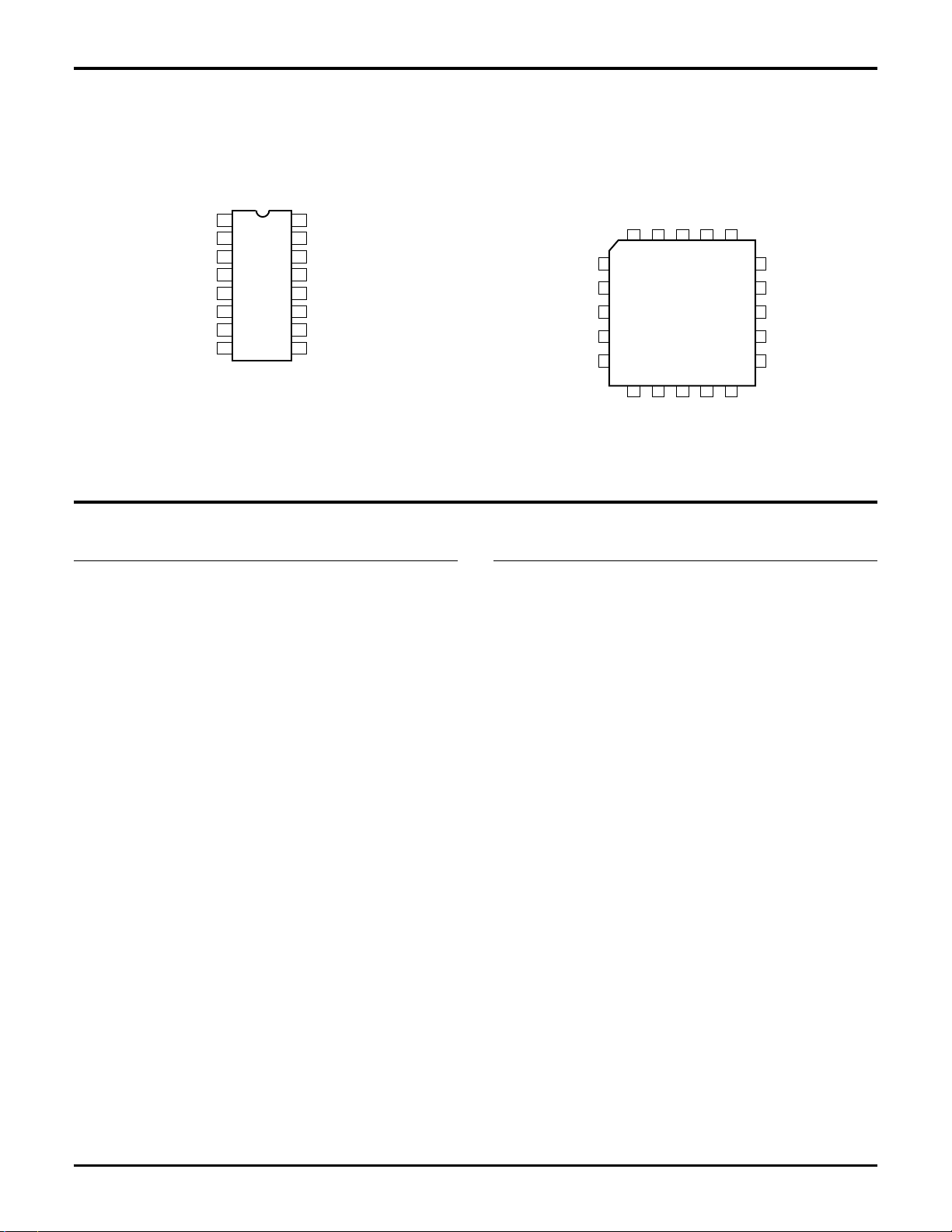

PIN CONFIGURATION

ML4823

16-PIN DIP (P16)

ML4823

20-PIN PLCC (Q20)

16-PIN SOIC (S16W)

INV

E/A OUT

CLOCK

RAMP

1

NI

2

3

4

R

5

T

C

6

T

7

SS

8

TOP VIEW

5.1V REF

16

V

15

CC

OUTPUT

14

V

13

C

PWR GND

12

I

LIM

GND

I

LIM

REF

/S.D.

11

10

9

E/A OUT

CLOCK

NC

C

R

T

T

NI

INV

3212019

4

5

6

7

8

910111213

SS

RAMP

TOP VIEW

PIN DESCRIPTION (Pin Numbers in Parentheses are for PLCC Version)

PIN NAME FUNCTION PIN NAME FUNCTION

1 (2) INV Inverting input to error amp.

2 (3) NI Non-inverting input to error amp.

3 (4) E/A OUT Output of error amplifier and input to

main comparator.

4 (5) CLOCK Oscillator output.

5 (7) R

T

Timing resistor for oscillator — sets

charging current for oscillator timing

capacitor (pin 6).

6 (8) C

T

Timing capacitor for oscillator.

7 (9) RAMP Non-inverting input to main

comparator. Connected to C

T

for

Voltage mode operation or to current

sense resistor for current mode.

8 (10) SS Normally connected to soft start

capacitor.

9 (12) I

10 (13) GND Analog signal ground.

11 (14) I

12 (15) PWR GND Return for the high current totem

13 (17) V

14 (18) OUT B High current totem pole output.

15 (19) V

16 (20) 5.1V REF Buffered output for the 5.1V voltage

/S.D. Current limit sense pin. Normally

LIM

connected to current sense resistor.

REF Reference input for cycle-by-cycle

LIM

current limit comparator.

pole output.

C

Positive supply for the high current

totem pole output.

CC

Positive supply for the IC.

reference.

NC

NC

CC

5.1V REF

V

/S.D.

GND

LIM

I

18

17

16

15

14

OUTPUT

V

C

NC

PWR GND

REF

I

LIM

2 REV. 1.0 10/12/2000

Page 3

ABSOLUTE MAXIMUM RATINGS

ML4823

Absolute maximum ratings are those values beyond which

the device could be permanently damaged. Absolute

maximum ratings are stress ratings only and functional

device operation is not implied.

Supply Voltage (V

, VCC) ...........................................30V

C

OUTPUT Current, Source or Sink

DC .......................................................................0.5A

Junction Temperature ............................................ 125°C

Storage Temperature Range ..................... –65°C to 150°C

Lead Temperature (Soldering 10 sec.) .................... 260°C

Thermal Resistance (θ

)

JA

Plastic DIP .......................................................80°C/W

Plastic SOIC................................................... 105°C/W

Plastic Chip Carrier (PLCC) .............................. 78°C/W

Pulse (0.5µs) ......................................................... 2.0A

Analog Inputs

(INV, NI, RAMP, SS, I

).................. GND –0.3V to 6V

LIM

CLOCK OUTPUT Current ...................................... –5mA

F/A OUT Current ......................................................5mA

SOFT START Sink Current....................................... 20mA

RT Charging Current ............................................... –5mA

OPERATING CONDITIONS

Temperature Range

ML4823C ..................................................0°C to 70°C

ML4823I................................................ –40°C to 85°C

ELECTRICAL CHARACTERISTICS

Unless otherwise specified, R

PARAMETER CONDITIONS MIN TYP MAX UNITS

OSCILLATOR

Initial Accuracy TJ = 25°C, 360 400 440 kHz

Voltage Stability 10V ≤ VCC ≤ 30V, 0.2 2 %

Temperature Stability 5%

Total Variation Line, temp. 340 460 kHz

Clock Out High 3.9 4.5 V

Clock Out Low 2.3 2.9 V

Ramp Peak 2.6 2.8 3.0 V

Ramp Valley 0.7 1.0 1.25 V

Ramp Valley to Peak 1.6 1.8 2.0 V

REFERENCE

Output Voltage TJ = 25°C, IO = 1mA 5.025 5.10 5.175 V

Line Regulation 10V ≤ VCC ≤ 30V 2 20 mV

Load Regulation 1mA ≤ IO ≤ 10mA 5 20 mV

Temperature Stability –40°C ≤ TJ ≤ 150°C, 0.2 0.4 %

Total Variation Line, load, temp. 4.975 5.225 V

Output Noise Voltage 10Hz to 10kHz 50 µV

Long Term Stability TJ = 125°C, 1000 hrs, 5 25 mV

Short Circuit Current V

ERROR AMPLIFIER

Input Offset Voltage ±30 mV

Input Bias Current 0.6 3 µA

Input Offset Current 0.1 1 µA

Open Loop Gain 1 ≤ VO ≤ 4V 50 95 dB

= 3.65kΩ, C

T

= 1000pF, TA = Operating Temperature Range, VCC = 15V. (Note 1)

T

= 0V –15 –50 –100 mA

REF

REV. 1.0 10/12/2000 3

Page 4

ML4823

ELECTRICAL CHARACTERISTICS (Continued)

PARAMETER CONDITIONS MIN TYP MAX UNITS

ERROR AMPLIFIER (Continued)

CMRR 1.5 ≤ VCC ≤ 5.5V 50 80 dB

PSRR 10 ≤ VCC ≤ 30V 70 100 dB

Output Sink Current V

Output Source Current V

Output High Voltage I

Output Low Voltage I

E/A OUT

E/A OUT

Unity Gain Bandwidth 3 5.5 MHz

Slew Rate 6 12 V/µs

PWM COMPARATOR

RAMP Bias Current V

Duty Cycle Range 0 80 %

E/A OUT Zero DC Threshold V

Delay to Output 50 80 ns

SOFT START

Charge Current V

Discharge Current V

CURRENT LIMIT/SHUTDOWN

I

Bias Current 0V ≤ I

LIM

Current Limit Offset I

I

REF Common Mode Range 1.0 1.25 V

LIM

LIM

Shutdown Threshold 1.25 1.40 1.55 V

Delay to Output 50 80 ns

OUTPUT

Output Low Level I

Output High Level I

OUT

I

OUT

OUT

I

OUT

Collector Leakage VC = 30V 100 500 µA

Rise/Fall Time CL = 1000pF 30 60 ns

UNDER VOLTAGE LOCKOUT

Start Threshold 8.8 9.2 9.7 V

UVLO Hysteresis 0.4 0.8 1.2 V

SUPPLY

Start Up Current VCC = 8V 1.1 2.5 mA

I

CC

INV, RANP, I

NI = 1V

= 1V 1 2.5 mA

E/A OUT

= 4V –0.5 –1.3 mA

E/A OUT

= –0.5mA 4.0 4.7 5.0 V

= 1mA 0 0.5 1.0 V

= 0V –1 –5 µA

RAMP

= 0V 1.1 1.25 V

RAMP

SOFT START

SOFT START

= 0.5V 3 9 20 µA

= 1V 1 mA

≤ 4V ±10 µA

LIM

REF = 1.1V 0 15 mV

= 20mA 0.25 0.40 V

= 200mA 1.2 2.2 V

= –20mA 12.8 13.5 V

= –200mA 12.0 13.0 V

= 0V 22 33 mA

LIM

Note 1: Limits are guaranteed by 100% testing, sampling, or correlation with worst-case test conditions.

4 REV. 1.0 10/12/2000

Page 5

FUNCTIONAL DESCRIPTION

160

140

120

100

80

10k 100k 1M

FREQ (Hz)

T

D

(ns)

1.0nF

470pF

OSCILLATOR

The ML4823 oscillator charges the external capacitor (C

with a current (I

voltage reaches the upper threshold (Ramp Peak), the

comparator changes state and the capacitor discharges to

the lower threshold (Ramp Valley) through Q1. While the

capacitor is discharging, Q2 provides a high pulse.

I

SET

R

T

SET

R

T

3V

C

T

I

Q1

) equal to 3/R

Q1

. When the capacitor

SET

5.1V

I

SET

+

–

400µA

Q

2

CLOCK

OUT

ML4823

)

T

The oscillator period can be described by the following

relationship:

T

where: T

and: T

= T

OSC

= C (Ramp Valley to Peak)/I

RAMP

DEADTIME

+ T

RAMP

DEADTIME

= C (Ramp Valley to Peak)/I

SET

Q1

CLOCK OUT

RAMP PEAK

C

T

RAMP VALLEY

Figure 1. Oscillator Block Diagram

100k

100nF

47nF

22nF

10k

RT (OHMS)

Figure 2. Oscillator Timing Resistance vs Frequency

REV. 1.0 10/12/2000 5

1k

0.1k

10nF

4.7nF

1k 10k

FREQ (Hz)

2.2nF

1nF

100k

T

D

470pF

1M 10M

Figure 3. Oscillator Deadtime vs Frequency

30

25

20

(µs)

15

D

T

10

5

0

0.47 1.0 2.2 4.7 10.0 22

(nF)

C

T

Figure 4. Oscillator Deadtime vs C

47 100

(3ký - RT - 100ký)

T

Page 6

ML4823

ERROR AMPLIFIER

The ML4823 error amplifier is a 5.5MHz bandwidth 12V/µs

slew rate op-amp with provision for limiting the positive

output voltage swing (Output Inhibit line) for ease in

implementing the soft start function.

5

100

80

60

GAIN

40

4

V

IN

3

(V)

2

1

0 0.2 0.4 0.6 0.8 1.0

V

OUT

TIME (µs)

Figure 5. Unity Gain Slew Rate

OUTPUT DRIVER STAGE

The ML4823 Output Driver is a 2A peak output high speed

totem pole circuit designed to quickly switch the gates of

capacitive loads, such as power MOSFET transistors.

V

CC

POWER

V

C

Q2

OUT

20

0

–20

100 1K 10K 100K 1M 10M

φ

100M

FREQ (Hz)

Figure 6. Open Loop Frequency Response

15

(V)

OUT

10

T

0

0

–90

–180

0.2

I

0

–0.2

(A)

L

Q1

Figure 7. Simplified Schematic

3

2

(V)

SAT

V

1

0

0 0.5 1.0 1.5

SOURCE

SINK

I

OUT

(A)

Figure 8. Saturation Curves

POWER

GND

5

0

0 40 80 120 160 200

TIME (ns)

Figure 9. Rise/Fall Time (CL = 1000pF)

15

(V)

OUT

10

T

5

0

0 100 200 300 400 500

TIME (ns)

Figure 10 Rise/Fall Time (CL = 10,000pF)

2

(A)

I

L

0

–2

6 REV. 1.0 10/12/2000

Page 7

SOFT START AND CURRENT LIMIT

The ML4823 employs two current limits. When the

voltage at I

REF, the outputs are immediately shut off and the cycle is

terminated for the remainder of the oscillator period by

resetting the RS flip flop.

If the output current is rising quickly (usually due to

transformer saturation) such that the voltage on pin 9

reaches 1.4V before the outputs have turned off, a soft

start cycle is initiated. The soft start capacitor is discharged

and outputs are held “off” until the voltage at SS reaches

1V, ensuring a complete soft start cycle. The duty cycle on

start up is limited by limiting the output voltage of the

error amplifier voltage to the voltage at the SS pin.

/SD exceeds the I

LIM

REF threshold on I

LIM

LIM

ML4823

REV. 1.0 10/12/2000 7

Page 8

ML4823

PHYSICAL DIMENSIONS inches (millimeters)

Package: P16

16-Pin PDIP

0.740 - 0.760

(18.79 - 19.31)

16

0.02 MIN

(0.50 MIN)

(4 PLACES)

0.170 MAX

(4.32 MAX)

0.125 MIN

(3.18 MIN)

PIN 1 ID

1

0.055 - 0.065

(1.40 - 1.65)

0.016 - 0.022

(0.40 - 0.56)

0.385 - 0.395

(9.78 - 10.03)

0.350 - 0.356

(8.89 - 9.04)

1

0.100 BSC

(2.54 BSC)

SEATING PLANE

Package: Q20

20-Pin PLCC

0.240 - 0.260

(6.09 - 6.61)

0.015 MIN

(0.38 MIN)

0.295 - 0.325

(7.49 - 8.26)

0º - 15º

0.042 - 0.056

(1.07 - 1.42)

0.008 - 0.012

(0.20 - 0.31)

0.025 - 0.045

(0.63 - 1.14)

(RADIUS)

0.042 - 0.048

(1.07 - 1.22)

PIN 1 ID

6

0.050 BSC

(1.27 BSC)

0.026 - 0.032

(0.66 - 0.81)

0.013 - 0.021

(0.33 - 0.53)

11

SEATING PLANE

0.350 - 0.356

16

(8.89 - 9.04)

0.165 - 0.180

(4.19 - 4.57)

0.385 - 0.395

(9.78 - 10.03)

0.146 - 0.156

(3.71 - 3.96)

0.200 BSC

(5.08 BSC)

0.009 - 0.011

(0.23 - 0.28)

0.100 - 0.110

(2.54 - 2.79)

0.290 - 0.330

(7.36 - 8.38)

8 REV. 1.0 10/12/2000

Page 9

PHYSICAL DIMENSIONS inches (millimeters)

Package: S16W

16-Pin Wide SOIC

0.400 - 0.414

16

(10.16 - 10.52)

ML4823

PIN 1 ID

0.024 - 0.034

(0.61 - 0.86)

(4 PLACES)

0.090 - 0.094

(2.28 - 2.39)

1

0.050 BSC

(1.27 BSC)

0.012 - 0.020

(0.30 - 0.51)

ORDERING INFORMATION

PART NUMBER TEMPERATURE RANGE PACKAGE

ML4823CP 0°C to 70°C 16-Pin PDIP (P16)

ML4823CQ 0°C to 70°C 20-Pin PLCC (Q20)

ML4823CS 0°C to 70°C 20-Pin Wide SOIC (S16W)

ML4823IQ –40°C to 85°C 16-Pin PDIP (P16)

ML4823IS –40°C to 85°C 20-Pin PLCC (Q20)

ML4823MJ –40°C to 85°C 16-Pin Wide SOIC (S16W)

0.291 - 0.301

(7.39 - 7.65)

0.095 - 0.107

(2.41 - 2.72)

SEATING PLANE

0.398 - 0.412

(10.11 - 10.47)

0.005 - 0.013

(0.13 - 0.33)

0º - 8º

0.022 - 0.042

(0.56 - 1.07)

0.009 - 0.013

(0.22 - 0.33)

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO

ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME

ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN;

NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES

OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR

CORPORATION. As used herein:

1. Life suppor t devices or systems are devices or systems

which, (a) are intended for surgical implant into the body,

or (b) support or sustain life, and (c) whose failure to

perform when properly used in accordance with

2. A critical component in any component of a life support

device or system whose failure to perform can be

reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

instructions for use provided in the labeling, can be

reasonably expected to result in a significant injury of the

user.

www.fairchildsemi.com © 2000 Fairchild Semiconductor Corporation

REV. 1.0 10/12/2000 9

Loading...

Loading...