Page 1

MK3233

ICRO

C

LOCK

Description

The MK3233 is the smallest size, lowest power system

clock synthesizer available. It is the ideal way to

generate clocks for smart cell phones, PDAs, and other

devices where low power is required. Using analog

Phase-Locked Loop (PLL) techniques, the device

operates from a single 32.768 kHz crystal to produce

the 32.768 kHz, CPU, and serial communications

output clocks.

The device has multiple power down modes for the

CPU, communications, and 32.768 kHz clocks.

The MK3233 can save board space and cost even if it

only replaces the 32 kHz oscillator circuitry and one

additional surface mount crystal or oscillator. The

extremely low IDD, the ease of surface mounting, the

upgradeability of CPU frequencies, and the power

down capability are added benefits in using the part.

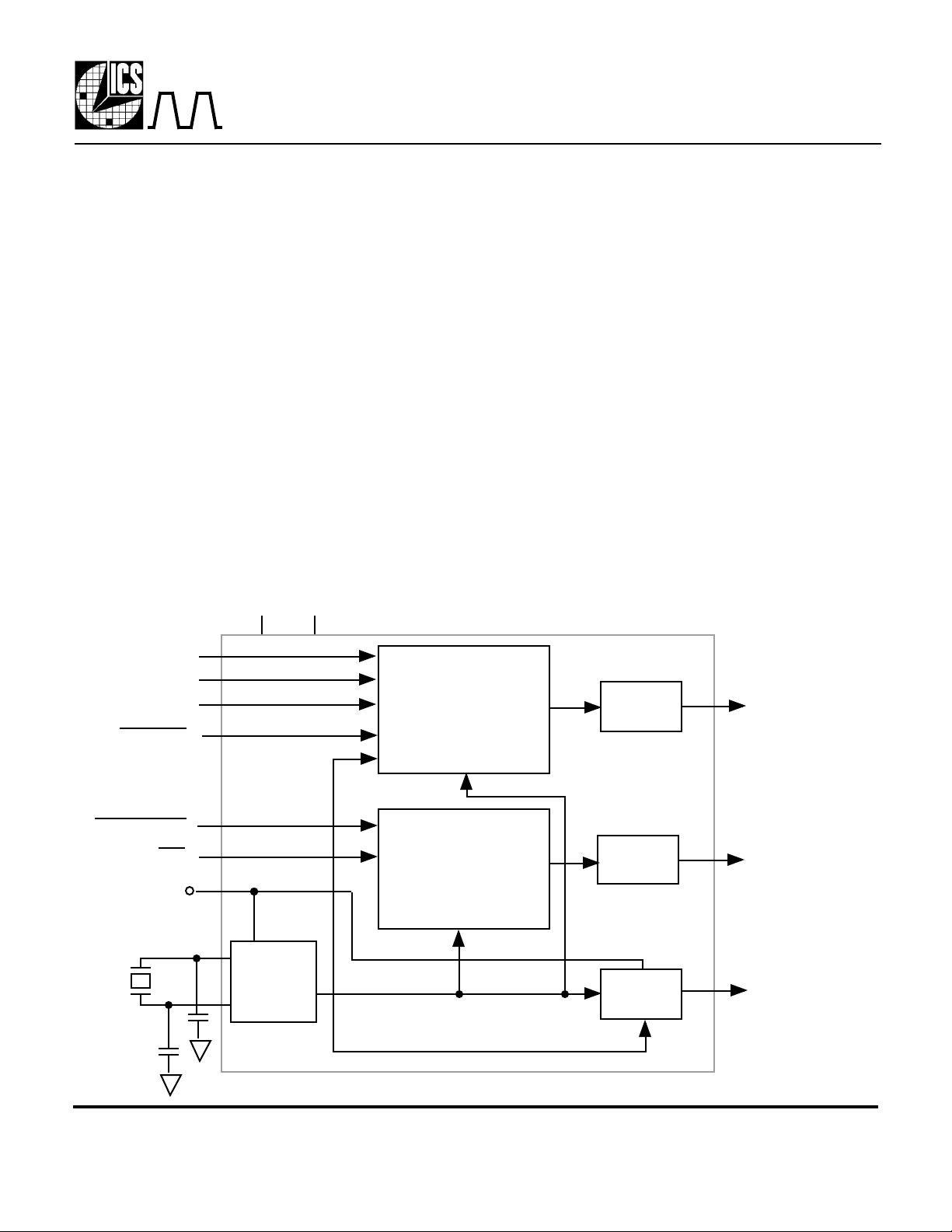

Block Diagram

VDD GND

Handheld System Clock Synthesizer

Features

• Input crystal frequency of 32.768 kHz

• Lowest power solution available

• Operating temperature of -20 to 70 °C

• Output clock frequencies up to 50 MHz

• Three output clocks

• 3.3 V or 5.0 V operation

• Duty cycle of 45/55

• Eight selectable CPU frequencies

• CPU or Communication clock power down

• Separate battery supply pin for 32 kHz runs to 2V

• IDD less than 4µA when 32 kHz running

• Serial port clocks of 1.8432 MHz (-01 version) or

3.6864 MHz (-02 version)

• Packaged in 16 pin narrow SOIC

CPUS0

CPUS1

CPUS2

PDCPU

PDCOMM

VDD32

32.768 kHz

crystal

or

clock

X1

X2

PD

Crystal

Oscillator

CPU

Clock Synthesis

and Control

Circuitry

Communications

Clock Synthesis

and Control

Circuitry

Output

Buffer

Output

Buffer

Output

Buffer

CPUCLK

1.843 or

3.686 MHz

32.768 kHz

MDS 3233 F 1 Revision 11070 Printed 11/16/00

Integrated Circuit Systems, Inc.• 525 Race Street• San Jose • CA • 95126• (408) 295-9800 tel • www.icst.com

Page 2

MK3233

Handheld System Clock Synthesizer

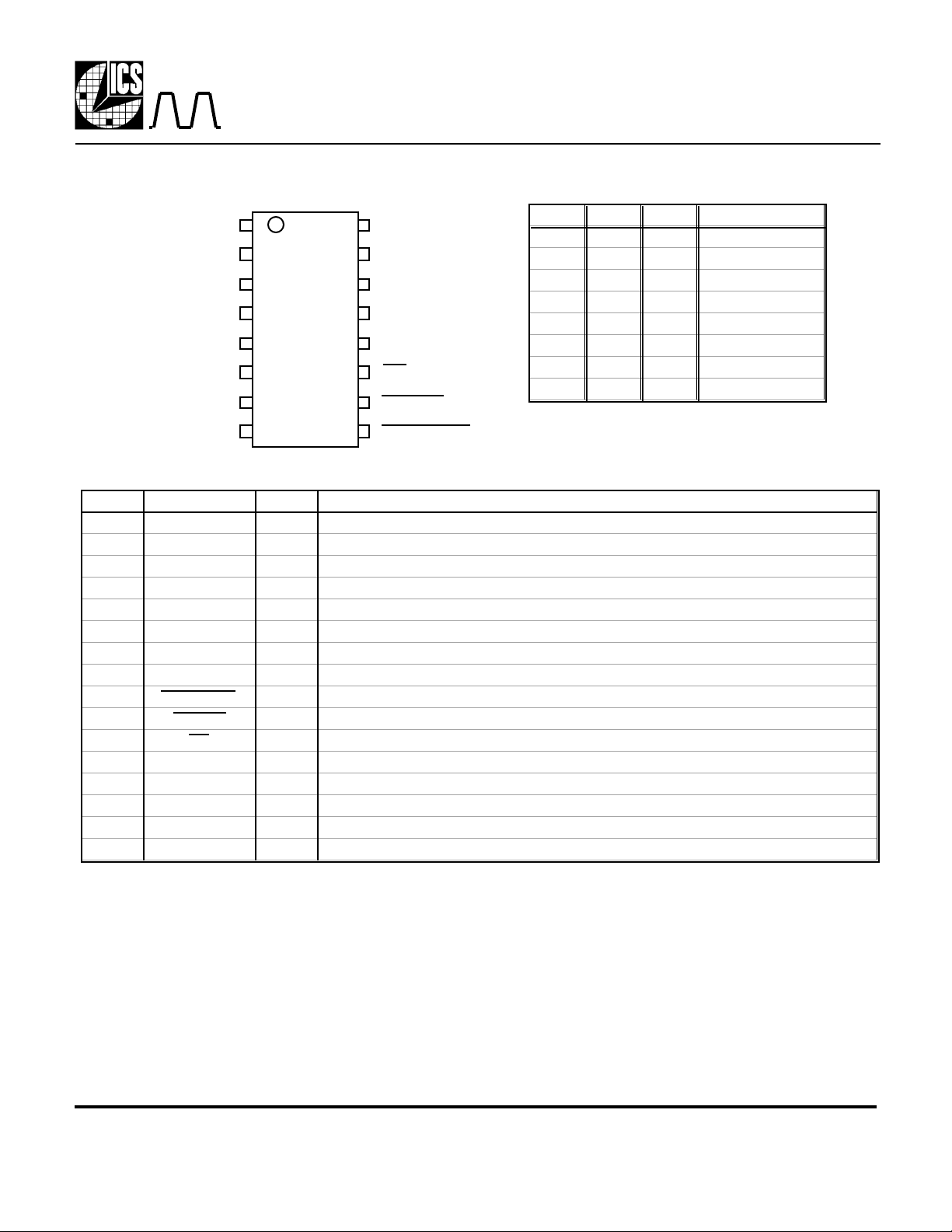

CPU Clock Decoding

CPUS2 CPUS1 CPUS0 CPUCLK (MHz)

0 0 0 8.00

0 0 1 13.00

0 1 0 16.00

0 1 1 20.00

1 0 0 40.00

1 0 1 25.00

1 1 0 50.00

1 1 1 33.33

Pin Assignment

CPUS2

VDD32

VDD

GND

COMMCLK

ICRO

X2

X1

C

LOCK

1

2

3

4

5

6

16

15

14

13

12

11

7 10

CPUS1

CPUS0

CPUCLK

VDD

GND

PD

PDCPU

Frequency transitions will occur smoothly.

32K

8 9

PDCOMM

Pin Descriptions

Number Name Type Description

1 CPUS2 I Select 2 for CPUCLK frequencies. See Table above.

2 X2 O Crystal connection. Connect to 32.768 kHz crystal.

3 X1 I Crystal connection. Connect to 32.768 kHz crystal.

4 VDD32 P Separate power supply connection for 32.768 kHz clock. Will operate to 2.0 V.

5 VDD P Connect to +3.3 V or +5 V. Must be the same voltage as pin 13.

6 GND P Connect to ground.

7 COMMCLK O Serial communications (1.84 on -01 version, or 3.68MHz on -02 version) clock output.

8 32K O 32.768 kHz square wave clock output.

9 PDCOMM I Power Down serial Communications clock output (stops low) when low.

10 PDCPU I Power Down CPU clock output (stops low) when low.

11 PD I Powers Down everything but 32 kHz oscillator internally. 32 kHz output buffer is off.

12 GND P Connect to ground.

13 VDD P Connect to +3.3 V or +5 V. Must be the same voltage as pin 5.

14 CPUCLK O CPUCLK output. See Table above.

15 CPUS0 I Select 0 for CPUCLK frequencies. See Table above.

16 CPUS1 I Select 1 for CPUCLK frequencies. See Table above.

Type: I = Input, O = output, P = power supply connection

Power Down status: Output clocks will stop in a low state when powered down

External Components

The MK3233 requires a minimum number of external components for proper operation. Decoupling

capacitors of 0.1µF should be connected between VDD and GND, and VDD32 and GND, as close to the

MK3233 as possible. A series resistor should be used on the VDD32 supply. A series termination resistor of

33Ω may be used for each clock output, except the 32.768 kHz. For tuning the real time clock output, use

a 32.768 kHz crystal with a load capacitance of 12.5pF, and connect a 20pF±5% (NPO dielectric)

capacitor between each crystal pin and ground. The 32.768 kHz crystal must be connected as close to the

chip as possible. Consult MicroClock for a recommended external circuit schematic.

MDS 3233 F 2 Revision 11070 Printed 11/16/00

Integrated Circuit Systems, Inc.• 525 Race Street• San Jose • CA • 95126• (408) 295-9800 tel • www.icst.com

Page 3

MK3233

ABSOLUTE MAXIMUM RATINGS (note 1)

DC CHARACTERISTICS (at 5.0 V unless otherwise noted)

AC CHARACTERISTICS (at 5.0 V unless otherwise noted)

32.768kHz crystal with ESR ≤25kΩ

32.768kHz oscillator running

ICRO

C

LOCK

Handheld System Clock Synthesizer

Electrical Specifications

Parameter Conditions Minimum Typical Maximum Units

Supply Voltage, VDD Referenced to GND 7 V

Inputs and Clock Outputs Referenced to GND -0.5 VDD+0.5 V

Ambient Operating Temperature -20 70 °C

Soldering Temperature Max of 10 seconds 260 °C

Storage Temperature -65 150 °C

Operating Voltage, VDD 3.0 5.5 V

Operating Voltage, VDD32 2.0 5.5 V

Input High Voltage, VIH VDD=5 V 2.0 V

Input Low Voltage, VIL VDD=5 V 0.8 V

Output High Voltage, VOH VDD=5 V, IOH=-25mA 2.4 V

Output Low Voltage, VOL VDD=5 V, IOL=25mA 0.4 V

Input High Voltage, VIH VDD=3.3 V 1.9 V

Input Low Voltage, VIL VDD=3.3 V 0.4 V

Output High Voltage, VOH VDD=3.3 V, IOH=-8mA 2.4 V

Output Low Voltage, VOL VDD=3.3 V, IOL=8mA 0.4 V

IDD Operating Supply Current, 5 V No Load, 50MHz 11 mA

IDD32 with only 32 kHz running, 5 V No Load 3.5 µA

IDD Operating Supply Current, 3.3 V No Load, 50MHz 6.5 mA

IDD32 with only 32 kHz output running, 3.3 V No Load 2.5 µA

IDD32, only 32 kHz osc. running, 3.3 V, note 2 32kHz output off. PD=0 1 µA

Short Circuit Current, 5 V 32 kHz output ±30 mA

Short Circuit Current, 5 V CPU output ±100 mA

Input Capacitance 7 pF

Input Frequency 32.768 kHz

Output Clock Rise and Fall Time, 0.2 to 0.8VDD 2 ns

Output Clock Duty Cycle, all MHz clocks At VDD/2 45 49 to 51 55 %

32.768 kHz Clock Duty Cycle At VDD32/2 57 %

Absolute Clock Period Jitter, CPU clock 20 to 50 MHz -500 500 ps

Power up time, CPU off to 50 MHz, 32k running VDD=3.3 or 5 V 9 ms

Transition time, 8 MHz to 50 MHz VDD=3.3 or 5 V 4 ms

Transition time, 50 MHz to 8 MHz VDD=3.3 or 5 V 2.5 ms

Power on time,VDD32=0 V to all clocks stable

Power on time, all power down pins taken high

Note 1: Stresses beyond those listed under Absolute Maximum Ratings could cause permanent damage to the device. Prolonged

exposure to levels above the operating limits but below the Absolute Maximums may affect device reliability.

Note 2: When PD=0 (low) and VDD32 is greater than 2.0V, then the 32kHz oscillator will continue to run on the chip, but the

output is turned off. This allows for a quick power-up (<20ms), while the chip is only consuming approximately 1µA.

MDS 3233 F 3 Revision 11070 Printed 11/16/00

Integrated Circuit Systems, Inc.• 525 Race Street• San Jose • CA • 95126• (408) 295-9800 tel • www.icst.com

500 1000 ms

15 ms

Page 4

MK3233

Inches

Millimeters

ICRO

C

LOCK

Handheld System Clock Synthesizer

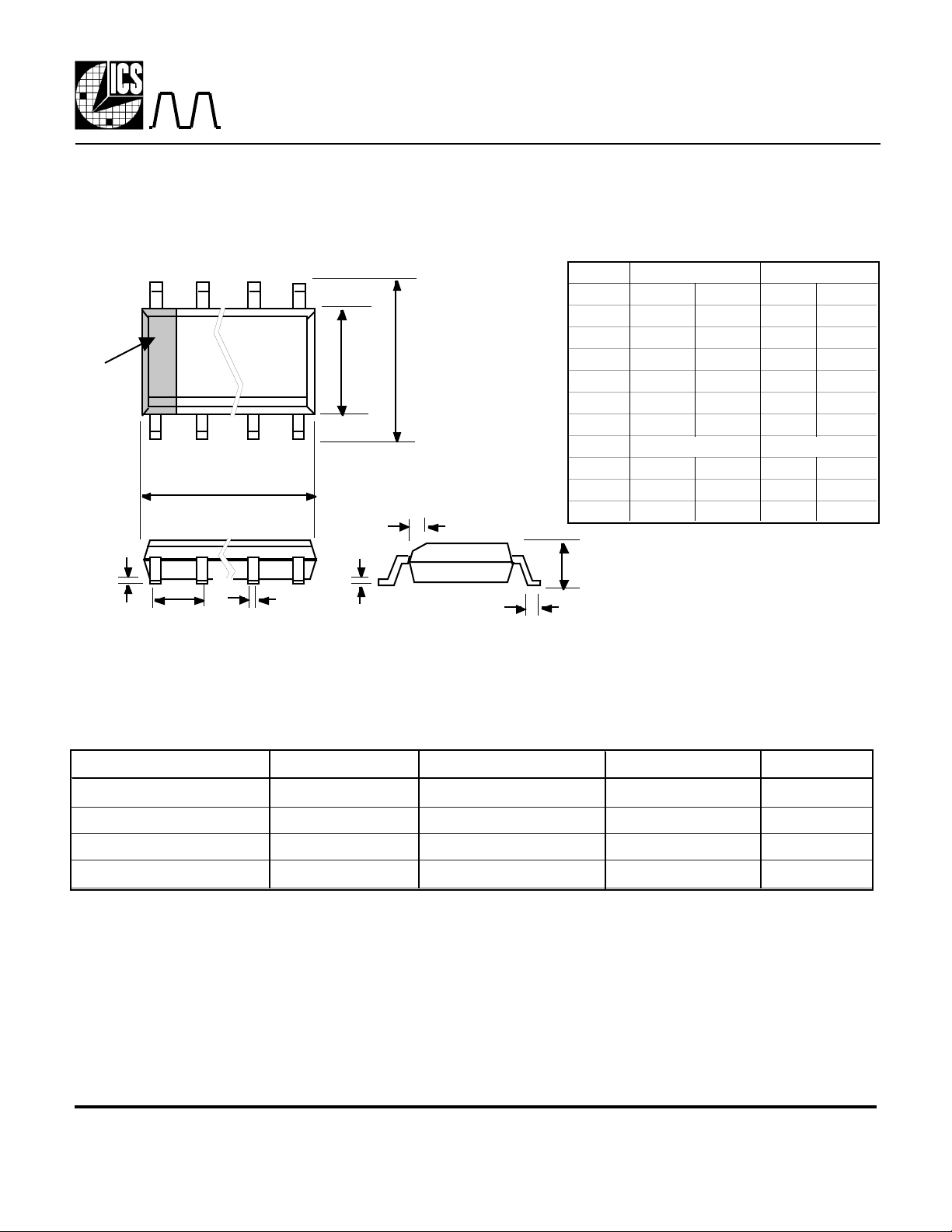

Package Outline and Package Dimensions

(For current dimensional specifications, see JEDEC Publication No. 95.)

16 pin SOIC narrow

Symbol Min Max Min Max

A 0.0532 0.0688 1.35 1.75

A1

E H

INDEX

AREA

h x 45°

D

B 0.0130 0.0200 0.33 0.51

C

D 0.3859 0.3937 9.80 10.00

E 0.1497 0.1574 3.80 4.00

e

H 0.2284 0.2440 5.80 6.20

h 0.0099 0.0195 0.25 0.50

L 0.0160 0.0500 0.41 1.27

A

A1 C

e

B

L

0.0040 0.0098 0.10 0.24

0.0075 0.0098 0.19 0.24

Ordering Information

Part/Order Number Marking Communications Clock Package Temperature

MK3233-01S MK3233-01S 1.843 MHz 16 pin SOIC -20 to 70 °C

MK3233-02S MK3233-02S 3.686 MHz 16 pin SOIC -20 to 70 °C

MK3233-01STR MK3233-01S 1.843 MHz Add Tape & Reel -20 to 70 °C

MK3233-02STR MK3233-02S 3.686 MHz Add Tape & Reel -20 to 70 °C

While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems, Incorporated (ICS) assumes no responsibility for either its

use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is

intended for use in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary

environmental requirements are not recommended without additional processing by ICS. ICS reserves the right to change any circuitry or specifications without notice. ICS does

not authorize or warrant any ICS product for use in life support devices or critical medical instruments.

MDS 3233 F 4 Revision 11070 Printed 11/16/00

Integrated Circuit Systems, Inc.• 525 Race Street• San Jose • CA • 95126• (408) 295-9800 tel • www.icst.com

Loading...

Loading...