Page 1

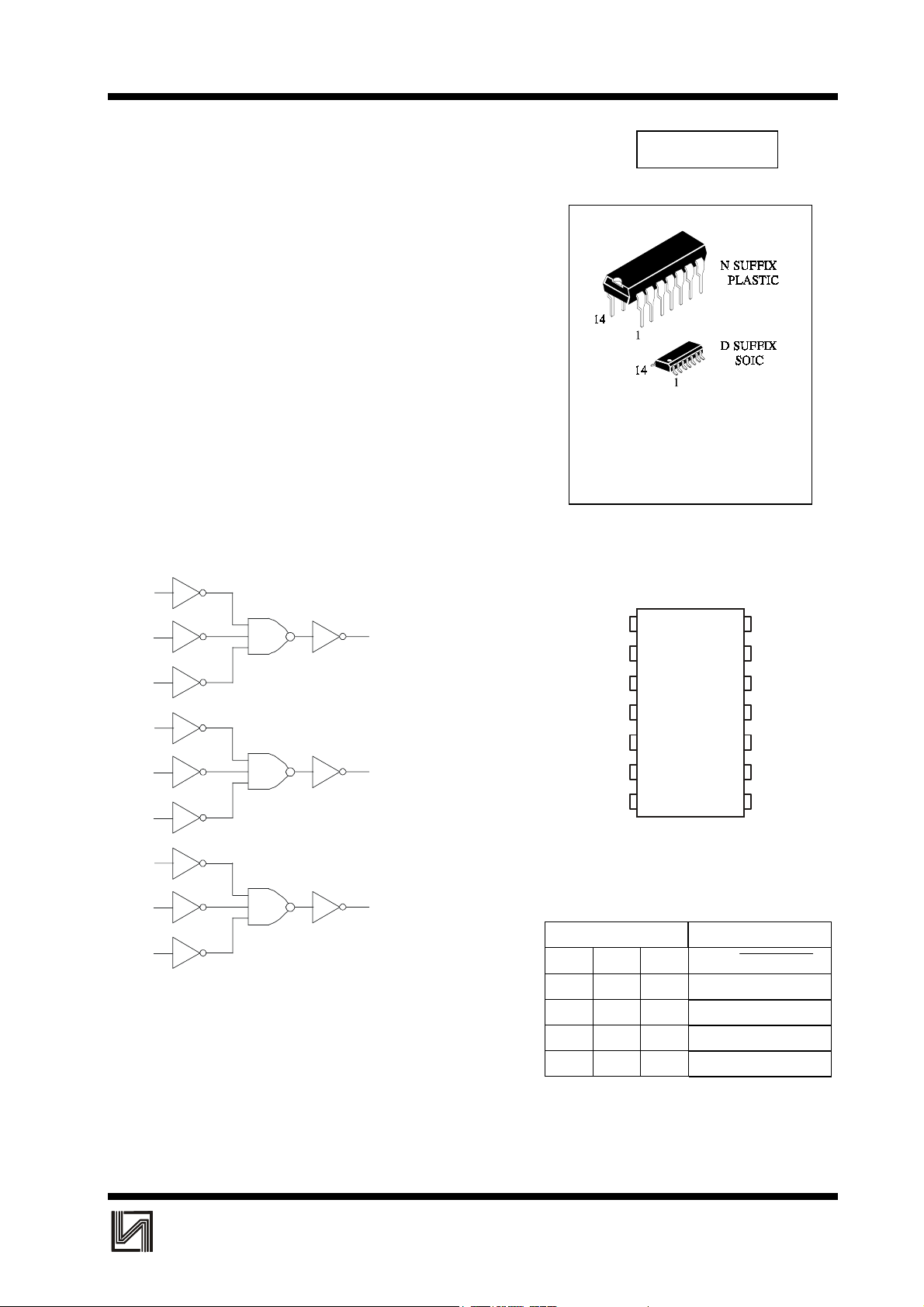

Triple 3-Input NOR Gate

The IN74HC27A is high-speed Si-gate CMOS device and are pin

compatible with low power Schottky TTL (LSTTL) . The device

provide Triple 3-input NOR function.

• Outputs Directly Interface to CMOS, NMOS, and TTL

• Operating Voltage Range: 2.0 to 6.0 V

• Low Input Current: 1.0 µA

• High Noise Immunity Characteristic of CMOS Devices

LOGIC DIAGRAM

TECHNICAL DATA

IN74HC27A

ORDERING INFORMATION

IN74HC27AN Plastic

IN74HC27AD SOIC

IZ74HC27A Chip

T

= -55° to 125° C for all packages

A

A1

B1

C1

A2

B2

C2

A3

B3

C3

PIN 14 =V

PIN 7 = GND

CC

Y1

Y2

Y3

PIN ASSIGNMENT

A1

B1

A2

B2

C2

Y2

GND

1

2

3

4

5

6

7

14

13

12

11

10

9

8

V

CC

C1

Y1

C3

B3

A3

Y3

FUNCTION TABLE

Inputs Output

ABC

LLL H

XXH L

XHX L

HXX L

CBAY ++=

INTEGRAL

X = don’t care

1

Page 2

IN74HC27A

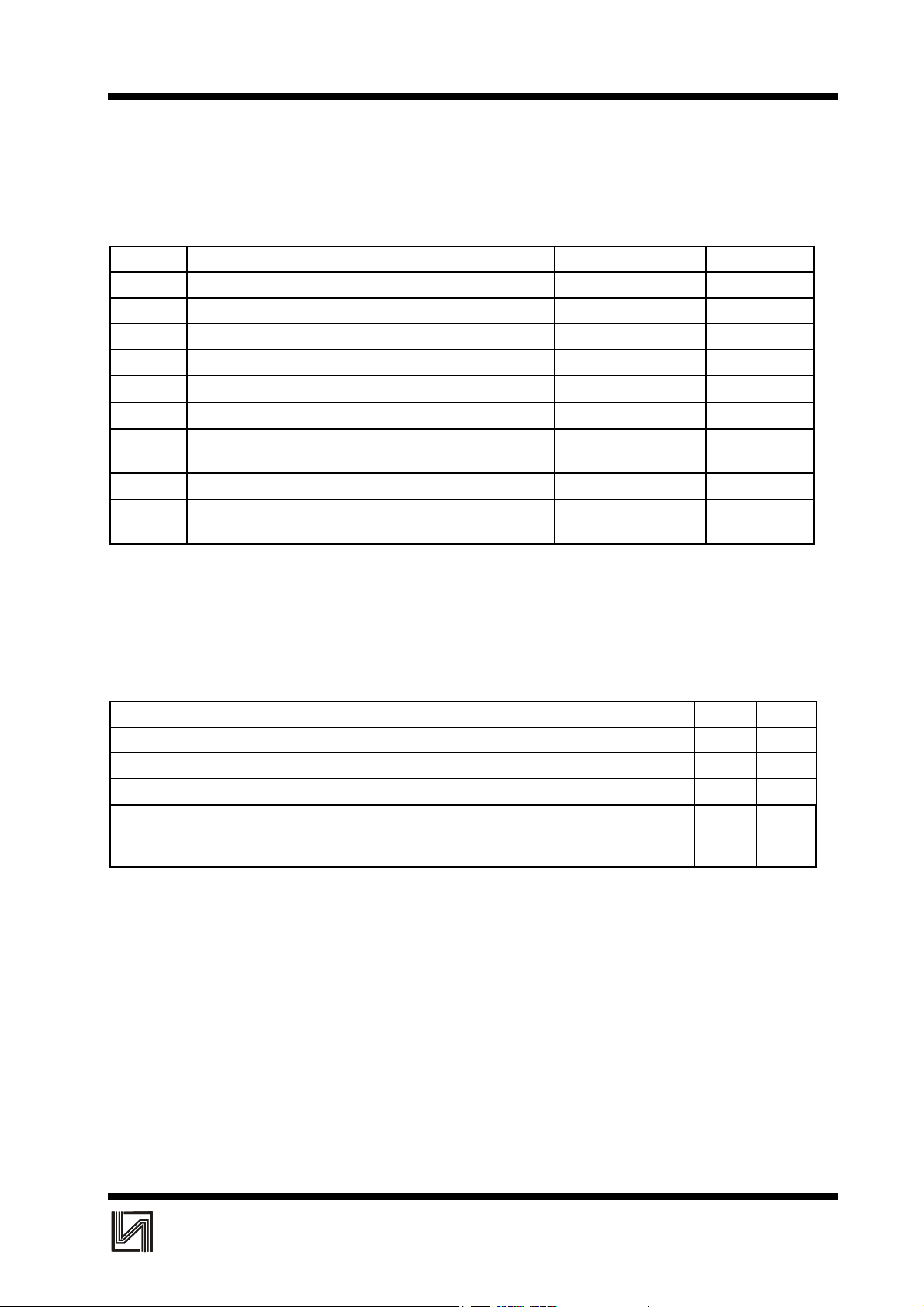

MAXIMUM RATINGS

*

Symbol Parameter Value Unit

V

CC

V

V

OUT

I

IN

I

OUT

I

CC

P

DC Supply Voltage (Referenced to GND) -0.5 to +7.0 V

DC Input Voltage (Referenced to GND) -1.5 to VCC +1.5 V

IN

DC Output Voltage (Referenced to GND) -0.5 to VCC +0.5 V

DC Input Current, per Pin

DC Output Current, per Pin

DC Supply Current, VCC and GND Pins

Power Dissipation in Still Air, Plastic DIP**

D

SOIC Package**

±20

±25

±50

750

500

Tstg Storage Temperature -65 to +150

T

Lead Temperature, 1 mm from Case for 10 Seconds

L

260

(Plastic DIP or SOIC Package)

*Maximum Ratings are those values beyond which damage to the device may occur.

Functional operation should be restricted to the Recommended Operating Conditions.

**Derating - Plastic DIP: - 10 mW/°C from 65° to 125°C

SOIC Package: : - 7 mW/°C from 65° to 125°C

mA

mA

mA

mW

°C

°C

RECOMMENDED OPERATING CONDITIONS

Symbol Parameter Min Max Unit

V

CC

VIN, V

OUT

T

A

tr, t

f

This device contains protection circuitry to guard against damage due to high static voltages or electric

fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages

to this high-impedance circuit. For proper operation, V

)≤V

V

OUT

CC

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or V

outputs must be left open.

DC Supply Voltage (Referenced to GND) 2.0 6.0 V

DC Input Voltage, Output Voltage (Referenced to GND) 0 V

Operating Temperature, All Package Types -55 +125

Input Rise and Fall Time (Figure 1) VCC =2.0 V

V

=4.5 V

CC

V

=6.0 V

CC

and V

IN

should be constrained to the range GND≤(V

OUT

0

1000

0

0

.

CC

500

400

V

°C

ns

). Unused

CC

or

IN

INTEGRAL

2

Page 3

IN74HC27A

DC ELECTRICAL CHARACTERISTICS

V

V

V

OH

V

OL

I

IL

I

IH

I

CC

Minimum High-Level

IH

Input Voltage

Maximum Low -Level

IL

Input Voltage

Minimum High-Level

Output Voltage

Maximum Low-Level

Output Voltage

Maximum Low-Level

V

≤0.1V or

OUT

≥V

V

OUT

I

OUT

V

OUT

V

OUT

I

OUT

VIN=VIH or V

I

OUT

VIN= VIH or V

I

OUT

VIN= VIH or V

I

OUT

= VIH or V

V

IN

I

OUT

VIN= VIH or V

I

OUT

VIN= VIH or V

I

OUT

VIN= VIH or V

I

OUT

= VIH or V

V

IN

I

OUT

-0.1V

CC

≤ 20 µA

≤0.1V or

≥V

-0.1V

CC

≤ 20 µA

IL

≤ - 20 µA

IL

≤ - 2.4 mA

IL

≤ - 4.0 mA

IL

≤ - 5.2 mA

IL

≤ 20 µA

IL

≤ 2.4 mA

IL

≤ 4.0 mA

IL

≤ 5.2 mA

VIN= 0 V 6.0 -0.1 -1.0 -1.0

Input Leakage Current

Maximum High-Level

VIN= V

CC

Input Leakage Current

Maximum Quiescent

Supply Current

VIN=VCC or 0 V

I

=0 µA

OUT

(per Package)

(Voltages Referenced to GND)

V

CC

V

Guaranteed LimitSymbol Parameter Test Conditions

25 °C

to

-55°C

2.0

3.0

4.5

6.0

2.0

3.0

4.5

6.0

2.0

4.5

6.0

1.5

2.1

3.15

4.2

0.5

0.9

1.35

1.8

1.9

4.4

5.9

3.0 2.48 2.34 2.20

4.5 3.98 3.84 3.70

6.0 5.48 5.34 5.20

2.0

4.5

6.0

0.1

0.1

0.1

3.0 0.26 0.33 0.4

4.5 0.26 0.33 0.4

6.0

0.26 0.33 0.4

6.0 0.1 1.0 1.0

6.0 2.0 20 40

≤85°C≤125

°C

1.5

2.1

3.15

4.2

0.5

0.9

1.35

1.8

1.9

4.4

5.9

0.1

0.1

0.1

1.5

2.1

3.15

4.2

0.5

0.9

1.35

1.8

1.9

4.4

5.9

0.1

0.1

0.1

Unit

V

V

V

V

µA

µA

µA

INTEGRAL

3

Page 4

IN74HC27A

AC ELECTRICAL CHARACTERISTICS

(CL=50pF,Input tr=tf=6.0 ns)

Symbol Parameter V

t

t

THL

PHL

, t

, t

Maximum Propagation Delay (Figure 1) 2.0

PLH

Maximum Output Transition Time

TLH

(Figure 1)

C

IN

Maximum Input Capacitance 6.0 10 10 10 pF

Power Dissipation Capacitance (Per Gate)

C

PD

Used to determine the no-load dynamic power

consumption:

P

D=CPDVCC

2

f+ICCV

Input

Output

CC

0.9

t

f

V

2

0.1 0.1

t

PLH

2

0.1

0.9

t

TLH

V

V

t

4.5

6.0

2.0

4.5

6.0

r

0.9

CC

V

Guaranteed Limit

25 °C

≤85°C ≤125°C

Unit

to

-55°C

90

18

15

75

15

13

T

=25°C,V

A

115

23

20

95

19

16

=5.0 V

CC

135

27

23

110

22

19

ns

ns

54 pF

V

1

0.9

2

t

PHL

t

THL

GND

V

CC

V

2

0.1

0 V

PULSE

GENERATOR

INTEGRAL

V = V

1 CC

V = 0.5 V

2 CC

V

I

Figure 1. Switching Waveforms

V

CC

V

DEVICE

UNDER

R

TEST

T

O

C

50 pF

L

Termination resistance RT – should

be equal to Z

of pulse generators

OUT

Figure 2. Test Circuit

4

Page 5

CHIP PAD DIAGRAM IZ74HC27A

Chip marking

74HC27

(x=0.114; y=1.104

IN74HC27A

)

12

1011

13

±

1.32 0.03

14

01

02

Pad size 0.108 x 0.108 mm (Pad size is given as per passivation layer)

Thickness of chip 0.46 ± 0,02 mm

03

1.27 0.03

PAD LOCATION

04

±

09

08

07

06

05

Pad No Symbol X Y

01 А1 0.129 0.442

02 B1 0.132 0.124

03 А2 0.433 0.133

04 B2 0.751 0.133

05 C2 1.017 0.148

06

07 GND 1.047 0.561

08 А3 1.047 0.828

09 B3 1.017 1.073

10 C3 0.751 1.088

11

12 H 0.262 1.095

13 C1 0.128 0.838

14 Vcc 0.129 0.606

2Y

1Y

1.047 0.392

0.433 1.088

INTEGRAL

5

Loading...

Loading...