Page 1

Features

•

Operating voltage 2.7V~5.5V

•

Low power consumption

–

Operation: 25mA max. (VCC=5V)

10mA max. (V

–

Standby: 30µA max. (VCC=5V)

10

•

Access time:150ns max. (VCC=5V)

µA max. (V

250ns max. (V

CC

CC

=3V)

CC

=3V)

=3V)

General Description

The HT23C020 is a read-only memory with

high performance CMOS storage device whose

2048K of memory is arranged into 262144

words by 8 bits.

For applica tion flexibility, the chip enable and

output enabl e control pins can be selected a s

active high or active low. This flexibility not

only allows easy interface with most microprocessors, but also eliminates bus contention in

HT23C020

CMOS 256K×8-Bit Mask ROM

•

262144×8 bits of mask ROM

•

Mask option s: chip enab le CE/CE/OE1/OE1,

CE1/

CE1/OE2/OE2/NC and output enable

OE/

•

•

•

•

multiple bus mi cropro cessor syste ms. An add itional feature of the HT23C020 is its ability to

enter the standb y mode wh enever the chip enable (CE/

ducing current consumption to below 30

combination of these functions make the chip

suitable for high density low power memory

applications.

OE/NC

TTL compatible inputs and outputs

Tristate outputs

Fully static operation

Package type: 32-pin DIP/SOP/PLCC

CE or CE1/CE1) is inactive, thus re-

µA. The

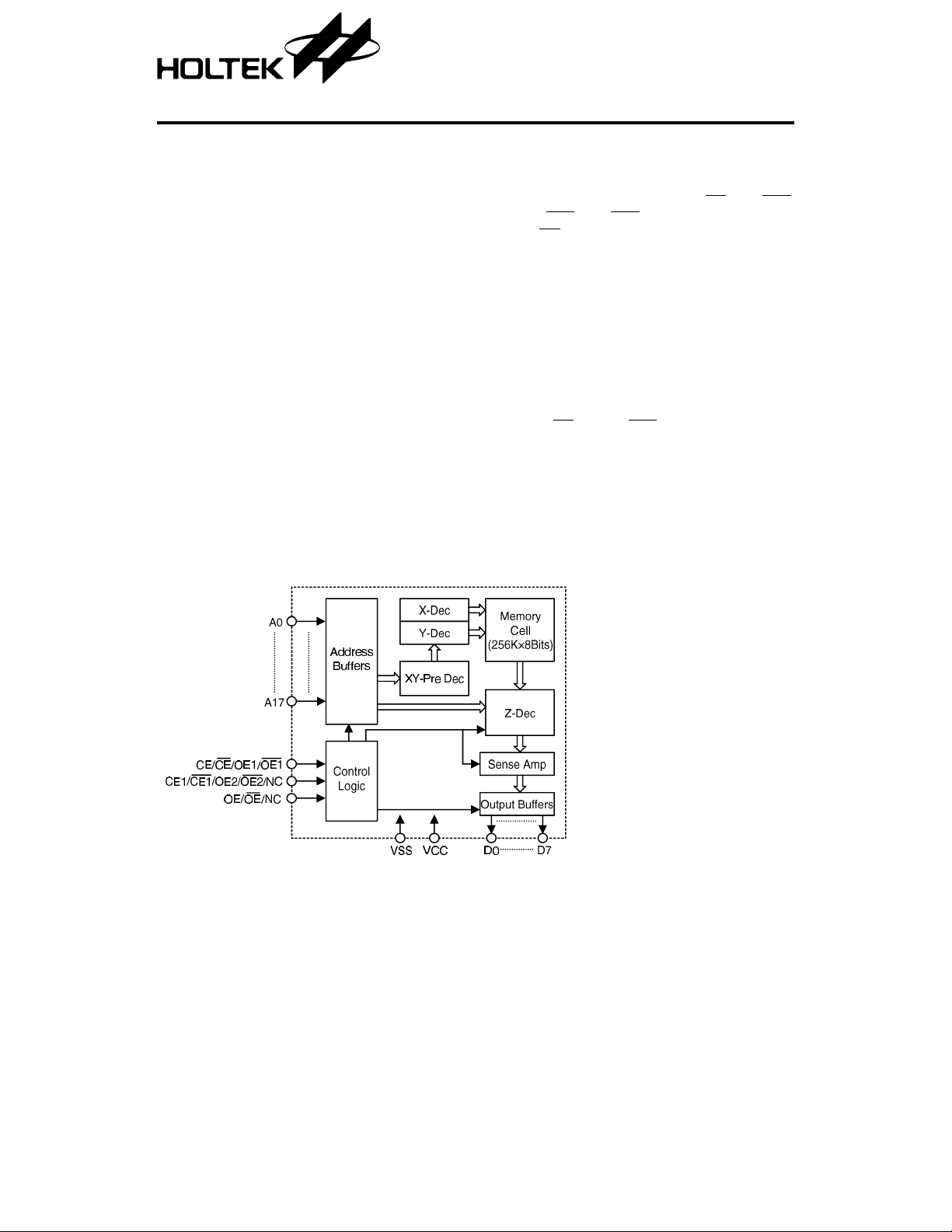

Block Diagram

1 21st Aug ’98

Page 2

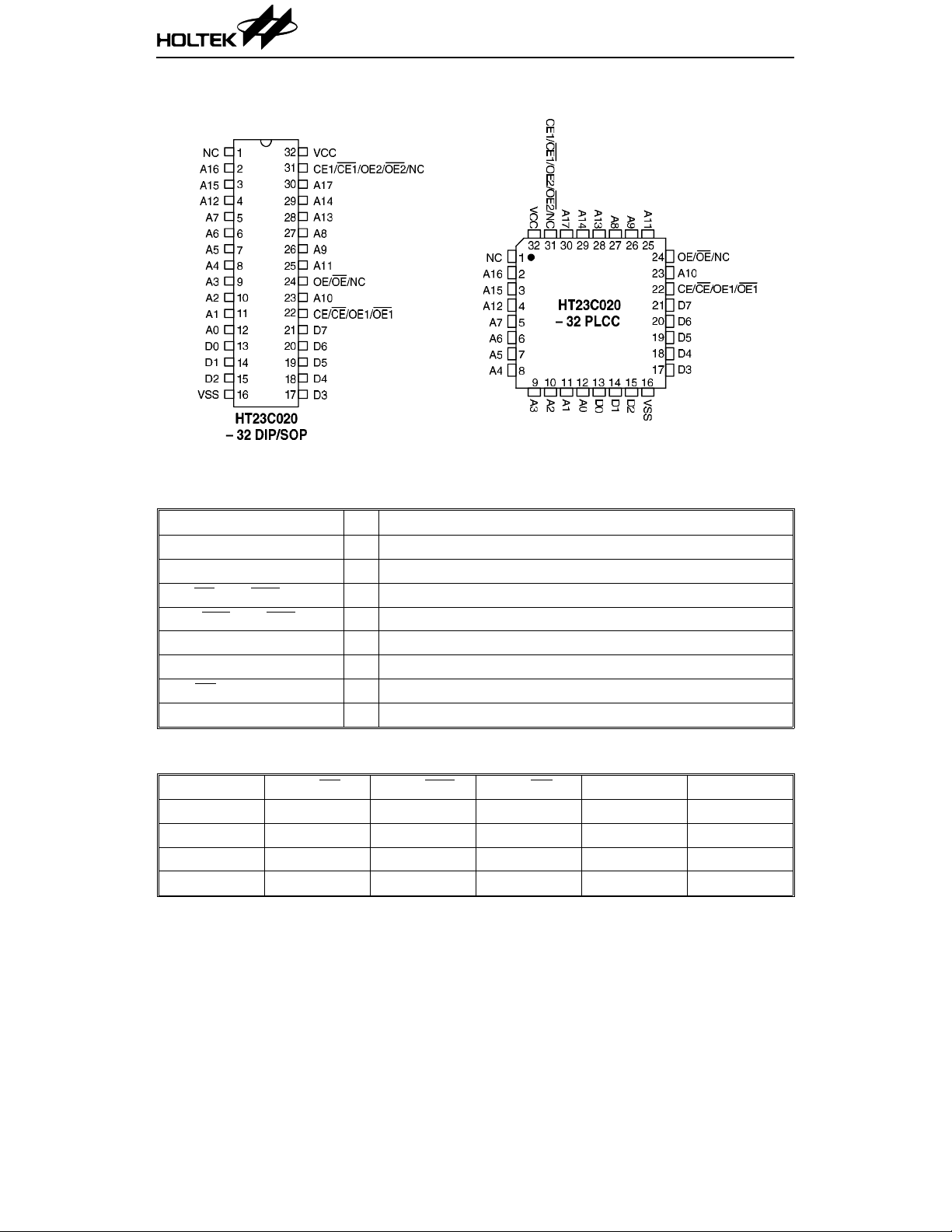

Pin Assignment

Pin Description

HT23C020

Pin Name I/O Description

A0~A17 I Address inputs

D0~D7 O Data outputs

CE/OE1/OE1 I Chip enable, output enable input

CE/

CE1/OE2/OE2/NC I Chip enable, output enable input

CE1/

VSS I Negative power supply

VCC I Positive power supply

OE/NC I Output enable input

OE/

NC — No connection

Operation Truth Table

Mode CE /CE CE1/CE1 OE/OE A0~A17 D0~D7

Read H/L H/L H/L Valid Data Out

Deselect H/L H/L L/H X High Z

Standby L/H X X X High Z

Standby X L/H X X High Z

Note: H=V

, L=VIL, X=VIH or V

IH

IL

2 21st Aug ’98

Page 3

HT23C020

Absolu te Maximum Ra tin g s*

Supply Voltage.................................–0.3V to 6V Storage Temperature.................–50°C to 125°C

Input Voltage........................–0.3V to V

*Note: These are stress ra tings on ly. Stresses exceeding the range specified under “Abso lute Maxi -

mum Ratings” ma y cause substantial damage to the device. Functional operation of this

device at other conditions beyond those listed in the specification is not implied and prolonged

exposure to extreme condition s may affect device reliability.

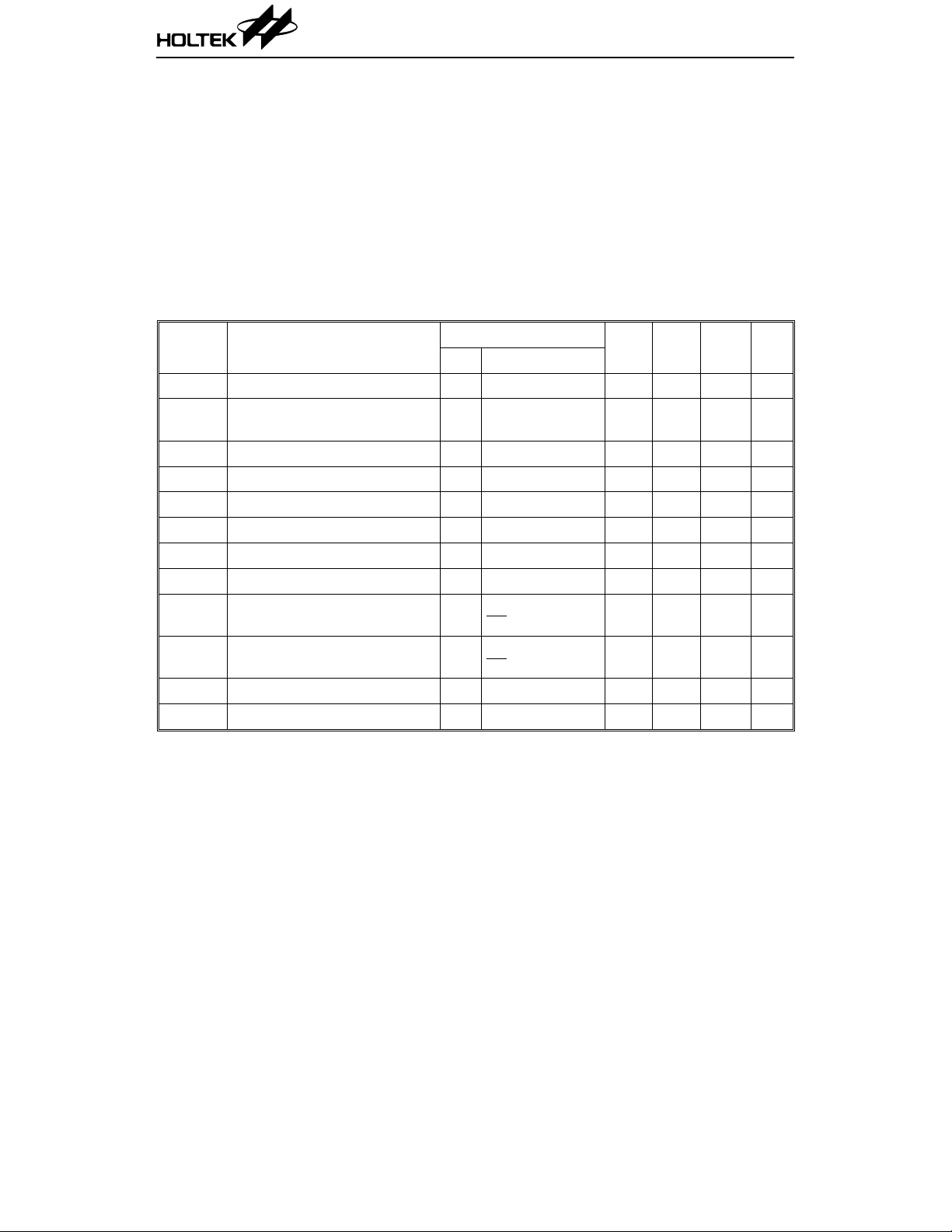

D.C. Characteristics

Supply voltage: 2.7V~3.6V Ta=–40°C to 85°C

+0.3V Operating Temperature ..............–40°C to 85°C

CC

Symbol Parameter

V

CC

I

CC

V

IL

V

IH

V

OL

V

OH

I

LI

I

LO

I

STB1

I

STB2

C

IN

C

OUT

Operating Voltage — — 2.7 — 3.6 V

Operating Current 3V

Input Low Voltage 3V — V

Input High Voltage 3V — 2.0 — V

Output Low Voltage 3V IOL= 2.1mA — — 0.4 V

Output High Voltage 3V IOH= –0.4mA 2.4 — V

Input Leakage Current 3V VIN= 0 to V

Output Leakage Current 3V V

Standby Current 3V

Standby Current 3V

Input Capacitance (See note) — f= 1MHz — — 10 pF

Output Capacitance (See note) — f = 1MHz — — 10 pF

Test Conditions

V

CC

Conditions

O/P Unload,

f= 5MHz

= 0 to V

OUT

CE=V

IL

CE=V

IH

≤0.2V

CE

CE≥VCC-0.2V

CC

CC

Note: These parameters are periodically sampled but not 100% tested.

Min. Typ. Max. Unit

——10mA

— 0.4 V

SS

V

CC

V

CC

——10µA

——10µA

——500µA

——10

µA

3 21st Aug ’98

Page 4

HT23C020

Supply voltage: 4.5V~5.5V Ta=–40°C to 85°C

Symbol Parameter

V

CC

I

CC

V

IL

V

IH

V

OL

V

OH

I

LI

I

LO

I

STB1

I

STB2

C

IN

C

OUT

Operating Voltage — — 4.5 — 5.5 V

Operating Current 5V

Input Low Voltage 5V — V

Input High Voltage 5V — 2.2 — V

Output Low Voltage 5V IOL= 3.2mA — — 0.4 V

Output High Voltage 5V IOH= –1mA 2.4 — V

Input Leakage Current 5V VIN= 0 to V

Output Leakage Current 5V V

Standby Current 5V

Standby Current 5V

Input Capacitance (See note) — f= 1MHz — — 10 pF

Output Capacitance (See note) — f = 1MHz — — 10 pF

Test Conditions

V

CC

Conditions

O/P Unload,

f= 5MHz

= 0 to V

OUT

CE=V

IL

CE=V

IH

≤0.2V

CE

CE≥VCC-0.2V

CC

Min. Typ. Max. Unit

——25mA

— 0.8 V

SS

——10µA

CC

——10µA

— — 1.5 mA

——30

CC

CC

V

V

µA

Note: These parameters are periodically sampled but not 100% tested.

A.C. Characteristics Ta=–40°C to 85°C

=2.7V~3.6V VCC=4.5V~5.5V

V

Symbol Parameter

CC

Min. Max. Min. Max.

t

CYC

t

AA

t

ACE

t

AOE

t

OH

t

OD

t

OE

Cycle Time 250 — 150 — ns

Address Access Time — 250 — 150 ns

Chip Enable Access Time — 250 — 150 ns

Output Enable Access Time — 150 — 80 ns

Output Hold Time — — 10 — ns

Output Disable Time (See Note) — — — 70 ns

Output Enable Time (See Note) — — 10 — ns

Note: These parameters are periodically sampled but not 100% tested.

4 21st Aug ’98

Unit

Page 5

A.C. test conditions

Output load: see figure right

Input rise and fall time: 10ns

Input pulse levels : 0.4V to 2.4V

Input and output timing reference levels:

0.8V and 2.0V (V

=5V), 1.5V (VCC=3V)

CC

Functional Description

The HT23C020 has two modes, namely data

read mode and standby mode, controlled by

CE/

CE/OE1/OE1,CE1/CE1/OE2/OE2/NC and

OE/

OE/NC inputs.

•

Standby mode

The HT23C020 has lower current consumption,

controlled by the chip enable input (CE/

CE1/

CE1). When a low/high level is applied to

the CE/

output enable (OE/

CE or CE1/CE1 input, regardless of the

OE/NC) states, the chip will

enter the standby mode.

CE and

HT23C020

Output load circuit

•

Data read mode

When both the chip enable (CE/

CE1/

CE1/OE2/OE2/NC) and the output en-

able (OE/

OE/NC) are active, the chip is in

data read mode. Otherwise, active CE/

CE1/

CE1 and inactive OE/OE/NC result in

deselect mode. The output will remain in Hi-Z

state.

CE/OE1/OE1,

CE,

Timing Diagrams

•

Propagation delay due to address (CE/CE/OE1/OE1, CE1/CE1/OE2/OE2

and OE/

•

Propagation delay due to chip and output enable (address valid)

OE are active)

5 21st Aug ’98

Page 6

Characteristic Curves

HT23C020

6 21st Aug ’98

Page 7

HT23C020

7 21st Aug ’98

Page 8

HT23C020 MASK ROM ORDERING SHEET

Custom:

Input Medium:

EPROM DISK File (Mail Address: romfile@holtek.com.tw) OTHER

HT23C020

User No. Type/Ref. Name Q’ty Check Sum

Control Pin and Package Form Option:

(a) 32 Pin Type Pin 22:

Pin 31:

Pin 24:

(b) Package Form:

Companion User No.

Package Marking :

Delivery Date : Q’ty:

CUSTOM CONFIRMED BY :

(C1) CE (C2) CE (D1) OE1 (D2) OE1

(C1) CE1 (C2) CE1 (C3) NC (D1) OE2 (D2) OE2 (D3) NC

(1) OE (2) OE (3) NC

(1) Chip Form (2) 32 DIP (3) 32 SOP (4) 32 PLCC

(NAME, DATE, POSITION & CO. CHOP)

Memory Address

Start End

HOL TEK CONFI RMED BY:

(SALES) (SALES MANAGER)

8 21st Aug ’98

Loading...

Loading...