HS-1212RH

Data Sheet August 1999

Radiation Hardened, Dual, High Speed

Low Power, Video Closed Loop Buffer

The HS-1212RH is a dual closed loop buffer featuring user

programmable gain and high speed performance.

Manufactured on Intersil’s proprietary complementary

bipolar UHF-1 (DI bonded wafer) process, this device offers

wide -3dB bandwidth of 340MHz, very fast slew rate,

excellent gain flatness and high output current. These

devicesare QML approved and are processed and screened

in full compliance with MIL-PRF-38535.

A unique feature of the pinout allows the user to select a

voltage gain of +1, -1, or +2, without the use of any external

components. Gain selection is accomplished via

connections to the inputs, as described in the “Application

Information” section. The result is a more flexible product,

fewerpart types in inventory, and more efficient use of board

space.

Compatibility with existing op amp pinouts provides flexibility

to upgrade low gain amplifiers, while decreasing component

count. Unlike most buffers, the standard pinout provides an

upgrade path should a higher closed loop gain be needed at

a future date.

Specifications for Rad Hard QML devices are controlled

by the Defense Supply Center in Columbus (DSCC). The

SMD numbers listed here must be used when ordering.

Detailed Electrical Specifications for these devices are

contained in SMD 5962-96831. A “hot-link” is provided

on our homepage for downloading.

www.intersil.com/spacedefense/space.asp

Ordering Information

INTERNAL

ORDERING NUMBER

5962F9683101VPA HS7-1212RH-Q -55 to 125

5962F9683101VPC HS7B-1212RH-Q -55 to 125

MKT. NUMBER

TEMP. RANGE

(oC)

File Number 4228.1

Features

• Electrically Screened to SMD # 5962-96831

• QML Qualified per MIL-PRF-38535 Requirements

• MIL-PRF-38535 Class V Compliant

• User Programmable For Closed-Loop Gains of +1, -1 or

+2 Without Use of External Resistors

• Standard Operational Amplifier Pinout

• Low Supply Current . . . . . . . . . . . . 5.9mA/Op Amp (Typ)

• Excellent Gain Accuracy . . . . . . . . . . . . . . . 0.99V/V (Typ)

• Wide -3dB Bandwidth. . . . . . . . . . . . . . . . . .340MHz (Typ)

• Fast Slew Rate. . . . . . . . . . . . . . . . . . . . . .1155V/µs (Typ)

• High Input Impedance . . . . . . . . . . . . . . . . . . . 1MΩ (Typ)

• Excellent Gain Flatness (to 50MHz). . . . . . ±0.02dB (Typ)

• Fast Overdrive Recovery . . . . . . . . . . . . . . . . <10ns (Typ)

• Total Gamma Dose. . . . . . . . . . . . . . . . . . . . 300kRAD(Si)

• Latch Up. . . . . . . . . . . . . . . . . . . . . None (DI Technology)

Applications

• Flash A/D Driver

• Video Switching and Routing

• Pulse and Video Amplifiers

• Wideband Amplifiers

• RF/IF Signal Processing

• Imaging Systems

Pinout

HS-1212RH (CERDIP) GDIP1-T8

OR

HS-1212RH (SBDIP) CDIP2-T8

TOP VIEW

OUT1

1

-IN1

2

3

+IN1

4

V-

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

+

-

+

-

8

V+

7

OUT2

6

-IN2

5

+IN2

Application Information

HS-1212RH

HS-1212RH Advantages

The HS-1212RH features a novel design which allows the

user to select from three closed loop gains, without any

external components. The result is a more flexible product,

fewerpart types in inventory, and more efficient use of board

space. Implementing a dual, gain of 2, cable driver with this

IC eliminates the four gain setting resistors, which frees up

board space for termination resistors.

Like most newer high performance amplifiers, the

HS-1212RH is a current feedback amplifier (CFA). CFAs

offer high bandwidth and slew rate at low supply currents,

but can be difficult to use because of their sensitivity to

feedback capacitance and parasitics on the inverting input

(summing node). The HS-1212RH eliminates these

concerns by bringing the gain setting resistors on-chip. This

yields the optimum placement and value of the feedback

resistor, while minimizing feedback and summing node

parasitics.Because there is no access to the summing node,

the PCB parasitics do not impact performance at gains of +2

or -1 (see “Unity Gain Considerations” for discussion of

parasitic impact on unity gain performance).

The HS-1212RH’s closed loop gain implementation provides

better gain accuracy, lower offset and output impedance,

and better distortion compared with open loop buffers.

Closed Loop Gain Selection

This “buffer” operates in closed loop gains of -1, +1, or +2, with

gain selection accomplished via connections to the inputs.

Applying the input signal to +IN and floating -IN selects a gain

of +1 (see next section for la y out ca v eats), while g rounding -IN

selects a gain of +2. A gain of -1 is obtained by applying the

input signal to -IN with +IN grounded through a 50Ω resistor.

The table below summarizes these connections:

GAIN

(ACL)

-1 50Ω to GND Input

+1 Input NC (Floating)

+2 Input GND

+INPUT -INPUT

CONNECTIONS

Unity Gain Considerations

Unity gain selection is accomplished by floating the -Input of

the HS-1212RH. Anything that tends to short the -Input to

GND, such as stray capacitance at high frequencies, will

cause the amplifier gain to increase toward a gain of +2. The

result is excessive high frequency peaking, and possible

instability. Even the minimal amount of capacitance

associated with attaching the -Input lead to the PCB results

in approximately 6dB of gain peaking. At a minimum this

requires due care to ensure the minimum capacitance at the

-Input connection.

Table 1 lists five alternate methods for configuring the

HS-1212RH as a unity gain buffer, and the corresponding

performance. The implementations vary in complexity and

involve performance trade-offs. The easiest approach to

implement is simply shorting the two input pins together,

and applying the input signal to this common node. The

amplifier bandwidth decreases from 430MHz to 280MHz,

but excellent gain flatness is the benefit. A drawback to this

approach is that the amplifier input noise voltage and input

offset voltage terms see a gain of +2, resulting in higher

noise and output offset voltages. Alternately, a 100pF

capacitor between the inputs shorts them only at high

frequencies, which prevents the increased output offset

voltage but delivers less gain flatness.

Another straightforward approach is to add a 620Ω resistor

in series with the amplifier’s positive input. This resistor and

the HS-1212RH input capacitance form a low pass filter

which rolls off the signal bandwidth before gain peaking

occurs. This configuration was employed to obtain the data

sheet AC and transient parameters for a gain of +1.

Pulse Overshoot

The HS-1212RH utilizes a quasi-complementary output stage

to achieve high output current while minimizing quiescent

supply current. In this approach, a composite device replaces

the traditional PNP pulldown transistor . The composite device

switches modes after crossing 0V, resulting in added distortion

forsignals swinging below ground, and an increased overshoot

on the negative portion of the output wavef orm (see Figure 6,

Figure 9, and Figure 12). This overshoot isn’t present for small

bipolar signals (see Figure 4, Figure 7, and Figure 10) or large

positive signals (see Figure 5, Figure 8 and Figure 11).

PC Board Layout

This amplifier’s frequency response depends greatly on the

care taken in designing the PC board (PCB). The use of low

inductance components such as chip resistors and chip

capacitors is strongly recommended, while a solid

ground plane is a must!

Attention should be given to decoupling the power supplies.

A large value (10µF) tantalum in parallel with a small value

(0.1µF) chip capacitor works well in most cases.

2

HS-1212RH

TABLE 1. UNITY GAIN PERFORMANCE FOR VARIOUS IMPLEMENTATIONS

APPROACH PEAKING (dB) BW (MHz) ±0.1dB GAIN FLATNESS (MHz)

Remove -IN Pin 4.5 430 21

+RS= 620Ω 0 220 27

+RS= 620Ω and Remove -IN Pin 0.5 215 15

Short +IN to -IN (e.g., Pins 2 and 3) 0.6 280 70

100pF Capacitor Between +IN and -IN 0.7 290 40

Terminated microstrip signal lines are recommended at the

input and output of the device. Capacitance directly on the

output must be minimized, or isolated as discussed in the

next section.

An example of a good high frequency layout is the

Evaluation Board shown in Figure 3.

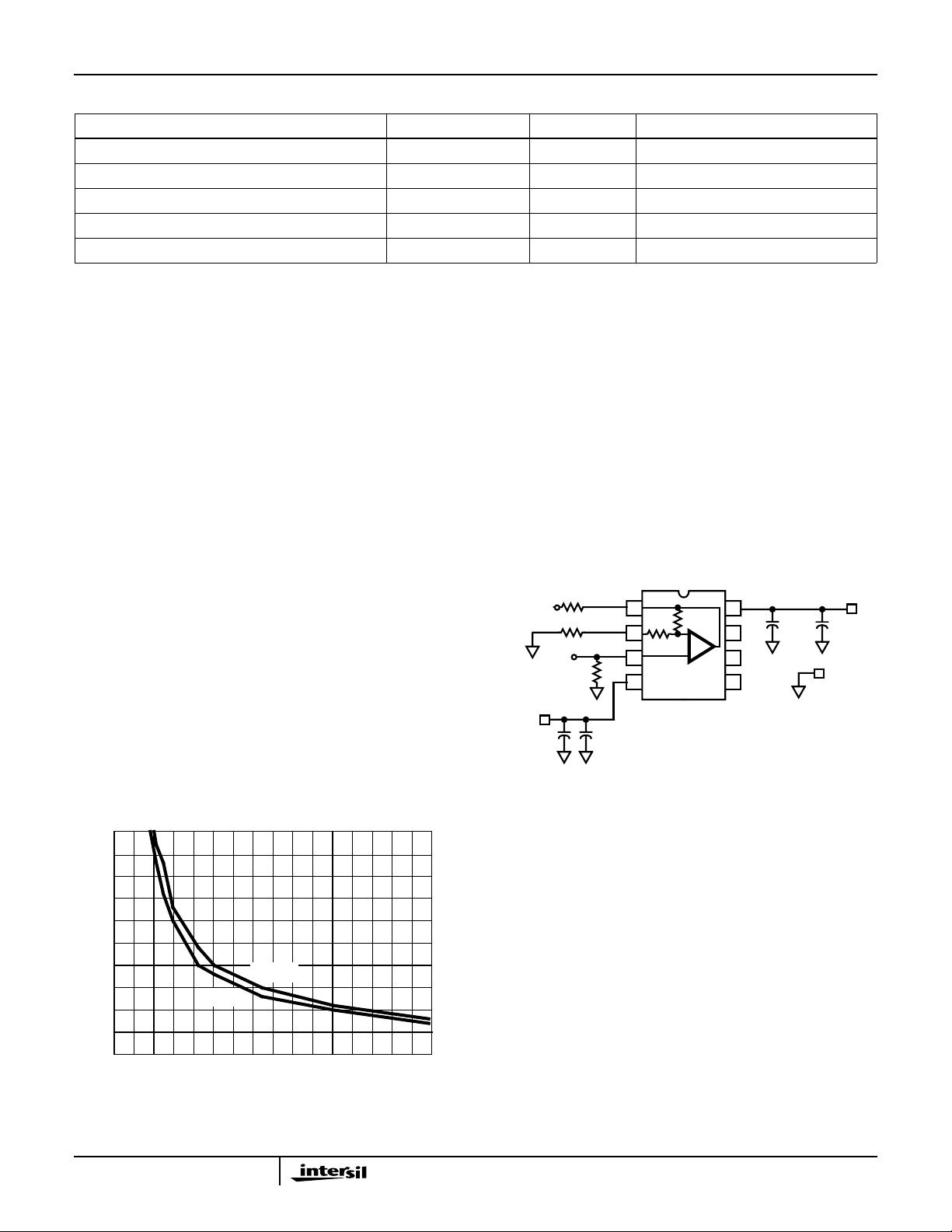

Driving Capacitive Loads

Capacitive loads, such as an A/D input, or an improperly

terminated transmission line will degrade the amplifier’s

phase margin resulting in frequency response peaking and

possible oscillations. In most cases, the oscillation can be

avoided by placing a resistor (R

prior to the capacitance.

Figure 1 details starting points for the selection of this

resistor. The points on the curve indicate the R

combinations for the optimum bandwidth, stability, and

settling time, but experimental fine tuning is recommended.

Picking a point above or to the right of the curve yields an

overdampedresponse, while points below or left of the curve

indicate areas of underdamped performance.

R

and CL form a low pass network at the output, thus

S

limiting system bandwidth well below the amplifier bandwidth

of 350MHz. By decreasing R

illustrated in the curves), the maximum bandwidth is

obtained without sacrificing stability. In spite of this,

bandwidth decreases as the load capacitance increases.

) in series with the output

S

S

as CL increases (as

S

and C

L

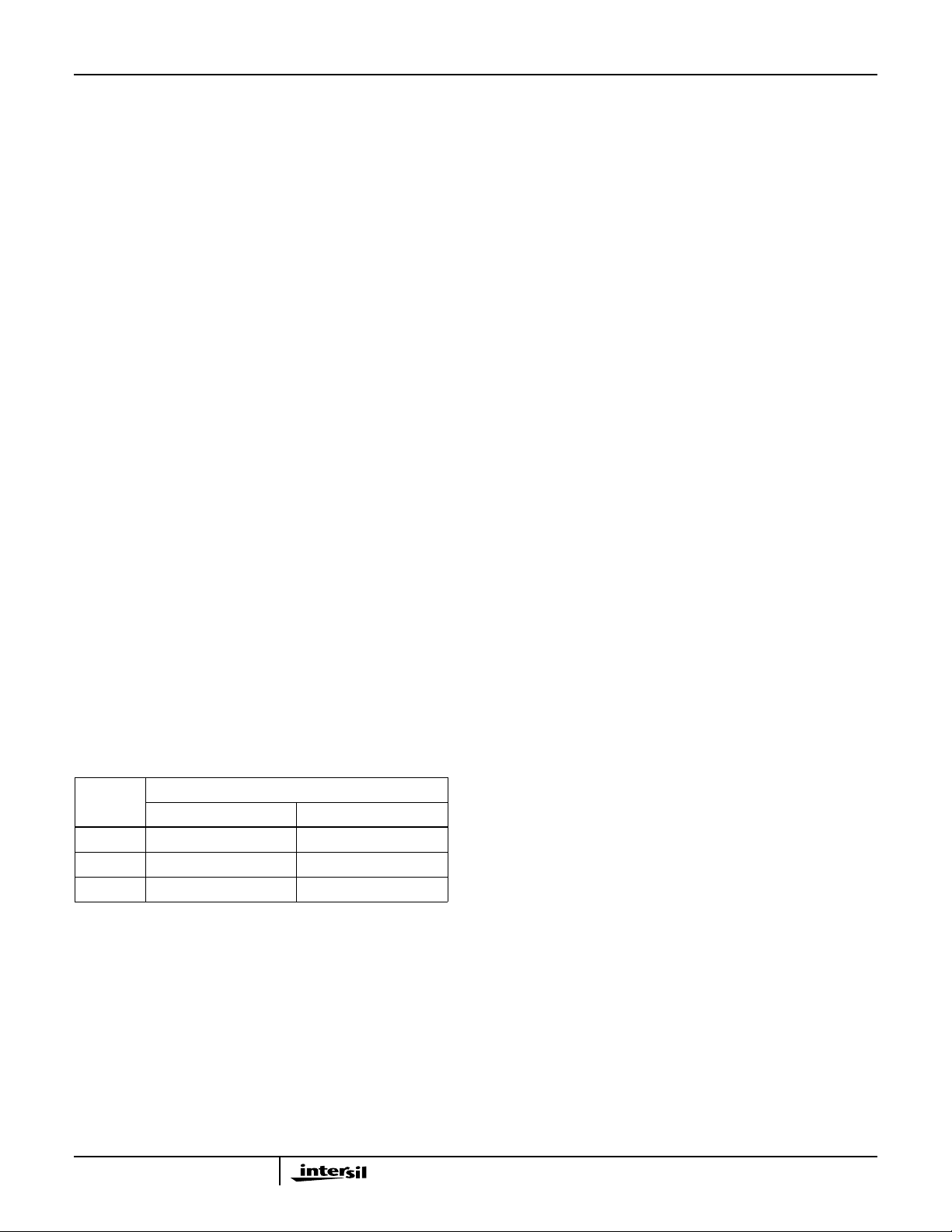

Evaluation Board

The performance of the HS-1212RH maybe evaluatedusing

the HA5023 Evaluation Board, slightly modified as follows:

1. Remove the two feedback resistors, and leave the

connections open.

2. a. For A

resistors (R

b. For A

with 0Ω resistors to GND.

The modified schematic for amplifier 1, and the board layout

are shown in Figures 2 and 3.

To order evaluation boards (part number HA5023EVAL),

please contact your local sales office.

OUT

−5V

10µF 0.1µF

FIGURE 2. MODIFIED EVALUATION BOARD SCHEMATIC

= +1 evaluation,remove the gain setting

V

), and leave pins 2 and 6 floating.

1

= +2, replace the gain setting resistors (R1)

V

IN

50Ω

R

50Ω

(NOTE)

1

1

2

3

4

−

+

8

7

6

5

GND

NOTE: R1=

OR 0Ω (A

0.1µF

∞ (A

V

V

+5V

10µF

GND

=+1)

=+2)

50

40

30

20

10

SERIES OUTPUT RESISTANCE (Ω)

0

0 100 200 300 400

FIGURE 1. RECOMMENDED SERIES RESISTOR vs LOAD

AV=+2

LOAD CAPACITANCE (pF)

CAPACITANCE

AV=+1

150 250 35050

3

HS-1212RH

FIGURE 3A. TOP LAYOUT FIGURE 3B. BOTTOM LAYOUT

FIGURE 3. EVALUATION BOARD LAYOUT

Typical Performance Curves V

200

A

= +2

V

150

100

50

0

-50

-100

OUTPUT VOLTAGE (mV)

-150

-200

FIGURE 4. SMALL SIGNAL PULSE RESPONSE FIGURE 5. LARGE SIGNAL POSITIVE PULSE RESPONSE

2.0

= +2

A

V

1.5

1.0

TIME (5ns/DIV.)

= ±5V, TA = 25oC, RL = 100Ω, Unless Otherwise Specified

SUPPLY

2.0

A

= +2

V

1.5

1.0

0.5

0

-0.5

OUTPUT VOLTAGE (V)

-1.0

-1.5

-2.0

200

150

100

= +1

A

V

TIME (5ns/DIV.)

0.5

0

-0.5

OUTPUT VOLTAGE (V)

-1.0

-1.5

-2.0

TIME (5ns/DIV.)

50

0

-50

-100

OUTPUT VOLTAGE (mV)

-150

-200

TIME (5ns/DIV.)

FIGURE 6. LARGE SIGNAL BIPOLAR PULSE RESPONSE FIGURE 7. SMALL SIGNAL PULSE RESPONSE

4

HS-1212RH

Typical Performance Curves V

2.0

= +1

A

V

1.5

1.0

0.5

0

-0.5

OUTPUT VOLTAGE (V)

-1.0

-1.5

-2.0

TIME (5ns/DIV.)

= ±5V, TA = 25oC, RL = 100Ω, Unless Otherwise Specified (Continued)

SUPPLY

2.0

A

= +1

V

1.5

1.0

0.5

0

-0.5

OUTPUT VOLTAGE (V)

-1.0

-1.5

-2.0

TIME (5ns/DIV.)

FIGURE 8. LARGE SIGNAL POSITIVE PULSE RESPONSE FIGURE 9. LARGE SIGNAL BIPOLAR PULSE RESPONSE

200

150

100

A

= -1

V

2.0

1.5

1.0

A

= -1

V

50

0

-50

-100

OUTPUT VOLTAGE (mV)

-150

-200

TIME (5ns/DIV.)

0.5

-0.5

OUTPUT VOLTAGE (V)

-1.0

-1.5

-2.0

0

TIME (5ns/DIV.)

FIGURE 10. SMALL SIGNAL PULSE RESPONSE FIGURE 11. LARGE SIGNAL POSITIVE PULSE RESPONSE

2.0

1.5

1.0

0.5

-0.5

OUTPUT VOLTAGE (V)

-1.0

-1.5

-2.0

= -1

A

V

0

TIME (5ns/DIV.)

6

3

0

-3

-6

-9

NORMALIZED GAIN (dB)

GAIN

AV = +1

PHASE

V

= 200mV

OUT

+RS = 620Ω (+1)

+R

= 0Ω (-1, +2)

S

1 10 100 600

P-P

FREQUENCY (MHz)

AV = -1

AV = +1

AV = +2

AV = +2

0

-90

-180

-270

-360

NORMALIZED PHASE (DEGREES)

FIGURE 12. LARGE SIGNAL BIPOLAR PULSE RESPONSE

5

FIGURE 13. FREQUENCY RESPONSE

HS-1212RH

Typical Performance Curves V

6

3

0

-3

-6

-9

NORMALIZED GAIN (dB)

V

= 4V

= 5V

(+1)

P-P

(-1, +2)

P-P

FREQUENCY (MHz)

OUT

V

OUT

+R

= 620Ω (+1)

S

1 10 100 300

SUPPLY

AV = -1

A

= +2

V

A

= +1

V

FIGURE 14. FULL POWER BANDWIDTH FIGURE 15. GAIN FLATNESS

-10

-20

-30

-40

-50

-60

-70

GAIN (dB)

-80

-90

-100

-110

0.3 1 10 100

FREQUENCY (MHz)

AV = -1

AV = +1

AV = +2

= ±5V, TA = 25oC, RL = 100Ω, Unless Otherwise Specified (Continued)

0.7

V

= 200mV

OUT

0.6

+RS = 620Ω (+1)

= 0Ω (-1, +2)

+R

0.5

S

0.4

0.3

0.2

0.1

0

NORMALIZED GAIN (dB)

-0.1

-0.2

-0.3

1 10 100

-10

AV = +2

-20

-30

-40

-50

-60

-70

CROSSTALK (dB)

-80

-90

-100

-110

0.3 1 10 100 500

P-P

AV = +2

AV = +1

FREQUENCY (MHz)

RL = ∞

FREQUENCY (MHz)

AV = -1

RL = 100Ω

FIGURE 16. REVERSE ISOLATION FIGURE 17. ALL HOSTILE CROSSTALK

-40

-45

-50

-55

-60

DISTORTION (dBc)

-65

-70

-10 -5 0 5 10

20MHz

10MHz

OUTPUT POWER (dBm)

FIGURE 18. 2nd HARMONIC DISTORTION vs P

6

OUT

-40

-45

-50

-55

-60

DISTORTION (dBc)

-65

15

-70

-10 -5 0 5 10 15

FIGURE 19. 3rd HARMONIC DISTORTION vs P

20MHz

10MHz

OUTPUT POWER (dBm)

OUT

HS-1212RH

Typical Performance Curves V

0.10

0.05

-0.05

SETTLING ERROR (%)

-0.10

0

AV = +1

13 33 53 73 93 113 153 173133

TIME (ns)

FIGURE 20. SETTLING RESPONSE FIGURE 21. INPUT NOISE CHARACTERISTICS

3.6

3.5

3.4

3.3

3.2

3.1

3.0

2.9

OUTPUT VOLTAGE (V)

2.8

2.7

2.6

-50 -25 0 25 50 75 100 125

SUPPLY

A

= -1

V

|-V

= ±5V, TA = 25oC, RL = 100Ω, Unless Otherwise Specified (Continued)

20

16

12

8

NOISE VOLTAGE (nV/√Hz)

4

0

| (RL= 50Ω)

OUT

+V

+V

(RL= 100Ω)

OUT

(RL= 50Ω)

OUT

TEMPERATURE (

|-V

OUT

0.1 1 10 100

| (RL= 100Ω)

o

C)

FREQUENCY (kHz)

20

16

12

E

NI

I

NI

8

NOISE CURRENT (pA/√Hz)

4

0

FIGURE 22. OUTPUT VOLTAGE vs TEMPERATURE

7

Burn-In Circuit

HS-1212RH

HS-1212RH CERDIP

D4

V-

R1

D2 C2

NOTES:

1. R1 = 1kΩ, ±5% (Per Socket).

2. C1 = C2 = 0.01µF (Per Socket) or 0.1µF (Per Row) Minimum.

3. D1 = D2 = 1N4002 or Equivalent (Per Board).

4. D3 = D4 = 1N4002 or Equivalent (Per Socket).

5. |(-V)| + |(+V)| = 11V ±1.0V.

6. 10mA < | I

7. -50mV < V

, IEE | < 16mA.

CC

< +50mV.

OUT

Irradiation Circuit

1

+

-

2

3

4

8

7

+

-

6

5

HS-1212RH CERDIP

D3

V+

C1 D1

R1

NOTES:

8. R1=1kΩ, ±5%

9. C1= 0.01µF

10. V+ = +5.0V ±0.5V

11. V- = -5.0V ±0.5V

1

+

-

2

R1

3

V-

4

C1

8

7

+

-

6

5

C1

R1

V+

8

Die Characteristics

HS-1212RH

DIE DIMENSIONS:

69 mils x 92 mils x 19 mils

1750µm x 2330µm x 483µm

INTERFACE MATERIALS:

Glassivation:

Type: Nitride

Thickness: 4k

Å ±0.5kÅ

Top Metallization:

Type: Metal 1: AICu(2%)/TiW

Thickness: Metal 1: 8k

Å ±0.4kÅ

Type: Metal 2: AICu(2%)

Thickness: Metal 2: 16k

Å ±0.8kÅ

Substrate:

UHF-1X, Bonded Wafer, DI

Backside Finish:

Silicon

Metallization Mask Layout

-IN1

HS-1212RH

OUT1

ASSEMBLY RELATED INFORMATION:

Substrate Potential (Powered Up

):

Floating (Recommend Connection to V-)

ADDITIONAL INFORMATION:

Transistor Count:

180

NC

NC

+IN1

NC

NC

V-

NC

+IN2

V+

OUT2

-IN2

NC

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and

reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

9

Loading...

Loading...