Page 1

1

CLK

D in

AD in

CLK

D in

AD in

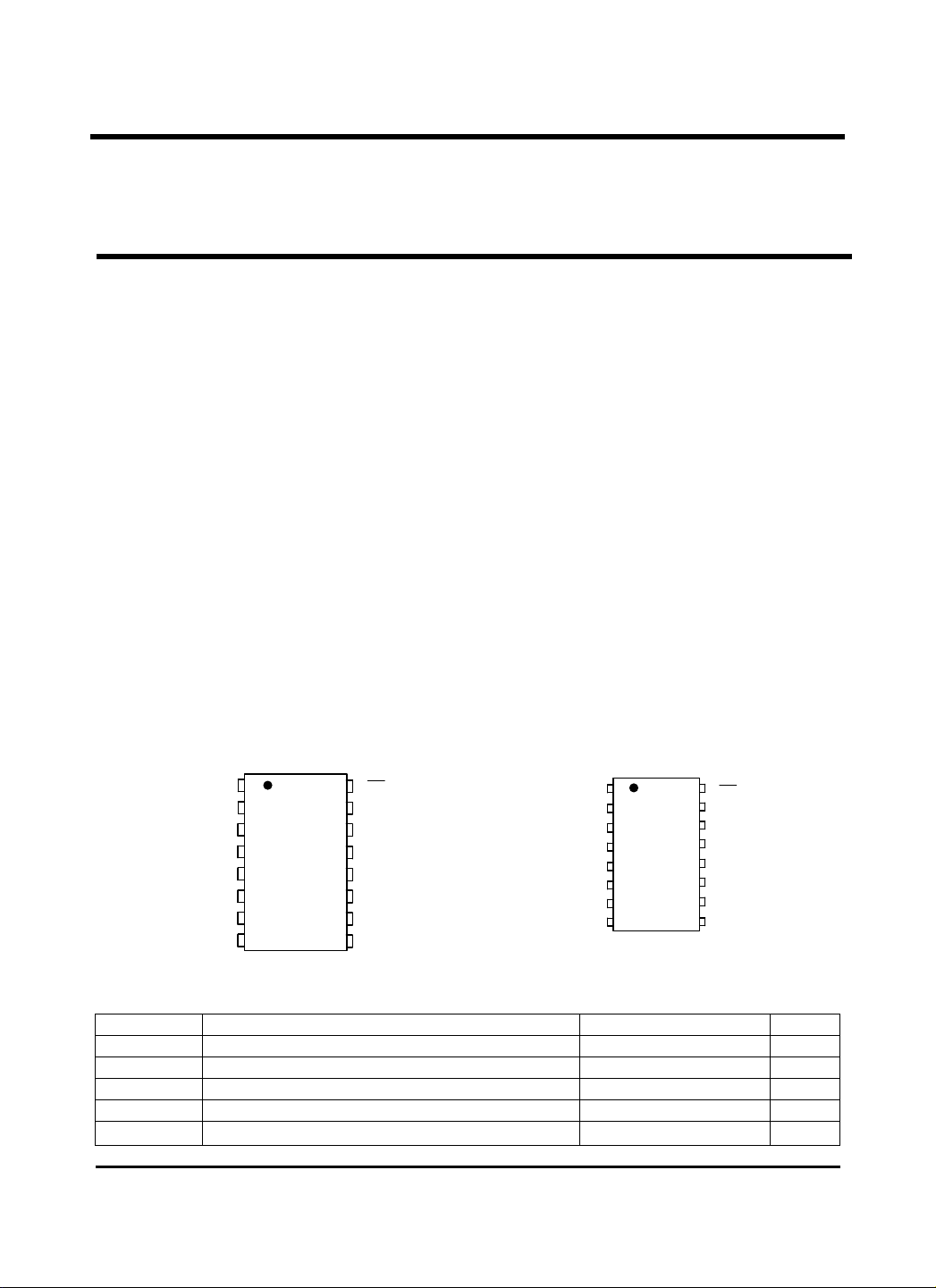

16DIP

16 SOP (150Mil)

GM6535

GM6535

60 MHz Universal Programmable

Dual PLL Frequency synthesizer

GENERAL DESCRIPTIONS

The GM6535 is a dual phase – locked loop

(PLL) frequency synthesizer especially designed for

CT-1 cordless phone applications worldwide. This

frequency synthesizer is also for any products with

frequency operation at 60 MHz or below.

The device features fully programmable

receive, transmit, reference, and auxiliary reference

counters accessed through an MCU serial interface,

this feature allows this device to operate in any CT1 cordless phone application.

The device consists of two independent phase

detectors for transmit and receive loops. A common

reference oscillator, driving two independent

reference frequency counters, provides independent

reference frequencies for transmit and receive loops.

The auxiliary reference counter allows the

user to select an additional reference frequency for

receive and transmit loops if required.

PIN CONFIGURATION

ENB

MCUCLK

Vss

OSC

OSC

out

i

Tx PD

fin-T

TxPS/f

VDD

RxPS/f

RxPD

fin-R

OUT

Tx

Rx

o

FEATURES

• Operating Voltage Range: 2.5 to 5.5 V

• Operating Temperature Range:-40 to +75¡É

• Operating Power Consumption:3.0mA@2.5V

• Maximum Operating Frequency:

60MHz@200mV

• 3 or 4 Pins Used for serial MCU Interface

• Power Saving Mode Controlled by MCU

• Lock Detect Signal

• On-Chip Reference Oscillator Supports External

Crystals to 16.0 MHz

• Reference Frequency Counter Division Range: 16 to

4095

• Auxiliary Reference Frequency Counter Division

Range: 16 to 16,383

• Transmit Counter Division Range:16 to 65,535

• Receive Counter Division Range: 16 to 65,53

ENB

MCUCLK

OSC

OSC

Vss

out

i

, VDD=2.5V

p-p

Tx PD

fin-T

TxPS/f

VDD

RxPS/f

RxPD

fin-R

OUT

Tx

Rx

o

ABSOLUTE MAXIMUM RATINGS (Voltages Referenced to v

)

ss

Symbol

Ranting Value Unit

VDD DC Supply Voltage -0.5 to +6.0 V

V

Iin , I

IDD , I

T

stg

in

Input Voltage, all Inputs -0.5 to V

DC Current Drain Per Pin 10 mA

out

DC Current Drain VDD or VSS Pins 30 mA

SS

+0.5 V

DD

Storage Temperature Range -65 to + 150

¡É

Page 2

2

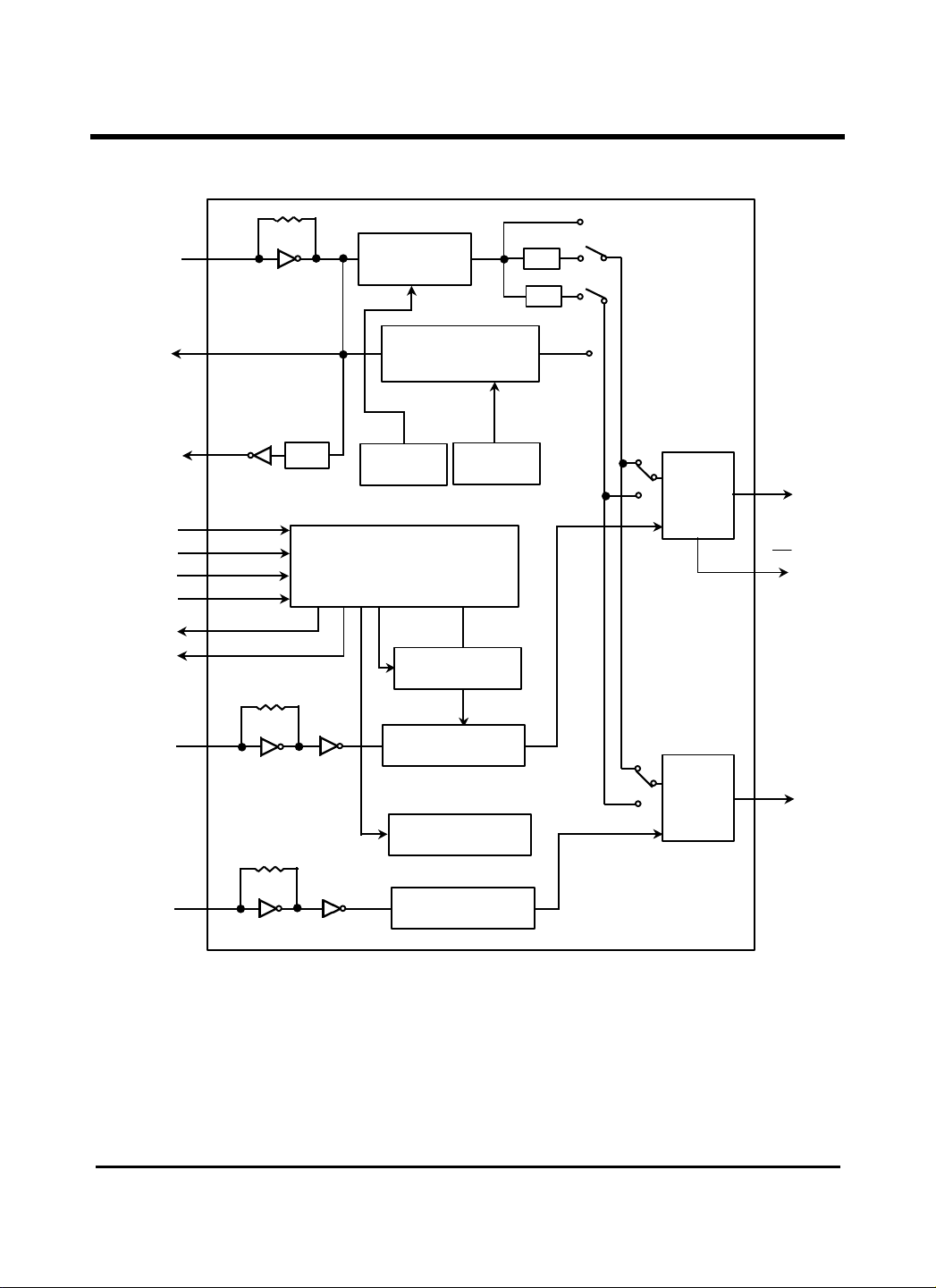

BLOCK DIAGRAM

12-Bit Shift

14-Bit Shift

MCU Interface Programming

16-Bit Tx Programmable

16-Bit Rx Programmable

Rx

Rx

TRANSMIT

RECEIVE

OSC

in

8

OSC

out

7

MCUCLK

5

AD

in

2

1

CLK

D

in

ENB

TX

RX

3

4

13

11

TxPS/f

PxPS/f

÷ 3 / ÷ 4

12-Bit Programmable

Reference Counter

14-Bit Programmable

Auxiliary Reference

Counter

Register

Mode control Register

16-Bit Shift Register

Register

÷ 4

÷ 25

A

B

C

D

f

R1

f

R2

SELECT

Phase

Detector

GM6535

TxPD

out

15

LD

16

f in

14

-T

Counter

16-Bit Shift Register

SELECT

Phase

Detector

RxPD

10

out

f in

9

-R

Counter

VDD = PIN 12

VSS = PIN 6

Page 3

3

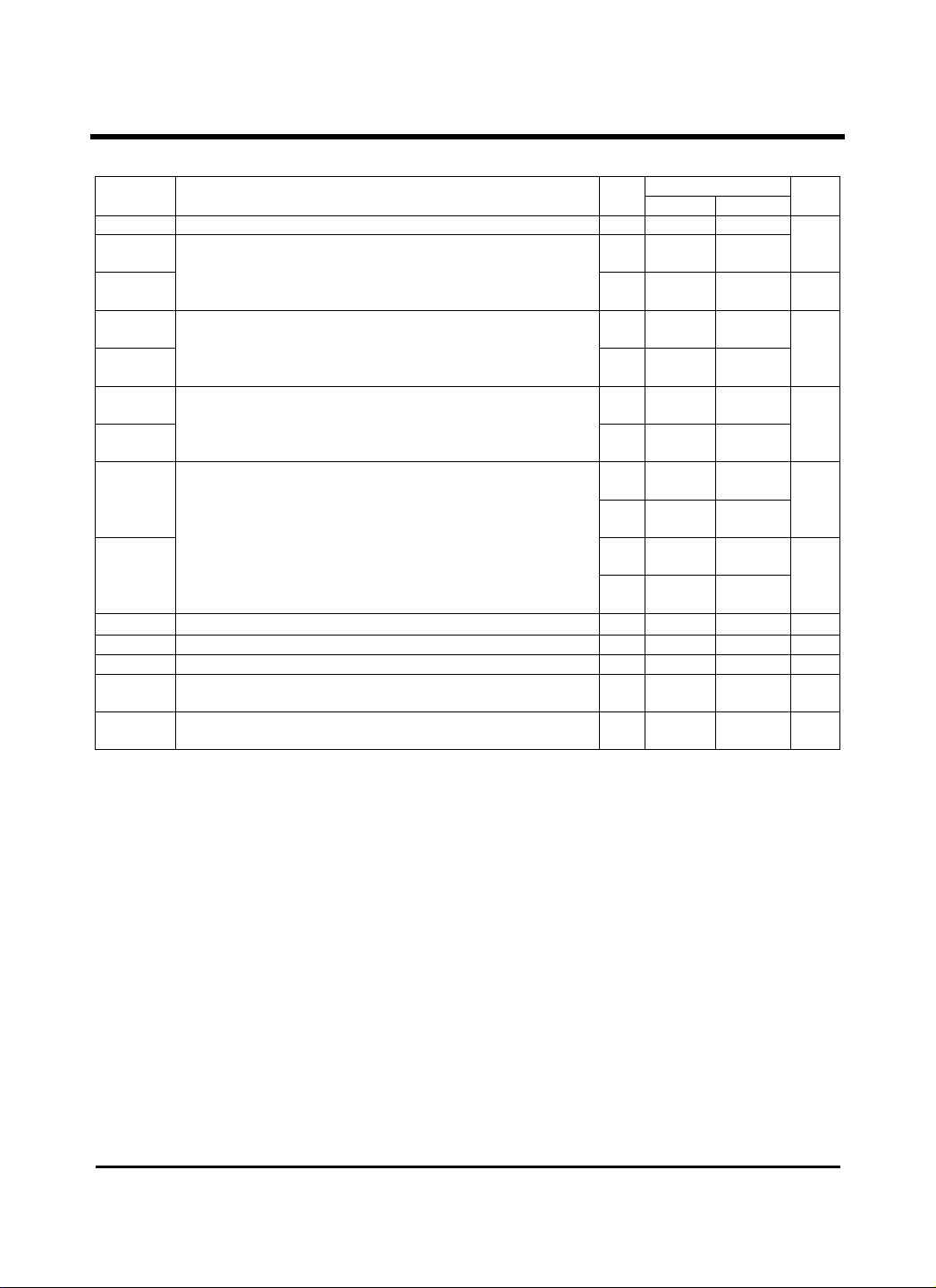

ELECTRICAL CHARACTERISTICS (Voltages Referenced to VSS, TA =25 ¡É)

V

V

V

V

V

V

I

OL

I

IL

Power Supply Voltage - 2.5 5.5

DD

Output Voltage 0 Level

OL

OH

IL

IH

OH

(I

= 0)

out

(V

or 0) 1 Level

in =VDD

Input Voltage 0 Level

(V

0.5 V or V

out

1 Level

Output Current (V

Input Current OSC

(Vin = 0)

ADin , CLK , Din , ENB

Characteristic V

– 0.5V)

DD

= 2.2V) Source

out

(V

= 5.0V)

out

(V

= 0.3V) Sink

out

(V

= 0.5V)

out

, f

in

in-T

, f

in-R

Symbol

(Vin = VDD –0.5)

IIH

I

OZ

C

in

C

out

IDD

(standby)

I

DD

OSC

ADin

Three-Stats Leakage Current (V

, CLK , Din , ENB

= 0 V or 5.5 V)

out

Input Capacitance - - 8.0 pF

Output Capacitance - - 8.0 pF

Standby Current

(All Counters are in Power-Down Mode with Oscillator On)

Operating Current (200mV

input at f

p-p

in-T

=60MHz, OSC = 10.24MHz)

, f

, f

in

in-T

in-R

= 60MHz, and f

in-R

Guaranteed Limit

DD

Min Max

2.5

5.5

2.5

5.5

2.5

5.5

2.5

5.5

2.5

5.5

2.5

5.5

2.5

5.5

2.5

5.5

2.5

5.5

2.5

5.5

5.5

2.5

5.5

2.5

5.5

-

-

2.45

5.45

-

-

1.75

3.85

-0.18

-0.55

0.18

0.55

-

-

-

-

-

-

-

-

- ¡¾100 nA

-

-

-

-

GM6535

0.1

0.1

-

-

0.75

1.65

-

-

-

-

-

-

-30

-66

-1.0

-1.0

30

61

5.0

5.0

0.3

1.5

3.0

10

Unit

V

V

V

mA

¥ìA

¥ìA

mA

mA

Page 4

4

tTLH

tTHL

ANY

OUTPUT

in

f

in-T, f in-R

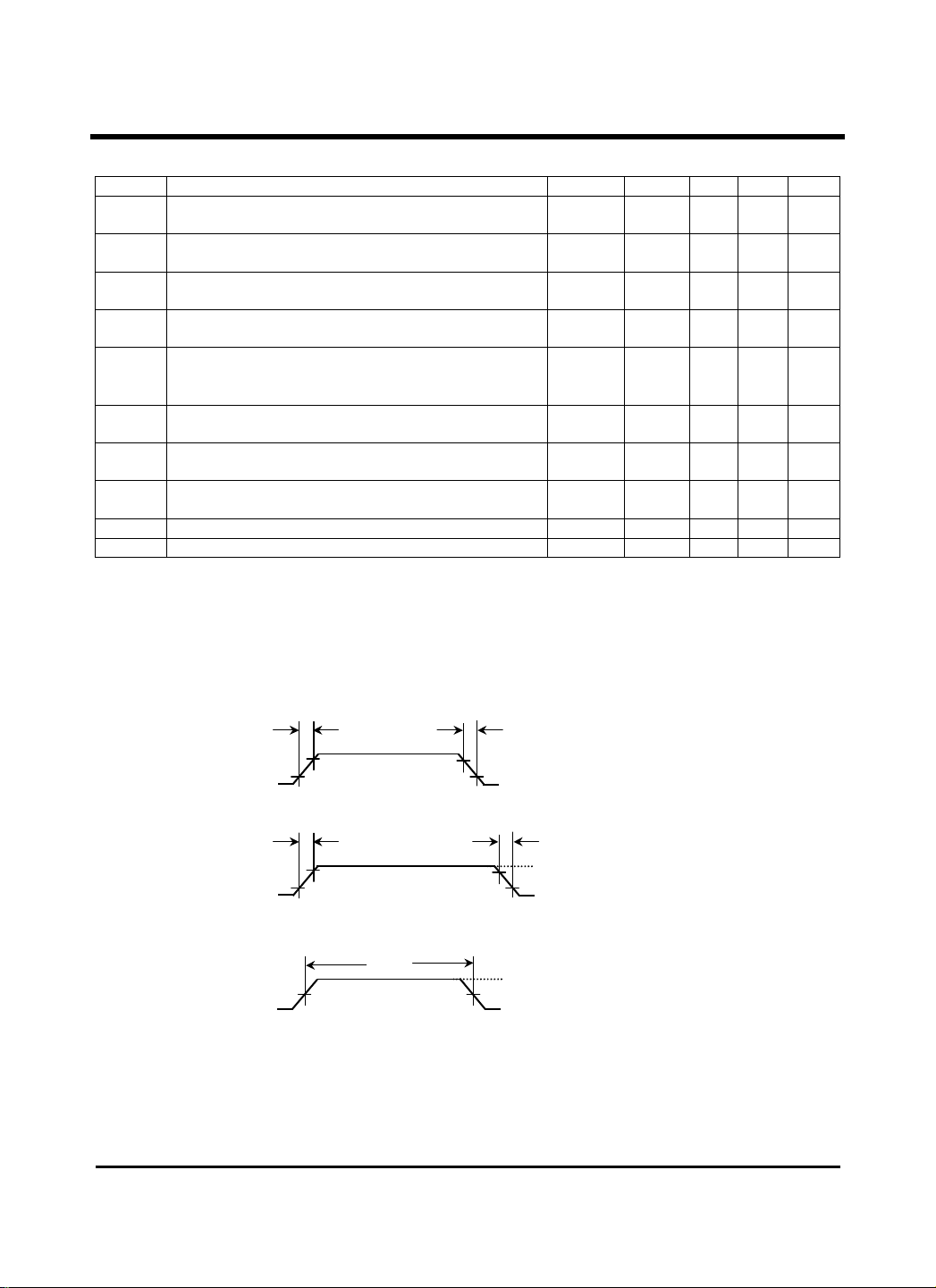

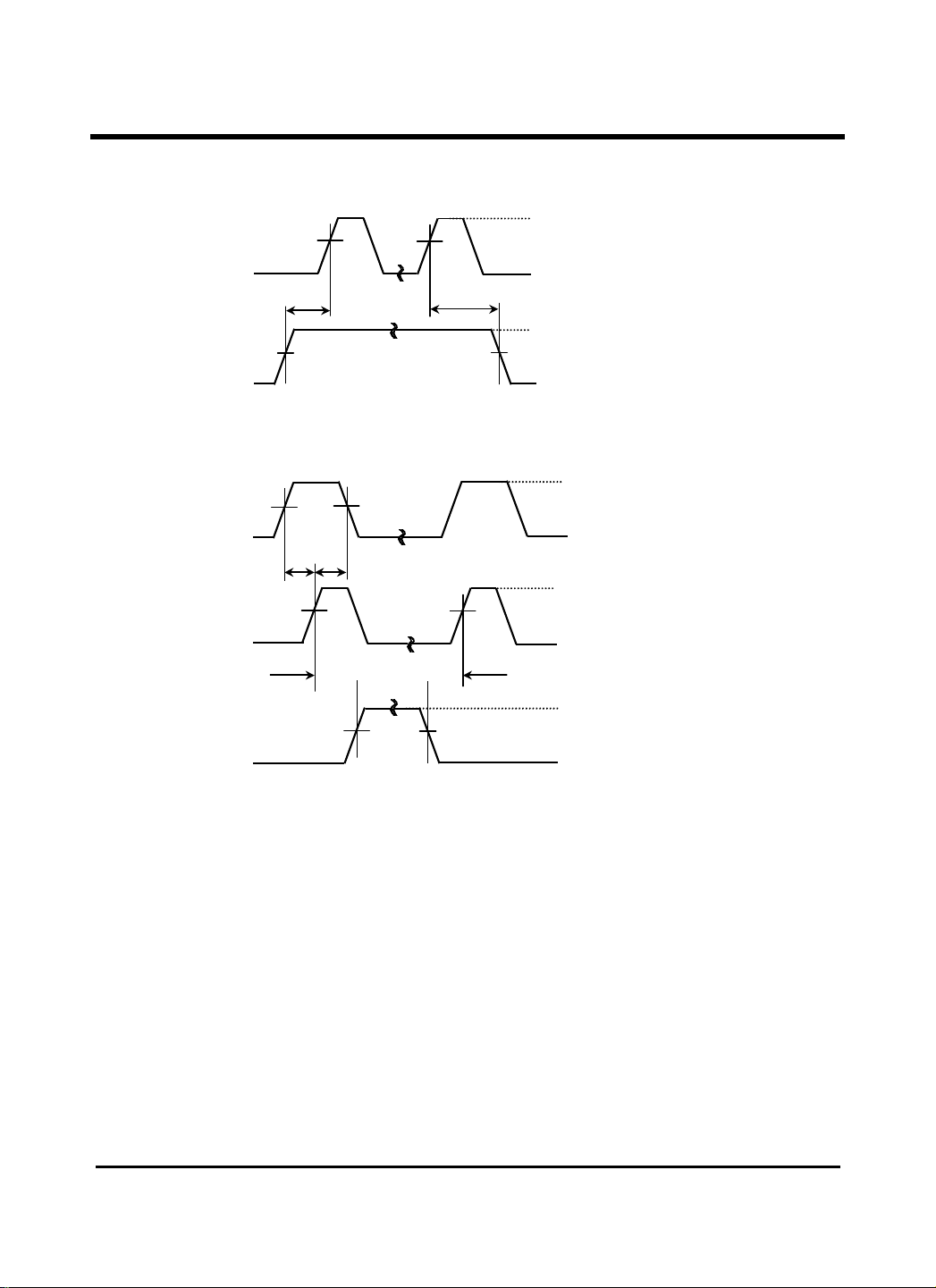

SWITCHING CHARACTERISTICS (TA = 25

t

TLH

t

THL

tT, t

t

f

max

Output Rise Time

Output Fall Time

Input Rise and Fall Time, OSC

f

Input Pulse Width, CLK and ENB

W

Input frequency OSCin

(Input = Sine Wave @ ≥ 200mV

Characteristic Figure # V

Symbol

t

t

Setup Time Data to CLK

t

su

Hold Time, CLK to Data

t

h

Recovery Time, ENB to CLK

rec

Setup Time, ENB to CLK 4 2.5-5.5 80

sul

t

Hold Time, CLK to ENB 4 2.5-5.5 600 - ns

hl

in

p-p

¡É, CL = 50 pF)

f

ENB to CLK

in-T

f

in-R

1

1

2

3

5

5

5

DD

2.5

5.5 - -

2.5

5.5 - -

2.5

5.5 - -

2.5

5.5

2.5-5.5

2.5-5.5

2.5-5.5

2.5-5.5

5.5-5.5

2.5

5.5

2.5

5.5

GM6535

Min Max Unit

200

100

200

100

5.0

4.0

80

60

-

-

100

200

80

40

80

40

ns

ns

µs

ns

-

16

MHz

60

60

ns

-

ns

-

ns

-

- ns

SWITCHING WAVERORMS

90%

10%

CLK, OSC

90%

10%

t

r

ENB, CLK

50%

Figure 1.

Figure 2.

t

W

Figure 3.

t

f

V

DD

V

SS

V

DD

V

SS

Page 5

5

LAST

FIRST

AD in,

FIRST

LAST

PREVIOUS

CLK

CLK

t

hl

ENB

CLK

t

sul

Figure 4.ENB High During Serial Transfer

D in

CLK

50%

t

su

50%

t

su

CLK

t

h

CLK

t

rec

GM6535

V

DD

V

SS

V

DD

V

SS

V

DD

V

SS

V

DD

V

SS

ENB

50%

DATA LATCHED

V

DD

V

SS

Figure 5. ENB Low During Serial Transfer

Page 6

6

PIN DESCRIPTIONS

D C

B A

OSC

in

OSC

out f R1

f

R2

Figure 6. Reference Frequencies for Cordless Phone

OSCin/OSC

out

Reference Oscillator Input/Output (Pins8, 7)

These pins form a reference oscillator when

connected to an external parallel-resonant crystal

frequencies and reference frequencies for cordless

phone applications in various countries. OSCin may

also serve as input for an externally generated

reference signal which is typically ac coupled.

ADin, Din, CLK, ENB

Auxiliary Data In, Data In, Clock, Enable (Pins2, 3,

1, 4)

These four pins provide an MCU serial interface for

programming the reference counter, the transmitchannel counter, and the receive-channel counter. They

also provide various controls of the PLL including the

power saving mode and the programming format.

TxPS/fTx,RxPS/f

Rx

Transmit Power Save, Receive Power Save (Pins 13,

11)

For a normal application, these output pins provide

the status of the internal power saving mode operation.

If the transmit channels counter circuitry is in power

down mode, TxPS/fTx outputs a high state. If the

receive-channels counter circuitry is in power down

mode, RxPS/fRx is set high. These output can be

applied for controlling the external power switch for

the transmitter and the receiver to save MCU control

pins. In the Tx/Rx channel counter test mode, the

TxPS/fTx and RxPS/fRx pins output the divided value of

the transmit channel counter (fTx) and the receive

channel counter (fRx), respectively. This test mode

operation is controlled by the control register. Details

of the counter test mode are in the Tx/Rx Channel

Counter Test section of this data sheet.

÷ N (12 bits)

÷ M ( 14bits )

Crystal ¡ÀN Value f

11.150 MHz 446 6.25 MHz 1.0 MHz

11.150 MHz 223 12.5 MHz

10.240 MHz 512 5.0 MHz

12.000 MHz 600 5.0 MHz

Applications of Various Countries

GM6535

f

Transmit/Receive Counter Inputs (Pins14, 9)

receive counters, respectively. These signals are

typically driven from the loop VCO and ac-coupled.

The minimum input signal level is 200mV

60.0MHz.

TxPD

Transmit/Receive Phase detector Outputs (Pins15,

10)

receive phase detectors for use as loop error signals

(see Figure7 for phase detector output waveforms).

Frequency fV > fR or fV leading: output=negative pulse.

Frequency fV < fR or fV lagging: output = positive pulse.

Frequency fV = fR and phase coincidence: output = high

impedance state.

phase detector input and fV is the divided-down VCO

frequency at the phase detector input.

LD Lock Detect (Pin16)

loop. The output at a high level indicates an out-oflock condition (see Figure 7 for the LD output

waveform).

VDD Positive Power Supply (Pin 12)

ranging from 2.5 to 5.5V with respect to VSS.

VSS Negative Power Supply (Pin 6)

usually connected to ground.

in-T/fin-R

f

in-T

and f

out

are inputs to the transmit and the

in-R

/RxPD

out

p-p

These are three-state outputs of the transmit and

fR is the divided-down reference frequency at the

The lock detect signal is associated with the transmit

VDD is the most positive power supply potential

VSS is the most negative supply potential and is

÷4

÷25

¡æ B f

R1

¡æ C

R2

@

Page 7

7

f R ,REFERENCE

REFERENCE COUNTER)

f v ,FEEDBACK

Tx COUNTER OR

Rx COUNTER)

TxPD

(OSC

÷

in

(F

÷

in - T

f

÷

in -_R

RxPD

OR

out

out

LD

V H = High voltage level

V L = Low voltage level

*At this point, when both fR and fv are in phase, the output is forced to near mid supply.

NOTE: The TxPD

When locked in phase and frequency, the output is high impedance and the voltage at that pin is determined

By the low-pass filter capacitor

and PxPDout generates error pulses during out-of-lock conditions.

out

Figure 7. Phase Detector/Lock Detector Output Waveforms

MCU PROGRAMMING SCHEME

The MCU programming scheme is defined in

two formats controlled by the ENB input. If the

enable signal is high during the serial data transfer,

control register/reference frequency programming is

selected. If the ENB is low, programming of the

transmit and receive counters is selected. During

programming of the transmit and receive counters,

both AD in and D in pins can input the data to the

transmit and receive counters. Both counters data is

clocked into the PLL internal shift register at the

leading edge of the CLK signal. It is not necessary

to reprogram the reference frequency

counter/control register when using the enable

signal to program the transmit/receive channels.

In programming the control register/reference

frequency scheme, the most significant bit (MSB) of

the programming word identifies whether the input

data is the control word. If the MSB is 1, the input

data is the control word (Figure 8). Also see figure

NO TAG and Table 1 for control register and bit

function. If the MSB is 0, the input data is the

reference frequency (Figure 9).

The reference frequency data word is 32-bit word

containing the 12-bit reference frequency data, the

14-bit auxiliary reference frequency counter

information, the reference frequency selection plus,

the auxiliary reference frequency counter enable

bit(Figure 9).

If the AUX REF ENB bit is high, the 14-bit

auxiliary reference frequency counter provides an

additional phase reference frequency output for the

loops. If AUX REF ENB bit is low, the auxiliary

reference frequency counter is forced into powerdown modes for current saving. (other power down

modes are also provided through the control register

per Table 2 and Figure 8). At the falling edge of the

ENB signal, the data is stored in the registers.

There are two interfacing schemes for the

universal channel mode: the three-pin and four-pin

interfacing schemes. The three-pin interfacing

scheme is suited for use with the MCU SPI (serial

peripheral interface) (Figure 10), while the four-pin

interfacing scheme is commonly used for general

I/O port connection (Figure 11).

For the three-pin interfacing scheme, the

auxiliary data select bit is set to 0. All 32 bits of data,

which define both the 16-bit transmit counter and

the 16-bit receive counter, latch into the PLL

internal register though the data in pins at the

leading edge of CLK. See Figure 12 and 13.

For the four-pin interfacing scheme, the auxiliary

data select bit is set to 1. In this scheme, the 16-bit

transmit counter’s data enters into the ADin pin at

the same time as the 16-bit receive. This

simultaneous entry of the transmit and receive

counters causes the programming period of the fourpin scheme to be half that of the three-pin scheme

(see Figures 14 and 15).

While programming Tx/Rx Channel Counter,

the ENB pin must be pulsed to provide falling edge

to latch the shifted data after the rising edge of the

last clock. Maximum data transfer rate is 500 kbps.

V

H

V

L

V

H

V

L

V

H

HIGH IMPEDANCE

GM6535

Page 8

8

TxPD

RxPD

Ref PD

AUX

TEST

REF

GM6535

COMTROL REGISTER IDENTIFIER = 1

D

in

1

MSB

0

COMTROL REGISTER DATA

OUT

Data

BIT

Select

÷3/÷ 4

Enable

Enable

Enable

LSB

CLK

ENB

NOTE: ENB must be high during the serial transfer.

Figure 8. Programming Format of the control Register

Table 1. Control Register Function Bits Description

Test Bit

Aux Data

Select

REF

out

TxPD Enable

RxPD Enable

Ref PD

Set to 1 for Tx/Rx channel counter test mode

Set to 0 for normal application

Set to 1 for both ADin and Din pins inputting the transmit 16-bits data and receive 16-bits data respectively

Set to 0 for normal application interfacing with MCU serial peripheral interface.

Does not use AD in pin; tie AD in to VSS.

If set to 1, REFout output frequency is equal to OSC

÷3/÷ 4

If set to 0, REFout output is OSC

out

÷ 4.

out

÷ 3.

If set to 1, the transmit counter, transmit phase detector, and the associated circuitry is in power-down

mode. TxPS/fTx is set “High”.

If set to 1, the receive counter, receive phase detector, and the associated circuitry is in power-down mode.

RxPS/fTx is set “High”.

If set to 1, both 12-bit and 14-bit reference frequency counters are in power-down mode

Enable

Table 2. Control Register Power Down Bits Function

TxPD

Enable

RxPD

Enable

REF PD

Enable

Tx-Channel Counter Rx-channel Counter

0 0 0 - - 0 0 1 - - Power Down

0 1 0 - Power Down 0 1 1 - Power Down Power Down

1 0 0 Power Down - 1 0 1 Power Down - Power Down

1 1 0 Power Down Power Down 1 1 1 Power Down Power Down Power Down

Reference

Frequency Counter

Page 9

9

Aux Reference

Reference

Reference Frequency

fR1

Rx-0

AUX

fR1

Reference

Tx-0

12-BITS REF FREQ

14-BITS AUX REF FREQ

Reference Frequency

Counter Identifier = 0

Universal PLL

MCU Using

Universal PLL

MCU Using

TxPD

RxPD

Ref PD

AUX

TEST

Control Register

REF

Frequency

Select

D

in

0

REF

ENABLE

SELECT

CLK

ENB

NOTE: ENB must be high during the serial transfer.

Figure 9. Programming Format of Auxiliary/reference Frequency Counter

Serial Peripheral

Interface Port

Figure 10. MCU Interface Using SPI

Normal I/O Port

Figure 11. MCU Interface Using Normal I/O Ports with Both Din

And A Din for Faster Programming Time

Identifier = 1

D

in

AUX DATA SELECT = 0

MSB

1

0

SELECT

BIT

Counter Divide Ratio

DATA

D

in

CLK

ENB

ADin

D

in

CLK

ENB

Control Register Data

OUT

Data

÷3/÷ 4

Select

S1

Aux Data Bit = 0

Aux Data Bit = 1

Enable

Frequency

Select

Enable

S2

Enable

Frequency Counter

Divide Ratio

DATA

LSB

GM6535

CLK

ENB

NOTE: ENB must be high during the serial transfer.

Figure 12. Programming Format for control Register (3-Pin Interfacing Scheme)

Page 10

10

16-BIT Tx COUNTER

16-BIT Rx COUNTER

Last

TxPD

RxPD

Ref PD

AUX

TEST

Control Register

REF

mat for control Register

(4-Pin Interfacing Scheme)

16-BIT Tx COUNTER

16-BIT Rx COUNTER

Last

Figure 15. Programming Format for Transmit and Receive Counters

(4-Pin Interfacing Scheme)

GM6535

D

in

DIVIDE RATIO

CLK

ENB

NOTE: ENB must be low during the serial transfer.

Figure 13. Programming Format for Transmit and Receive Counters

(3-Pin Interfacing Scheme)

DIVIDE RATIO

Clock

Identifier = 1

MSB

1

0

D

in

AUX DATA SELECT = 1

CLK

ENB

NOTE: ENB must be high during the serial transfer.

Figure 14. Programming For

AD

in

D

in

CLK

Control Register Data

BIT

Select

DIVIDE RATIO

DIVIDE RATIO

Data

OUT

÷3/÷ 4

Enable

Clock

Enable

Enable

LSB

ENB

NOTE: ENB must be low during the serial transfer.

Page 11

11

Table 3. Global CT-1 Reference frequency Setting vs Channel Frequencies

Country Channel Frequency f

U.S.A 46/49MHz(10,15,25 Channels)

France 26/41 MHz

R1

5.0 KHz -

6.25 KHz/12.5

KHz

Spain 31/41 MHz 5.0 KHz Australia 30/39 MHz 5.0 KHz U.K 1.7/47 MHz 6.25 KHz 1.0 KHz

New

Zealand

1.7/34/40 MHz 6.25 KHz 1.0 KHz

REFERENCE FREQUENCY SELECTION

AND PROGRAMMING

Figure 16 shows the bit function of the reference

frequency programming word. The user can either

select the fixed reference frequency for all channels

accordingly or provide a specific reference

frequency for a particular channel by using two

reference frequency counters (e.g., for an

application in France, the base set transmit channel

common fixed reference frequency is 6.25 KHz or

12.5 KHz). (See Table 3 Figure 6 for reference

frequencies for various countries.)

However, transmit channels 6, 8, and 14 can be

set to 25 KHz, and channel 8 reference frequency

can be set to 50 KHz. But this reference frequency

may not be applied to the receiving side; therefore,

the receiving side reference frequency must be

generated by another reference frequency counter.

The higher the reference frequency, the better the

phase noise performance and faster the lock time,

but the PLL consumes more current if both

reference frequency counters are in operation. In

general, the 12-bit reference frequency counter plus

frequencies for global CT-1 transmit and receive

channel requirements. Users can select their own

reference frequency by introducing the additional

14-bit auxiliary reference frequency counter.

Again, the 14-bit auxiliary reference frequency

counter can be shut down by the auxiliary reference

enable bit in the reference counter programming

word by setting the bit to 0. At this state, the fR2 is

automatically connected to point C (the ÷ 25 block

output), and fR1 cha be connected to point A or B by

setting the fR1-S1 and fR1-S2 bits in the reference

counter program word. The 14-bit auxiliary

reference frequency counter data will be in Don’t

Care state.

If the 14-bit auxiliary reference frequency counter

is enabled (auxiliary reference enable = 1), the fR2 is

automatically connected to point D (14-bit counter

output), and fR1 can be selected to connect to point

A,B, or C, depending on the bit setting of fR1-S1 and

fR1-S2.

Table 4 and Figure 16 describe the functions of

the auxiliary reference enable bit and the fR1-S1 and

fR1-S2 bits selection.

the ÷ 4 and ÷ 25 module can offer all the reference

Table 4. Bit Function and the Reference Frequency Selection Bit Setting of the

Reference Frequency Counter Programming Word

N/A Not Applicable

AUX REF

Enable

0

Auxiliary Reference Frequency

Counter Mode

14-Bit Auxiliary Reference Frequency

Counter Disable

Module

Select

fR2→ C

f

S1

R1

0

0

1

1

1

14-Bit Auxiliary Reference Frequency

Counter Disable

fR2→ D

0

0

1

1

f

S2

f

R1

0

1

0

1

0

1

0

1

GM6535

R2

-

fR1

Routin

g

N/A

fR1→ A

fR1→ B

N/A

N/A

fR1→ A

fR1→ B

fR1→ C

Page 12

12

Rx-0

Tx-0

12-Bits Programmable

14-Bits Programmable

Tx

Rx

Reffrequency

Auxiliary Reference

Reference

Reference

fR1

Rx-0

AUX

fR1

Reference

Tx-0

12-BITS REF FREQ

14-BITS AUX REF FREQ

0 1 0

GM6535

D

in

OSC

in

OSC

out

Maximum

Crystal Frequency

16.0 MHZ

Counter

Identifier = 0

REF

0

Enable

Frequency

Select

Select

Reference Counter

Auxiliary Reference

Counter

Select

Frequency

Counter

DATA

÷4

÷25

Frequency

Select

S1

S2

f

R1

f

R2

DATA

Phase

Detector

Phase

Detector

TxPD

LD

RxPD

out

out

1

SELECT

SELECT

Frequency Counter

CLK

ENB

NOTE: ENB must be high during the serial transfer.

Figure 16. Reference Frequency Counter/selection Programming Mode

Page 13

13

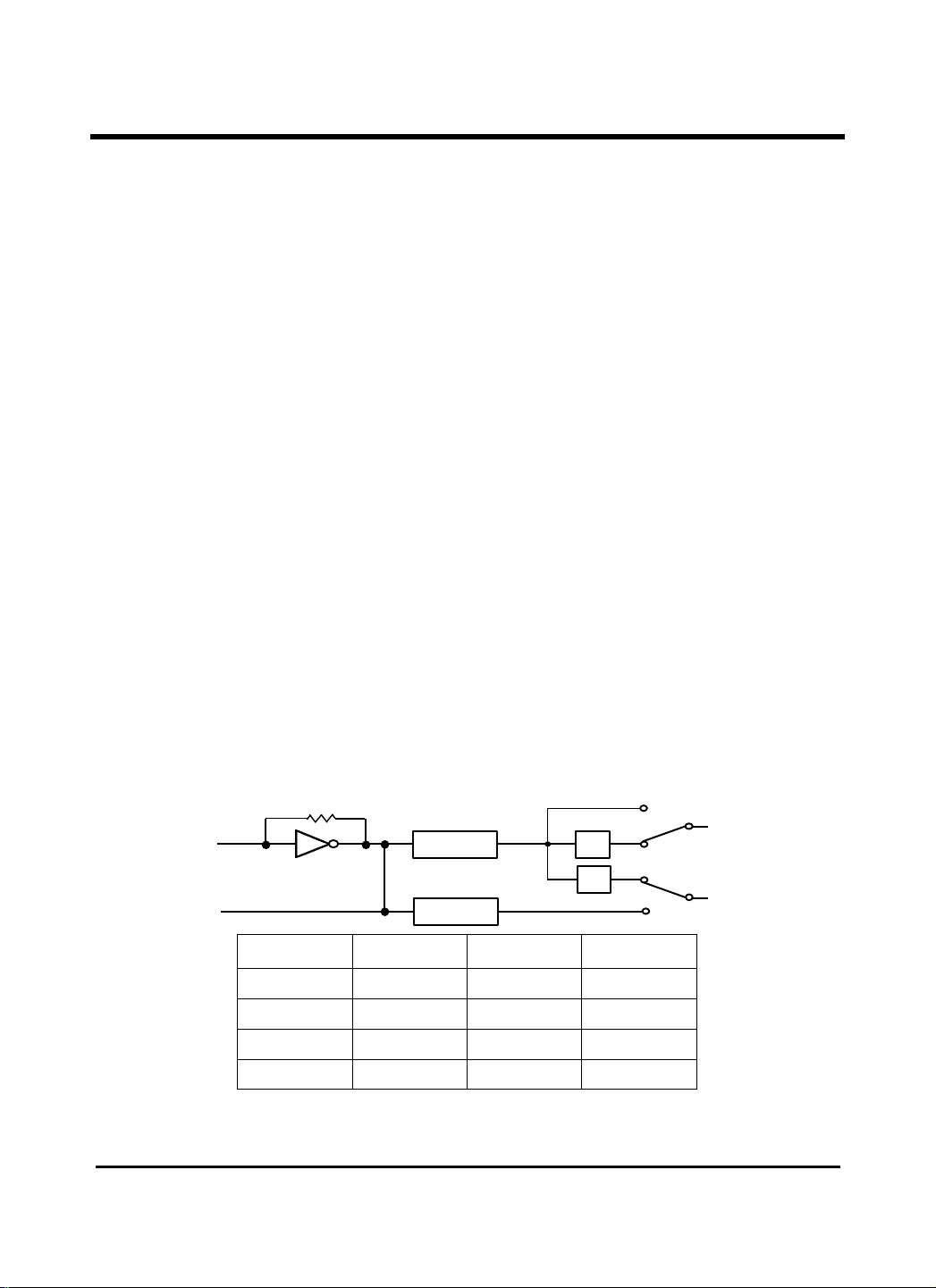

POWER SAVING OPERATION

To control

POWER SWITCH

TX

AMP

Tx Power-Down

Rx Power-Down

GM6535

This PLL has a programmable power-saving

scheme. The transmit counter, receive counter and

the reference frequency counter can be powered

down individually by setting the TxPD enable,

RxPD enable and Ref PD enable bits of the control

register. The functions of the power down control

bits are explained in Table 2 and the programming

format is in Figure 8.

The output pins TxPS/fTx and RxPS/fRx output the

Power Supply

UNIVERSAL DUAL PLL

FOR TRANSMITTER

TxPS/f

Tx

Power

status of the internal power saving setting. If the bit

TxPD enable is set high (transmit counter is set to

power-down mode), then the TxPS/fTx pin will also

output a high state. This TxPS/fTx output can control

an external power switch to switch off the

transmitter, as shown in Figure 17. This scheme

can be applied to the RxPS/fRx output to control the

receiver power saving operation as required.

V

DD

Q

Enable Flag

Tx Divider chain Counter, Phase Detector

V

DD

RxPS/f

The Receiver

Power Switch

Rx

Rx Divider chain Counter, Phase Detector

Q

Enable Flag

Figure 17. TxPS/fTx and RxPS/fRx Outputs to Control Power Switches

of the Transmitter and Receiver

Page 14

14

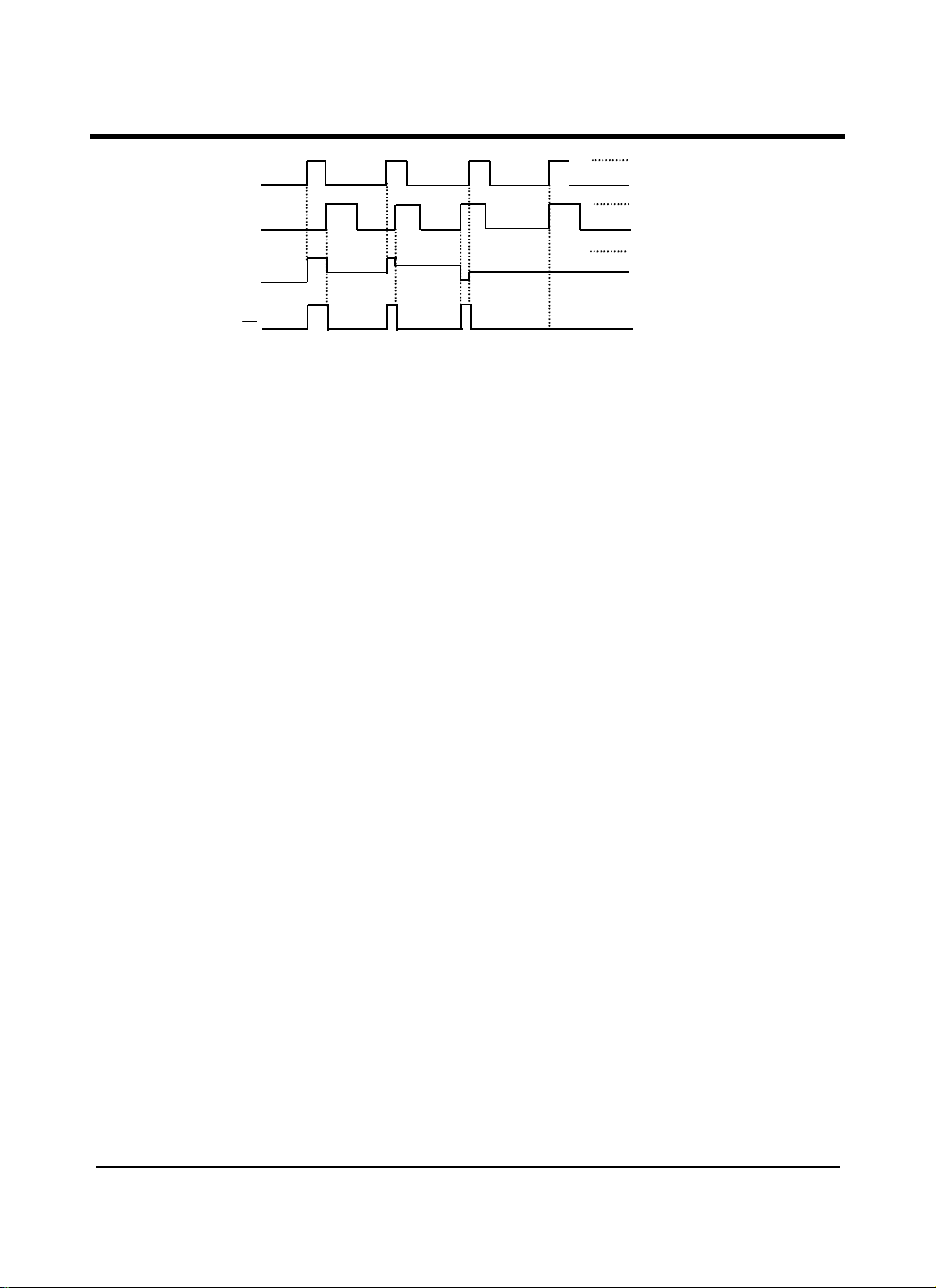

TX/RX CHANNEL COUNTER TEST

CONTROL REGISTER

16-BIT Tx PROGAMMABLE

TxPD

RxPD

Ref PD

AUX

TEST

REF

16-BIT Rx PROGRAMMABLE

IF TEST BIT TO 1, THE f

GM6535

In normal applications, the TxPS/fTx and the

RxPS/fRx output pins indicate the power saving

mode status. However, the user can examine the Tx

and Rx channel counter outputs by setting the Test

bit in the control register to 1. The final value of

the transmit-channel counter and the receive-

f

in-T

TxPS/f

Tx

AND f Rx ARE MIXED OUT AT PINS

TxPS/f

AND RxPS/f

Tx

RESPECTIVEY, FOR Rx/Tx

CHANNEL COUNTER TEST.

Tx

D

in

IDENTIFIER = 1

1

Rx

channel counter multiplex out to TxPS/fTx and

RxPS/fRx respectively. The user can verify the

divided-down output waveform associated with the

RF input level in the PLL circuitry implementation

(Figure 18).

CHANNELS COUNTER

f

Tx

TxPS

CONTROL REGISTER

0

BIT

SELECT

DATA

OUT

÷3/÷ 4

ENABLE

ENABLE

ENABLE

f

in-R

f

TxPS/f

Rx

Figure 18. RF Buffer Sensitivity

Rx

RxPS

CHANNELS COUNTER

Page 15

15

Table 5. France CT-1 Base Set Frequency

Tx Counter

Value

(Ref. Freq.=

6.25 KHz)

f

Input

in-R

Frequency(MHz)

[1st IF = 10.7MHz]

Channel

Number

Tx-Channel

Frequency

(MHz)

1 26.4875 4238 30.7875 4926

2 26.4750 4236 30.7750 4924

3 26.4625 4234 30.7625 4922

4 26.4500 4232 30.7500 4920

5 26.4375 4230 30.7375 4918

6 26.4250 4228 30.7250 4916

7 26.4125 4226 30.7125 4914

8 26.4000 4224 30.7000 4912

9 26.3875 4222 30.6875 4910

10 26.3750 4220 30.6750 4908

11 26.3625 4218 30.6625 4906

12 26.3500 4216 30.6500 4904

13 26.3375 4214 30.6375 4902

14 26.3250 4212 30.6250 4900

15 26.3125 4210 30.6125 4898

Table 6. France CT-1 Hand Set Frequency

Channel

Number

Tx-Channel

Frequency

(MHz)

Tx Counter Value

(Ref. Freq. =

6.25 KHz)

f

Input

in-R

Frequency(MHz)

[1st IF = 10.7MHz]

1 41.4875 6638 37.1875 5950

2 41.4750 6636 37.1750 5948

3 41.4625 6634 37.1625 5946

4 41.4500 6632 37.1500 5944

5 41.4375 6630 37.1375 5942

6 41.4250 6628 37.1250 5940

7 41.4125 6626 37.1125 5938

8 41.4000 6624 37.1000 5936

9 41.3875 6622 37.0875 5934

10 41.3750 6620 37.0750 5932

11 41.3625 6618 37.0625 5930

12 41.3500 6616 37.0500 5928

13 41.3375 6614 37.0375 5926

14 41.3250 6612 37.0250 5924

15 41.3125 6610 37.0125 5922

GM6535

Rx Counter Value

(Ref. Freq. =

6.25 KHz)

Rx Counter Value

(Ref. Freq. =

6.25 KHz)

Page 16

16

Table 7. Spain CT – 1 Base Set Frequency

GM6535

Channel

Number

1 31.0250 6205 29.2300 5846

2 31.0500 6210 29.2550 5851

3 31.0750 6215 29.2800 5856

4 31.1000 6220 29.3050 5861

5 31.1250 6225 29.3300 5866

6 31.1500 6230 29.3550 5871

7 31.1750 6235 29.3800 5876

8 31.2000 6240 29.4050 5881

9 31.2500 6250 29.4550 5891

10 31.2750 6255 29.4800 5896

11 31.3000 6260 29.5050 5901

12 31.3250 6265 29.5300 5906

Tx-Channel

Frequency

(MHz)

Tx Counter Value

(Ref. Freq. = 5.00KHz)

f

Input

in-R

Frequency (MHz)

[1st IF= 10.695 MHz]

Table 8. Spain CT – 1 Hand Set Frequency

Channel

Number

1 39.9250 7985 20.3300 4066

Tx-Channel

Frequency

(MHz)

Tx Counter Value

(Ref. Freq. = 5.00KHz)

f

Input

in-R

Frequency (MHz)

[1st IF= 10.7 MHz]

Rx counter value

(Ref. Freq.=5.00KHz)

Rx counter value

(Ref. Freq.=5.00KHz)

2 39.9500 7990 20.3550 4071

3 39.9750 7995 20.3800 4076

4 40.0000 8000 20.4050 4081

5 40.0250 8005 20.4300 4086

6 40.0500 8010 20.4550 4091

7 40.0750 8015 20.4800 4096

8 40.1000 8020 20.5050 4101

9 40.1500 8030 20.5550 4111

10 40.1750 8035 20.5800 4116

11 40.2000 8040 20.6050 4121

12 40.2250 8045 20.6300 4126

Page 17

17

Table 9. New Zealand CT – 1 Base Set Frequency

GM6535

Channel

Number

1 1.7820 1782 29.7625 4762

2 1.7620 1762 29.7500 4760

3 1.7420 1742 Ref. Freq. 29.7375 4758

4 1.7220 1722 = 1.0KHz 29.7250 4756

5 1.7020 1702 29.7125 4754

6 34.3500 5496 29.7000 4752

7 34.3625 5498 29.6875 4750

8 34.3750 5500 Ref. Freq. 29.6750 4748

9 34.3875 5502 = 6.25KHz 29.6625 4746

10 34.4000 5504 29.6500 4744

Tx-Channel

Frequency

(MHz)

Tx Counter Value

f

Input

in-R

Frequency (MHz)

[1st IF= 10.7 MHz]

Rx counter value

(Ref. Freq.=6.25KHz)

Table 10. New Zealand CT – 1 Hand Set Frequency

Channel

Number

1 40.4625 6474 2.2370 2237

2 40.4500 6472 2.2170 2217

3 40.4375 6470 2.1970 Ref. Freq. 2197 Ref. Freq.

4 40.4250 6468 2.1770 =45.5KHz 2177 =1.0KHz

5 40.4125 6466 2.1570 2157

6 40.4000 6464 23.6500 3784

7 40.3875 6462 2.6625 3786

8 40.3750 6460 23.6750 Ref. Freq. 3788 Ref. Freq.

9 40.3625 6458 23.6875 =10.7KHz 3790 =6.25KHz

10 40.3500 6456 23.7000 3792

Tx-Channel

Frequency

(MHz)

Tx Counter Value

(Ref. Freq. = 6.25KHz)

f

Input

in-R

Frequency (MHz)

Rx counter value

Page 18

18

Table 11. Australia CT – 1 Base Set Frequency

GM6535

Channel

Number

1 30.0750 6015 29.0800 5816

2 30.1250 6025 29.1300 5826

3 30.1750 6035 29.1800 5836

4 30.2250 6045 29.2300 5846

5 30.2750 6055 29.2800 5856

6 30.1000 6020 29.1050 5821

7 30.1500 6030 29.1550 5831

8 30.2000 6040 29.2050 5841

9 30.2500 6050 29.2550 5851

10 30.3000 6060 29.3050 5861

Tx-Channel

Frequency

(MHz)

Tx Counter Value

(Ref. Freq. = 5.00KHz)

f

Input

in-R

Frequency (MHz)

[1st IF= 10.695 MHz]

Table 12. Australia CT – 1 Hand Set Frequency

Channel

Number

1 39.7750 7955 19.3800 3876

2 38.8250 7965 19.4300 3886

3 37.8750 7975 19.4800 3896

4 36.9250 7985 19.5300 3906

5 35.9750 7995 19.5800 3916

6 39.8000 7960 19.4050 3881

7 39.8500 7970 19.4550 3891

8 39.9000 7980 19.5050. 3901

9 39.9500 7990 19.5550 3911

10 40.0000 8000 19.6050 3921

Tx-Channel

Frequency

(MHz)

Tx Counter Value

(Ref. Freq. = 5.00KHz)

F

Input

in-R

Frequency (MHz)

[1st IF= 10.7 MHz]

Rx counter value

(Ref. Freq.=5.00KHz)

Rx counter value

(Ref. Freq.=5.00KHz)

Page 19

19

Table 13. U.K. CT – 1 Base Set Frequency

GM6535

Channel

Number

1 1.6420 1642 36.75625 5881

2 1.6620 1662 36.76875 5883

3 1.6820 1682 36.78125 5885

4 1.7020 1702 36.79375 5887

5 1.7220 1722 36.80625 5889

6 1.7420 1742 36.81875 5891

7 1.7620 1762 36.83125 5893

8 1.7820 1782 36.84375 5895

Tx-Channel

Frequency

(MHz)

Tx Counter Value

(Ref. Freq. = 1.00KHz)

f

Input

in-R

Frequency (MHz)

[1st IF= 10.7 MHz]

Table 14. U.K. CT – 1 Hand Set Frequency

Channel

Number

1 47.45625 7593 2.097 2097

2 47.46875 7595 2.117 2117

3 47.48125 7597 2.137 2137

4 47.49375 7599 2.157 2157

5 47.50625 7601 2.177 2177

6 47.51875 7603 2.197 2197

7 47.53125 7605 2.217 2217

8 47.54375 7607 2.237 2237

Tx-Channel

Frequency

(MHz)

Tx Counter Value

(Ref. Freq. = 0.25KHz)

f

Input

in-R

Frequency (MHz)

[1st IF= 45.5 KHz]

Rx counter value

(Ref. Freq.=6.25KHz)

Rx counter value

(Ref. Freq.=1.00KHz)

Page 20

20

Table 15. U.S.A. CT-1 Base Set Frequency

GM6535

Channel

Number

1 46.610 9322 38.975 7795

2 46.630 9326 38.150 7830

3 46.670 9334 38.165 7833

4 46.710 9342 39.075 7815

5 46.730 9346 39.180 7836

6 46.770 9354 39.135 7827

7 46.830 9366 39.195 7839

8 46.870 9374 39.235 7847

9 46.930 9386 39.295 7859

10 46.970 9394 39.275 7855

Tx-Channel

Frequency

(MHz)

Tx Counter Value

(Ref.Freq. =

5.00 KHz)

f

Input

in-R

Frequency (MHz)

[1st IF=10.695 MHz]

Table 16. U.S.A. CT-1 Hand Set Frequency

Channel

Number

1 49.670 9934 35.915 7183

2 49.845 9969 35.935 7187

3 49.860 9972 35.975 7195

4 49.770 9954 36.015 7203

5 49.875 9975 36.035 7207

6 49.830 9966 36.075 7215

7 49.890 9978 36.135 7227

8 49.930 9986 36.175 7235

9 49.990 9998 36.235 7247

10 49.970 9994 36.275 7255

Tx-Channel

Frequency

(MHz)

Tx Counter Value

(Ref.Freq. =

5.00 KHz)

f

Input

in-R

Frequency (MHz)

[1st IF=10.7 MHz]

Rx Counter Value

(Ref. Freq. =

5.00 KHz)

Rx Counter Value

(Ref. Freq. =

5.00 KHz)

Page 21

21

Table 17. U.S.A. CT-1 Base Set Frequency

GM6535

Channel

Number

1 43.72 8744 38.06 7612

2 43.74 8748 38.14 7628

3 43.82 8764 38.16 7632

4 43.84 8768 38.22 7644

5 43.92 8784 38.32 7664

6 43.96 8788 38.38 7678

7 44.12 8824 38.40 7680

8 44.16 8832 38.46 7692

9 44.18 8836 38.50 770

10 44.20 8840 38.54 7708

11 44.32 8864 38.58 7716

12 44.36 8872 38.66 7732

13 44.40 8880 38.70 7740

14 44.46 8892 38.76 7752

15 44.48 8896 38.80 7760

16 46.61 9322 38.97 7794

17 46.63 9326 39.145 7829

18 46.67 9331 39.16 7832

19 46.71 9342 39.07 7814

20 46.73 9346 39.175 7835

21 46.77 9354 39.13 7826

22 46.83 9366 39.19 7838

23 46.87 9374 39.23 7846

24 46.93 9386 39.29 7858

25 46.97 9394 39.27 7854

Tx-Channel

Frequency

(MHz)

Tx Counter Value

(Ref.Freq. =

5.00 KHz)

f

Input

in-R

Frequency (MHz)

[1st IF=10.7 MHz]

Rx Counter Value

(Ref. Freq. =

5.00 KHz)

Page 22

22

Table 18 U.S.A. CT-1 Hand Set Frequency

GM6535

Channel

Number

1 48.76 9752 33.02 6604

2 48.84 9768 33.04 6608

3 48.86 9772 33.12 6624

4 48.92 9748 33.14 6628

5 49.02 9804 33.22 6644

6 49.08 9816 33.26 6652

7 49.10 9820 33.42 6684

8 49.16 9832 33.46 6692

9 49.20 9840 33.48 6696

10 49.24 9848 33.50 6700

11 49.28 9856 33.62 6724

12 49.36 9872 33.66 6732

13 49.40 9880 33.70 6740

14 49.46 9892 33.76 6752

15 49.50 9900 33.78 6756

16 49.67 9934 33.91 7182

17 49.845 9969 33.93 7186

18 49.88 9972 33.97 7194

19 49.77 9954 36.01 7202

20 49.875 9975 36.03 7206

21 49.83 9966 36.07 7214

22 449.89 9978 36.13 7226

23 49.93 9986 36.17 7234

24 49.99 9998 36.23 7246

25 49.97 9994 36.27 7254

Tx-Channel

Frequency

(MHz)

Tx Counter Value

(Ref.Freq. =

5.00 KHz)

f

Input

in-R

Frequency (MHz)

[1st IF=10.7 MHz]

Rx Counter Value

(Ref. Freq. =

5.00 KHz)

Page 23

23

Table 19 Korea CT-1 Base Set Frequency

GM6535

Channel

Number

1 46.610 9322 38.975 7795

2 46.630 9326 38.150 7830

3 46.670 9334 38.165 7833

4 46.710 9342 39.075 7815

5 46.730 9346 39.180 7836

6 46.770 9354 39.135 7827

7 46.830 9366 39.195 7839

8 46.870 9374 39.235 7847

9 46.930 9386 39.295 7859

10 46.970 9394 39.275 7855

11 46.510 9302 39.000 7800

12 46.530 9306 39.015 7803

13 46.550 9310 39.030 7806

14 46.570 9314 39.045 7809

15 46.590 9318 39.060 7812

Tx-Channel

Frequency

(MHz)

Tx Counter Value

(Ref.Freq. =

5.00 KHz)

f

Input

in-R

Frequency (MHz)

[1st IF=10.695 MHz]

Table 20. Korea CT-1 Hand Set Frequency

Channel

Number

1 49.670 9934 35.915 7183

2 49.845 9969 35.935 7187

3 49.860 9972 35.975 7195

4 49.770 9954 36.015 7203

5 49.875 9975 36.035 7207

6 49.830 9966 36.075 7215

7 49.890 9978 36.135 7227

8 49.930 9986 36.175 7235

9 49.990 9998 36.235 7247

10 49.970 9994 36.275 7255

11 49.695 9939 35.815 7163

12 49.710 9942 35.835 7167

13 49.725 9945 35.855 7171

14 49.740 9948 35.875 7175

15 49.755 9951 35.895 7179

Tx-Channel

Frequency

(MHz)

Tx Counter Value

(Ref.Freq. =

5.00 KHz)

f

Input

in-R

Frequency (MHz)

[1st IF=10.7 MHz]

Rx Counter Value

(Ref. Freq. =

5.00 KHz)

Rx Counter Value

(Ref. Freq. =

5.00 KHz)

Loading...

Loading...