Page 1

GENERAL DESCRIPTION

The EM78811 is an 8-bit CID (Call Identification) RISC type microprocessor with low power , high speed

CMOS technology. Integrated onto a single chip are on_chip watchdog (WDT) , RAM , ROM , programmable

real time clock /counter , internal interrupt , power down mode , LCD driver , FSK decoder , DTMF generator

and tri-state I/O . The EM78811 provides a single chip solution to design a CID of calling message_display .

FEATURES

CPU

• Operating voltage range : 2.5V~5.5V

• 16K X13 on chip ROM

• 2.8K X 8 on chip RAM

• Up to 32 bi-directional tri-state I/O ports

• 8 level stack for subroutine nesting

• 8-bit real time clock/counter (TCC)

• Two sets of 8 bit counters can be interrupt sources

• Selective signal sources and trigger edges , and with overflow interrupt

• Programmable free running on chip watchdog timer

• 99.9% single instruction cycle commands

• Three modes (internal clock 3.679MHz)

1. sleep mode : CPU and 3.679MHz clock turn off, 32.768KHz clock turn off

2. Idle mode : CPU and 3.679 MHz clock turn off, 32.768KHz clock turn on

3. Green mode : 3.679MHz clock turn off, CPU and 32.768KHz clock turn on

4. Normal mode : 3.679MHz clock turn on , CPU and 32.768KHz clock turn on

• Ring on voltage detector and low battery detector

• Input port wake up function

• 8 interrupt source , 4 external , 4 internal

• 100 QFP or chip

• Port key scan function

• Port interrupt, Pull high and Open drain functions

• Clock frequency 32.768KHz

• Main clock can switch to 1.84MHz by code option

EM78811

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

CID

• Operation Volltage 3.5 ~5.5V for FSK

• Operation Volltage 2.5 ~5.5V for DTMF

• Bell 202 , V.23 FSK demodulator

• DTMF generator

• Ring detector on chip

LCD

• LCD operation voltage chosen by software

• Common driver pins : 16

• Segment driver pins : 60

• 1/4 bias

• 1/8,1/16 duty

* This specification are subject to be changed without notice.

10.12.1998

1

Page 2

APPLICATION

1. adjunct units

2. answering machines

3. feature phones

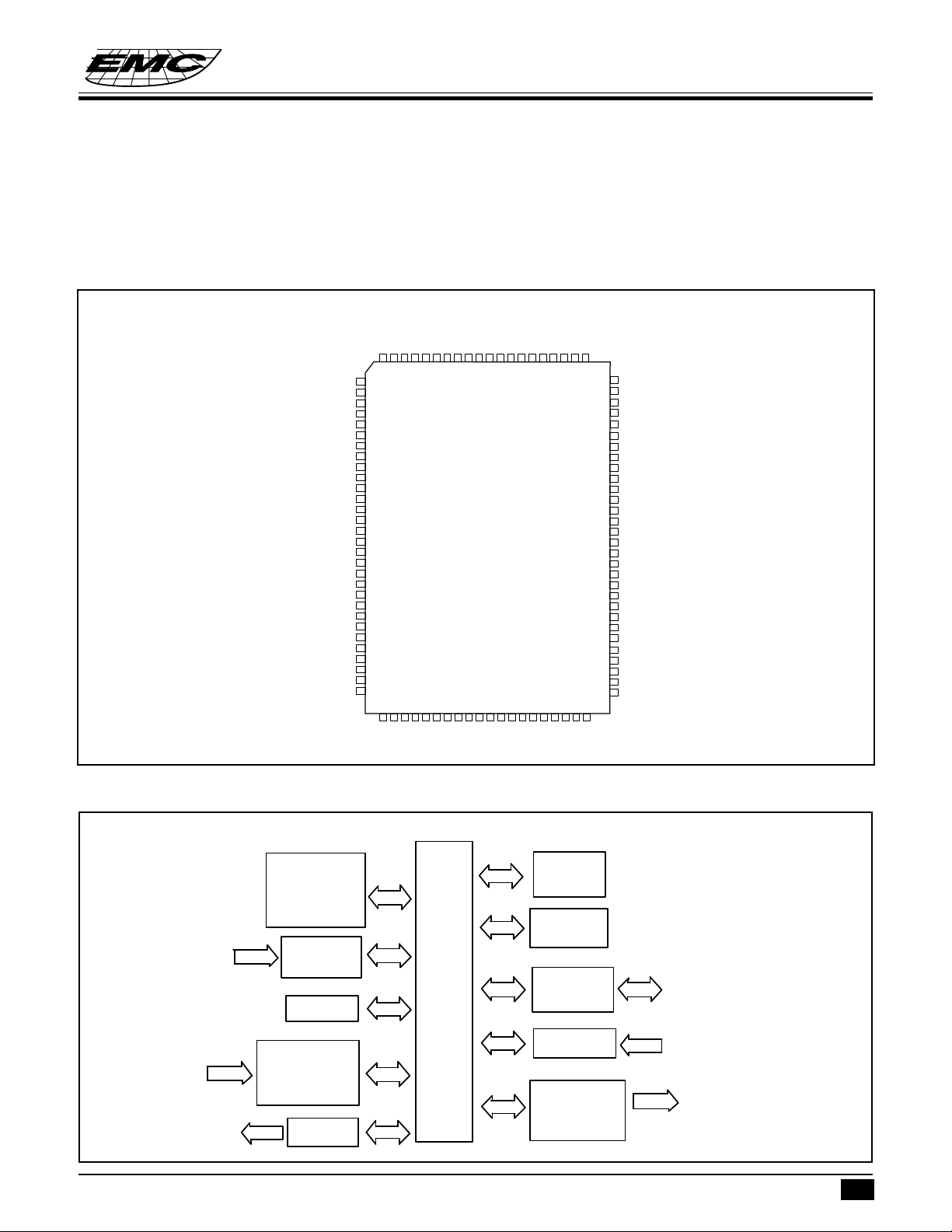

PIN ASSIGNMENTS

SEG59/P9.7

VDD1

SEG56/P9.4

SEG57/P9.5

SEG58/P9.6

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

SEG44/P8.0

SEG45/P8.1

SEG46/P8.2

SEG47/P8.3

SEG48/P8.4

SEG49/P8.5

SEG50/P8.6

SEG51/P8.7

SEG52/P9.0

SEG53/P9.1

SEG54/P9.2

SEG55/P9.3

SEG42

SEF43

TEST

AVSS

DTMF

PLLC

RINGTIME

RDET1

RING

TIP

NC

XIN

XOUT

AVDD

SEG0

SEG1

SEG2

SEG3

SEG4

SEG5

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

SEG13

SEG14

SEG15

SEG16

VDD2

SEG17

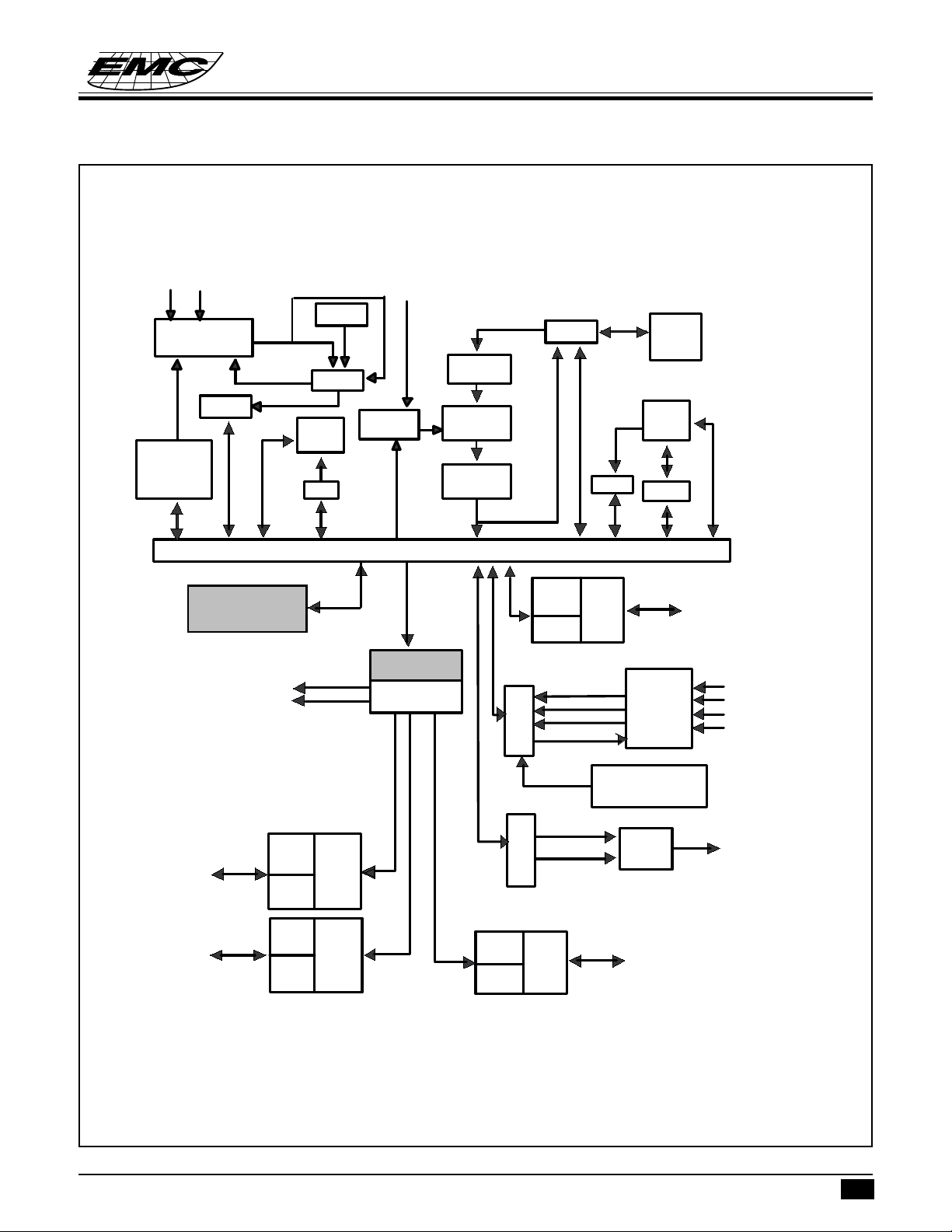

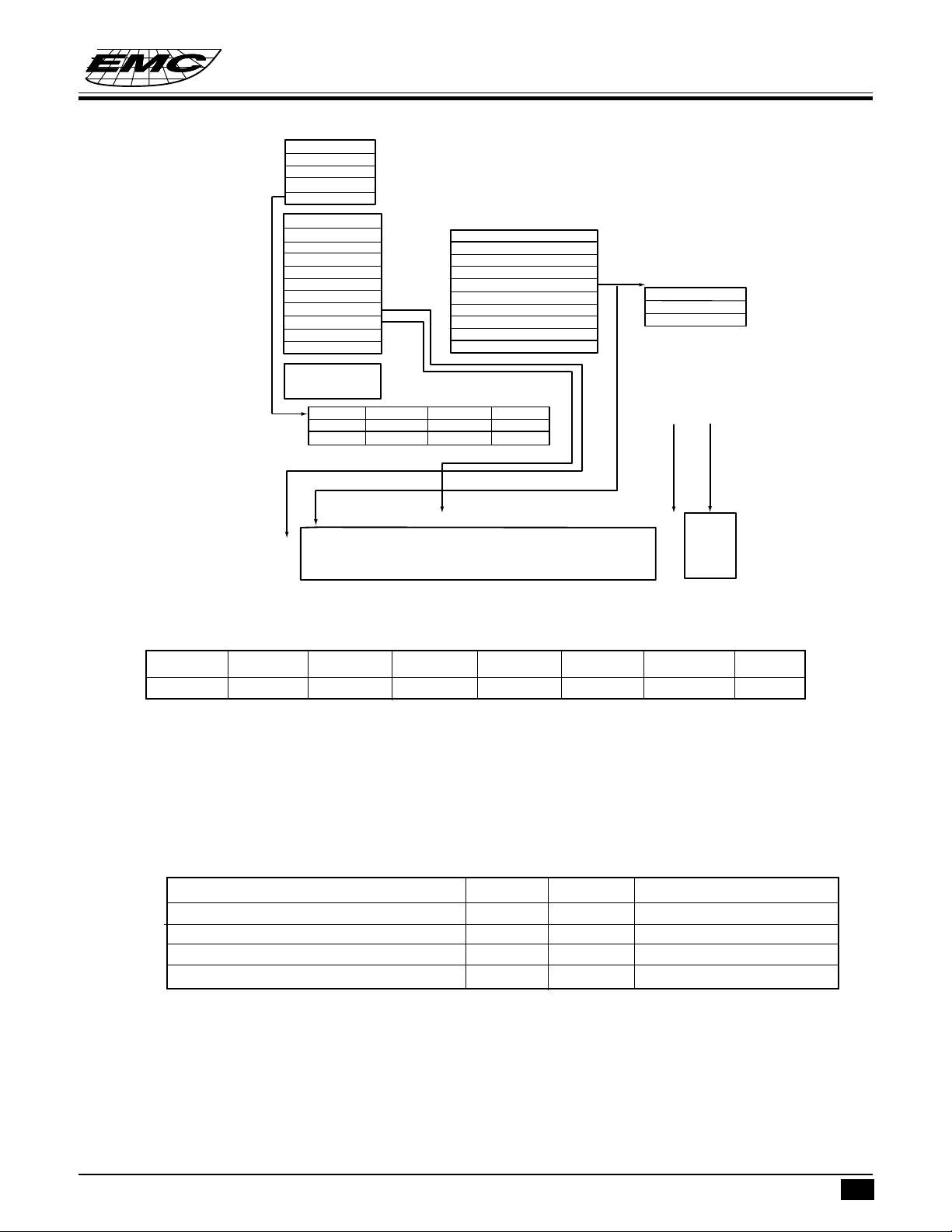

FUNCTIONAL BLOCK DIAGRAM

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

SEG19

SEG18

SEG20

SEG21

SEG22

EM78811

SEG28

SEG27

SEG26

SEG25

SEG24

SEG23

SEG29

SEG30

SEG31

SEG32

SEG33

SEG34

SEG35

COM0

81828384858687888990919293949596979899

50494847464544434241403938373635343332

COM1

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

SEG41

SEG40

SEG39

SEG38

SEG37

SEG36

RESET

P7.7

P7.6

P7.5

P7.4

P7.3/INT3

P7.2/INT2

P7.1/INT1

P7.0/INT0

COM15/P6.7

COM14/P6.6

COM13/P6.5

COM12/P6.4

COM11/P6.3

COM10/P6.2

COM9/P6.1

COM8/P6.0

COM7

COM6

COM5

COM4

COM3

VSS2

COM2

CPU

CLK

FSK

INPUT

TIMING

CONTROL

TIMER

FSK

DEMODULATOR

DTMF

* This specification are subject to be changed without notice.

ROM

RAM

I/O PORT

INPUT PORT

LCD

LATCH

& DRIVER

I/O PORT

INPUT PORT

LCD

OUTPUT

10.12.1998

2

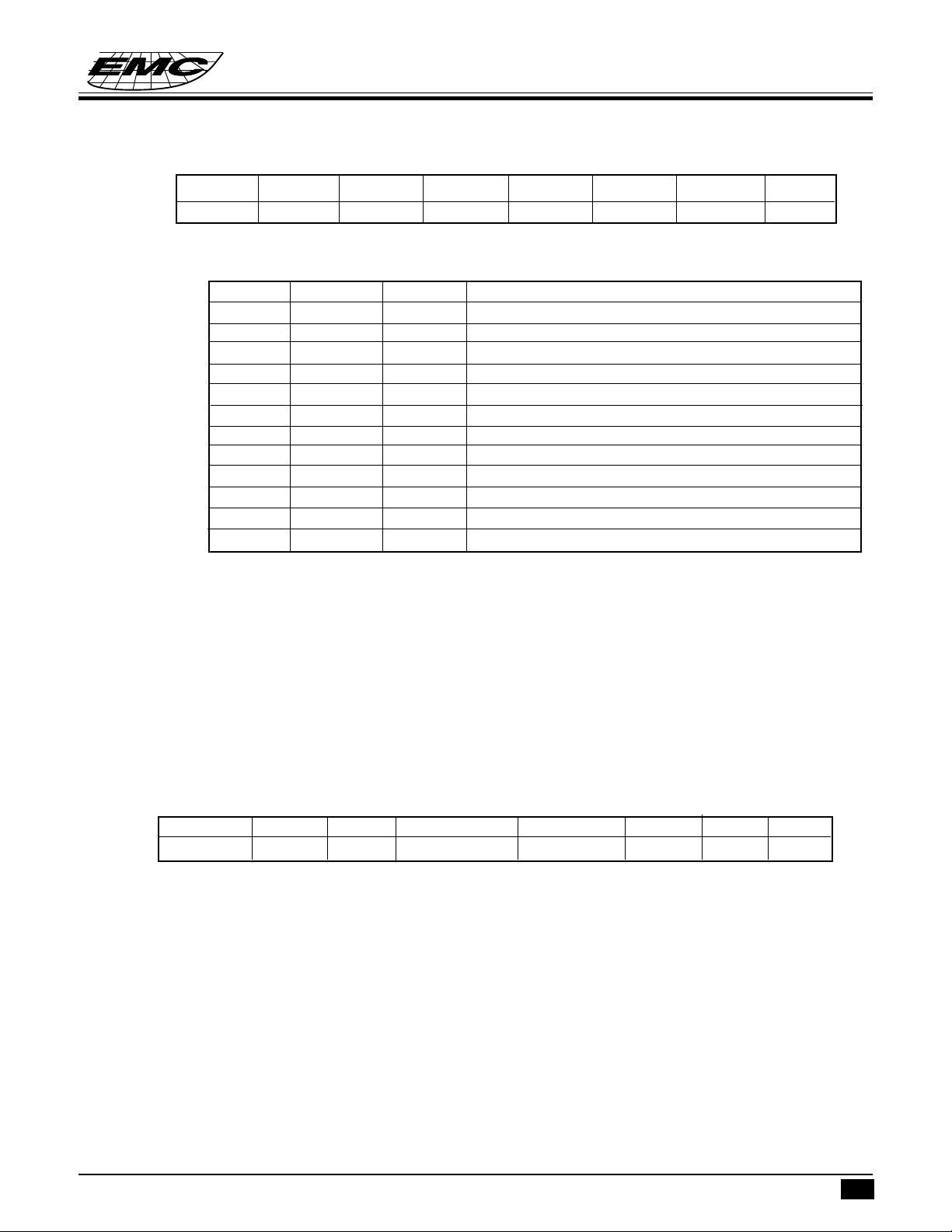

Page 3

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

Xin Xout

Oscillator/Timing

Control

sleep and

wake-up

on I/O ports

Control

WDT Timeout

R1(TCC)

CALLER ID

RAM

COM0˜COM7

SEG0˜SEG35

WDTTimer

Prescaler

RAM

R4

TCC

ROM

Interrupt

Controller

Instruction

register

Instruction

Decoder

DATA & CONTROLL BUS

LCD RAM

LCD Driver

RA

R2

IOC7

R7

Ring det

Carrier det

Data

/FSKPWR

R3

I/O

PORT

Stack

ALU

ACC

FSK

Decoder

P70˜P77

TIP

RING

RING DET1

RING TIME

IOC8

P80˜P87

SEG44˜SEG51

P90˜P97

SEG52˜SEG59

R8

IOC9

R9

I/O

PORT

8

I/O

PORT

9

* This specification are subject to be changed without notice.

IOC6

R6

RB

I/O

PORT

6

Row

Column

low battery

detect

DTMF

P60˜P67

COM8˜COM15

DTMF output

10.12.1998

3

Page 4

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

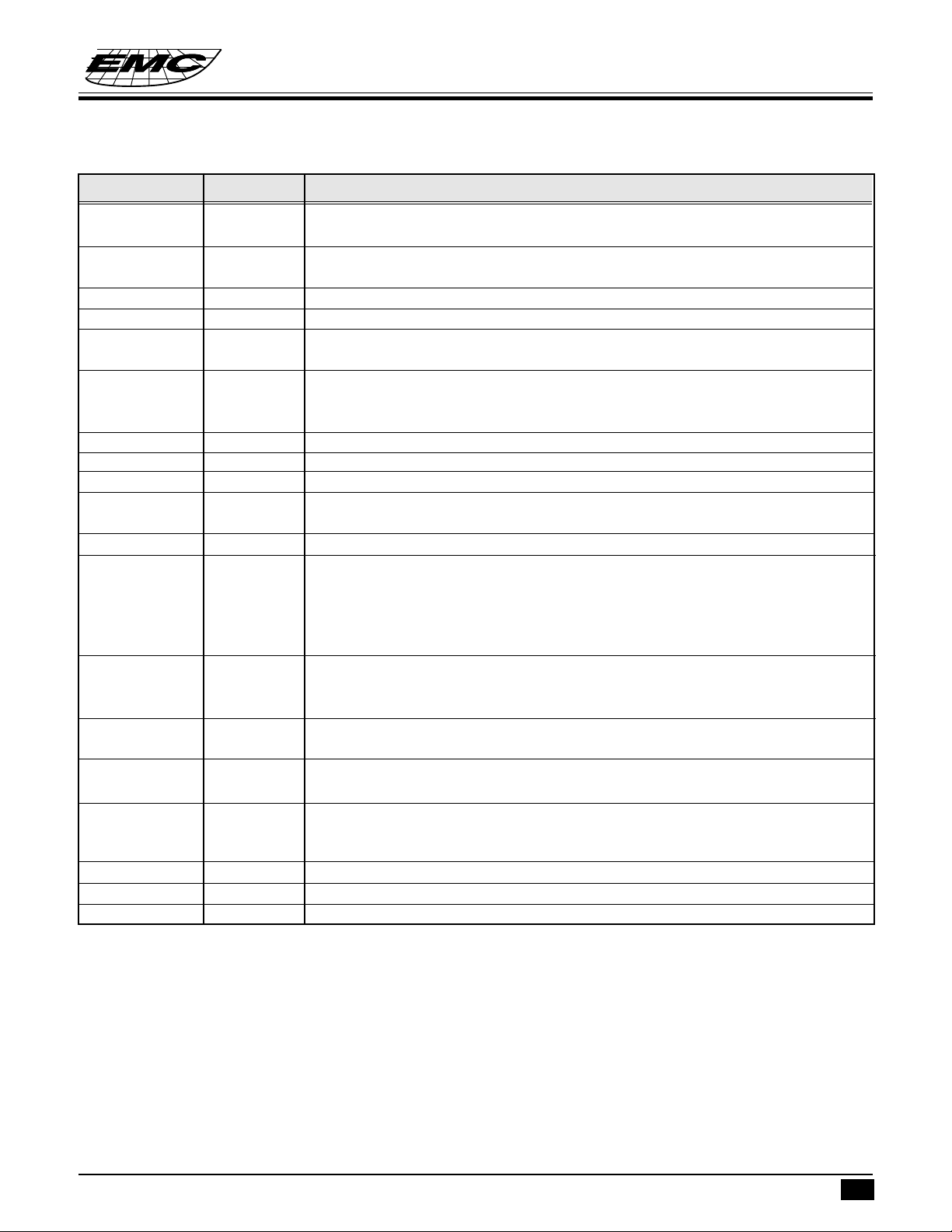

PIN DESCRIPTIONS

Symbol Type Function

VDD1,VDD2 POWER digital power

AVDD analog power

VSS1,VSS2 POWER digital ground

AVSS analog ground

XTin I Input pin for 32.768 kHz oscillator

XTout O Output pin for 32.768 kHz oscillator

COM0..COM7 O

COM8..COM15 O (PORT6) Common driver pins of LCD drivers

SEG0..SEG43 Segment driver pins of LCD drivers

SEG44..SEG51 0 (PORT8)

SEG52..SEG59 O (PORT9) PORT9 AS FUNCTION KEY CAN WAKE UP WATCHDOG.

PLLC I Phase loop lock capacitor, connect a capacitor 0.01µ to 0.047µ with AVSS.

TIP I Should be connected with TIP side of twisted pair lines

RING I Should be connected with TIP side of twisted pair lines

RDET1..RDET 2 I Detect the energy on the twisted pair lines.These two pins coupled to the twisted pair

lines through an attenuating network.

/RING TIME I Determine if the incoming ring is valid. An RC network may be connected to the pin.

INT0 PORT7(0) PORT7(0)~PORT7(3) signal can be interrupt signals.

INT1 PORT7(1)

INT2 PORT7(2)

INT3 PORT7(3)

PORT7(4:7) IO port

P7.0~P7.7 PORT7 PORT 7 can INPUT or OUTPUT port each bit.

Internal Pull high function.

Key scan function. Bit6,7 has open drain function

P6.0~P6.7 PORT6 PORT6 can be INPUT or OUTPUT port each bit.

And shared with common signal.

P8.0~P8.7 PORT8 PORT 8 can be INPUT or OUTPUT port each bit.

And shared with Segment signal.

P9.0~P9.7 PORT9 PORT 9 can be INPUT or OUTPUT port each bit.

And can be set to wake up watch dog timer.

And shared with Segment signal.

TEST I Test pin into test mode , normal low

DTMF O DTMF tone output

RESET I

FUNCTION DESCRIPTION

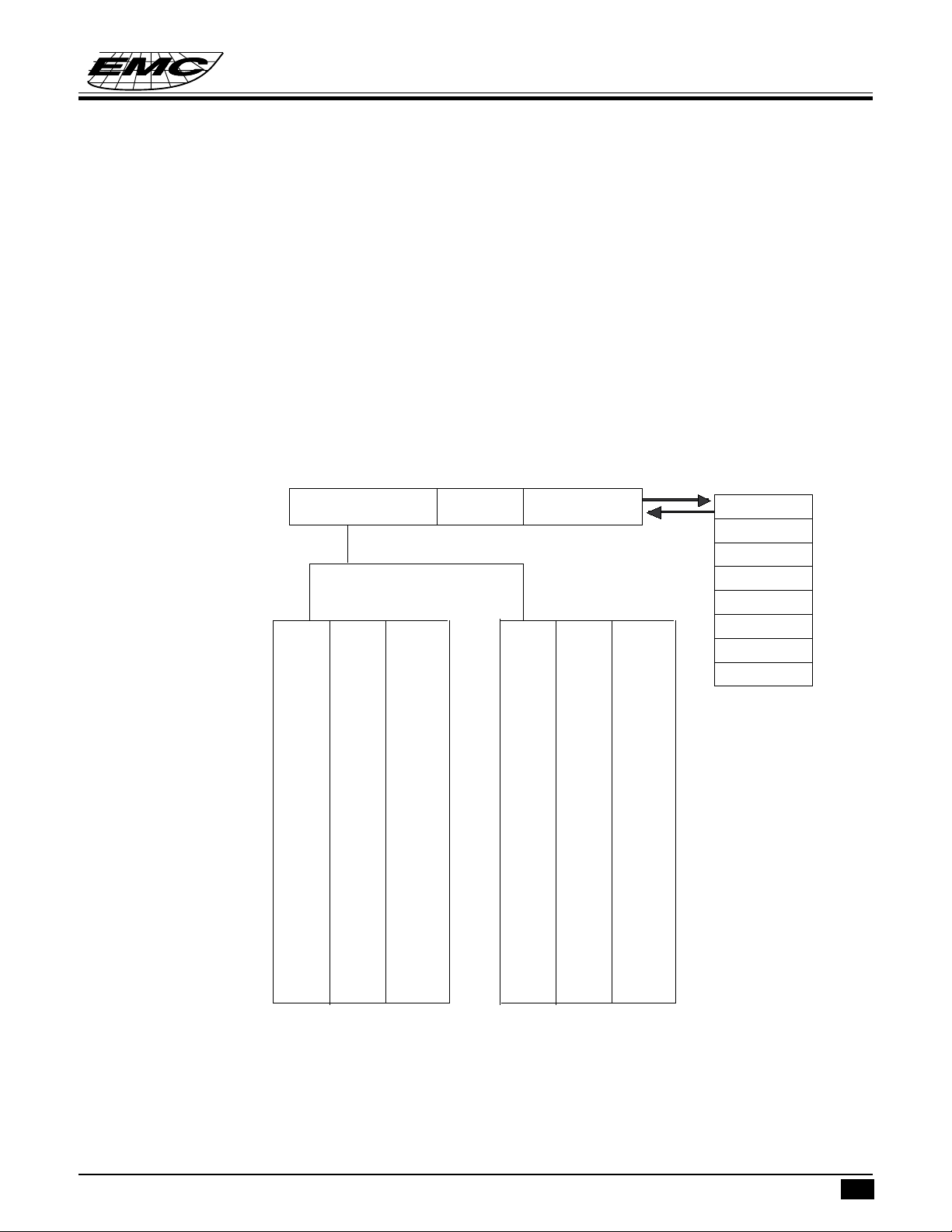

Operational Registers

R0 (Indirect Addressing Register)

* R0 is not a physically implemented register. It is useful as indirect addressing pointer. Any instruction using

R0 as register actually accesses data pointed by the RAM Select Register (R4).

R1 (TCC)

* Increased by an external signal edge applied to TCC , or by the instruction cycle clock Written and read by

the program as any other register.

* This specification are subject to be changed without notice.

10.12.1998

4

Page 5

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

R2 (Program Counter)

* The structure is depicted in Fig. 4.

* Generates 16Kx13 ( 14 on-chip ROM addresses to the relative programming instruction codes.

* "JMP" instruction allows the direct loading of the low 10 program counter bits.

* "CALL" instruction loads the low 10 bits of the PC, PC+1, and then push into the stack.

* "RET'' ("RETL k", "RETI") instruction loads the program counter with the contents at the top of stack.

* "MOV R2,A" allows the loading of an address from the A register to the PC, and the ninth and tenth bits

are cleared to "0''.

* "ADD R2,A" allows a relative address be added to the current PC, and contents of the ninth and tenth bits

are cleared to "0''.

* "TBL" allows a relative address be added to the current PC, and contents of the ninth and tenth bits don't

change. The most significant bit (A10~A13) will be loaded with the content of bit PS0~PS3 in the status

register (R5) upon the execution of a "JMP'', "CALL'', "ADD R2,A'', or "MOV R2,A'' instruction.

CALL

PC

A13 A12 A11 A10

A9 A8

A7~A0

RET

RETL

RETI

Stack 1

Stack 2

Stack 3

Stack 4

Stack 5

1000

2000

Page 8

0000

0000

Page 0

Stack 6

Stack 7

1001

23FF

2400

Page 9

0001

03FF

0400

Page 1

Stack 8

1010

1011

1100

1101

1110

1111

27FF

2800

2CFF

2D00

2FFF

3000

33FF

3400

37FF

3800

3CFF

3D00

3FFF

Page 10

Page 11

Page 12

Page 13

Page 14

Page 15

0010

0011

0100

0101

0110

0111

07FF

0800

0CFF

0D00

0FFF

1000

13FF

1400

1CFF

1D00

1FFF

Fig.4 Program counter organization

17FF

1800

Page 2

Page 3

Page 4

Page 5

Page 6

Page 7

* This specification are subject to be changed without notice.

10.12.1998

5

Page 6

00

01

02

03

04

05

06

07

08

09

0A

0B

0C

0D

0E

0F

10

:

1F

20

:

3F

R0

R1(TCC)

R2(PC)

R3(STATUS)

R4(RSR)

R5(Program Page)

R6(PORT6)

R7(PORT7)

R8(PORT8)

R9(PORT9)

RA(FSK STATUS)

RB(DTMF)

RC(CID ADRESS)

RD(CID DATA)

RE(LCD,WDT,WUE)

RF(INTERRUPT)

16x8

Common

Register

00 BANK0

32X8

REGISTER

01 BANK1

32X8

REGISTER

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

IOC6

IOC7

IOC8

IOC9

IOCA(RAM,IO,PAGE ctl )

IOCB(lcd address )

IOCC(lcd data )

IOCD(PULL HIGH control)

IOCE(IO,Vlcd control )

IOCF(interrupt control)

10 BANK2

32X8

REGISTER

11 BANK3

32X8

REGISTER

IOCB(COUNTER1)

IOCC(COUNTER2)

IOCE(OTHER )

IOCB IOCC

00h

ffH

0001

CALLER RAM

0010

0011

BAND3

BAND4

256X8

256X8

0100

BAND5

256X8

0101

BAND6

256X8

0110

BAND7

256X8

0111

BAND8

256X8

1000

BAND9

256X8

BAND10

0000

BAND1

256X8

BAND2

256X8

:

1001

256X8

00h

78h

:

:

:

LCD RAM

120x8

Fig.5 Data memory configuration

R3 ( Status Register )

76 5432 10

- page - T P Z DC C

• Bit 0 (C) : Carry flag

• Bit 1 (DC) : Auxiliary carry flag

• Bit 2 (Z) : Zero flag

• Bit 3 (P) : Power down bit. Set to 1 during power on or by a “WDTC” command and reset to 0 by a

SLEP” command.

• Bit 4 (T) : Time-out bit. Set to 1 by the “SLEP” and “WDTC” command, or during power up and reset

to 0 by WDT time out.

EVENT T P REMARK

WDT wake up from sleep mode 0 0

WDT time out (not sleep mode) 0 1

/RESET wake up from sleep 1 0

power up 1 1

• Bit 5 : unused

• Bit 6 PAGE : change IOCB~IOCE to another page, 0/1→page0/page1

• Bit 7 : unused

R4 ( RAM Select Register )

• Bit 0 ~ 5 are used to select up to 64 register in the indirect addressing mode.

• Bit 6 ~ 7 determine which bank is actived among the 4 banks.

• See the configuration of the data memory in Fig.5.

* This specification are subject to be changed without notice.

10.12.1998

6

Page 7

R5 (Program Page Select Register)

76543210

- - - - PS3 PS2 PS1 PS0

• Bir0 (PS0) ~ 3 (PS3) Page select bits

Page selects bits

PS3 PS2 PS1 PS0 Program memory page (Address)

0 0 0 0 Page 0 ( 0000 - 03FF )

0 0 0 1 Page 1 ( 0400 - 07FF )

0 0 1 0 Page 2 ( 0800 - 0BFF )

0 0 1 1 Page 3 ( 0C00 - 0FFF )

0 1 0 0 Page 4 (1000 - 13FF )

0 1 0 1 Page 5 ( 1400 - 17FF )

0 1 1 0 Page 6 ( 1800 - 1BFF )

0 1 1 1 Page 7 ( 1C00 - 1FFF )

1 1 1 1 Page 8 ( 2000 - 23FF)

1 1 1 1 Page 9 (2400 - 27FF)

:::;:

1 1 1 1 Page 15 (3C00 - 3FFF)

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

• User can use PAGE instruction to change page. To maintain program page by user. Otherwise, user can use

far jump (FJMP) or far call (FCALL) instructions to program user's code. And the program page is maintained

by EMC's complier. It will change user's program by inserting instructions within program.

• Bit4~7 : unused

R6 ~ R9 (Port 6 ~ Port 9)

• Five 8-bit I/O registers.

RA (FSK Status Register)(bit0,1,2,4 read only))

765 4 3 210

IDLE /358E /LPD /LOW-BAT /FSKPWR DATA /CD /RD

• Bit0 (Read Only) (Ring detect signal)

0/1 : Ring Valid/Ring Invalid

• Bit1(Read Only)(Carrier detect signal)

0/1 : Carrier Valid/Carrier Invalid

• Bit2(Read Only)(FSK demodulator output signal)

Fsk data transmitted in a baud rate 1200 Hz. Data from FSK demodulator when /CD is Low.

• Bit3(read/write)(FSK block power up signal)

1/0 : FSK demodulator block power up/FSK demodulator power down

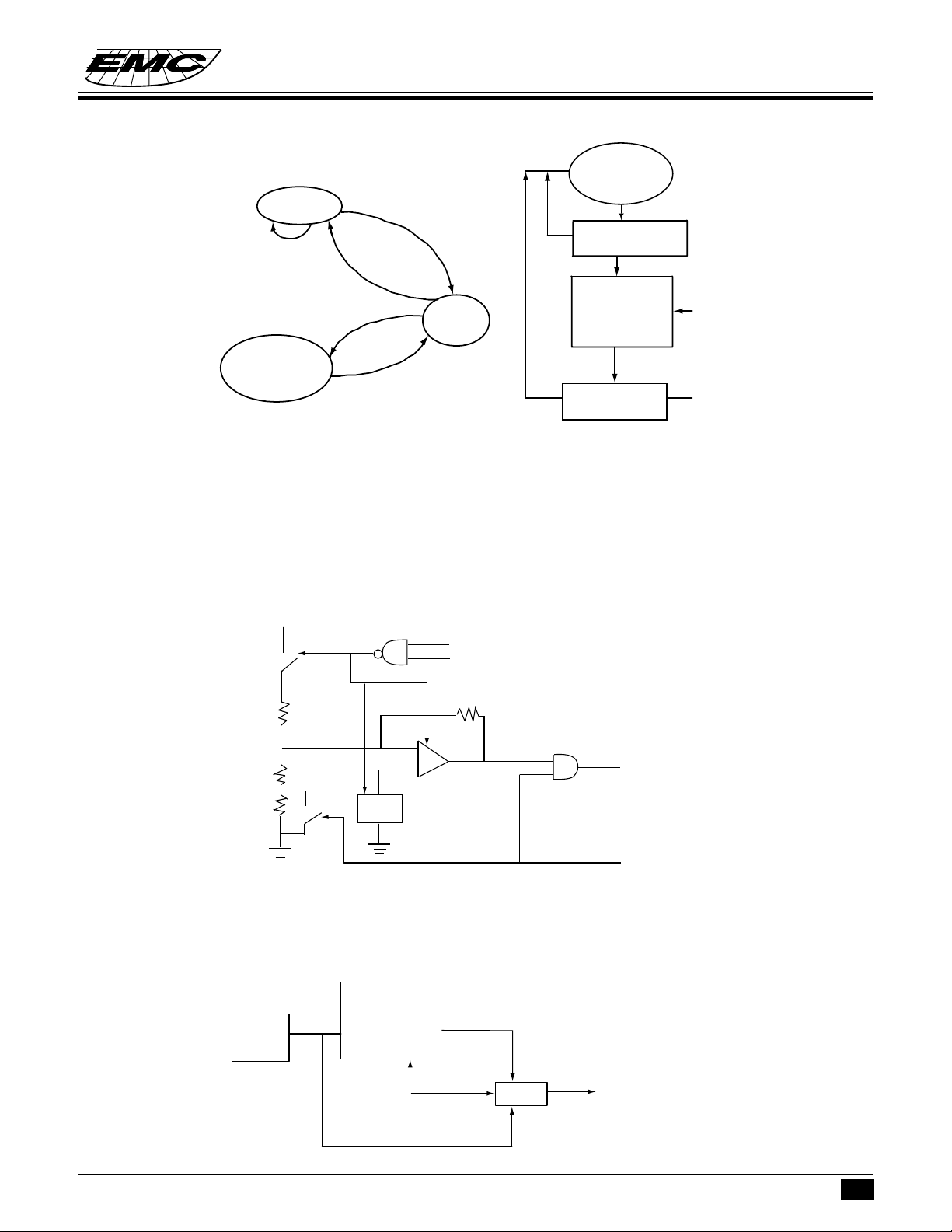

The relation between Bit0 to Bit3 is shown in Fig.6.

* This specification are subject to be changed without notice.

10.12.1998

7

Page 8

/RD and /CD ='1'

/RINGTIME='0'

or EXTERNAL KEYS

PRESSEDsleep mode

/RD and /CD ='1' and

nothing to do for 30

sec , /FSKPWR='0'

/FSKPWR='1'

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

SLEEP MODE

Begin

set /FSKPWR='0'

/RINGTIME ='0'

No

or external keys

pressed

Yes

WAKE UP MODE

8-bit wake up andÁ

wake up

mode

set /FSKPWR='1'

accept data from

FSK decoder

FSK decoder

begin its work

STATE Diagram between 8-bit

and FSK decoder

DATA transfer

DATA transfer

to Micro

/RD and /CD ='1'

Yes

data end and 30

sec nothing to do.

Flow Diagram between 8-bit

and FSK decoder

No

Fig6. The relation between Bit0 to Bit3.

• Bit4(Read Only)(Low battery signal)

0/1 = Battery voltage is low/Normal . If the battery voltage is under 3.6V then sends a ‘0’ signal to RA register

bit4 or sends a '1' signal to this bit.

• Bit5(read/Write)(Low battery detect enable)

0/1 = low battery detect DISABLE/ENABLE. The relation between /LPD,/POVD and /LOW_BAT can see

Fig7.

Vdd

s2

1 on

0 off

1 on

Vref

+

-

/POVD

/LPD

to Low bat

1 on

To reset

s2

1 on

0 off

Fig7. The relation between /LPD,/POVD

• Bit6(read/write)(PLL enable signal)

0/1=DISABLE/ENABLE, The relation between 32.768K and 3.679M can see Fig8.

PLL

32.768K

3.679M

/358E

Fig8. The relation between 32.768K and 3.58K .

* This specification are subject to be changed without notice.

1

switch

0

/LPD

To system clock

10.12.1998

8

Page 9

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

• Bit7 IDLE : Sleep mode selection bit

0/1=sleep mode/IDLE mode. This bit will decide SLEP instruction which mode to go.

These two modes can be waken up by TCC clock or Watch Dog or PORT9 and run from "SLEP" next

instruction.

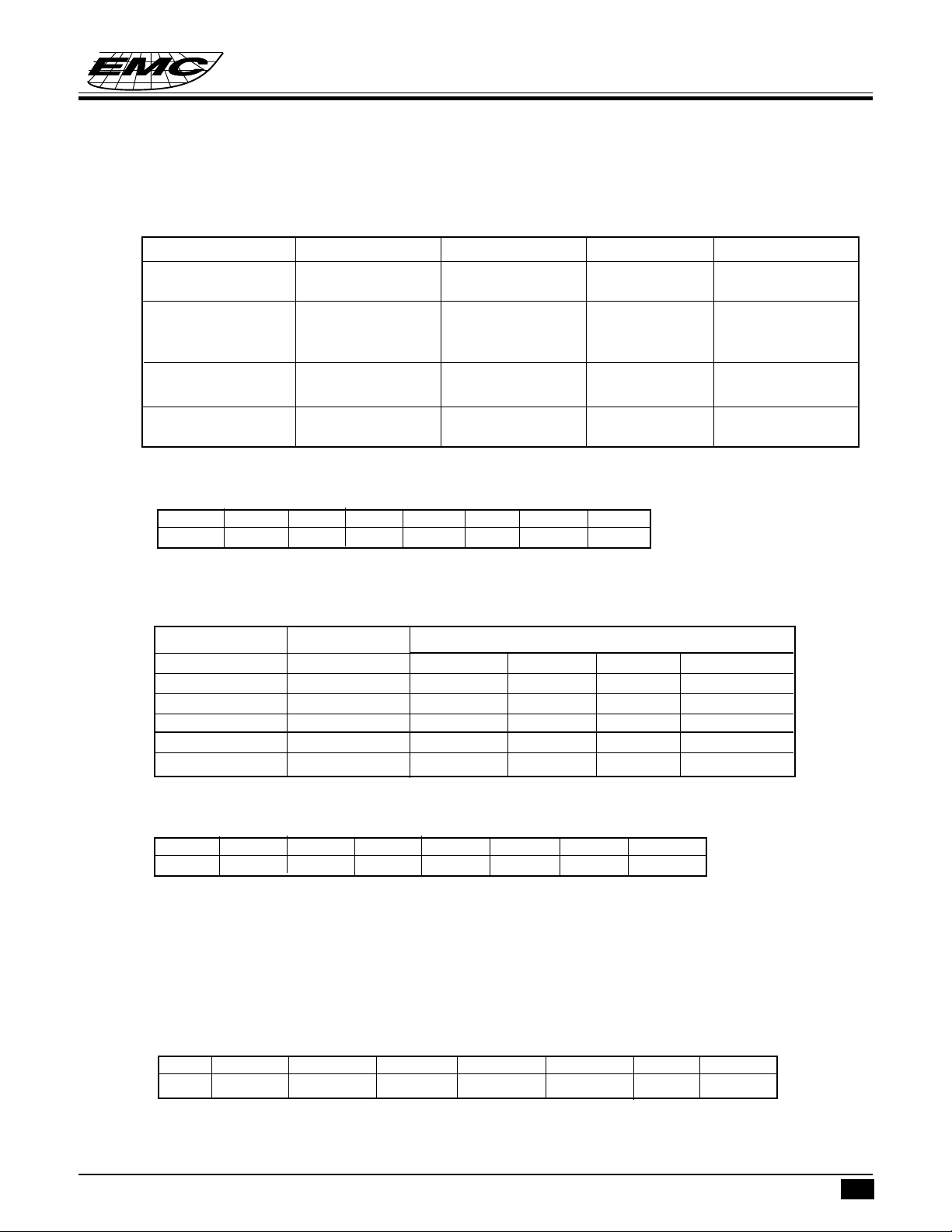

SLEEP moe IDLE mode GREEN mode NORMAL mode

RA(7,6)=(0,0) RA(7,6)=(1,0) RA(7,6)=(x,0) RA(7,6)=(x,1)

+SLEP +SLEP no SLEP no SLEP

TCC time out X Wake-up Interrupt Interrupt

+Interrupt

+Next instruction

WDT time out RESET Wake-up RESET RESET

+Next instruction

Port9 wake-up RESET Wake-up RESET RESET

+Next instruction

RB(DTMF tone row and column register) (read/write)

EM78811

7 6543 210

c7 c6 c5 c4 r3 r2 r1 r0

• Bit 0 - Bit 3 are row-frequency tone.

• Bit 4 - Bit 7 are column-frequency tone.

• Initial RB is equal to high. Bit7~0 are all "1", turn off DTMF power.

bit3~0 Row freq

1110 699.2 Hz 1 2 3 A

1101 771.6 Hz 4 5 6 B

1011 854 Hz 7 8 9 C

0111 940.1 Hz * 0 # D

Column freq 1203 Hz 1331.8 Hz 1472 Hz 1645.2 Hz

bit 7~4 1110 1101 1011 0111

RC(CALLER ID address)(read/write)

765 432 1 0

CIDA7 CIDA6 CIDA5 CIDA4 CIDA3 CIDA2 CIDA1 CIDA0

• Bit 0 ~ Bit 7 select CALLER ID RAM address up to 256.

RD(CALLER ID RAM data)(read/write)

• Bit 0 ~ Bit 8 are CALLER ID RAM data transfer register.

User can see IOCA register how to select CID RAM banks.

RE(LCD Driver,WDT Control)(read/write)

76 5 4 3 2 1 0

- /WDTE /WUP9H /WUP9L /WURING LCD_C2 LCD_1 LCD_M

• Bit0 (LCD_M):LCD_M decides the methods, including duty, bias, and frame frequency.

• Bit1~Bit2 (LCD_C#):LCD_C# decides the LCD display enable or blanking.

change the display duty must set the “LCD_C2,LCD_C1” to “00”.

* This specification are subject to be changed without notice.

10.12.1998

9

Page 10

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

LCD_C2, LCD_C1 LCD Display Control LCD_M duty bias

0 0 change duty 0 1/16 1/4

Disable (turn off LCD) 1 1/8 1/4

0 1 Blanking : :

1 1 LCD display enable : :

• Bit3 (/WURING, RING Wake Up Enable): used to enable the wake-up function of /RINGTIME input pin.

(1/0=enable/disable)

• Bit4 (/WUP9L, PORT9 low nibble Wake Up Enable): used to enable the wake-up function of low nibble in

PORT9.(1/0=enable/disable)

• Bit5 (/WUP9H, PORT9 high nibble Wake Up Enable): used to enable the wake-up function of high nibble

in PORT9.(1/0=enable/disable)

• Bit6 (/WDTE,Watch Dog Timer Enable)

Control bit used to enable Watchdog timer.

(1/0=enable/disable)

The relation between Bit3 to Bit6 can see the diagram 9.

• Bit7 unused

/WURING

/RINGTIME

/WUP9L

PORT9(3:0)

/WUP9H

PORT9(7:4)

/WDTE

/WDTEN 1/0=enable/disable

fig.9 Wake up function and control signal

RF (Interrupt Status Register)

76543210

INT3 FSKDATA C8_2 C8_1 INT2 INT1 INT0 TCIF

*“1” means interrupt request, “0” means non-interrupt

* Bit 0 (TCIF) TCC timer overflow interrupt flag. Set when TCC timer overflows.

* Bit 1 (INT0) external INT0 pin interrupt flag .

* Bit 2 (INT1) external INT1 pin interrupt flag .

* Bit 3 (INT2) external INT2 pin interrupt flag .

* Bit 4 (C8_1) internal 8 bit counter interrupt flag .

* Bit 5 (C8_2) internal 8 bit counter interrupt flag .

* Bit 6 (FSKDATA) FSK data interrupt flag.

* Bit 7 (INT3) external INT3 pin interrupt flag.

* High to low edge trigger , Refer to the Interrupt subsection.

* IOCF is the interrupt mask register. User can read and clear.

R10~R3F (General Purpose Register)

• R10~R3F (Banks 0~3) all are general purpose registers.

* This specification are subject to be changed without notice.

10.12.1998

10

Page 11

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

Special Purpose Registers

A (Accumulator)

• Internal data transfer, or instruction operand holding

• It’s not an addressable register.

CONT (Control Register)

76543210

- - TS PAB PSR2 PSR1 PSR0

Bit 0 (PSR0) ~ Bit 2 (PSR2) TCC/WDT prescaler bits.

PSR2 PSR1 PSR0 TCC Rate WDT Rate

0 0 0 1:2 1:1

0 0 1 1:4 1:2

0 1 0 1:8 1:4

0 1 1 1:16 1:8

1 0 0 1:32 1:16

1 0 1 1:64 1:32

1 1 0 1:128 1:64

1 1 1 1:256 1:128

EM78811

Bit 3 ( PAB ) Prescaler assignment bit

0/1 : TCC/WDT

Bit 4 : unsed

Bit 5 ( TS ) : TCC signal source

0 : internal instruction cycle clock

1 : 16.38KHz

Bit 6: unused

Bit 7: unused

• CONT register is readable and writable

IOC6 ~ IOC9 (I/O Port Control Register)

• Five I/O direction control registers.

• "1" put the relative I/O pin into high impedance, while "0" put the relative I/O pin as output.

• User can see IOCB register how to switch to normal I/O port.

* This specification are subject to be changed without notice.

10.12.1998

11

Page 12

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

IOCA (CALLER ID RAM,IO ,PAGE Control Register)(read/write,initial "00000000")

76543210

P8SH P8SL - CALL_4 CALL_3 CALL_2 CALL_1 0

• Bit4~Bit1:"0000" to "1001" are ten blocks of CALLER ID RAM area. User can use 2.5K RAM with RC

ram address.

• Bit 5 unused

• Bit6: port8 low nibble switch, 0/1= normal I/O port/SEGMENToutput .

• Bit7: port8 high nibble switch , 0/1= normal I/O port/SEGMENT output.

IOCB (LCD ADDRESS)

PAGE0 : Bit6 ~ Bit0 = LCDA6 ~ LCDA0

The LCD display data is stored in the data RAM . The relation of data area and COM/SEG pin is as below:

COM15~COM8 COM7~COM0

40H (Bit15~Bit8) 00H (Bit7~Bit0) SEG0

41H 01H SEG1

:: :

:: :

7BH 3BH SEG59

7CH 3CH Empty

7DH 3DH Empty

7EH 3EH Empty

7FH 3FH Empty

PAGE1 : 8 bit up-counter (COUNTER1) preset and read out register . ( write = preset ) . After a interruption

, it will count from "00".

IOCC (LCD DATA)

PAGE0 : Bit7 ~ Bit0 = LCD RAM data register

PAGE1 : 8 bit up-counter (COUNTER2) preset and read out register . ( write = preset) After a interruption

, it will count from "00".

IOCD (Pull-high Control Register)

PAGE0:

76543210

PH7 PH6 PH5 PH4 PH3 PH2 PH1 PH0

• Bit 0 ~ 7 (/PH#) Control bit used to enable the pull-high of PORT7(#) pin.

1: Enable internal pull-high

0: Disable internal pull-high

* This specification are subject to be changed without notice.

10.12.1998

12

Page 13

EM78811

VDD

V1

V2

V3

V4

VLCD

GND

VDD

V1

V2

V3

V4

VLCD

GND

30µs

seg

com2

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

IOCE (Bias,PLL Control Register)

PAGE0 :

76543210

P9SH P9SL P6S Bias3 Bias2 Bias1 PHR SC

• Bit 0 : SC(SCAN KEY signal) 0/1=disable/enable. once you enablethis bit, all of the LCD signal will have

a low pulse during a common period. This pulse has 30µs width. Please use the procedure to implement the

key scan function.

a. set port7 as input port.

b. set IOCD page0 port7 pull high.

c. enable scan key signal. And enable interruption.

d. Once push a key. Set RA(6)=1 and switch to normal mode.

e. Blank LCD. Disable scan key signal.

f. Set P6S=0. Port6 sent probe signal to port7 nd read port7. Get the key.

g. Note!! A probe signal should be delay a instruction at least to another probe signal.

h. Set P6S=1. Port6 as LCD signal. Enable LCD.

P63

KEY5

KEY1

KEY2

P62

KEY3

P61

KEY4

P60

P73 P72 P71 P70

Fig10. Key scan circuit

Fig11. Key scan signal

* This specification are subject to be changed without notice.

10.12.1998

13

Page 14

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

• Bit 1 :PORT7 PULL HIGH register option. Please use defaut value.

• Bit 2~4 (Bias1~Bias3) Control bits used to choose LCD operation voltage.

LCD operate voltage Vop (VDD 5V) VDD=5V

000 0.60VDD 3.0V

001 0.66VDD 3.3V

010 0.74VDD 3.7V

011 0.82VDD 4.0V

100 0.87VDD 4.4V

101 0.93VDD 4.7V

110 0.96VDD 4.8V

111 1.00VDD 5.0V

• Bit5:port6 switch , 0/1= normal I/O port/COMMON output

• Bit6:port9 low nibble switch , 0/1= normal I/O port/SEGMENT output . Bit7:port9 high nibble switch

PAGE1 :

76543210

OD7 OD6 C2S C1S PSC1 PSC0 CDRD -

• Bit0: unused

• Bit1: cooked data or raw data select bit , 0/1 ==> cooked data/raw data

• Bit3~Bit2: counter1 prescaler , reset=(0,0)

(PSC1,PSC0) = (0,0)=>1:1 , (0,1)=>1:2 , (1,0)=>1:4 , (1,1)=>1:8

• Bit4:counter1 source , (0/1)=(32768Hz/3.679MHz if enable) scale=1:1

• Bit5:counter2 source , (0/1)=(32768Hz/3.679MHz if enable) scale=1:1

• Bit6: PORT7(6) open drain control, 0/1=disable/enable

• Bit7: PORT7(7) open drain control, 0/1=disable/enable

IOCF (Interrupt Mask Register)

7 6 543210

INT3 FSKDATA C8-2 C8-1 INT2 INT1 INT0 TCIF

• Bit 0 ~ 7 interrupt enable bit.

0: disable interrupt

1: enable interrupt

• IOCF Register is readable and writable.

TCC/WDT Prescaler

There is an 8-bit counter available as prescaler for the TCC or WDT. The prescaler is available for the TCC only

or WDT only at the same time.

• An 8 bit counter is available for TCC or WDT determined by the status of the bit 3 (PAB) of the CONT register.

• See the prescaler ratio in CONT register.

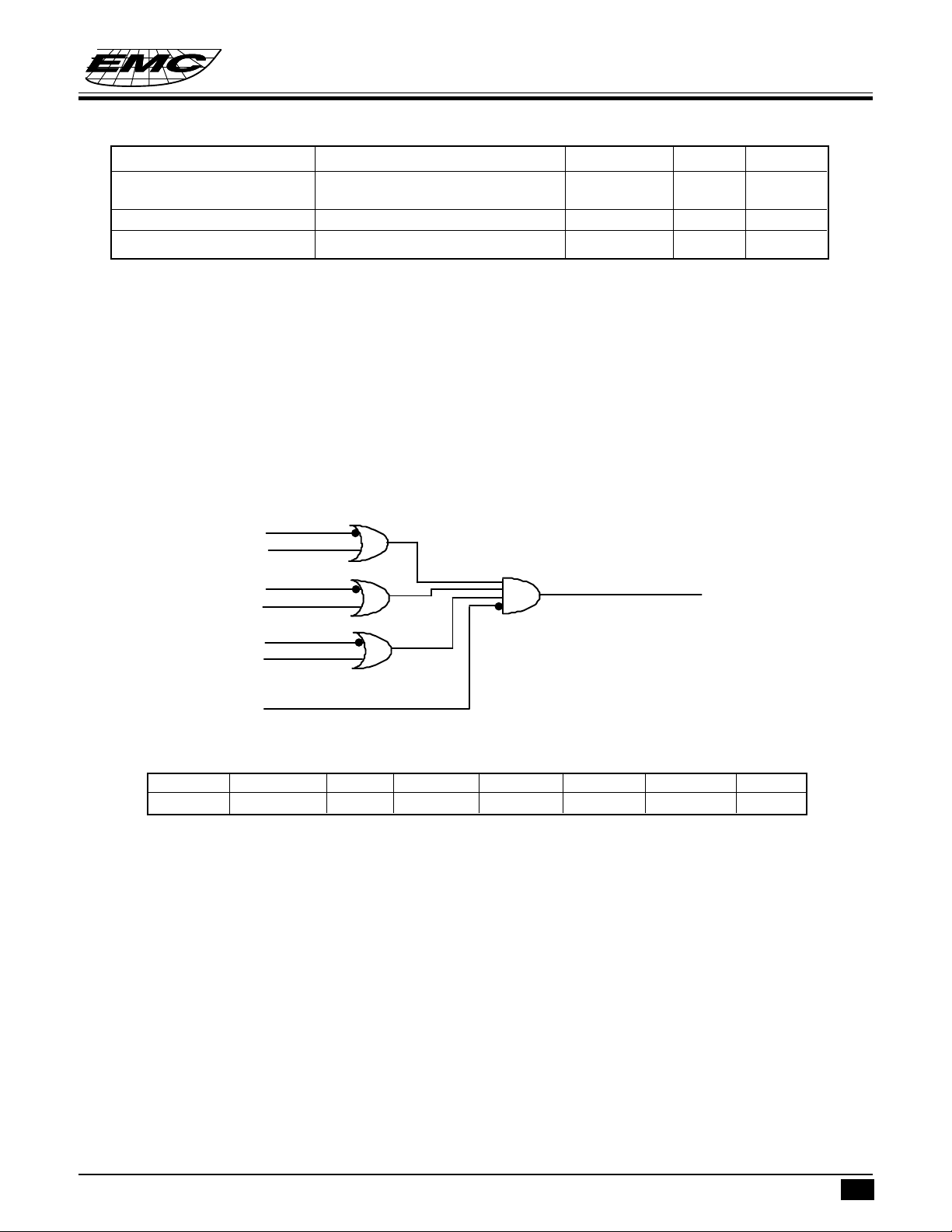

• Fig. 12 depicts the circuit diagram of TCC/WDT.

• Both TCC and prescaler will be cleared by instructions which write to TCC each time.

• The prescaler will be cleared by the WDTC and SLEP instructions, when assigned to WDT mode.

• The prescaler will not be cleared by the SLEP instruction, when assigned to TCC mode.

* This specification are subject to be changed without notice.

10.12.1998

14

Page 15

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

TCC

(16.38KHz CLK)

CLK(=Fosc/2)

TE

WDT

WDTE

0

M

1

U

X

TS

0

1

M

U

X

PAB

1

0

M

U

X

PAB

8-bit Counter

8-to-1 MUX

WDT timeout

SYNC

2 cycle

MUX

Fig. 12 Block diagram of TCC WDT

Data Bus

TCC(R1)

TCC overflow interrupt

PSR0~PSR2

PAB

I/O Ports

The I/O registers, Port 6 ~ Port 9, are bi-directional tri-state I/O ports. Port 7 can be pulled-high internally by

software control. The I/O ports can be defined as “input” or “output” pins by the I/O control registers (IOC6 ~

IOC9 ) under program control. The I/O registers and I/O control registers are both readable and writable. The

I/O interface circuit is shown in Fig.13. Port 7 bit6 and bit7 can be open drain.

PCRD

PR

D

Q

PORT

CLK

Q

CL

PR

Q

CLK

Q

CL

0

M

U

1

X

PCWR

D

PDWR

PDRD

IOD

Fig. 13 The circuit of I/O port and I/O control register

* This specification are subject to be changed without notice.

10.12.1998

15

Page 16

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

RESET and Wake-up

The RESET can be caused by

(1) Power on reset, or Voltage detector

(2) WDT timeout. (if enabled and in GREEN or NORMAL mode)

Note that only Power on reset, or only Voltage detector in Case(1) is enabled in the system by CODE Option bit.

If Voltage detector is disabled, Power on reset is selected in Case (1). Refer to Fig. 14

V

DD

Oscillator

DQ

CLK

CLR

CLK

.

Option

WDTE

Code

Power-on

Reset

Voltage

Detector

/Enable

1

0

WDT

M

U

X

18 ms

RESET

Fig. 14 Block diagram of Reset of controller

Once the RESET occurs, the following functions are performed.

• The oscillator is running, or will be started.

• The Program Counter (R2) is set to all “0”.

• When power on, the upper 3 bits of R3 and the upper 2 bits of R4 are cleared.

• The Watchdog timer and prescaler are cleared.

• The Watchdog timer is disabled.

• The CONT register is set to all “1”

• The other register (bit7. . bit0)

R5 = "00000000"

R6 = PORT IOC6 = "11111111"

R7 = PORT IOC7 = "11111111"

R8 = PORT IOC8 = "11111111"

R9 = PORT IOC9 = "11111111"

RA = "000x0xxx IOCA = "00000000"

RB = "11111111" IOCB = "00000000" Page1 IOCB = "00000000"

RC = "00000000" IOCC = "0xxxxxxx" Page1 IOCC = "00000000"

RD = "xxxxxxxx" IOCD = "00000000"

RE = "00000000" IOCE = "00000000" Page1 IOCE = "00000000"

RF = "00000000" IOCF = "00000000"

* This specification are subject to be changed without notice.

10.12.1998

16

Page 17

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

RA(7)=0 SLEEP mode

RA(7,6) Sleep IDLE Green Normal

0 0+SLEEP 1 0+SLEEP x 0 No Slep x 1 No slep

TCC x Wakeup int int

+int

+Next ins

WDT RESET wakeup RESET RESET

Next ins

Port 9 RESET wakeup RESET RESET

wakeup Next ins

X: No function

The controller can be awakened from SLEEP mode or IDLE mode (execution of “SLEP” instruction, named as

SLEEP MODE or IDLE mode controllered by RA bit 7) by (1) TCC time out (2)WDT time-out (if enabled) or,

(3) external input at PORT9 (4) RINGTIME pin. The four cases will cause the controller wake up and run from

next instruction in IDLE mode, reset in SLEEP mode. After wakeup, user should control WATCH DOG in case

of reset in GREEN mode or NORMAL mode. The last three should be open RE register before into SLEEP mode

or IDLE mode. The first one case should set a flag in IOCF bit0. After time-out, it will go to address 0x08, then

return to next instruction.

Interrupt

The CALLER ID IC has internal interrupts which are falling edge triggered, as followed : TCC timer overflow

interrupt (internal) , two 8-bit counters overflow interrupt .

If these interrupt sources change signal from high to low , then RF register will generate ‘1’ flag to corresponding

register if you enable IOCF register.

RF is the interrupt status register which records the interrupt request in flag bit. IOCF is the interrupt mask

register. Global interrupt is enabled by ENI instruction and is disabled by DISI instruction. When one of the

interrupts (when enabled) generated, will cause the next instruction to be fetched from address 008H. Once in

the interrupt service routine the source of the interrupt can be determined by polling the flag bits in the RF register.

The interrupt flag bit must be cleared in software before leaving the interrupt service routine and enabling

interrupts to avoid recursive interrupts.

There are four external interrupt pins including INT0 , INT1 , INT2 , INT3 . The INT0 to INT3 sent to the different

interrupt flag . And three internal counter interrupt available.

External interrupt INT0 , INT1 , INT2 , INT3 signals are from PORT7 bit0 to bit3 . If IOCF is enable then these

signal will cause interrupt , or these signals will be treated as general input data .

After resetting, the next instruction will be fetched from address 000H, and the software interrupt is 001H and

the hardware interrupt is 008H.

TCC will go to address 0x08 in GREEN mode or NORMAL mode after time out. And it will run next instruction

from "SLEP" instruction. These two cases will set a RF flag.

* This specification are subject to be changed without notice.

10.12.1998

17

Page 18

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

Instruction Set

(1). Every bit of any register can be set, cleared, or tested directly.

(2). The I/O register can be regarded as general register. That is, the same instruction can operates on I/O

register.

The symbol “R” represents a register designator which specifies which one of the 64 registers (including

operational registers and general purpose registers) is to be utilized by the instruction. Bits 6 and 7 in R4

determine the selected register bank. “b’’ represents a bit field designator which selects the number of the bit,

located in the register “R’’, affected by the operation. “k’’ represents an 8 or 10-bit constant or literal value.

INSTRUCTION BINARY HEX MNEMONIC OPERATION STATUS

AFFECTED

0 0000 0000 0000 0000 NOP No Operation None

0 0000 0001 0001 0001 DAA Decimal Adjust A C

0 0000 0000 0010 0002 CONTW A → CONT None

0 0000 0000 0011 0003 SLEP 0 → WDT, Stop oscillator T,P

0 0000 0000 0100 0004 WDTC 0 → WDT T,P

0 0000 0000 rrrr 000r IOW R A → IOCR None

0 0000 0001 0000 0010 ENI Enable Interrupt None

0 0000 0001 0001 0011 DISI Disable Interrupt None

0 0000 0001 0010 0012 RET [Top of Stack] → PC None

0 0000 0001 0011 0013 RETI [Top of Stack] → PC

Enable Interrupt None

0 0000 0001 0100 0014 CONTR CONT → A None

0 0000 0001 rrrr 001r IOR R IOCR → A None

0 0000 0010 0000 0020 TBL R2+A → R2 bits 9,10

do not clear Z,C,DC

0 0000 01rr rrrr 00rr MOV R,A A → R None

0 0000 1000 0000 0080 CLRA 0 → AZ

0 0000 11rr rrrr 00rr CLR R 0 → RZ

0 0001 00rr rrrr 01rr SUB A,R R-A → A Z,C,DC

0 0001 01rr rrrr 01rr SUB R,A R-A → R Z,C,DC

0 0001 10rr rrrr 01rr DECA R R-1 → AZ

0 0001 11rr rrrr 01rr DEC R R-1 → RZ

0 0010 00rr rrrr 02rr OR A,R A∨R→ AZ

0 0010 01rr rrrr 02rr OR R,A A∨R→ RZ

0 0010 10rr rrrr 02rr AND A,R A & R → AZ

0 0010 11rr rrrr 02rr AND R,A A & R → RZ

0 0011 00rr rrrr 03rr XOR A,R A ⊕ R → AZ

0 0011 01rr rrrr 03rr XOR R,A A ⊕ R → RZ

0 0011 10rr rrrr 03rr ADD A,R A + R → A Z,C,DC

0 0011 11rr rrrr 03rr ADD R,A A + R → R Z,C,DC

0 0100 00rr rrrr 04rr MOV A,R R → AZ

0 0100 01rr rrrr 04rr MOV R,R R → RZ

0 0100 10rr rrrr 04rr COMA R /R → AZ

0 0100 11rr rrrr 04rr COM R /R → RZ

0 0101 00rr rrrr 05rr INCA R R+1 → AZ

0 0101 01rr rrrr 05rr INC R R+1 → RZ

0 0101 10rr rrrr 05rr DJZA R R-1 → A, skip if zero None

R(0) → C, C → A(7) C

* This specification are subject to be changed without notice.

10.12.1998

18

Page 19

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

INSTRUCTION BINARY HEX MNEMONIC OPERATION STATUS

AFFECTED

0 0101 11rr rrrr 05rr DJZ R R-1 → R, skip if zero None

0 0110 00rr rrrr 06rr RRCA R R(n) → A(n-1)

0 0110 01rr rrrr 06rr RRC R R(n) → R(n-1)

R(0) → C, C → R(7) C

0 0110 10rr rrrr 06rr RLCA R R(n) → A(n+1)

R(7) → C, C → A(0) C

0 0110 11rr rrrr 06rr RLC R R(n) → R(n+1)

R(7) → C, C → R(0) C

0 0111 00rr rrrr 07rr SWAPA R R(0-3) → A(4-7)

R(4-7) → A(0-3) None

0 0111 01rr rrrr 07rr SWAP R R(0-3) ↔ R(4-7) None

0 0111 10rr rrrr 07rr JZA R R+1 → A, skip if zero None

0 0111 11rr rrrr 07rr JZ R R+1 → R, skip if zero None

0 100b bbrr rrrr 0xxx BC R,b 0 → R(b) None

0 101b bbrr rrrr 0xxx BS R,b 1 → R(b) None

0 110b bbrr rrrr 0xxx JBC R,b if R(b)=0, skip None

0 111b bbrr rrrr 0xxx JBS R,b if R(b)=1, skip None

1 00kk kkkk kkkk 1kkk CALL k PC+1 → [SP]

(Page, k) → PC None

1 01kk kkkk kkkk 1kkk JMP k (Page, k) → PC None

1 1000 kkkk kkkk 18kk MOV A,k k → A None

1 1001 kkkk kkkk 19kk OR A,k A ⁄ k → AZ

1 1010 kkkk kkkk 1Akk AND A,k A & k → AZ

1 1011 kkkk kkkk 1Bkk XOR A,k A ⊕ k → AZ

1 1100 kkkk kkkk 1Ckk RETL k k → A, [Top of Stack] → PC None

1 1101 kkkk kkkk 1Dkk SUB A,k k-A → A Z,C,DC

1 1110 0000 0001 1E01 INT PC+1 → [SP]

001H → PC

1 1110 1000 kkkk 1E8k PAGE k K→R5 None

1 1111 kkkk kkkk 1Fkk ADD A,k k+A → A Z,C,DC

CODE Option Register

The CALLER ID IC has one CODE option register which is not part of the normal program memory. The option

bits cannot be accessed during normal program execution.

76543210

------/POVD MCLK

Bit 0 : main clock selection, 0/1=3.68MHz/1.84MHz

Bit 1 ( /POVD ) : Power on voltage detector.

0 : enable

1 : disable

* This specification are subject to be changed without notice.

10.12.1998

19

Page 20

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

/POVD 2.2V reset power on 3.6V detect no 3.6V detect control sleep mode

reset reset by RA(5) current

1 no yes yes yes 1µA

0 yes yes yes yes 20µA

Bit 2~7 : unused, must be "0"s.

EM78811

* This specification are subject to be changed without notice.

10.12.1998

20

Page 21

FSK FUNCTION

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

Tip

Ring

Ring det1

/Ring Time

Ring

Det

Circuit

Band Pass

Filter

OSC in

OSC out

FSK

demodul

Power

Up

Data Valid

Energy Det

Circuit

/FSKPWR

CLOCK

DATA OUT

/CD

/RD

Fig15. FSK Block Diagram

Function Descriptions

The CALLER ID IC is a CMOS device designed to support the Caller Number Deliver feature which is offered

by the Regional Bell Operating Companies.The FSK block comprises two paths: the signal path and the ring

indicator path. The signal path consist of an input differential buffer,a band pass filter, an FSK demodulator and

a data valid with carrier detect circuit. The ring detector path includes a clock generator, a ring detect circuit and

a power-up logic circuit.

In a typical application, the ring detector maintains the line continously while all other functios of the chip are

inhibited. If a ring signal is sent, the /RINGTIME pin will has a low signal. User can use this signal to wake up

whole chip or read /RD signal from RA register.

A /FSKPWR input is provided to active the block regardless of the presence of a power ring signal. If /FSKPWR

is sent low, the FSK block will power down whenever it detects a valid ring signal, it will power on when

/FSKPWR is high.

The input buffer accepts a differential AC coupled input signal through the TIP and RING input and feeds this

signal to a band pass filter. Once the signal is filtered, the FSK demodulator decodes the information and sends

it to a post filter. The output data is then made available at DATA OUT pin. This data, as sent by the central office,

includes the header information (alternate “1” and “0”) and 150 ms of marking which precedes the date , time

and calling number. If no data is present, the DATA OUT pin is held in a high state. This is accomplished by an

carrier detect circuit which determines if the in-band energy is high enough. If the incoming signal is valid and

thus the demodulated data is transferred to DATA OUT pin . If it is not, then the FSK demodulator is blocked.

* This specification are subject to be changed without notice.

10.12.1998

21

Page 22

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

Ring detect circuit

When Vdd is applied to the circuit, the RC netwiok will charge cap C1 to Vdd holding/RING TIME off. The

resistor network R2 to R3 attenuates the incoming power ring applied to the top of R2. The values given have

been chosen to provide a sufficient voltage at DET1 pin, to turn on the Schmitt trigger input. When Vt+ of the

Schmitt is exceeded, cap C1 will discharge.

The value of R1 and C1 must be chosen to hold the /RING TIME pin voltage below the Vt+ of the Schmitt

between the individual cycle of the power ring With /RINGTIME enabled, this signal will be a /RD signal in

RA throught a buffer.

/Ring Time

/Ring Time

Vdd

R1

C1

/RD

det1

R2

R3

Fig16. Ring detect circuit

DTMF ( Dual Tone Multi Frequency ) Tone Generator

Built-in DTMF generator can generate dialing tone signals for telephone of dialing tone type. There are two kinds

of DTMF tone . One is the group of row frequency, the other is the group of column frequency, each group has

4 kinds of frequency , user can get 16 kinds of DTMF frequency totally. DTMF generator contains a row

frequency sine wave generator for generating the DTMF signal which selected by low order 4 bits of RB and a

column frequency sine wave generator for generating the DTMF signal which selected by high order 4 bits

of RB. This block can generate single tone by filling one bit zero to this register.

If all the values are high , the power of DTMF will turn off until one or two low values.

Either high or low 4 bits must be set by an effective value, otherwise, if any ineffective value or both 4 bits are

load effective value, tone output will be disable. Recommend value refer to table as follow please :

* This specification are subject to be changed without notice.

10.12.1998

22

Page 23

SYSTEM CLOCK

Low frequency generator

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

ROW

Register

COLUMN

Register

DTMF low-freq

selection

DTMF high-freq

selection

High frequency generator

Sine wave

generator

Sine wave

generator

Adder

DTMF tone

output

Fig17. DTMF Block Diagram

RB ( DTMF Register )

• Bit 0 - Bit 3 are row-frequency tone.

• Bit 4 - Bit 7 are column-frequency tone.

• Initial RB is equal to HIGH.

• Except below values of RB ,the other values of RB are not effect. If RB is set by ineffective value, the DTMF

output will be disable and there is no tone output.

• Bit 7 ~ 0 are all “1” , turn off DTMF power .

bit 3~0 Row freq Xin=3.58MHz

1110 699.2Hz 1 2 3 A

1101 771.6Hz 4 5 6 B

1011 854Hz 7 8 9 C

0111 940.1Hz * 0 # D

Column freq 1203Hz 1331.8Hz 1472Hz 1645.2Hz

bit 7~4 1110 1101 1011 0111

LCD Driver

The CALLER ID IC can drive LCD directly and has 60 segments and 16 commons that can drive 60*16 dots

totally. LCD block is made up of LCD driver , display RAM, segment output pins , common output pins and LCD

operating power supply pins.

Duty , bias , the number of segment , the number of common and frame frequency are determined by LCD mode

register . LCD control register.

The basic structure contains a timing control which uses the basic frequency 32.768KHz to generate the proper

timing for different duty and display access. RE register is a command register for LCD driver, the LCD display(

disable, enable, blanking) is controlled by LCD_C and the driving duty and bias is decided by LCD_M and the

display data is stored in data RAM which address and data access controlled by registers RC and RD.

* This specification are subject to be changed without notice.

10.12.1998

23

Page 24

32.768KHz

LCD timing control

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

RC(address)

RD(data)

RAM

RE(LCD_C,LCD_M)

Bias control

Vdd-Vlcd

LCD duty control

LCD commom control

COM

Display data control

LCD SEGMENT control

SEG

Fig18. LCD DRIVER CONTROL

LCD Driver Control

RE(LCD Driver Control)(initial state “00000000”)

76543210

-----LCD_C2 LCD_C1 LCD_M

• Bit0 (LCD_M):LCD_M decides the methods, including duty, bias, and frame frequency.

• Bit1~Bit2 (LCD_C#):LCD_C# decides the LCD display enable or blanking.

change the display duty must set the LCD_C to “00”.

LCD_C LCD Display Control LCD_M LCD driving method/frame freq.

bit2,1 bit 0 duty bias

0 0 change duty 0 1/16 1/4

Disable(turn off LCD) 1 1/8 1/4

0 1 Blanking : :

1 1 LCD display enable : :

LCD display area

The LCD display data is stored in the data RAM . The relation of data area and COM/SEG pin is as below:

COM15 ~ COM8 COM7 ~ COM0

40H (Bit15 ~ Bit8) 00H (Bit7 ~ Bit0) SEG0

41H 01H SEG1

:::

:::

7BH 3BH SEG59

7CH 3CH empty

7DH 3DH empty

7EH 3EH empty

7FH 3FH empty

* This specification are subject to be changed without notice.

10.12.1998

24

Page 25

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

• IOCB(LCD Display RAM address)

7654321 0

- LCD6 LCD5 LCD4 LCD3 LCD2 LCDA1 LCD0

Bit 0 ~ Bit 6 select LCD Display RAM address up to 120.

LCD RAM can be write whether in enable or disable condition and read only in disable condition.

• IOCC(LCD Display data) : Bit 0 ~ Bit 8 are LCD data.

LCD COM and SEG signal

• COM signal : The number of COM pins varies according to the duty cycle used, as following: in 1/8 duty

mode COM8 ~ COM15 must be open. in 1/16 duty mode COM0 ~ COM15 pins must be used.

COM0 COM1 COM2 COM3 COM4 COM5 COM6 COM7 COM8 .. COM15

1/8oooooo oo x ..x

1/16 o o o o o o o o o .. o

x:open,o:select

• SEG signal: The 60 segment signal pins are connected to the corresponding display RAM address 00h to 3Bh.

The high byte and the low byte bit7 down to bit0 are correlated to COM15 to COM0 respectively .

When a bit of display RAM is 1, a select signal is sent to the corresponding segment pin, and when the bit

is 0 , a non-select signal is sent to the corresponding segment pin.

• COM, SEG and Select/Non-select signal is shown as following:

* This specification are subject to be changed without notice.

10.12.1998

25

Page 26

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

frame

com0

com1

com2

seg

seg

com0 ... com7

VDD

V1

V2

V3

VLCD

VDD

V1

V2

V3

VLCD

VDD

V1

V2

V3

VLCD

VDD

V1

V2

V3

VLCD

dark

VDD

V1

V2

V3

VLCD

light

Fig.19 Lcd wave 1/4 bias , 1/8 duty

* This specification are subject to be changed without notice.

10.12.1998

26

Page 27

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

frame

com0

com1

com2

seg

seg

com0 ... com15

VDD

V1

V2

V3

VLCD

VDD

V1

V2

V3

VLCD

VDD

V1

V2

V3

VLCD

VDD

V1

V2

V3

VLCD

dark

VDD

V1

V2

V3

VLCD

light

Fig.20 Lcd wave 1/4 bias , 1/16 duty

* This specification are subject to be changed without notice.

10.12.1998

27

Page 28

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

LCD Bias control

IOCE (Bias Control Register)

76543210

Bias3 Bias2 Bias1

• Bit 2~4 (Bias1~Bias3) Control bits used to choose LCD operation voltage .

Bias3 Bias2 Bias1 LCD operate voltage Vop (VDD 5V)

000 0.60 V

001 0.66 V

010 0.74 V

011 0.82 V

100 0.87 V

101 0.93 V

110 0.96 V

111 1.00 V

DD

DD

DD

DD

DD

DD

DD

DD

3.0V

3.3V

3.7V

4.0V

4.4V

4.7V

4.8V

5.00V

EM78811

• Bit 5~7 unused

Vdd

Vss

Vop=Vdd-Vlcd

Vop

Bias3˜1

Fig.19 LCD bias circuit

MUX

R=1K

R

V1

R

V2

R

V3

R

Vlcd

:

000

001

010

011

100

101

110

111

8.2R

0.4R

0.4R

0.3R

0.3R

0.2R

0.1R

0.1R

Vop=Vdd-Vlcd

R=1K

* This specification are subject to be changed without notice.

10.12.1998

28

Page 29

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

ABSOLUTE MAXIMUM RATINGS

Items Sym. Condition Rating Unit

EM78811

Temperature under bias V

Input voltage V

Operating temperature range T

DC ELECTRICAL CHARACTERISTICS (T

(V

=2.5V to 5.5V for CPU ; VDD=3.5V to 5.5V for FSK ; VDD=2.5V to 5.5V for DTMF)

DD

A

DD

IN

= 0°C~70°C, V

A

-0.3 to 6 V

- 0.5 to VDD+ 0.5 V

0 to 70 °C

= 5V±5%; VSS = 0V)

DD

Parameter Sym. Condition Min. Typ. Max. Unit

V

Input Leakage Current I

IL1

= VDD, V

IN

SS

for input pins

Input Leakage Current I

IL2

VIN = V

DD

, V

SS

for bi-directional pins

Input High Voltage V

Input Low voltage V

Input High Threshold V

IH

IL

RESET, TCC, RDET1 2.0 V

IHT

2.5 V

Voltage

Input Low Threshold V

RESET, TCC, RDET1 0.8 V

ILT

Voltage

Clock Input High Voltage V

Clock Input Low Voltage V

Output High Voltage V

OSCI 3.5 V

IHX

OSCI 1.5 V

ILX

OH1IOH

= -1.6 mA 2.4 V

(port5,6,7,8)

(port9) I

Output Low Voltage V

OL1IOL

= -6.0 mA 2.4 V

OH

= 1.6 mA 0.4 V

(port5,6,7,8)

(port9) I

Com Voltage drop V

Segment Voltage drop V

LCD Drive Reference V

COMI O

SEGI O

LCD

= 6.0 mA 0.4 V

OL

= ±50 µA - - 2.9 V

= ±50 µA - - 3.8 V

Contrast adjustment

Voltage

Pull-high Current I

Power Down Current I

Pull-high active input pin at V

PH

All input and I/O pin at VDD, output pin 4 µA

SB1

SS

-50 -100 -240 µA

floating, WDT disabled

Low Clock Current I

CLK=32.768 KHz, FSK, DTMF block

SB2

disable,All input and I/O pin at V

, 100 µA

DD

output pin floating, WDT disabled,

LCD enable

Operating Supply I

RESET=HIGH, CLK=3.679MHz, output pin 3 mA

CC

floating, FSK, DTMF block disable

±1 µA

± 1 µA

0.8 V

* This specification are subject to be changed without notice.

10.12.1998

29

Page 30

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

AC ELECTRICAL CHARACTERISTIC ( T

= 0 ~ 70°C, V

A

= 5V`VSS = 0V )

DD

Parameter Sym. Condition Min. Typ. Max. Unit

Input CLK duty cycle Dclk 45 50 55 %

Instruction cycle time Tins 32.768K 60 µs

3.679M 550 µs

Device delay hold time Tdrh 18 ms

TCC input period Ttcc Note 1 (Tin+20)/N ns

Watchdog timer period Twdt T

= 25°C18ms

A

Note 1: N = selected prescaler ratio.

( FSK Band Pass Filter AC Characteristic)(V

= 5V`TA=25° C )

DD

Characteristic Min. Typ. Max. Unit

Input Sensitivity TIP and RING pin1 and pin2 V

=+5V -35 -48 — dBm

DD

Band Pass Filter dBm

FSK DECODER BLOCK FUNCTION TIMING

( VDD = 5.0V ± 5%, VSS = 0V TA = operating temperature range, unless otherwise note )

Parameter Sym. Min. Typ. Max. Unit

OSC start up (32.768KHz) Tosc — 400

(3.679MHz PLL) 10

Carrier detect low Tcdl — 10 14 ms

Data out to Carrier det low Tdoc — 10 20 ns

Power up to FSK(setup time) PS(1) Tsup — 15 20 ms

/RD low to Ringtime low Trd 10 ms

End of FSK to Carrier Detect high Tcdh 8 — — ms

PS (1) : Please watch out the setup time.

ms

* This specification are subject to be changed without notice.

10.12.1998

30

Page 31

TIMING DIAGRAMS

AC Test Input/Output Waveform

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

2.4

2.0

0.8

0.45

2.0

0.8

AC Testing : Input are driven at 2.4V for logic "1", and 0.45V for logic "0". Timing

measurements are made at 2.0V for logic "1", and 0.8V for logic "0".

RESET Timing

NOP

Instruction 1

Executed

TCC Input Timing

CLK

TCC

Tdrh

Tins

Ttcc

Fig.20 AC timing

* This specification are subject to be changed without notice.

10.12.1998

31

Page 32

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

TIP/RING

/RING TIME

/RD

/CD

DATA

OSC

POWER

Trd

FIRST RING

2 SECONDS

Tosc

3.68 MHz

0.5 SEC

Tpd

Tcdl

Tdoc

DATA

Tsup

0.5 SEC

Tcdh

Fig.23 FSK Power Down Mode Timing Diagram

SECOND RING

2 SECONDS

* This specification are subject to be changed without notice.

10.12.1998

32

Page 33

APPLICATION CIRCUIT

1000p

250V

0.1u

250V

0.1u

250V

1000p

250V

TIP

RING

ZNR

250V

FUSE

To Phone

40044004

40044004

470k

30k

30k

30k

EM78811

8-BIT MICRO-CONTROLLER FOR TELECOM PRODUCT

POWER

0.1uF

270k

0.22u

Vdd

TIP

RING

DET1

/RINGTIME

AVSS

TEST

VSS2

VDD1

VDD2

AVDD

K1

K2

K3

K4

DIAL

PLLC

Xin

Xout

100

0.1uF

/PULSE

MUTE

TONE

/HKS

10n

32.768K

Vdd

100K

AVSS

C1

C2

LCD DISPLAY

Fig.24 Application Circuit

* This specification are subject to be changed without notice.

10.12.1998

33

Loading...

Loading...