Page 1

1

Standard ICs

Picture cell driver for STN (LCD driver)

BU9716BK / BU9716BKV

The BU9716BK and BU9716BKV are man-machine interface ICs designed for applications such as multi-media

portable terminals.

Specifically, these products are used as driver ICs for operating mode display LCD panels in portable terminals,

household appliances, and other similar products. The number of display cells includes 32 segments and 3 commons, enabling drive of up to 96 cells.

•

Applications

•

Features

1) Up to 32 segment outputs and 3 common outputs

can be displayed, for a total of 96 segments.

2) 1 / 3 duty display.

3) Either 1 / 2 or 1 / 3 can be selected for power supply

for LCD display.

Multi-media portable terminals, POS terminals, ECR

terminals, short wave radios, telephones, cameras,

VCRs, movie projectors, car audio systems, and others

•

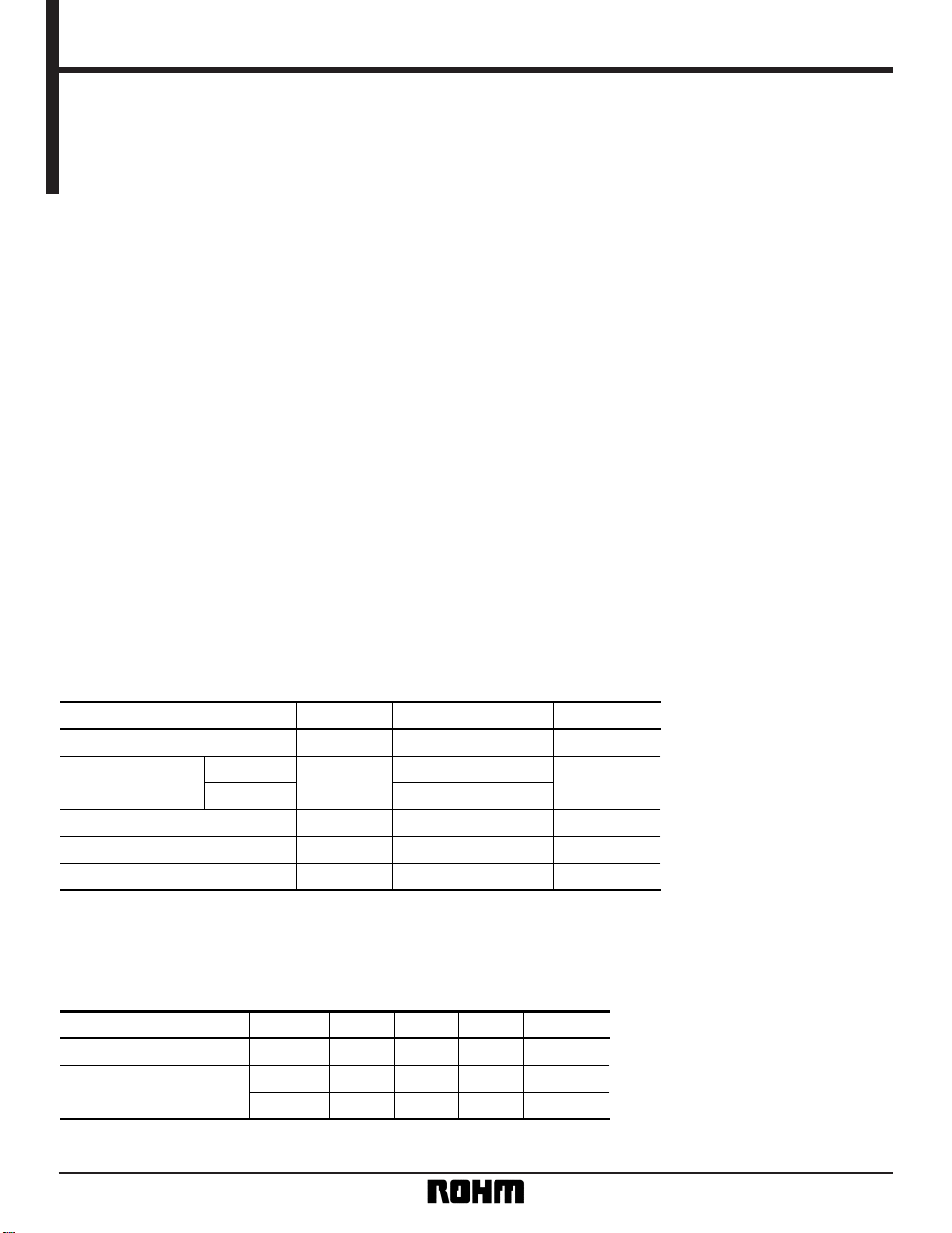

Absolute maximum ratings (Ta = 25°C, VSS = 0V)

∗

1 Reduced by 5mW for each increase in Ta of 1°C over 25°C .

∗

2 Reduced by 4mW for each increase in Ta of 1°C over 25°C .

Parameter Symbol Limits Unit

Power supply voltage V

DD V

BU9716BK

Pd

500

∗

1

mW

BU9716BKV 400

∗

2

Input voltage VIN – 0.3 ~ VDD + 0.3 V

Storage temperature

Topr

°C

Operating temperature

Tstg

°C

– 0.3 ~ + 7.0

– 40 ~ + 85

– 55 ~ + 125

dissipation

Power

•

Recommended operating conditions (Ta = 25°C, VSS = 0V)

Parameter Symbol Min. Typ. Max. Unit

Power supply voltage V

DD 4.5 — 5.5 V

Input voltage

V

DD1 0 2 / 3V

DDVDD

V

V

DD2 0 1 / 3V

DDVDD

V

Page 2

2

Standard ICs BU9716BK / BU9716BKV

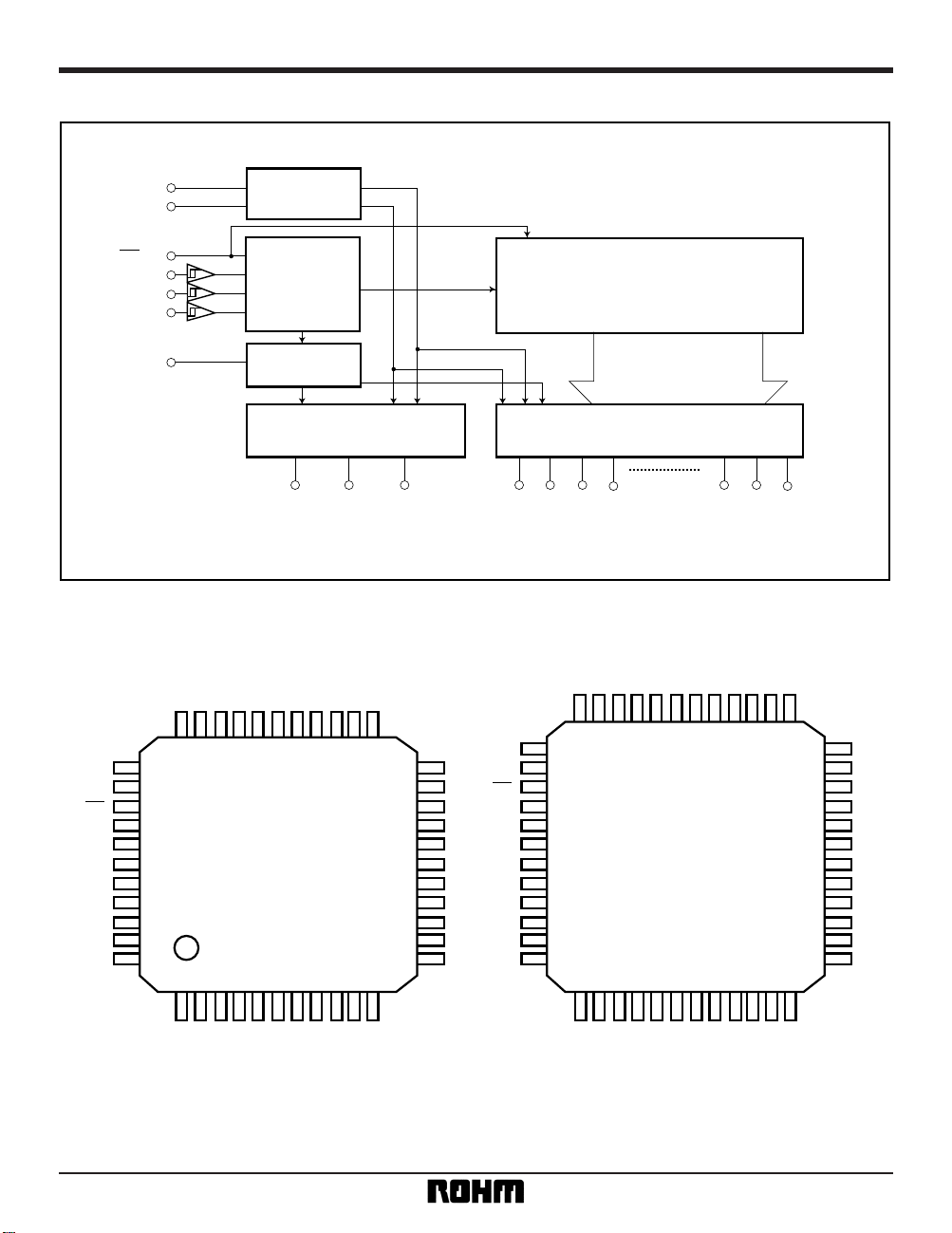

•

Block diagram

DATA Latch

Segment Driver

Common Driver

LCD Power

CTRL Logic

OSC

V

DD1

VDD2

RES

CS

DI

CK

OSC

COM1

COM2

COM3

S1

S2

S3

S4

S30

S31

S32

•

Pin assignments

COM1

S32

S31

S30

S29

S28

S27

S26

S25

S24

S23

S1S2S3

S4S5S6S7S8

S9

S10

S11

S22

S21

S20

S19

S18

S17

S16

S15

S14

S13

S12

COM2

COM3

RES

VDD

VDD1

VDD2

VSS

OSC

CS

CK

DI

33

23

2234

44 12

11

1

BU9716BK

COM1

S32

S31

S30

S29

S28

S27

S26

S25

S24

S23

N.C.

S1S2S3

S4S5S6S7S8

S9

S10

S11

N.C.

S22

N.C.

S21

S20

S19

S18

S17

S16

S15

S14

S13

S12

COM2

COM3

RES

VDD

VDD1

VDD2

VSS

OSC

CS

CK

DI

N.C.

36

25

24

37

48 13

12

1

BU9716BKV

Page 3

3

Standard ICs BU9716BK / BU9716BKV

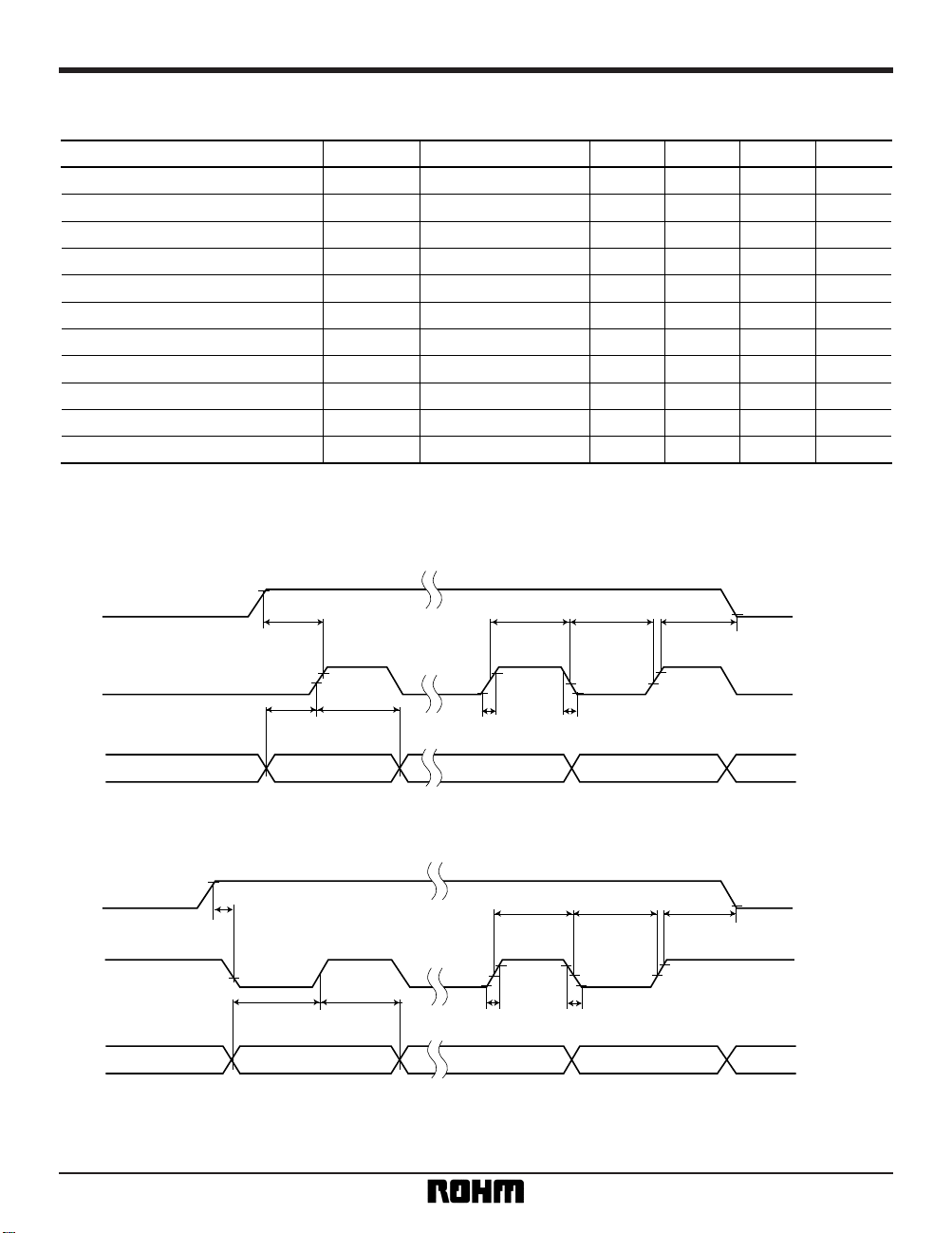

•

Pin descriptions (BU9716BK)

Pin name I / O

Processing

when not

used

1 - 32 S1 - S32 O OPEN

33

34

35

O OPEN

36 RES I V

DD

41 OSC — VSS

42 CS I Chip select input. At CS = H, data can be transferred. VSS

43 CK I Synchronous clock input for serial data transfer VSS

44 DI I Serial data input VSS

38 VDD1 — OPEN

39 V

DD2 — OPEN

Oscillator pin (for common and segment alternating waveforms)

Output pin for segment data. Outputs consistent LCD drive voltage to the

data corresponding to COM1 to COM3.

COM1

COM2

COM3

Pin No. Function

Internal reference voltage for LCD drive. In 1 / 2 bias mode, this is connected to V

DD2.

Internal reference voltage for LCD drive. In 1 / 2 bias mode, this is connected to V

DD1.

Common driver output. The frame frequency is f

C = (fOSC / 384) Hz

Reset input. At RES = L, internal data (including control data) is reset.

•

Electrical characteristics (unless otherwise noted, Ta = 25°C, VDD = 4.5V to 5.5V, VSS = 0V)

Parameter Symbol Min. Typ. Max. Unit Conditions

V

IH 0.8VDD — VDD V CS, CK, DI, RES

V

IL 0 — 0.2VDD V CS, CK, DI, RES

I

IH 0 — 6.0 µA

I

IL 0 — 6.0 µA

V

SOH ——VS1 ~ S32, IO = – 20µA

V

COH ——V

V

SOL — 1.0 — VS1 ~ S32, IO = – 20µA

V

COL — 1.0 — V

Intermediate output voltage

VCM1 —

1 / 2V

DD

± 1.0

— V

V

SM1 —

2 / 3V

DD

± 1.0

— VS1 ~ S32, 1 / 3Bias

V

CM2 —

2 / 3V

DD

± 1.0

— V

V

SM2 —

1 / 3V

DD

± 1.0

— VS1 ~ S32, 1 / 3Bias

V

CM3 —

1 / 3V

DD

± 1.0

— V

Power supply current

I

Q — 30 70 µA Low-power mode

I

DD — 100 300 µAfOSC = 38kHz

Input low level voltage

Input low level current

Output low level voltage

CS, CK, DI, RES, VI = VDD

CS, CK, DI, RES, VI = VSS

COM1 ~ COM3, IO = – 100µA

COM1 ~ COM3, I

O = – 100µA

COM1 ~ COM3, 1 / 2Bias

COM1 ~ COM3, 1 / 3Bias

COM1 ~ COM3, 1 / 3Bias

V

DD – 1.0

V

DD – 1.0

Input high level voltage

Input high level current

Output high level voltage

Page 4

4

Standard ICs BU9716BK / BU9716BKV

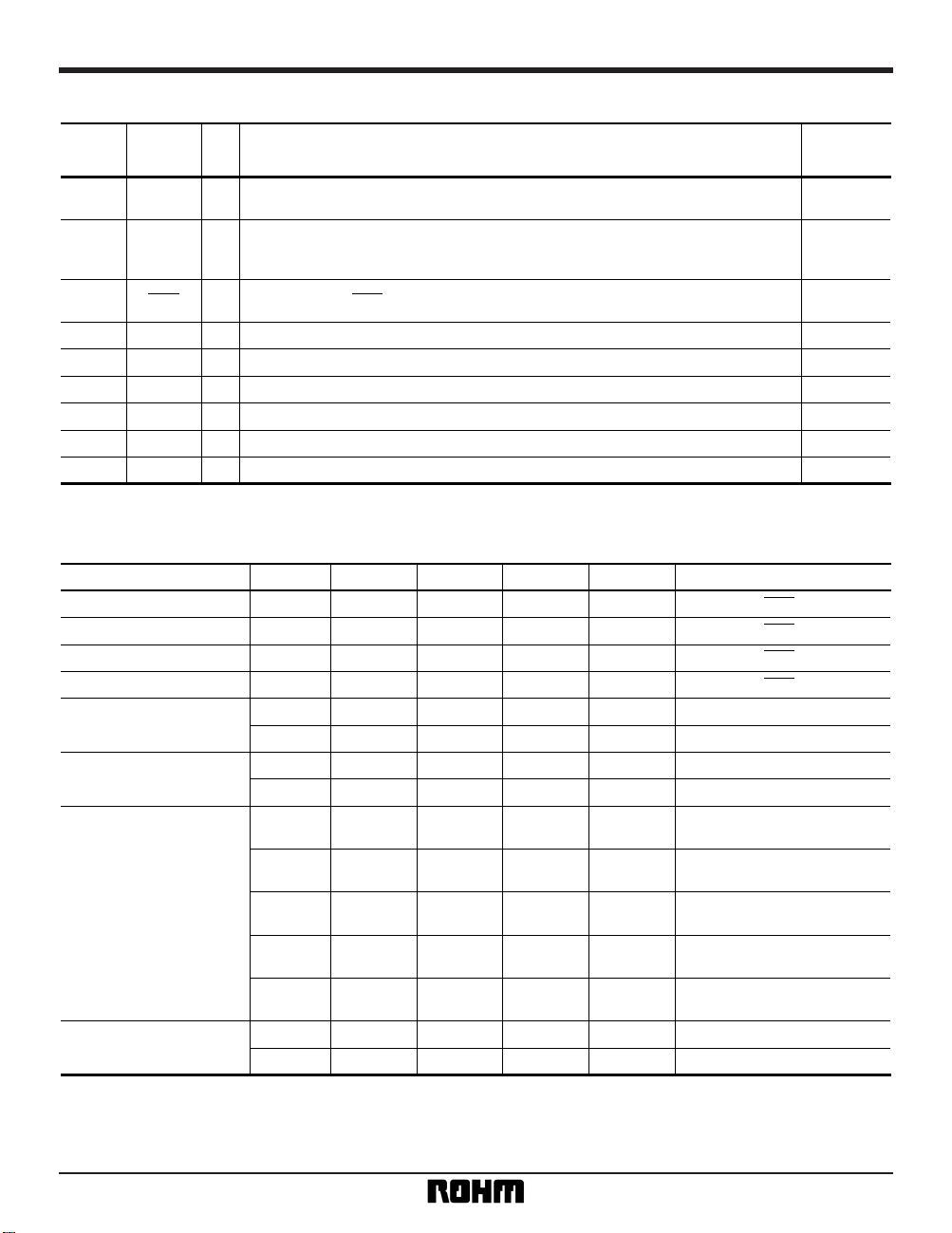

•

Electrical characteristics

AC characteristics (unless otherwise noted, Ta = 25°C, V

DD = 4.5V to 5.5V, VSS = 0V)

Parameter Symbol Min. Typ. Max. Unit

Recommended external resistance R OSC — 47 — k

Ω

Recommended external capacitance C OSC — 1000 — pF

Guaranteed oscillation range OSC 19 38 76 kHz

Data setup time CK, DI 100 ——ns

Data hold time CK, DI 100 ——ns

CS setup time CS, CK 100 ——ns

CS hold time CS, CK 100 ——ns

CK 100 ——ns

CK 100 ——ns

Rise time CS, CK, DI ——300 ns

Fall time CS, CK, DI ——300 ns

f

OSC

tDS

tDH

tCS

tCH

tCKH

tCKL

Pin

CK "L" pulse width

t

r

tf

CK "H" pulse width

AC timing waveform

(1) When CK is stopped at “L”

(2) When CK is stopped at “H”

CS

CK

DI

tCS tCKH

tr tf

tCKL tCH

tDS tDH

0.8VDD

0.8VDD

0.5VDD

0.5VDD

0.8VDD

0.2VDD

0.2VDD

CS

CK

DI

tCS

tr tf

tDS tDH

0.8VDD

0.5VDD

0.5VDD

0.8VDD

tCKH tCKL tCH

0.2VDD

0.2VDD

0.2VDD

Page 5

5

Standard ICs BU9716BK / BU9716BKV

•

Measurement circuit

V

A

A

P. G.

V

GND

V

1

1

1

1

1

2

2

2

2

3

I

O

SW2

SW3

SW4

SW1

VCM1, VCM2, VCM3

VSM1, VSM2

VSOH, VSOL

VCOH, VCOL

IDD, IQ

VDD

VDD1

VDD2

VSS

S1 ~ S32

COM1 ~ COM3

CS, CK

OSC

DI, RES

IIH, LH

V2

GND

0.047µF

0.047µF

1000pF, 47kΩ

∗

P. G.: Control signal generator for programmable signal generator, etc.

Fig.1

Measurement conditions

SW1 SW2 SW3 SW4

V

IH

2 —— 1

V

IL

IIH

2 —— 2

V

2 = VDD

V2 = VSSIIL

VSOH

3

1

11

Pattern 1, I

O = – 20

µA

V

COH 2

V

SOL

3

1

21

2V

COL

Intermediate output voltage

V

CM1

1

22

1

1

1

V

SM1

VCM2 2

V

SM2 1

2V

CM3

Current dissipation

I

Q

2 —— 1

I

DD

AC characteristics 2 —— 1

Symbol

Set as P.G. input voltage;

Parameter Conditions

Input low level voltage

Input low level current

Output low level voltage

mode switching test

Input high level voltage

Input high level current

Output high level voltage

Pattern 1, I

O = – 100

µA

Pattern 2, I

O = 20

µA

Pattern 2, I

O = 100

µA

Pattern 3

Pattern 4

Pattern 4

Pattern 5

Pattern 5

Pattern 6

Test after power on

Used as P.G. input condition

Measurement pattern

CS

DI

CK

Pattern 1

Fig.2

CS

DI

CK

Pattern 4

Fig.5

CS

DI

CK

Pattern 5

Fig.6

CS

DI

CK

Pattern 6

Fig.7

CS

DI

CK

Pattern 2

Fig.3

CS

DI

CK

Pattern 3

Fig.4

Page 6

6

Standard ICs BU9716BK / BU9716BKV

•

Circuit operation

Timing charts

(1) When CK is stopped at “L”

(2) When CK is stopped at “H”

D1D2D3 D9600000BMLCOE

CS

CK

DI

Fig.8

Display data Control code

When CS is HIGH, data can be transferred. Data is

sent to the shift register at the rising edge of CK. After

all of the DI data has been transferred, CS should be

set to LOW. The voltage corresponding to the display

data transferred at the falling edge of CS is output.

D1D2D3 D9600000BMLCOE

Display data Control code

CS

CK

DI

Fig.9

Control code table

OE

0

1

Output enable control

Normal operation

All display data is 0; no display (internal oscillation circuit is operating)

BM

0

1

Bias mode control

1 / 3 bias

1 / 2 bias

LC

0

1

Low power mode control

Normal operation

Low power mode = The internal oscillation circuit stops

oscillating, and segment and common output = 0

Page 7

7

Standard ICs BU9716BK / BU9716BKV

Correspondence between display data input and segments

Segment COM3 COM2 COM1

S1 D1 D2 D3

S2 D4 D5 D6

S3 D7 D8 D9

S4 D10 D11 D12

S5 D13 D14 D15

S6 D16 D17 D18

S7 D19 D20 D21

S8 D22 D23 D24

S9 D25 D26 D27

S10 D28 D29 D30

S11 D31 D32 D33

S12 D34 D35 D36

S13 D37 D38 D39

S14 D40 D41 D42

S15 D43 D44 D45

S16 D46 D47 D48

Segment COM3 COM2 COM1

S17 D49 D50 D51

S18 D52 D53 D54

S19 D55 D56 D57

S20 D58 D59 D60

S21 D61 D62 D63

S22 D64 D65 D66

S23 D67 D68 D69

S24 D70 D71 D72

S25 D73 D74 D75

S26 D76 D77 D78

S27 D79 D80 D81

S28 D82 D83 D84

S29 D85 D86 D87

S30 D88 D89 D90

S31 D91 D92 D93

S32 D94 D95 D96

Page 8

8

Standard ICs BU9716BK / BU9716BKV

•

Timing chart

VDD

VDD1, VDD2

VSS

VDD

VDD1

VDD2

VSS

VDD

VDD1

VDD2

VSS

VDD

VDD1

VDD2

VSS

VDD

VDD1

VDD2

VSS

VDD

VDD1

VDD2

VSS

VDD

VDD1

VDD2

VSS

VDD

VDD1

VDD2

VSS

VDD

VDD1

VDD2

VSS

VDD

VDD1

VDD2

VSS

VDD

VDD1

VDD2

VSS

VDD

VDD1

VDD2

VSS

VDD

VDD1, VDD2

VSS

VDD

VDD1, VDD2

VSS

VDD

VDD1, VDD2

VSS

VDD

VDD1, VDD2

VSS

VDD

VDD1, VDD2

VSS

VDD

VDD1, VDD2

VSS

VDD

VDD1, VDD2

VSS

VDD

VDD1, VDD2

VSS

VDD

VDD1, VDD2

VSS

VDD

VDD1, VDD2

VSS

1 / 2 bias 1 / 3 duty waveform

f

O = fOSC / 384

1 / 3 bias 1 / 3 duty waveform

fO = fOSC / 384

COM 1

Fig.10

COM 2

COM 3

LCD driver output when all LCD segments

for COM1, 2, and 3 are out

LCD driver output when only the LCD segment

for COM1 is lit up

LCD driver output when only the LCD segment

for COM2 is lit up

LCD driver output when the LCD segments

for COM1 and 2 are lit up

LCD driver output when only the LCD segment

for COM3 is lit up

LCD driver output when the LCD segments

for COM1 and 3 are lit up

LCD driver output when the LCD segments

for COM2 and 3 are lit up

LCD driver output when all the LCD segments

for COM1, 2 and 3 are lit up

Page 9

9

Standard ICs BU9716BK / BU9716BKV

•

Application example 1

96

Segment

LCD

OSC

V

DDVDD

VDD1

VDD2

VSS

RES

CS

CK

DI

C ⭌ 0.047µF

Controller

BU9716BK / BKV

COM1

COM2

COM3

S1

S2

S3

S4

S5

S6

S32

47kΩ

1000pF

GND

1 / 2 bias mode

Fig.11

96

Segment

LCD

OSC

V

DDVDD

VDD1

VDD2

VSS

RES

CS

CK

DI

C ⭌ 0.047µF

Controller

BU9716BK / BKV

COM1

COM2

COM3

S1

S2

S3

S4

S5

S6

S32

47kΩ

1000pF

GND

C ⭌ 0.047 µF

1 / 3 bias mode

Fig.12

Page 10

10

Standard ICs BU9716BK / BU9716BKV

•

Application example 2

96

Segment

LCD

OSC

V

DDVDD

VDD1

VDD2

VSS

RES

CS

CK

DI

C ⭌ 0.047µF

Controller

BU9716BK / BKV

COM1

COM2

COM3

S1

S2

S3

S4

S5

S6

S32

47kΩ

1000pF

GND

R

R

∗

1

1 / 2 bias mode

Fig.13

96

Segment

LCD

OSC

V

DDVDD

VDD1

VDD2

VSS

RES

CS

CK

DI

C ⭌ 0.047µF

Controller

BU9716BK / BKV

COM1

COM2

COM3

S1

S2

S3

S4

S5

S6

S32

47kΩ

1000pF

GND

∗

2

R

R

R

1 / 3 bias mode

The resistance values and capacitance for∗1 and ∗2 should be set to match the LCD panel, and should be checked using test operation.

Fig. 14

Page 11

11

Standard ICs BU9716BK / BU9716BKV

•

External dimensions (Units: mm)

QFP44 VQFP48

33 23

22

12

1

34

44

10.0 ± 0.2

14.0 ± 0.3

0.35 ± 0.1

10.0 ± 0.2

14.0 ± 0.3

1.2

0.05

2.15 ± 0.1

0.15 ± 0.1

0.8

11

0.15

0.10

BU9716BK BU9716BKV

0.5

0.125 ± 0.1

0.2

±

0.1

9.0 ± 0.3

7.0

±

0.2

9.0 ± 0.3

7.0

±

0.2

48

37

1

12

13

24

2536

0.5

1.425

±

0.1

0.10

0 < tON < 10ms

V

DD ⭌ 1.8V

V

DD < 0.3V

t

WAIT ⭌ 1ms

Instruction receipt possible

Make sure of the following when resetting when the power is on.

• When using the external reset terminal, make RST = “L” at 1 ms or more with V

DD at 1.8V or more.

• When not using the external reset terminal, V

DD has to satisfy the following conditions.

Loading...

Loading...