Conexant RS8953BEPF, RS8953BEPJ, RS8953SPB EPF, RS8953SPB EPJ Datasheet

Data Sheet D8953BDSB

March 30, 1999

RS8953B/8953SPB

HDSL Channel Unit

The RS8953B is a High-Bit-Rate Digital Subscriber Line (HDSL) channel unit designed

to perform data, clock, and format conversions necessary to construct a Pulse Code

Multiplexed (PCM) channel from one, two, or three HDSL channels. The PCM channel

consists of transmit and receive data, clock and frame sync signals configured for

standard T1 (1544 kbps), standard E1 (2048 kbps), or custom (Nx64 kbps) formats.

The PCM channel connects directly to a Bt8370 T1/E1 Controller or similar T1/E1 device.

Connection to other network/subscriber physical layer devices is supported by the

custom PCM frame format. Three identical HDSL channel interfaces consist of serial

data and clock connected to a Bt8970 HDSL Transceiver or similar 2B1Q bit pump

device. The RS8953SPB contains one HDSL channel interface.

Control and status registers are accessed via the Microprocessor Unit (MPU)

interface. One common register group configures the PCM interface formatter,

Pseudo-Random Bit Sequence (PRBS) generator, Bit Error Rate (BER) meter, timeslot

router, Digital Phase Lock Loop (DPLL) clock recovery, and PCM Loopbacks (LB). Three

groups of HDSL channel registers configure the elastic store FIFOs, overhead MUXes,

receive framers, payload mappers, and HDSL loopbacks. Status registers monitor

received overhead, DPLL, FIFO, and framer operations, including CRC and FEBE error

counts.

The RS8953B adheres to Bellcore TA-NWT-001210 and FA-NWT-001211 and the

latest ETSI RTR/TM-03036 standards. C-language software for all standard T1/E1

configuration and startup procedures is implemented on Conexant's HDSL Evaluation

Module (Bt8973EVM) and is available under a no-fee license agreement. RS8953B

software can also be developed for non-standard HDSL applications or to interoperate

with existing HDSL equipment.

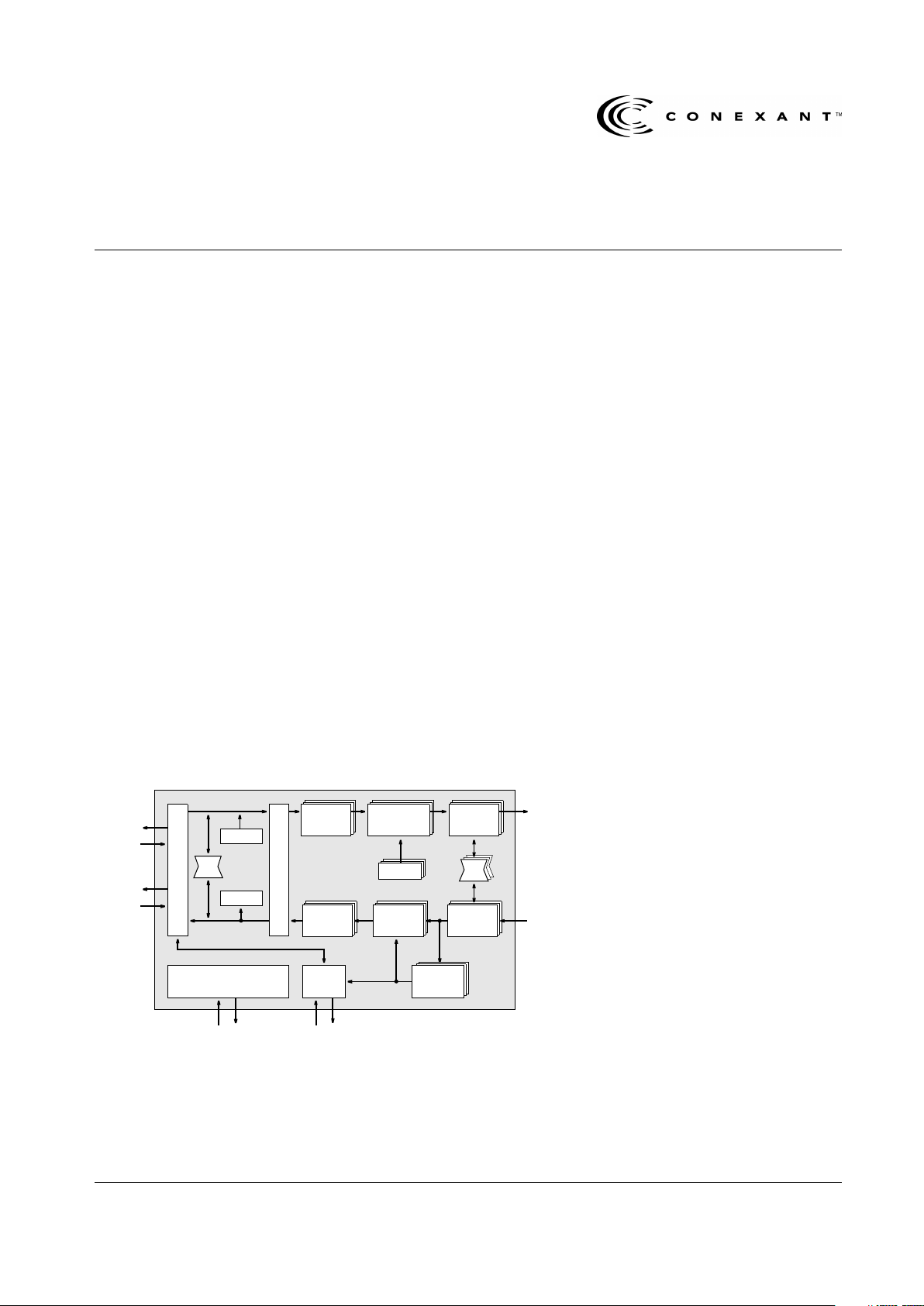

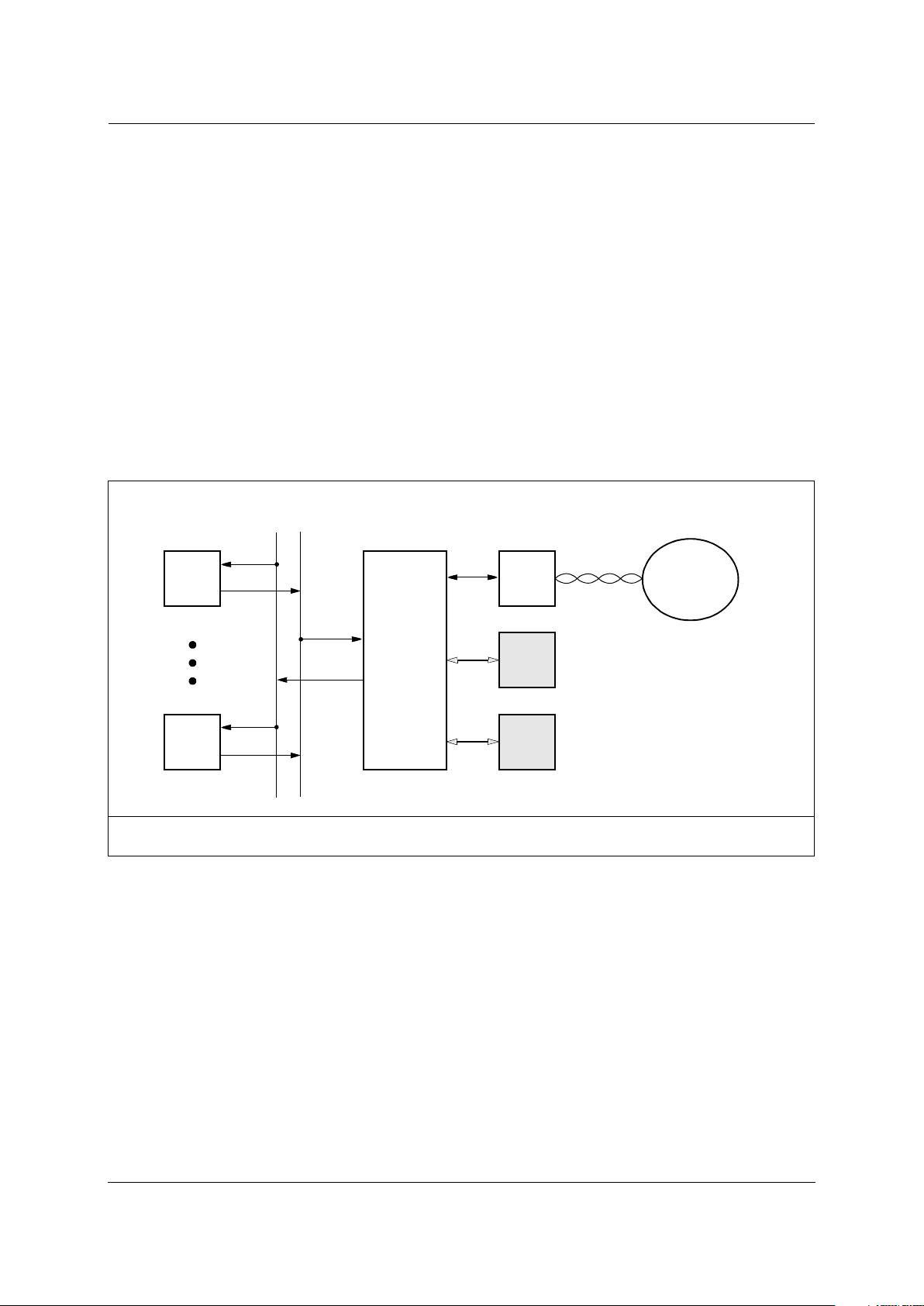

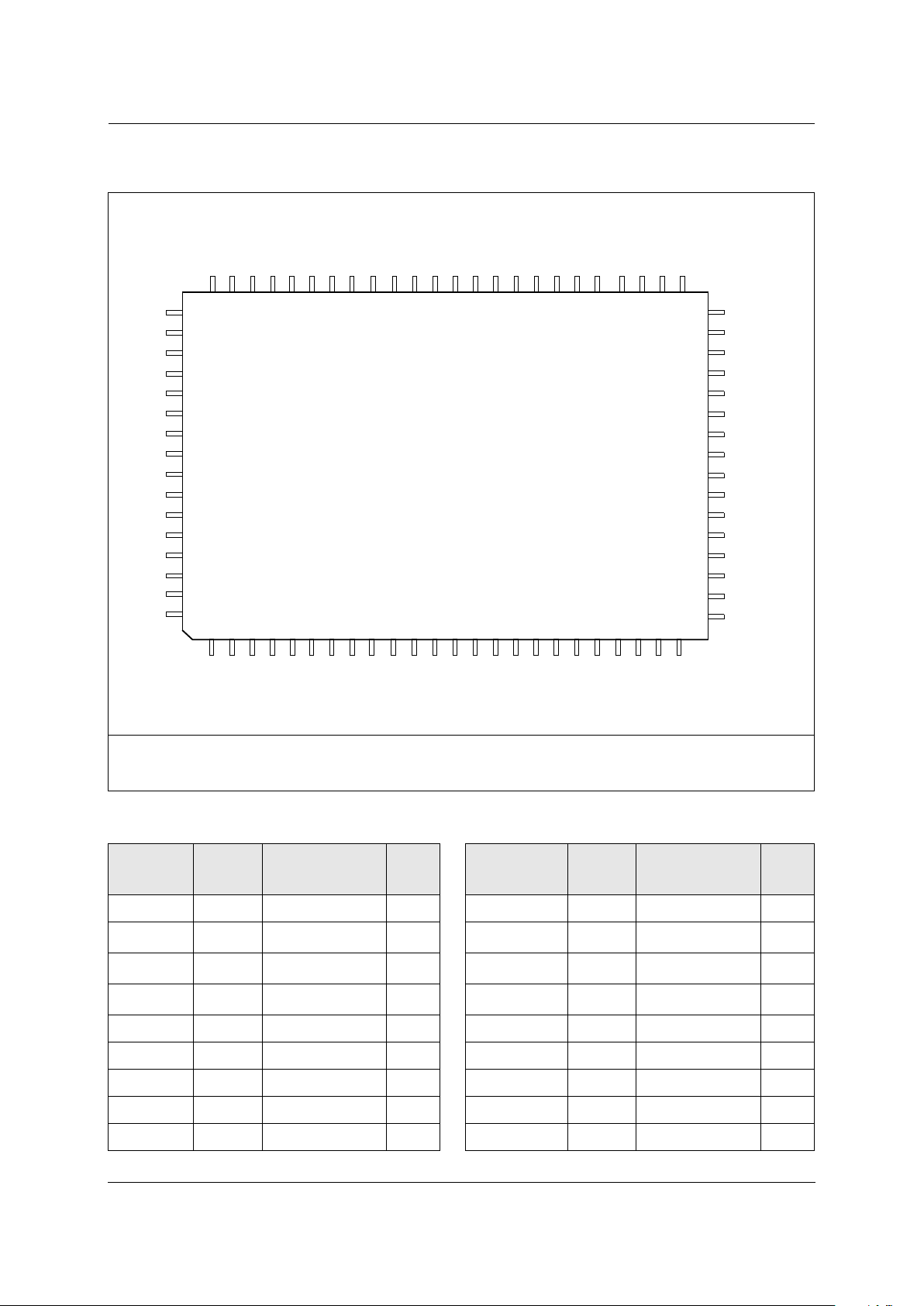

Functional Block Diagram

Distinguishing Features

• Supports All HDSL Bit Rates

– 2 pair T1 standard (784 kbps)

– 2 pair E1 standard (1168 kbps)

– 3 pair E1 standard (784 kbps)

– 1/2/3 pair custom (Nx64 kbps,

N=2-36)

• T1/E1 Primary Rate (PCM) Channel

– Connects to Conexant E1/T1

Framers

– Framed or unframed mode

– Sync/Async payload mapping

– Clock recovery/jitter attenuation

– PRBS/fixed test patterns

– BER measurement

• HDSL Channels

– Connects to Conexant ZipWire

Transceivers

– Three independent serial channels

– Central, remote, or repeater

– Overhead (HOH) management

– Programmable path delays

– Error performance monitoring

– Software controlled EOC and IND

– Auxiliary payload/Z-bit data link

– Master loop ID and interchange

– Auto tip/ring reversal

• Programmable Data Routing

– PCM timeslots – HDSL payload

– Drop/Insert – HDSL payload

– Auxiliary – HDSL payload

– PRBS/Fixed – PCM or HDSL

– PCM and HDSL loopbacks

•Intel

®

or Motorola® MPU interface

• CMOS technology, 3.3 V operation

• 68-pin PLCC or 80-pin PQFP

Applications

• Full, Fractional or Multipoint T1/E1

• Single and Multichannel Repeaters

• Voice Pair Gain Systems

• Wireless LAN/PBX

• PCS, Cellular Base Station

• Fiber Access/Distribution

• Loop Carrier, Remote Switches

• Subscriber Line Modem

MPU

Registers

DPLL

Receive

Framer

Payload

Mapper

Elastic

Store

Stuff

2B1Q

Decoder

LB

Mapper

HOH Mux

2B1Q

Encoder

Elastic

Store

LB

PRBS

BER

PCM Formatter

Timeslot Router

HDSL

Channels

1, 2, 3

Drop

Insert

PCM

Channel

Microprocessor

PLL Filter

D8953BDSB Conexant

Information provided by Conexant Syste ms, Inc. (Conexant) is believed to be accurate and reliable. However, no responsibility is

assumed by Conexant for its use, nor any infringement of patents or other rights of third parties which may result from its use. No

license is granted by implication or otherwise under any patent rights of Conexant other than for circuitry embodied in Conexant

products. Conexant reserves the right to change circuitry at any time without notice. This document is subject to change without

notice.

Conexant and “What’s Next in Communications Technologies” are trademarks of Conexant Systems, Inc.

Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered

trademarks of their respective companies. All other marks mentioned herein are the property of their respective holders.

© 1999 Conexant Systems, Inc.

Print ed in U.S.A.

All Rights Reserved

Reader Response:

To improve the qu ali ty o f our publicatio ns, we welcome your feedback. Please send c om me nts or

suggestions via e-mail to Conexant Reader Response@conexant.com. Sorry, we can't answer your technical

questions at this address. Please contact your local Conexant sales office or local field applications engineer if you

have technical questions.

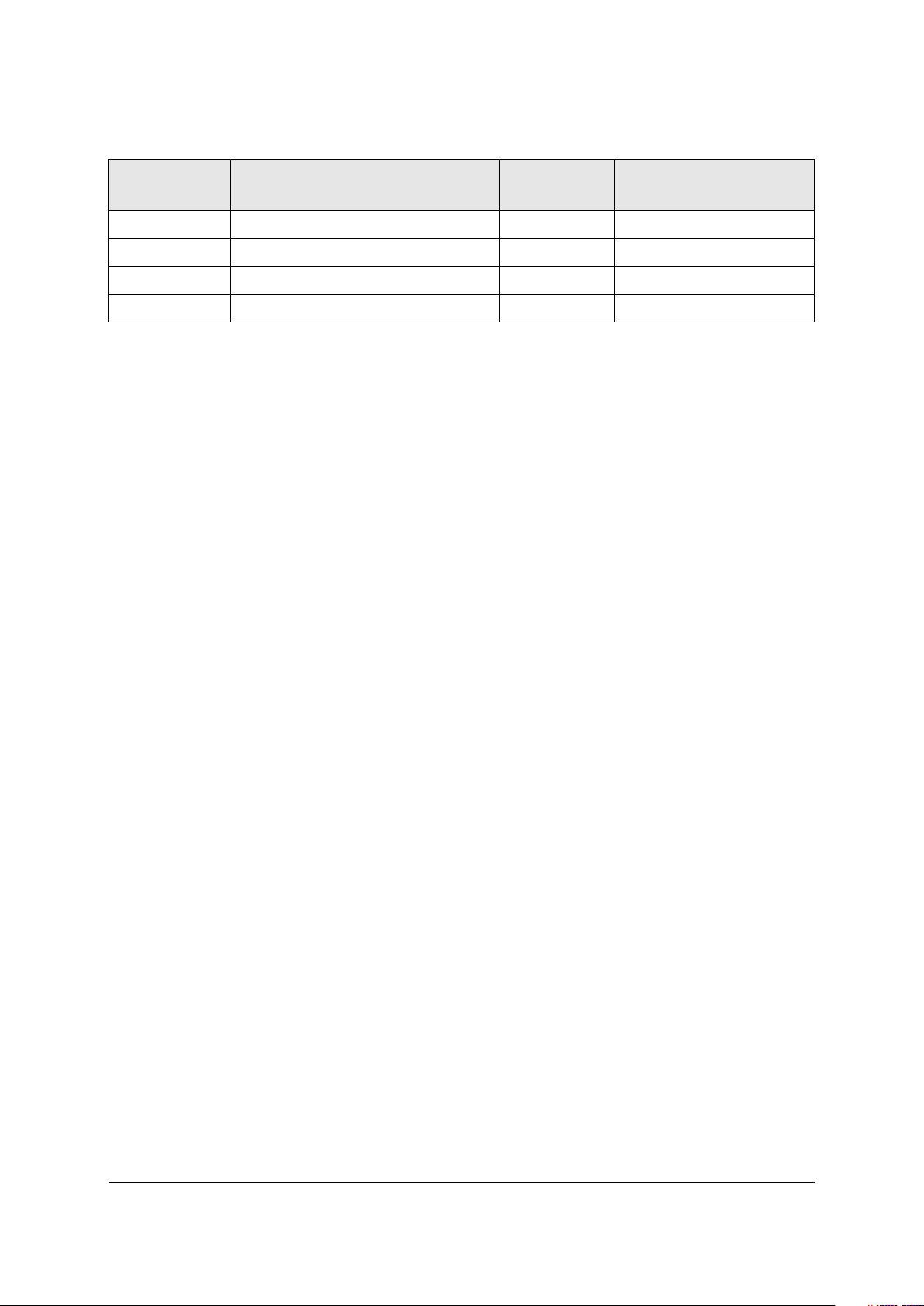

Ordering Information

Order Number Package

Number of

HDSL Channels

Operating Temperature Range

RS8953BEPF 80–Pin Plastic Quad Flat Pack (PQFP) 3 –40°C to +85°C

RS8953BEPJ 68–Pin Plastic Leaded Chip Carrier (PLCC) 3 –40°C to +85°C

RS8953SPB EPF 80–Pin Plastic Quad Flat Pack (PQFP) 1 –40°C to +85°C

RS8953SPB EPJ 68–Pin Plastic Leaded Chip Carrier (PLCC) 1 –40°C to +85°C

N8953BDSB Conexant iii

Table of Contents

List of Figures

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xi

List of Tables

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xiii

1.0 HDSL Systems

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1 HTU Applications

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1.1 Repeaters

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.1.2 Fractional Transport

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.1.3 Switching Systems

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.1.4 Loop Carrier/Pair Gain

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

1.1.5 Point-to-Multipoint

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.1.6 Subscriber Modem

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.2 System Interfaces

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

2.0 Pin Descriptions

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.1 Pin Assignments

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.2 Signal Definitions

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

3.0 Circuit Descriptions

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1 MPU Interface

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1.1 Address/Data Bus

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.1.2 Bus Controls

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.1.3 Interrupt Request

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.1.4 Hardware Reset

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.2 PCM Channel

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3.2.1 PCM Transmit

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.2.1.1 Transmit Synchronization

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3.2.1.2 Transmit Routing Table

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.2.1.3 PRBS Generator

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.2.1.4 Drop/Insert Channel

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

3.2.1.5 TFIFO Water Levels

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

3.2.2 PCM Receive

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

Table of Contents

RS8953B/8953SPB

HDSL Channel Unit

iv Conexant N8953BDSB

3.2.2.1 Receive Synchronization

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

3.2.2.2 Receive Combination Table

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

3.2.2.3 BER Meter

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

3.2.2.4 RFIFO Water Level

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

3.3 Clock Recovery DPLL

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15

3.4 Loopbacks

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

3.5 HDSL Channel

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19

3.5.1 HDSL Transmit

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-24

3.5.1.1 Transmit Payload Mapper

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-24

3.5.1.2 HOH Multiplexer

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-24

3.5.1.3 CRC Calculation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-25

3.5.1.4 Scrambler

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-25

3.5.1.5 STUFF Generator

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-25

3.5.1.6 2B1Q Encoder

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-26

3.5.1.7 HDSL Auxiliary Transmit

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-27

3.5.2 HDSL Receive

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-28

3.5.2.1 2B1Q Decoder

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-28

3.5.2.2 HDSL Receive Framer

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-29

3.5.2.3 Descrambler

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-31

3.5.2.4 CRC Checking

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-32

3.5.2.5 HOH Demux

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-32

3.5.2.6 Receive Payload Mapper

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-32

3.5.2.7 HDSL Auxiliary Receive

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-32

3.6 PRA Function

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-34

3.6.1 Transferring Data from HDSL to RSER

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-34

3.6.2 Definitions of Detection Algorithms

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-35

3.6.3 Inserting Data Transferred from HDSL to RSER

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-35

3.6.4 Transferring Data from TSER to HDSL

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-35

3.6.5 Inserting Data Transferred from TSER to HDSL

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-36

4.0 Registers

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

4.1 Address Map

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

4.2 HDSL Transmit

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

RS8953B/8953SPB

Table of Contents

HDSL Channel Unit

N8953BDSB Conexant v

0x00—Transmit Embedded Operations Channel (TEOC_LO)

. . . . . . . . . . . . . . . . . . . . . 5-10

0x01—Transmit Embedded Operations Channel (TEOC_HI)

. . . . . . . . . . . . . . . . . . . . . . 5-10

0x02—Transmit Indicator Bits (TIND_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

0x03—Transmit Indicator Bits (TIND_HI)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

0x04—Transmit Z-Bits (TZBIT_1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

0xDF—Transmit Z-Bits (TZBIT_2)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

0xE0—Transmit Z-Bits (TZBIT_3)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

0xE1—Transmit Z-Bits (TZBIT_4)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

0xE2—Transmit Z-Bits (TZBIT_5)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

0xE3—Transmit Z-Bits (TZBIT_6)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

0x05—Transmit FIFO Water Level (TFIFO_WL)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

0x06—Transmit Command Register 1 (TCMD_1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

0x07—Transmit Command Register 2 (TCMD_2)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13

4.3 Transmit Payload Mapper

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

0x08—Transmit Payload Map (TMAP_1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

0x09—Transmit Payload Map (TMAP_2)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

0x0A—Transmit Payload Map (TMAP_3)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

0x0B—Transmit Payload Map (TMAP_4)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

0x0C—Transmit Payload Map (TMAP_5)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

0x0F—Transmit Payload Map (TMAP_6)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-16

0x10—Transmit Payload Map (TMAP_7)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-16

0x11—Transmit Payload Map (TMAP_8)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-16

0x12—Transmit Payload Map (TMAP_9)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-16

0x0D—Transmit FIFO Reset (TFIFO_RST)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-17

0x0E—Scrambler Reset (SCR_RST)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-17

4.4 HDSL Receive

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-18

0x60—Receive Command Register 1 (RCMD_1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-19

0x61—Receive Command Register 2 (RCMD_2)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20

0x62—Receive Elastic Store FIFO Reset (RFIFO_RST)

. . . . . . . . . . . . . . . . . . . . . . . . . . 5-21

0x63—Receive Framer Synchronization Reset (SYNC_RST)

. . . . . . . . . . . . . . . . . . . . . 5-21

4.5 Receive Payload Mapper

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-22

0x64—Receive Payload Map (RMAP_1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-22

0x65—Receive Payload Map (RMAP_2)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-22

0x66—Receive Payload Map (RMAP_3)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-22

0x69—Receive Payload Map (RMAP_4)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-22

0x6A—Receive Payload Map (RMAP_5)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-22

0x6B—Receive Payload Map (RMAP_6)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-23

0x67—Error Count Reset (ERR_RST)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-23

0x68—Receive Signaling Location (RSIG_LOC)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-23

4.6 PCM Formatter

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25

0xC0—TSER Frame Bit Location (TFRAME_LOC_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . . 5-26

0xC1—TSER Frame Bit Location (TFRAME_LOC_HI)

. . . . . . . . . . . . . . . . . . . . . . . . . . . 5-26

Table of Contents

RS8953B/8953SPB

HDSL Channel Unit

vi Conexant N8953BDSB

0xC2—TSER Multiframe Bit Location (TMF_LOC)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-26

0xC3—RSER Frame Bit Location (RFRAME_LOC_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . . 5-26

0xC4—RSER Frame Bit Location (RFRAME_LOC_HI)

. . . . . . . . . . . . . . . . . . . . . . . . . . 5-27

0xC5—RSER Multiframe Bit Location (RMF_LOC)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-27

0xC6—PCM Multiframe Length (MF_LEN)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-27

0xC7—PCM Multiframes per HDSL Frame (MF_CNT)

. . . . . . . . . . . . . . . . . . . . . . . . . . 5-28

0xC8—PCM Frame Length (FRAME_LEN_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28

0xC9—PCM Frame Length (FRAME_LEN_HI)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28

4.7 HDSL Channel Configuration

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29

0xCA—HDSL Frame Length (HFRAME_LEN_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29

0xF5—HDSL Frame Length (HFRAME_LEN_HI)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30

0xF8—HDSL Frame Length (HFRAME2_LEN_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30

0xF9—HDSL Frame Length (HFRAME2_LEN_HI)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30

0xFA—HDSL Frame Length (HFRAME3_LEN_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30

0xFB—HDSL Frame Length (HFRAME3_LEN_HI)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-31

0xCB—SYNC Word A (SYNC_WORD_A)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-31

0xCC—SYNC Word B (SYNC_WORD_B)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-31

0xCD—RX FIFO Water Level (RFIFO_WL_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-31

0xCE—RX FIFO Water Level (RFIFO_WL_HI)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-32

4.8 Transmit Bit Stuffing Thresholds

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-32

0xCF—Bit Stuffing Threshold A (STF_THRESH_A_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . 5-33

0xD0—Bit Stuffing Threshold A (STF_THRESH_A_HI)

. . . . . . . . . . . . . . . . . . . . . . . . . . 5-33

0xD1—Bit Stuffing Threshold B (STF_THRESH_B_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . 5-33

0xD2—Bit Stuffing Threshold B (STF_THRESH_B_HI)

. . . . . . . . . . . . . . . . . . . . . . . . . . 5-33

0xD3—Bit Stuffing Threshold C (STF_THRESH_C_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . 5-33

0xD4—Bit Stuffing Threshold C (STF_THRESH_C_HI)

. . . . . . . . . . . . . . . . . . . . . . . . . . 5-34

4.9 DPLL Configuration

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-35

0xD5—DPLL Residual (DPLL_RESID_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-35

0xD6—DPLL Residual (DPLL_RESID_HI)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-36

0xD7—DPLL Factor (DPLL_FACTOR)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-36

0xD8—DPLL Gain (DPLL_GAIN)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-37

0xDB—DPLL Phase Detector Init (DPLL_PINI)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-38

0xF6—Reset DPLL Phase Detector (DPLL_RST)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-38

4.10 Data Path Options

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-39

0xDC—Data Bank Pattern 1 (DBANK_1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-39

0xDD—Data Bank Pattern 2 (DBANK_2)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-39

0xDE—Data Bank Pattern 3 (DBANK_3)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-40

0xEA—Fill Pattern (FILL_PATT)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-40

0xE4—Transmit Stuff Bit Value (TSTUFF)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-40

0xED—Transmit Routing Table (ROUTE_TBL)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-41

0xEE—Receive Combination Table (COMBINE_TBL)

. . . . . . . . . . . . . . . . . . . . . . . . . . . 5-42

0xF2—Receive Signaling Table (RSIG_TBL)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-43

4.11 Common Command

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-44

0xE5—Command Register 1 (CMD_1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-44

0xE6—Command Register 2 (CMD_2)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-45

RS8953B/8953SPB

Table of Contents

HDSL Channel Unit

N8953BDSB Conexant vii

0xE7—Command Register 3 (CMD_3)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-46

0xE8—Command Register 4 (CMD_4)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-47

0xE9—Command Register 5 (CMD_5)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-47

0xF3—Command Register 6 (CMD_6)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-48

0xF4—Command Register 7 (CMD_7)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-49

4.12 Interrupt and Reset

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-51

0xEB—Interrupt Mask Register (IMR)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-51

0xEC—Interrupt Clear Register (ICR)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-51

0xEF—Reset BER Meter/Start BER Measurement (BER_RST)

. . . . . . . . . . . . . . . . . . . . 5-52

0xF0—Reset PRBS Generator (PRBS_RST)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-52

0xF1—Reset Receiver (RX_RST)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-52

4.13 Receive/Transmit Status

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-53

0x00—Receive Embedded Operations Channel (REOC_LO)

. . . . . . . . . . . . . . . . . . . . . . 5-53

0x01—Receive Embedded Operations Channel (REOC_HI)

. . . . . . . . . . . . . . . . . . . . . . 5-54

0x02—Receive Indicator Bits (RIND_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-54

0x03—Receive Indicator Bits (RIND_HI)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-54

0x04—Receive Z-Bits (RZBIT_1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-54

0x18—Receive Z-Bits (RZBIT_2)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-55

0x19—Receive Z-Bits (RZBIT_3)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-55

0x1A—Receive Z-Bits (RZBIT_4)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-55

0x1B—Receive Z-Bits (RZBIT_5)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-55

0x1C—Receive Z-Bits (RZBIT_6)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-55

0x05—Receive Status 1 (STATUS_1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-55

0x06—Receive Status 2 (STATUS_2)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-57

0x07—Transmit Status (STATUS_3)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-58

0x21—CRC Error Count (CRC_CNT)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-58

0x22—Far End Block Error Count (FEBE_CNT)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-59

4.14 Common Status

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-60

0x1D—Bit Error Rate Meter (BER_METER)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-60

0x1E—BER Status (BER_STATUS)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-61

0x1F—Interrupt Request Register (IRR)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-61

0x28—DPLL Residual Output (RESID_OUT_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-62

0x20—DPLL Residual Output (RESID_OUT_HI)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-62

0x30—Interrupt Mask Register (IMR)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-62

0x38—DPLL Phase Error (PHS_ERR)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-63

0x39—Multiframe Sync Phase Low (MSYNC_PHS_LO)

. . . . . . . . . . . . . . . . . . . . . . . . 5-63

0x3A—Multiframe Sync Phase High (MSYNC_PHS_HI)

. . . . . . . . . . . . . . . . . . . . . . . . 5-63

0x3B—Shadow Write (SHADOW_WR)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-64

0x3C—Error Status (ERR_STATUS)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-64

4.15 PRA Transmit Read

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-65

0x40—PRA Transmit Control Register 0 (TX_PRA_CTRL0)

. . . . . . . . . . . . . . . . . . . . . . 5-65

0x41—PRA Transmit Control Register 1 (TX_PRA_CTRL1)

. . . . . . . . . . . . . . . . . . . . . . 5-66

Table of Contents

RS8953B/8953SPB

HDSL Channel Unit

viii Conexant N8953BDSB

0x42—PRA Transmit Monitor Register 1 (TX _PRA_MON1)

. . . . . . . . . . . . . . . . . . . . . 5-67

0x43—PRA Transmit E-Bits Counter (TX _PRA_E_CNT)

. . . . . . . . . . . . . . . . . . . . . . . . 5-67

0x45—PRA Transmit In-Band Code (TX_PRA_CODE)

. . . . . . . . . . . . . . . . . . . . . . . . . . 5-67

0x46—PRA Transmit Monitor Register 0 (TX_PRA_MON0)

. . . . . . . . . . . . . . . . . . . . . . 5-68

0x47—PRA Transmit Monitor Register 2 (TX_PRA_MON2)

. . . . . . . . . . . . . . . . . . . . . . 5-68

4.16 PRA Transmit Write

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-69

0x70—PRA Transmit Control Register 0 (TX_PRA_CTRL0)

. . . . . . . . . . . . . . . . . . . . . . 5-69

0x71—PRA Transmit Control Register 1 (TX_PRA_CTRL1)

. . . . . . . . . . . . . . . . . . . . . . 5-70

0x72—PRA Transmit Bits Buffer 1 (TX_BITS_BUFF1)

. . . . . . . . . . . . . . . . . . . . . . . . . . 5-71

0x73—PRA Transmit TMSYNC offset Register (TX_PRA_TMSYNC_OFFSET)

. . . . . . . . . 5-71

0x74—PRA Transmit Bits Buffer 0 (TX_BITS_BUFF0)

. . . . . . . . . . . . . . . . . . . . . . . . . . 5-72

4.17 PRA Receive Read

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-73

0x80—PRA Receive Control Register 0 (RX_PRA_CTRL0)

. . . . . . . . . . . . . . . . . . . . . . 5-73

0x81—PRA Receive Control Register 1 (RX_PRA_CTRL1)

. . . . . . . . . . . . . . . . . . . . . . 5-74

0x82—PRA Receive Monitor Register 1 (RX _PRA_MON1)

. . . . . . . . . . . . . . . . . . . . . . 5-75

0x83—PRA Receive E bits Counter (RX_PRA_E_CNT)

. . . . . . . . . . . . . . . . . . . . . . . . . 5-75

0x84—PRA Receive CRC4 Errors Counter (RX_PRA_CRC_CNT)

. . . . . . . . . . . . . . . . . . 5-75

0x85—PRA Receive In-Band Code (RX_PRA_CODE)

. . . . . . . . . . . . . . . . . . . . . . . . . . . 5-76

0x86—PRA Receive Monitor Register 0 (RX_PRA_MON0)

. . . . . . . . . . . . . . . . . . . . . . 5-76

0x87—PRA Receive Monitor Register 2 (RX_PRA_MON2)

. . . . . . . . . . . . . . . . . . . . . . 5-76

4.18 PRA Receive Write

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-77

0xB0—PRA Receive Control Register 0 (RX_PRA_CTRL0)

. . . . . . . . . . . . . . . . . . . . . . 5-77

0xB1—PRA Receive Control Register 1 (RX_PRA_CTRL1)

. . . . . . . . . . . . . . . . . . . . . . 5-78

0xB2—PRA Receive Bits Buffer 1 (RX_BITS_BUFF1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . 5-79

0xB4—PRA Receive Bits Buffer 0 (RX_BITS_BUFF0)

. . . . . . . . . . . . . . . . . . . . . . . . . . . 5-79

5.0 Applications

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

5.1 Interfacing to a Conexant HDSL Transceiver

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

5.2 Interfacing to the Bt8370 E1/T1 Framer

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

5.3 Interfacing to the 68302 Processor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

5.4 Interfacing to the 8051 Controller

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

5.5 References

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6.0 Electrical and Timing Specifications

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

6.1 Absolute Maximum Ratings

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

6.1.1 Recommended Operating Conditions

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

6.1.2 Electrical Characteristics

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

6.1.3 Timing Requirements

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

6.1.4 Switching Characteristics

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

6.1.5 MPU Interface Timing

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

6.2 Mechanical Specifications

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-10

7.0 Acronyms, Abbreviations and Notation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

7.1 Arithmetic Notation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

RS8953B/8953SPB

Table of Contents

HDSL Channel Unit

N8953BDSB Conexant ix

7.1.1 Bit Numbering

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

7.1.2 Acronyms and Abbreviations

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

Appendix A

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

A.1 Differences Between Bt8953A and RS8953B

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

Appendix B: Bt8953A/RS8953B Product Bulletin

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

B.1 BCLK Phase Constraints In Repeater Mode; Non-Conformance Product Affected: Bt8953A and

RS8953B

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

Table of Contents

RS8953B/8953SPB

HDSL Channel Unit

x Conexant N8953BDSB

RS8953B/8953SPB

List of Figures

HDSL Channel Unit

N8953BDSB Conexant xi

List of Figures

Figure 1-1. HTU Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

Figure 1-2. Repeater System Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-2

Figure 1-3. Drop/Insert System Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-3

Figure 1-4. Switch/Mux System Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Figure 1-5. Voice (Pairgain/Cellular/PCS) System Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Figure 1-6. Point-to-Multipoint (Fractional) System Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

Figure 1-7. Subscriber Modem (Terminal) System Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

Figure 1-8. RS8953B System Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

Figure 2-1. Three-Pair PLCC Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2

Figure 2-2. Single-Pair PLCC Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

Figure 2-3. Three-Pair PQFP Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

Figure 2-4. Single-Pair PQFP Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

Figure 3-1. MPU Bus Control Logic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

Figure 3-2. MPU Interrupt Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

Figure 3-3. PCM Channel Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

Figure 3-4. PCM Transmit Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

Figure 3-5. PCM Transmit Sync Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

Figure 3-6. PCM Transmit Data Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

Figure 3-7. Drop/Insert Channel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

Figure 3-8. TFIFO Water Level Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

Figure 3-9. PCM Receive Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-10

Figure 3-10. PCM Receive Data Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

Figure 3-11. PCM Receive Sync Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

Figure 3-12. PRBS/BER Measurements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

Figure 3-13. RFIFO Water Level Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

Figure 3-14. DPLL Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15

Figure 3-15. PCM and HDSL Loopbacks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-17

Figure 3-16. 2T1 Frame Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-21

Figure 3-17. 2E1 Frame Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-22

Figure 3-18. 3E1 Frame Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-22

Figure 3-19. HDSL Transmitter Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-24

Figure 3-20. HDSL Auxiliary Channel Payload Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-27

Figure 3-21. HDSL Auxiliary Channel Z-bit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-27

Figure 3-22. HDSL Receiver Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-28

Figure 3-23. HDSL Receive Framer Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-30

Figure 3-24. Threshold Correlation Effect on Expected Sync Locations. . . . . . . . . . . . . . . . . . . . . . . . . 3-31

Figure 3-25. HDSL Auxiliary Receive Payload Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-32

Figure 3-26. HDSL Auxiliary Receive Z-bit Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-33

List of Figures

RS8953B/8953SPB

HDSL Channel Unit

xii Conexant N8953BDSB

Figure 3-27. An Overview of the PRA Transfer of Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-34

Figure 4-1. Transmit Routing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-41

Figure 5-1. RS8953B HDSL Channel Unit to Conexant HDSL Transceiver Interconnection . . . . . . . . . . 6-2

Figure 5-2. RS8953B HDSL Channel Unit to Bt8360 DS1 Framer Interconnection . . . . . . . . . . . . . . . . 6-3

Figure 5-3. RS8953B to 68302 Processor Interconnection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

Figure 5-4. RS8953B HDSL Channel Unit to 8051 Controller Interconnection . . . . . . . . . . . . . . . . . . . 6-5

Figure 6-1. Input Clock Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

Figure 6-2. Input Setup and Hold Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

Figure 6-3. Output Clock and Data Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

Figure 6-4. MPU Write Timing, MPUSEL = 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-8

Figure 6-5. MPU Read Timing, MPUSEL = 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-8

Figure 6-6. MPU Write Timing, MPUSEL = 0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-9

Figure 6-7. MPU Read Timing, MPUSEL = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

Figure 6-8. 68-Pin PLCC Package Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-10

Figure 6-9. 80–Pin PQFP Mechanical Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

RS8953B/8953SPB

List of Tables

HDSL Channel Unit

N8953BDSB Conexant xiii

List of Tables

Table 2-1. Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

Table 2-2. Signal Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

Table 3-1. PCM And HDSL Loopbacks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-18

Table 3-2. HDSL Frame Structure and Overhead Bit Allocation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-20

Table 3-3. HDSL Frame Mapping Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-23

Table 3-4. 2B1Q Encoder Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-26

Table 3-5. Z-Bit Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-26

Table 3-6. 2B1Q Decoder Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-28

Table 4-1. Register Summary Address Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-3

Table 4-2. HDSL Transmit Write Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

Table 4-3. HDSL Receive Write Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-18

Table 4-4. PCM Formatter Write Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25

Table 4-5. HDSL Channel Configuration Write Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29

Table 4-6. DPLL Configuration Write Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-35

Table 4-7. Data Path Options Write Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-39

Table 4-8. Common Command Write Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-44

Table 4-9. Interrupt and Reset Write Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-51

Table 4-10. Receive and Transmit Status Read Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-53

Table 4-11. Common Status Read Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-60

Table 4-12. PRA Transmit Read Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-65

Table 4-13. PRA Transmit Write Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-69

Table 4-14. PRA Receive Read Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-73

Table 4-15. PRA Receive Write Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-77

Table 6-1. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

Table 6-2. Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

Table 6-3. Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

Table 6-4. Clock Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

Table 6-5. Data Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

Table 6-6. Input Clock Edge Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

Table 6-7. Clock and Data Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

Table 6-8. Output Clock Edge Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

Table 6-9. MPU Interface Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

Table 6-10. MPU Interface Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-7

Table A-1. Pin Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

Table A-2. Power Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

List of Tables

RS8953B/8953SPB

HDSL Channel Unit

xiv Conexant N8953BDSB

N8953BDSB Conexant 1-1

1

1.0 HDSL Systems

1.1 HTU Applications

The High-Bit-Rate Digital Subscriber Line (HDSL) is a simultaneous full-duplex

transmission scheme which uses twisted-pair wire cables as the physical medium

to transport signals between standard types of network or subscriber

communication interfaces. A complete HDSL system consists of two pieces of

terminal equipment connected by 1, 2, or 3 wire pairs. Each HDSL Terminal Unit

(HTU) translates standard interface signals into HDSL payload for transmission,

and reconstructs the standard interface from received payload. Bellcore standards

define a 1.544 Mbps T1 transport application that uses two HDSL wire pairs

(2T1), each operating at 784 kpbs. ETSI standards define a 2.048 Mbps E1

transport application using either two wire pairs (2E1), each operating at 1168

kpbs, or three wire pairs (3E1), each operating at 784 kpbs.

1.0 HDSL Systems

RS8953B/RS8953SPB

1.1 HTU Applications

HDSL Channel Unit

1-2 Conexant N8953BDSB

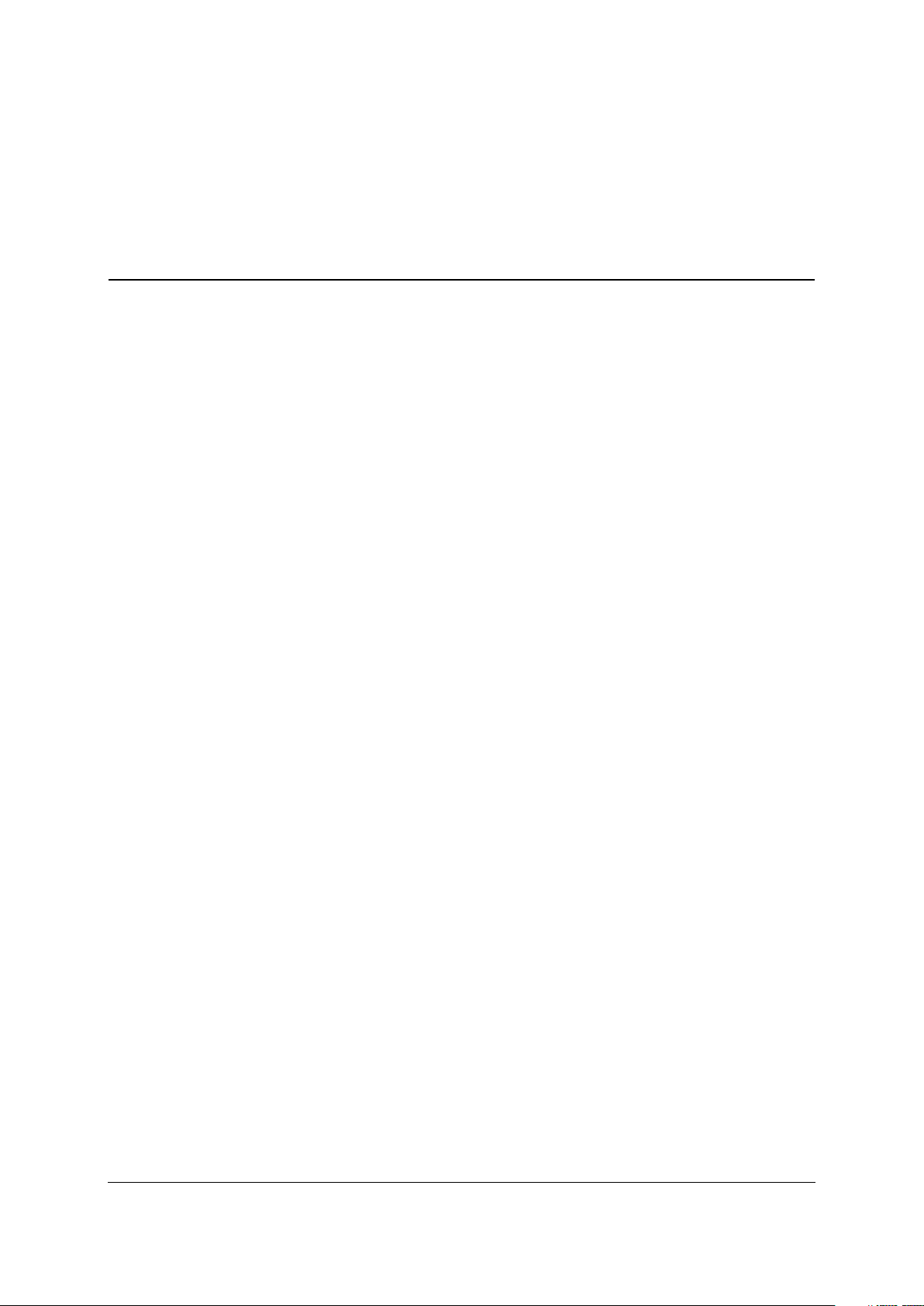

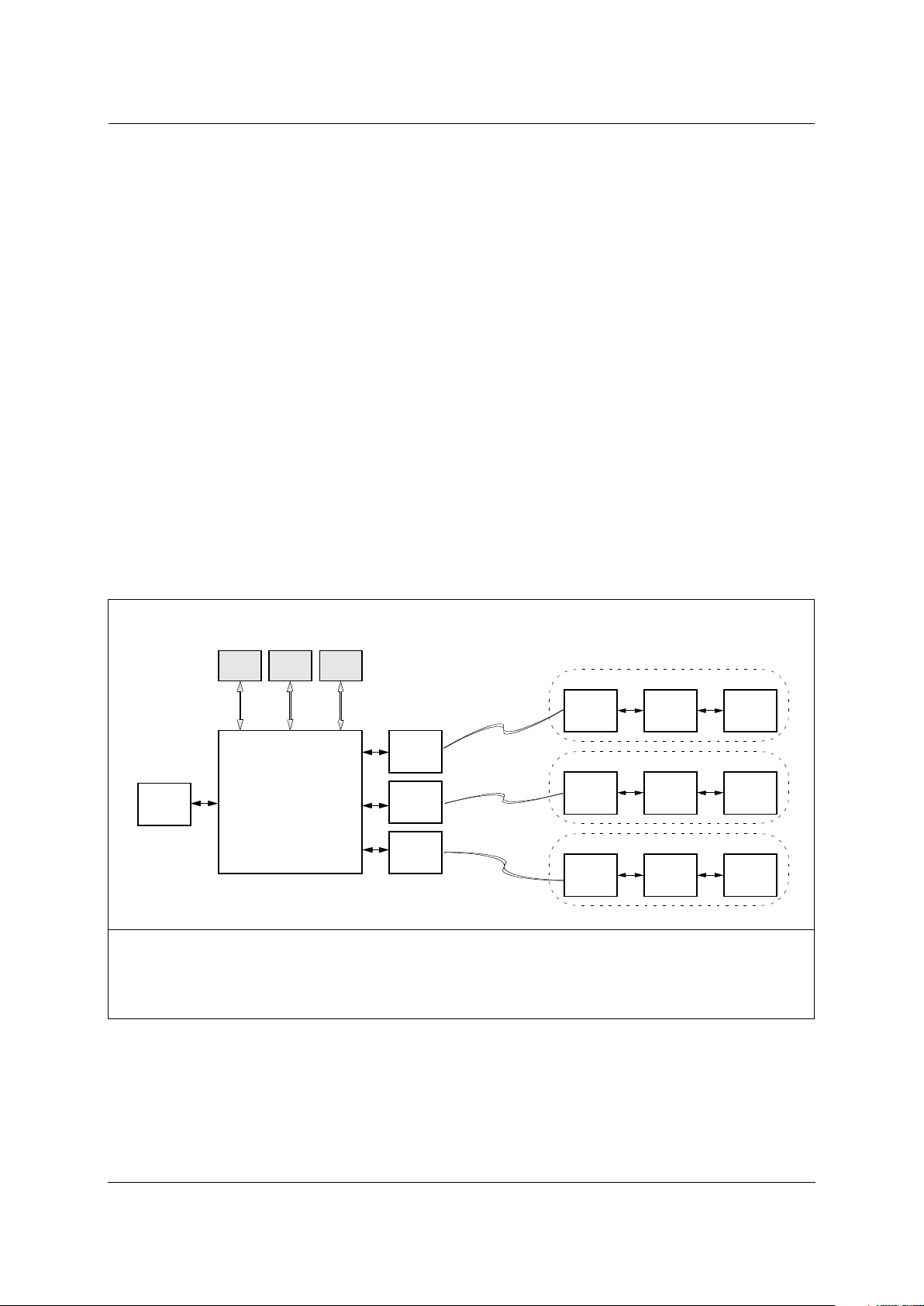

Figure 1-1 illustrates how an HDSL Terminal Unit (HTU) transports standard

T1/E1 signals. T1/E1 transceivers convert T1/E1 interface signals into a Pulse

Code Multiplexed (PCM) channel of clock, serial data, and optional frame sync.

ZipWire transceivers convert 2B1Q line signals to HDSL channels of clock, serial

data, and quat sync. The RS8953B translates between PCM and HDSL by

performing PCM timeslot and HDSL payload routing, data scrambling and

descrambling, overhead insertion and extraction, clock synchronization and clock

synthesis. The Microprocessor Unit (MPU) configures devices for the intended

application, manages overhead protocol, and monitors real-time performance.

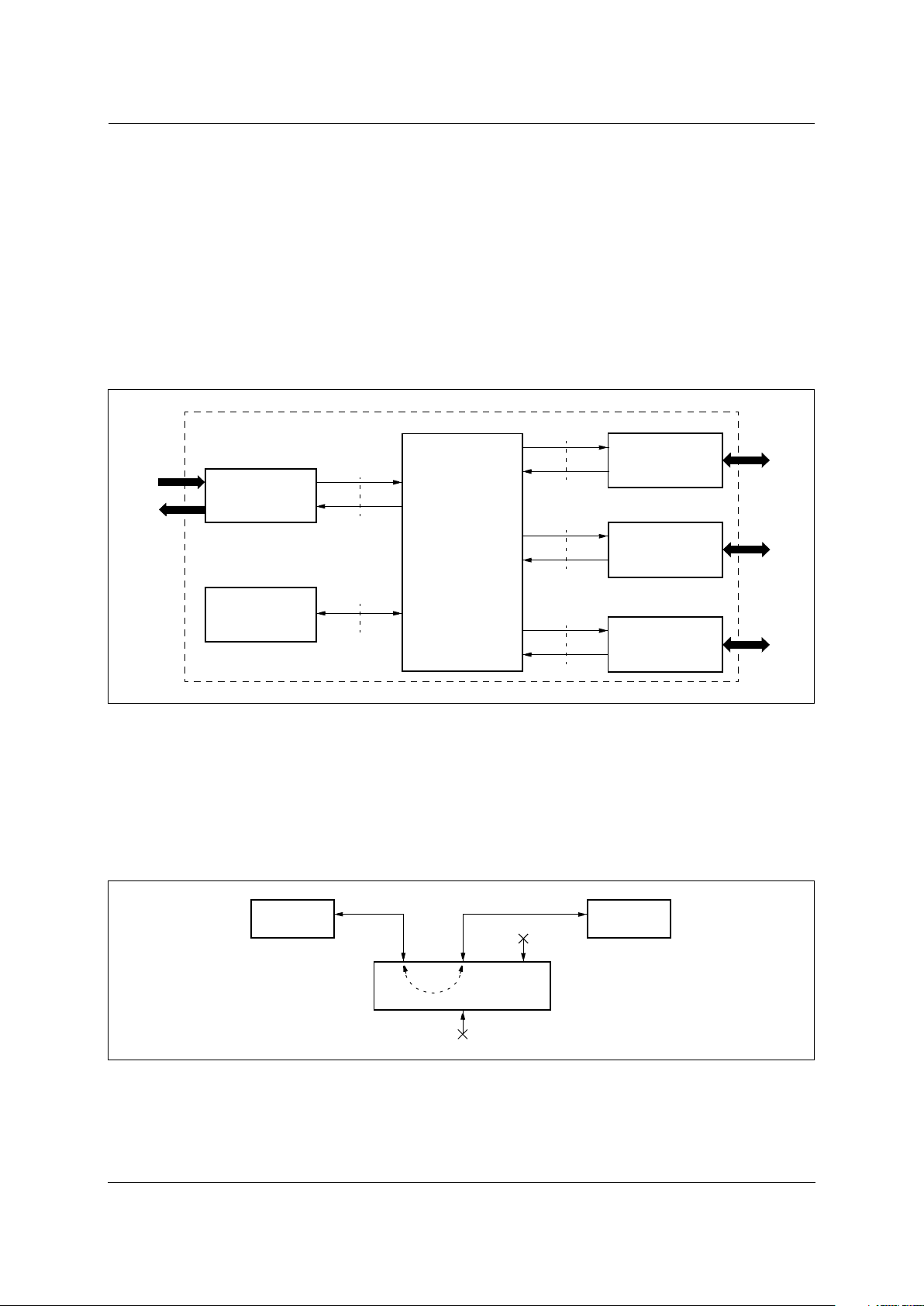

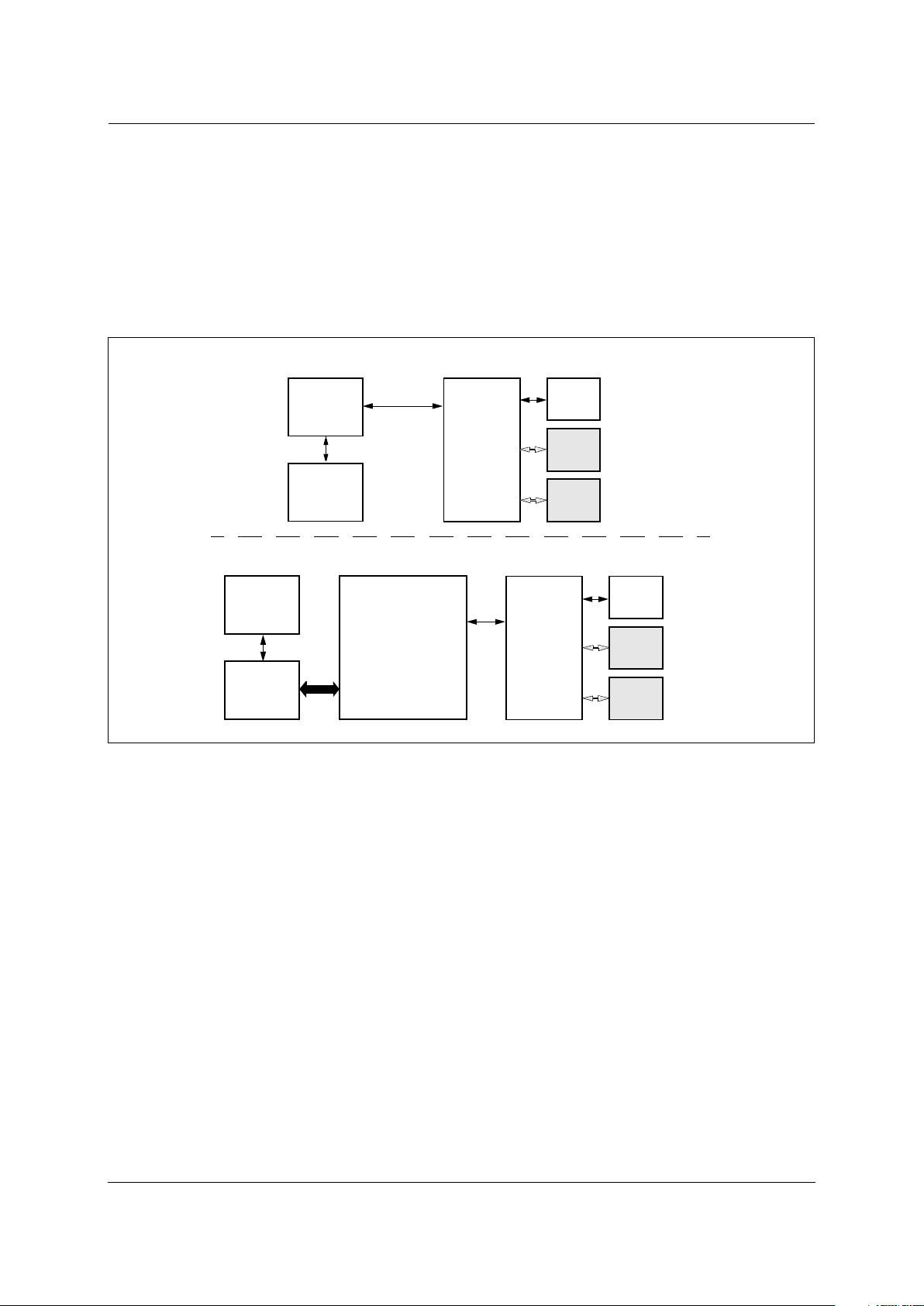

1.1.1 Repeaters

Figure 1-2 shows single pair repeaters placed in line between HDSL terminals to

extend transmission distance. RS8953B provides an internal cross-connect path

between HDSL channels 1 and 2 to support single pair repeaters.

Figure 1-1. HTU Block Diagram

PCM Channel

MPU Bus

HDSL

Channel 1

HDSL

Channel 2

HDSL

Channel 3

RS8953B

HDSL

Channel Unit

T1/E1

Transceiver

MPU

ZipWire Transceiver

ZipWire Transceiver

ZipWire Transceiver

CH1

CH2

CH3

Figure 1-2. Repeater System Block Diagram

RS8953B

PCM

CH1

CH2

CH3

RS8953B/RS8953SPB

1.0 HDSL Systems

HDSL Channel Unit

1.1 HTU Applications

N8953BDSB Conexant 1-3

1.1.2 Fractional Transport

Figure 1-3 illustrates a drop/insert application where only a portion of the PCM

channel bandwidth is transported over one or more HDSL wire pairs. The

RS8953B provides drop/insert indicator signals to control external data MUXes

and internal routing tables to map timeslots from either one of two synchronized

PCM data sources. For remote terminals using partial payloads, the PCM channel

may be configured to operate either at the standard interface rate or at the Nx64

effective payload rate.

Figure 1-3. Drop/Insert System Block Diagram

Mux

HDSL

CH1

HDSL

CH2

HDSL

CH3

PCMD/I

Optional

RS8953B HDSL Channel Unit

Transceiver

Drop

Insert

T1/E1

FIBER

or Other

Transceiver

T1/E1

FIBER

or Other

Mux

1.0 HDSL Systems

RS8953B/RS8953SPB

1.1 HTU Applications

HDSL Channel Unit

1-4 Conexant N8953BDSB

1.1.3 Switching Systems

Figure 1-4 illustrates how the RS8953B is incorporated into a digital switch or

multiplexer system that uses multiple HDSL lines to transport Nx64 or standard

T1/E1 applications. The RS8953B’s PCM timeslot router contains 64 table entries

that extends the maximum PCM channel rate to 64x64 or 4.096 Mbps. RS8953B

allows PCM channels at the central office (CO) and remote ends to operate at

different rates. For example, the PCM channel in a digital switch may connect to a

4.096 Mbps shelf bus, while the remote terminal connects to a T1/E1 standard

PCM channel.

Figure 1-4. Switch/Mux System Block Diagram

NOTE(S):

SLIP BUFFER = Optional frame SLIP BUFFER to align receive PCM with local master frame.

DS0 Switch Matrix

RS8953B RS8953B

CH1 CH2 CH3 CH1 CH2 CH3

Nx64 Nx64

SLIP

BUFFER

SLIP

BUFFER

RS8953B/RS8953SPB

1.0 HDSL Systems

HDSL Channel Unit

1.1 HTU Applications

N8953BDSB Conexant 1-5

1.1.4 Loop Carrier/Pair Gain

Figure 1-5 shows a channel bank application where the PCM channel connects a

bank of voice and/or data subscriber line interfaces using an Nx64 bus. The total

number of subscriber lines determines the PCM channel rate and determines how

many HDSL wire pairs are needed to transport the application up to the digital

loop carrier, cellular base station, network distribution element, or to the private

branch exchange. The RS8953B supplies the PCM frame sync reference and acts

as the PCM bus master for the remote channel bank. The RS8953B’s Digital

Phase Locked Loop (DPLL) clock recovery allows PCM channel rates down to

2x64 or 128 kpbs. Unpopulated PCM timeslots or HDSL payload bytes can be

replaced by an 8-bit programmable fixed pattern, or one of four Pseudo-Random

Bit Sequence (PRBS) patterns.

Figure 1-5. Voice (Pairgain/Cellular/PCS) System Block Diagram

NOTE(S):

SLI = Subscriber Line Interface

Loop, Access,

or Distribution

Node

CH1

CH2

CH3

RS8953B

SLI

1

SLI

n

Nx64

Bus

Optional

1.0 HDSL Systems

RS8953B/RS8953SPB

1.1 HTU Applications

HDSL Channel Unit

1-6 Conexant N8953BDSB

1.1.5 Point-to-Multipoint

Figure 1-6 shows fractional T1/E1 services delivered from the CO to multiple

remote sites in a Point-to-Multipoint (P2MP) application. The number of HDSL

wire pairs and PCM channel rates at each site is variable. The RS8953B provides

the ability to measure and compensate for misalignment between separate PCM

frame syncs coming from each remote site. By programming transmit delays from

PCM to HDSL frame syncs, each remote site can send its HDSL frames back to

the central office. The HDSL frames are then sufficiently aligned with the others

to be reconstructed into a single PCM frame at the central site. The RS8953B

accommodates large differential delays associated with the P2MP application. It

receives HDSL frame offsets to groom Channel Associated Signaling (CAS)

from different sites.

P2MP applications of primary rate ISDN transport are also supported, where

different LAPD channels are received from each remote site. The RS8953B

provides auxiliary HDSL channel inputs and outputs for the system to externally

insert and monitor transmitted or received HDSL payload bytes. Auxiliary HDSL

channels may alternately be configured to terminate the last 40 Z-bits through an

external data link controller.

Figure 1-6. Point-to-Multipoint (Fractional) System Block Diagram

NOTE(S):

1. SCC = Serial Communications Controller

2. LAPD = Link Access Procedure D-Channel

3. AUX = Auxiliary HDSL channel attaches to payload or Z-bits

RS8953B

Full

T1/E1

RS8953B

CH1

CH2

CH3

CH1

Partial

T1/E1

Site C

RS8953B

CH1

Partial

T1/E1

Site B

RS8953B

CH1

Partial

T1/E1

Site A

SCC SCC SCC

Aux1

Aux2

Aux3

Optional

Management Protocol

LAPD Signaling or

RS8953B/RS8953SPB

1.0 HDSL Systems

HDSL Channel Unit

1.1 HTU Applications

N8953BDSB Conexant 1-7

1.1.6 Subscriber Modem

Figure 1-7 shows an HDSL data modem application where a CPU processor

delivers PCM data directly to the RS8953B. Alternately, a multichannel

communications controller such as the Bt8071A can be used to manage the

transfer of data between the CPU and PCM channel through a local shared

memory.

Figure 1-7. Subscriber Modem (Terminal) System Block Diagram

Single Channel Payload

RS8953B

CH1

CH2

CH3

CPU

Memory

Serial

Port

Optional

RS8953B

CH1

CH2

CH3

PCM

Bt8071A

32-Channel

HDLC Controller

CPU

Shared

Multichannel Payload

Optional

Memory

1.0 HDSL Systems

RS8953B/RS8953SPB

1.2 System Interfaces

HDSL Channel Unit

1-8 Conexant N8953BDSB

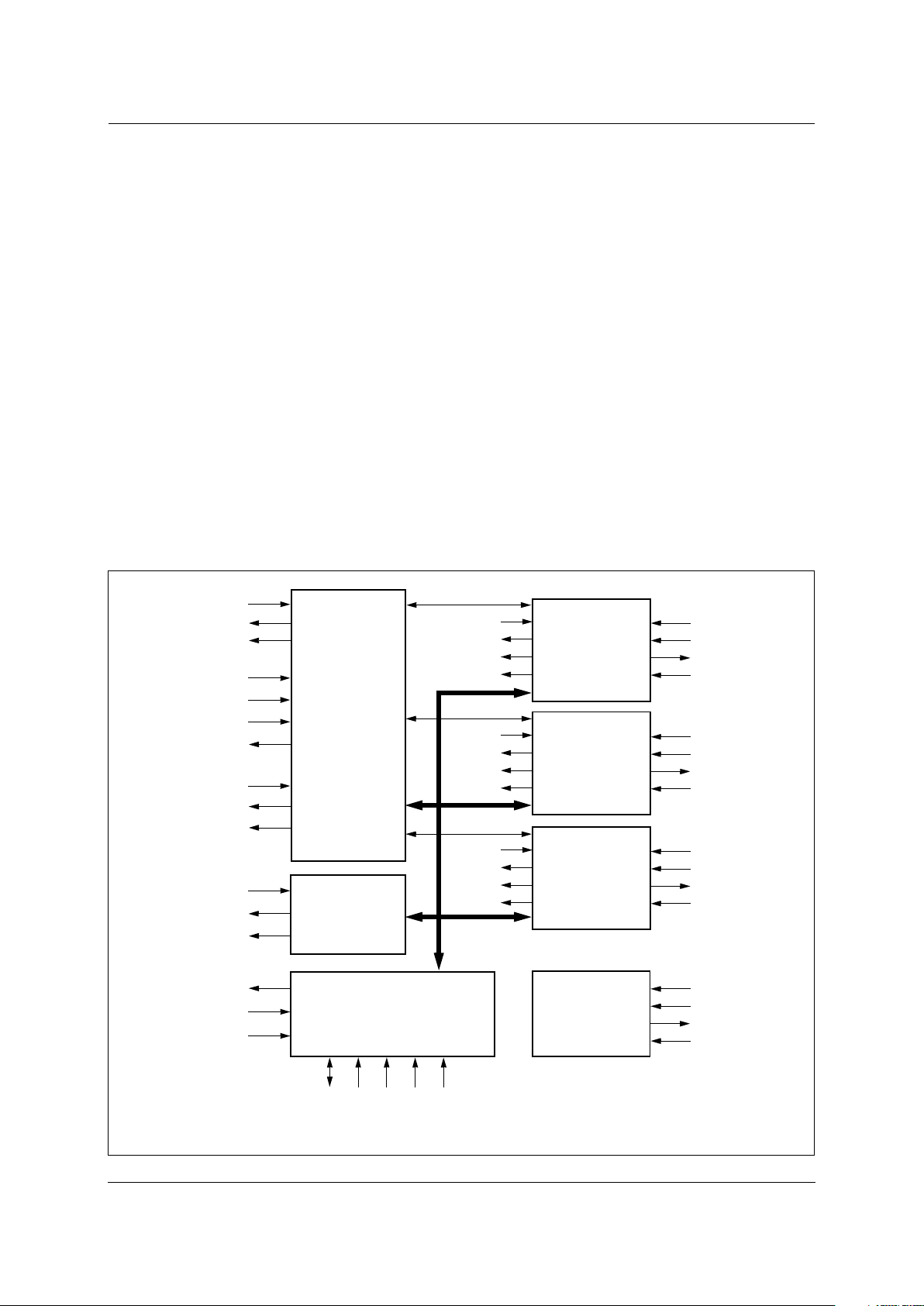

1.2 System Interfaces

System interfaces and associated signals for the RS8953B functional circuit

blocks are shown in Figure 1-8. Circuit blocks are described in sections 3 and 4,

and signals are defined in Ta bl e 2- 2 .

The single-pair version (RS8953SPBEPF and RS8953SPBEPJ) only supports

HDSL Channel 1. HDSL Channels 2 and 3 are not usable. Although only 1 HDSL

channel is usable, the internal registers are not changed from the 3 HDSL channel

versions. The single-pair versions (RS8953SPBEPF and RS8953SPBEPJ) only

supports HDSL Channel 1. HDSL Channels 2 and 3 are not usable. Although

only 1 HDSL channel is usable, the internal registers are not changed from the 3

HDSL channel versions. This means that the registers should be programmed

with the same value as if only HDSL channel 1 was used in a 3 channel version.

This allows the 3 channel version to be used for development, and without a

software change, a single-pair version used for production.

Figure 1-8. RS8953B System Interfaces

MCLK

RCLK

INSDAT

INSERT

DROP

EXCLK

TCLK

TSER

TMSYNC

MSYNC

RSER

RMSYNC

SCLK

INTR*

RST*

MPUSEL

TAUX1

TLOAD1

RAUX1

ROH1

TAUX2

TLOAD2

RAUX2

ROH2

TAUX3

TLOAD3

RAUX3

ROH3

BCLK1

QCLK1

TDAT1

RDAT1

BCLK2

QCLK2

TDAT2

RDAT2

BCLK3

QCLK3

TDAT3

RDAT3

AD[7:0]

CS*

ALE

RD*

WR*

PCM

Channel

HDSL

Channel1

HDSL

Channel2

HDSL

Channel3

MPU

Interface

DPLL

TCK

TDI

TDO

TMS

Tes t

Access

N8953BDSB Conexant 2-1

2

2.0 Pin Descriptions

2.1 Pin Assignments

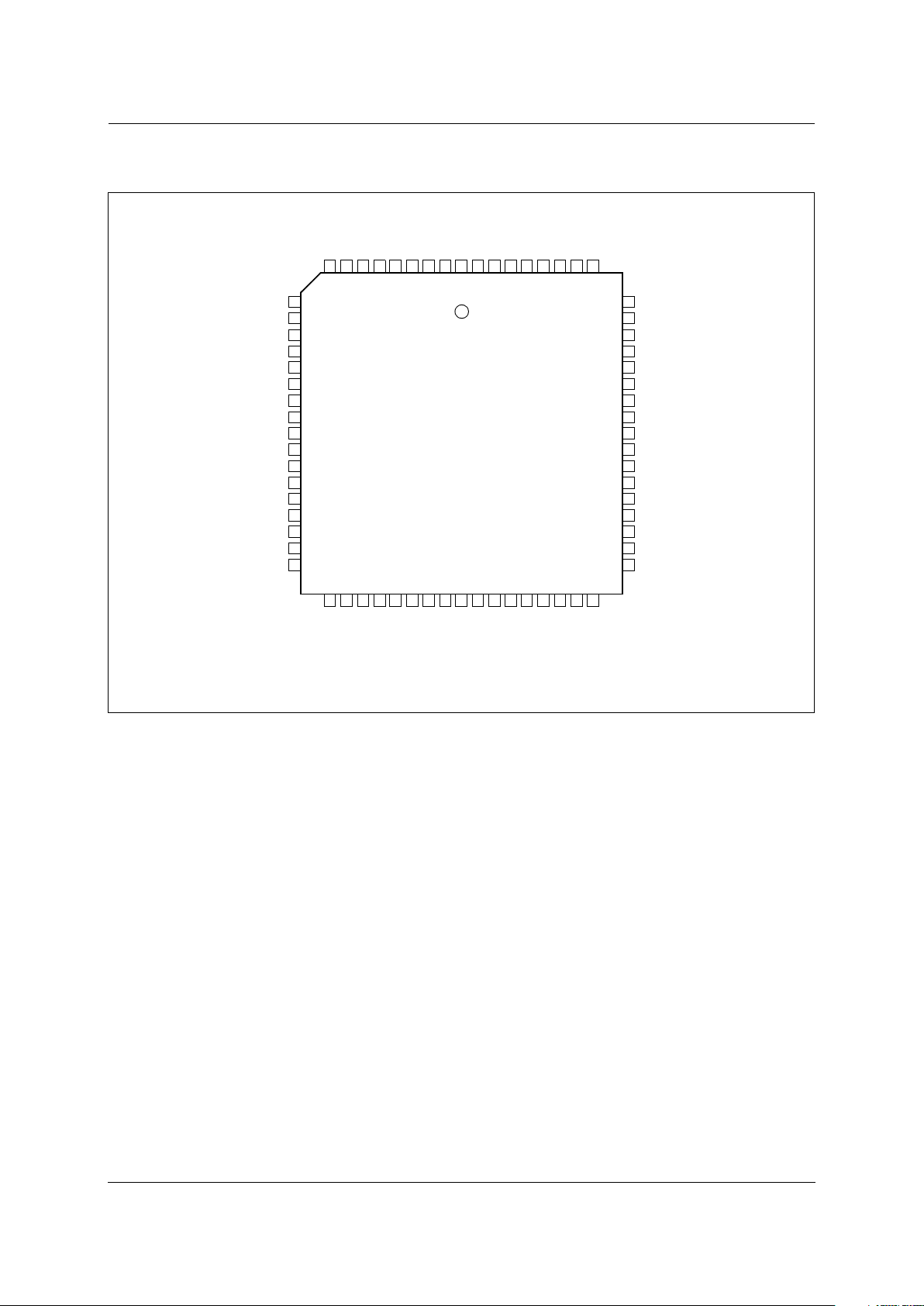

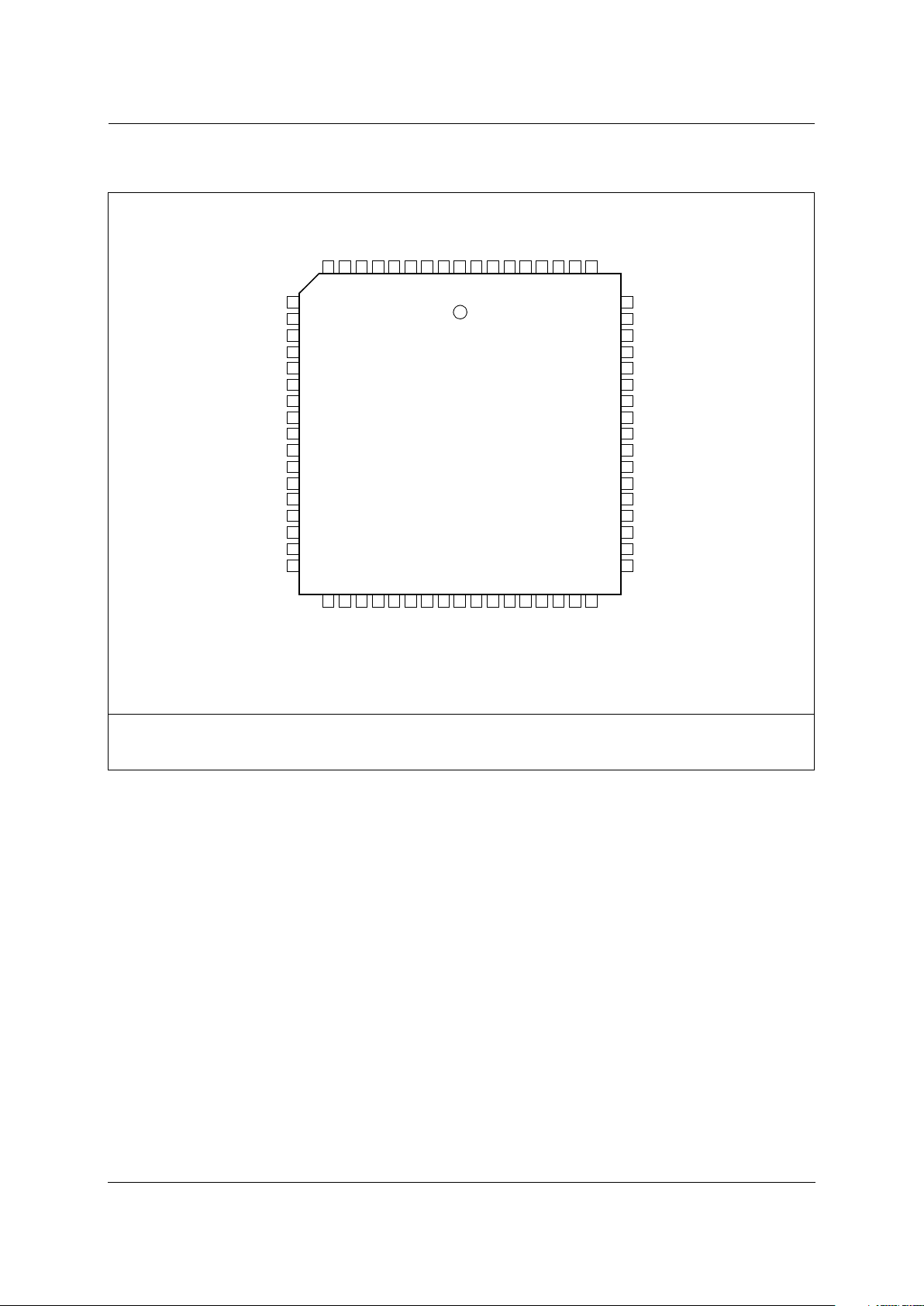

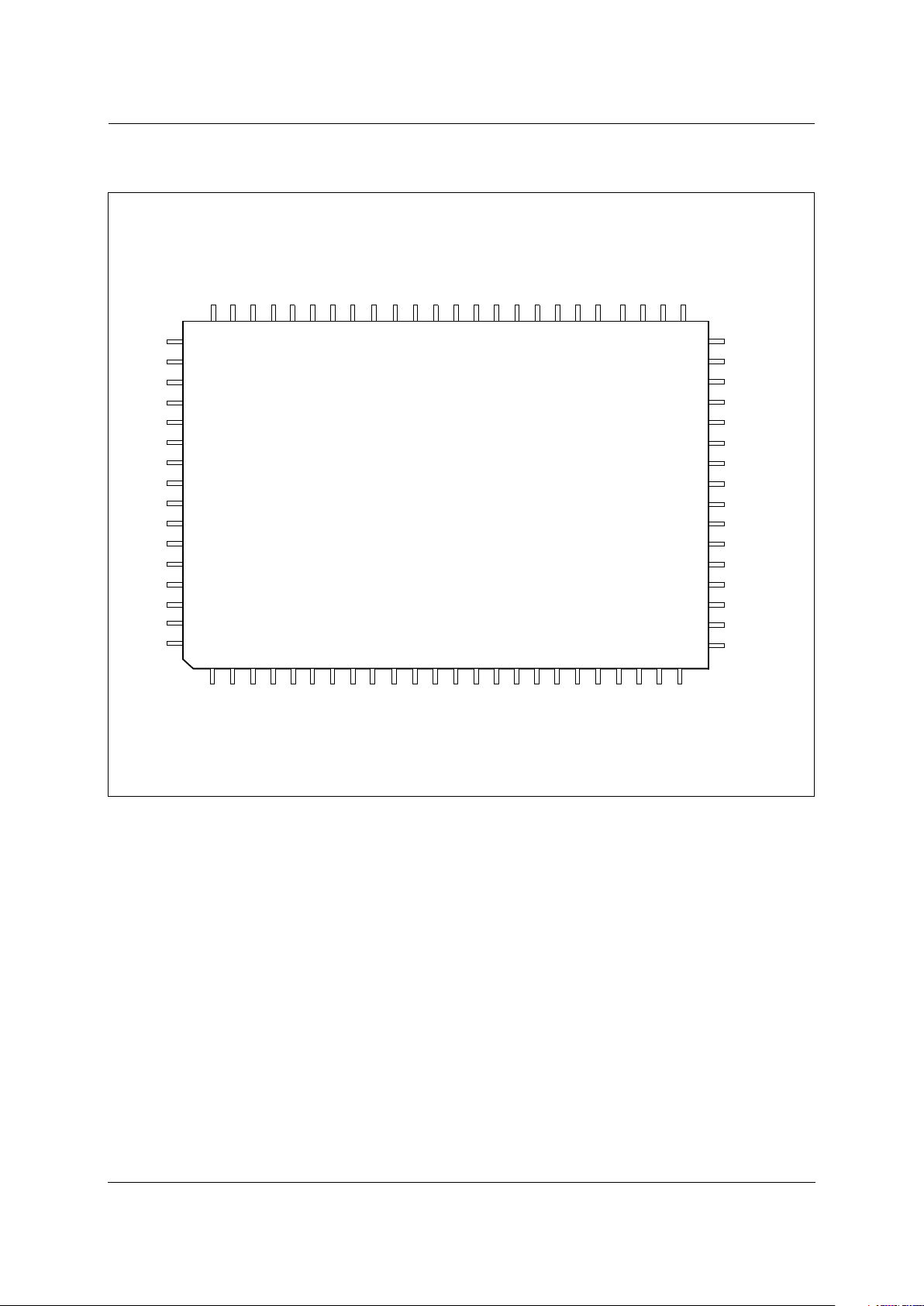

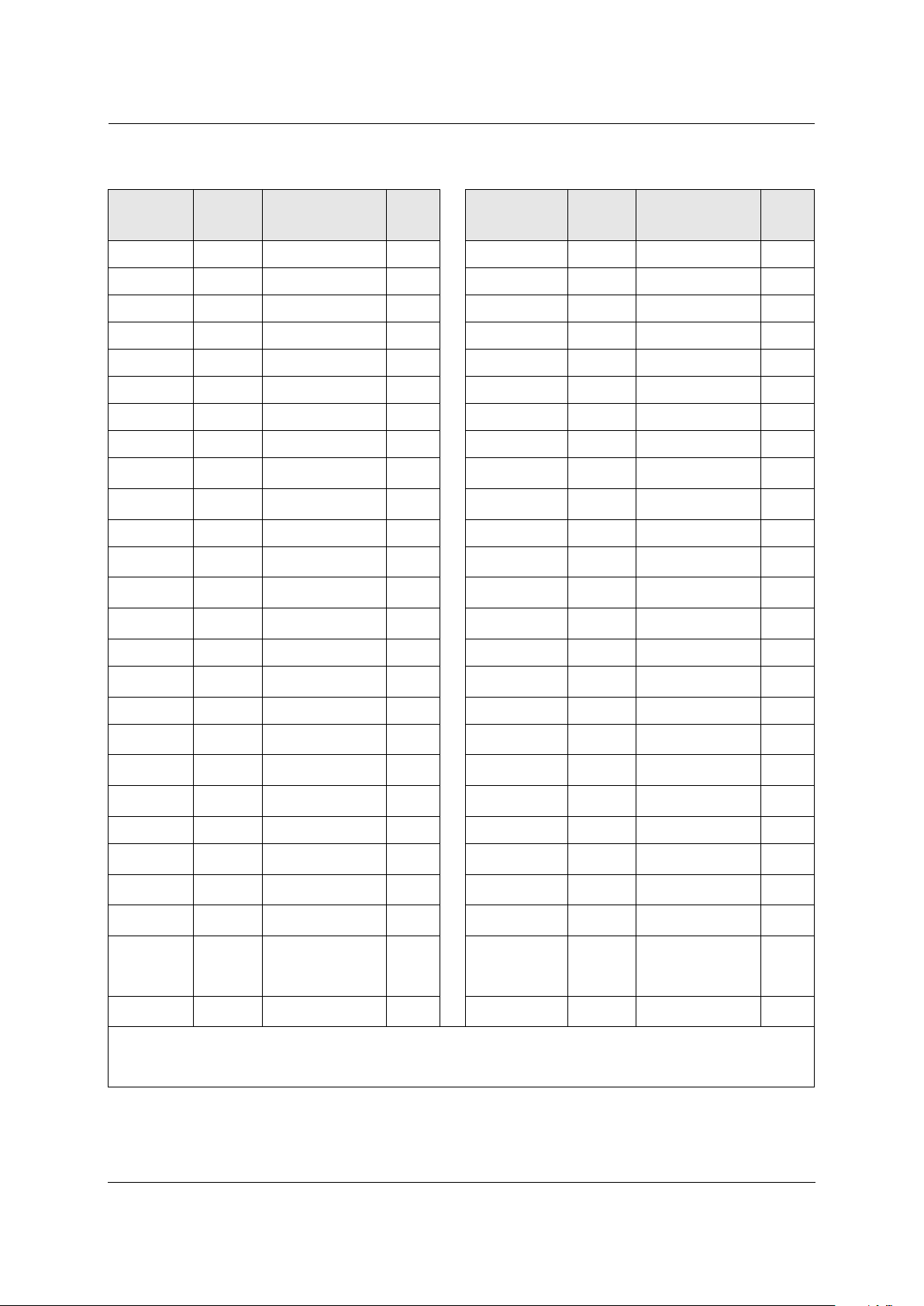

The RS8953B pin assignments for the 68–pin Plastic Leaded Chip Carrier

(PLCC) package are shown in Figure 2-1 and Figure 2-2. The RS8953B pin

assignments for the 80–pin Plastic Quad Flat Pack (PQFP) are shown in

Figure 2-3 and Figure 2-4. The pinouts for RS8953B packages are listed in

Table 2- 1 and defined in Ta bl e 2- 2. The input/output (I/O) column in Tab le 2 -1 is

coded as follows:

I = Input, O = Output, I/O = Bidirectional, VCC = Power, GND = Ground, and

NC = No Connection.

2.0 Pin Descriptions

RS8953B/8953SPB

2.1 Pin Assignments

HDSL Channel Unit

2-2 Conexant N8953BDSB

Figure 2-1. Three-Pair PLCC Pin Assignments

TDAT3

SCLK

MSYNC/RAUX3

TAUX3

TAUX2

TAUX1

TLOAD3

TLOAD2

TLOAD1

WR*

ALE

VCC

PLLVCC

PLLDGND

PLLAGND

VEXT

VCC

RDAT1

AD[0]

AD[1]

AD[2]

AD[3]

AD[4]

AD[5]

AD[6]

AD[7]

VCC

EXCLK

INSDAT

INSERT/RAUX2

INTR*

TMSYNC

RMSYNC

GND

VCC

ROH3

RDAT3

BCLK3

GND

QCLK3

ROH2

QCLK2

GND

BCLK2

TDAT2

RDAT2

GND

BCLK1

ROH1

TDAT1

QCLK1

VCC

MCLK

CS*

DROP/RAUX1

GND

TMS

TDO

TDI

TCK

RST*

RD*

RSER

TSER

RCLK

TCLK

MPUSEL

VCC

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

61

62

63

64

65

66

67

68

1

2

3

4

5

6

7

8

9

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

RS8953BEPJ

RS8953B/8953SPB

2.0 Pin Descriptions

HDSL Channel Unit

2.1 Pin Assignments

N8953BDSB Conexant 2-3

Figure 2-2. Single-Pair PLCC Pin Assignments

NOTE(S):

(1)

These pins are only functional when RAUX_EN is not active (RAUX_EN = 0).

NC

SCLK

MSYNC

(1)

NC

NC

TAUX1

NC

NC

TLOAD1

WR*

ALE

VCC

PLLVCC

PLLDGND

PLLAGND

VEXT

VCC

RDAT1

AD[0]

AD[1]

AD[2]

AD[3]

AD[4]

AD[5]

AD[6]

AD[7]

VCC

EXCLK

INSDAT

INSERT

(1)

INTR*

TMSYNC

RMSYNC

GND

VCC

NC

NC

NC

GND

NC

NC

NC

GND

NC

NC

NC

GND

BCLK1

ROH1

TDAT1

QCLK1

VCC

MCLK

CS*

DROP/RAUX1

GND

TMS

TDO

TDI

TCK

RST*

RD*

RSER

TSER

RCLK

TCLK

MPUSEL

VCC

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

61

62

63

64

65

66

67

68

1

2

3

4

5

6

7

8

9

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

RS8953SPBEPJ

2.0 Pin Descriptions

RS8953B/8953SPB

2.1 Pin Assignments

HDSL Channel Unit

2-4 Conexant N8953BDSB

Figure 2-3. Three-Pair PQFP Pin Assignments

59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 4161626364

65

66

67

68

69

70

71

72

73

74

75

76

77

78

21 3 4 5 6 7 8 9 1011121314151617181920

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24232221

MCLK

CS*

NC

MPUSEL

BCLK2

NC

TDAT2

RDAT2

GND

BCLK1

QCLK1

NC

AD[0]

AD[1]

AD[2]

AD[3]

AD[4]

AD[5]

AD[6]

AD[7]

VCC

NC

EXCLK

INSDAT

INSERT/RAUX2

INTR*

TMSYNC

RMSYNC

RS8953BEPF

60

79

80

ROH1

TDAT1

NC

RDAT1

GND

GND

VCC

NCNCVCC

VCC

SCLK

ROH3

VCC

NC

TDAT3

NC

VEXT

PLLAGND

PLLDGND

PLLVCC

VCC

ALE

WR*

TLOAD1

TLOAD2

TLOAD3

TAUX1

TAUX2

TAUX3

MSYNC/RAUX3

DROP/RAUX1

GND

TMS

NC

TD0

TDI

TCK

RST*

RD*

RSER

TSER

RCLK

TCLK

RDAT3

BCLK3

GND

QCLK3

ROH2

QCLK2

GND

GND

RS8953B/8953SPB

2.0 Pin Descriptions

HDSL Channel Unit

2.1 Pin Assignments

N8953BDSB Conexant 2-5

Figure 2-4. Single-Pair PQFP Pin Assignments

NOTE(S):

(1)

These pins are only functional when RAUX_EN is not active (RAUX_EN = 0).

59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41

NC

NC

NC

VCC

61626364

65

66

67

68

69

70

71

72

73

74

75

76

77

78

21 3 4 5 6 7 8 9 1011121314151617181920

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24232221

VCC

TAUX1

NC

NC

MSYNC

(1)

SCLK

MCLK

CS*

NC

DROP/RAUX1

GND

TMS

NC

TDO

TDI

TCK

RST*

RD*

RSER

TSER

RCLK

TCLK

MPUSEL

NC

NC

GND

NC

NC

NC

GND

GND

NC

NC

NC

NC

GND

BCLK1

QCLK1

NC

AD[0]

AD[1]

AD[2]

AD[3]

AD[4]

AD[5]

AD[6]

AD[7]

VCC

NC

EXCLK

INSDAT

INSERT

(1)

INTR*

TMSYNC

RMSYNC

RS8953SPBEPF

60

79

80

ROH1

TDAT1

NC

RDAT1

GND

GND

VCC

NC

VCC

NC

NC

NC

VEXT

PLLAGND

PLLDGND

PLLVCC

VCC

ALE

WR*

TLOAD1

NC

Table 2-1. Pin Assignments (1 of 2)

80-Pin

PQFP

68-Pin

PLCC

Signal I/O 80-Pin PQFP

68-Pin

PLCC

Signal I/O

71, 72 1 GND GND 33 37 TDO O

73 2

BCLK2

(1)

I3538TMSI

75 3

TDAT2

(1)

O3639GNDGND

76 4

RDAT2

(1)

I 37 40 DROP/RAUX1 O

77 5 GND GND 39 41 CS* I

78 6 BCLK1 I 40 42 MCLK I

79 7 ROH1 O 41 43 VCC VCC

80 8 TDAT1 O 43 44 VCC VCC

1 9 QCLK1 I 45 45 VEXT I

2.0 Pin Descriptions

RS8953B/8953SPB

2.1 Pin Assignments

HDSL Channel Unit

2-6 Conexant N8953BDSB

3 10 RDAT1 I 32 36 TDI I

5 11 AD[0] I/O 46 46 PLLAGND GND

6 12 AD[1] I/O 47 47 PLLDGND GND

7 13 AD[2] I/O 48 48 PLLVCC VCC

8 14 AD[3] I/O 49 49 VCC(SCAN_MD) VCC

9 15 AD[4] I/O 50 50 ALE I

10 16 AD[5] I/O 51 51 WR* I

11 17 AD[6] I/O 52 52 TLOAD1 O

12 18 AD[7] I/O 53 53

TLOAD2

(1)

O

13 19 VCC VCC 54 54

TLOAD3

(1)

O

15 20 EXCLK I 55 55 TAUX1 I

16 21 INSDAT I 56 56

TAUX2

(1)

I

17 22

INSERT/RAUX2

(2)

O5757

TAUX3

(1)

I

18 23 INTR* O 58 58

MSYNC/RAUX3

(2)

O

19 24 TMSYNC I 59 59 SCLK O

20 25 RMSYNC O 60 60

TDAT3

(1)

O

21, 22 26 GND GND 63 61 VCC VCC

23 27 VCC VCC 64 62

ROH3

(1)

O

24 28 MPUSEL I 65 63

RDAT3

(1)

I

25 29 TCLK I 66 64

BCLK3

(1)

I

26 30 RCLK O 67 65 GND(SCAN_EN) GND

27 31 TSER I 68 66

QCLK3

(1)

I

28 32 RSER O 69 67

ROH2

(1)

O

29 33 RD* I 70 68

QCLK2

(1)

I

30 34 RST* I 2, 4, 14, 34,

38, 42, 44, 61,

62, 74

—NC—

31 35 TCK I — —

—

—

NOTE(S):

(1)

These pins do not perform the functions in RS8953SPBEPF and RS8953SPBEPJ.

(2)

These pins are only functional in RS8953SPBEPF and RS8953SPBEPJ when RAUX_EN is not active (RAUX_EN = 0).

Table 2-1. Pin Assignments (2 of 2)

80-Pin

PQFP

68-Pin

PLCC

Signal I/O 80-Pin PQFP

68-Pin

PLCC

Signal I/O

RS8953B/8953SPB

2.0 Pin Descriptions

HDSL Channel Unit

2.2 Signal Definitions

N8953BDSB Conexant 2-7

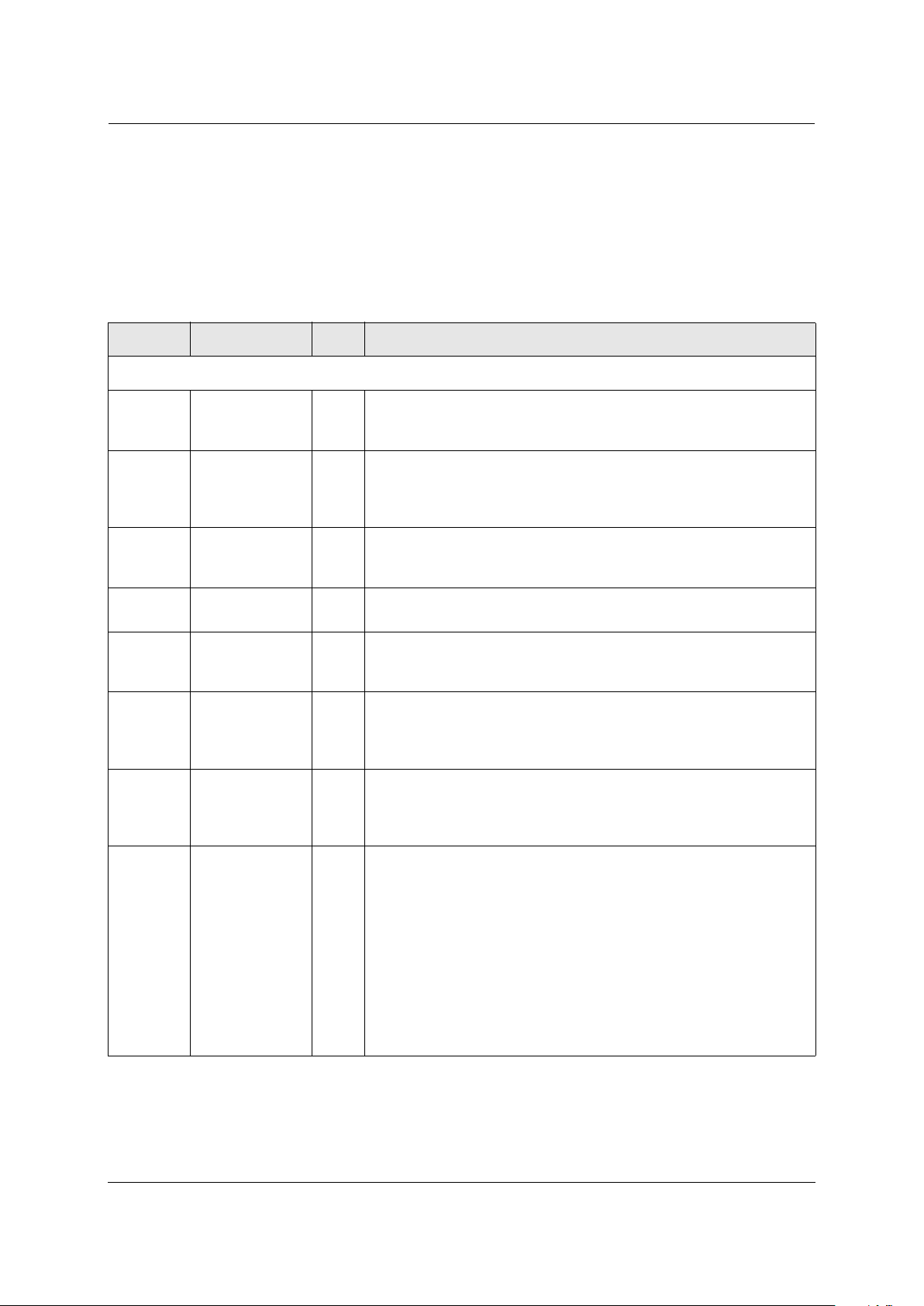

2.2 Signal Definitions

Table 2-2. Signal Definitions (1 of 4)

Signal Name I/O Description

Microprocessor (MPU) Interface

MPUSEL MPU Select

I

(1)

Determines the type of MPU bus control signals expected during data transfers.

Intel (MPUSEL = 0) or Motorola (MPUSEL = 1) bus types are supported. RD*

and WR* signal functions are affected.

AD[0:7] Address/Data Bus

I/O

(1)

Eight multiplexed address and data signals. The address is latched on the falling

edge of ALE and selects one of 256 internal register locations (0x00-0xFF). The

data bus transfers the contents of the latched address location during the read

or write cycle.

CS* Chip Select

I

(1)

Active-low input enables MPU read and write cycles. The rising edge of CS*

completes the read or write data transfer cycle and places the address/data bus

(AD[0]–AD[7]) in a high impedance state.

ALE Address Latch

Enable

I

(1)

Active-high input enables the address bus. The falling edge of ALE latches the

address internally.

RD* Read Strobe

I

(1)

Signal function determined by MPUSEL:

MPUSEL = 0; RD* is an active low data strobe for read cycles.

MPUSEL = 1; RD* is an active low data strobe for read/write cycles.

WR* Write Strobe

I

(1)

Signal function determined by MPUSEL:

MPUSEL = 0; WR* is an active low data strobe for write cycles.

MPUSEL = 1; WR* controls the data bus transfer direction: high during read

cycles and low during write cycles.

INTR* Interrupt Request O Active low, open-drain output indicates when any one or more Interrupt Request

Register (IRR) bit is high and its respective Interrupt Mask Register (IMR) bit is

low. INTR* remains active until all pending interrupts are cleared by writing 0s

to their corresponding Interrupt Clear Register (ICR) bits.

RST* Reset

I

(1)

Active low input required to initialize internal circuits after power and master

clock have been applied. All MPU registers remain accessible while reset is

active. Unless stated otherwise, reset activation does not affect the MPU register

contents.

RS8953B reset activation disables interrupts on the INTR* output by forcing

all 1s in the Interrupt Mask Register (IMR), and zeros in the TX_ERR_EN,

DPLL_ERR_EN, and RX_ERR_EN bits.

RS8953B reset activation disables auxiliary channels by forcing zeros in all

TAUX_EN and RAUX_EN bits.

To facilitate system upgrades from prototype Bt8953EPF, RS8953B reset

activation also forces zeros in those command register bits which do not exist

on Bt8953EPF, but were added on RS8953B.

2.0 Pin Descriptions

RS8953B/8953SPB

2.2 Signal Definitions

HDSL Channel Unit

2-8 Conexant N8953BDSB

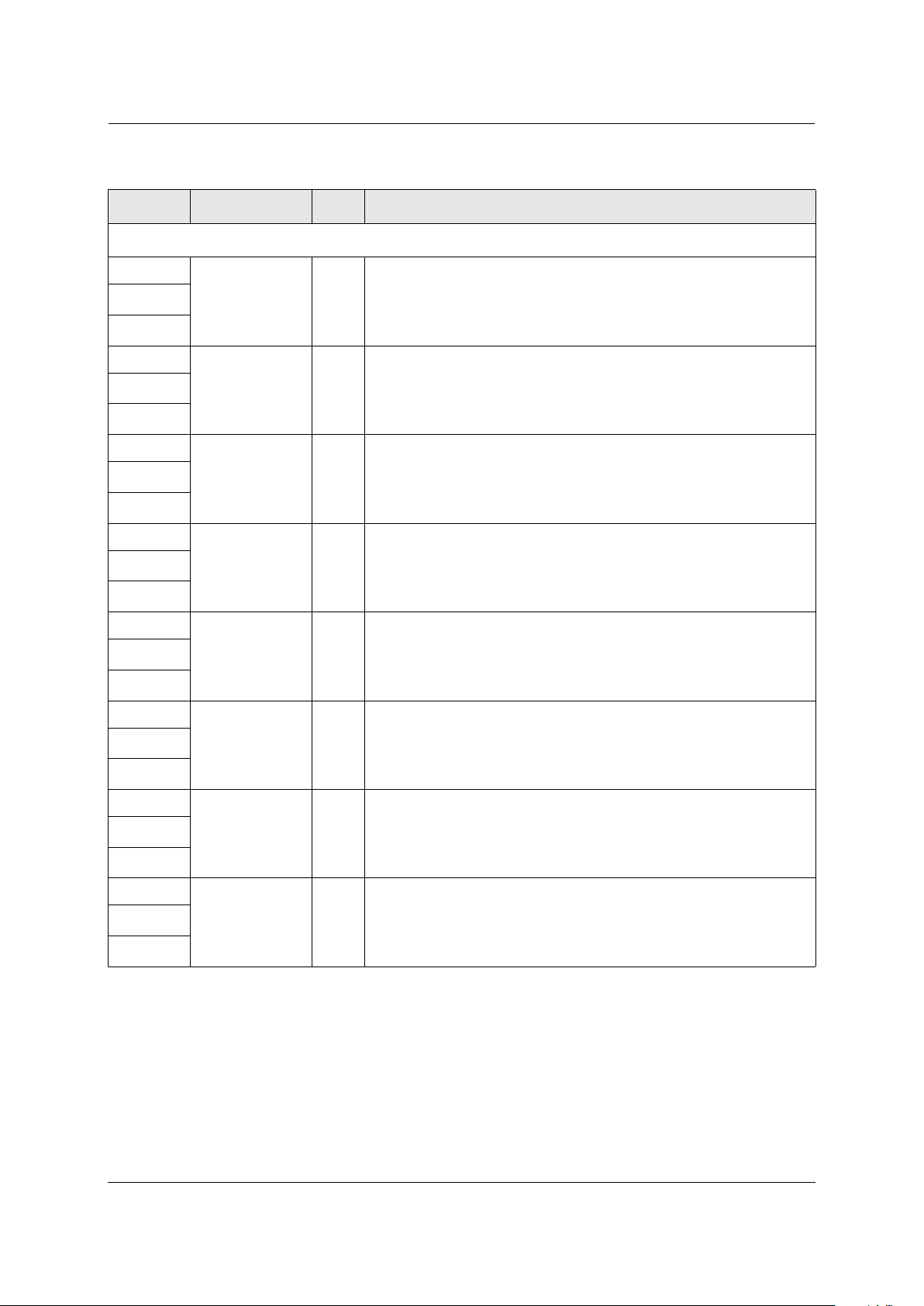

HDSL Channels

BCLK1 Bit Clock

I

(1)

Corresponds to three HDSL and three Auxiliary channels. BCLKn operates at

twice the 2B1Q symbol rate. The rising edge of BCLKn outputs TDATn, TLOADn,

RAUXn and ROHn; the falling edge samples QCLKn, RDATn, and TAUXn inputs.

BCLK2

(3)

BCLK3

(3)

QCLK1 Quaternary Clock

I

(1)

Operates at the 2B1Q symbol rate (half-bit rate) and identifies sign and

magnitude alignment of both RDATn and TDATn serially encoded bit streams.

The falling edge of BCLKn samples QCLKn: 0 = sign bit; 1 = magnitude bit.

QCLK2

(3)

QCLK3

(3)

TDAT1 Transmit Data O HDSL transmit data output at the bit rate on the rising edge of BCLKn. Serially

encoded with the 2B1Q sign bit aligned to the QCLKn low level and the 2B1Q

magnitude bit aligned to the QCLKn high level.

TDAT2

(3)

TDAT3

(3)

TAUX1 Transmit

Auxiliary Data

I

(1)

HDSL transmit auxiliary data input sampled on the falling edge of BCLKn when

TLOADn is active. TAUXn replaces data normally supplied by PCM or HDSL

transmitters to the HDSL scrambler input. Payload bytes or Z-bits can be

mapped from TAUXn.

TAU X2

(3)

TAU X3

(3)

RDAT1 Receive Data

I

(1)

HDSL receive data input sampled on the falling edge of BCLKn. The serially

encoded 2B1Q sign bit is sampled when QCLKn is low, and the 2B1Q magnitude

bit is sampled when QCLKn is high.

RDAT2

(3)

RDAT3

(3)

RAUX1 Receive Auxiliary

Data

O Receives data from the HDSL descrambler output on the rising edge of BCLKn.

Includes all SYNC, STUFF, HOH, payload, and Z-bits. RAUXn shares pin locations

with DROP, INSERT, and MSYNC, as controlled by RAUX_EN (CMD_6; addr

0xF3).

RAUX2

(3)

RAUX3

(3)

TLOAD1 Transmit Load

Indicator

O Active-high output that indicates when specific payload or Z-bits are sampled at

TAUXn. TLOADn is active for 8 bits coincident with each marked payload byte or

1 bit for Z-bits. The last 40 Z-bits or any combination of payload bytes may be

marked.

TLOAD2

(3)

TLOAD3

(3)

ROH1 Receive Overhead

Indicator

O Indicate when overhead is received. Has two modes of operation:

• RAS = 0. ROHn is high to mark only data passed into the RFIFO.

• RAS=1. ROHn is high to mark only the last 40 Z-bits.

ROH2

(3)

ROH3

(3)

Table 2-2. Signal Definitions (2 of 4)

Signal Name I/O Description

Loading...

Loading...