Conexant RF25A Datasheet

Data Sheet Conexant – Preliminary Doc. No. 101110A

Proprietary Information August 4, 2000

RF25A

RF25A for CDMA, and AMPS Applications

The RF25A device includes the following functional blocks:

• Low Noise Amplifier (LNA)

• RF Downconverted Mixer

• Intermediate Frequency (IF) Variable Gain Amplifier (VGA)

• In-Phaseand Quadrature (I/Q) Demodulator

• Voltage Controlled Oscillator (VCO)

The RF25A Application-Specific Integrated Circuit (ASIC) is a dual-mode,singleband receiver (Rx) intended for use in Code Division Multiple Access(CDMA)

portable phones in thecellular band. It can be used in CDMA mode or Advanced

Mobile Phone System (AMPS) mode.The ASIC provides excellent RF

performance with low DC power dissipation and isassembled in a lowcost, high

performance, 40-pin Land GridArray (LGA) 6 x 6 mm package.

The device incorporates all the components required toimplement the complete

dual-mode receiver front end;from the Low Noise Amplifier (LNA) to the In-Phase

and Quadrature (I/Q) demodulator stages, except for external SAW filters. The LNA

amplifies the incoming signaland outputs to anexternal SAW filter. After filtering,

the signal goes to the mixer for downconversion. The mixer output for the AMPS

mode is single-ended, followedby the external AMPSIntermediate Frequency (IF)

Surface Acoustic Wave (SAW) filter.The mixer output for the CDMA mode mixer

has balanced outputs forexternal IF SAW filtering. The IF SAW filters are followed

by a Variable Gain Amplifier (VGA) and and I/Q demodulator. The mode selection

is controlled by amode control pin.

The IF filter outputs are buffered at the input of the VGA,which has a dynamic

range greater than 90dB.

The on-chip Very High Frequency (VHF) Voltage Controlled Oscillators (VCO)

operates with an externaltank circuit to providethe Local Oscillator (LO) signal for

the I/Q demodulator.

The Gain, Noise Figure(NF), and third order Input Intercept (IIP3) of each stage in

the receiver chip are optimized to meet the system requirements for AMPSand

CDMA modes according to the TIA/EIA 98-B standard. Employingsilicon bipolar

technology, the ASIC is designed for high performance with a high level of

integration and provides acost-effective RF solution for dual-mode phone

applications

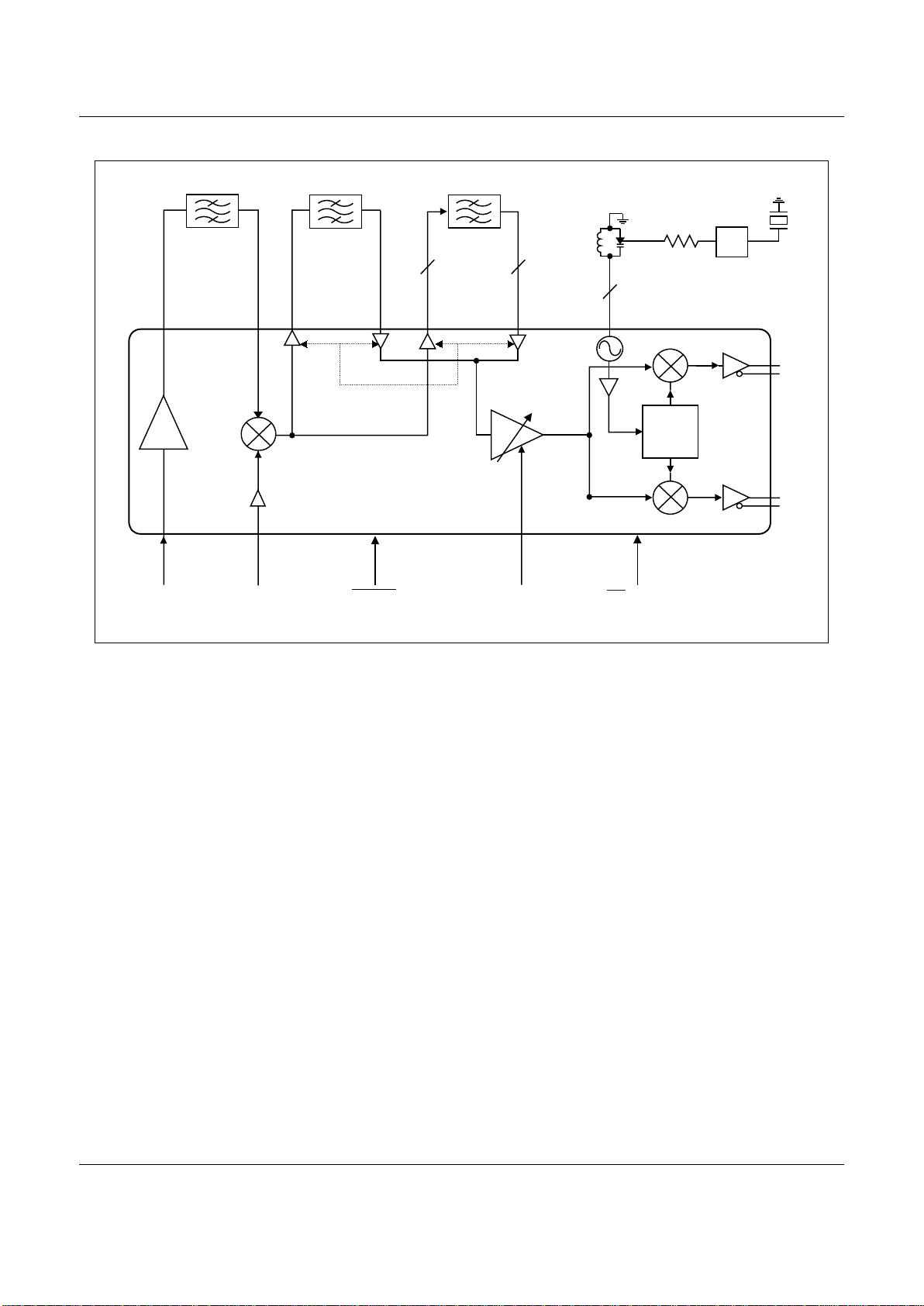

The RF25A pin-out is shown in Figure 1,a functional block diagramis illustrated in

Figure 2, and aschematic diagram in Figure 3.

Features

• Dual-Mode Operation

• Battery operation 2.7 to 3.6 V

• High level of integration

• Differential I/Qoutputs for baseband interfaces

• On-chip 100 to 600MHzVCO

• Low DC consumption: < 60 mA

• 40-pin Land Grid Array (LGA)6x6mmpackage

Applications

• CDMA and AMPS handset in the cellular band:

− AMPS

− CDMA (US)

− CDMA (Japan)

Figure 1.RF25ARx ASICPin-out

40-Pin LGA Package

C506

NC

LNA_DECOUPLE

NC

LNA_IN

VCC_RFBIAS

BIAS_SET

FM/CDMA

VCC_VCO

GND

TANK-

TANK+

31

30

29

28

27

26

25

24

23

22

21

NC

DIV2/DIV4

PLL+

Q+

Q-

SLEEP

PLL-

I+

I-

403938

343332

373635

NC

LNA_OUT

NC

VCC_MIXNCLO_IN

MIXEMIT

IF_TRAP

MIX_IN

121314

181920

151617

NC

NC

AMPS_MIXEROUT

CDMA_MIXEROUT-

CDMA_MIXEROUT+

MIX_BYPASS

VGA_AMPS_IN

VGA_CDMA_IN-

VGA_CDMA_IN+

VCC_IF

VGA_CONTROL

1

2

3

4

5

6

7

8

9

10

11

RF25A Rx ASIC

2 Conexant – Preliminary. 1011110A

Proprietary Information August 4, 2000

÷ 2,4

AMPS IF SAW

CDMA IF SAW

I

Q

RF25A

Rx ASIC

RF SAW(CELL)

PLL

LNA_IN

4

39

35

29

25

27,28

23,24

14,15

16

17

18

19

C507

LO_IN VGA_CONTROL

22

2

721

7

20

FM/CDMA

SLEEP

32

Figure 2. RF25ARxASIC Block Diagram

Rx ASIC RF25A

101110A Conexant – Preliminary 3

August 4, 2000 Proprietary Information

Technical Description

Low Noise Amplifier (LNA). The LNA is designed with a high

gain, low noise figure,and high 3

rd

order input intercept (IIP3)

performance. These parameters canbe optimized with the

mixer gain, noise figure, and IIP3 to achieve the cascade NF

and IIP3 system requirements.RF25A pin 2 isLNA decoupled,

requiring a RF bypasscapacitor to ground with minimal trace

length. Input and outputmatching networks are externalto the

Rx ASIC.

Mixers. The active doublebalanced mixer is designed for high

gain, a low noise figure, and high IIP3performance. The mixer

can also be optimizedfor RF performance to complement the

LNA RF performance, andsatisfy overall Rx NFand IIP3 system

requirements. The LO portoperates with a typicalLO drive level

of -10 dBm. Themixer has a balanced output to drive the IF

SAW filter in CDMA mode, and single-ended output to drive the

IF SAW filter in the AMPS mode.

Variable Gain Amplifier (VGA). Thehigh dynamic range

required by a CDMAhandset is achieved bythe VGA, which has

a minimum dynamic rangeof 90 dB anda control voltage range

from 0.5 to 2.5V. The VGA is common in both modes (CDMA

and AMPS) by switching its internal input buffers.

I/Q Demodulator. The I/Q Demodulator is designed for mobile

handset application. It hasan on-chip generated VHFLO with a

typical operating range of100 to 600 MHz and a typical I/Q

output operating range of 0 to 5 MHz. The I/Q Demodulator is

internally connected to theVGA output, and is fully differential to

reduce common mode noise.DC offsets between differentialI/Q

outputs, and between Iand Q channels, are extremely low to

facilitate compatibility with basebandinterfaces. The

I/Q Demodulator is alsodesigned to have very low amplitude

and phase imbalance.

VHF Oscillator. With external tankcircuits, the VCO p rovides

the LO signal to drive the demodulator, andthe prescaler of an

external Phase Locked Loop (PLL). The oscillator can operate

at two or four times at twice the IF frequency. Usinga selectable

divide ratio, the LOfor the I/Q demodulator is derived. The logic

signal to select thedivider ratio (2 or 4) is available on Pin 13

(DIV2/DIV4).

Mode Control. The operation of the chip is controlled by signals

at Pin 7 (FM/CDMA), Pin 20 (SLEEP), and Pin 13 (DIV2/DIV4).

All the switching is done internally. The supplyvoltage should be

present at all the VCC pins for normal operation. The modes

selected are shown inTable 4.

Electrical and Mechanical Specifications

Included in this documentare Tables 1 through 5 and Figures 1

through 4, which defineand illustrate the electrical and

mechanical specifications of the RF25A.

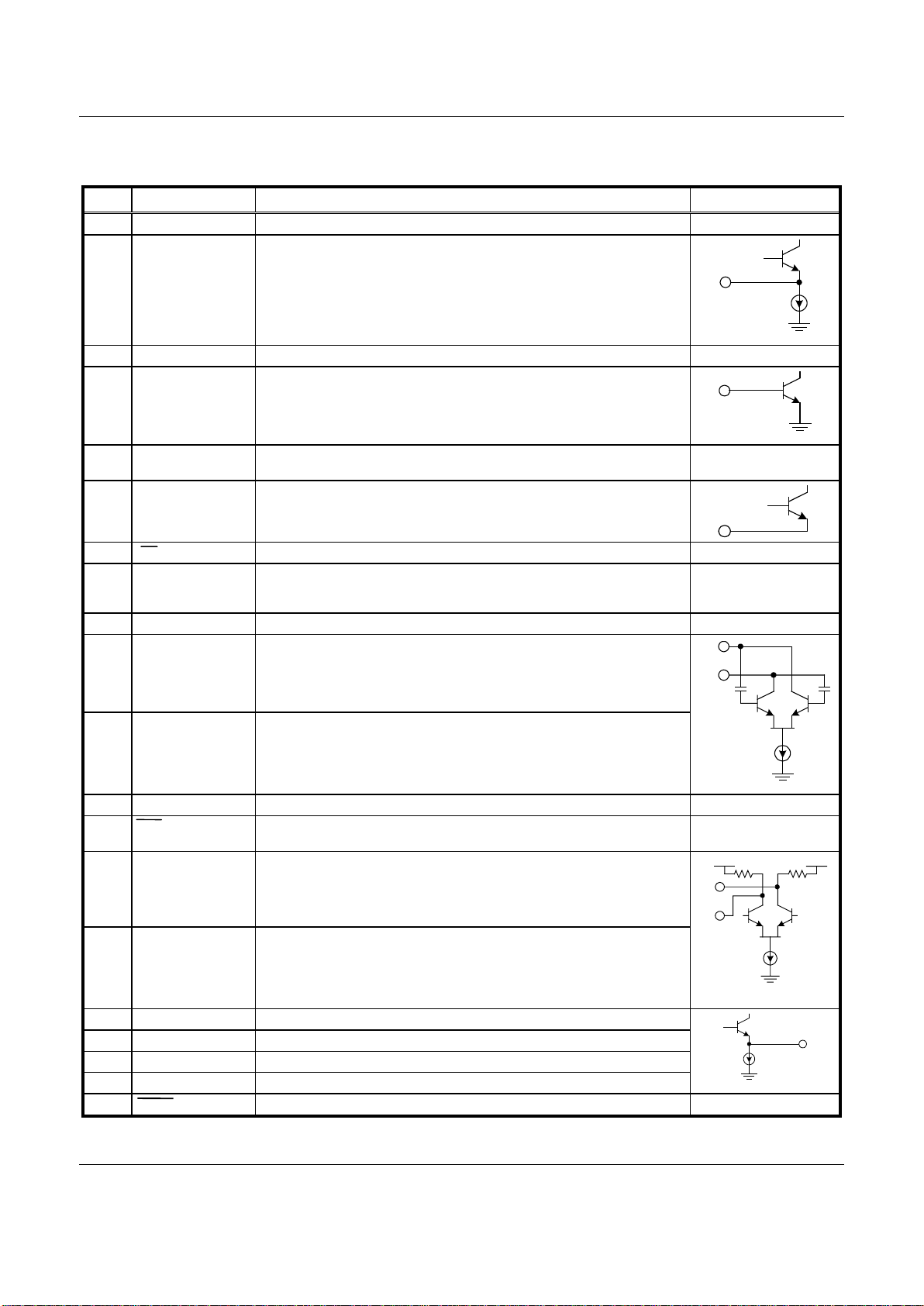

Table 1: RF25A Pin Assignments and Signal

Descriptions

Table 2: Absolute Maximum Ratings

Table 3: Recommended Operating Conditions

Table 4: Mode Control Select SignalSwitching

Table 5: RF25A RX ASIC Electrical Specifications

Figure 1: RF25A Rx ASIC Pin-out - 40-Pin LGA

6x6mmPackage

Figure 2: RF25A Rx ASIC Block Diagram

Figure 3 – 19: Typical Functional Block Performance

Figure 20: RF25A Schematic Diagram

Figure 21: RF25A Package Dimensions – 40-PinLGA

6x6mmPackage

Figure 22: 40-Pin LGA Tape and Reel Dimensions

ESD Sensitivity

The RF25A is a Class 1 device. The following extreme

Electrostatic Discharge (ESD) precautions arerequired

according to the HumanBody Model (HBM):

• Protective outer garments.

• Handle device in ESD safeguarded work area.

• Transport device in ESD shielded containers.

• Monitor and test all ESDprotection equipment.

The HBM ESD withstand threshold value, with respect to

ground, is ±1.5 kV.The HBM ESD withstand threshold value,

with respect to VDD(the positive power supplyterminal) is also

±1.5 kV.

RF25A Rx ASIC

4 Conexant – Preliminary. 1011110A

Proprietary Information August 4, 2000

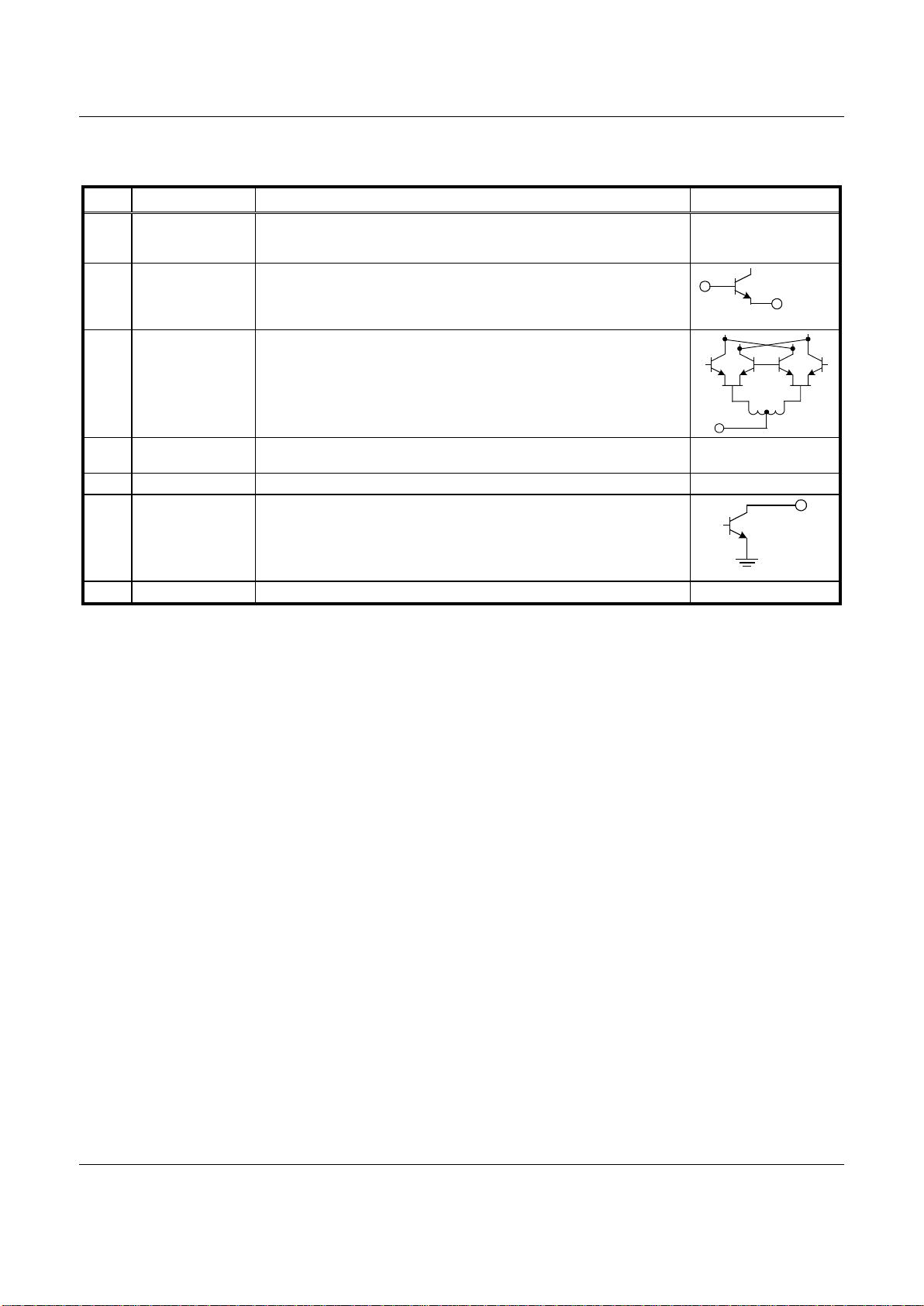

Table 1. RF25A Pin Assignments and Signal Descriptions (1 of 3)

Pin # Name Description Equivalent Circuit

1 NC No connection.

2 LNA_DECOUPLE An RFbypasscapacitor(1000pF) with veryshorttrace shouldbeconnected tothispin.

3 NC No connection

4 LNA_IN The inputto LNAneedsexternal matching.The matching networkshouldbeplaced asclose

to thispin as possible.High Q componentsarerecommended to minimizethe effect onthe

noisefigure.A DC blockingcapacitor isnecessaryatthe input.

5 VCC_RFBIAS Supplyvoltageto the RFbias.An RF bypasscapacitorshouldbeconnectedfromthe pin to

ground withshort traces.

6 BIAS_SET

This pin sets thecellularRFbiascurrent.Typically,a180Ω resistoris connectedfromthe pin

to ground.

7 FM/CDMA Cellularbandmode select: 0=AMPS; 1 = CDMA.

8 VCC_VCO Voltagesupplypin to theVCObuffer. A bypasscapacitor shouldbeplaced closetothe device

frompin8 to pin 9.Thetrace shouldbeshortandconnected immediatelytothe ground plane

forbestperformance.

9 GND Ground returnfrom the VCObuffer.

10 TANK- Differentialtank connectionforthe cellularbandVCO. Care shouldbetaken during thelayout

of the external tank circuit toprevent parasitic oscillations.

11 TANK+ Differentialtank connectionforthe cellularbandVCO. Care shouldbetaken during thelayout

of the external tank circuit toprevent parasitic oscillations.

–

+

12 NC No connection.

13 DIV2/DIV4 Selectsthedivide ratio ofthe VCOtothe LO portofthe I/Q demodulator:0 = divideby2,

1 =divideby40.

14 PLL+ Differentialbuffered VCO output

15 PLL- Differentialbuffered VCOoutput

–

+

VccVcc

16 I+ I channeldifferential output.

17 I- I channeldifferential output.

18 Q+ Q channeldifferentialoutput.

19 Q- Q channeldifferential output.

20 SLEEP Activatessleepmode:0= sleep;1=enable

Rx ASIC RF25A

101110A Conexant – Preliminary 5

August 4, 2000 Proprietary Information

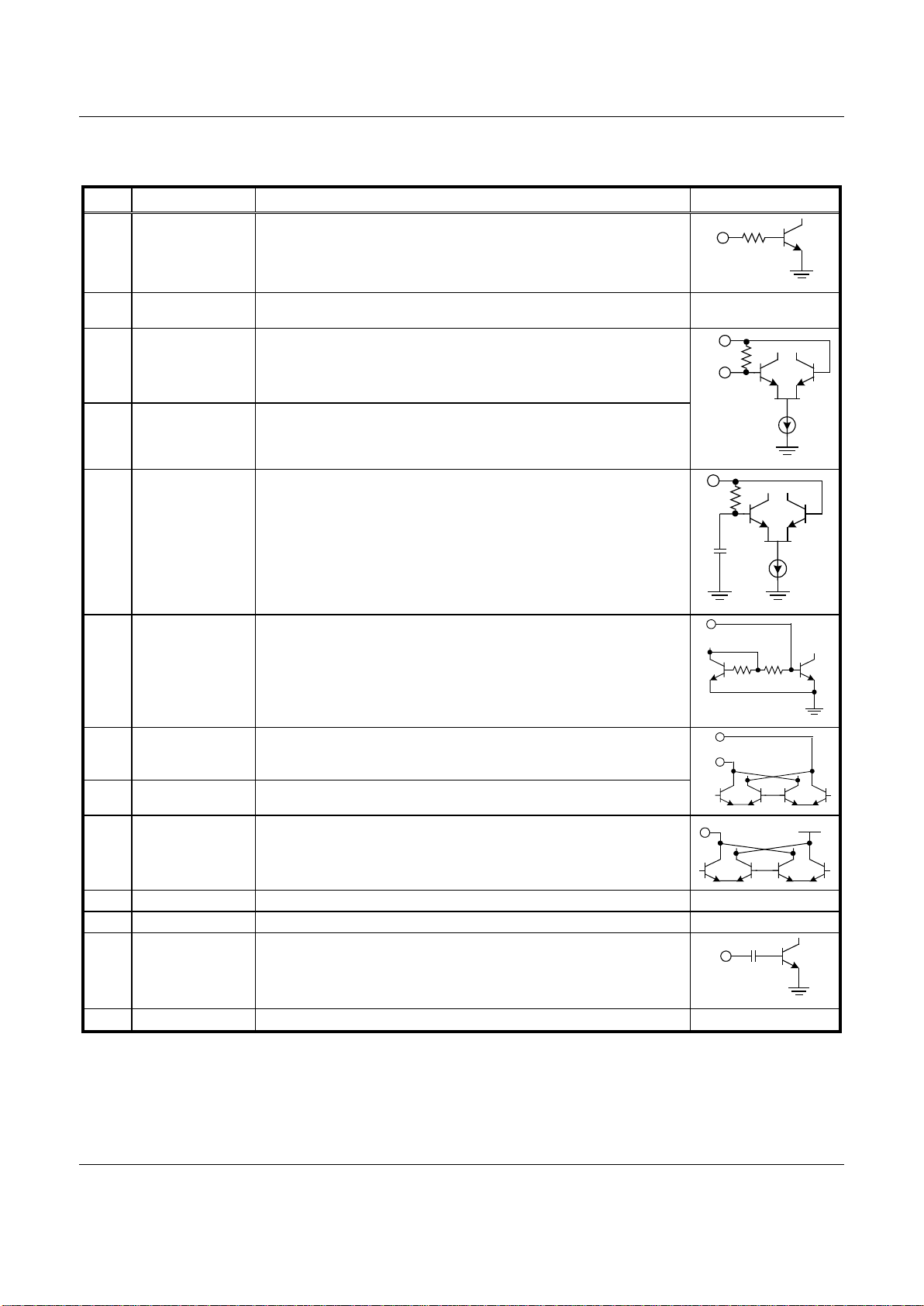

Table 1. RF25A Pin Assignments and Signal Descriptions (2 of 3)

Pin # Name Description Equivalent Circuit

21 VGA_CONTROL

VGA voltageinput. Input impedanceis greater than50KΩ.

22 VCC_IF Voltagesupplyto VGA andI/Qdemodulator stages.Supplyshould be wellregulated and

bypassedtoprevent modulationofthe signal bythe supply ripple.

23 VGA_CDMA_IN+ CDMA differentialVGA input

24 VGA_CDMA_IN- CDMA differentialVGA input

–

+

25 VGA_AMPS_IN AMPS VGAinput.

26 MIX_BYPASS Low frequencybypass fortheamps mixer.

27 CDMA_MIXEROUT+ CDMA differential mixeroutput. Requiresanexternal inductortoVCC. An externalmatch sets

outputimpedance.

28 CDMA_MIXEROUT- CDMAdifferentialmixer output.Requiresan external inductorto VCC. Anexternalmatch sets

outputimpedance.

–

+

29 AMPS_MIXEROUT AMPSmixer output.Requiresan externalinductorto VCC. Anexternalmatchsets output

impedance.

Vcc

30 NC No connection.

31 NC No connection.

32 LO_IN The mixerlocal oscillatorinput drive istypically–10dBm.

33 NC No connection.

RF25A Rx ASIC

6 Conexant – Preliminary. 1011110A

Proprietary Information August 4, 2000

Table 1. RF25A Pin Assignments and Signal Descriptions (3 of 3)

Pin # Name Description Equivalent Circuit

34 VCC_MIX Voltagesupplypin for themixers.AnRF bypass capacitorshould be connectedfrom thispin

to ground.It should beconnected asclose to thedeviceaspossible withveryshort trace

lengths.

35 MIX_IN Cellularmixerinput.

Pin 37

36 IF_TRAP The parallelLC circuitistuned to thecellularIFfrequency.

37 MIXEMIT Typicalground connection,buta 1.5 nHemitterdegeneration canbeused toimprovemixer

inputIP3.

See Pin35

38 NC No connection.

39 LNA_OUT Thisisan open collectorLNA output. Aninductormust be connectedto VCC. Thematchingis

done externallyto the chip.

40 NC No connection.

Loading...

Loading...