Conexant RF133 Datasheet

Data Sheet

Conexant

100776A

Proprietary Information and Specifications are Subject to Change October 8, 1999

RF133

RF/IF Transceiver For GSM Applications

The RF133 RF/IF Transceiver is a highly integrated, monolithic device optimized

for use in GSM and other TDMA single-band or multi-band applications.

The receive path of the device consists of three Intermediate Frequency (IF)

amplifiers with selectable gain, an I/Q demodulator, baseband filters, DC offset

compensation circuitry, and selectable gain baseband amplifiers.

The transmit path of the device consists of an I/Q modulator and a frequency

translation loop designed to perform frequency up-conversion with high output

spectral purity. The translation loop consists of a phase/frequency detector, a

charge-pump, a mixer, and buffers for the required isolation between the RF input,

Local Oscillator (LO), and IF inputs.

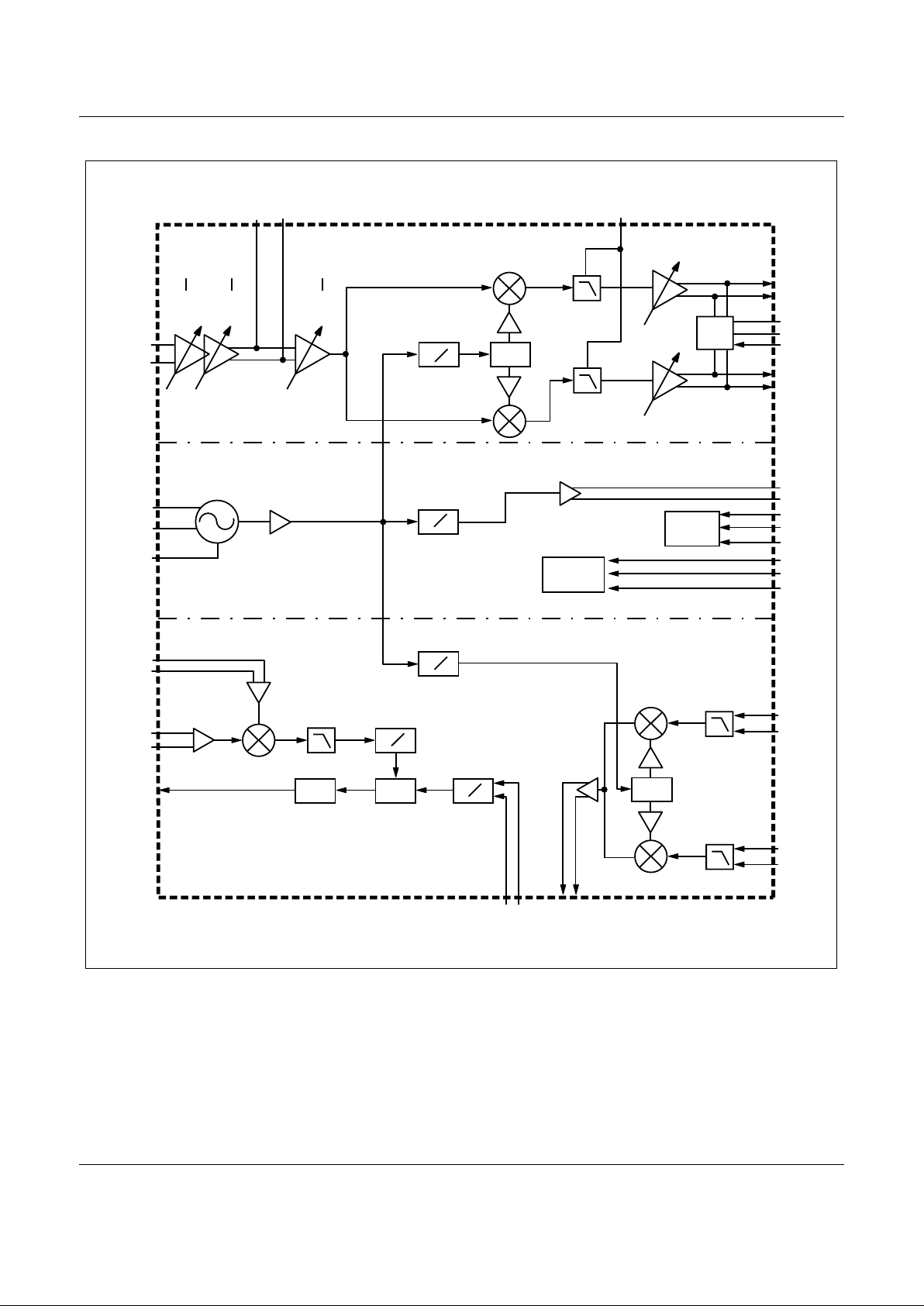

The device package and pin configuration are shown in Figure 1. A block diagram

of the RF133 is shown in Figure 2. The signal pin assignments and functional pin

descriptions are found in Table 1.

1

48 47 46 45 44 43 42 41 40 39 38 37

13 14 15 16 17 18 19 20 21 22 23 24

2

3

4

5

6

7

8

9

10

11

12

36

35

34

33

32

31

30

29

28

27

26

25

C100a

GND

TLCPO

VCC

VCC

GND

TXIFIN+

TXIFIN–

GND

TXI+

TXI–

TXQ+

TXQ–

TXMO+

TXMO–

RXI+

RXI–

RXQ+

RXQ–

T/H

CTH1

CTH2

GND

LO2O+

LO2O–

TXENA

TXRFIN+

TXRFIN–

VCC

LO1IN+

LO1IN–

GND

RFIFN+

RFIFN–

RXENALECLK

DATA

RXIFF+

RXIFF–

SXENA

BPC

GND

VCC

RES2

RES1

VCC

LPFADJ

VCC

Figure 1. RF133 Pin Configuration – 48-pin TQFP

Features

• Quadrature demodulator for downconversion

• 80 dB IF gain range and 30 dB baseband gain

range

• Integrated receive baseband filters with tunable

bandwidth

• Integrated transmit path with high phase accuracy

• Reduced filtering requirements for the transmit path

• Broad RF and IF range for multi-band operation

• Integrated selectable local oscillator dividers/phase

shifters and selectable high/low-side injection for

frequency plan flexibility

• On-chip second local oscillator

• Separate enable lines for transmit, receive, and

synthesizer modes for power management

• 48-pin Thin Quad Flat Pack (TQFP) package (7mm

x 7mm)

Applications

• GSM900/DCS1800/PCS1900 digital cellular

telephony

• Multi-mode, multi-band terminals

RF133 RF/IF Transceiver

2

Conexant

100776A

October 8, 1999 Proprietary Information and Specifications are Subject to Change

C068

Bias

3-Wire

Control

+20 dB

0 dB –10 dB

+20 dB

+18 dB

PGA

Rx

Sx

Rx

Sx

Sx

Tx

Sx

Tx

RES1

RES2

RXIF+

RXIF–

BPC

LO1IN+

LO1IN–

TXRFIN+

TXRFIN–

TLCPO

RXI+

RXI–

RXQ+

RXQ–

CTH1

CTH2

T/H

RXENA

TXENA

SXENA

CLK

DATA

TXMO–

TXMO+

TXIFIN–

TXIFIN+

LE

LO2O+

LO2O–

TXI+

TXI–

TXQ+

TXQ–

PGB

–10 dB

DC

OC

90

˚

+20 dB

+18 dB

PGC

RXIFF+

RXIFF–

LPFADJ

PGD

0/10/20/30 dB

PFD

CHP

90

˚

÷2 ÷4

÷2 ÷4

÷2 ÷4

÷1 ÷2

÷1 ÷2

Figure 2. RF133 Block Diagram

RF/IF Transceiver RF133

100776A

Conexant

3

Proprietary Information and Specifications are Subject to Change October 8, 1999

Table 1. RF133 Signal Descriptions

Pin # Name Description Pin # Name Description

1 GND Ground (Tx phase detector/charge pump) 25 VCC Supply (2nd LO output buffers)

2 TLCPO Translation loop char ge pump output 26 LPFADJ Adjustment pin for bas eband low pass filter corner

frequency

3 VCC Supply (phase detector and charge pump) 27 VCC Supply (2nd LO)

4 VCC Supply (Tx modulator, Rx baseband sections) 28 RES1 Resonator pin

5 GND Ground (Tx modulator, Rx baseband sections) 29 RES2 Resonator pin

6 TXIFIN+ Tx IF input 30 VCC Supply (2nd LO)

7 TXIFIN– Tx IF input 31 GND Ground (2nd LO)

8 GND Ground 32 BPC Bypass capacitor

9 TXI+ Tx modulator input 33 SXENA Synthesizer enable

10 TXI– Tx modulator input 34 RXIFF– Rx IF filter pin

11 TXQ+ Tx modulator input 35 RXIFF+ Rx IF filter pin

12 TXQ– Tx modulator input 36 DATA Data input

13 TXMO+ Tx modulator output 37 CLK Clock input

14 TXMO– Tx modulator output 38 LE Latch enable input

15 RXI+ Rx baseband output 39 RXENA Receiver enable

16 RXI– Rx baseband output 40 RXIFIN– Rx IF input

17 RXQ+ Rx baseband output 41 RXIFIN+ Rx IF input

18 RXQ– Rx baseband output 42 GND Ground (Tx mixer, Rx IF secti ons)

19 T/H Track and hold signal 43 LO1IN– 1st local oscillator input

20 CTH1 Capacitor for track and hold 44 LO1IN+ 1st local oscillator input

21 CTH2 Capacitor for track and hold 45 VCC Supply (Tx mixer, Rx IF sections)

22 GND Ground (2nd LO output buffers) 46 TXRFIN– Transmit RF input

23 LO2O+ 2nd local oscillator output 47 TXRFIN+ Transmit RF input

24 LO2O– 2nd local oscillator output 48 TXENA Transmit enable

Technical Description

The RF 133 RF/IF transceiver unit is comprised of a receive

path, a transmit path, and a synthesizer section as shown in

Figure 2. The receive path consists of a selectable gain IF

chain, a quadrature demodulator, and baseband amplifier

circuitry with I and Q outputs. The transmit path is essentially an

I/Q modulator with a translation loop for frequency upconversion. An on-chip oscillator and frequency dividers make

up the synthesizer section. Each section of the RF 133 is

separately enabled via the enable signals: TXENA, RXENA, and

SXENA.

To control different modes of operation, a serial 21-bit word (bits

S1 to S21) is written to the on-chip registers. This 21-bit word is

programmed using the three-wire input signals, CLK, DATA, and

LE. To ensure that the data remains latched, either one of the

signals TXENA, RXENA, or SXENA must stay enabled. The

operating mode that draws the least current (12 mA) is the

synthesizer mode (i.e., the mode that results when only SXENA

is enabled) (refer to Table 5). In the sleep mode, the device

typically draws less than 1 µA of current.

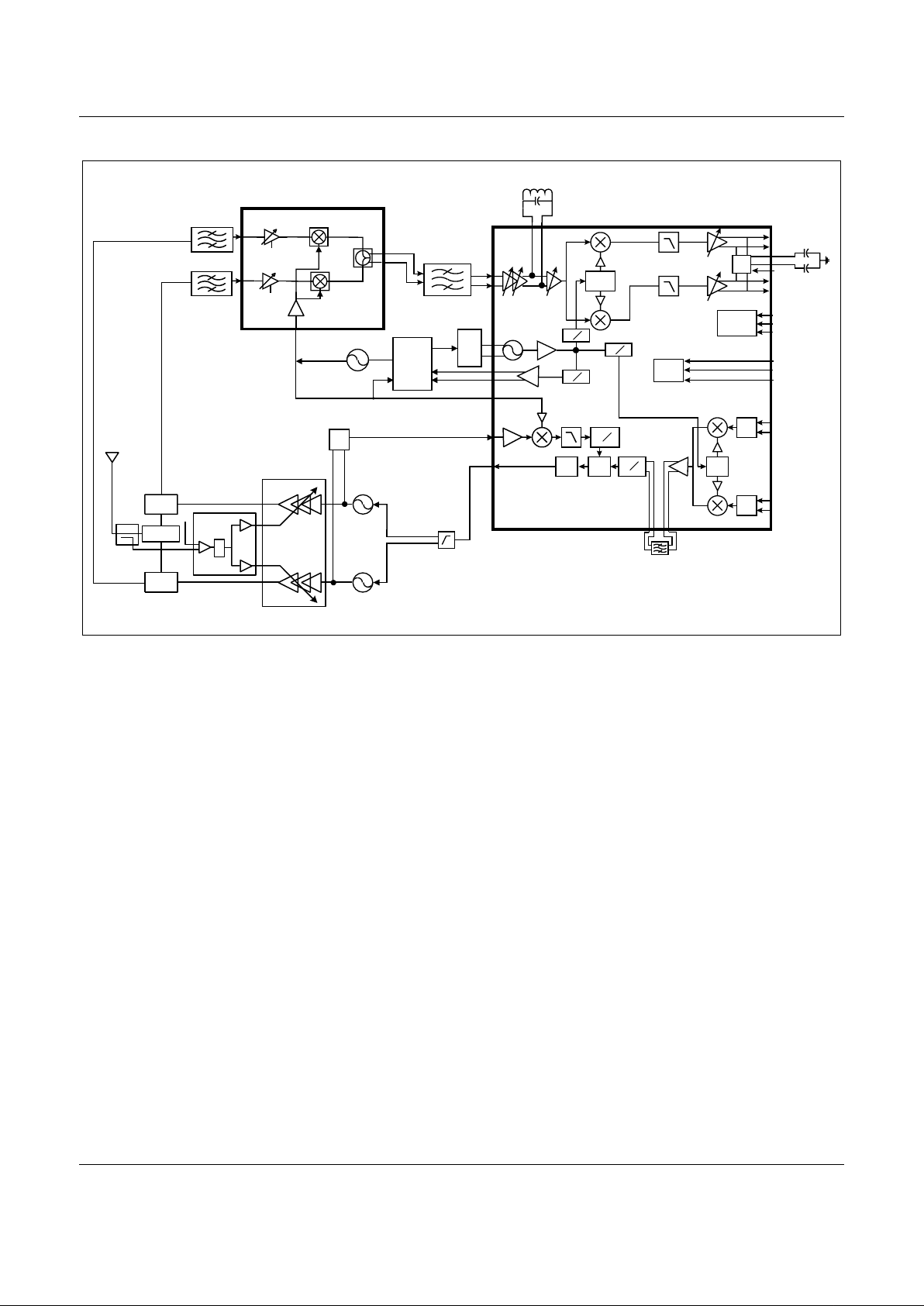

The block diagram in Figure 3 shows a complete RF/IF dualband transceiver chipset using the RF133.

Receive Path _______________________________________

Selectable Gain IF Chain and Quadrature Mixer. The receive

path of the RF133 is composed of an IF section and a baseband

section. The IF section consists of three programmable gain

amplifiers: PGA, PGB, and PGC.

RF133 RF/IF Transceiver

4

Conexant

100776A

October 8, 1999 Proprietary Information and Specifications are Subject to Change

PFD

CHP

3 Wire

Control

Bias

DC

OC

PGBPGA PGC

PGD

PGD

DUAL PLL

Combiner

CTH1

CTH2

LOOP FILTER

TX DCS VCO

TX GSM VCO

TX ENA

T/H

RX ENA

SX ENA

RXI

RXQ

TXI

TXQ

CLK

DATA

LE

C453

LPF

LPF

TX IF FILTER

90

˚

90

˚

÷2 ÷4

÷2 ÷4

÷1 ÷2

÷1 ÷2

÷2 ÷4

RF210

LNA/Image Reject Mixer

IF SAW

Filter

Tx/Rx VCO

UHF VCO

GSM

Rx Filter

DCS

Rx Filter

RF133

Tx/Rx VCO

Tank

LC

Tank

Diplexer

Coupler

T/R

Antenna

RM008

RF142

VAPC

T/R

Figure 3. Dual-Band Transceiver Chipset Using The RF133

PGA has two gain settings, either 0 dB or 20 dB, whereas both

PGB and PGC have a gain range of -10 dB to 20 dB

programmable in 2 dB steps. The output of PGC is fed to a

quadrature mixer. The quadrature mixer has a fixed conversion

gain of 10 dB and its LO inputs are taken from the outputs of a

quadrature divider (divide by 2 or 4).

Baseband Integrated Filters, Baseband Amplifiers, and DC

Offset Compensation. Immediately following the quadrature

mixer (demodulator) is the baseband section (DC offset

compensation circuitry, two integrated baseband filters and two

programmable gain amplifiers). Each programmable gain

amplifier in the baseband section, both labelled PGD, has four

different gain settings: 0 dB, 10 dB, 20 dB, or 30 dB.

The corner frequency of the integrated baseband filters is

adjustable by using an appropriate value resistor at pin 26,

LPFADJ. At the nominal cutoff frequency of 105 kHz, the

resistor value is 75.1 kΩ.

Due to possible high gain of the baseband amplifiers (PGD), any

DC offsets at the outputs of the quadrature mixer are amplified

and, if uncorrected, the I and Q outputs can suffer from

significant unwanted DC offset voltages. To cancel out these

effects, the RF133 must be calibrated.

During compensation, the correction voltages are stored in

external hold capacitors CTH1 and CTH2, then the loop is

opened immediately thereafter. The corrected I and Q outputs

are then fed directly to external circuitry for further baseband

processing.

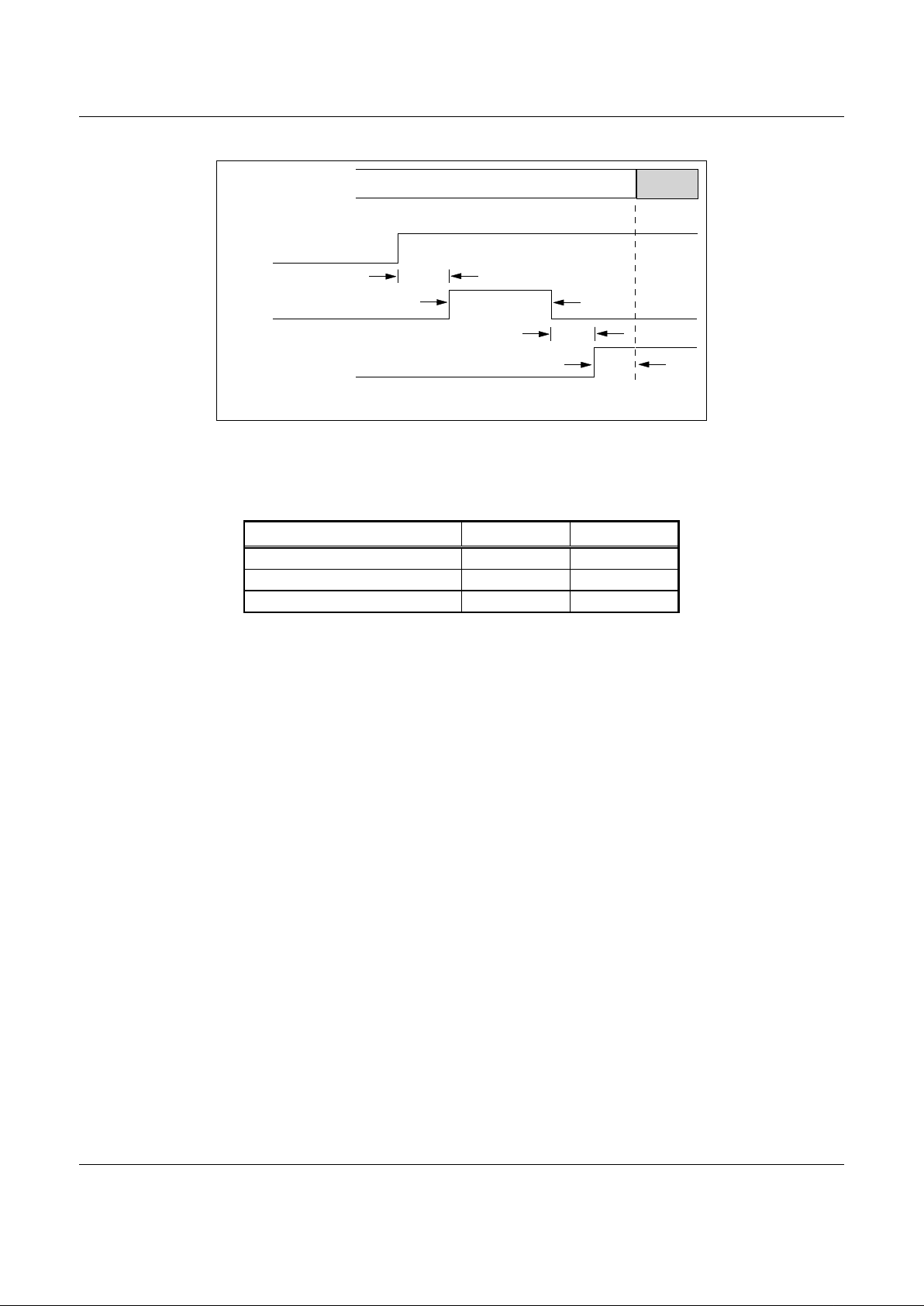

The timing diagram for this calibration sequence in reference to

the receive slot is shown in Figure 4 (the front-end mixer is

assumed to be Rockwell’s RF210 dual-band, image reject

downconverter). At first, the RF133 receiver is turned on

(RXENA is high). After time T1, the track and hold signal, T/H,

places the DC compensation circuitry in the track mode for time

T2. Then, there is a settling time, T3, before the external frontend is turned on. Finally, the front-end must be turned on for

time T4 before the receive slot.

Time T2 can vary from 10 µsec to 350 µsec. This duration is

dependent on 1) the value of the hold capacitors (CTH1 and

CTH2), and 2) whether the calibration is done from frame to

frame or from a cold start. This is tabulated in Table 2.

RF/IF Transceiver RF133

100776A

Conexant

5

Proprietary Information and Specifications are Subject to Change October 8, 1999

T1

Rx slot

RXENA

T/H

Front-end

enable

(external to RF133)

TDMA slots

T2

T3

T4

C064

Figure 4. RF133 Sample and Hold Timing Diagram

Table 2. Minimum Required DC Offset Calibration Time T2 a nd Droop Rate

Hold Capacitor (CTH1, CTH2) 22 nF 120 nF

Cold start 60 µsec 350 µs

Frame-to-frame 10 µsec 60 µs

Typical droop-rat e (@ I/Q outputs) 1 mV/msec 0.17 mV/m s

Because of on-chip loading currents, the hold capacitors (CTH1

and CTH2) slowly discharge causing the I and Q DC offset

voltages to droop if the RF133 remains uncalibrated for an

extended period of time (the droop rate versus the hold

capacitor is also shown in Table 2).

To rectify this voltage droop, it is recommended that

recalibration occur before every receive slot (i.e., every 4.6 ms

for GSM).

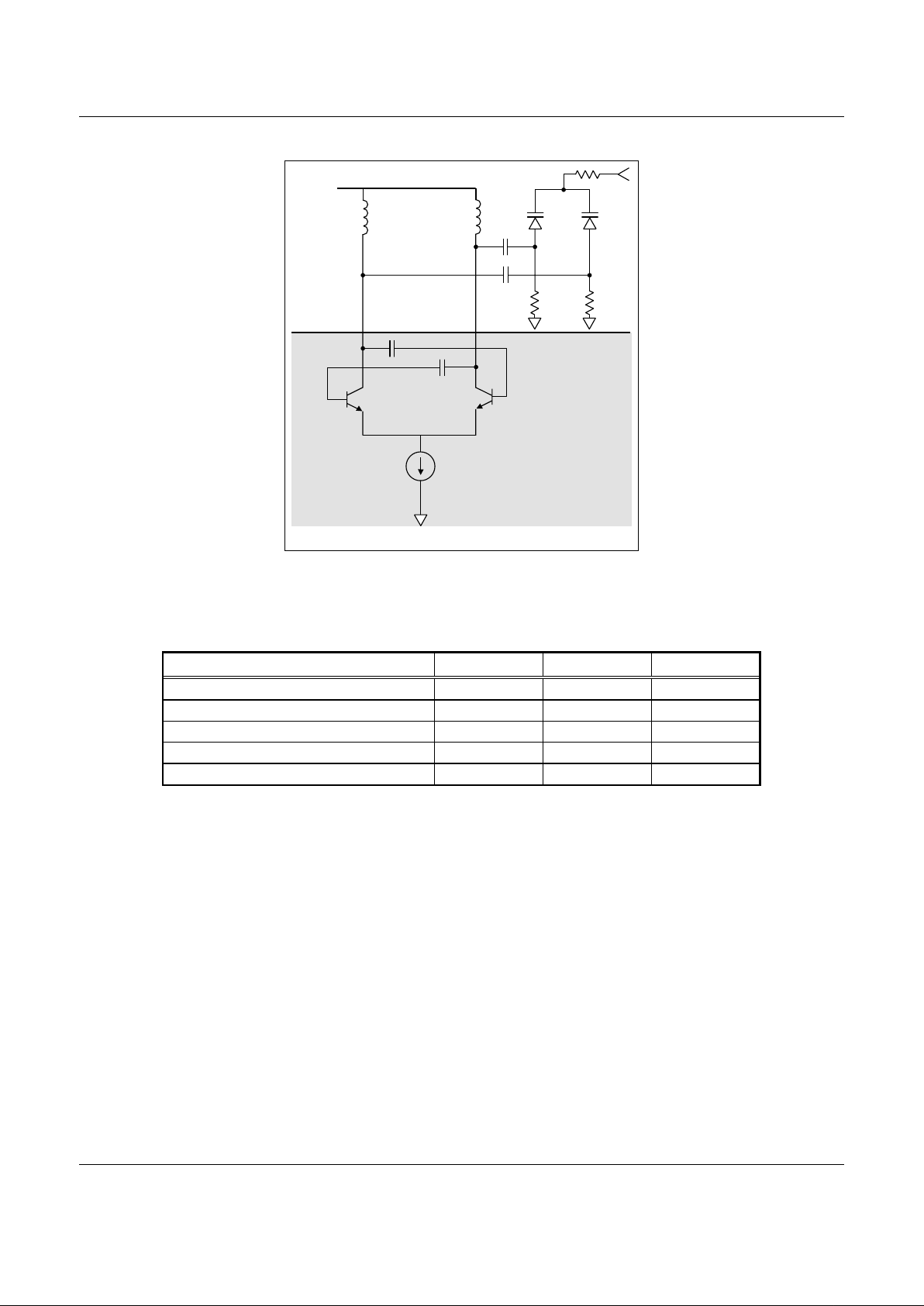

Internal Voltage Controlled Oscillator (VCO) and Frequency

Dividers. The differential VCO output is buffered and then fed to

three frequency dividers (Rx, Tx, PLL) with a selectable divide

ratio of either 2 or 4. The Rx and Tx dividers are both

quadrature dividers, which generate in-phase and quadrature

LOs. The buffered PLL divider output can be used to drive an

external PLL IC. The resonant element of the VCO is connected

to pins 28 (RES1) and 29 (RES2). Figure 5 shows the VCO

configuration.

Transmit Path_______________________________________

The transmit path consists of the following functional blocks:

•

An I/Q modulator with IF output amplifier.

•

A translation loop circuit consisting of a phase/frequency

detector, a charge pump, a Tx RF input buffer, an LO input

buffer, a mixer, two dividers, and a low pass filter.

The inputs to the I/Q modulator are differential I and Q

baseband signals which are low-pass filtered and then applied

to a pair of double balanced mixers (see Figure 2). The outputs

of the mixers are combined to produce a modulated signal

which is then filtered externally and input through pins 6 and 7

(TXIFIN+ and TXIFIN-) to the reference divider in the translation

loop.

The translation loop circuit together with the external transmit

VCO, external LO, and loop filter, form a PLL with a mixer in the

feedback loop. This PLL upconverts the modulated IF signal to

the transmit frequency which then drives the final power

amplifier. Since inherent bandpass filtering occurs in the PLL,

the need for a post PA duplexer is removed. This is the major

advantage a translation loop approach has over the

conventional upconversion scheme. The elimination of this

duplexer reduces the loss in the transmit path which in turn

reduces the output level of the final power amplifier and,

therefore, reduces the current consumption. Immediate benefits

of this approach are increased handset talk time and standby

time, and less component count.

RF133 RF/IF Transceiver

6

Conexant

100776A

October 8, 1999 Proprietary Information and Specifications are Subject to Change

VCC

External

Resonator

RF133

RES1

(pin 28)

RES2

(pin 29)

Vtune

C321

Figure 5. RF133 Internal VCO

Table 3. Absolute Maximum Ratings

Parameter Minimum Maximum Units

Ambient Operating Temperature –40 +85 °C

Storage Temperature –50 +125 °C

Power Dissipation 600 mW

Supply Voltage (VCC) 0 +5 V

Input Voltage Range GND VCC V

The charge pump current can be programmed to be either 1 mA

or 0.5 mA and the translation loop can also be programmed to

allow for high side or low side injection of the first LO input with

respect to the transmit RF.

Even greater flexibility in the transceiver frequency planning is

possible because of the programmable dividers in the feedback

and the reference paths.

The absolute maximum ratings of the RF133 are provided in

Table 3, and the electrical specifications are provided in Table 4.

Tables 5, 6, and 7 detail the setting of the programmable

operation modes. Figure 6 illustrates the timing of the three-wire

bus control signal and Figure 7 provides a graph of the input

compression versus the receiver gain.

Figure 8 shows a typical application circuit diagram. Figure 9

provides the package dimensions for the 48-pin device.

Loading...

Loading...