Conexant RF109 Datasheet

RF109

2400 MHz Digital Spread Spectrum Transceiver

The RF109, a fully integrated transceiver device, provides the transmit, receive, and

frequency synthesis functions for 2400 MHz digital spread spectrum systems operating

in the 2400–2483.5 MHz portion of the ISM (Industrial, Scientific, Medical) band. The

device has a direct conversion architecture that minimizes circuit complexity and cost.

The receive path of the RF109 provides complete RF-to-baseband I/Q demodulation,

including an LNA, double-balanced quadrature mixers, fully integrated baseband filters,

and baseband variable-gain amplifiers. The transmit path is a variable-gain direct

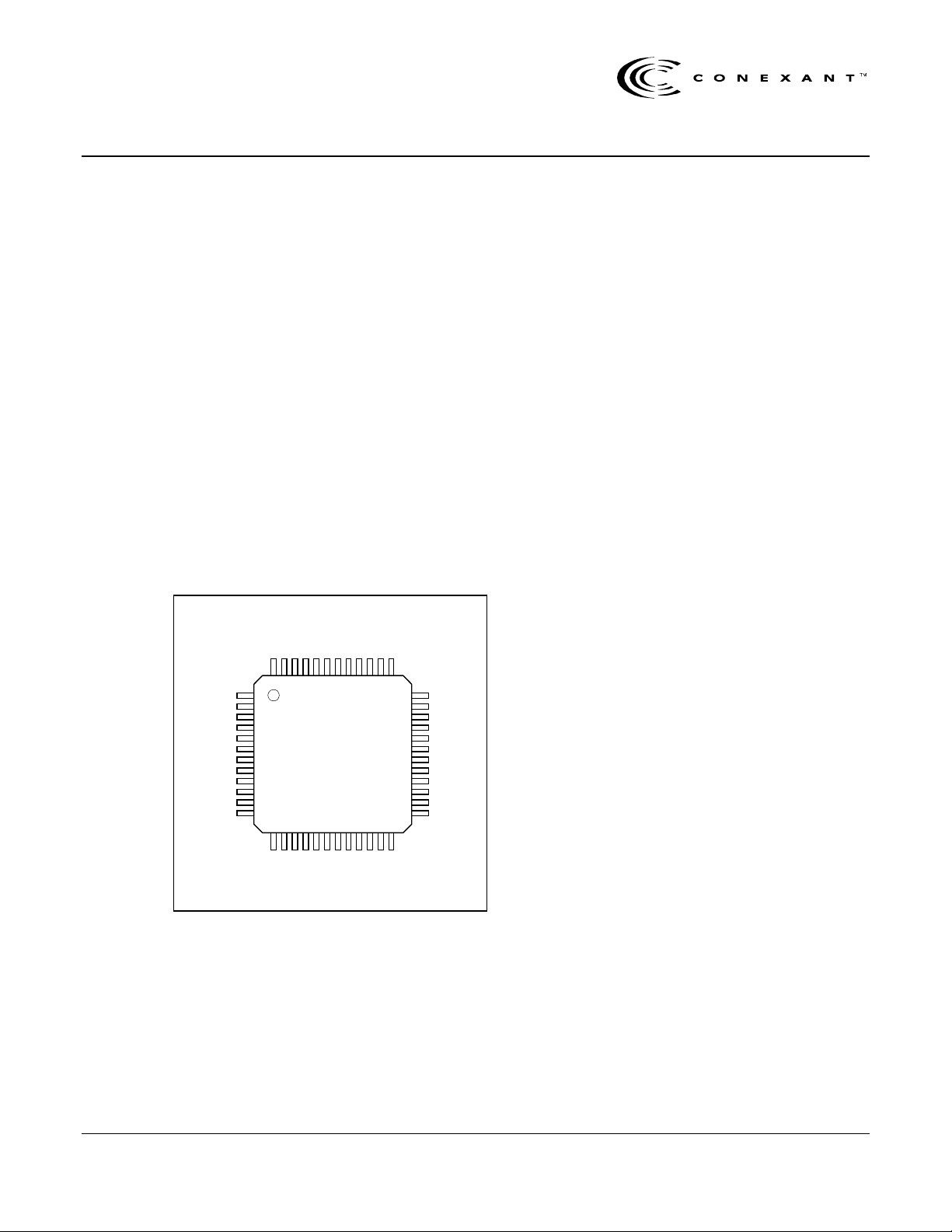

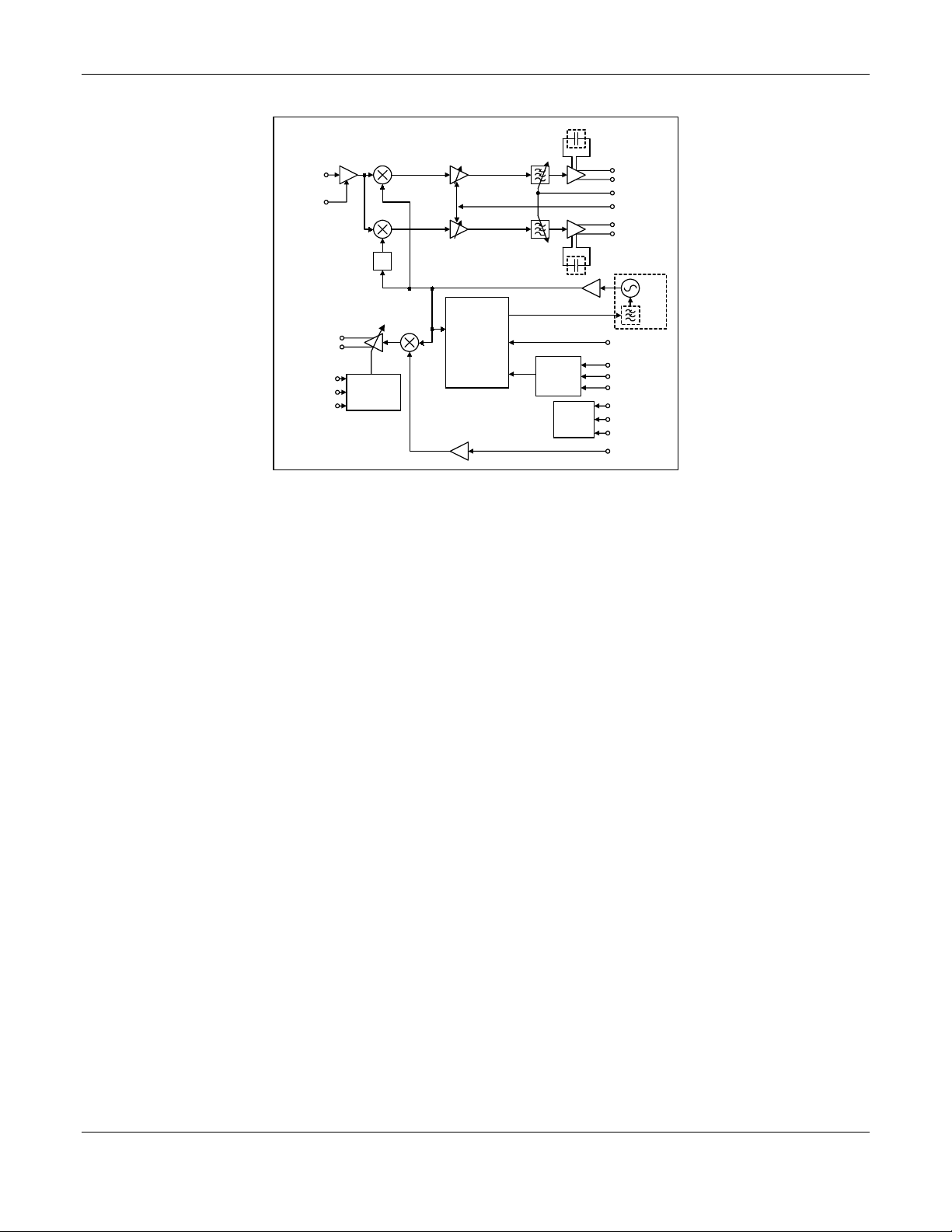

conversion modulator. Figure 1 shows the RF109’s pin signals. Figure 2 shows the

RF109 block diagram.

The RF109 generates the Local Oscillator (LO) frequencies using a Phase Lock Loop

(PLL) frequency synthesizer and an external 2.4 GHz Voltage Controlled Oscillator

(VCO). The PLL provides a full frequency range of 2392.2–2505.6 MHz.

The RF109 features low-voltage operation (3.0–4.5V) for low power consumption. A

complete RF system solution for 2.4 GHz cordless telephone applications can be

constructed with the RF109, a power amplifier, a differential 2.4 GHz frequency source

and a Transmit/Receive (T/R) switch.

VCC6

STROBE

NC8

NC1

CLK

FREF

DATA

TXREF

VCC1

VCC2

TXD

RXEN

LNAATTN

LNAIN

NC2

SYNTHEN

48474645444342

1

2

3

4

5

6

7

8

9

10

11

12

13141516171819

RFO1

GND1

GMCRES

Figure 1. RF109 Pin Signals

VCC5

RF109

RFO2

GND2

NC7

CHPO

TXEN

MIXBPC

NC6

VCO2

NC5

4137403938

2024212223

PS2

PS1

MODSET

VCO1

NC4

36

35

34

33

32

31

30

29

28

27

26

25

AGC

GCREF

NC3

SRI+

SRISRQ+

SRQVCC4

GND3

RXI+

RXIRXQ+

RXQVCC3

Features

• Low power dissipation

• Fast settling from standby mode to active

mode

• Separate enable lines for transmit, receive,

and synthesizer

• 64 programmable channels with 1.8 MHz

channel spacing

• 3-battery-cell operation

• 48-pin TQFP package with exposed paddle

(refer to Figure 6)

Receiver

•

− LNA/Quadrature mixer from RF down to

baseband

− Selectable LNA gain

− Integrated baseband filter with external

bandwidth adjustment

− Receiver baseband amplifier with

automatic gain control

− Direct conversion with differential

baseband outputs

− Low system noise figure (9.0 dB typ ical)

− Large dynamic range (89 dB typical)

Transmitter

•

− Variable gain modulator

− Mixer for baseband-to-RF modulation

− Differential TX inputs and outputs

− Selectable transmitter output levels for

high, medium, and low power modes

Applications

• Digital Spread Spectrum (DSS) cordless

telephone

• Direct sequence spread spectrum systems

• Frequency hopping spread spectrum

systems

• Wireless LANs

• Wireless modems

• Wireless security

• Inventory control systems

Data Sheet Doc. No. 100646A

Conexant Proprietary

January 19, 2000

RF109 2400 MHz Digital Spread Spectrum Transceiver

External

CSERVO

LNAIN

LNAATTN

LNA

RXI

GMCRES

AGC

RXQ

o

90

RFO1

RFO2

MODSET

PS1

PS2

Modulator

Gain

Control

Figure 2. RF109 Block Diagram

Technical Description

Receive Path_______________________________________

The LNA provides two gain levels for coarse Automatic Gain

Control (AGC), which are selected via the LNAATTN control.

The signal is down-converted to In-phase and Quadraturephase (I/Q) baseband signals using a matched pair of mixers

and the LO.

The receive baseband bandwidth has a bandpass characteristic.

The I/Q baseband signals are internally low-pass and high-pass

filtered to attenuate out-of-channel signals and to remove DC

components. The low-pass cutoff is determined by the GmC

filters and is set by the R

high-pass cutoff is set by the value of the C

connected between pins 32–33, and pins 34–35.

The baseband high-pass cutoff frequency should be set much

lower than the low-pass cutoff frequency or else the servo loop

will become unstable.

The optimum receive bandwidth values are:

f

= 820 kHz, R

LPF

= 20 kHz, C

f

HPF

gmc

resistor connected to pin 13. The

servo

capacitors

gmc

servo

Ω

= 825

= 0.082 µF

Synthesizer

External

CSERVO

Interface

Serial

Power

Mgmt.

External

VCO

LPF

FREF

STROBE

CLK

DATA

RXEN

SYNTHEN

TXEN

TXD

Transmit Path_______________________________________

The transmit path consists of an amplifier and a mixer. The

mixer modulates the LO with baseband data supplied to pin 8.

The transmit RF outputs from the RF109 are differential and

matched for a 100Ω differential load. If a single-ended

connection is required, then the unused output must be suitably

terminated by a 50Ω resistor (as shown in Figure 5).

The transmit output power is determined by the output power

control inputs, PS1 (pin 21) and PS2 (pin 22), and by the value

mod

of R

(connected to pin 20). R

mod

sets the bias current into the

modulator which is then multiplied by a factor set by the state of

PS1 and PS2. PS1 and PS2 input programming is given in the

Transmitter Section of Table 3.

LO Generation ______________________________________

The LO is generated by a programmable PLL frequency

synthesizer and a 2.4 GHz external VCO. Synthesizer

performance parameters are determined by the loop filter, the

external reference oscillator, the sensitivity and phase noise of

the VCO, and the frequency synthesizer programming.

A matched pair of VGAs provide fine AGC. The differential I/Q

baseband signals are DC-coupled to the RXI+, RXI-, RXQ+, and

RXQ- outputs, respectively.

2

Conexant Proprietary 1/19/00

Conexant

The RF109 requires differential inputs for VCO1 (pin 38) and

VCO2 (pin 39). The typical differential input level is 200 mVp-p.

A BALUN transformer, shown in Figure 5, is used to generate

differential signals from a single-ended VCO output.

100646A

2400 MHz Digital Spread Spectrum Transceiver RF109

Synthesizer Programming____________________________

The frequency synthesizer block is comprised of a divide-by-3

counter (D), 9.6 MHz reference frequency (FREF) source, a

fixed reference divider of 16 (R), 16/17 prescaler (M), a fixed

counter of 83 (N), a programmable counter of 64 (A),an external

loop filter, and a 2.4 GHz external VCO.

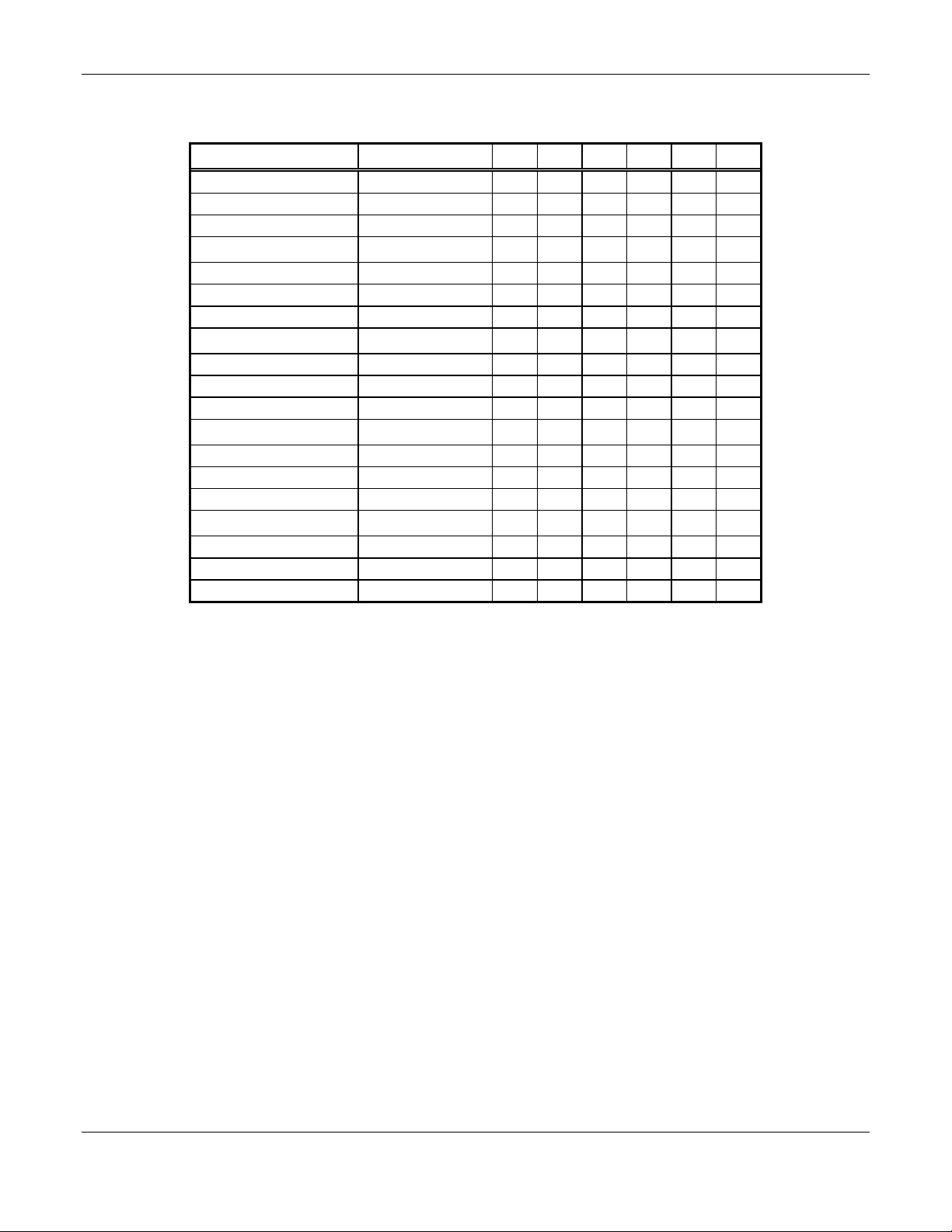

The synthesizer can be programmed to cover 64 channels

(channel spacing = 1.8 MHz) from 2392.2 MHz to 2505.6 MHz

Table 1).

The LO frequency is given by the following equation:

f

= (D) × (FREF/R) × ((M × N) + (A + 1)),

LO

where N > A.

Example:

= 3 × (9.6 MHz / 16) × ((16 × 83) + 7) = 2403.0 MHz

f

LO

= 3 × (9.6 MHz / 16) × ((16 × 83) + 46) = 2473.2 MHz

f

LO

Data Format.

The synthesizer is programmed with a halfduplex 3-wire serial interface. The three signals are DATA, CLK,

and STROBE. Each rising edge of the CLK signal shifts one bit

of the data into a shift register. When the STROBE input is

toggled from low to high, the data latched in the shift register is

transferred to the A counter. The data format is as follows:

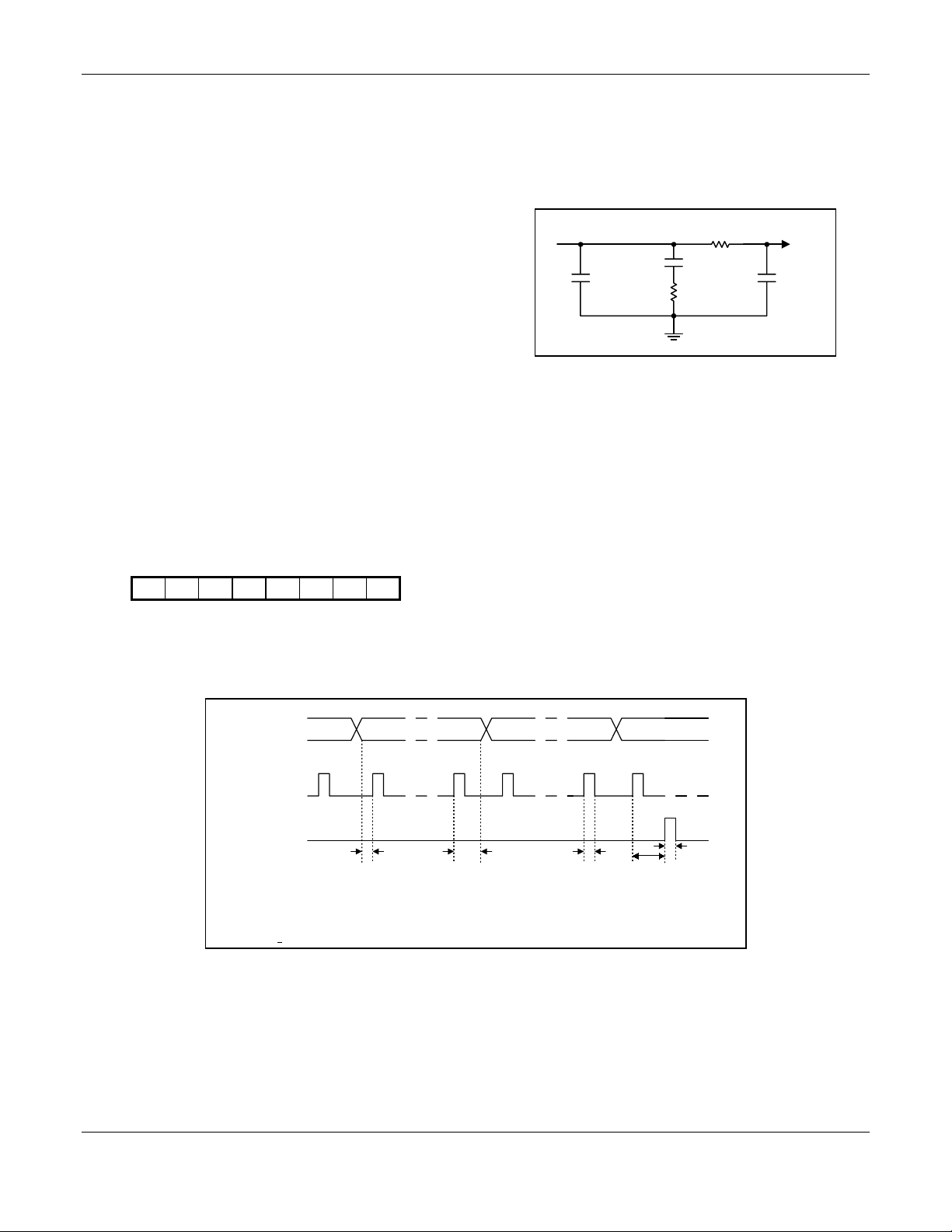

Synthesizer Loop Filter.

A typical loop filter design is shown

below in Figure 3. The loop bandwidth is approximately 5 kHz

with a nominal phase margin of 45 degrees for a VCO sensitivity

of 60 MHz/V.

CHPO

pin 43

0.01µF

390

pF

Figure 3. Typical Loop Fi lter

10k

10k

Ω

Ω

VCO

TUNE

330

pF

Power Management__________________________________

Independent power-up/power-down control of the transmit path,

receive path, and frequency synthesizer is provided by the

TXEN, RXEN and SYNTHEN controls, respectively. When all of

the functions are powered down, the current drain from the

voltage supply (Vcc) is at a minimum.

MSB

S7 S6 S5 S4 S3 S2 S1 S0

LSB

The timing relationship is shown in Figure 4. Programming bits

S0 to S5, used for the A counter, are defined in Table 1. Bits S6

and S7 are reserved.

MSB LSB

DATA

CLK

STROBE

t1 t2 t3

t1 =Data setup time

t2 =Data hold time

t3 =Clock pulse-width

t4 =STROBE enable pulse-width

t5 =STROBE setup time to the rising edge of the last clock

>

t1 to t5

1µs each

Figure 4. Timing Diagram

t5

t4

100646A

Conexant

1/19/00 Conexant Proprietary

3

RF109 2400 MHz Digital Spread Spectrum Transceiver

Table 1. Swallow C ounter Data Input

Synth. Channel No. (A) Frequency (MHz) S5 S4 S3 S2 S1 S0

0 2392.2 000000

1 2394.0 000001

2 2395.8 000010

.

.

.

6 2403.0 000110

7 2404.8 000111

8 2406.6 001000

.

.

.

25 2437.2 011001

26 2439.0 011010

27 2440.8 011011

.

.

.

45 2473.2 101101

46 2475.0 101110

47 2476.8 101111

.

.

.

61 2502.0 111101

62 2503.8 111110

63 2505.6 111111

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

4

Conexant

100646A

Conexant Proprietary 1/19/00

Loading...

Loading...