Conexant RC224ATL, RC224ATLV Datasheet

RC224ATL/224ATLV

EmbeddedModem Family

The new Conexant RC224ATL utilizes a new integrated data pump/controller to allow

the device to directly connect to host processors that are 3.3 V I/O capable. The codec

used in the new part is the same as the codec used in the existing RC224ATL. The

new device is form, fit, and function compatible with the existing device. This means

there are no hardware and software differences between the existing and the new part,

with one exception. The 3.3 V I/O capable part incorporates 3.3 V compatible digital

I/O buffers, hence requiring 3.3 V digital supply instead of 5 V digital supply.

In addition, unlike the current version of RC224ATL, the new part provides both

data and fax capabilities.

Data modes, controlled by an industry standard 2400 AT command set, can

transmit and receive up to 2400 bps.

Fax modes, controlled by a built-in EIA-578 Class 1 command interface, provide

Group 3 transmit and receive functions.

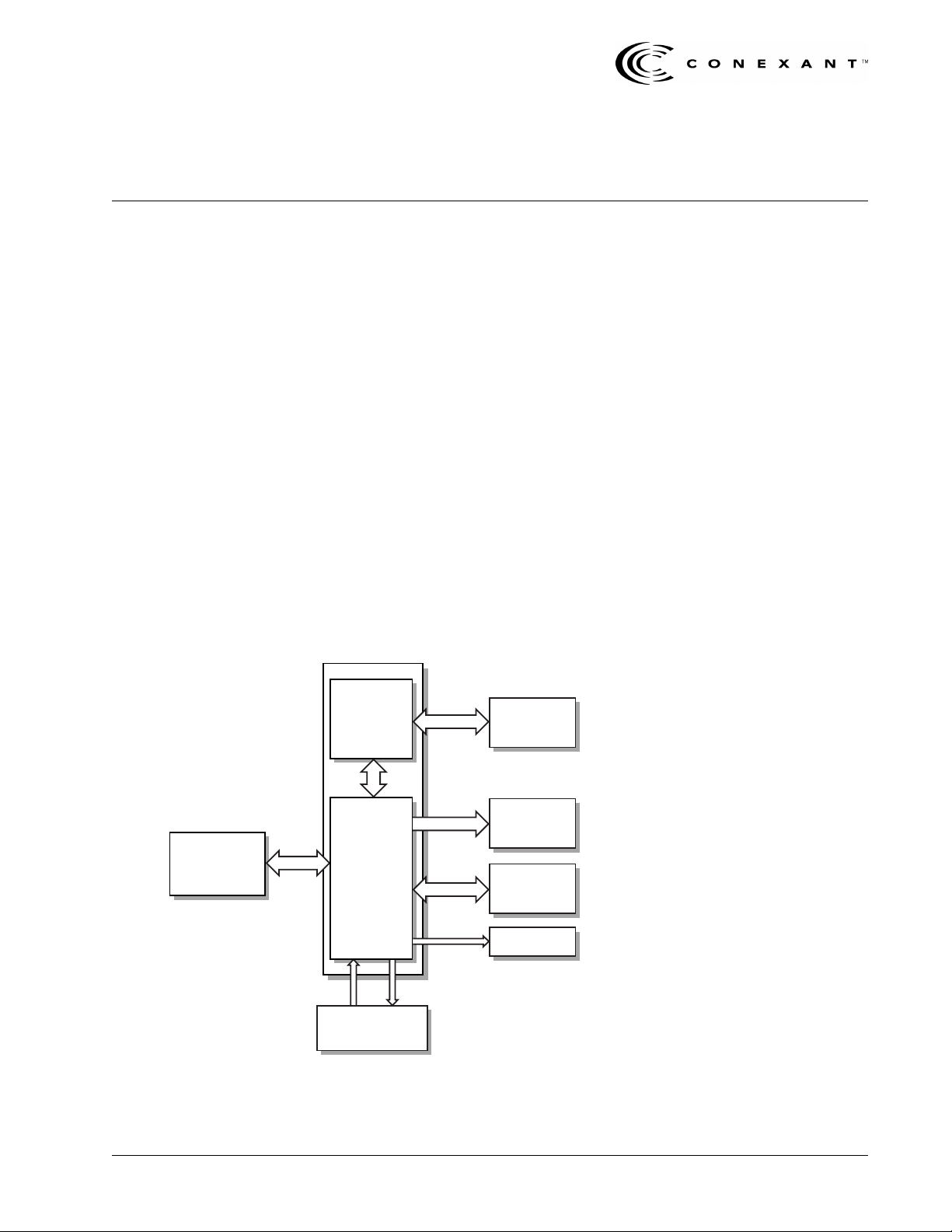

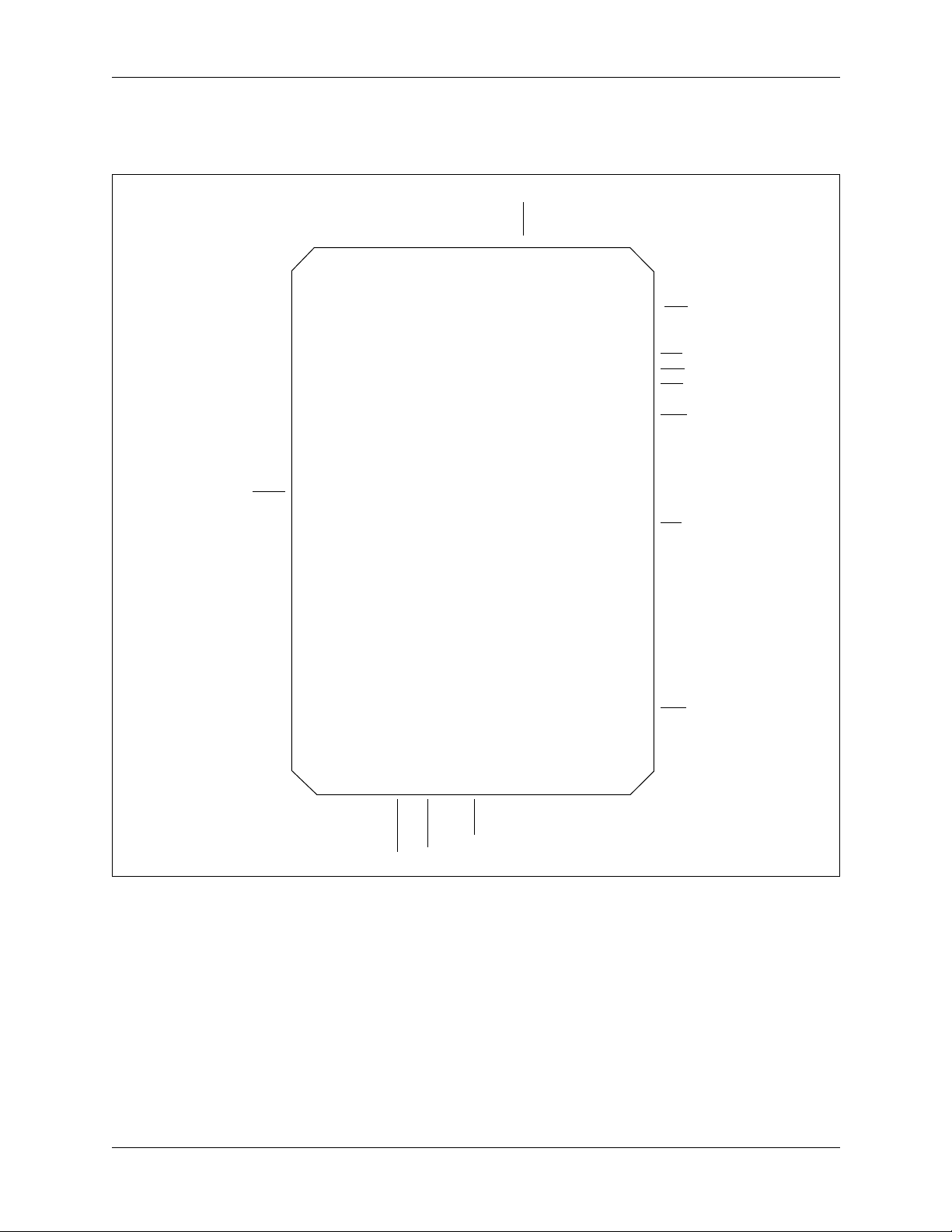

Functional Block Diagram

V.24

EIA-232-D

Interface

Modem

Data Pump

Modem

Controller

Crystal

Telephone

Line

Interface

Modem

LED

Indictors

Optional

NVRAM

Optional

Speaker

Distinguishing Features

• Data modes

– CCITT V.22 bis (2400 bps), V.22

(1200 bps)

– Bell 212A (1200 bps) and 103

(300 bps)

– Enhanced AT commands

• Group 3 fax modes

– V.29 (9600/7200 bps) transmit

– V.27 ter (4800/2400 bps)

transmit and receive

– V.21 Channel 2 (300 bps)

transmit and receive

• EIA-578 Service Class 1 commands

• V.42/MNP2-4 and V.42 bis/MNP 5

can be supported through host

software without additional hardware

• Data/fax discriminator and auto

answering

• Communications software

compatible

• Integrated call progress and dialing

• No external microcomputer or

memory required

• Parallel or serial asynchronous DTE

interface

• A/A1 relay control

• NVRAM interface allows storage of

two user configurations and four

36-digit dial strings

• Automatic adaptive/fixed

compromise equalization

• Programmable sleep mode and

wake-up

• Full-duplex data mode test

capabilities: Analog loop, local digital

loop, and remote digital loop

• Half-duplex fax mode test capabilities

• Automatic format/speed sensing

• Low power consumption (typical)

– Operating: 100 mW

– Sleep—Idle: 25 mW

– Sleep—Stop: 5 mW

• Single +5 V power supply or Dual

+ 3.3 VDD and + 5 VAA power

supplies

• Package options:

– 68-pin plastic leaded chip carrier

(PLCC)

– 100-pin plastic quad flat pack

(PQFP)

Data Sheet D224ATLVDSC

March 25, 1999

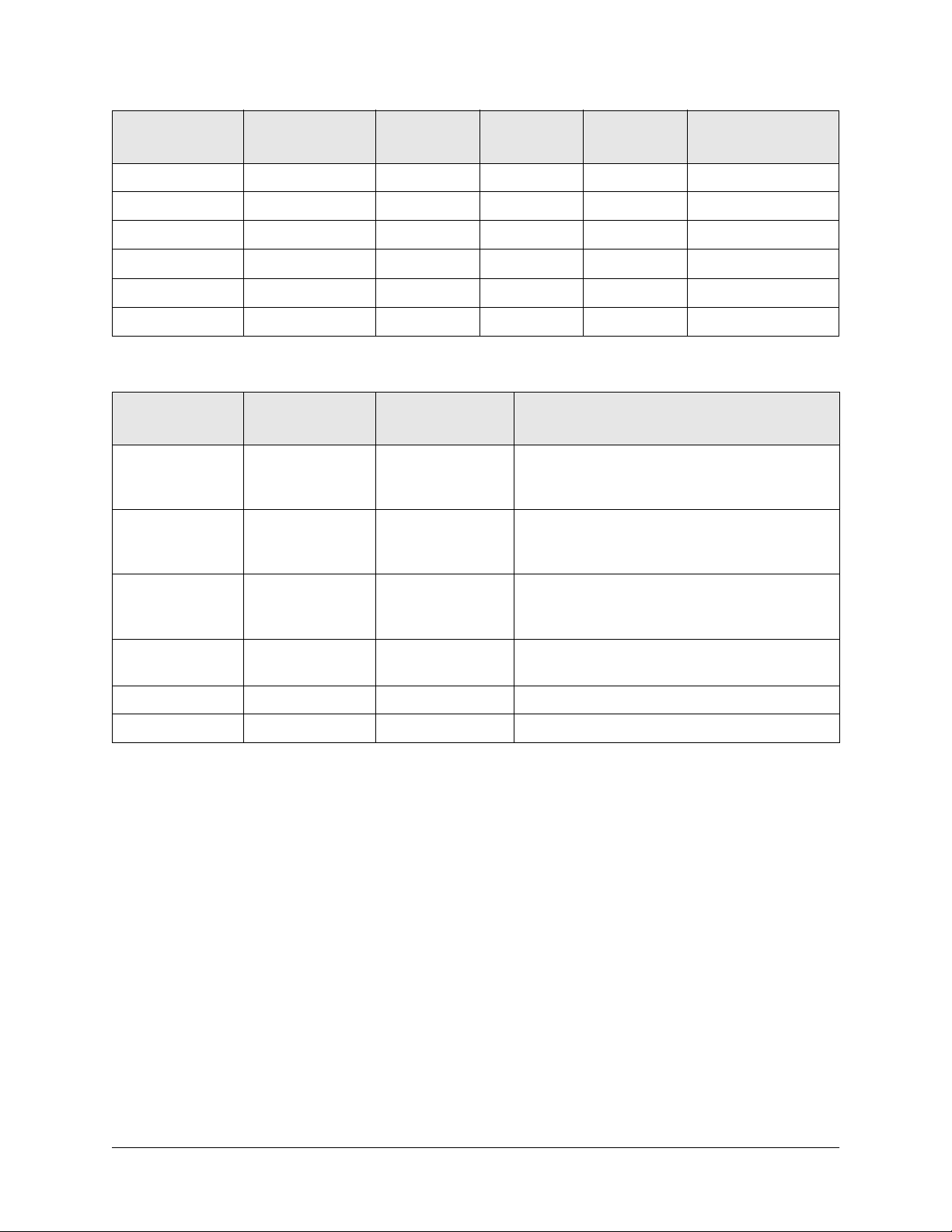

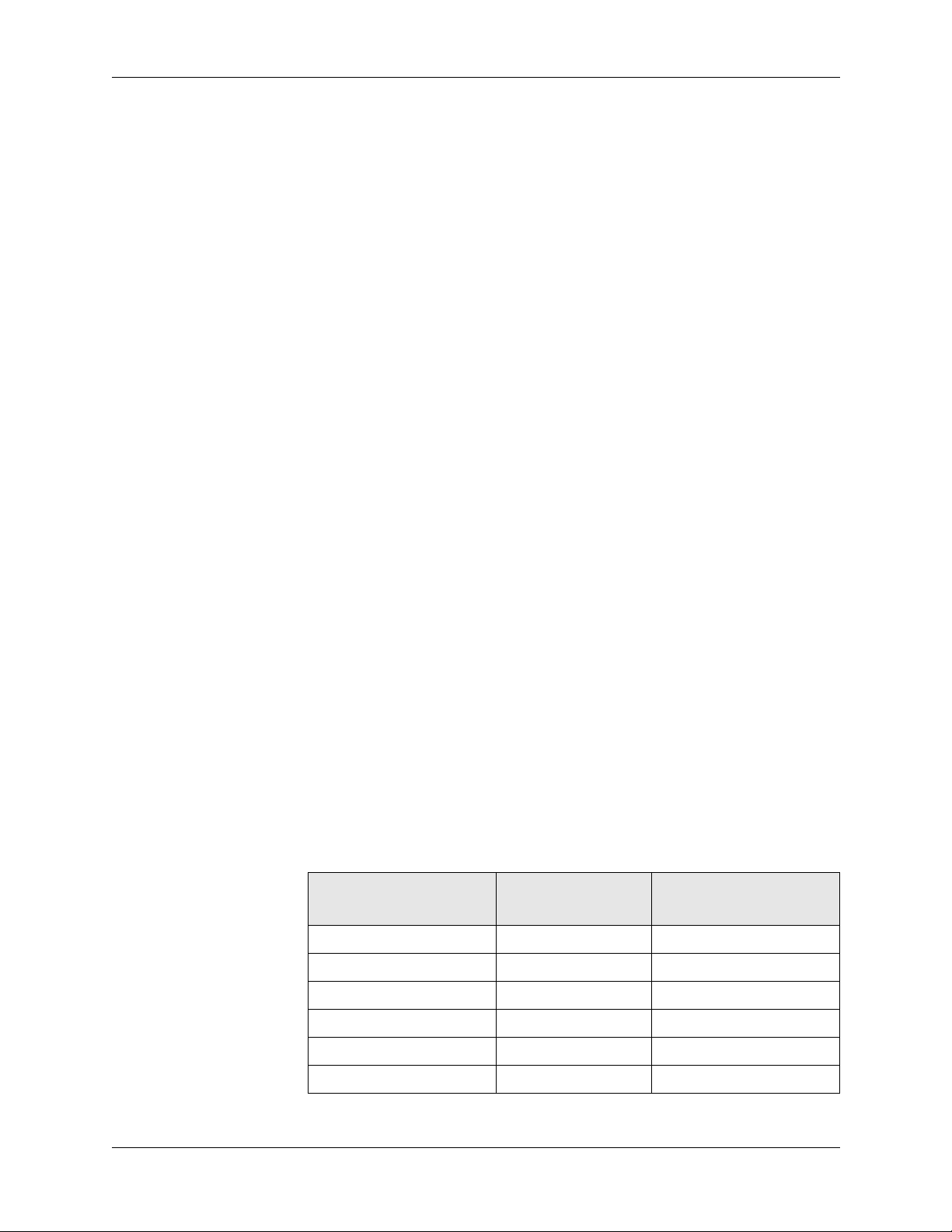

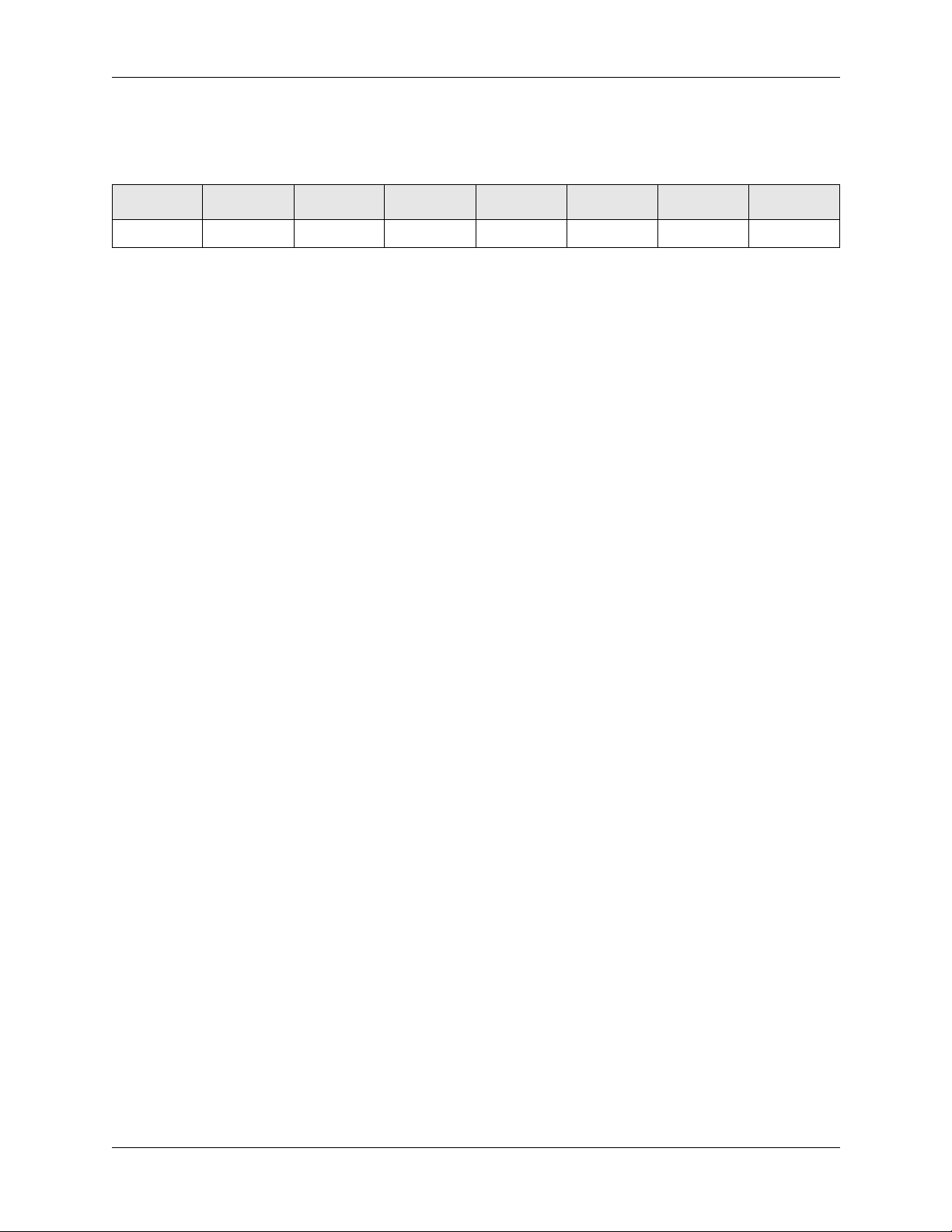

Ordering Information

Marketing

Number

Manufacturing

Number

DSP Die

Number

I/O & VCC VAA/Codec Package

RC224ATL R6781-11 L2501 5V 5V 68 PLCC

RC224ATL R6781-12 L2501 5V 5V 100 PQFP

RC224ATL R6781-13 L2503 5V 5V 68 PLCC

RC224ATL R6781-14 L2503 5V 5V 100 PQFP

RC224ATLV R6781-21 L2531 3V 5V 68 PLCC

RC224ATLV R6781-22 L2531 3V 5V 100 PQFP

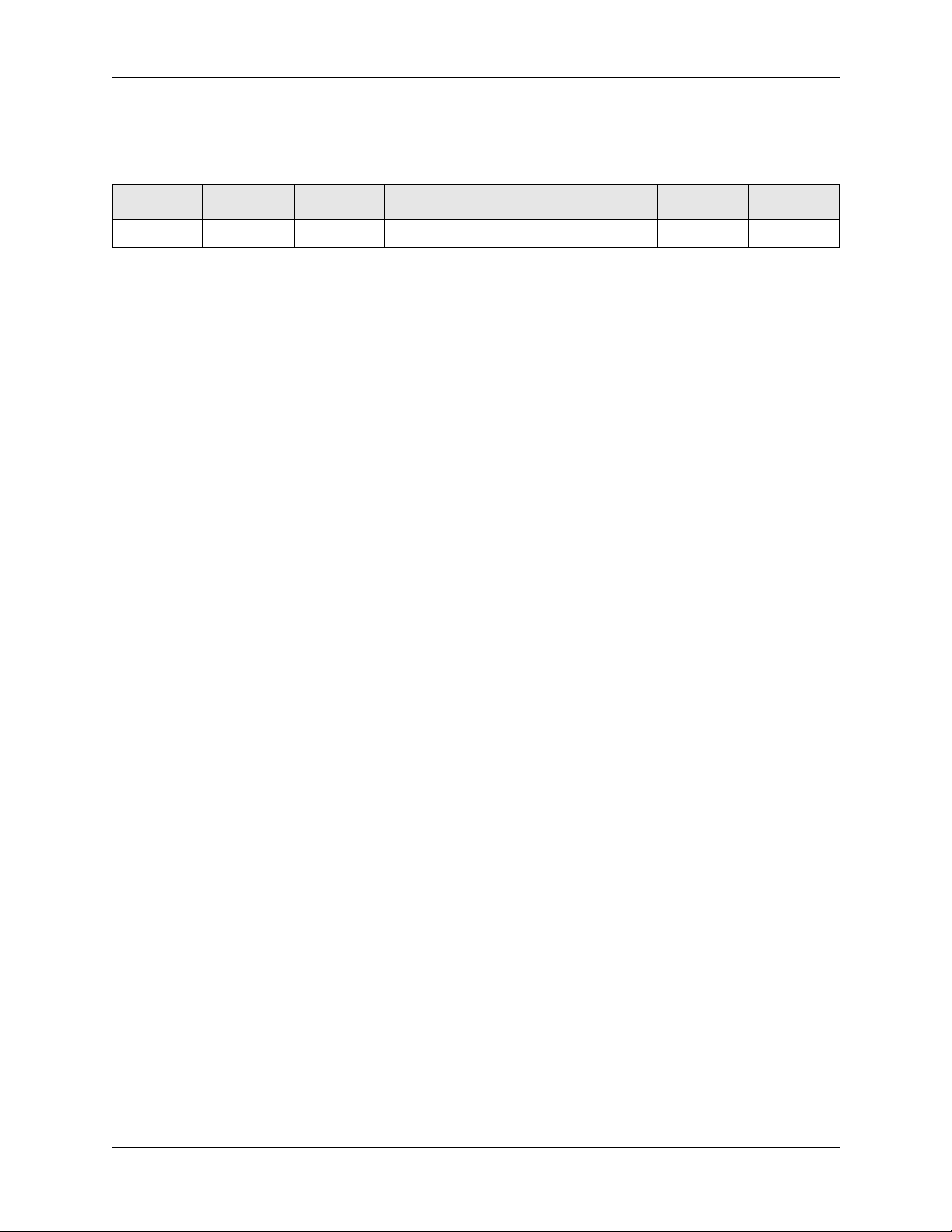

Replacement Matrix

Marketing

Number

RC224ATL R6781-11 68 PLCC RC224ATL/V (R6641-14), RC224ATL (R6641-15),

RC224ATL R6781-12 100 PQFP RC224ATL/V (R6641-18), RC224ATL (R6641-19),

Manufacturing

Number

Package Replaces

RC224ATL/VN (R6641-16), RC224ATLN (R6641-17),

RC224ATL/VE (R6641-24), RC224ATLE (R6641-25)

RC224ATL/VN (R6641-20), RC224ATLN (R6641-21),

RC224ATL/VE (R6641-26), RC224ATLE (R6641-27)

RC224ATL R6781-13 68 PLCC RC224ATL/VN (R6641-36), RC224ATL/V

(R6641-37), RC224ATLN (R6641-38), RC224ATL

(R6641-39)

RC224ATL R6781-14 100 PQFP RC224ATL/VN (R6641-40), RC224ATATL/V

(R6641-41), RC224ATL (R6641-43)

RC224ATLV R6781-21 68 PLCC N/A: New 3.3 V Digital I/O

RC224ATLV R6781-22 100 PQFP N/A: New 3.3 V Digital I/O

Information provided by C onexant Systems, Inc. (Conexant) is believed to be accurate and reliable. However, no responsibility is

assumed by Conexant for its use, nor any infringement of patents or other rights of third parties which may result from its use. No

license is granted by implication or otherwise under any patent rights of Conexant other than for circuitr y embodied in Conexant

products. Conexant reserves the right to change circuitry at any time without notice. This document is subject to change without

notice.

Conexant and “What’s Next in Communications Technologies” are tr ademarks of Conexant Systems, Inc.

Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered

trademarks of their respective companies. All other mark s mentioned herein are the property of their respective holders.

© 1999 Conexant Systems, Inc.

Print e d in U.S.A.

All Rights Reserved

Reader Response:

suggestions via e-mail to Conexant Reader Response@conexant.com. Sorry, we can't answer your technical

questions at this address. Please contact your local Conexant sales office or local field applications engineer if you

have technical questions.

To improv e th e qu ali t y o f our p ublications, we welco me your feedback. Pleas e se nd c om me nts or

D224ATLVDSC Conexant

Table of Contents

List of Figures

List of Tables

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . vii

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ix

1.0 Functional Description

1.1 Overview

1.2 Technical Specifications

1.2.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.2 Configurations and Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.3 Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.4 Data/Fax Auto Answering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.5 Data Modulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.6 Equalization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.7 Scrambler/Descrambler. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.8 Transmit Level . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.9 Transmit Tones . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.10 Receive Level. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.11 Receiver Tracking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.12 Low Power Sleep Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.2.3.1 Data Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.3.2 Fax Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1-1

1-2

1-3

1-3

1-3

1-3

1-3

1-3

1-3

1-4

1-4

1-4

1-4

1-5

2.0 Hardware Interface

2.1 Hardware Interface

2.1.1 Parallel Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.2 Serial/Indicator Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.3 Speaker Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.4 Line Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Additional Information

D224ATLVDSC Conexant

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

2-6

2-12

2-12

2-12

iii

Table of Contents

RC224ATL/224ATLV

3.0 Pin Descriptions

4.0 AT Commands

5.0 S Registers

6.0 Operation

6.1 Data Modes

6.1.1 Data Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1.2 Data Modem Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1.3 Call Origination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1.4 Call Answering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1.5 Call Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2 Fax Modes

6.2.1 Fax Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.2 Fax Mode Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.3 Fax Origination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.4 Fax Answering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.5 Fax Data Transmission. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.6 Fax Data Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.7 Fax Control Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.8 Fax Control Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.9 Fax I/O Processing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

EmbeddedModem Family

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6-1

6-1

6-2

6-2

6-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6-3

6-3

6-3

6-3

6-4

6-4

6-4

6-5

6-5

6.3 Fax Enhanced Flow Control

6.3.1 Parallel/Serial Interface Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.2 Fax V.42 Buffer Sizes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.3 DTE Flow Control Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4 Data/Fax Auto Answering

6.5 Call Progress

6.5.1 Call Progress Algorithms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.5.2 Ring Detection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-12

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

7.0 Electrical/Mechanical Specifications

7.1 Interfacing the RC224ATLV

7.2 Environmental Requirements

7.3 Interface Timing and Waveforms

Appendix A: RC224ATF Modem Designs

A.1 68-Pin PLCC Design for Serial Interface

A.2 68-Pin PLCC Design for Parallel Interface

Appendix B: Acronyms/Abbreviations

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

6-7

6-7

6-8

6-12

6-13

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-6

iv

Conexant

D224ATLVDSC

RC224ATL/224ATLV

List of Figures

EmbeddedModem Family

List of Figures

Figure 2-1. RC224ATLV Signals—Parallel Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

Figure 2-2. RC224ATLV Signals—Serial Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Figure 3-1. 68-Pin PLCC Package—Serial. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

Figure 3-2. 68-Pin PLCC Package—Parallel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-2

Figure 3-3. 100-Pin PQFP Package—Serial. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-3

Figure 3-4. 100-Pin PQFP Package—Parallel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-4

Figure 3-5. NVRAM Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-20

Figure 7-1. Timing Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

Figure 7-2. 68-Pin PLCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

Figure 7-3. 100-Pin PQFP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

Figure A-1. Serial Interface Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

Figure A-2. Serial Interface Design DAA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-3

Figure A-3. Parallel Interface Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-7

Figure A-4. Parallel Interface Design DAA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-8

D224ATLVDSC Conexant v

List of Figures

RC224ATL/224ATLV

EmbeddedModem Family

vi Conexant D224ATLVDSC

RC224ATL/224ATLV

List of Tables

EmbeddedModem Family

List of Tables

Table 1-1. Configurations and Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

Table 1-2. Data Rates vs. Connection Modem Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1- 3

Table 1-3. Dial Digits/Tone Pairs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Table 1-4. Current and Power Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-5

Table 2-1. Parallel Interface Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

Table 2-2. Programmable Baud Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

Table 3-1. RC224ATL/224ATLV 68-Pin PLCC Pin Assignments—Serial Mode . . . . . . . . . . . . . . . . . . . 3-5

Table 3-2. RC224ATLV 68-Pin PLCC Pin Assignments—Parallel Mode. . . . . . . . . . . . . . . . . . . . . . . . . 3-6

Table 3-3. RC224ATL/224ATLV 100-Pin PQFP Pin Assignments—Serial . . . . . . . . . . . . . . . . . . . . . . . 3-7

Table 3-4. RC224ATL/224ATLV 100-Pin PQFP Pin Assignments—Parallel . . . . . . . . . . . . . . . . . . . . . 3-11

Table 3-5. Hardware Interface Signal Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-15

Table 4-1. Result Codes and Messages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

Table 4-2. AT Command Set Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

Table 4-3. Fax Command Set Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

Table 5-1. S Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Table 5-2. S Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

Table 6-1. Data Rate Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

Table 6-2. Terminal Called by a 1200 bps Data Modem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-10

Table 6-3. Terminal Called by a Fax Machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-11

Table 6-4. Tone Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-12

Table 6-5. Fax Class 1 Calling Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

Table 6-6. Fax Class 1 Answering Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-15

Table 7-1. Environmental Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

Table 7-2. Timing–Host Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

Table 7-3. Current and Power Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-4

Table 7-4. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

Table 7-5. Digital Interface Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

Table 7-6. Analog Interface Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

Table 7-7. 68-Pin PLCC Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-8

Table 7-8. 100-Pin PQFP Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-10

Table A-1. Serial Bill of Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

Table A-2. Parallel Billing Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-9

D224ATLVDSC Conexant vii

List of Tables

RC224ATL/224ATLV

EmbeddedModem Family

viii Conexant D224ATLVDSC

1

1.0 Functional Description

1.1 Overview

The Conexant RC224ATLV is a combination V.22 bis data and Group 3 fax

CMOS modem in a single VLSI package and is identical to the RC224ATLV. The

RC224ATLV integrated data/fax modem is available in either a 68-pin plastic

leaded chip carrier (PLCC) or a 100-pin plastic quad flat pack (PQFP).

Full error correction (V.42 LAPM, MNP2-4) and data compression (V.42 bis,

MNP 5) capabilities can be supported in the RC224ATLV using the host

communication software.

The modem has a selectable parallel or serial interface to the host data

terminal equipment (DTE). When parallel mode is selected, a 16C450-compatible

interface allows direct connection to a notebook, laptop, or PC-compatible bus

without an external universal asynchronous receive/transmit (UART). When

serial mode is selected, a CCITT V.24 logic-compatible interface with transistor to

transistor logic (TTL) levels is supplied along with indicator outputs.

1.2 Technical Specifications

1.2.1 General

The RC224ATLV modem is a full-featured, self-contained data/fax solution. No

external microcontroller for data or fax control functions is required. Dialing, call

progress, and telephone line interface functions are fully supported and controlled

through the AT command set.

Data modes perform complete handshake and data rate negotiations. All tone

and pattern detection required by the applicable CCITT or Bell standard are

supported.

Fax modes support Group 3 fax requirements. Fax data and fax control (V.21

300 bps), performed by the modem, are controlled and monitored through the fax

EIA-578 Class 1 command interface. Full HDLC formatting, flag

insertion/deletion, and CRC generation/checking is provided.

Both transmit and receive fax data is buffered within the modem. Fax data

transfer to and from the DTE is flow controlled by X-on/X-off.

D224ATLVDSC Conexant 1-1

1.0 Functional Description

RC224ATL/224ATLV

1.2 Technical Specifications

1.2.2 Configurations and Rates

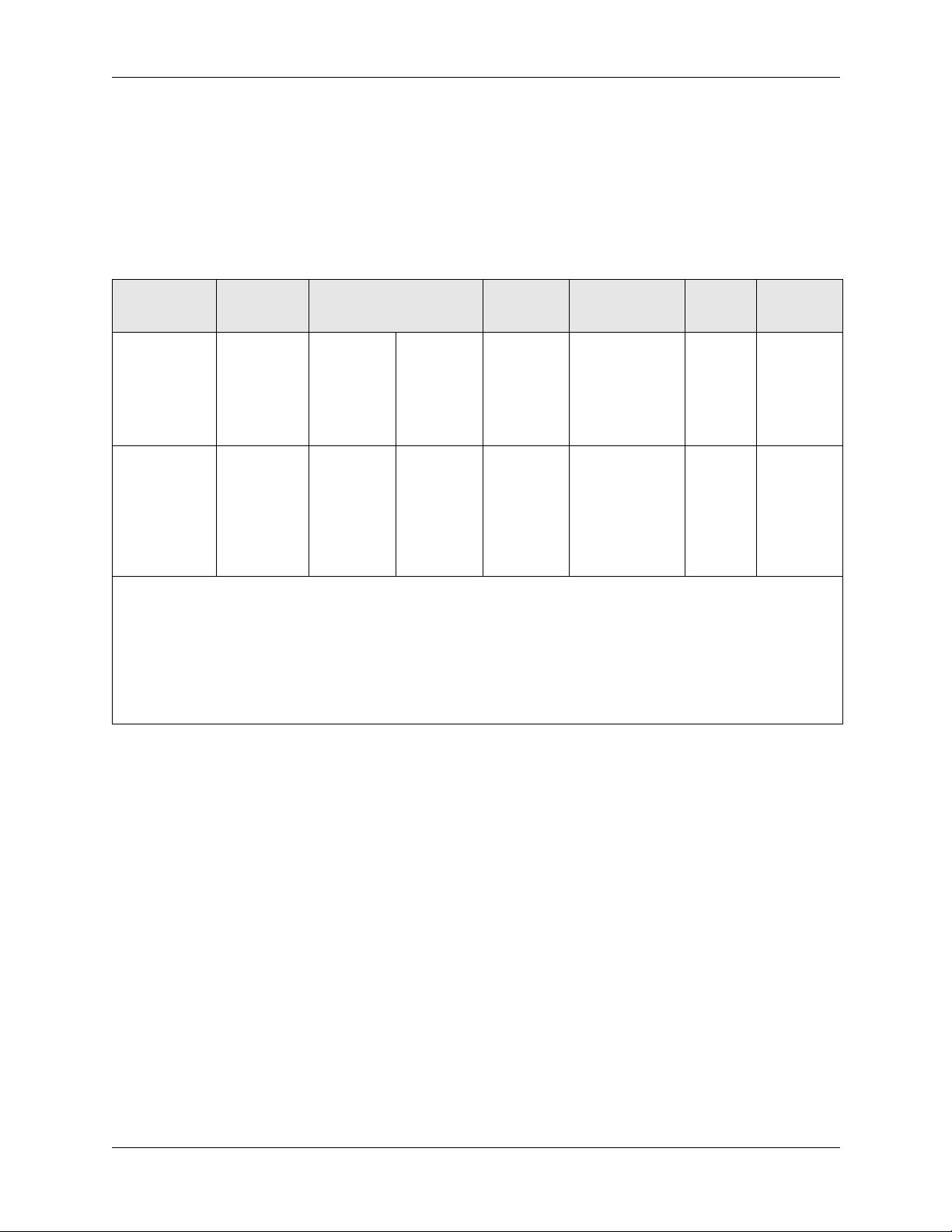

The supported modem configurations and signaling rates are listed in Ta bl e 1-1 .

In data modes with serial interface selected, DTE rate offsets of + 1%, – 2.5% are

accommodated by adding/deleting stop bits as required. In fax modes, the DTE

rate is 19,200 bps.

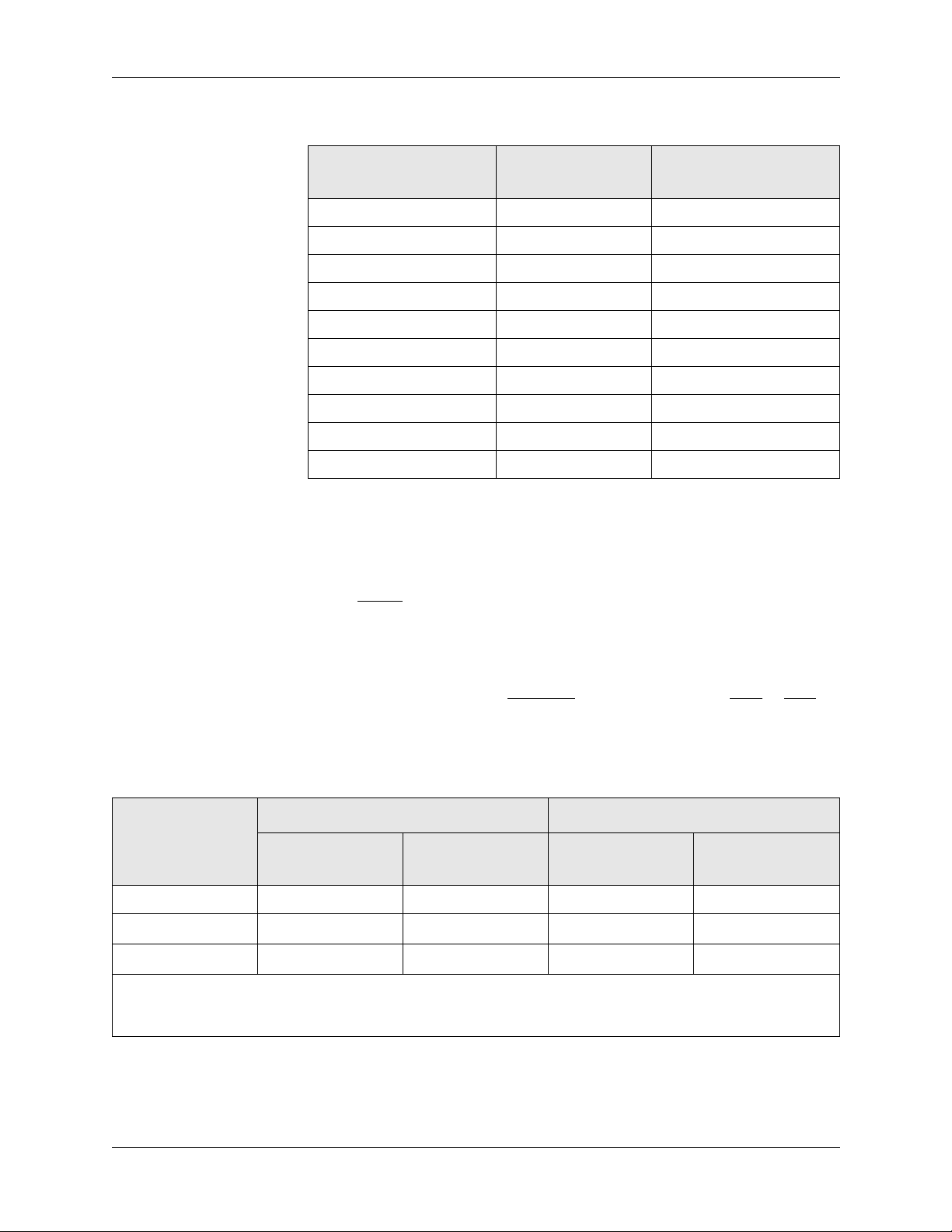

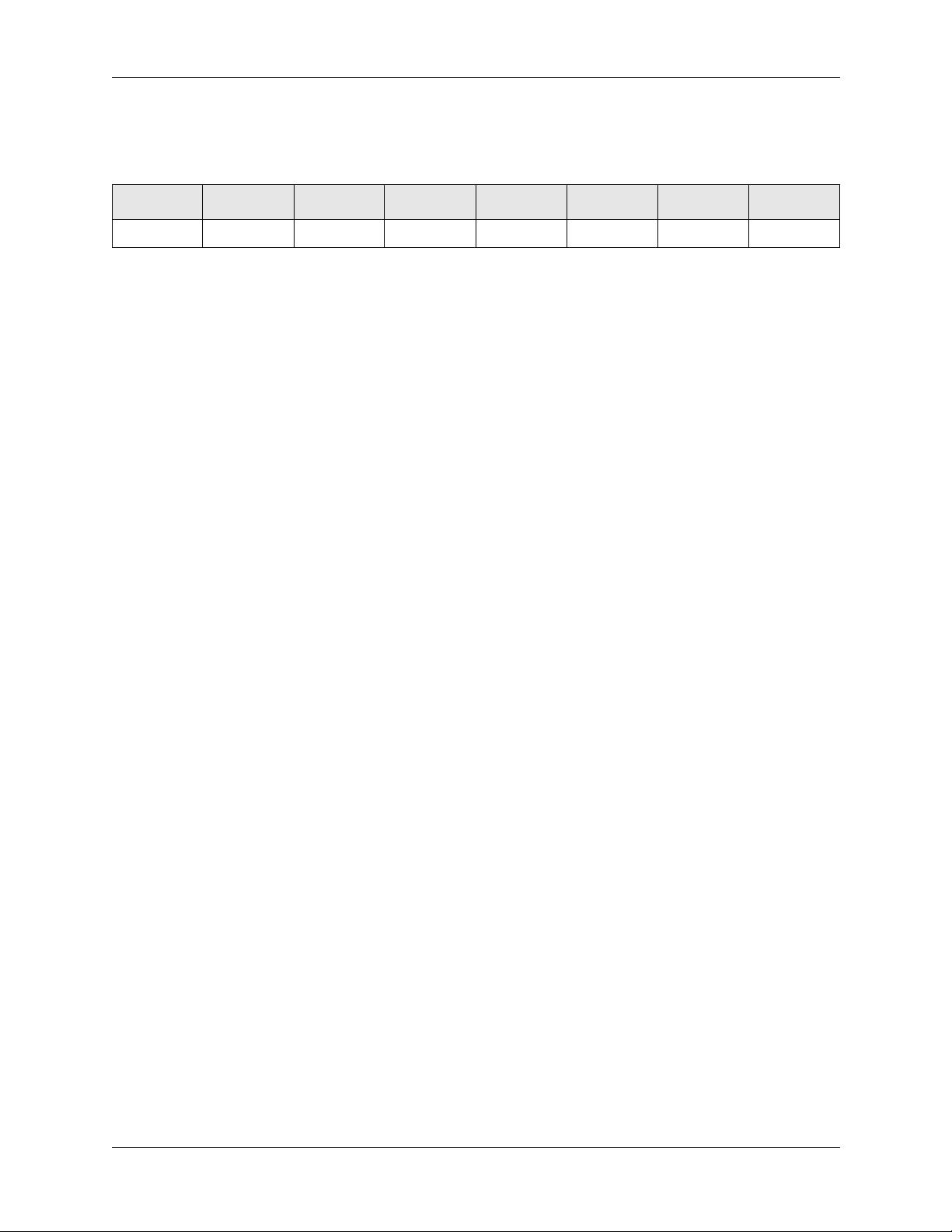

Table 1-1. Configurations and Rates

Configuration Modulation

Data Mode

V.22 bis

V. 2 2

Bell 212A

Bell 103

Fax Mode

V. 2 9

V.2 7 te r

V.2 1

QAM

DPSK

DPSK

FSK

QAM

QAM

DPSK

DPSK

FSK

Transmitter Carrier

Frequency (Hz)

Answer

2400

2400

2400

2225 M

2025 S

Receive

N/A

N/A

1800

1800

1650 M

1850 S

0.01%

±

Originate

1200

1200

1200

1270 M

1070 S

Transmit

1700

1700

1800

1800

1650 M

1850 S

Data Rate

(bps)

2400

1200

1200

300

9600

7200

4800

2400

300

Baud

(Symbols/Sec.)

600

600

600

300

2400

2400

1600

1200

300

EmbeddedModem Family

Bits Per

Symbol

4

2

2

1

4

3

3

2

1

Constellation

Points

16

4

4

1

16

8

8

4

1

Legend:

QAM Quadrature Amplitude Modulation

DPSK Differential Phase Shift Keying

FSK Frequency Shift Keying

M Mark condition

S Space Condition

N/A Not Applicable

1-2 Conexant D224ATLVDSC

RC224ATL/224ATLV

1.0 Functional Description

EmbeddedModem Family

1.2.3 Operation

1.2.3.1 Data Modes

1.2.3.2 Fax Modes

1.2 Technical Specifications

Modem operation is controlled by AT commands, fax service class 1 commands,

and supporting S registers.

Data rate selection is determined by the speed of the originating and answering

modems, as defined in Ta ble 1 -2 .

Table 1-2. Data Rates vs. Connection Modem Rate

Originate Modem Rate

(bps)

300 300 300 300

1200 300 1200 1200

2400 300 1200 2400

Fax modes are negotiated as defined in T.30 and are implemented by AT+F

commands. The AT+FCLASS=1 command causes entry into the fax mode from

the data mode. Most other fax class 1 commands, which start with the AT+F

prefix, are valid only in the fax mode. All data commands are valid in the fax

mode except A/, On, &Tn, and the escape sequence (+++). The AT+FCLASS=0

command terminates the fax mode and causes entry into the data mode.

Connect Speed Based on Answer Modem Rate (bps)

300 1200 2400

1.2.4 Data/Fax Auto Answering

The modem can automatically determine if the incoming call is from a data or fax

modem, make the appropriate connection, and inform the DTE of the connection

type.

1.2.5 Data Modulation

The data modulation conforms to V.29, V.27 ter, V.22 bis, V.22, V.21, Bell 212A,

or Bell 103, depending on the selected configuration. Transmitter and receiver

spectrum shaping is provided in accordance with the applicable standard.

1.2.6 Equalization

Automatic adaptive equalization and fixed compromised equalization are

provided to compensate for line distortions and to minimize the effects of

intersymbol interference.

1.2.7 Scrambler/Descrambler

The modem incorporates a self-synchronizing scrambler/descrambler, which

satisfies the applicable CCITT or Bell requirements.

D224ATLVDSC Conexant 1-3

1.0 Functional Description

RC224ATL/224ATLV

1.2 Technical Specifications

1.2.8 Transmit Level

1.2.9 Transmit Tones

Answer Tone

Guard Tone

Calling Tone

1.2.10 Receive Level

EmbeddedModem Family

The transmit level is – 10 dBm ± 1 dB (at TIP and RING) and can be obtained

using the circuits shown in Appendix A. Carrier and dual tone multi-frequency

(DTMF) transmit levels can be further attenuated using AT%Ln + AT%Dn

commands, respectively. If a higher transmit level is required, an external op amp

can be added.

An answer tone of 2100 Hz (V.22 bis, V.22, or T.30) or 2225 Hz (Bell 212A or

103) is generated.

An 1800 Hz guard tone can be generated in all data modes.

An 1100 Hz (0.5 seconds on, 3 seconds off) calling tone (T.30) is generated in the

originate fax mode.

The receiver satisf ies performance requirements for a received signal from

– 9 dBm to – 43 dBm. The carrier detect is ON at – 43 dBm and OFF at – 48 dBm

with a minimum of 2 dB hysteresis.

1.2.11 Receiver Tracking

The modem can accommodate carrier frequency offset up to ± 7 Hz, and a

transmit timing error of

212A).

DTMF Dialing

Ring Detection

Standard DTMF tones (digits 0-9, A, B, C, D, *, and #) or pulses (digits 0-9) can

be generated. Refer to Table 1- 3.

RING signal is detected from valid high to low transitions on the RING input line

at frequencies of 15.3 Hz to 63 Hz. A RING is valid if the RING ON time is

greater than 0.125 seconds and is followed by a RING OFF time greater than 0.5

seconds.

Table 1-3. Dial Digits/Tone Pairs (1 of 2)

±

0.01% (V.22 bis or V.27 ter) or ± 0.02% (V.22 or Bell

Dial Digit

0 941 1336

1 697 1209

2 697 1336

3 697 1477

4 770 1209

Tone 1

Frequency (Hz)

Tone 2

Frequency (Hz)

5 770 1336

1-4 Conexant D224ATLVDSC

RC224ATL/224ATLV

1.0 Functional Description

EmbeddedModem Family

Table 1-3. Dial Digits/Tone Pairs (2 of 2)

1.2.12 Low Power Sleep Mode

1.2 Technical Specifications

Dial Digit

6 770 1477

7 852 1209

8 852 1336

9 852 1477

* 941 1209

# 941 1477

A 697 1633

B 770 1633

C 852 1633

D 941 1633

Tone 1

Frequency (Hz)

Tone 2

Frequency (Hz)

To conserve power, the RC224ATLV has two selectable sleep (power-down)

modes – Idle and Stop. If enabled by the IDLEN0 and IDLN1 inputs, the selective

sleep mode is entered whenever the modem is active. The sleep mode indicator

output, SLEEP

, is provided to allow external circuits to be powered down when

the modem is in Idle or Stop mode.

The Idle mode allows reduced power consumption with automatic recovery

without additional circuitry. If Idle mode is selected, the modem exits Idle mode

and returns to full operation whenever a ring signal occurs, the DTE writes to the

modem (parallel interface), or WAKEUP

input, normally tied to DTR or TXD, is

asserted (serial interface).

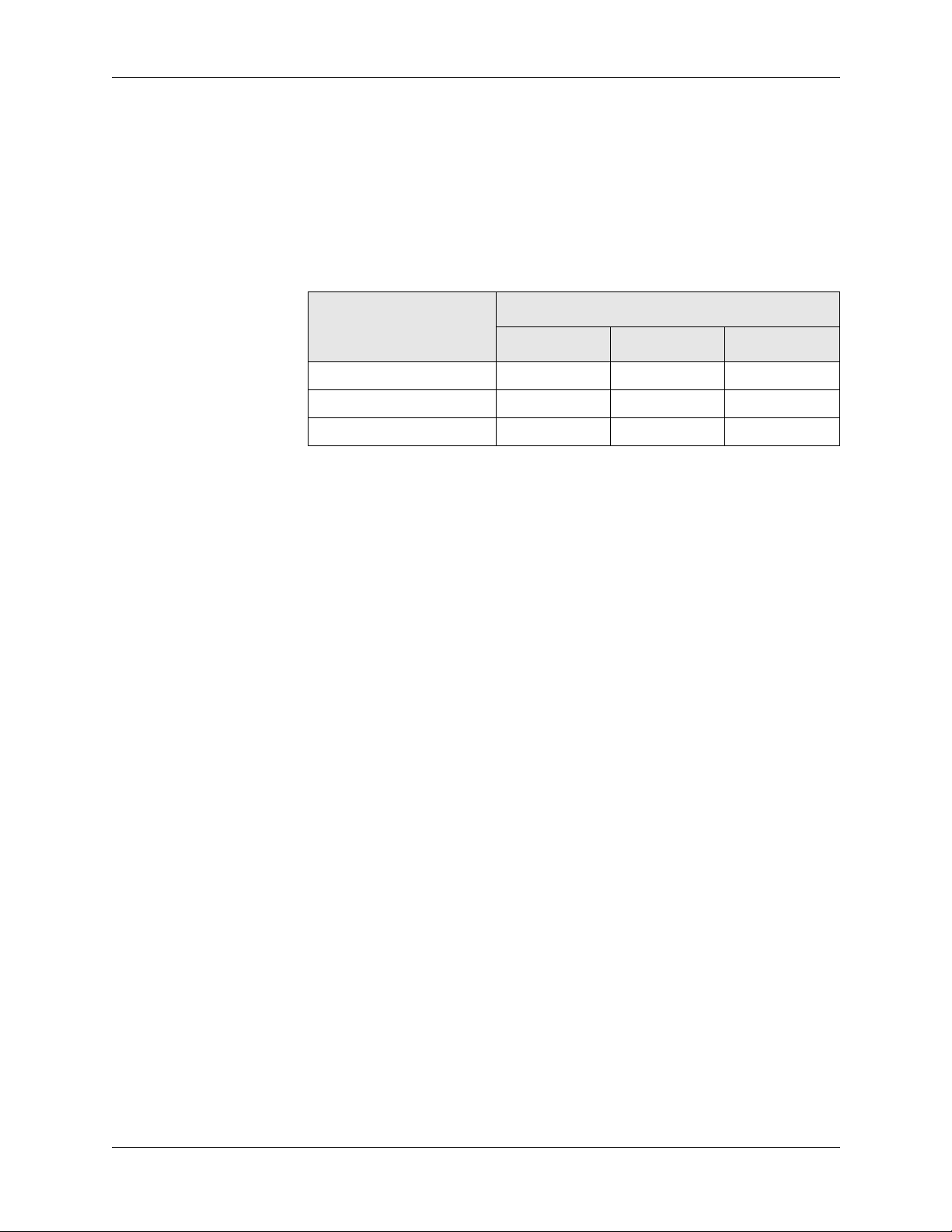

The Stop mode further reduces power consumption, as defined in Tabl e 1 -4 .

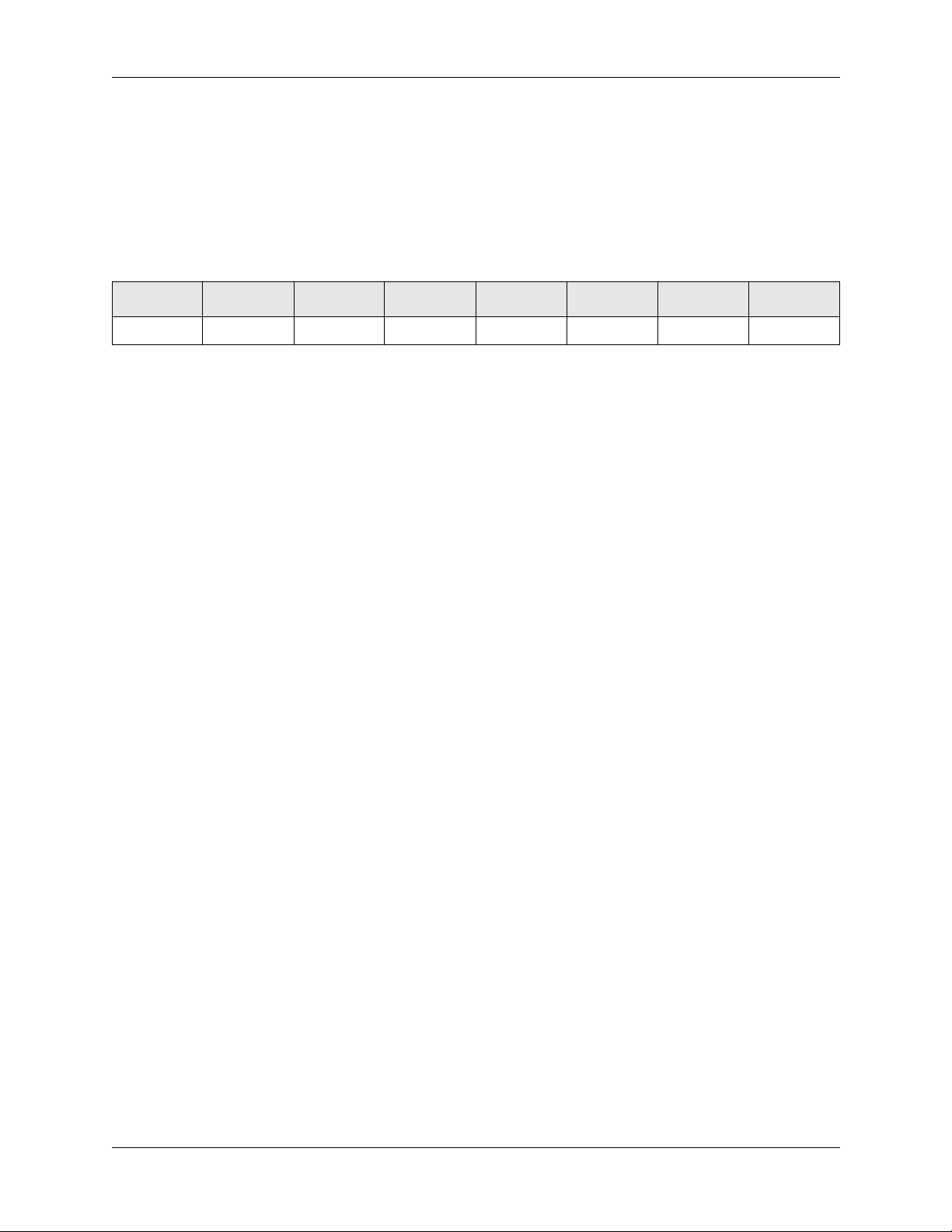

Table 1-4. Current and Power Requirements

Current (ID) Power (PD)

Mode

Operating 21 mA 22 mA 100 mW 110 mW

Idle

Sleep

–

Sleep–Stop

NOTE(S):

1. Test conditions: VDD = 5.0 VDC for typical values; VDD = 5.25 VDC for maximum values.

2. Test conditions: VDD = 3.3 V

Typical

Current @ 25°C

5 mA 6 mA 25 mW 30 mW

1 mA 1 mA 5 mW 5 mW

for typical values; VDD = 3.6 VDC for maximum values.

DC

Maximum Current

@ 0°C

Typical

Power @ 25°C

Maximum

Power @ 0°C

D224ATLVDSC Conexant 1-5

1.0 Functional Description

RC224ATL/224ATLV

1.2 Technical Specifications

Entry

Wake-up—Parallel

Interface Configuration

Wake-up—Serial

Interface Configuration

EmbeddedModem Family

The modem will enter the low-power sleep mode when no line connection exists

and no host activity occurs for the period of time specified in the S24 register. All

EmbeddedModem circuits are turned off except the internal Microcontroller Unit

(MCU) clock circuitry in order to consume lower power but are able to

immediately wake up and resume normal operation.

Wake-up occurs when a ring signal occurs, or the host write to the modem.

Wake-up occurs when a ring signal occurs, or the DTE sends a character to the

modem.

1-6 Conexant D224ATLVDSC

2

2.0 Hardware Interface

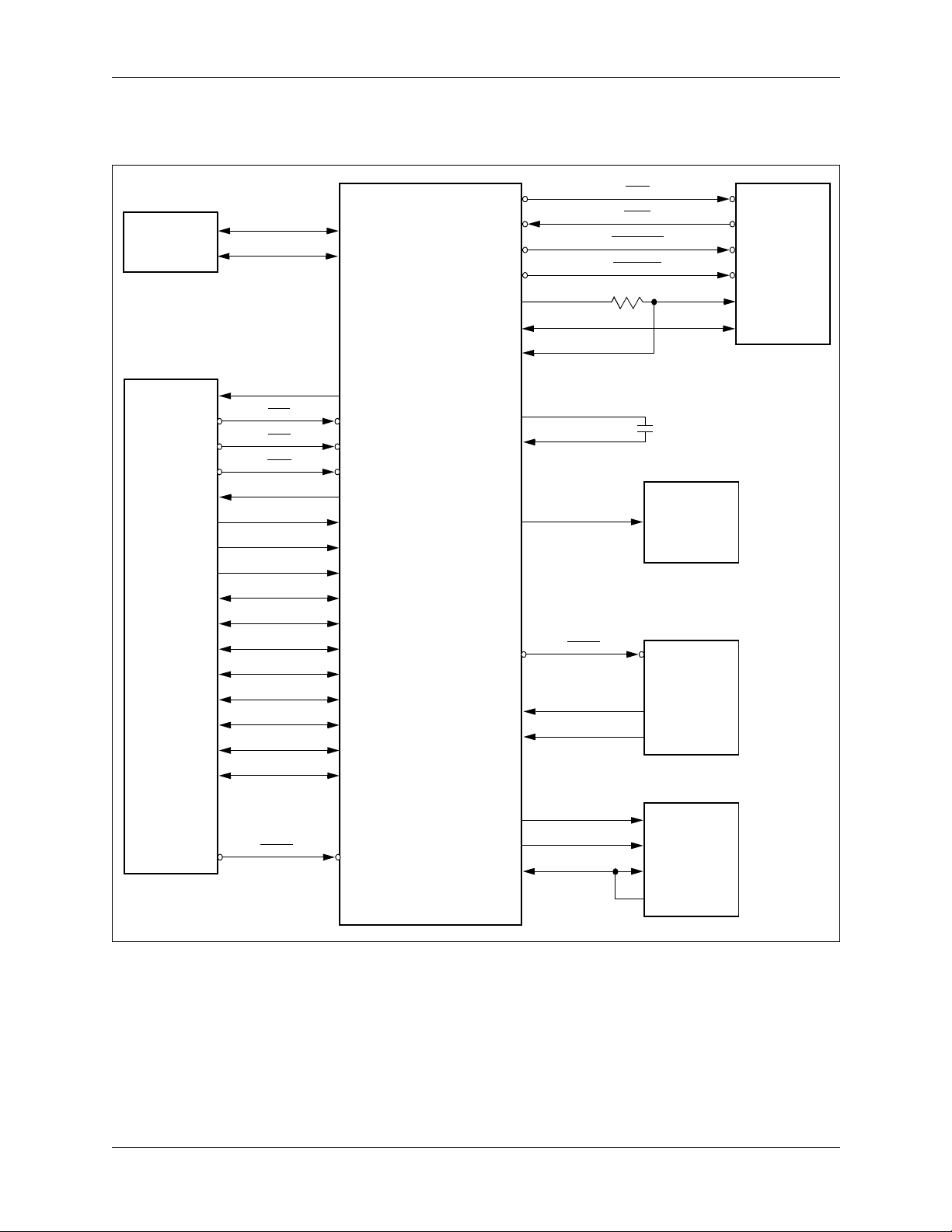

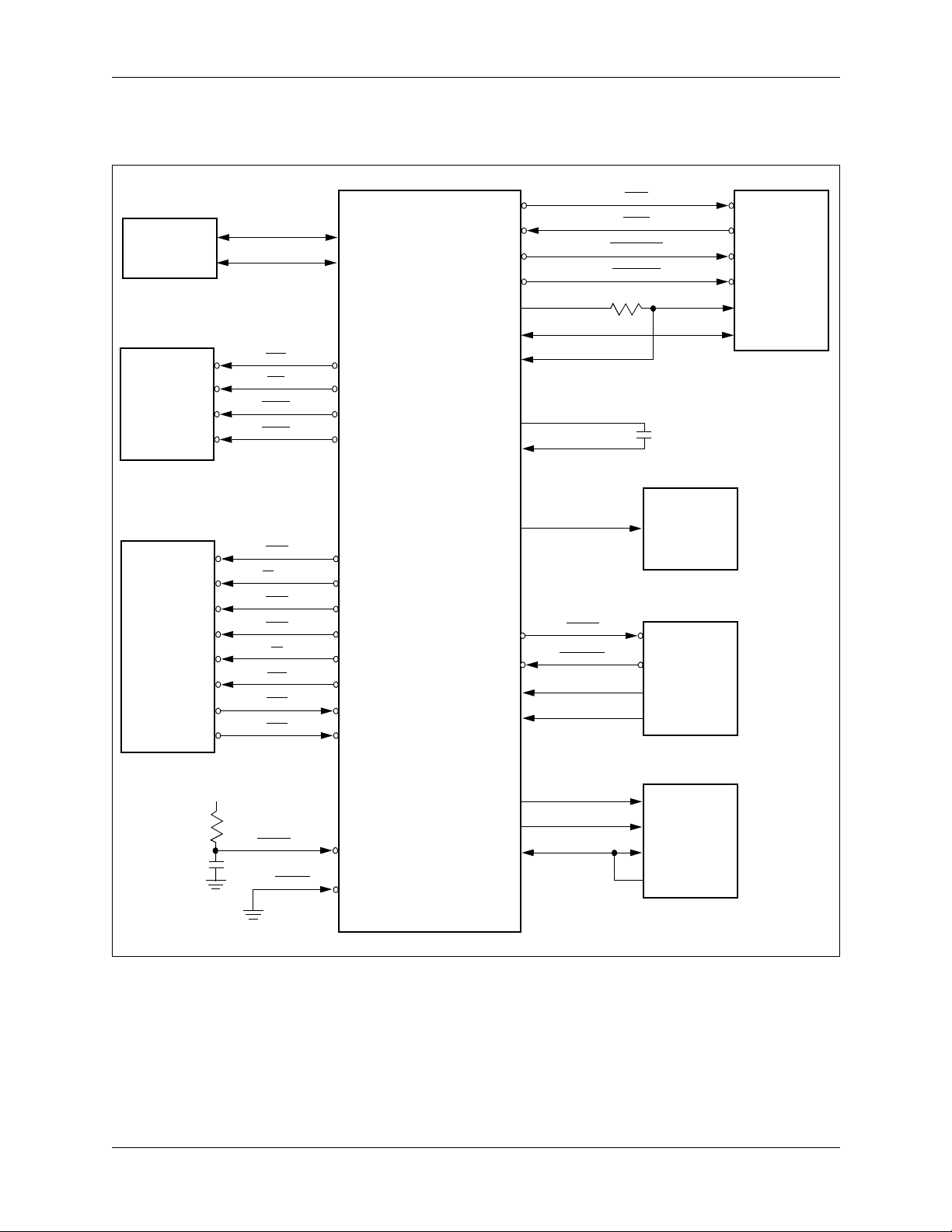

Figure 2-1 and Figure 2-2 illustrate the RC224ATLV hardware interface signals

for the parallel and serial interfaces, respectively.

The RC224ATLV hardware interface signals are described in

Table 3-5,

See Table 7-2,

timing parameters and Figure 7-1,

interface waveforms.

Hardware Interface Signal Definitions

Timing–Host Bus Interface

Timing Waveform

for a list of the host bus interface

.

for an illustration of the

D224ATLVDSC Conexant 2-1

2.0 Hardware Interface

RC224ATL/224ATLV

Figure 2-1. RC224ATLV Signals—Parallel Interface

XTLI

Crystal

Host

Computer

Parallel BUS

XTLO

HDIS

HCS

HRD

HWT

HINT

HA0

HA1

HA2

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

RC224ATL

RC224ATLV

MODEM

TXAI

TXA2

RXA

RFILO

AGCIN

SPKR

SLEEP

IDLEN0

IDLEN1

A/A1

RING

TLKRELAY

OHRELAY

EmbeddedModem Family

Telephone

Line

Interface

Optional

Speaker

Amplifier

Sleep Mode

Interface

NVRCS

RESET

NVRSK

NVRDIO

Optional

NVRAM

2-2 Conexant D224ATLVDSC

RC224ATL/224ATLV

2.0 Hardware Interface

EmbeddedModem Family

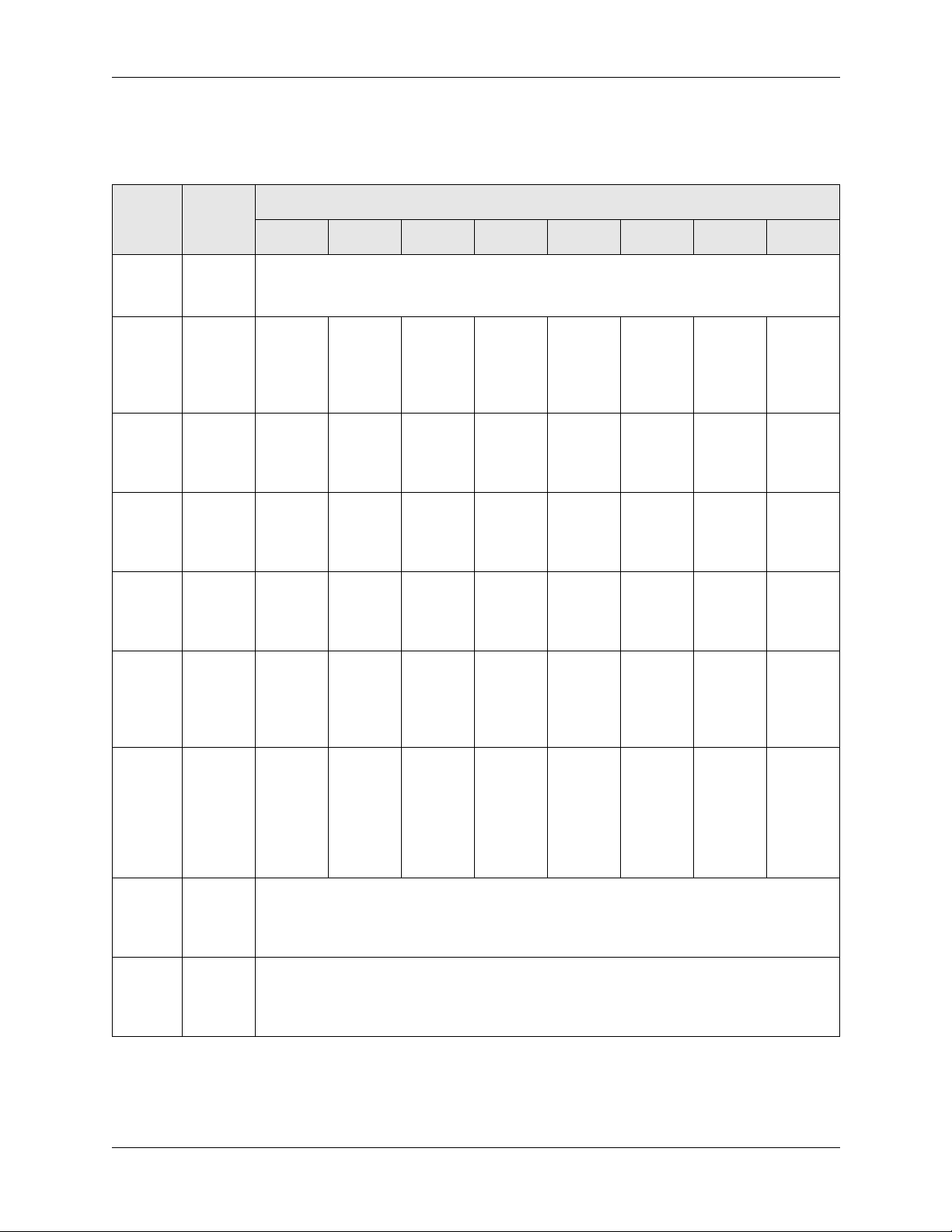

Figure 2-2. RC224ATLV Signals—Serial Interface

XTLI

Crystal

LED

Indicators

V. 24

EIA-232-D

Interface

XTLO

AAE

MR

DCDL

DTRL

RXD

CI/HS

DCD

DSR

RI

CTS

TXD

DTR

RC224ATL

RC224ATLV

MODEM

TXAI

TXA2

RXA

RFILO

AGCIN

SPKR

SLEEP

WAKEUP

IDLEN0

IDLEN1

A/A1

RING

TLKRELAY

OHRELAY

Telephone

Line

Interface

Optional

Speaker

Amplifier

Sleep Mode

Interface

+5 V

RESET

SEREN

NVRCS

NVRSK

NVRDIO

Optional

NVRAM

D224ATLVDSC Conexant 2-3

2.0 Hardware Interface

RC224ATL/224ATLV

The parallel interface registers are identified in Ta ble 2- 1.

Table 2-1. Parallel Interface Registers (1 of 2)

Register

Number

7 Scratch

6Modem

5Line Status

4Modem

Register

Name

Register

(SCR)

Status

Register

(MSR)

Register

(LSR)

Control

Register

(MCR)

7 6 5 4 3 2 1 0

Data

Carrier

Detect

(DCD)

Ring

Indicator

(RI)

0 Transmitter

Empty

(TEMT)

0 0 0 Local

Data Set

Ready

(DSR)

Transmitter

Holding

Register

(THRE)

Bit Number

Scratch Register

Clear to

Send (CTS)

Break

Interrupt

(BI)

Loopback

EmbeddedModem Family

Delta Data

Carrier

Detect

(DDCD)

Framing

Error (FE)

Out 2 Out 1 Request to

Trailing

Edge of

Ring

Indicator

(TERI)

Parity Error

(PE)

Delta Data

Set Ready

(DDSR)

Overrun

Error (OE)

Send (RTS)

Delta Clear

to Send

(DCTS)

Data Ready

(DR)

Data

Terminal

Ready

(DTR)

3Line

Control

Register

(LCR)

2 Interrupt

Identify

Register

(IIR) (Read

Only)

1

Interrupt

DLAB = 0

DLAB = 0

DLAB = 0

0

0

Enable

Register

(IER)

Transmitter

Holding

Register

(THR)

Receiver

Buffer

Register

(RBR)

Divisor

Latch

Access Bit

(DLAB)

Set Break

(SB)

0 0 0 0 0 Pending

0000Enable

Stick Parity

(SP)

Even Parity

Select

(EPS)

Transmitter Holding Register (Write Only)

Receiver Buffer Register (Read Only)

Parity

Enable

(PEN)

Modem

Status

Interrupt

(EDSSI)

Number of

Stop Bits

(STB)

Interrupt ID

Bit 1

(PL1)

Enable

Receiver

Line Status

Interrupt

(ELSI)

Word

Length

Select Bit 1

(WLS1)

Pending

Interrupt ID

Bit 0

(PL0)

Enable

Transmitter

Holding

Register

Empty

Interrupt

(ETBEI)

Word

Length

Select Bit 0

(WLS0)

0 if

Interrupt

Pending

(IP)

Enable

Received

Data

Available

Interrupt

(ERBFI)

2-4 Conexant D224ATLVDSC

RC224ATL/224ATLV

2.0 Hardware Interface

EmbeddedModem Family

Table 2-1. Parallel Interface Registers (2 of 2)

Register

Number

1

DLAB = 1

0

DLAB = 1

Register

Name

Divisor

Latch MSB

Register

(DLM)

Divisor

Latch LSB

Register

(DLL)

7 6 5 4 3 2 1 0

Bit Number

Divisor Latch (MS)

Divisor Latch (LS)

D224ATLVDSC Conexant 2-5

2.0 Hardware Interface

RC224ATL/224ATLV

2.1 Hardware Interface

EmbeddedModem Family

2.1 Hardware Interface

2.1.1 Parallel Interface

A 16450 UART-compatible parallel interface is provided.

Host Bus Interface

Interrupt Enable Register

(Addr=1, DLAB=0)

7 6 5 4 3 2 1 0

0 0 0 0 EDSSI ELSI ETBEI ERBFI

Eight data lines, three address lines, and four control lines are supported.

The Interrupt Enable Register (IER) enables four types of interrupts that can

separately assert the HINT output. A selected interrupt can be enabled by setting

the corresponding enable bit to a logic 1, or disabled by resetting the

corresponding enable bit to a logic 0. All interrupt sources are disabled by setting

bits 0–3 to a logic 0. Disabling all interrupts inhibits the Interrupt Identifier

Register (IIR) and inhibits assertion of the HINT output. All other system

functions operate normally, including the setting of the Line Status Register

(LSR) and the Modem Status Register (MSR).

Bits 4-7:

EDSSI Enable Modem Status Interrupt.

ELSI Enable Receiver Line Status Interrupt.

ETBEI Enable Transmitter Holding Register Empty Interrupt.

ERBFI Enable Received Data Available Interrupt.

Not used (always logic 0).

When this bit is a logic 1,

it enables assertion of the HINT output whenever bit 0, 1, 2, or

3 in the Modem Status Register (MSR) is a logic 1. When this

bit is a logic 0, it disables assertion of HINT due to setting of

any of these four MSR bits.

When this bit is a

logic 1, it enables assertion of the HINT output when any

receiver status bit in the Line Status Register (LSR); i.e., bits

1, 2, 3, or 4, changes state. When this bit is a logic 0, it

disables assertion of HINT due to change of the receiver LSR

bits.

When this bit is a logic 1, it enables assertion of the HINT

output when the Transmitter Holding Register Empty (THRE)

bit in the Line Status Register (LSR5) is set to a logic 1. When

this bit is a logic 0, it disables assertion of HINT due to LSR5.

When this bit is

a logic 1, it enables assertion of the HINT output when

received data is available in the Receiver Buffer; i. e., the Data

Ready bit in the Line Status Register (LSR0) is a logic 1.

When this bit is a logic 0, it disables assertion of HINT due to

the LSR0.

2-6 Conexant D224ATLVDSC

RC224ATL/224ATLV

2.0 Hardware Interface

EmbeddedModem Family

Interrupt Identifier

Register (Addr = 2)

The Interrupt Identifier Register (IIR) identifies the existence and type of

prioritized pending interrupts. Four priority levels are set to assist interrupt

2.1 Hardware Interface

processing in the host.

When addressed during chip-select time, the IIR freezes the highest priority

interrupt pending and acknowledges no other interrupts until the particular

interrupt is serviced by the host.

7 6 5 4 3 2 1 0

00000PL1PL0IP

Bits 3-7:

PL0-1 Highest Priority Pending Interrupt.

Not used (always 0).

These two bits identify

the highest priority pending interrupt.

Priority

2 1 Level Pending Interrupt

1 1 (highest) Receiver Line Status

1 0 2 Receiver Buffer Full

0 1 3 Transmitter Holding Register

Empty

0 0 4 Modem Status

IP Interrupt Pending

pending. When this bit is a logic 1, no interrupt is pending.

This bit can be used in a hardwired prioritized or polled

environment to indicate whether an interrupt is pending. If an

interrupt is pending, the IIR contents can be used as a pointer

to the appropriate interrupt service routine in the host.

. When this bit is a logic 0, an interrupt is

D224ATLVDSC Conexant 2-7

2.0 Hardware Interface

RC224ATL/224ATLV

2.1 Hardware Interface

Line Control Register

(Addr = 3)

7 6 5 4 3 2 1 0

DLAB SB SP EPS PEN STB WLS1 WLS0

The Line Control Register (LCR) specifies the format of the asynchronous data

communications exchange.

DLAB Divisor Latch Access Bit

. This bit must be set to a logic 1 to

EmbeddedModem Family

access the Divisor latches of the baud generator during a read

or write operation. It must be reset to a logic 0 to access the

Receiver Buffer, the Transmitter Holding Register, or the

Interrupt Enable Register.

SB Set Break

. When this bit is set to a logic 1, the transmit data is

forced to the space (logic 0) state. The break is disabled by

setting this bit to a logic 0. The Set Break bit acts only on the

transmit data and has no effect on the serial in logic.

SP Stick Parity

. When stick parity is selected (LCR5 = 1), parity

is enabled (LCR3 = 1), and even parity is selected (LCR4 = 1),

the parity bit is transmitted and checked by the receiver as a

logic 0. When stick parity is selected (LCR5 = 1), parity is

enabled (LCR3 = 1), and odd parity is selected (LCR4 = 0),

the parity bit is transmitted and checked by the receiver as a

logic 1.

EPS Even Parity Select

. When parity is enabled (LCR3 = 1), and

Stick Parity (LCR5) is a logic 0, the number of logic 1s

transmitted or checked in the data word bits and parity bit is

either even (LCR4 = 1) or odd (LCR4 = 0).

PEN Parity Enable

. When bit 3 is a logic 1, a parity bit is

generated in the serial out (transmit) data stream and checked

in the serial in (receive) data stream. The parity bit is located

between the last data bit and the first stop bit.

STB Number of Stop Bits

bits in each serial out character. If bit 2 is a logic 0, one stop

bit is generated regardless of word length. If bit 2 is a logic 1

when either a 5-, 6-, 7-, or 8-bit word length is selected, two

stop bits are generated. The serial in logic checks the f irst stop

bit only regardless of the number of stop bits selected.

WLS0 and WLS1 Word Length Select

bits in each serial in or serial out character. The encoding of

bits 0 and 1 is:

Bit 1 Bit 0 Word Length

0 0 5 Bits

0 1 6 Bits

1 0 7 Bits

1 1 8 Bits

. This bit specifies the number of stop

. These two bits specify the number of

2-8 Conexant D224ATLVDSC

RC224ATL/224ATLV

2.0 Hardware Interface

EmbeddedModem Family

Modem Control Register

(Addr = 4)

7 6 5 4 3 2 1 0

0 0 0 LL OUT2 OUT1 RTS DTR

The Modem Control Register (MCR) controls the interface with the modem or

data set.

Bit 5-7:

LL Local Loopback

Not used (always 0).

. When this bit is set to a logic 1, the

2.1 Hardware Interface

diagnostic mode is selected and the following occurs:

1.

Data written to the Transmit Holding Register will be

looped back to the Receiver Buffer Register.

2.

The four modem control bits (CTS, DSR, RI, and DCD)

are internally connected to the four modem control

outputs (RTS, DTR, OUT1, and OUT2), respectively.

OUT2 Output 2

. When this bit is a logic 1, HINT is enabled. When

this bit is a logic 0, HINT is in the high impedance state.

OUT1 Output 1

. This bit is used in local loopback (see MCR4).

RTS Request to Send

. This bit controls the Request to Send (RTS)

function. When this bit is a logic 1, RTS is on. When this bit is

a logic 0, RTS is off.

DTR Data Terminal Ready

Ready (DTR) function. When this bit is a logic 1, DTR is on.

When this bit is a logic 0, DTR is off.

. This bit controls the Data Terminal

D224ATLVDSC Conexant 2-9

2.0 Hardware Interface

RC224ATL/224ATLV

2.1 Hardware Interface

Line Status Register

(Addr = 5)

7 6 5 4 3 2 1 0

0TEMTTHREBI FE PE OE DR

The LSR, an 8-bit register, provides status information to the host concerning data

transfer.

Bit 7:

This bit is set to logic 0.

TEMT Transmitter Empty

. This bit is set to a logic 1 whenever the

EmbeddedModem Family

Transmitter Holding Register (THR) and the Transmitter Shift

Register (TSR) are both empty. It is reset to a logic 0 whenever

either the THR or TSR contains a data character.

THRE Transmitter Holding Register Empty

. This bit indicates that

the modem is ready to accept a new character for

transmission. In addition, this bit causes the modem to issue

an interrupt to the host when the Transmit Holding Register

Empty Interrupt Enable bit (IIR1) is set to logic 1. The THRE

bit is set to a logic 1 when a character is transferred from the

Transmitter Holding Register into the Transmitter Shift

Register. The bit is reset to logic 0 concurrently with the

loading of the Transmitter Holding Register by the host.

BI Break Interrupt

received data input is a space (logic 0) for longer than two full

word lengths plus 3 bits. The 81 indicator is reset whenever

the host reads the LSR.

FE Framing Error

did not have a valid stop bit. Bit 3 is set to a logic 1 whenever

the stop bit following the last data bit or parity bit is detected

as a zero bit. The FE bit is reset to a logic 0 whenever the host

reads the LSR.

PE Parity Error

. This bit indicates that the received data

character does not have the correct even or odd parity, as

selected by the Even Panty Select bit (LCR4) and the Stick

Parity bit (LCR5). The PE bit is set to a logic 1 upon detection

of parity error and is reset to a logic 0 whenever the host reads

the LSR.

OE Overrun Error

Buffer Register was not read by the host before the next

character was transferred into the Receiver Buffer Register,

thereby destroying the previous character. The OE bit is reset

whenever the host reads the LSR.

DR Data Ready

. This bit is set to a logic 1 whenever a complete

incoming character has been received and transferred into the

Receiver Buffer Register. Bit 0 is reset to a logic 0 when the

host reads the Receiver Buffer Register.

. This bit is set to a logic 1 whenever the

. This bit indicates that the received character

. This bit indicates that data in the Receiver

2-10 Conexant D224ATLVDSC

RC224ATL/224ATLV

2.0 Hardware Interface

EmbeddedModem Family

Modem Status Register

(Addr = 6)

The Modem Status Register (MSR) reports the modem’s current state and change

information. Bits 4-7 supply current state, and bits 0-3 supply change

2.1 Hardware Interface

information. The change bits are set to a logic 1 whenever a control input from the

modem changes state from the last MSR read by the host. Bits 0-3 are reset to

logic 0 when the host reads the MSR or upon reset.

Whenever Bits 0,1, 2, or 3 are set to a logic 1, a Modem Status Interrupt is

generated.

7 6 5 4 3 2 1 0

DCD RI DSR CTS DDCD TERI DDSR DCTS

DCD Data Carrier Detect

. This bit indicates the logic state of the

DCD output. If Loopback is selected (MCR4 = 1), this bit

reflects the state of OUT2 in the MCR (MCR3).

RI Ring Indicator

. This bit indicates the logic state of the RI

output. If Loopback is selected (MCR4 = 1), this bit reflects

the state of OUT1 in the MCR (MCR2).

DSR Data Set Ready

. This bit indicates the logic state of the DSR

output. If Loopback is selected (MCR4 = 1), this bit reflects

the state of DTR in the MCR (MCR0).

Receiver Buffer Register

(Addr=0, DLAB=0)

Transmitter Holding

Register (Addr=0,

DLAB=0)

CTS Clear to Send

. This bit indicates the logic state of the CTS

output. If Loopback is selected (MCR4 = 1), this bit reflects

the state of RTS in the MCR (MCR1).

DDCD Delta Data Carrier Detect

. This bit is set to a logic 1 when

the DCD bit has changed since the MSR was last read by the

host.

TERI Trailing Edge of Ring Indicator

. This bit is set to a logic 1

when the RI bit changes from a 1 to a 0 state since the MSR

was last read by the host.

DDSR Delta Data Set Ready

. This bit is set to a logic I when the

DSR bit has changed state since the MSR was last read by the

host.

DCTS Delta Clear to Send

. This bit is set to a logic 1 when the CTS

bit has changed state since the MSR was last read by the host.

The Receiver Buffer Register (RBR) is a read-only register at location 0 (with

DLAB = 0). Bit 0 is the least significant bit of the data, and is the first bit

received.

The Transmitter Holding Register (THR) is a write-only register at address 0

when DLAB = 0. Bit 0 is the least significant bit and the first bit sent.

D224ATLVDSC Conexant 2-11

2.0 Hardware Interface

RC224ATL/224ATLV

2.2 Additional Information

Divisor Registers

(Addr=0 and 1, DLAB=1)

Scratch Register (SCR)

(Addr = 7)

EmbeddedModem Family

The Divisor Latch LS Byte and Divisor Latch MS Byte are two read-write

registers at locations 0 and 1 when DLAB = 1, respectively.

The baud rate is selected by loading each divisor latch with the appropriate

hex value. Ta bl e 2 -2 lists the programmable values corresponding to the desired

baud rate.

Table 2-2. Programmable Baud Rates

Divisor Latch (Hex)

MS LS

01

00

00

00

80

C0

60

30

Divisor

(Decimal)

384

192

96

48

Baud Rate

300

600

1200

2400

The Scratchpad Register is a read-write register at location 7. This register is not

used by the DSP and can be used by the host for temporary storage.

2.1.2 Serial/Indicator Interface

A DTE serial interface and indicator outputs are supported.

• Serial Interface: An 8-line V.24/EIA-232-D or TTL logic serial interface to

the DTE is supported.

• LED Indicator Interface: Four direct connect LED indicator outputs are

supported.

2.1.3 Speaker Interface

A speaker output, controlled by AT or V.25 bis commands, is provided for an

optional OEM-supplied speaker circuit.

2.1.4 Line Interface

The EmbeddedModem connects to the line interface circuitry by means of a

receive analog input, two transmit analog outputs, and a ring signal input.

The EmbeddedModem provides three relay control outputs to the line

interface. These outputs may be used to control relays such as off-hook, A/A1

and talk/data.

,

2.2 Additional Information

Additional information is provided in the RC224ATLV

(Order No. 821).

2-12 Conexant D224ATLVDSC

Modem Designer’s Guide

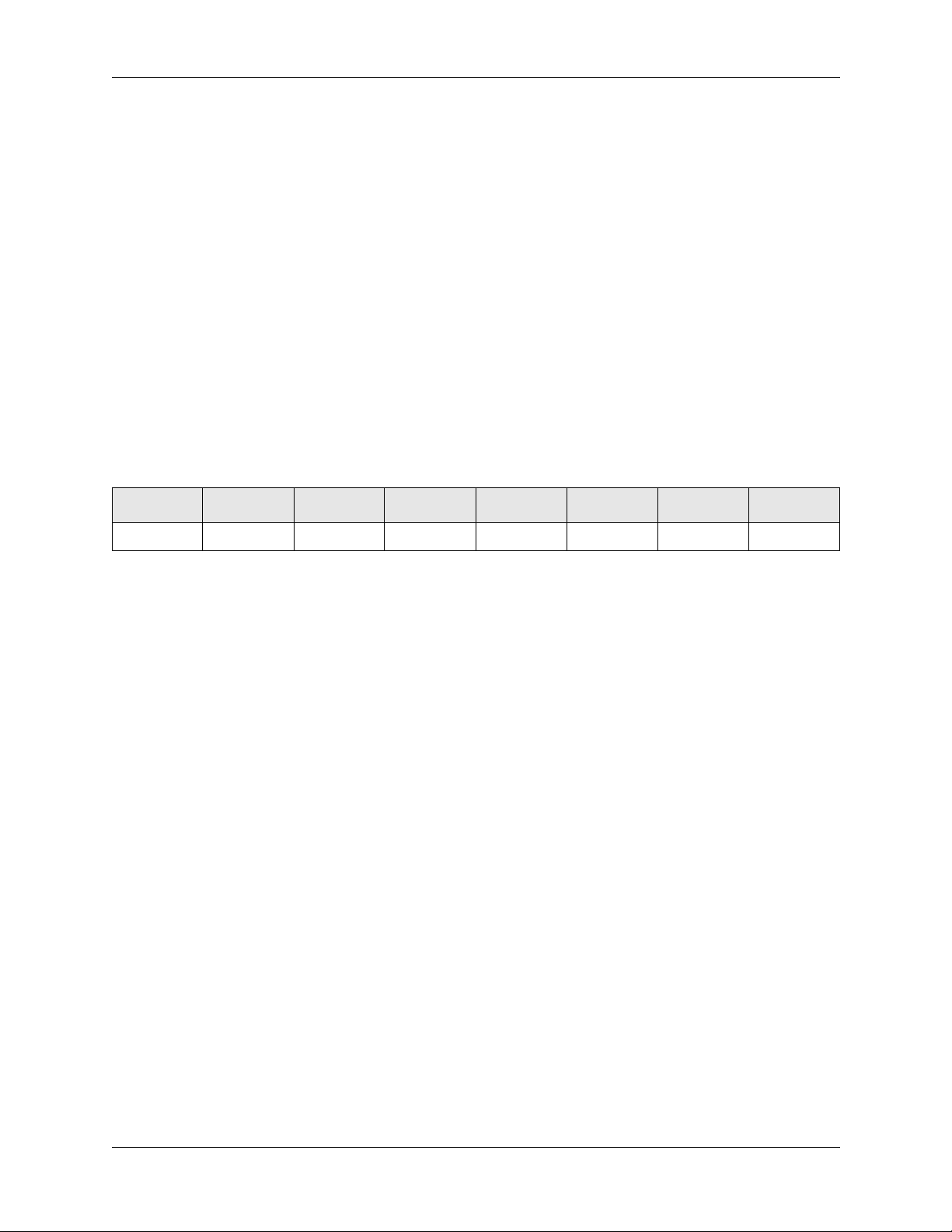

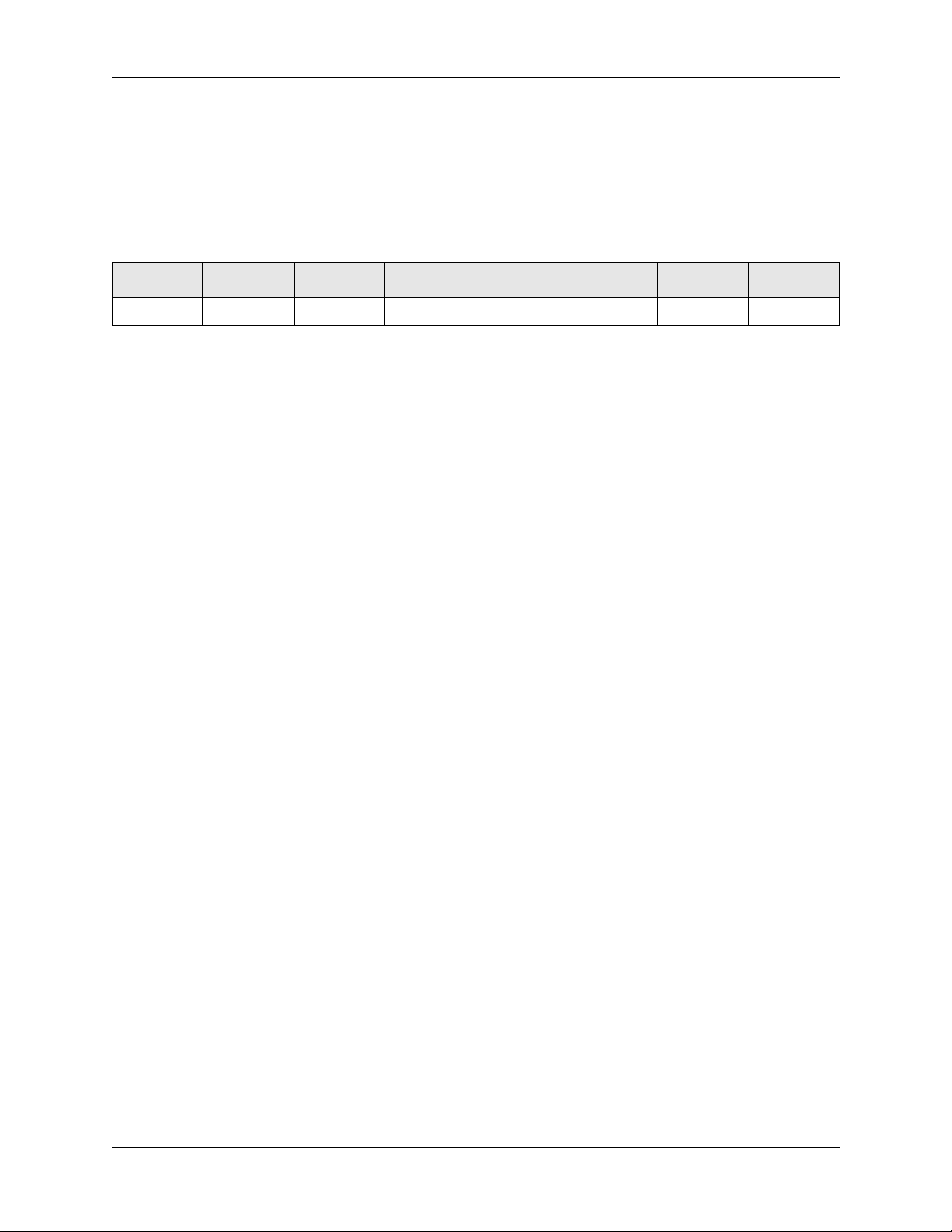

3.0 Pin Descriptions

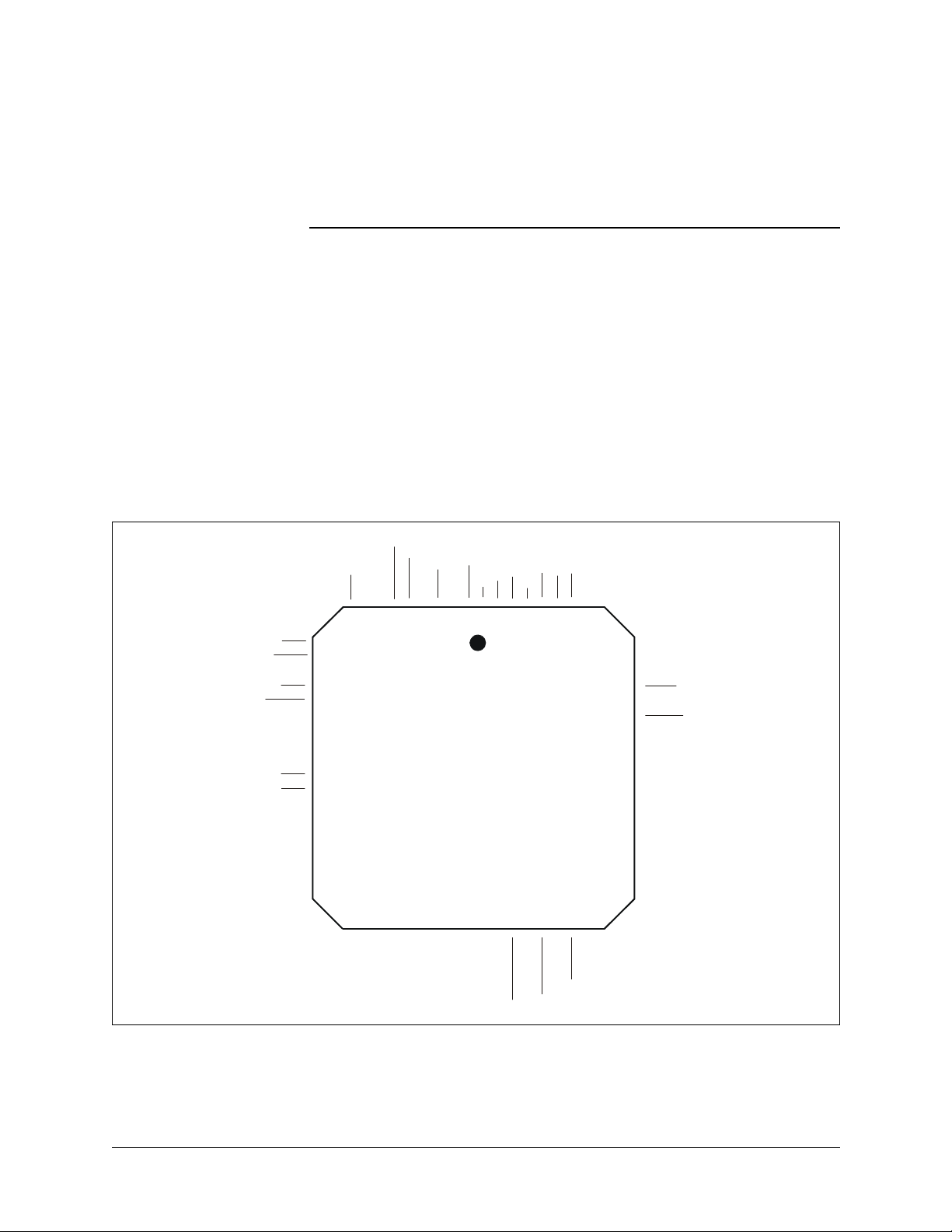

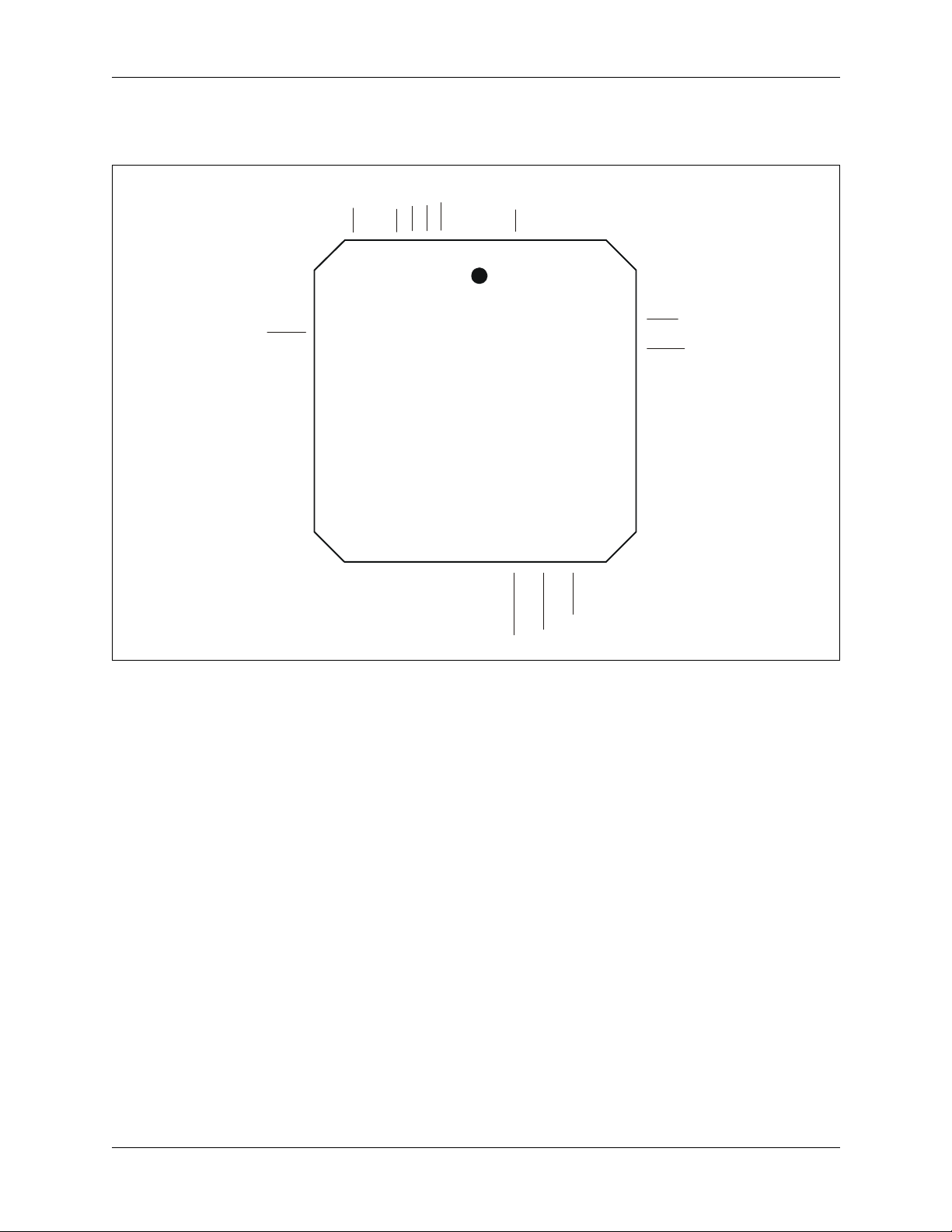

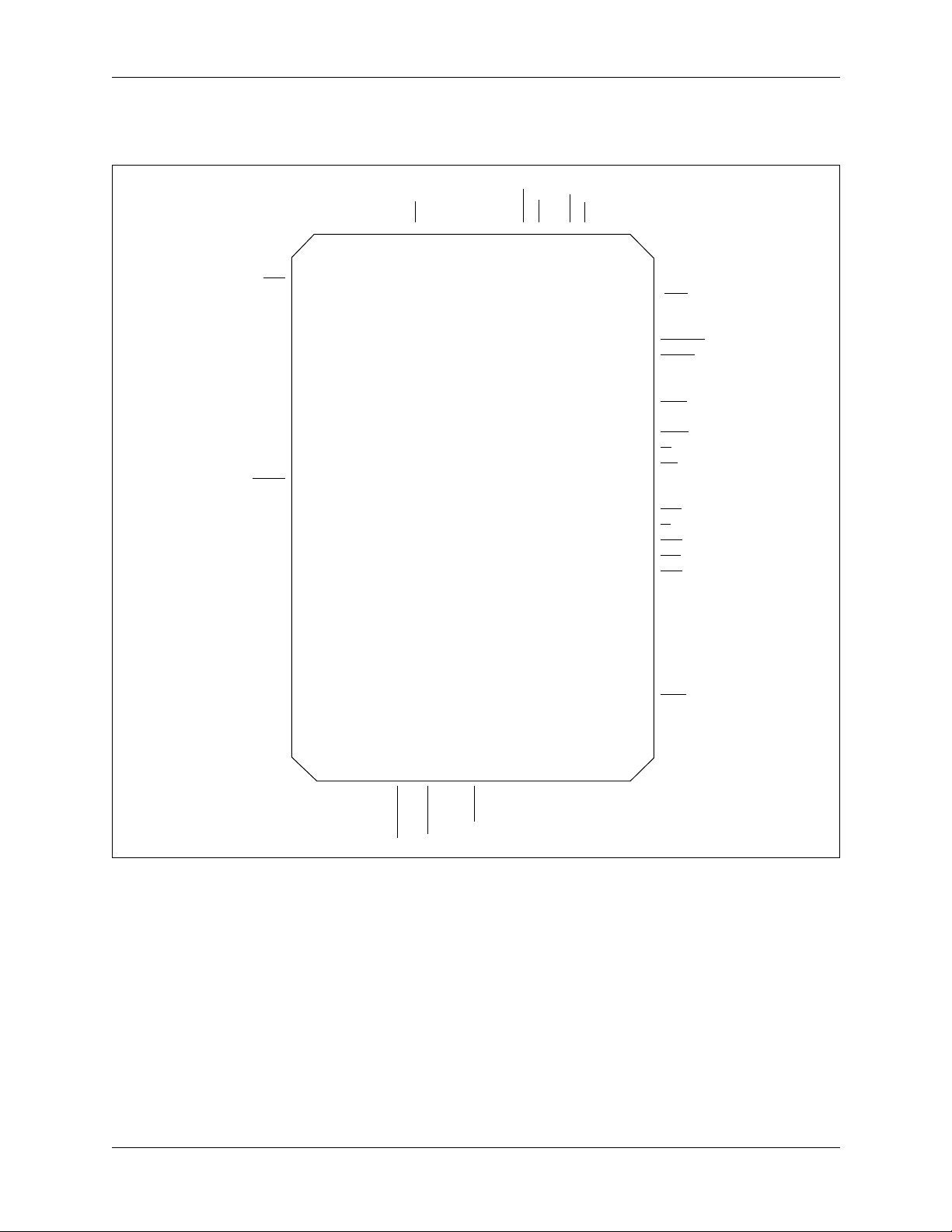

The RC224ATLV 68-pin PLCC serial and parallel pinouts are displayed in

Figure 3-1 and Figure 3-2, respectively. The 100-pin PQFP serial and parallel

pinout diagrams are displayed in Figure 3-3 and Figure 3-4, respectively.

Figure 3-5 displays NVRAM timing.

RC224ATLV 68-pin PLCC serial and parallel pin assignments are displayed in

Ta bl e 3 - 1 and Ta ble 3- 2, respectively. The 100-pin serial and parallel pin

assignments are displayed in Ta bl e 3 -3 and Table 3-4 , respectively.

Figure 3-1. 68-Pin PLCC Package—Serial

AAE

NC

RXD

VCC

NC

NC

TXD

DTR

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

DTRL

RESET

NVRSK

IDLEN1

RAGCO

RADCI

TSTBO

RSTBO

RRSTO

A/A1

NVRDIO

NVRCS

WAKEUP

SEREN

NC

RING

IDLEN0

9 8 7 6 5 4 3 2 1

3

DCDL

RI

68

MR

67

NMI

66

CI/HS

65

DCD

CTS

64

63

DSR

62

DGND2

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

DGND1

XTLO

XTLI

TEST

φ

2

SLEEP

SPKR

VAA

MODEI

TSTBI

TRSTI

TDACI

RADCO

RRSTI

NC

RSTBI

NC

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

TRSTO

NC

TXA1

TXA2

TDACO

MODEO

RXA

RFILO

AGCIN

VC

NC

NC

AGND

TLKRELAY

RAGCI

SLEEPI

OHRELAY

D224ATLVDSC Conexant 3-1

3.0 Pin Descriptions

RC224ATL/224ATLV

Figure 3-2. 68-Pin PLCC Package

HA1

HA0

IDLEN0

NVRSK

RESET

VCC

HINT

HDIS

NC

NVRDIO

NC

IDLEN1

RAGCO

RADCI

TSTBO

RSTBO

RRSTO

Parallel

—

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

A/A1

9

HA2

NVRCS

8 7 6

HCS

HWT

5 4 3

HRD

EmbeddedModem Family

RING

HD7

HD6

HD5

HD4

NMI

HD3

HD2

HD1

HD0

DGND2

1

2

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

DGND1

XTLO

XTLI

TEST

φ

2

SLEEP

SPKR

VAA

MODEI

TSTBI

TRSTI

TDACI

RADCO

RRSTI

NC

RSTBI

NC

27

TRSTO

28

MODEO

29

TDACO

30

NC

31

TXA2

32

TXA1

33

RXA

34

RFILO

35

36

37

VC

NC

AGCIN

38

TLKRELAY

39

AGND

40

OHRELAY

41

NC

42

SLEEPI

43

RAGCI

3-2 Conexant D224ATLVDSC

RC224ATL/224ATLV

3.0 Pin Descriptions

EmbeddedModem Family

Figure 3-3. 100-Pin PQFP Package

DTR

RADCI

NC

NC

NC

SLEEP

NC

DGND

VAA

SPKR

NC

AGND

TXA2

TXA1

NC

RXA

NC

RFILO

AGCIN

VC

AGND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

IDLEN1

RAGCO

TSTBO

RSTBO

RRSTO

TRSTO

MODEO

TDACO

MODEI

Serial

—

NCNCNC

DGNDNCNC

99989796959493929190898887868584838281

100

TXDNCNC

NVRSKNCVCC

VCC

RESET

RXDNCDTRL

AAENCDGND

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

DGND

)

(A/A1

NVRDIO

NVRCS

WAKEUP

SEREN

NC

NC

RING

IDLENO

DCDL

RI

MR

NC

DGND

NMI

CI/HS

DCD

CTS

DSR

NC

NC

DGND

DGND

NC

XTLO

XTLI

TEST

2

φ

NC

31323334353637383940414243444546474849

NC

NCNCNCNCNC

AGND

TLKRELAY

NC

AGND

RSTBI

TDACI

RRSTI

RAGCI

OHRELAY

SLEEPI

RADCO

TRSTI

50

NC

TSTBI

D224ATLVDSC Conexant 3-3

3.0 Pin Descriptions

RC224ATL/224ATLV

Figure 3-4. 100-Pin PQFP Package

NC

RADCI

NC

NC

NC

SLEEP

NC

DGND

VAA

SPKR

NC

AGND

TXA2

TXA1

NC

RXA

NC

RFILO

AGCIN

VC

AGND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

IDLEN1

RAGCO

TSTBO

RSTBO

RRSTO

TRSTO

MODEO

TDACO

MODEI

Parallel

—

NCNCNC

DGNDNCNC

99989796959493929190898887868584838281

100

NVRDIONCHDIS

HINTNCVCC

VCC

RESET

NVRSK

IDLENO

HA0

HA1NCDGND

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

EmbeddedModem Family

DGND

)

(A/A1

HA2

NVRCS

HCS

HWT

HRD

NC

RING

HD7

HD6

HD5

HD4

NC

DGND

NMI

HD3

HD2

HD1

HD0

NC

NC

DGND

DGND

NC

XTLO

XTLI

TEST

2

φ

NC

31323334353637383940414243444546474849

NC

NCNCNCNCNC

AGND

TLKRELAY

NC

AGND

RSTBI

TDACI

RRSTI

RAGCI

OHRELAY

SLEEPI

RADCO

50

NC

TSTBI

TRSTI

3-4 Conexant D224ATLVDSC

Loading...

Loading...