Page 1

A

1 1

B

C

D

E

Compal Confidential

2 2

DIS M/B Schematics Document

Haswell with DDRIII + Lynx Point PCH

MARS XT / SUN PRO

2013-04-18

3 3

LA-9641P

REV:1.0

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

C

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

LA-9641P

LA-9641P

LA-9641P

E

1 61Friday, April 19, 2013

1 61Friday, April 19, 2013

1 61Friday, April 19, 2013

1.0

of

of

of

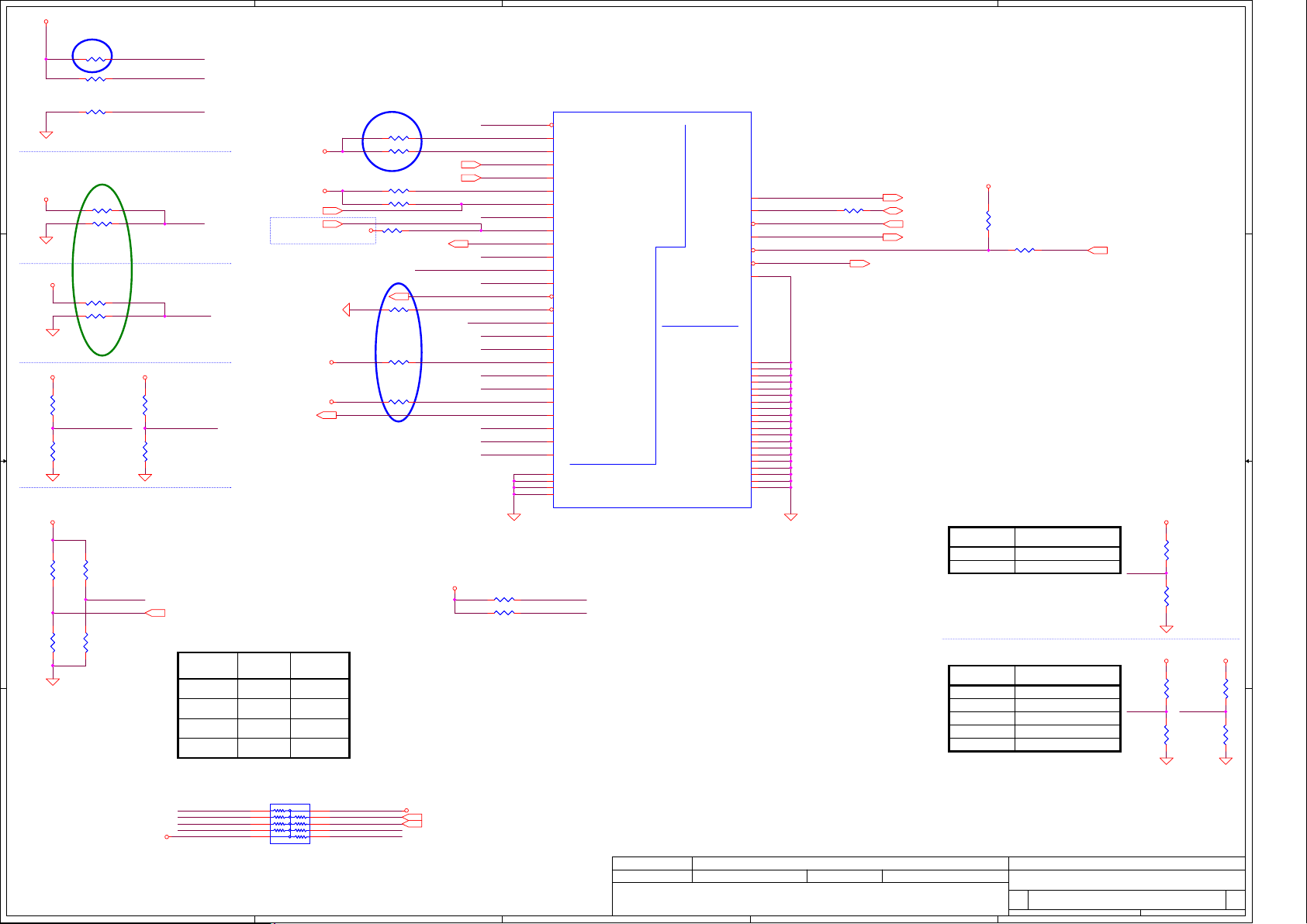

Page 2

A

Compal confidential

File Name :

B

C

D

E

1 1

2 2

RJ45 Conn.

3 3

Sub-borad

AMD MARS XT M2 128 bits

UN PRO M2 64 bits

/ S

VRAM 512MB/1GB/2GB

MARS XT : DDR3 x 8

SUN PRO : DDR3 x 4

LVDS Conn.

page 34

HDMI Conn.

page 36

CRT Conn.

page 35

LAN

Atheros

page 39

AR8162/QCA8172(10/100)

PCIe Mini Card

WLAN

PCIe Port 0

PCIe Mini Card

USB20 Port 10

page 23~32

LVD

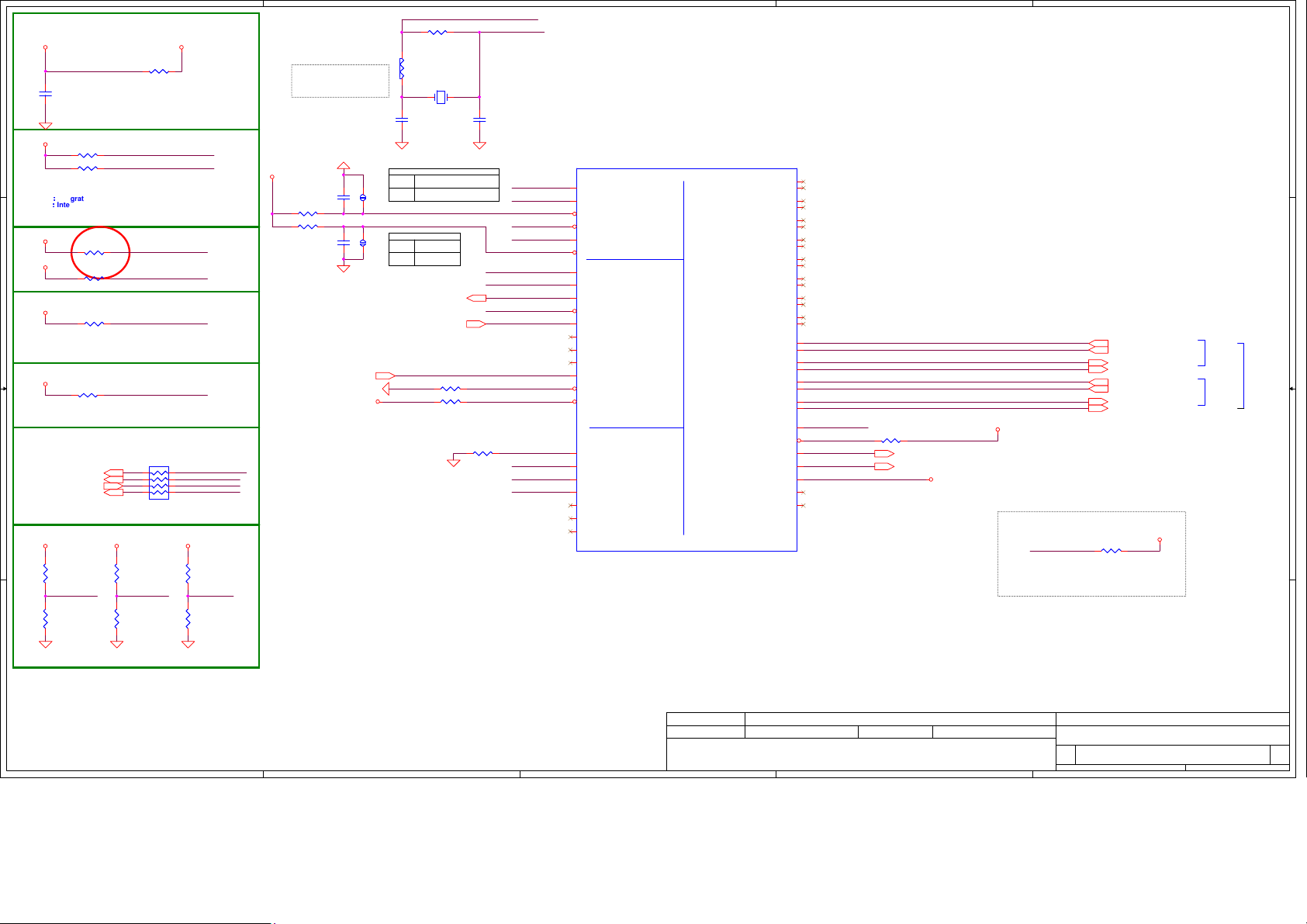

S Translator

RTD2132R(Single)

page 38

page 28

page 28

PEG 8x

Gen2 / Gen3

page 33

PCIe x1

Ie x1

PC

USB20 x1

FDI *2

2.7GT/s

Intel

ocessor

Pr

Haswell

rPGA946

37.5mm x 37.5mm

page 5,~11

Intel

PCH

Lynx Point

FCBGA 695Balls

20mm x 20mm

Me

mory Bus

Dual Channel

DDR3L

DDR3L

DMI2 *4

5GT

/s

USB30 x2

USB20 x6

SATA Gen3

SATA

AZALIA

1600MHz

1333MHz

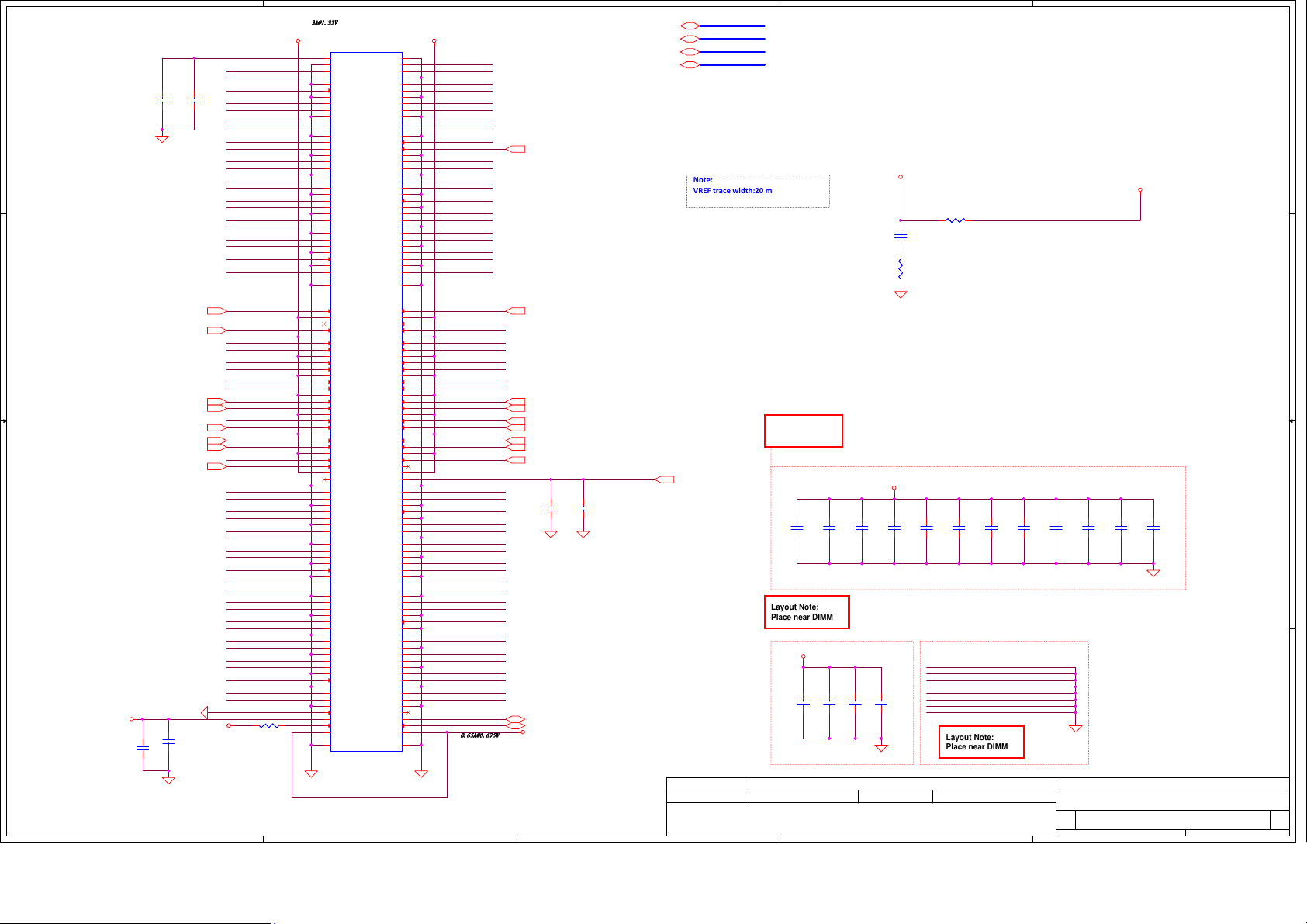

204pin DDRIII-SO-DIMM X2

Left USB3.0 x2

USB30 Port 0,1

page 46

Touch Screen

USB20 Port 2

HDD Conn.

SATA Port 4

page 41

ODD Conn.

SATA Port 5

Audio Codec

CONEXANT

CX20757

page 41

page 42

BANK 0, 1, 2

Right USB2.0

USB20 Port 9

Card Reader

Realtek RTS5170

USB20 Port 11

page 46

page 44

page 12,13

Int. Camera

USB20 Port 3

page 33

Shark Bay

Int. MIC Conn.

page 42

SPI ROM

2MB + 4MB

page 17

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

A

ODD/B

LSXXXP

LED/B

LSXXXP

page 44

CR/B

LSXXXP

page 44

page 44

B

15"

14"

Power/B

USB/B

LSXXXP

LSXXXP

page 44

page 44

4 4

EC

ENE KB9012

page 44

Thermal Sensor

C

page 40

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

Touch Pad

page 44

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Int. KBD

page 44

D

Int. Speaker Conn.

page 42

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Audio Combo Jacks

HP & MIC

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Block Diagram

Block Diagram

Block Diagram

LA-9641P

LA-9641P

LA-9641P

page 42

2 61Friday, April 19, 2013

2 61Friday, April 19, 2013

E

2 61Friday, April 19, 2013

1.0

Page 3

A

Voltage Rails

power

State

plane

+B

+5VALW

+3VALW

+1.35V

1 1

B

BOARD ID Table

Board ID

+5VS

+3VS

+VCC_CORE

+VGA_CORE

+1.5VS

+0.675VS

+1.05VS

0

1

2

3

4

5

6

7

C

PCB Revision

0.1

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SIGNAL

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

100K +/- 5%Ra/Rc/Re

Rb / Rd / Rf V min

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

D

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

HIGH HIGH HIGH HIGH

LOW

LOW

LOW

LOW LOW LOW LOW

HIGH

LOWLOWLOW

HIGHHIGHHIGH

HIGH

HIGH

ON

ON

ON

ON

ON

ON

ON

ON

OFF

OFF

E

ON ON

ON

OFF

OFF

OFF

Board ID / SKU ID Table for AD channel

AD_BID

0 V

V typ

AD_BID

V

AD_BID

0 V 0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

0.503 V

0.819 V

0.538 V

0.875 V

max

Porject Phase

G-series

G-series

G-series

G-series

LOW

OFF

OFF

OFF

MP

PVT

DVT

EVT

S0

S3

2 2

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

O

O

O

O

X

EC SM Bus1 address

Device

Smart Battery

0001 011X b

PCH SM Bus address

Device Address

3 3

DDR DIMM1 ChannelA

DDR DIMM2 ChannelB

0xA0

0xA4

O

O

O

X

O

X X

X

X X X

EC SM Bus2 address

Device

Thermal Sen sor

AMD-GPU SM Bus address

Device Address

Internal thermal sensor

Address

1001_100xb

1000_001xb

OO

USB Port Table

X

X

EHCI1

EHCI2

USB 2.0 Port

UHCI0

UHCI1

UHCI2

UHCI3

UHCI4

UHCI5

UHCI6

0

1

2

3

4

5

6

7

8

9

10

11

12

13

3 External

USB Port

Left USB3.0

Left USB3.0

Touch screen

Camera

Right USB2.0

WLAN

Card reader

BOM Structure Table

BTO Item BOM Structure

DIS PX@

MARS XT

SUN PRO

HDMI HDMI@

Deep S3

NO Deep S3 NODS3@

8162 LAN

8172 LAN

LAN LDO MODE

LAN SWR MODE

LAN Surge GAS@

USB30

Cameara CMOS@

LAN Switch mode SWR@

Touch screen TS@

Righ side USB RUSB@

MARS@

SUN@

DS3@

8162@

8172@

LDO@

SWR@

USB30@

Zero ODD circuit R_USB@ZODD@

Device Address

RTD2132R

1101 010Xb

Share ROM SROM@

Non-share ROM NOSROM@

14" 14@

15" 15@

45 LEVEL 45@

SMBUS Control Table

X

X

X

V

+3VS

SODIMM

SOURCE

SMB_EC_CK1

SMB_EC_DA1

SMB_EC_CK2

SMB_EC_DA2

4 4

SMBCLK

SMBDATA

SML0CLK

SML0DATA

SML1CLK

SML1DATA

KB9012

+3VALW

KB9012

+3VALW

PCH

+3VALW

PCH

+3VALW

PCH

+3VALW

VGA BATT KB9012

X V

X

X

X

V

+3VS

A

+3VALW

X

X

X

X

X

V

+3VS

X

WLAN

WWAN

X

XX

V

+3VS

X

B

Thermal

Sensor

X

X

X

XX

V

+3VS

PCH

X

V

+3VS

X

X

XX X

RTD2132

X

V

+3VS

X

X

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

V

+3VS

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

C

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

X76 LEVEL X76@

Unpop

@

AUDIO PART MIC@

Connector ME@

VRAM BOM STRUCTURE Refer P4. VGA NOTE

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

LA-9641P

LA-9641P

LA-9641P

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Notes List

Notes List

Notes List

E

3 61Friday, April 19, 2013

3 61Friday, April 19, 2013

3 61Friday, April 19, 2013

1.0

Page 4

5

4

3

2

1

Mars XT VRAM STRAP

Vendor

UV5, UV6, UV7, UV8

UV9, UV10, UV11, UV12

Samsung 2048Mbits

ZZZ4

SA000068U00

128Mx16 K4W2G1646E-BC1A

D D

2GBytes

1GBytes

2GBytes

C C

MS2G@

ZZZ5

MM2G@

ZZZ6

MH2G@

ZZZ7

MS1G@

ZZZ8

MH1G@

ZZZ15

MH2GN@

ZZZ4

ZZZ4

Samsung_2G

Samsung_2G

MS2G@

MS2G@

X7646738L01

X7646738L01

Micron 2048Mbits

SA000067500

128Mx16 MT41J128M16JT-093G:K

Hynix 2048Mbits

SA000065300

H5TQ2G63DFR-N0C

Samsung 1028Mbits

SA00004GS00

64Mx16 K4W1G1646G-BC11

Hynix 1024Mbits

SA

000041SB0

64Mx16 H5TQ1G63EFR-11C

ynix 2048Mbits

H

SA

00006H400

128Mx16 H5TC2G63FFR-11C

2GBytes 1GBytes

ZZZ6

ZZZ5

ZZZ5

Micron_2G

Micron_2G

MM2G@

MM2G@

X7646738L02

X7646738L02

ZZZ6

Hynix_2G

Hynix_2G

MH2G@

MH2G@

X7646738L09

X7646738L09

0 0

0 1 1

ZZZ15

ZZZ15

Hynix_2G

Hynix_2G

MH2GN@

MH2GN@

X7646738L10

X7646738L10

PS_3[ 1 ]PS_3[ 2 ]PS_3[ 3 ]

0

10 0

00 1

1 1 4.75K NC1

01 0 4.99K4.53K

ZZZ7

ZZZ7

Samsung_1G

Samsung_1G

MS1G@

MS1G@

X7646738L03

X7646738L03

X76@X76@

R_pu R_pd

RV20 RV27

NC 4.75K

8.45K 2K

4.53K 2K

6.98K 4.99K

ZZZ8

ZZZ8

Hynix_1G

Hynix_1G

MH1G@

MH1G@

X7646738L04

X7646738L04

Power-Up/Down Sequence

"Mars" has the following requirements with regards to power-supply

sequencing to avoid damaging the ASIC:

All the ASIC supplies must reach their respective nominal voltages within 20 ms

‧

of the start of the ramp-up sequence, though a shorter ramp-up duration is

preferred. The maximum slew rate on all rails is 50 mV/µs.

The external pull ups on the DDC/AUX signals (if applicable) should ramp up

‧

before or after both VDDC and VDD_CT have ramped up.

VDDC and VDD_CT should not ramp up simultaneously. For example, VDDC

‧

should reach 90% before VDD_CT starts to ramp up (or vice versa).

For power down, reversing the ramp-up sequence is recommended.

‧

VDDR3(3.3VGS)

PCIE_VDDC(0.95VGSV)

VDDR1(1.5VGS)

VDDC/VDDCI(1.12V)

VDD_CT(1.8V)

PERSTb

REFCLK

Sun PRO VRAM STRAP

Vendor

UV9, UV10, UV11, UV12

Samsung 4096Mbits

ZZZ9

SA000068R00

256Mx16 K4W4G1646B-HC11

SS2G@

B B

2GBytes

1GBytes

1GBytes

Micron 4096Mbits

ZZZ10

SA000065D00

256Mx16/1866 MT41K256M16HA-107G:E

SM2G@

Hynix 4096Mbits

ZZZ11

SA00006DG00

256MX16 H5TQ4G63MFR-11C

SH2G@

Samsung 2048Mbits

ZZZ12

SA000068U00

128Mx16 K4W2G1646E-BC1A

SS1G@

ZZZ13

SM1G@

ZZZ14

SH1G@

ZZZ16

SH1GN@

icron 2048Mbits

M

SA000067500

128Mx16 MT41J128M16JT-093G:K

Hynix 2048Mbits

SA000065300

H5TQ2G63DFR-N0C

Hynix 2048Mbits

SA

00006H400

H5TC2G63FFR-11C

0 0

0 1 1

1

1 0 0 4.53K 4.99K

PS_3[ 1 ]PS_3[ 2 ]PS_3[ 3 ]

1 0

1 11

0

10 0

00 1

R_pu R_pd

RV20 RV27

NC 4.75K

8.45K 2K

4.53K 2K

6.98K 4.99K

3.4K 10K

4.75K NC

X76@X76@

Straps Reset

Straps Valid

Global ASIC Reset

T4+16clock

A A

ZZZ9

ZZZ9

Samsung_2G

Samsung_2G

SS2G@

SS2G@

X7646738L05

X7646738L05

2GBytes 1GBytes

ZZZ10

ZZZ10

Micron_2G

Micron_2G

SM2G@

SM2G@

X7646738L06

X7646738L06

ZZZ11

ZZZ11

Hynix_2G

Hynix_2G

SH2G@

SH2G@

X7646738L11

X7646738L11

5

ZZZ12

ZZZ12

Samsung_1G

Samsung_1G

SS1G@

SS1G@

X7646738L07

X7646738L07

ZZZ13

ZZZ13

Micron_1G

Micron_1G

SM1G@

SM1G@

X7646738L08

X7646738L08

4

ZZZ14

ZZZ14

Hynix_1G

Hynix_1G

SH1G@

SH1G@

X7647538L01

X7647538L01

ZZZ16

ZZZ16

Hynix_1G

Hynix_1G

SH1GN@

SH1GN@

X7646738L13

X7646738L13

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Compal Electronics, Inc.

VGA Notes List

VGA Notes List

VGA Notes List

LA-9641P

LA-9641P

LA-9641P

4 61Friday, April 19, 2013

4 61Friday, April 19, 2013

4 61Friday, April 19, 2013

1

1.0

Page 5

5

ZZZ2

15@ZZZ2

ZZZ1

14@ZZZ1

14@

14" PCB LA9641

14" PCB LA9641

DA6000WQ000

DA6000WQ000

D D

C C

B B

FDI_CSYNC<15>

FDI_INT<15>

Note:

Trace width=4 mils ,Spacing=5mil

Max length= 10000 mils.

15@

15" PCB LA9641

15" PCB LA9641

DA6000WQ100

DA6000WQ100

DMI_CRX_PTX_N0<15>

DMI_CRX_PTX_N1<15>

DMI_CRX_PTX_N2<15>

DMI_CRX_PTX_N3<15>

DMI_CRX_PTX_P0<15>

DMI_CRX_PTX_P1<15>

DMI_CRX_PTX_P2<15>

DMI_CRX_PTX_P3<15>

DMI_CTX_PRX_N0<15>

DMI_CTX_PRX_N1<15>

DMI_CTX_PRX_N2<15>

DMI_CTX_PRX_N3<15>

DMI_CTX_PRX_P0<15>

DMI_CTX_PRX_P1<15>

DMI_CTX_PRX_P2<15>

DMI_CTX_PRX_P3<15>

4

DMI_CRX_PTX_N0

DMI_CRX_PTX_N1

DMI_CRX_PTX_N2

DMI_CRX_PTX_N3

DMI_CRX_PTX_P0

DMI_CRX_PTX_P1

DMI_CRX_PTX_P2

DMI_CRX_PTX_P3

DMI_CTX_PRX_N0

DMI_CTX_PRX_N1

DMI_CTX_PRX_N2

DMI_CTX_PRX_N3

DMI_CTX_PRX_P0

DMI_CTX_PRX_P1

DMI_CTX_PRX_P2

DMI_CTX_PRX_P3

D21

C21

B21

A21

D20

C20

B20

A20

D18

C17

B17

A17

D17

C18

B18

A18

H29

J29

Haswell rPGA EDS

Haswell rPGA EDS

JCPU1A

JCPU1A

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

FDI_CSYNC

DISP_INT

INT

INT

EL_HASWELL_HASWELL

EL_HASWELL_HASWELL

ME@

ME@

3

+VCOMP_OUT

PEG_RCOMP

Note:

Trace width=12 mils ,Spacing=15mils

Max length= 400 mils.

E23

PEG_RCO MP

PEG_RXN _0

PEG_RXN _1

PEG_RXN _2

PEG_RXN _3

PEG_RXN _4

PEG_RXN _5

PEG_RXN _6

PEG

PEG

PEG_RXN _7

DMI FDI

DMI FDI

PEG_RXN _8

PEG_RXN _9

PEG_RXN _10

PEG_RXN _11

PEG_RXN _12

PEG_RXN _13

PEG_RXN _14

PEG_RXN _15

PEG_RXP _0

PEG_RXP _1

PEG_RXP _2

PEG_RXP _3

PEG_RXP _4

PEG_RXP _5

PEG_RXP _6

PEG_RXP _7

PEG_RXP _8

PEG_RXP _9

PEG_RXP _10

PEG_RXP _11

PEG_RXP _12

PEG_RXP _13

PEG_RXP _14

PEG_RXP _15

PEG_TXN _0

PEG_TXN _1

PEG_TXN _2

PEG_TXN _3

PEG_TXN _4

PEG_TXN _5

PEG_TXN _6

PEG_TXN _7

PEG_TXN _8

PEG_TXN _9

PEG_TXN _10

PEG_TXN _11

PEG_TXN _12

PEG_TXN _13

PEG_TXN _14

PEG_TXN _15

PEG_TXP _0

PEG_TXP _1

PEG_TXP _2

PEG_TXP _3

PEG_TXP _4

PEG_TXP _5

PEG_TXP _6

PEG_TXP _7

PEG_TXP _8

PEG_TXP _9

PEG_TXP _10

PEG_TXP _11

PEG_TXP _12

PEG_TXP _13

PEG_TXP _14

PEG_TXP _15

1 OF 9

1 OF 9

PEG_RCOMP

M29

K28

M31

L30

M33

L32

M35

L34

E29

PCIE_CRX_GTX_N7

D28

PCIE_CRX_GTX_N6

E31

PCIE_CRX_GTX_N5

D30

PCIE_CRX_GTX_N4

E35

PCIE_CRX_GTX_N3

D34

PCIE_CRX_GTX_N2

E33

PCIE_CRX_GTX_N1

E32

PCIE_CRX_GTX_N0

L29

L28

L31

K30

L33

K32

L35

K34

F29

PCIE_CRX_GTX_P7

E28

PCIE_CRX_GTX_P6

F31

PCIE_CRX_GTX_P5

E30

PCIE_CRX_GTX_P4

F35

PCIE_CRX_GTX_P3

E34

PCIE_CRX_GTX_P2

F33

PCIE_CRX_GTX_P1

D32

PCIE_CRX_GTX_P0

H35

H34

J33

H32

J31

G30

C33

B32

B31

PCIE_CTX_GRX_C_N7

A30

PCIE_CTX_GRX_C_N6

B29

PCIE_CTX_GRX_C_N5

A28

PCIE_CTX_GRX_C_N4

B27

PCIE_CTX_GRX_C_N3

A26

PCIE_CTX_GRX_C_N2

B25

PCIE_CTX_GRX_C_N1

A24

PCIE_CTX_GRX_C_N0

J35

G34

H33

G32

H31

H30

B33

A32

C31

PCIE_CTX_GRX_C_P7

B30

PCIE_CTX_GRX_C_P6

C29

PCIE_CTX_GRX_C_P5

B28

PCIE_CTX_GRX_C_P4

C27

PCIE_CTX_GRX_C_P3

B26

PCIE_CTX_GRX_C_P2

C25

PCIE_CTX_GRX_C_P1

B24

PCIE_CTX_GRX_C_P0

12

C9 0.22U_0402_10V6KPX@C9 0.22U_0402_10V6KPX@

C10 0.22U_0402_10V6KPX@C10 0.22U_0402_10V6KPX@

C11 0.22U_0402_10V6KPX@C11 0.22U_0402_10V6KPX@

C12 0.22U_0402_10V6KPX@C12 0.22U_0402_10V6KPX@

C13 0.22U_0402_10V6KPX@C13 0.22U_0402_10V6KPX@

C14 0.22U_0402_10V6KPX@C14 0.22U_0402_10V6KPX@

C15 0.22U_0402_10V6KPX@C15 0.22U_0402_10V6KPX@

C16 0.22U_0402_10V6KPX@C16 0.22U_0402_10V6KPX@

C25 0.22U_0402_10V6KPX@C25 0.22U_0402_10V6KPX@

C26 0.22U_0402_10V6KPX@C26 0.22U_0402_10V6KPX@

C27 0.22U_0402_10V6KPX@C27 0.22U_0402_10V6KPX@

C28 0.22U_0402_10V6KPX@C28 0.22U_0402_10V6KPX@

C29 0.22U_0402_10V6KPX@C29 0.22U_0402_10V6KPX@

C30 0.22U_0402_10V6KPX@C30 0.22U_0402_10V6KPX@

C31 0.22U_0402_10V6KPX@C31 0.22U_0402_10V6KPX@

C32 0.22U_0402_10V6KPX@C32 0.22U_0402_10V6KPX@

R124.9_0402_1% R124.9_0402_1%

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

PCIE_CRX_GTX_N[0..7] <23>

PCIE_CRX_GTX_P[0..7] <23>

2

PCIE_CTX_GRX_N7

PCIE_CTX_GRX_N6

PCIE_CTX_GRX_N5

PCIE_CTX_GRX_N4

PCIE_CTX_GRX_N3

PCIE_CTX_GRX_N2

PCIE_CTX_GRX_N1

PCIE_CTX_GRX_N0

PCIE_CTX_GRX_P7

PCIE_CTX_GRX_P6

PCIE_CTX_GRX_P5

PCIE_CTX_GRX_P4

PCIE_CTX_GRX_P3

PCIE_CTX_GRX_P2

PCIE_CTX_GRX_P1

PCIE_CTX_GRX_P0

1

PCIE_CTX_GRX_N[0..7] <23>

PCIE_CTX_GRX_P[0..7] <23>

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

3

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Title

Title

Title

PROCESSOR(1/7) DMI,FDI,PEG

PROCESSOR(1/7) DMI,FDI,PEG

PROCESSOR(1/7) DMI,FDI,PEG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-9641P

LA-9641P

LA-9641P

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

5 61Friday, April 19, 2013

5 61Friday, April 19, 2013

5 61Friday, April 19, 2013

1

1.0

Page 6

5

D D

4

3

H_DRAMRST#

2

R46

R46

1K_0402_5%

1K_0402_5%

1 2

DDR3_DRAMRST# <12,13>

1

+VCCIO_OUT

Haswell rPGA EDS

12

R8

R8

62_0402_5%

62_0402_5%

1 2

R9

H_PROCHOT#<43,48,49,56>

C C

H_CPUPWRGD<19>

C536

C536

22P_0402_50V8J

22P_0402_50V8J

C536 ESD reserve

R9

56_0402_5%

56_0402_5%

1

R15

R15

10K_0402_5%

10K_0402_5%

2

1 2

Note:

PECI/THERMTRIP:

Trace width=4 mils ,Spacing=18mil

Zo=50 ohm

H_PECI<19,43>

H_PROCHOT#_RH_PROCHOT#

H_THRMTRIP#<19>

H_PM_SYNC<15>

PM_SYS_PWRGD_BUF

CPU_PLTRST#<19>

CLK_CPU_DPLL#<16>

CLK_CPU_DPLL<16>

CLK_CPU_SSC_DPLL#<16>

CLK_CPU_SSC_DPLL<16>

CLK_CPU_DMI#<16>

CLK_CPU_DMI<16>

CLK_CPU_SSC_DPLL

CLK_CPU_SSC_DPLL#

T31T31

1 2

R10 0_0402_5%R10 0_0402_5%

1 2

R37 0_0402_5%R37 0_0402_5%

R26 10K_0402_5%@R26 10K_0402_5%@

R27 10K_0402_5%@R27 10K_0402_5%@

H_CATERR#

+VCCST

H_PM_SYNC_R

BUF_CPU_RST#

+VCCIO_OUT

12

12

JCPU1B

JCPU1B

AP32

SKTOCC

AN32

CATERR

AR27

PECI

AK31

FC_AK31

AM30

PROCHOT

AM35

THERMTRIP

AT28

PM_SYNC

AL34

PWRGOOD

AC10

SM_DRAMPWR OK

AT26

PLTRSTIN

G28

DPLL_REF_CLKN

H28

DPLL_REF_CLKP

F27

SSC_DPLL_REF_CLKN

E27

SSC_DPLL_REF_CLKP

D26

BCLKN

E26

BCLKP

ME@

ME@

Haswell rPGA EDS

MISC

MISC

THERMAL

THERMAL

PWR

PWR

INTEL_HASWELL_HAS WELL

INTEL_HASWELL_HAS WELL

DDR3

DDR3

CLOCK

CLOCK

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

SM_DRAMRST

JTAG

JTAG

BPM_N_0

BPM_N_1

BPM_N_2

BPM_N_3

BPM_N_4

BPM_N_5

BPM_N_6

BPM_N_7

2 OF 9

2 OF 9

PRDY

PREQ

TCK

TMS

TRST

TDO

DBR

AP3

SM_RCOMP0

AR3

SM_RCOMP1

AP2

SM_RCOMP2

AN3

H_DRAMRST#

AR29

XDP_PRDY#

AT29

XDP_PREQ#

AM34

XDP_TCLK

AN33

XDP_TMS

AM33

XDP_TRST#

AM31

XDP_TDI

TDI

AL33

XDP_TDO

AP33

XDP_DBRESET#

AR30

AN31

AN29

AP31

AP30

AN28

AP29

AP28

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

XDP_BPM#4

XDP_BPM#5

XDP_BPM#6

XDP_BPM#7

1

C186

C186

47P_0402_50V8J

47P_0402_50V8J

2

For EMI

Near Chip

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

Note:

Trace width=12~15 mil, Spcing=20 mils

Max trace length= 500 mils

PU/PD for JTAG signals

XDP_DBRESET#

XDP_TDO

XDP_TRST#

XDP_TCLK

SSC CLOCK TERMINATION, IF NOT USED, stuff R26,R27

B B

1 2

R5 100_0402_1%R5 100_0402_1%

1 2

R6 75_0402_1%R6 75_0402_1%

1 2

R7 100_0402_1%R7 100_0402_1%

R11 1K_0402_5%R11 1K_0402_5%

12

51_0804_8P4R_5%

51_0804_8P4R_5%

45

36

27

18

RP19

RP19

+3VS

+1.05VS

SM_DRAMPWROK with DDR Power Gating Topology

+3V_PCH +3V_PCH

DDR3 COMPENSATION SIGNALS

Q1

@

Q1

@

2N7002H_SOT23-3

2N7002H_SOT23-3

+1.35V_CPU_VDDQ

12

R30

R30

1.8K_0402_1%

1.8K_0402_1%

PM_SYS_PWRGD_BUF

12

R36

R36

3.3K_0402_1%

3.3K_0402_1%

@

@

1

C35

12

12

@

@

@

@

R28

R28

100K_0402_5%

100K_0402_5%

1 2

R32

@ R32

SYS_PWROK<15,43>

PM_DRAM_PWR GD<15>

A A

@

0_0402_5%

0_0402_5%

R29

R29

200_0402_1%

200_0402_1%

C35

0.1U_0402_16V7K

0.1U_0402_16V7K

2

1

B

2

A

1 2

R133 0_0402_5%@R133 0_0402_5%@

SUSP<47>

U1

U1

5

@

@

P

4

O

G

74AHC1G09GW_TSSOP5

74AHC1G09GW_TSSOP5

3

12

@

@

R35

R35

39_0402_5%

39_0402_5%

13

D

D

2

G

G

S

S

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

3

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Title

Title

Title

PROCESSOR(2/7) PM,XDP,CLK

PROCESSOR(2/7) PM,XDP,CLK

PROCESSOR(2/7) PM,XDP,CLK

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-9641P

LA-9641P

LA-9641P

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

1

6 61Friday, April 19, 2013

6 61Friday, April 19, 2013

6 61Friday, April 19, 2013

1.0

Page 7

5

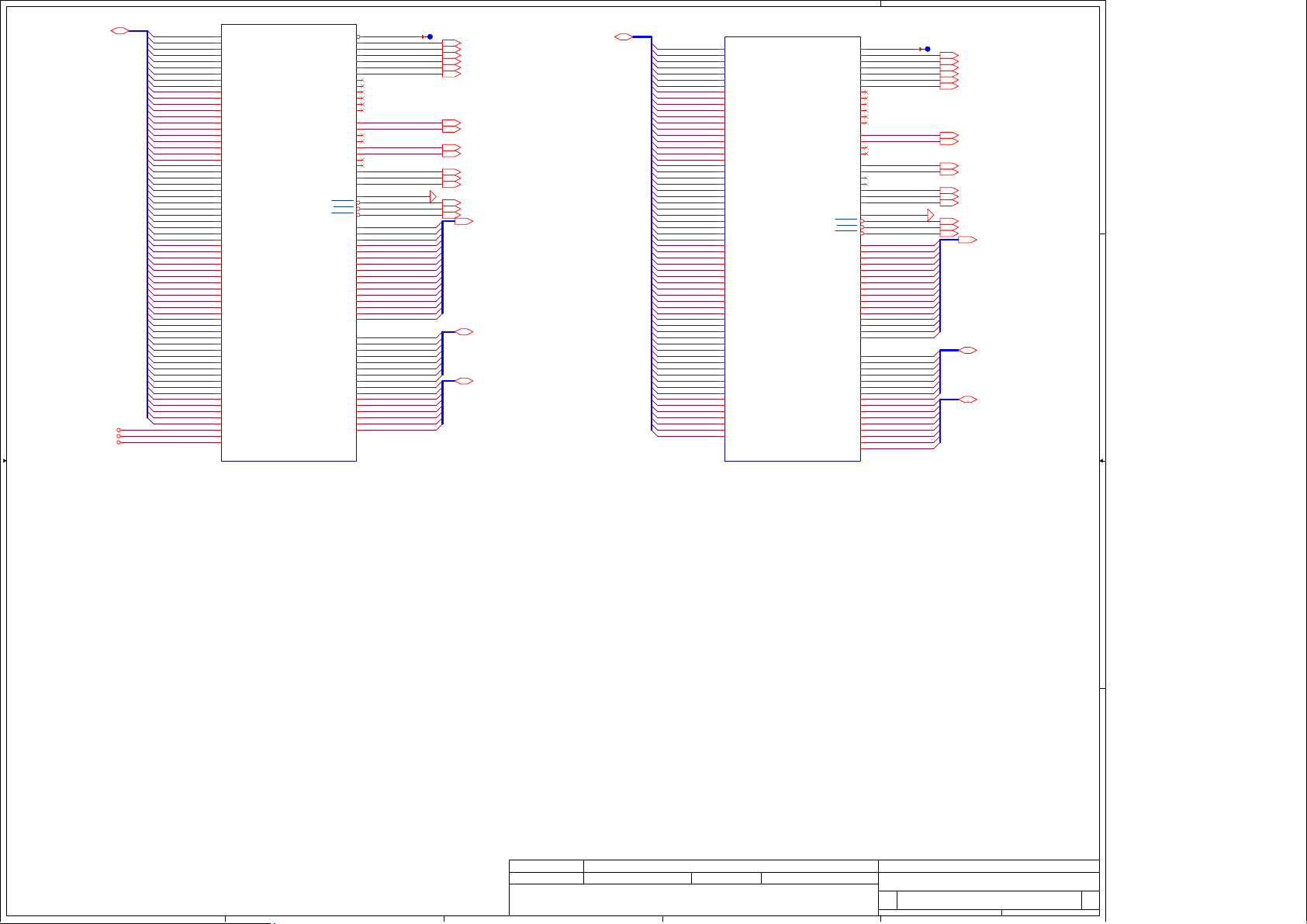

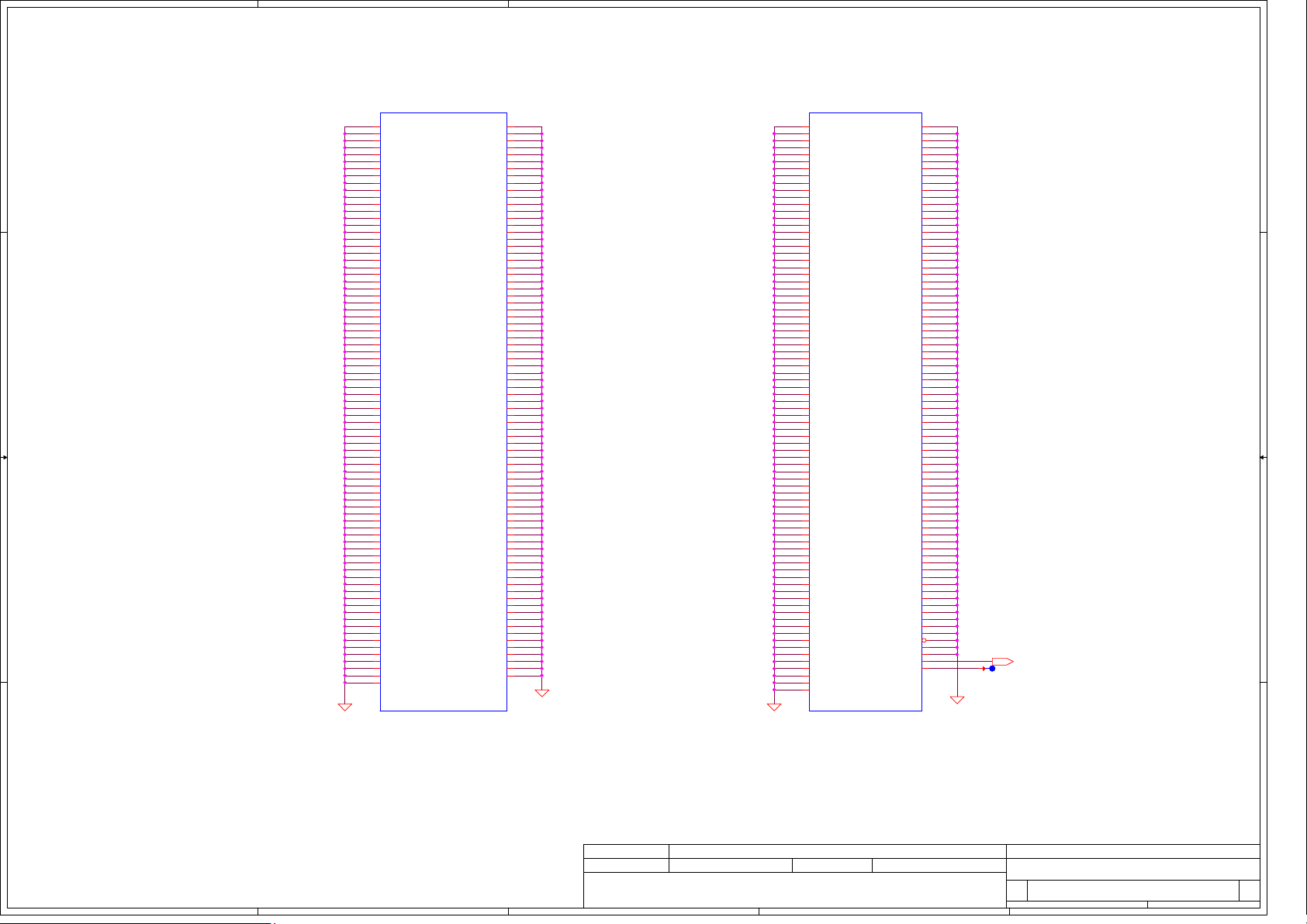

JCPU1C

DDR_A_D[0..63]<12>

D D

C C

+VREF_CA_R

+VREF_DQ_DIMMA_R

+VREF_DQ_DIMMB_R

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

+VREF_CA_R

+VREF_DQ_DIMMA_R

+VREF_DQ_DIMMB_R

AR15

AT14

AM14

AN14

AT15

AR14

AN15

AM15

AK10

AM9

AN9

AM8

AN8

AR9

AR8

AJ10

AG4

AG5

AG1

AG2

AM3

AT9

AT8

AJ9

AK9

AJ6

AK6

AJ7

AK7

AF4

AF5

AF1

AF2

J1

J2

J5

H5

H2

H1

J4

H4

F2

F1

D2

D3

D1

F3

C3

B3

B5

E6

A5

D6

D5

E5

B6

A6

E12

D12

B11

A11

E11

D11

B12

A12

F16

F13

JCPU1C

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

SM_VREF

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

EL_HASWELL_HASWELL

EL_HASWELL_HASWELL

INT

INT

ME@

ME@

Haswell rPGA EDS

Haswell rPGA EDS

SA_CK_N_0

SA_CK_P_0

SA_CKE_0

SA_CK_N_1

SA_CK_P_1

SA_CKE_1

SA_CK_N_2

SA_CK_P_2

SA_CKE_2

SA_CK_N_3

SA_CK_P_3

SA_CKE_3

SA_CS_N_0

SA_CS_N_1

SA_CS_N_2

SA_CS_N_3

SA_ODT_0

SA_ODT_1

SA_ODT_2

SA_ODT_3

SA_BS_0

SA_BS_1

SA_BS_2

SA_RAS

SA_CAS

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

SA_MA_15

SA_DQS_N_0

SA_DQS_N_1

SA_DQS_N_2

SA_DQS_N_3

SA_DQS_N_4

SA_DQS_N_5

SA_DQS_N_6

SA_DQS_N_7

SA_DQS_P_0

SA_DQS_P_1

SA_DQS_P_2

SA_DQS_P_3

SA_DQS_P_4

SA_DQS_P_5

SA_DQS_P_6

SA_DQS_P_7

3 OF 9

3 OF 9

4

RSVD

SA_WE

VSS

AC7

U4

M_CLK_DDR#0

V4

M_CLK_DDR0

AD9

DDR_CKE0_DIMMA

U3

M_CLK_DDR#1

V3

M_CLK_DDR1

AC9

DDR_CKE1_DIMMA

U2

V2

AD8

U1

V1

AC8

M7

DDR_CS0_DIMMA#

L9

DDR_CS1_DIMMA#

M9

M10

M8

M_ODT0

L7

M_ODT1

L8

L10

V5

DDR_A_BS0

U5

DDR_A_BS1

AD1

DDR_A_BS2

V10

U6

DDR_A_RAS#

U7

DDR_A_WE#

U8

DDR_A_CAS#

V8

DDR_A_MA0

AC6

DDR_A_MA1

V9

DDR_A_MA2

U9

DDR_A_MA3

AC5

DDR_A_MA4

AC4

DDR_A_MA5

AD6

DDR_A_MA6

AC3

DDR_A_MA7

AD5

DDR_A_MA8

AC2

DDR_A_MA9

V6

DDR_A_MA10

AC1

DDR_A_MA11

AD4

DDR_A_MA12

V7

DDR_A_MA13

AD3

DDR_A_MA14

AD2

DDR_A_MA15

AP15

DDR_A_DQS#0

AP8

DDR_A_DQS#1

AJ8

DDR_A_DQS#2

AF3

DDR_A_DQS#3

J3

DDR_A_DQS#4

E2

DDR_A_DQS#5

C5

DDR_A_DQS#6

C11

DDR_A_DQS#7

AP14

DDR_A_DQS0

AP9

DDR_A_DQS1

AK8

DDR_A_DQS2

AG3

DDR_A_DQS3

H3

DDR_A_DQS4

E3

DDR_A_DQS5

C6

DDR_A_DQS6

C12

DDR_A_DQS7

T12T12

M_CLK_DDR#0 <12>

M_CLK_DDR0 <12>

DDR_CKE0_DIMMA <12>

M_CLK_DDR#1 <12>

M_CLK_DDR1 <12>

DDR_CKE1_DIMMA <12>

DDR_CS0_DIMMA# <12>

DDR_CS1_DIMMA# <12>

M_ODT0 <12>

M_ODT1 <12>

DDR_A_BS0 <12>

DDR_A_BS1 <12>

DDR_A_BS2 <12>

DDR_A_RAS# <12>

DDR_A_WE# <12>

DDR_A_CAS# <12>

DDR_A_MA[0..15] <12>

DDR_A_DQS#[0..7] <12>

DDR_A_DQS[0..7] <12>

3

DDR_B_D[0..63]<13>

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

AR18

AT18

AM17

AM18

AR17

AT17

AN17

AN18

AT12

AR12

AN12

AM11

AT11

AR11

AM12

AN11

AR5

AR6

AM5

AM6

AT5

AT6

AN5

AN6

AJ4

AK4

AJ1

AJ2

AM1

AN1

AK2

AK1

L2

M2

L4

M4

L1

M1

L5

M5

G7

J8

G8

G9

J7

J9

G10

J10

A8

B8

A9

B9

D8

E8

D9

E9

E15

D15

A15

B15

E14

D14

A14

B14

JCPU1D

JCPU1D

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

EL_HASWELL_HASWELL

EL_HASWELL_HASWELL

INT

INT

ME@

ME@

2

Haswell rPGA EDS

Haswell rPGA EDS

SB_CKN0

SB_CK0

SB_CKE_0

SB_CKN1

SB_CK1

SB_CKE_1

SB_CKN2

SB_CK2

SB_CKE_2

SB_CKN3

SB_CK3

SB_CKE_3

SB_CS_N_0

SB_CS_N_1

SB_CS_N_2

SB_CS_N_3

SB_ODT_0

SB_ODT_1

SB_ODT_2

SB_ODT_3

SB_BS_0

SB_BS_1

SB_BS_2

SB_RAS

SB_CAS

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

SB_MA_15

SB_DQS_N_0

SB_DQS_N_1

SB_DQS_N_2

SB_DQS_N_3

SB_DQS_N_4

SB_DQS_N_5

SB_DQS_N_6

SB_DQS_N_7

SB_DQS_P_0

SB_DQS_P_1

SB_DQS_P_2

SB_DQS_P_3

SB_DQS_P_4

SB_DQS_P_5

SB_DQS_P_6

SB_DQS_P_7

4 OF 9

4 OF 9

RSVD

SB_WE

VSS

AG8

Y4

M_CLK_DDR#2

AA4

M_CLK_DDR2

AF10

DDR_CKE2_DIMMB

Y3

M_CLK_DDR#3

AA3

M_CLK_DDR3

AG10

DDR_CKE3_DIMMB

Y2

AA2

AG9

Y1

AA1

AF9

P4

DDR_CS2_DIMMB#

R2

DDR_CS3_DIMMB#

P3

P1

R4

M_ODT2

R3

M_ODT3

R1

P2

R7

DDR_B_BS0

P8

DDR_B_BS1

AA9

DDR_B_BS2

R10

R6

DDR_B_RAS#

P6

DDR_B_WE#

P7

DDR_B_CAS#

R8

DDR_B_MA0

Y5

DDR_B_MA1

Y10

DDR_B_MA2

AA5

DDR_B_MA3

Y7

DDR_B_MA4

AA6

DDR_B_MA5

Y6

DDR_B_MA6

AA7

DDR_B_MA7

Y8

DDR_B_MA8

AA10

DDR_B_MA9

R9

DDR_B_MA10

Y9

DDR_B_MA11

AF7

DDR_B_MA12

P9

DDR_B_MA13

AA8

DDR_B_MA14

AG7

DDR_B_MA15

AP18

DDR_B_DQS#0

AP11

DDR_B_DQS#1

AP5

DDR_B_DQS#2

AJ3

DDR_B_DQS#3

L3

DDR_B_DQS#4

H9

DDR_B_DQS#5

C8

DDR_B_DQS#6

C14

DDR_B_DQS#7

AP17

DDR_B_DQS0

AP12

DDR_B_DQS1

AP6

DDR_B_DQS2

AK3

DDR_B_DQS3

M3

DDR_B_DQS4

H8

DDR_B_DQS5

C9

DDR_B_DQS6

C15

DDR_B_DQS7

T13T13

1

M_CLK_DDR#2 <13>

M_CLK_DDR2 <13>

DDR_CKE2_DIMMB <13>

M_CLK_DDR#3 <13>

M_CLK_DDR3 <13>

DDR_CKE3_DIMMB <13>

DDR_CS2_DIMMB# <13>

DDR_CS3_DIMMB# <13>

M_ODT2 <13>

M_ODT3 <13>

DDR_B_BS0 <13>

DDR_B_BS1 <13>

DDR_B_BS2 <13>

DDR_B_RAS# <13>

DDR_B_WE# <13>

DDR_B_CAS# <13>

DDR_B_MA[0..15] <13>

DDR_B_DQS#[0..7] <13>

DDR_B_DQS[0..7] <13>

CPI DRIVER VREF PATH IS DEFAULT

B B

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Title

Title

Title

PROCESSOR(3/7) DDRIII

PROCESSOR(3/7) DDRIII

PROCESSOR(3/7) DDRIII

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-9641P

LA-9641P

LA-9641P

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

7 61Friday, April 19, 2013

7 61Friday, April 19, 2013

7 61Friday, April 19, 2013

1

1.0

Page 8

5

D D

4

3

2

1

COMPENSATION PU FOR eDP

+VCOMP_OUT

EDP_COMP

Note:

Trace width=20 mils ,Spacing=25mil,

EDP_AUXN

EDP_AUXP

EDP_HPD

FDI_TXN_0

FDI_TXP_0

FDI_TXN_1

FDI_TXP_1

DDI

DDI

8 OF 9

8 OF 9

Max length=100 mils.

M27

EDP_CPU_AUX#

N27

EDP_CPU_AUX

P27

EDP_HPD#

E24

EDP_COMP

R27

P35

EDP_CPU_LANE_N0

R35

EDP_CPU_LANE_P0

N34

EDP_CPU_LANE_N1

P34

EDP_CPU_LANE_P1

P33

FDI_CTX_PRX_N0

R33

FDI_CTX_PRX_P0

N32

FDI_CTX_PRX_N1

P32

FDI_CTX_PRX_P1

T14T14

HPD INVERSION FOR EDP

Haswell rPGA EDS

Haswell rPGA EDS

1 2

HDMI D2

HDMI D1

HDMI D0

C C

HDMI CLK

HD

MI

HDMI_TX2-_CK<36>

HDMI_TX2+_CK<36>

HDMI_TX1-_CK<36>

HDMI_TX1+_CK<36>

HDMI_TX0-_CK<36>

HDMI_TX0+_CK<36>

HDMI_CLK-_CK<36>

HDMI_CLK+_CK< 36>

C48 0.1U_0402_16V7KHDMI@ C48 0.1U_0402_16V7KHDM I@

1 2

C41 0.1U_0402_16V7KHDMI@ C41 0.1U_0402_16V7KHDM I@

1 2

C42 0.1U_0402_16V7KHDMI@ C42 0.1U_0402_16V7KHDM I@

1 2

C43 0.1U_0402_16V7KHDMI@ C43 0.1U_0402_16V7KHDM I@

1 2

C44 0.1U_0402_16V7KHDMI@ C44 0.1U_0402_16V7KHDM I@

1 2

C45 0.1U_0402_16V7KHDMI@ C45 0.1U_0402_16V7KHDM I@

1 2

C46 0.1U_0402_16V7KHDMI@ C46 0.1U_0402_16V7KHDM I@

1 2

C47 0.1U_0402_16V7KHDMI@ C47 0.1U_0402_16V7KHDM I@

TMDS_B_DATA2#_PCH

TMDS_B_DATA2_PCH

TMDS_B_DATA1#_PCH

TMDS_B_DATA1_PCH

TMDS_B_DATA0#_PCH

TMDS_B_DATA0_PCH

TMDS_B_CLK#_PCH

TMDS_B_CLK_PCH

Place on connector side

T28

DDIB_TXBN_0

U28

DDIB_TXBP_0

T30

DDIB_TXBN_1

U30

DDIB_TXBP_1

U29

DDIB_TXBN_2

V29

DDIB_TXBP_2

U31

DDIB_TXBN_3

V31

DDIB_TXBP_3

T34

DDIC_TXCN_0

U34

DDIC_TXCP_0

U35

DDIC_TXCN_1

V35

DDIC_TXCP_1

U32

DDIC_TXCN_2

T32

DDIC_TXCP_2

U33

DDIC_TXCN_3

V33

DDIC_TXCP_3

P29

DDID_TXDN_0

R29

DDID_TXDP_0

N28

DDID_TXDN_1

P28

DDID_TXDP_1

P31

DDID_TXDN_2

R31

DDID_TXDP_2

N30

DDID_TXDN_3

P30

DDID_TXDP_3

INTEL_HASWELL_HAS WELL

INTEL_HASWELL_HAS WELL

ME@

ME@

JCPU1H

JCPU1H

eDP

eDP

EDP_RCOMP

EDP_DISP_UT IL

EDP_TXN_0

EDP_TXP_0

EDP_TXN_1

EDP_TXP_1

12

R6024.9_0402_1% R6024.9_0402_1%

EDP_CPU_AUX# <33>

EDP_CPU_AUX <33>

EDP_CPU_LANE_N0 <33>

EDP_CPU_LANE_P0 <33>

FDI_CTX_PRX_N0 <15>

FDI_CTX_PRX_P0 <15>

FDI_CTX_PRX_N1 <15>

FDI_CTX_PRX_P1 <15>

+VCCIO_OUT

10K_0402_5%

10K_0402_5%

RC1

RC1

1 2

B B

R458

R458

1 2

1K_0402_5%

TL_HPD<33>

1K_0402_5%

2

1

OUT

IN

GND

DTC124EKAT146_SC59-3

DTC124EKAT146_SC59-3

3

EDP_HPD#

Q6

Q6

HPD is a active high signal from device. The HPD processor input is a low voltage

active signal.

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

3

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Title

Title

Title

PROCESSOR(2/7) PM,XDP,CLK

PROCESSOR(2/7) PM,XDP,CLK

PROCESSOR(2/7) PM,XDP,CLK

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-9641P

LA-9641P

LA-9641P

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

1

8 61Friday, April 19, 2013

8 61Friday, April 19, 2013

8 61Friday, April 19, 2013

1.0

Page 9

5

4

3

2

1

CFG Straps for Processor

CFG2

12

R62

R62

1K_0402_1%

1K_0402_1%

PX@

D D

PEG Static Lane Reversal - CFG2 is for the 16x

CFG2

Haswell rPGA EDS

Haswell rPGA EDS

AT1

RSVD_TP

AT2

RSVD_TP

AD10

RSVD

A34

RSVD_TP

A35

RSVD_TP

W29

RSVD_TP

W28

RSVD_TP

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

G26

TESTLO_G26

W33

RSVD

AL30

RSVD

AL29

RSVD

F25

VCC

C35

RSVD_TP

B35

RSVD_TP

AL25

RSVD_TP

W30

RSVD_TP

W31

RSVD_TP

W34

TESTLO

AT20

CFG_0

AR20

CFG_1

AP20

CFG_2

AP22

CFG_3

AT22

CFG_4

AN22

CFG_5

AT25

CFG_6

AN23

CFG_7

AR24

CFG_8

AT23

CFG_9

AN20

CFG_10

AP24

CFG_11

AP26

CFG_12

AN25

CFG_13

AN26

CFG_14

AP25

CFG_15

INTEL_HASWELL_HAS WELL

INTEL_HASWELL_HAS WELL

ME@

ME@

H_CPU_RSVD

C C

B B

1 2

1 2

1 2

H_CPU_TESTLO

CFG_RCOMP

H_CPU_RSVD

R64 49.9_0402 _1%R64 49.9_0402 _1%

R309 49.9_0402_1%R309 49.9_0402_1%

R66 49.9_0402_1%R66 49.9_0402_1%

+CPU_CORE

T16T16

T17T17

T18T18

H_CPU_TESTLO

JCPU1I

JCPU1I

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

CFG_RCOMP

CFG_16

CFG_18

CFG_17

CFG_19

RSVD

FC_G6

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

VSS

VSS

9 OF 9

9 OF 9

C23

B23

D24

D23

AT31

CFG_RCOMP

AR21

CFG16

AR23

AP21

AP23

AR33

G6

AM27

AM26

F5

AM2

K6

E18

U10

P10

B1

NC

A2

AR1

E21

E20

AP27

AR26

AL31

AL32

T19T19

Embedded Display Port Presence Strap

PCIE Port Bifurcation Straps

CFG[6:5]

*

CFG4

CFG4

*

@ R67

@

1K_0402_1%

1K_0402_1%

11: (Default) x16 - Device 1 functions 1 and 2 disabled

*

10: x8, x8 - Device 1 function 1 enabled ; function 2

01: Reserved - (Device 1 function 1 disabled ; function

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

PX@

1: Normal Operation; Lane # definition matches

socket pin map definition

0:L

ane Reversed

12

R63

R63

1K_0402_1%

1K_0402_1%

1 : Disabled; No Physical Display Port

attached to Embedded Display Port

0 : Enabled; An external Display Port device is

con

nected to the Embedded Display Port

CFG6

CFG5

12

12

R67

R68

@R68

@

1K_0402_1%

1K_0402_1%

disabled

2 enabled)

PEG DEFER TRAINING

(Default) PEG Train immediately following xxRESETB

CFG7

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

3

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

1:

de assertion

*

0: PEG Wait for BIOS for training

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(4/7) RSVD,CFG

PROCESSOR(4/7) RSVD,CFG

PROCESSOR(4/7) RSVD,CFG

LA-9641P

LA-9641P

LA-9641P

1

9 61Friday, April 19, 2013

9 61Friday, April 19, 2013

9 61Friday, April 19, 2013

1.0

Page 10

5

4

3

2

1

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AA26

AA28

AA34

AA30

AA32

AB26

AB29

AB25

AB27

AB28

AB30

AB31

AB33

AB34

AB32

AC26

AB35

AC28

AD25

AC30

AD28

AC32

AD31

AC34

AD34

AD26

AD27

AD29

AD30

AD32

AD33

AD35

AE26

AE32

AE28

AE30

AG28

AG34

AE34

AF25

AF26

AF27

AF28

AF29

AF30

AF31

AF32

AF33

AF34

AF35

AG26

AH26

AH29

AG30

AG32

AH32

AH35

AH25

AH27

AH28

AH30

AH31

AH33

AH34

AJ25

AJ26

AJ27

AJ28

AJ29

AJ30

AJ31

AJ32

AJ33

AJ34

AJ35

G25

H25

J25

K25

L25

M25

N25

P25

R25

T25

U25

U26

V25

V26

W26

W27

+CPU_CORE

Haswell rPGA EDS

Haswell rPGA EDS

JCPU1E

JCPU1E

+CPU_CORE

AB11

AE11

AH11

W11

AL27

AK27

AL35

AN35

W32

AL16

AL13

AM28

AM29

AL28

AP35

AP34

AT35

AR35

AR32

AL26

AT34

AL22

AT33

AM21

AM25

AM22

AM20

AM24

AL19

AM23

AT32

K27

L27

T27

V27

AB2

AB5

AB8

AE2

AE5

AE8

K11

N11

N8

T11

T2

T5

T8

W2

W5

W8

N26

K26

E17

A23

F22

J27

H27

Y25

Y26

Y27

Y28

Y29

Y30

Y31

Y32

Y33

Y34

Y35

RSVD

RSVD

RSVD

RSVD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

RSVD

VCC

RSVD

RSVD

VCC_SENSE

RSVD

VCCIO_OUT

RSVD

VCOMP_OUT

RSVD

RSVD

RSVD

RSVD

VIDALERT

VIDSCLK

VIDSOUT

VSS

PWR_DEBUG

VSS

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

ME@

ME@

EL_HASWELL_HASWELL

EL_HASWELL_HASWELL

INT

INT

5 OF 9

5 OF 9

+1.35V_CPU_VDDQ Source

D D

VCCSENSE

VSSSENSE

+CPU_CORE

100_0402_1%

100_0402_1%

12

100_0402_1%

100_0402_1%

12

R79

R79

R84

R84

VCC_SENSE

Note:

0 ohm Resistor should be placed

cloose to CPU

C C

VCCSENSE<56>

VSSSENSE<11,56>

+1.35V +1.35V_CPU_VDDQ

J1

@J1

@

1 2

PAD-OPEN 43x118m

PAD-OPEN 43x118m

+1.05VS

R78 0_0603_5%@R78 0_0603_5%@

RESISTOR STUFFING OPTIONS ARE

PROVIDED FOR TESTING PURPOSES

12

+VCCIO_OUT

1

2

+CPU_CORE

@

@

C53

C53

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

VR_SVID_ALRT#<56>

VR_SVID_CLK<56>

VR_SVID_DAT<56>

Note:

Place the UP resistor close to CPU

+VCCIO_OUT

Note:

Place the UP resistor close to CPU

12

R81

R81

75_0402_1%

75_0402_1%

1 2

R83 43_0402_5%R83 43_0402_5%

+VCCIO_OUT

12

R87

R87

130_0402_1%

130_0402_1%

+1.05VS

+VCCIO_OUT

+VCOMP_OUT

R88

R88

150_0402_1%

150_0402_1%

10K_0402_5%

10K_0402_5%

12

R89

R89

+1.35V_CPU_VDDQ

VCCSENSE

H_CPU_SVIDALRT#

T23T23

@

@

1 2

VDDQ DECOUPLING

+1.35V_CPU_VDDQ

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

C55

C55

C54

C54

1

B B

1

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C60

C60

1

2

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

C56

C56

1

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C61

C61

1

2

10U_0603_6.3V6M

10U_0603_6.3V6M

C57

C57

C58

C58

1

1

1

+

+

C59

C59

220U_2.5V_M

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C62

C62

1

2

220U_2.5V_M

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

C63

C63

C64

C64

1

1

2

2

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

PROCESSOR(6/7) PWR

PROCESSOR(6/7) PWR

PROCESSOR(6/7) PWR

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-9641P

LA-9641P

LA-9641P

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

1

10 61Friday, April 19, 2013

10 61Friday, April 19, 2013

10 61Friday, April 19, 2013

1.0

Page 11

5

D D

C C

B B

AA11

AA25

AA27

AA31

AA29

AB10

AA33

AA35

AC25

AC27

AC11

AD11

AC29

AC31

AC33

AC35

AD7

AE10

AE25

AE29

AE27

AE35

AF11

AG11

AG25

AE31

AG31

AE33

AG6

AH1

AH10

AH2

AG27

AG29

AH3

AG33

AG35

AH4

AH5

AH6

AH7

AH8

AH9

AJ11

AK11

AK25

AK26

AK28

AK29

AK30

AK32

A10

A13

A16

A19

A22

A25

A27

A29

A3

A31

A33

A4

A7

AB1

AB3

AB4

AB6

AB7

AB9

AE1

AE3

AE4

AE6

AE7

AE9

AF6

AF8

AJ5

E19

Haswell rPGA EDS

Haswell rPGA EDS

4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

EL_HASWELL_HASW ELL

EL_HASWELL_HASW ELL

INT

INT

ME@

ME@

JCPU1F

JCPU1F

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

6 OF 9

6 OF 9

AK34

AK5

AL1

AL10

AL11

AL12

AL14

AL15

AL17

AL18

AL2

AL20

AL21

AL23

E22

AL3

AL4

AL5

AL6

AL7

AL8

AL9

AM10

AM13

AM16

AM19

E25

AM32

AM4

AM7

AN10

AN13

AN16

AN19

AN2

AN21

AN24

AN27

AN30

AN34

AN4

AN7

AP1

AP10

AP13

AP16

AP19

AP4

AP7

W25

AR10

AR13

AR16

AR19

AR2

AR22

AR25

AR28

AR31

AR34

AR4

AR7

AT10

AT13

AT16

AT19

AT21

AT24

AT27

AT3

AT30

AT4

AT7

B10

B13

B16

B19

B2

B22

3

Haswell rPGA EDS

Haswell rPGA EDS

B34

VSS

B4

VSS

B7

VSS

C1

VSS

C10

VSS

C13

VSS

C16

VSS

C19

VSS

C2

VSS

C22

VSS

C24

VSS

C26

VSS

C28

VSS

C30

VSS

C32

VSS

C34

VSS

C4

VSS

C7

VSS

D10

VSS

D13

VSS

D16

VSS

D19

VSS

D22

VSS

D25

VSS

D27

VSS

D29

VSS

D31

VSS

D33

VSS

D35

VSS

D4

VSS

D7

VSS

E1

VSS

E10

VSS

E13

VSS

E16

VSS

E4

VSS

E7

VSS

F10

VSS

F11

VSS

F12

VSS

F14

VSS

F15

VSS

F17

VSS

F18

VSS

F20

VSS

F21

VSS

F23

VSS

F24

VSS

F26

VSS

F28

VSS

F30

VSS

F32

VSS

F34

VSS

F4

VSS

F6

VSS

F7

VSS

F8

VSS

F9

VSS

G1

VSS

G11

VSS

G2

VSS

G27

VSS

G29

VSS

G3

VSS

G31

VSS

G33

VSS

G35

VSS

G4

VSS

G5

VSS

H10

VSS

H26

VSS

H6

VSS

H7

VSS

J11

VSS

J26

VSS

J28

VSS

J30

VSS

J32

VSS

J34

VSS

J6

VSS

K1

VSS

EL_HASWELL_HASW ELL

EL_HASWELL_HASW ELL

INT

INT

ME@

ME@

JCPU1G

JCPU1G

2

VSS_SENSE

RSVD

7 OF 9

7 OF 9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K10

K2

K29

K3

K31

K33

K35

K4

K5

K7

K8

K9

L11

L26

L6

M11

M26

M28

M30

M32

M34

M6

N1

N10

N2

N29

N3

N31

N33

N35

N4

N5

N6

N7

N9

P11

P26

P5

R11

R26

R28

R30

R32

R34

R5

T1

T10

T29

T3

T31

T33

T35

T4

T6

T7

T9

U11

U27

V11

V28

V30

V32

V34

W1

W10

W3

W35

W4

W6

W7

W9

Y11

H11

AL24

F19

T26

AK35

AK33

VSSSENSE <10,56>

T15T15

1

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL