Page 1

A

1 1

B

C

D

E

Compal Confidential

2 2

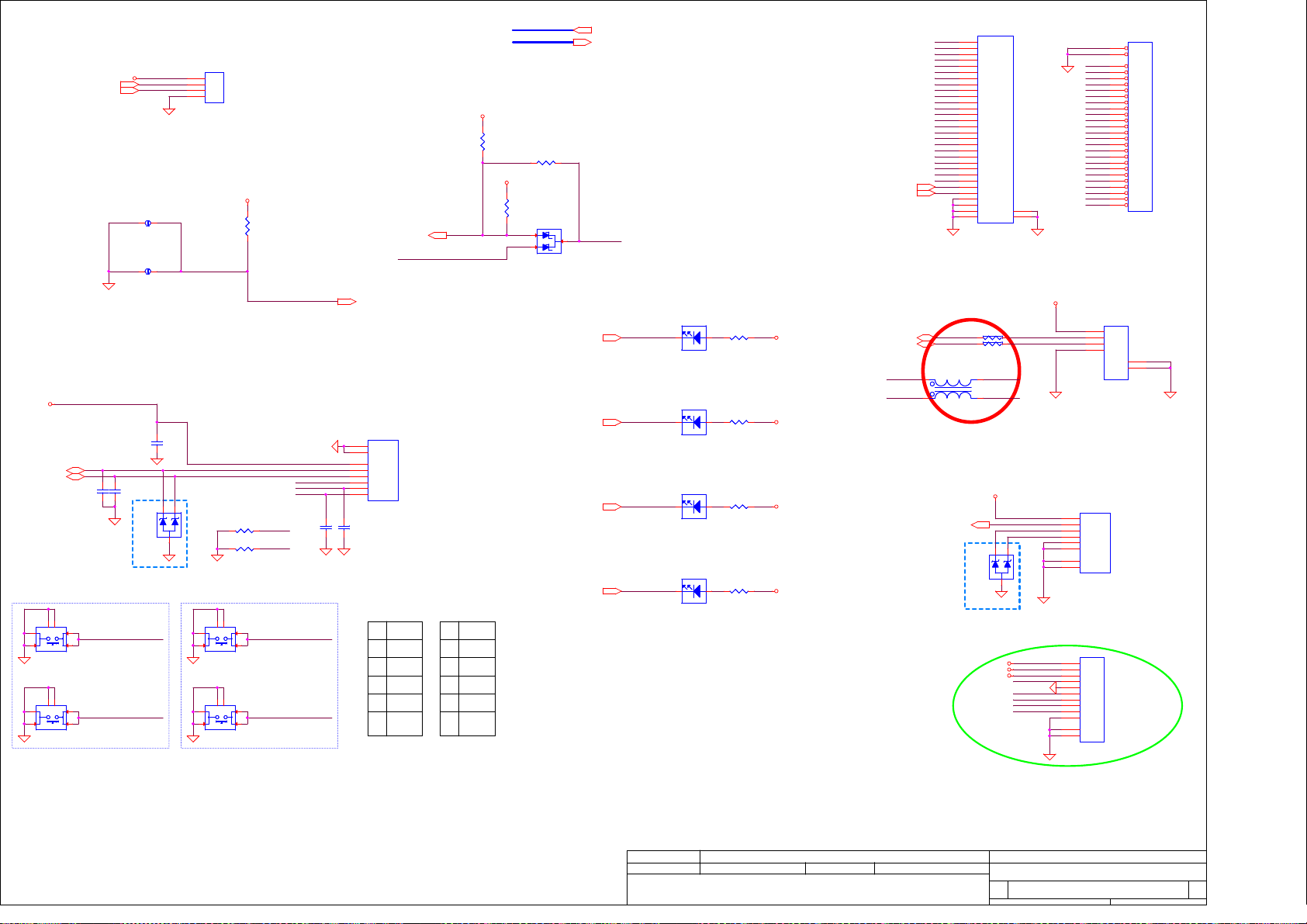

Gx00/Gx00 DIS M/B Schematics Document

Intel Ivy Bridge Processor with DDRIII + Panther Point PCH

AMD Mars XT / SUN Pro

2013-02-27

3 3

LA-9631P

REV:1.0

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

A

B

www.laptopfix.vn

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

C

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

LA-9631P

LA-9631P

LA-9631P

E

1 60Wednesday, February 27, 2013

1 60Wednesday, February 27, 2013

1 60Wednesday, February 27, 2013

1.0

1.0

1.0

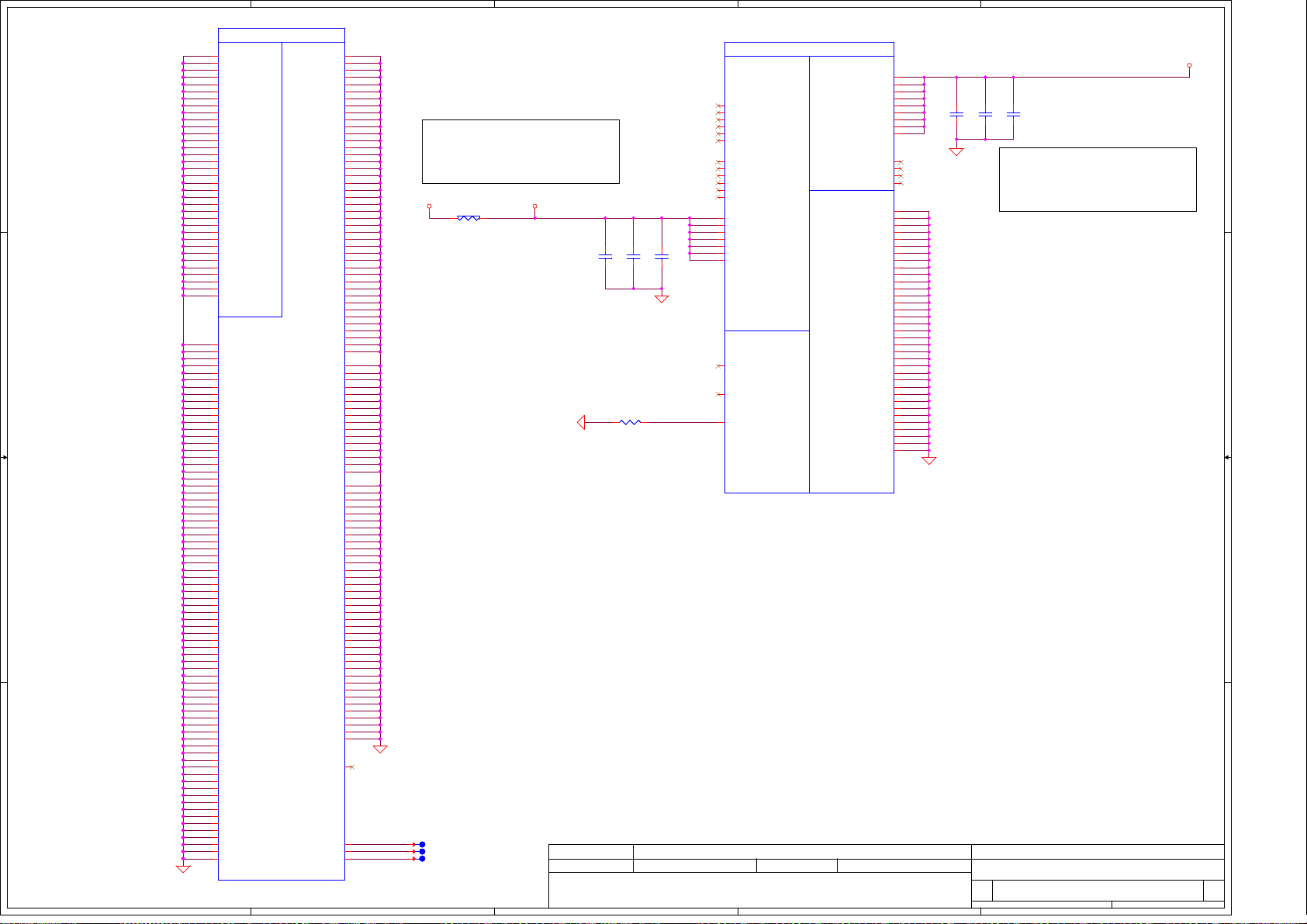

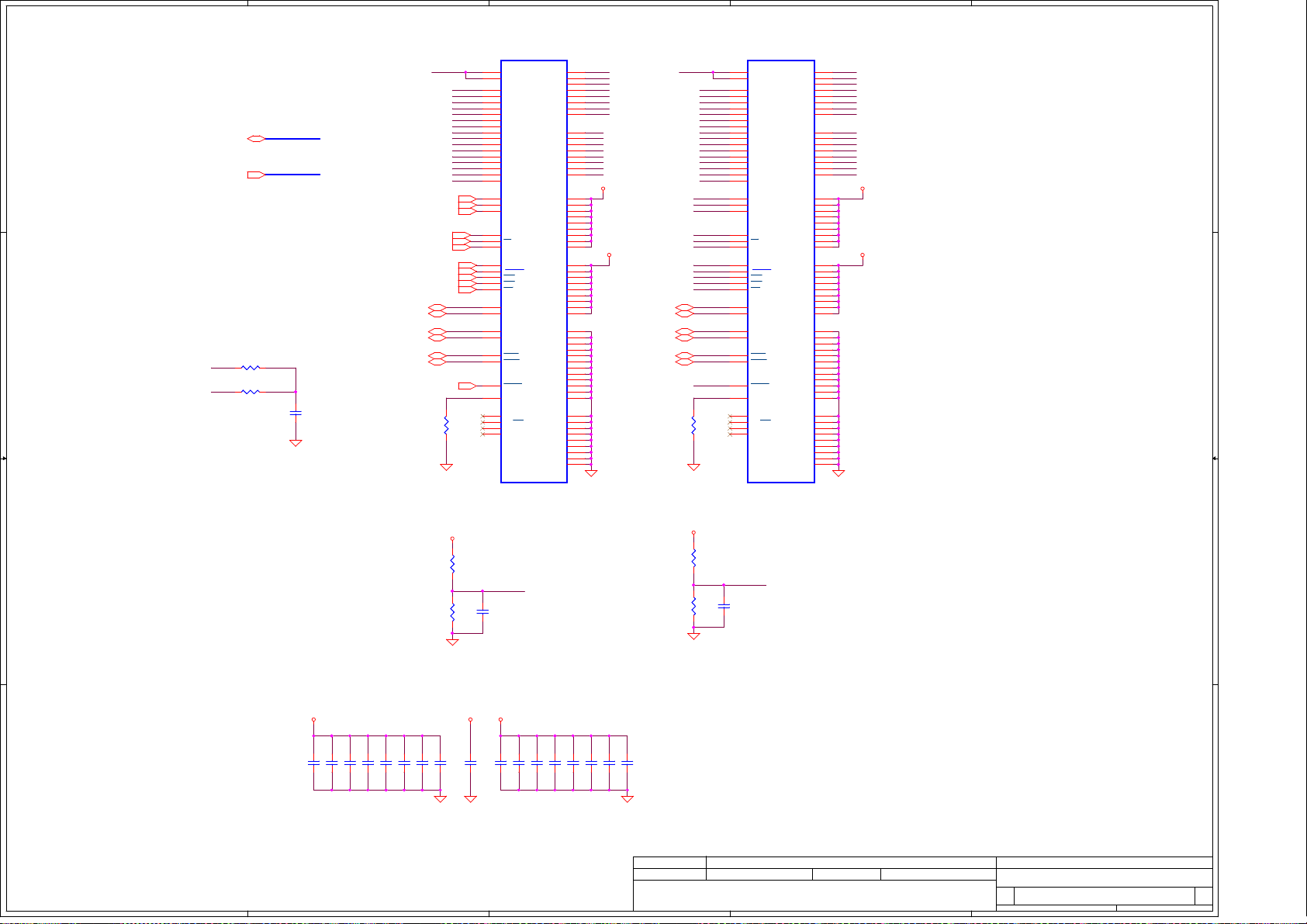

Page 2

A

B

C

D

E

Compal confidential

Project Name : VIWGP (14") / VIWGR (15")

Chief River

1 1

AMD MARS XT M2 128 bits

/ SUN PRO M2 64 bits

VRAM 512MB/1GB/2GB

MARS XT : DDR3 x 8

SUN PRO : DDR3 x 4

Page 23~32

PEG 8x

Gen2 / Gen3

Intel

Processor

Ivy Bridge

rPGA989

37.5mm x 37.5mm

Page 5~11

Memory Bus

Dual Channel

DDR3

DDR3

DDR3

1600MHz

1333MHz

1066MHz

204pin DDRIII-SO-DIMM X2

BANK 0, 1, 2

Page 12, 13

FDI *8

2.7GT/s

2 2

LVDS Conn.

Page 33

HDMI Conn.

Page 35

CRT Conn.

Page 34

Intel

DMI2 *4

5GT/s

USB30 x2

USB20 x6

Left USB3.0 x2

USB30 Port 0,1

Page 45

Touch Screen

USB20 Port 2

Page 45

Right USB2.0

USB20 Port 9

Card Reader

Realtek RTS5170

USB20 Port 11

Page 45

page 28

Int. Camera

USB20 Port 3

Page 33

PCH

Page 43

HDD Conn.

SATA Port 0

Page 40

ODD Conn.

SATA Port 2

Audio Codec

CONEXANT

CX20757

Page 40

Page 41

Int. MIC Conn.

Page 41

Int. KBD

Page 43

D

Int. Speaker Conn.

Page 41

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Audio Combo Jacks

HP & MIC

MB Block Diagram

MB Block Diagram

MB Block Diagram

LA-9631P

LA-9631P

LA-9631P

E

2 60Wednesday, February 27, 2013

2 60Wednesday, February 27, 2013

2 60Wednesday, February 27, 2013

Page 41

1.0

1.0

1.0

RJ45 Conn.

Page 38

LAN

PCIe Port 0

Atheros

AR8162/QCA8172(10/100)

Page 37

PCIe x1

Panther Point

FCBGA 989Balls

25mm x 25mm

3 3

PCIe Mini Card

WLAN

PCIe Port 1

Page 36

PCIe x1

Page 14~22

SATA Gen3

SATA

AZALIA

Sub-borad

15"

14"

Power/B

(LID)

4 4

LS9631

USB/B

LS9632 LS9634

IO/B

(Card Reader) (LED, LID)

LS9633

ODD/B

Switch/B

A

LS9635

B

www.laptopfix.vn

SPI ROM

2MB + 4MB

Page 14

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

EC

ENE KB9012

Page 42

Thermal Sensor

C

Page 39

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

Touch Pad

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

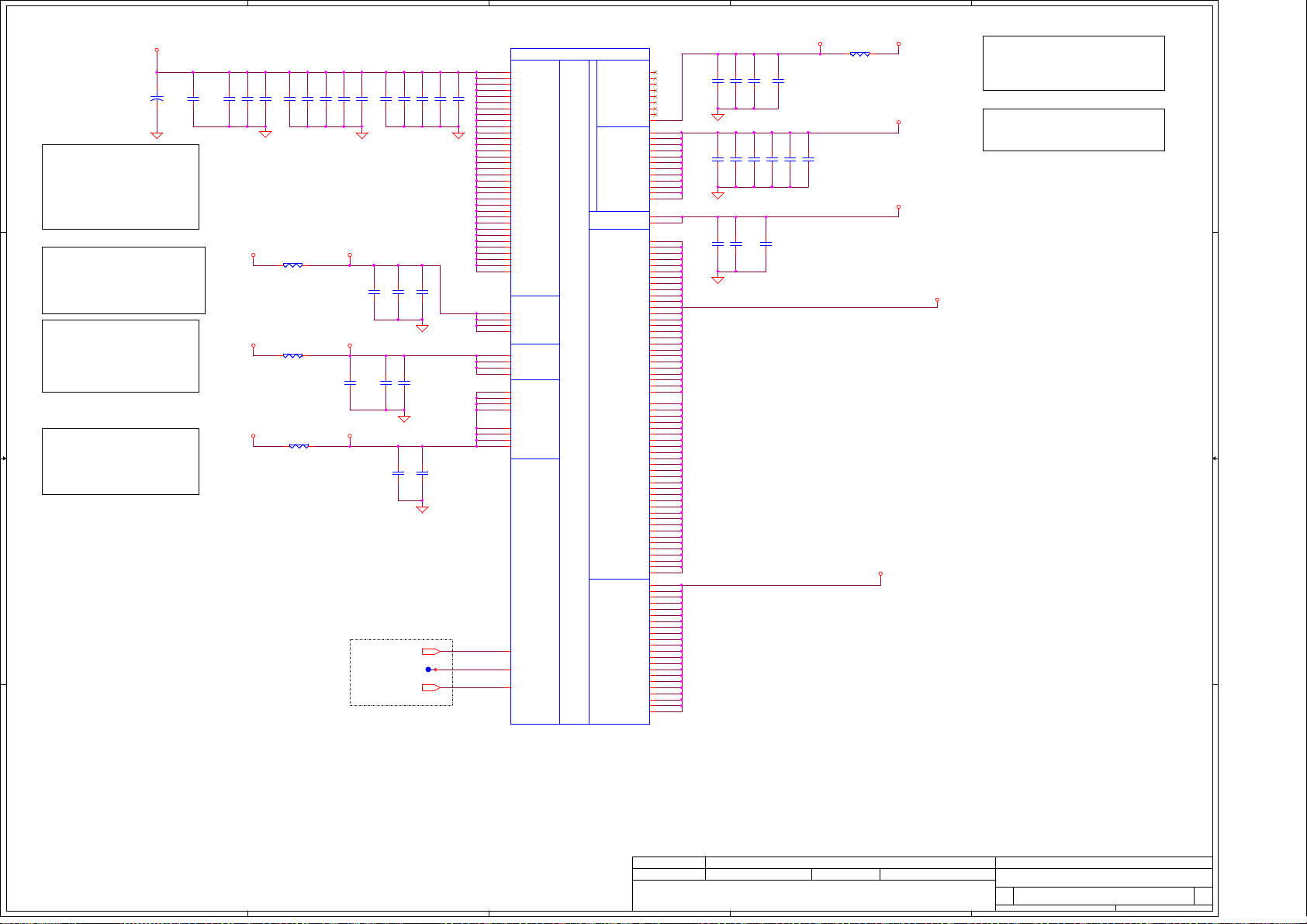

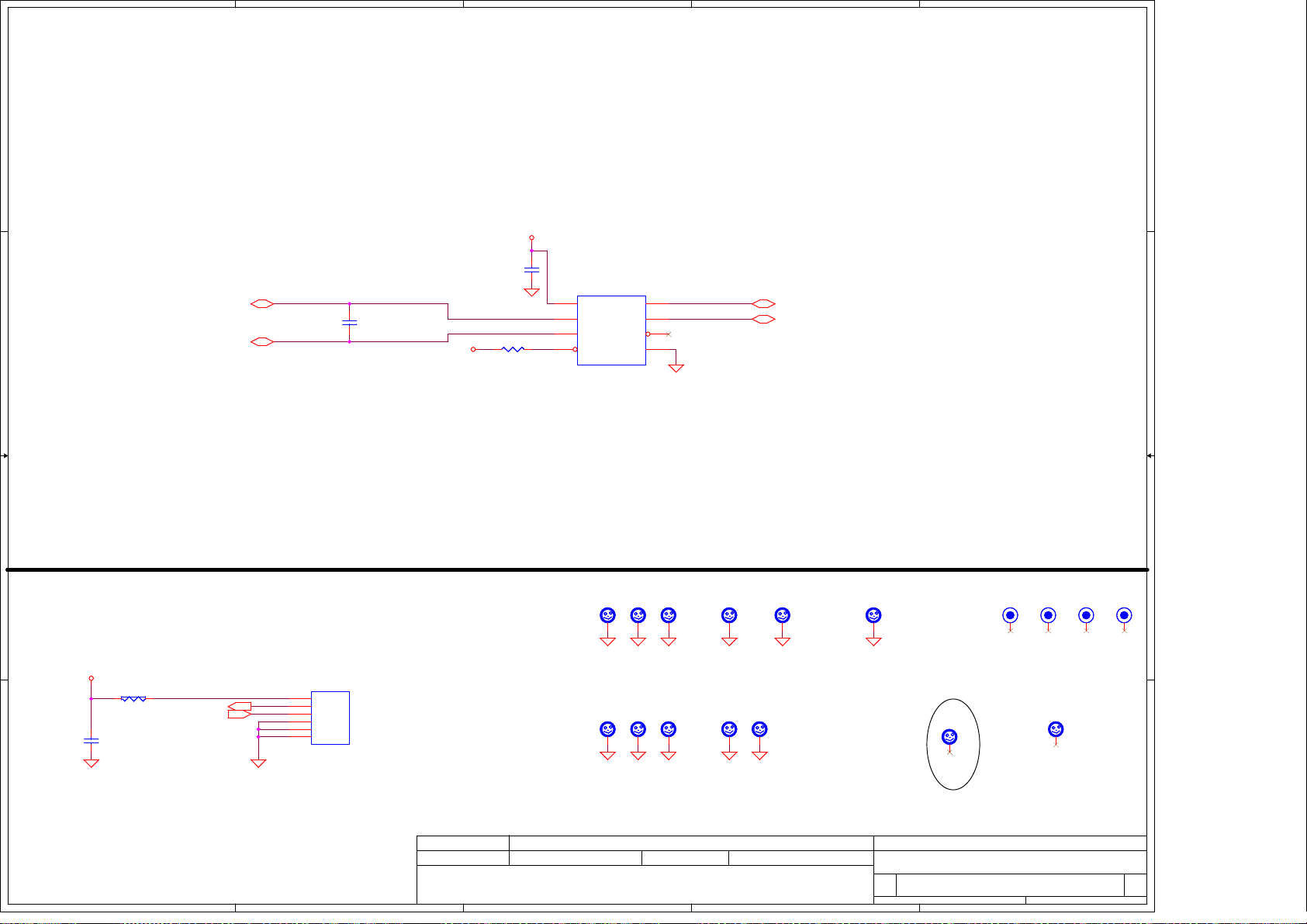

Page 3

A

B

C

D

E

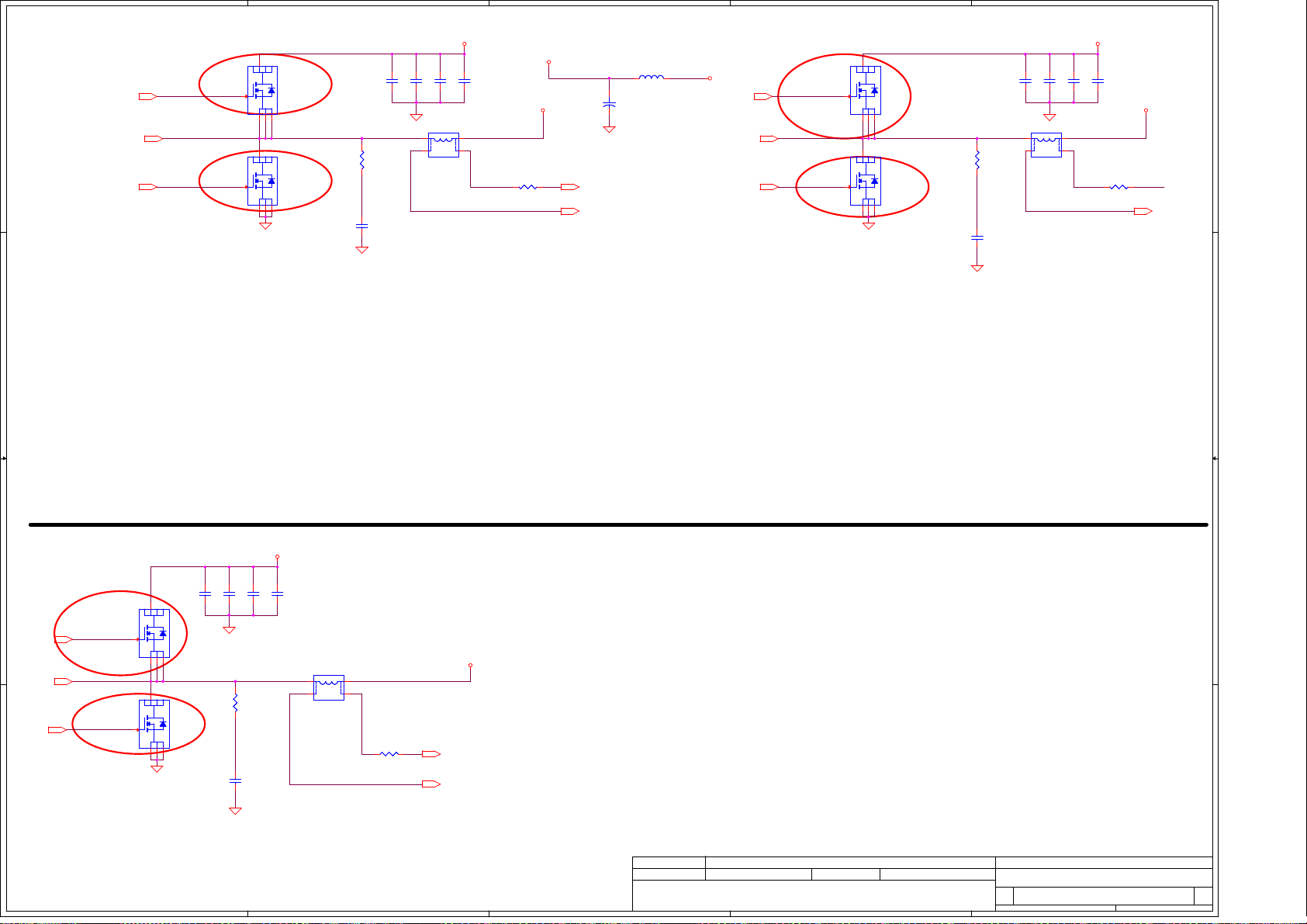

Voltage Rails

+5VS

power

State

S0

S3

S5 S4/AC

plane

Address

0001 011x

1010 000x A0h

1010 010x A4h

+B

O

O

O

O

X

+5VALW

+3VALW

O

O

O

X

X X X

+1.5V

O

X X

X

EC SM Bus2 address

Device

Thermal Sen sor

AMD-GPU SM Bus address

Device Address

Internal thermal sensor

1 1

2 2

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

EC SM Bus1 address

Device

Smart Battery

PCH SM Bus address

3 3

Device Address

DDR_JDIMM1

DDR_JDIMM2

+3VS

+1.5VS

+V1.05S_VCCP

+VCC_CORE

+VGA_CORE

+VCC_GFXCORE_AXG

+1.8VS

+0.75VS

+1.05VS

OO

X

X

Address

0100 1100

0100 0001 41h

BOARD ID Table

Board ID

0

1

2

3

4

5

6

7

USB Port Table

EHCI1

EHCI2

PCB Revision

0.1

USB 2.0 Port

UHCI0

UHCI1

UHCI2

UHCI3

UHCI4

UHCI5

UHCI6

0

1

2

3

4

5

6

7

8

9

10

11

12

13

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

Vcc

R694

Board ID

0

1

2

3

SIGNAL

3.3V

100K +/- 1%

R695 V

0

12K +/- 1%

15K +/- 1%

20K +/- 1%

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

HIGH HIGH HIGH HIGH

Board ID / SKU ID Table for AD channel

AD_BID

0.347V 0.354V 0.360V

0.423V

0.541V

3 External

USB Port

USB Port (Left Side)

USB Port (Left Side)

USB3.0

USB3.0

Touch Screen

Camera

USB Port (Right Side USB-BD)

Mini Card(WLAN)

Card Reader

LOW

LOW

LOW

LOW LOW LOW LOW

min

V

AD_BID

HIGH

LOWLOWLOW

typ

HIGHHIGHHIGH

HIGH

HIGH

V

AD_BID

0 V 0 V 0 V

0.430V

0.550V

0.438V

0.559V

BOM Structure Table

VIWGP (14") 14@

VIWGR (15") 15@

LAN 10/100 8172@

LAN Switch mode SWR@

LAN LDO Mode LDO@

Camera CMOS@

HDMI HDMI@

PCH is HM76

PCH is HM70

PCH is NM70

VGA is Mars XT

VGA is Sun Pro

For VGA PX@

For VRAM and Strap

Item BOM Structure

ON

ON

ON

ON

ON

max

0x00 - 0x0B

0x0C - 0x1C

0x27 - 0x30

ON

ON

ON

OFF

OFF

EC AD

45@HDMI Logo

8162@LAN 10/100

GAS@LAN Gas tube

HM76@

HM70@

NM70@

Mars@

Sun@

X76@

ON ON

ON

OFF

OFF

OFF

MP

PVT

DVT0x1D - 0x26

EVT

LOW

OFF

OFF

OFF

For UMA Strap UMA@

MIC@Microphone

Touch Screen

SMBUS Control Table

X

XX

V

+3VS

X

Thermal

Sensor

+3VS

+3VS

B

SOURCE

SMB_EC_CK1

SMB_EC_DA1

SMB_EC_CK2

SMB_EC_DA2

4 4

PCH_SMBCLK

PCH_SMBDATA

PCH_SML0CLK

PCH_SML0DATA

SML1CLK

SML1DATA

KB9012

+3VALW

KB9012

+3VS

PCH

+3VALW

PCH

+3VALW

PCH

+3VALW

VGA BATT KB9012 SODIMM

X V

+3VALW

V

+3VGS

X

X

V

+3VGS

A

X

X

X

+3VS

WLAN

X

X

X

X

X

V

+3VS

X

V

PCH

X

V

X

XX

V

X

V

+3VALW

X

X

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

XX X

www.laptopfix.vn

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

C

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Connector ME@

Board ID for EVT

Board ID for DVT DVT@

Board ID for PVT PVT@

For USB3.0 (HM76,HM70) USB3@

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

LA-9631P

LA-9631P

LA-9631P

Date: Sheet of

Date: Sheet of

Date: Sheet of

TS@

EVT@

USB2@For USB2.0 (All PCH)

SROM@For share ROM

NOSROM@For non-share ROM

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Notes List

Notes List

Notes List

3 60Wednesday, February 27, 2013

3 60Wednesday, February 27, 2013

3 60Wednesday, February 27, 2013

E

1.0

1.0

1.0

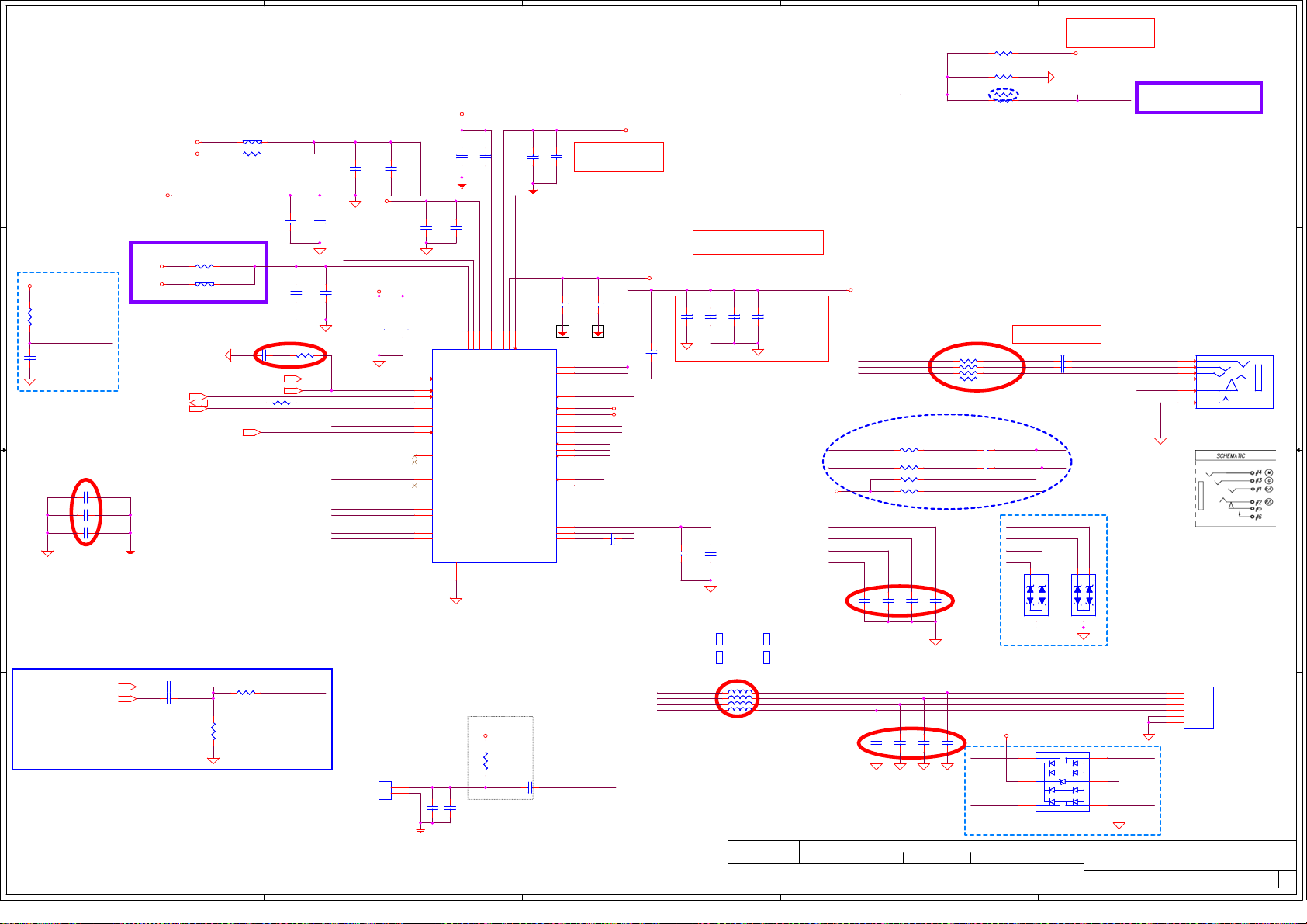

Page 4

5

4

3

2

1

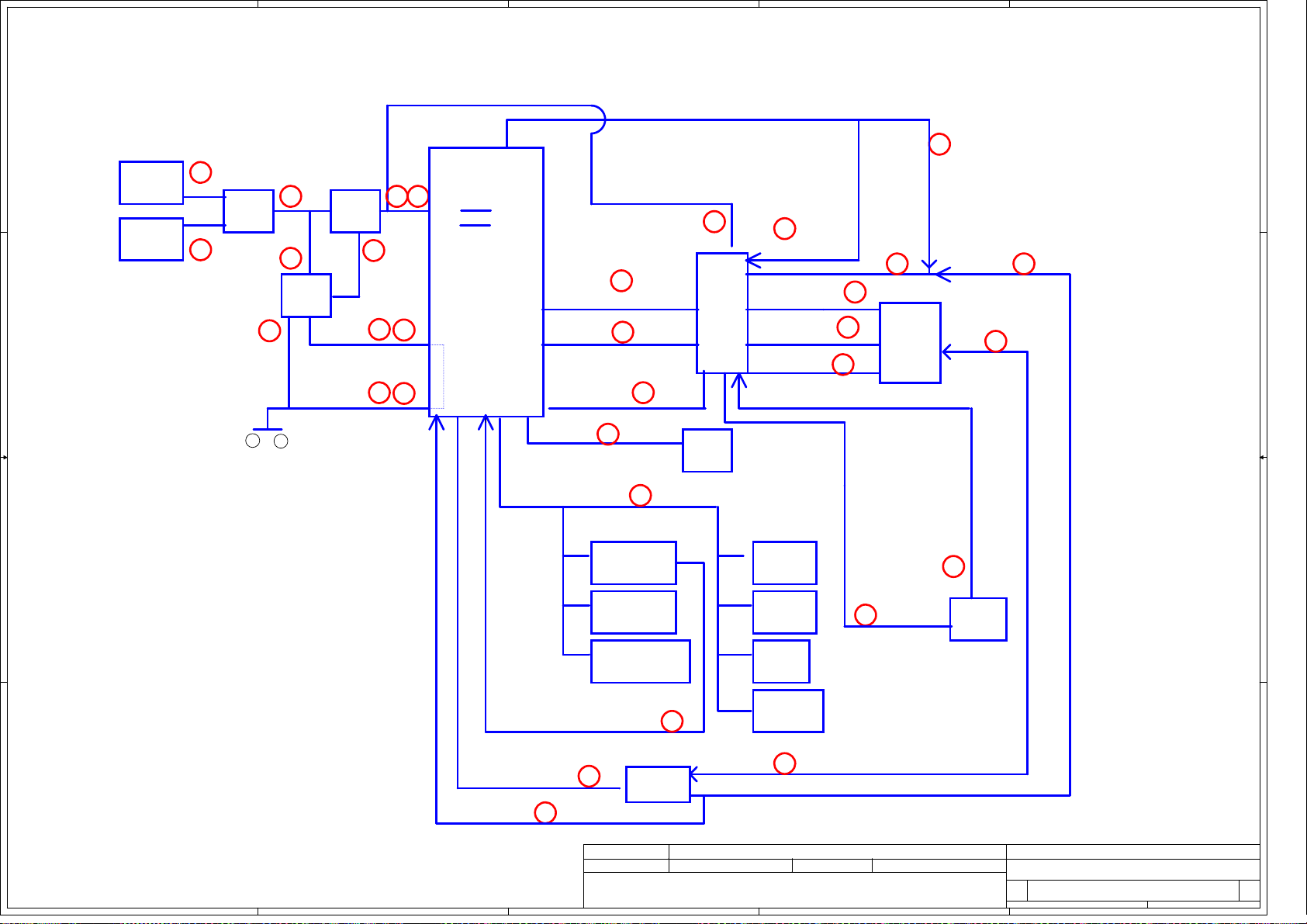

Power-Up/Down Sequence

Mars XT VRAM STRAP

Vendor

UV5, UV6, UV7, UV8

UV9, UV10, UV11, UV12

Samsung 2048Mbits

ZZZ4

D D

2GBytes

2GBytes

2GBytes

1GBytes

2GBytes 1 0 0

1GBytes

ZZZ4

ZZZ4

C C

Samsung_2G

Samsung_2G

MS2G@

MS2G@

X7646738L01

X7646738L01

SA000068U00

128Mx16 K4W2G1646E-BC1A

MS2G@

Micron 2048Mbits

ZZZ5

SA000067500

128Mx16 MT41J128M16JT-093G:K

MM2G@

Hynix 2048Mbits

ZZZ6

SA000065300

128M16 H5TQ2G63DFR-N0C

MH2G@

Samsung 1028Mbits

ZZZ7

SA00004GS00

64Mx16 K4W1G1646G-BC11

MS1G@

Hynix 2048Mbits

ZZZ15

SA00006H400

128Mx16 H5TC2G63FFR-11C

MH2GN@

Hynix 1024Mbits

ZZZ8

SA000041SB0

64Mx16 H5TQ1G63EFR-11C

MH1G@

ZZZ5

ZZZ5

Micron_2G

Micron_2G

MM2G@

MM2G@

X7646738L02

X7646738L02

ZZZ6

ZZZ6

Hynix_2G

Hynix_2G

MH2G@

MH2G@

X7646738L09

X7646738L09

ID

0

1

2

3

4

7

ZZZ15

ZZZ15

Hynix_2G

Hynix_2G

MH2GN@

MH2GN@

X7646738L10

X7646738L10

0 0

0 1 1

ZZZ7

ZZZ7

Samsung_1G

Samsung_1G

MS1G@

MS1G@

X7646738L03

X7646738L03

PS_3[ 1 ]PS_3[ 2 ]PS_3[ 3 ]

0

10 0

00 1

1 1 4.75K NC1

ZZZ8

ZZZ8

Hynix_1G

Hynix_1G

MH1G@

MH1G@

X7646738L04

X7646738L04

X76@X76@

R_pu R_pd

RV20 RV27

NC 4.75K

8.45K 2K

4.53K 2K

6.98K 4.99K

4.53K 4.99K

"Mars" has the following requirements with regards to power-supply

sequencing to avoid damaging the ASIC:

All the ASIC supplies must reach their respective nominal voltages within 20 ms

of the start of the ramp-up sequence, though a shorter ramp-up duration is

preferred. The maximum slew rate on all rails is 50 mV/µs.

The external pull ups on the DDC/AUX signals (if applicable) should ramp up

before or after both VDDC and VDD_CT have ramped up.

VDDC and VDD_CT should not ramp up simultaneously. For example, VDDC

should reach 90% before VDD_CT starts to ramp up (or vice versa).

For power down, reversing the ramp-up sequence is recommended.

VDDR3(3.3VGS)

PCIE_VDDC(0.95VGSV)

VDDR1(1.5VGS)

VDDC/VDDCI(1.12V)

VDD_CT(1.8V)

PERSTb

Sun PRO VRAM STRAP

Vendor

UV9, UV10, UV11, UV12

Samsung 4096Mbits

ZZZ9

2GBytes

2GBytes

B B

2GBytes

1GBytes

1GBytes

1GBytes

1GBytes

ZZZ9

ZZZ9

A A

Samsung_2G

Samsung_2G

SS2G@

SS2G@

X7646738L05

X7646738L05

SA000068R00

256Mx16 K4W4G1646B-HC11

SS2G@

Micron 4096Mbits

ZZZ10

SA000065D00

256Mx16/1866 MT41K256M16HA-107G:E

SM2G@

Hynix 4096Mbits

ZZZ11

SA00006DG00

256MX16 H5TQ4G63MFR-11C

SH2G@

Samsung 2048Mbits

ZZZ12

SA000068U00

128Mx16 K4W2G1646E-BC1A

SS1G@

Hynix 2048Mbits

ZZZ16

SA00006H400

128Mx16 H5TC2G63FFR-11C

SH1GN@

Micron 2048Mbits

ZZZ13

SA000067500

128Mx16 MT41J128M16JT-093G:K

SM1G@

Hynix 2048Mbits

ZZZ14

SA000065300

128M16 H5TQ2G63DFR-N0C

SH1G@

ZZZ10

ZZZ10

Micron_2G

Micron_2G

SM2G@

SM2G@

X7646738L06

X7646738L06

5

ZZZ11

ZZZ11

Hynix_2G

Hynix_2G

SH2G@

SH2G@

X7646738L11

X7646738L11

ID

0

1

2

3

4

6

7

ZZZ12

ZZZ12

Samsung_1G

Samsung_1G

SS1G@

SS1G@

X7646738L07

X7646738L07

0 0

0 1 1

1

ZZZ13

ZZZ13

Micron_1G

Micron_1G

SM1G@

SM1G@

X7646738L08

X7646738L08

4

PS_3[ 1 ]PS_3[ 2 ]PS_3[ 3 ]

0

10 0

00 1

001 4.99K4.53K

1 0

1 11

ZZZ14

ZZZ14

Hynix_1G

Hynix_1G

SH1G@

SH1G@

X7647538L01

X7647538L01

www.laptopfix.vn

X76@X76@

R_pu R_pd

RV20 RV27

NC 4.75K

8.45K 2K

4.53K 2K

6.98K 4.99K

3.4K 10K

4.75K NC

ZZZ16

ZZZ16

Hynix_1G

Hynix_1G

SH1GN@

SH1GN@

X7646738L13

X7646738L13

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

REFCLK

Straps Reset

Straps Valid

Global ASIC Reset

Issued Date

Issued Date

Issued Date

Compal Secret Data

Compal Secret Data

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

3

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

T4+16clock

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

VGA Notes List

VGA Notes List

VGA Notes List

LA-9631P

LA-9631P

LA-9631P

4 60Wednesday, February 27, 2013

4 60Wednesday, February 27, 2013

4 60Wednesday, February 27, 2013

1

1.0

1.0

1.0

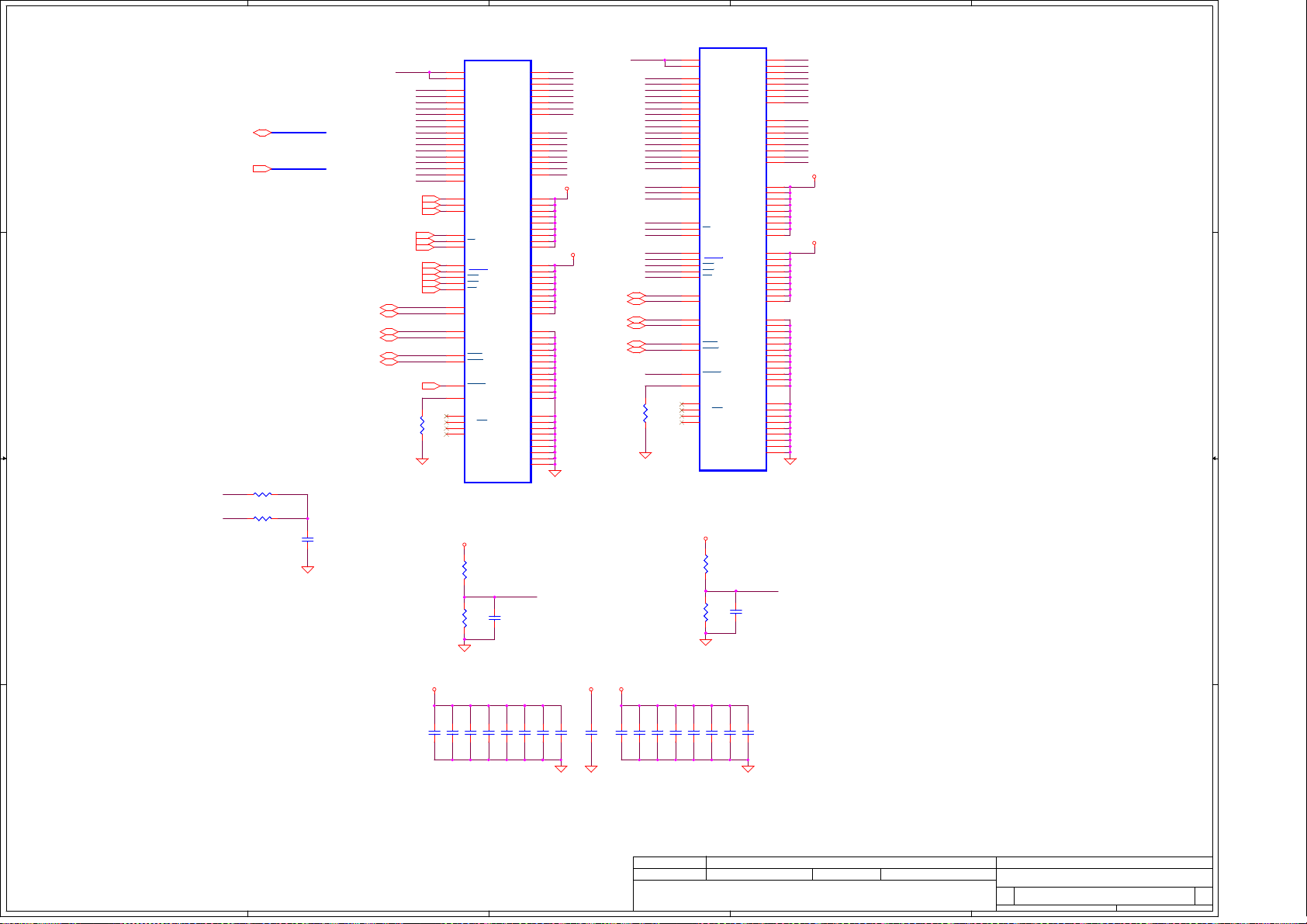

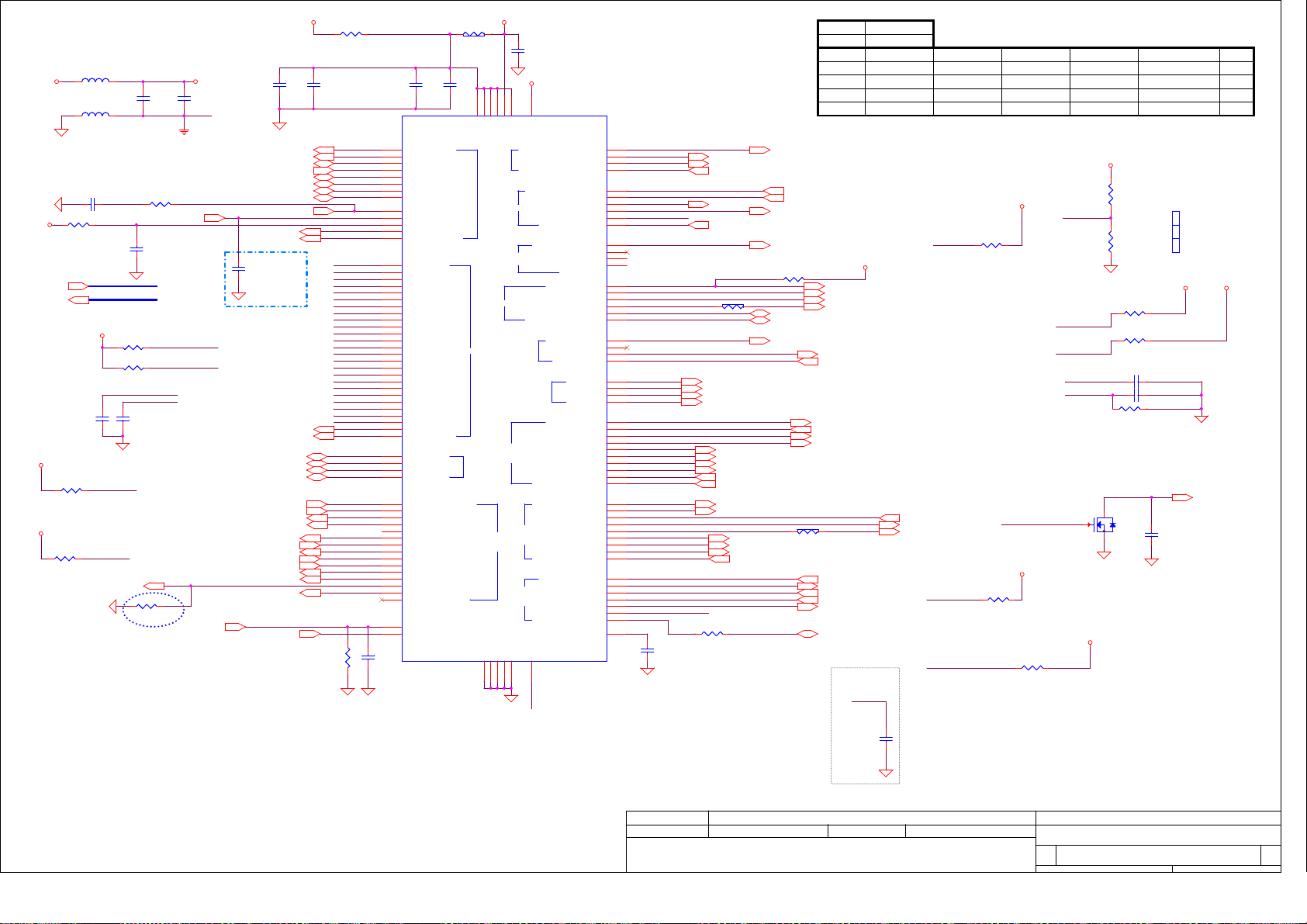

Page 5

5

ZZZ1

14@

ZZZ1

14@

14"_DIS_PCB_LA9631P

14"_DIS_PCB_LA9631P

DA6000WO000

DA6000WO000

PCB 0N1 LA-9631P REV0 M/B DIS 3

PCB 0N1 LA-9631P REV0 M/B DIS 3

D D

C C

B B

eDP_COMPIO and ICOMPO signals

should be shorted near balls

and routed with typical

impedance <25 mohms

ZZZ2

15@

ZZZ2

15@

15"_DIS_PCB_LA9631P

15"_DIS_PCB_LA9631P

DA6000WO100

DA6000WO100

PCB 0N2 LA-9631P REV0 M/B DIS 5

PCB 0N2 LA-9631P REV0 M/B DIS 5

+V1.05S_VCCP

12

R7

R7

24.9_0402_1%

24.9_0402_1%

DMI_CRX_PTX_N0<16>

DMI_CRX_PTX_N1<16>

DMI_CRX_PTX_N2<16>

DMI_CRX_PTX_N3<16>

DMI_CRX_PTX_P0<16>

DMI_CRX_PTX_P1<16>

DMI_CRX_PTX_P2<16>

DMI_CRX_PTX_P3<16>

DMI_CTX_PRX_N0<16>

DMI_CTX_PRX_N1<16>

DMI_CTX_PRX_N2<16>

DMI_CTX_PRX_N3<16>

DMI_CTX_PRX_P0<16>

DMI_CTX_PRX_P1<16>

DMI_CTX_PRX_P2<16>

DMI_CTX_PRX_P3<16>

FDI_CTX_PRX_N0<16>

FDI_CTX_PRX_N1<16>

FDI_CTX_PRX_N2<16>

FDI_CTX_PRX_N3<16>

FDI_CTX_PRX_N4<16>

FDI_CTX_PRX_N5<16>

FDI_CTX_PRX_N6<16>

FDI_CTX_PRX_N7<16>

FDI_CTX_PRX_P0<16>

FDI_CTX_PRX_P1<16>

FDI_CTX_PRX_P2<16>

FDI_CTX_PRX_P3<16>

FDI_CTX_PRX_P4<16>

FDI_CTX_PRX_P5<16>

FDI_CTX_PRX_P6<16>

FDI_CTX_PRX_P7<16>

FDI_FSYNC0<16>

FDI_FSYNC1<16>

FDI_INT<16>

FDI_LSYNC0<16>

FDI_LSYNC1<16>

EDP_COMP

eDP_HPD

4

JCPU1A

JCPU1A

B27

DMI_RX#[0]

B25

DMI_RX#[1]

A25

DMI_RX#[2]

B24

DMI_RX#[3]

B28

DMI_RX[0]

B26

DMI_RX[1]

A24

DMI_RX[2]

B23

DMI_RX[3]

G21

DMI_TX#[0]

E22

DMI_TX#[1]

F21

DMI_TX#[2]

D21

DMI_TX#[3]

G22

DMI_TX[0]

D22

DMI_TX[1]

F20

DMI_TX[2]

C21

DMI_TX[3]

A21

FDI0_TX#[0 ]

H19

FDI0_TX#[1 ]

E19

FDI0_TX#[2 ]

F18

FDI0_TX#[3 ]

B21

FDI1_TX#[0 ]

C20

FDI1_TX#[1 ]

D18

FDI1_TX#[2 ]

E17

FDI1_TX#[3 ]

A22

FDI0_TX[0]

G19

FDI0_TX[1]

E20

FDI0_TX[2]

G18

FDI0_TX[3]

B20

FDI1_TX[0]

C19

FDI1_TX[1]

D19

FDI1_TX[2]

F17

FDI1_TX[3]

J18

FDI0_FSYNC

J17

FDI1_FSYNC

H20

FDI_INT

J19

FDI0_LSYNC

H17

FDI1_LSYNC

A18

eDP_COMP IO

A17

eDP_ICOMPO

B16

eDP_HPD#

C15

eDP_AUX

D15

eDP_AUX#

C17

eDP_TX[0]

F16

eDP_TX[1]

C16

eDP_TX[2]

G15

eDP_TX[3]

C18

eDP_TX#[0 ]

E16

eDP_TX#[1 ]

D16

eDP_TX#[2 ]

F15

eDP_TX#[3 ]

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

ME@

ME@

PEG_RX[0 ]

PEG_RX[1 ]

PEG_RX[2 ]

PEG_RX[3 ]

PEG_RX[4 ]

PEG_RX[5 ]

PEG_RX[6 ]

PEG_RX[7 ]

PEG_RX[8 ]

PEG_RX[9 ]

PEG_TX[0 ]

PEG_TX[1 ]

PEG_TX[2 ]

PEG_TX[3 ]

PEG_TX[4 ]

PEG_TX[5 ]

PEG_TX[6 ]

PEG_TX[7 ]

PEG_TX[8 ]

PEG_TX[9 ]

J22

J21

H22

K33

M35

L34

J35

J32

H34

H31

G33

G30

F35

E34

E32

D33

D31

B33

C32

J33

L35

K34

H35

H32

G34

G31

F33

F30

E35

E33

F32

D34

E31

C33

B32

M29

M32

M31

L32

L29

K31

K28

J30

J28

H29

G27

E29

F27

D28

F26

E25

M28

M33

M30

L31

L28

K30

K27

J29

J27

H28

G28

E28

F28

D27

E26

D25

PEG_ICOMPI

PEG_ICOMPO

PEG_RCO MPO

PEG_RX# [0]

PEG_RX# [1]

PEG_RX# [2]

PEG_RX# [3]

PEG_RX# [4]

PEG_RX# [5]

PEG_RX# [6]

DMI

DMI

Intel(R) FDI

Intel(R) FDI

eDP

eDP

PEG_RX# [7]

PEG_RX# [8]

PEG_RX# [9]

PEG_RX# [10]

PEG_RX# [11]

PEG_RX# [12]

PEG_RX# [13]

PEG_RX# [14]

PEG_RX# [15]

PEG_RX[1 0]

PEG_RX[1 1]

PEG_RX[1 2]

PEG_RX[1 3]

PEG_RX[1 4]

PEG_RX[1 5]

PEG_TX# [0]

PEG_TX# [1]

PEG_TX# [2]

PEG_TX# [3]

PEG_TX# [4]

PEG_TX# [5]

PEG_TX# [6]

PEG_TX# [7]

PEG_TX# [8]

PEG_TX# [9]

PEG_TX# [10]

PEG_TX# [11]

PEG_TX# [12]

PCI EXPRESS* - GRAPHICS

PCI EXPRESS* - GRAPHICS

PEG_TX# [13]

PEG_TX# [14]

PEG_TX# [15]

PEG_TX[1 0]

PEG_TX[1 1]

PEG_TX[1 2]

PEG_TX[1 3]

PEG_TX[1 4]

PEG_TX[1 5]

3

PEG_COMP

PCIE_CRX_GTX_N7

PCIE_CRX_GTX_N6

PCIE_CRX_GTX_N5

PCIE_CRX_GTX_N4

PCIE_CRX_GTX_N3

PCIE_CRX_GTX_N2

PCIE_CRX_GTX_N1

PCIE_CRX_GTX_N0

PCIE_CRX_GTX_P7

PCIE_CRX_GTX_P6

PCIE_CRX_GTX_P5

PCIE_CRX_GTX_P4

PCIE_CRX_GTX_P3

PCIE_CRX_GTX_P2

PCIE_CRX_GTX_P1

PCIE_CRX_GTX_P0

PCIE_CTX_GRX_C_N7

PCIE_CTX_GRX_C_N6

PCIE_CTX_GRX_C_N5

PCIE_CTX_GRX_C_N4

PCIE_CTX_GRX_C_N3

PCIE_CTX_GRX_C_N2

PCIE_CTX_GRX_C_N1

PCIE_CTX_GRX_C_N0

PCIE_CTX_GRX_C_P7

PCIE_CTX_GRX_C_P6

PCIE_CTX_GRX_C_P5

PCIE_CTX_GRX_C_P4

PCIE_CTX_GRX_C_P3

PCIE_CTX_GRX_C_P2

PCIE_CTX_GRX_C_P1

PCIE_CTX_GRX_C_P0

PEG_ICOMPI and RCOMPO signals should be

shorted and routed

+V1.05S_VCCP

R1

R1

24.9_0402_1%

24.9_0402_1%

12

with - max length = 500 mils - typical

impedance = 43 mohms

PEG_ICOMPO signals should be routed with max length = 500 mils

- typical impedance = 14.5 mohms

PEG Static Lane Reversal - CF G2 is for the 16x

1: Normal Operation; Lane # definition matches

socket pin map definition

0:Lane Reversed

*

PCIE_CTX_GRX_N7

PCIE_CTX_GRX_N6

PCIE_CTX_GRX_N5

PCIE_CTX_GRX_N4

PCIE_CTX_GRX_N3

PCIE_CTX_GRX_N2

PCIE_CTX_GRX_N1

PCIE_CTX_GRX_N0

PCIE_CTX_GRX_P7

PCIE_CTX_GRX_P6

PCIE_CTX_GRX_P5

PCIE_CTX_GRX_P4

PCIE_CTX_GRX_P3

PCIE_CTX_GRX_P2

PCIE_CTX_GRX_P1

PCIE_CTX_GRX_P0

PCIE_CRX_GTX_N[0..7] <23>

PCIE_CRX_GTX_P[0..7] <23>

1 2

C9 0.22U_0402_10V6KPX@C9 0.22U_0402_10V6KPX@

1 2

C10 0.22U_0402_10V6KPX@C10 0.22U_0402_10V6KPX@

1 2

C11 0.22U_0402_10V6KPX@C11 0.22U_0402_10V6KPX@

1 2

C12 0.22U_0402_10V6KPX@C12 0.22U_0402_10V6KPX@

1 2

C13 0.22U_0402_10V6KPX@C13 0.22U_0402_10V6KPX@

1 2

C14 0.22U_0402_10V6KPX@C14 0.22U_0402_10V6KPX@

1 2

C15 0.22U_0402_10V6KPX@C15 0.22U_0402_10V6KPX@

1 2

C16 0.22U_0402_10V6KPX@C16 0.22U_0402_10V6KPX@

1 2

C25 0.22U_0402_10V6KPX@C25 0.22U_0402_10V6KPX@

1 2

C26 0.22U_0402_10V6KPX@C26 0.22U_0402_10V6KPX@

1 2

C27 0.22U_0402_10V6KPX@C27 0.22U_0402_10V6KPX@

1 2

C28 0.22U_0402_10V6KPX@C28 0.22U_0402_10V6KPX@

1 2

C29 0.22U_0402_10V6KPX@C29 0.22U_0402_10V6KPX@

1 2

C30 0.22U_0402_10V6KPX@C30 0.22U_0402_10V6KPX@

1 2

C31 0.22U_0402_10V6KPX@C31 0.22U_0402_10V6KPX@

1 2

C32 0.22U_0402_10V6KPX@C32 0.22U_0402_10V6KPX@

CFG2

2

PCIE_CTX_GRX_N[0..7] <23>

PCIE_CTX_GRX_P[0..15] <23>

1

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(1/7) DMI,FDI,PEG

PROCESSOR(1/7) DMI,FDI,PEG

PROCESSOR(1/7) DMI,FDI,PEG

LA-9631P

LA-9631P

LA-9631P

5 60W ednesday, February 27, 2013

5 60W ednesday, February 27, 2013

5 60W ednesday, February 27, 2013

1

1.0

1.0

1.0

www.laptopfix.vn

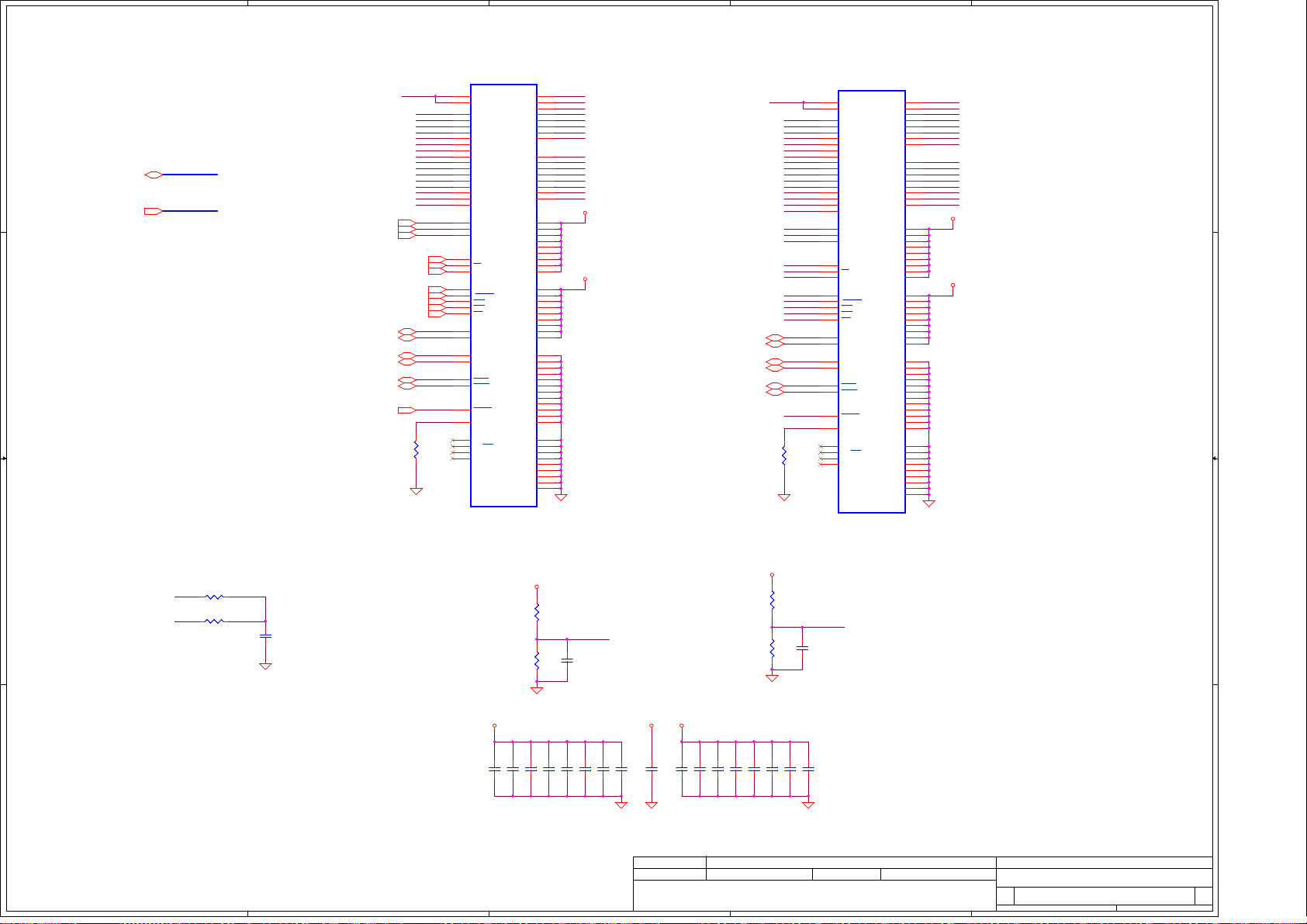

Page 6

5

D D

+V1.05S_VCCP

12

R9

R9

62_0402_5%

62_0402_5%

H_PROCHOT#<42,46,47,54>

C C

H_CPUPWRGD<19>

H_PROCHOT#

22P_0402_50V8J

22P_0402_50V8J

C549

C549

H_PM_SYNC<16>

R27

R27

1

10K_0402_5%

10K_0402_5%

1 2

2

ESD

4

JCPU1B

JCPU1B

H_SNB_IVB#<19>

T48T48

H_PECI<42>

R15

R15

56_0402_5%

56_0402_5%

1 2

H_THRMTRIP#<19>

R29

R29

1 2

130_0402_5%

130_0402_5%

H_CATERR#

H_PROCHOT#_R

PM_DRAM_PWR GD_R

BUF_CPU_RST#

C26

AN34

AL33

AN33

AL32

AN32

AM34

AP33

V8

AR33

PROC_SELECT#

SKTOCC#

CATERR#

PECI

PROCHOT#

THERMTRIP#

PM_SYNC

UNCOREPWRGOOD

SM_DRAMPWR OK

RESET#

3

BCLK

BCLK#

MISCTHERMALPWR MANAGEMENT

MISCTHERMALPWR MANAGEMENT

DPLL_REF_CLK

DPLL_REF_CLK#

CLOCKS

CLOCKS

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

DDR3

DDR3

MISC

MISC

PRDY#

PREQ#

TCK

TMS

TRST#

TDI

TDO

DBR#

BPM#[0]

BPM#[1]

JTAG & BPM

JTAG & BPM

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

A28

A27

A16

A15

R8

AK1

A5

A4

H_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

12

R12 1K_0402_5%R12 1K_0402_5%

12

R13 1K_0402_5%R13 1K_0402_5%

H_DRAMRST# <7>

12

R16 140_0402_1%R16 140_0402_ 1%

12

R17 25.5_0402_1%R17 25.5_0402_1%

12

R18 200_0402_1%R18 200_0402_ 1%

DDR3 Compe nsation S ignals

AP29

XDP_PRDY#

AP27

XDP_PREQ#

AR26

XDP_TCK

AR27

XDP_TMS

AP30

XDP_TRST#

AR28

XDP_TDI

AP26

XDP_TDO

AL35

XDP_DBRESET#

AT28

XDP_BPM#0

AR29

XDP_BPM#1

AR30

XDP_BPM#2

AT30

XDP_BPM#3

AP32

XDP_BPM#4

AR31

XDP_BPM#5

AT31

XDP_BPM#6

AR32

XDP_BPM#7

2

+V1.05S_VCCP

R28 1K_0402_5%R28 1K_0402_ 5%

12

C45

C45

47P_0402_50V8J

47P_0402_50V8J

ESD

CLK_CPU_DMI <15>

CLK_CPU_DMI# <15>

XDP_TRST#

XDP_TDI

XDP_TMS

XDP_TCK

12

51_0804_8P4R_5%

51_0804_8P4R_5%

+3VS

@

@

RP13

RP13

1

+V1.05S_VCCP

18

27

36

45

12

C46

C46

100P_0402_50V8J

100P_0402_50V8J

ESD

TYCO_2013620-2_IVY BRIDGE

+3VALW

TYCO_2013620-2_IVY BRIDGE

ME@

ME@

Buffered reset to CPU

B B

U1

U1

1 2

R161

R161

+3VS

10K_0402_5%

10K_0402_5%

PM_DRAM_PWR GD<16>

A A

5

5

1

P

B

O

2

A

G

74AHC1G09GW_TSSOP5

74AHC1G09GW_TSSOP5

3

4

PM_SYS_PWRGD_BUF

+1.5V_CPU_VDDQ

12

R30

R30

200_0402_5%

200_0402_5%

+V1.05S_VCCP

12

R32

R32

75_0402_5%

75_0402_5%

R34

R34

43_0402_1%

43_0402_1%

BUF_CPU_RST#

4

www.laptopfix.vn

1 2

BUFO_CPU_RST#

SN74LVC1G07DCKR_SC70-5

SN74LVC1G07DCKR_SC70-5

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

3

+3VS

5

U2

U2

4

1

P

NC

Y

2

PCH_PLTRST#

A

G

3

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

3V

PCH_PLTRST# <18>

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Title

Title

Title

PROCESSOR(2/7) PM,XDP,CLK

PROCESSOR(2/7) PM,XDP,CLK

PROCESSOR(2/7) PM,XDP,CLK

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-9631P

LA-9631P

LA-9631P

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

1

6 60Wednesday, February 27, 2013

6 60Wednesday, February 27, 2013

6 60Wednesday, February 27, 2013

1.0

1.0

1.0

Page 7

5

JCPU1C

JCPU1C

DDR_A_D[0..63]<12>

D D

C C

DDR_A_BS0<12>

DDR_A_BS1<12>

B B

DDR_A_BS2<12>

DDR_A_CAS#< 12>

DDR_A_RAS#< 12>

DDR_A_WE#<12>

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

G10

N10

M10

AG6

AG5

AK6

AK5

AH5

AH6

AK8

AK9

AH8

AH9

AL9

AL8

AP11

AN11

AL12

AM12

AM11

AL11

AP12

AN12

AJ14

AH14

AL15

AK15

AL14

AK14

AJ15

AH15

AE10

AF10

AE8

AD9

AF9

F10

AJ5

AJ6

AJ8

AJ9

C5

D5

D3

D2

D6

C6

C2

C3

F8

G9

F9

F7

G8

G7

K4

K5

K1

K2

M8

N8

N7

M9

N9

M7

V6

J1

J5

J4

J2

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

4

AB6

SA_CLK[0]

AA6

SA_CLK#[0]

V9

SA_CKE[0]

AA5

SA_CLK[1]

AB5

SA_CLK#[1]

V10

SA_CKE[1]

AB4

RSVD_TP[1]

AA4

RSVD_TP[2]

W9

RSVD_TP[3]

AB3

RSVD_TP[4]

AA3

RSVD_TP[5]

W10

RSVD_TP[6]

AK3

SA_CS#[0]

AL3

SA_CS#[1]

AG1

RSVD_TP[7]

AH1

RSVD_TP[8]

AH3

SA_ODT[0]

AG3

SA_ODT[1]

AG2

RSVD_TP[9]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AH2

C4

G6

J3

M6

AL6

AM8

AR12

AM15

D4

F6

K3

N6

AL5

AM9

AR11

AM14

AD10

W1

W2

W7

V3

V2

W3

W6

V1

W5

AD8

V4

W4

AF8

V5

V7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

RSVD_TP[10]

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

3

DDR_B_D[0..63]<1 3>

M_CLK_DDR0 <12>

M_CLK_DDR#0 <12 >

DDR_CKE0_DIMMA <12>

M_CLK_DDR1 <12>

M_CLK_DDR#1 <12 >

DDR_CKE1_DIMMA <12>

DDR_CS0_DIMMA# <12>

DDR_CS1_DIMMA# <12>

M_ODT0 <12>

M_ODT1 <12>

DDR_A_DQS#[0..7] <12>

DDR_A_DQS[0..7] <12>

DDR_A_MA[0..15] <12> DDR_B_MA[0..15] <13>

DDR_B_BS0<13>

DDR_B_BS1<13>

DDR_B_BS2<13>

DDR_B_CAS#<13>

DDR_B_RAS#<13>

DDR_B_WE#<13>

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

AM5

AM6

AR3

AN3

AN2

AN1

AN9

AN8

AR6

AR5

AR9

AJ11

AH11

AR8

AJ12

AH12

AT11

AN14

AR14

AT14

AT12

AN15

AR15

AT15

AA10

D10

K10

J10

M5

M4

M2

M1

AP3

AP2

AP5

AT5

AT6

AP6

AT8

AT9

AA9

AA7

AB8

AB9

C9

A7

C8

A9

A8

D9

D8

G4

F4

F1

G1

G5

F5

F2

G2

J7

J8

K9

J9

K8

K7

N4

N2

N1

N5

R6

JCPU1D

JCPU1D

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

2

AE2

SB_CLK[0]

AD2

SB_CLK#[0]

R9

SB_CKE[0]

AE1

SB_CLK[1]

AD1

SB_CLK#[1]

R10

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

AB2

AA2

T9

AA1

AB1

T10

AD3

AE3

AD6

AE6

AE4

AD4

AD5

AE5

D7

F3

K6

N3

AN5

AP9

AK12

AP15

C7

G3

J6

M3

AN6

AP8

AK11

AP14

AA8

T7

R7

T6

T2

T4

T3

R2

T5

R3

AB7

R1

T1

AB10

R5

R4

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

RSVD_TP[11]

RSVD_TP[12]

RSVD_TP[13]

RSVD_TP[14]

RSVD_TP[15]

RSVD_TP[16]

RSVD_TP[17]

RSVD_TP[18]

RSVD_TP[19]

RSVD_TP[20]

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

1

M_CLK_DDR2 <13>

M_CLK_DDR#2 <13>

DDR_CKE2_DIMMB <13>

M_CLK_DDR3 <13>

M_CLK_DDR#3 <13>

DDR_CKE3_DIMMB <13>

DDR_CS2_DIMMB# <13>

DDR_CS3_DIMMB# <13>

M_ODT2 <13>

M_ODT3 <13>

DDR_B_DQS#[0..7] <13>

DDR_B_DQS[0..7] <13>

TYCO_2013620-2_IVY BRIDGE

Deciphered Date

Deciphered Date

Deciphered Date

TYCO_2013620-2_IVY BRIDGE

ME@

ME@

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(3/7) DDRIII

PROCESSOR(3/7) DDRIII

PROCESSOR(3/7) DDRIII

LA-9631P

LA-9631P

LA-9631P

1

7 60Wednesday, February 27, 2013

7 60Wednesday, February 27, 2013

7 60Wednesday, February 27, 2013

1.0

1.0

1.0

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

ME@

ME@

D

S

D

S

13

H_DRAMRST#<6>

R39

R39

4.99K_0402_1%

4.99K_0402_1%

1 2

@

A A

DRAMRST_CNTRL_PC H<1 0,15>

5

@

1 2

R48

R48

0_0402_5%

0_0402_5%

DRAMRST_CNTRL_PC H_R

DDR3_DRAMRST#_RH_DRAMRST#

Q2

Q2

G

G

LBSS138LT1G_SOT-23-3

LBSS138LT1G_SOT-23-3

2

1

C35

C35

0.047U 16V K X7R 0402

0.047U 16V K X7R 0402

2

Eiffel used 0.01u

Module design used 0.047u

4

+1.5V

12

R37

R37

1K_0402_5%

1K_0402_5%

www.laptopfix.vn

R38

R38

1K_0402_5%

1K_0402_5%

1 2

DDR3_DRAMRST# <12,13>

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

3

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Page 8

5

4

3

2

1

CFG Straps for Processor

CFG2

12

R41

R41

1K_0402_1%

1K_0402_1%

PX@

D D

PX@

JCPU1E

JCPU1E

AK28

CFG[0]

AK29

CFG[1]

CFG2

CFG4

CFG5

CFG6

CFG7

+VCC_GFXCORE_AXG

+VCC_CORE

@

@

R252

R252

49.9_0402_1%

@

@

R255

R255

1 2

49.9_0402_1%

1 2

1 2

R82 100_0402_1%@R82 100_0402_1%@

1 2

R88 100_0402_1%@R88 100_0402_1%@

VSS_AXG_VAL_SENSE

VSS_VAL_SENSE

R257

R257

49.9_0402_1%

49.9_0402_1%

1 2

1 2

VCC_AXG_VAL_SENSE

VSS_AXG_VAL_SENSE

VCC_VAL_SENSE

VSS_VAL_SENSE

@

@

@

@

R253

R253

49.9_0402_1%

C C

B B

49.9_0402_1%

49.9_0402_1%

49.9_0402_1%

AL26

CFG[2]

AL27

CFG[3]

AK26

CFG[4]

AL29

CFG[5]

AL30

CFG[6]

AM31

CFG[7]

AM32

CFG[8]

AM30

CFG[9]

AM28

CFG[10]

AM26

CFG[11]

AN28

CFG[12]

AN31

CFG[13]

AN26

CFG[14]

AM27

CFG[15]

AK31

CFG[16]

AN29

CFG[17]

AJ31

VAXG_VAL_SENSE

AH31

VSSAXG_VAL_SENSE

AJ33

VCC_VAL_SENSE

AH33

VSS_VAL_SENSE

AJ26

RSVD5

F25

RSVD8

F24

RSVD9

F23

RSVD10

D24

RSVD11

G25

RSVD12

G24

RSVD13

E23

RSVD14

D23

RSVD15

C30

RSVD16

A31

RSVD17

B30

RSVD18

B29

RSVD19

D30

RSVD20

B31

RSVD21

A30

RSVD22

C29

RSVD23

J20

RSVD24

B18

RSVD25

J15

RSVD27

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

ME@

ME@

CFG

CFG

VCC_DIE_SENSE

VSS_DIE_SENSE

RESERVED

RESERVED

RSVD_NCTF10

RSVD_NCTF11

RSVD_NCTF12

RSVD_NCTF13

Interl request AH26 short GND

check on EVT phase

AH27

AH26

L7

RSVD28

AG7

RSVD29

AE7

RSVD30

AK2

RSVD31

W8

RSVD32

AT26

RSVD33

AM33

RSVD34

AJ27

RSVD35

T8

RSVD37

J16

RSVD38

H16

RSVD39

G16

RSVD40

RSVD51

RSVD52

BCLK_ITP

BCLK_ITP#

KEY

AR35

AT34

AT33

AP35

AR34

B34

A33

A34

B35

C35

AJ32

AK32

AN35

AM35

AT2

AT1

AR1

B1

RSVD_NCTF1

RSVD_NCTF2

RSVD_NCTF3

RSVD_NCTF4

RSVD_NCTF5

RSVD_NCTF6

RSVD_NCTF7

RSVD_NCTF8

RSVD_NCTF9

PEG Static Lane Reversal - CFG2 is for the 16x

T13PAD T13PAD

CFG2

1: Normal Operation; Lane # definition matches

socket pin map definition

0:Lane Reversed

*

CFG4

12

R42

@ R42

@

1K_0402_1%

1K_0402_1%

Display Port Presence Strap

CFG4

1 : Disabled; No Physical Display Port

attached to Embedded Display Port

*

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

CFG6

CFG5

12

12

R43

PX@ R43

PX@

1K_0402_1%

1K_0402_1%

R44

@R44

@

1K_0402_1%

1K_0402_1%

PCIE Port Bifurcation Straps

11: (Default) x16 - Device 1 functions 1 and 2 disabled

CFG[6:5]

10: x8, x8 - Device 1 function 1 enabled ; function 2

disabled

*

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

CFG7

12

R45

@R45

@

1K_0402_1%

1K_0402_1%

PEG DEFER TRAINING

1: (Default) PEG Train immediately following xxRESETB

CFG7

de assertion

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

5

4

www.laptopfix.vn

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

3

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

0: PEG Wait for BIOS for training

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(4/7) RSVD,CFG

PROCESSOR(4/7) RSVD,CFG

PROCESSOR(4/7) RSVD,CFG

LA-9631P

LA-9631P

LA-9631P

1

8 60Wednesday, February 27, 2013

8 60Wednesday, February 27, 2013

8 60Wednesday, February 27, 2013

1.0

1.0

1.0

Page 9

5

POWER

+VCC_CORE

JCPU1F

JCPU1F

POWER

QC=94A

DC=53A

D D

C C

B B

A A

AG35

AG34

AG33

AG32

AG31

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

CORE SUPPLY

CORE SUPPLY

4

8.5A

AH13

VCCIO1

AH10

VCCIO2

AG10

VCCIO3

AC10

VCCIO4

Y10

VCCIO5

U10

VCCIO6

P10

VCCIO7

L10

VCCIO8

J14

VCCIO9

J13

VCCIO10

J12

VCCIO11

J11

VCCIO12

H14

VCCIO13

H12

VCCIO14

H11

VCCIO15

G14

VCCIO16

G13

VCCIO17

G12

VCCIO18

F14

VCCIO19

F13

VCCIO20

F12

VCCIO21

F11

VCCIO22

E14

VCCIO23

E12

VCCIO24

E11

VCCIO25

D14

VCCIO26

D13

VCCIO27

D12

VCCIO28

D11

VCCIO29

C14

VCCIO30

C13

VCCIO31

VCCIO32

VCCIO33

VCCIO34

VCCIO35

VCCIO36

VCCIO37

VCCIO38

VCCIO39

VCCIO40

VIDALERT#

VIDSCLK

VIDSOUT

C12

C11

B14

B12

A14

A13

A12

A11

J23

AJ29

AJ30

AJ28

AJ35

AJ34

B10

A10

PEG AND DDR

PEG AND DDR

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

SENSE LINES SVID

SENSE LINES SVID

3

+V1.05S_VCCP

+V1.05S_VCCP

12

R46

R46

75_0402_5%

75_0402_5%

H_CPU_SVIDALRT#

1 2

R47 43_0402_5%R47 43_0402_5%

R50 130_0402_5%R 50 130_0402_5%

12

+V1.05S_VCCP

VR_SVID_CL K

0.1uF on power side

series-res istors clo se to VR

VR_SVID_ALRT# <54>

VR_SVID_CLK <54>

VR_SVID_DAT <54>

VCC_SENCE 100ohm +-1% pull-up to VCC near processor

Trace Impedance =27-33 ohm

Trace Length Matc < 25 mils

R79

R79

10_0402_1%

10_0402_1%

VCCIO_SENSE <52>

+V1.05S_VCCP

12

1 2

VSSIO_SENSEVSSIO_SENSE_L

R74

R74

10_0402_1%

10_0402_1%

R74 & R79 put together

VSSIO_SENSE_L <52>

VSS_SENCE 100ohm +-1% pull-down to GND near processor

2

+VCC_CORE

12

R51

R51

100_0402_1%

100_0402_1%

VCCSENSE <54>

R54

R54

100_0402_1%

100_0402_1%

VSSSENSE <54>

12

1

Security Classification

Security Classification

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

ME@

ME@

5

4

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

www.laptopfix.vn

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

PROCESSOR(5/7) PWR,BYPASS

PROCESSOR(5/7) PWR,BYPASS

PROCESSOR(5/7) PWR,BYPASS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-9631P

LA-9631P

LA-9631P

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

9 60Wednesday, February 27, 2013

9 60Wednesday, February 27, 2013

9 60Wednesday, February 27, 2013

1

1.0

1.0

1.0

Page 10

5

4

3

2

1

+1.5V +1.5V_CPU_VDDQ

+VREF_DQ_DIMMA

SUSP<45>

D D

C C

B B

+1.8VS

R69 0_0805_5%

R69 0_0805_5%

1 2

@

@

1

2

C130

C130

C345

C345

10U_0603_6.3V6M

10U_0603_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

1

@

@

2

B+

12

13

D

D

2

G

G

S

S

+VCC_GFXCORE_AXG

1.5A

+1.8VS_VCCPLL

C132

C132

1U_0402_6.3V6K

1U_0402_6.3V6K

1

2

DMN3030LSS-13_SOP8L-8

DMN3030LSS-13_SOP8L-8

8

7

5

R56

R56

82K_0402_5%

82K_0402_5%

RUN_ON_CPU1.5VS3

Q4

Q4

2N7002H_SOT23-3

2N7002H_SOT23-3

AT24

AT23

AT21

AT20

AT18

AT17

AR24

AR23

AR21

AR20

AR18

AR17

AP24

AP23

AP21

AP20

AP18

AP17

AN24

AN23

AN21

AN20

AN18

AN17

AM24

AM23

AM21

AM20

AM18

AM17

AL24

AL23

AL21

AL20

AL18

AL17

AK24

AK23

AK21

AK20

AK18

AK17

AJ24

AJ23

AJ21

AJ20

AJ18

AJ17

AH24

AH23

AH21

AH20

AH18

AH17

B6

A6

A2

U3

U3

JCPU1G

JCPU1G

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

VAXG37

VAXG38

VAXG39

VAXG40

VAXG41

VAXG42

VAXG43

VAXG44

VAXG45

VAXG46

VAXG47

VAXG48

VAXG49

VAXG50

VAXG51

VAXG52

VAXG53

VAXG54

VCCPLL1

VCCPLL2

VCCPLL3

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

ME@

ME@

4

1 2

12

R57

R57

330K_0402_5%

330K_0402_5%

@

@

1

2

36

R885

R885

15K_0402_1%

15K_0402_1%

AP4800

Id=9.6A

R02

1

C97

C97

0.047U_0603_25V7K

0.047U_0603_25V7K

2

POWER

POWER

SENSE

SENSE

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

VREFMISC

VREFMISC

GRAPHICS

GRAPHICS

DDR3 -1.5V RAILS

DDR3 -1.5V RAILS

SA RAIL

SA RAIL

1.8V RAIL

1.8V RAIL

VAXG_SENSE

VSSAXG_SENSE

LINES

LINES

SM_VREF

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VCCSA1

VCCSA2

VCCSA3

VCCSA4

VCCSA5

VCCSA6

VCCSA7

VCCSA8

VCCSA_SENSE

VCCSA_VID[0]

VCCSA_VID[1]

VCCIO_SEL

+VCC_GFXCORE_AXG

12

AK35

AK34

12

AL1

+V_SM_VREF_CNT

B4

+V_DDR_REFA_R

D1

+V_DDR_REFB_R

AF7

AF4

AF1

AC7

AC4

AC1

Y7

Y4

Y1

U7

U4

U1

P7

P4

P1

M27

+VCCSA

M26

L26

J26

J25

J24

H26

H25

H23

C22

C24

A19

R616

R616

10_0402_1%

10_0402_1%

R626

R626

10_0402_1%

10_0402_1%

10U_0603_6.3V6M

10U_0603_6.3V6M

1

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

2

H_VCCSA_VID0 <51>

H_VCCSA_VID1 <51>

C117

C117

C124

C124

10U_0603_6.3V6M

10U_0603_6.3V6M

1

2

+VREF_DQ_DIMMB

DRAMRST_CNTRL_PCH

LBSS138LT1G_SOT-23-3

LBSS138LT1G_SOT-23-3

M3 Circuit (Processor Generated SO-DIMM VREF_DQ)

VCC_AXG_SENSE <54>

VSS_AXG_SENSE <54>

+V_SM_VREF should

have 20 mil trace width

1

C98

C98

.1U_0402_16V7K

C125

C125

.1U_0402_16V7K

C119

C119

10U_0603_6.3V6M

10U_0603_6.3V6M

1

2

C126

C126

10U_0603_6.3V6M

10U_0603_6.3V6M

1

2

2

C120

C120

10U_0603_6.3V6M

10U_0603_6.3V6M

1

@

@

2

+VCCSA

1

+

2

2

G

G

+1.5V_CPU_VDDQ

12

R67

R67

1K_0402_1%

1K_0402_1%

12

R78

R78

1K_0402_1%

1K_0402_1%

+1.5V_CPU_VDDQ

1

C122

C122

10U_0603_6.3V6M

10U_0603_6.3V6M

1

+

+

2

2

C128

@+C128

@

330U_D2_2.5VY_R9M

330U_D2_2.5VY_R9M

+VCCSA_SENSE <51>

13

D

D

S

S

Q9

Q9

C123

C123

220U_6.3V_M

220U_6.3V_M

Q6

Q6

13

D

D

LBSS138LT1G_SOT-23-3

LBSS138LT1G_SOT-23-3

2

G

G

S

S

+V_DDR_REFA_R

+V_DDR_REFB_R

DRAMRST_CNTRL_PCH <15,7>

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

www.laptopfix.vn

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/06/15 2012/07/11

2011/06/15 2012/07/11

2011/06/15 2012/07/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

IVY Bridge drives VCCIO_SEL low

VCCP_PWRCTRL:0

Sandy Bridge is NC for A19

VCCP_PWRCTRL:1

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

Title

Title

PROCESSOR(6/7) PWR

PROCESSOR(6/7) PWR

PROCESSOR(6/7) PWR

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-9631P

LA-9631P

LA-9631P

Date: Sheet of

Date: Sheet of

Date: Sheet of

10 60Wednesday, February 27, 2013

10 60Wednesday, February 27, 2013

10 60Wednesday, February 27, 2013

1

1.0

1.0

1.0

Page 11

5

JCPU1H

JCPU1H

AT35

AT32

AT29

AT27

AT25

AT22

AT19

AT16

AT13

D D

C C

B B

A A

5

AT10

AT7

AT4

AT3

AR25

AR22

AR19

AR16

AR13

AR10

AR7

AR4

AR2

AP34

AP31

AP28

AP25

AP22

AP19

AP16

AP13

AP10

AP7

AP4

AP1

AN30

AN27

AN25

AN22

AN19

AN16

AN13

AN10

AN7

AN4

AM29

AM25

AM22

AM19

AM16

AM13

AM10

AM7

AM4

AM3

AM2

AM1

AL34

AL31

AL28

AL25

AL22

AL19

AL16

AL13

AL10

AL7

AL4

AL2

AK33

AK30

AK27

AK25

AK22

AK19

AK16

AK13

AK10

AK7

AK4

AJ25

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

ME@

ME@

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

4

AJ22

VSS81

AJ19

VSS82

AJ16

VSS83

AJ13

VSS84

AJ10

VSS85

AJ7

VSS86

AJ4

VSS87

AJ3

VSS88

AJ2

VSS89

AJ1

VSS90

AH35

VSS91

AH34

VSS92

AH32

VSS93

AH30

VSS94

AH29

VSS95

AH28

VSS96

AH25

VSS98

AH22

VSS99

AH19

VSS100

AH16

VSS101

AH7

VSS102

AH4

VSS103

AG9

VSS104

AG8

VSS105

AG4

VSS106

AF6

VSS107

AF5

VSS108

AF3

VSS109

AF2

VSS110

AE35

VSS111

AE34

VSS112

AE33

VSS113

AE32

VSS114

AE31

VSS115

AE30

VSS116

AE29

VSS117

AE28

VSS118

VSS

VSS

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS