Page 1

COMPAL CONFIDENTIAL

MODEL NAME : 888L2(SOLANO2-M)

Date: 01/11/01

Version: 2.0

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

Title

Size Document Number Rev

Date: Sheet of

Compal Electronics, Inc.

Cover Sheet

888L2 Main Board

1 42Thursday, January 11, 2001

2.0

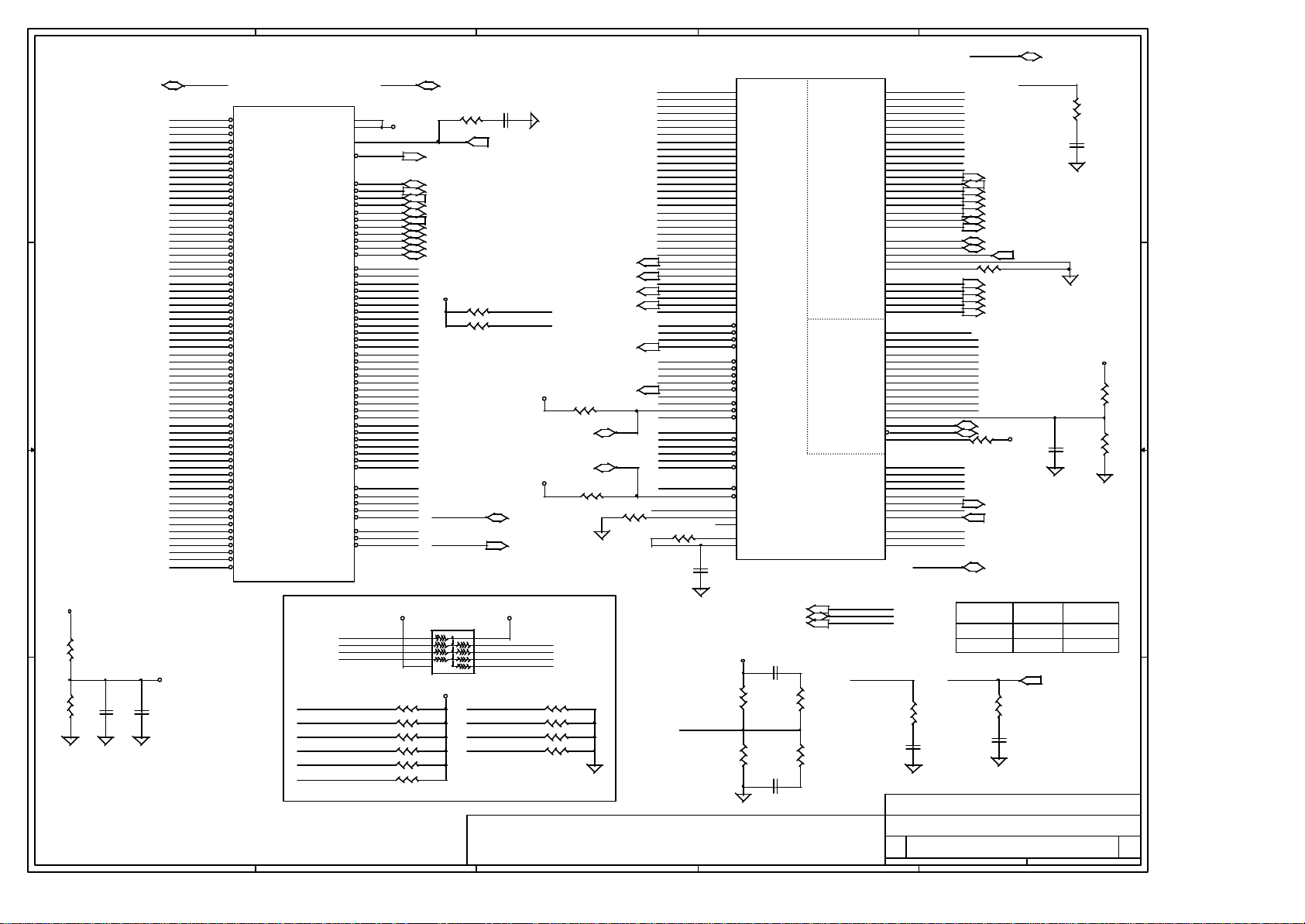

Page 2

MODEL NAME : 888L2 (SOLANO2-M)

LCD/INV. CONN.

DISPLAY CACHE CONN. & ITP

CARD-BUS

CONTROLLER

OZ 6933T

IDSEL: AD19

PIRQA#, PIRQC#

PCCARD

POWER

PAGE 20 PAGE 20

PAGE 12

LVDS

CRT CONN.

VCH

MINI_PCI CONN

MODEM/LAN

IDSEL: AD27, AD28

PAGE 19 PAGE 29

CARDBUS

SLOT 1/2

PIRQB#, PIRQD#

RJ11 RJ45

PAGE 12

PAGE 13

Sub board

PAGE 13

DVO/Vlink

PCI BUS

AC_LINK1/LAN

FWH

UPGA2

Socket

FSB BUS

GMCH2-M

IDSEL: AD11

HOST-HUB BRIDGE

IDSEL: AD13

INTERNAL GFX

PAGE 7,8,9 PAGE 10

BUS#0, DEV#30, DEV#31:

HUB, LPC, IDE, USB, SMBUS,

AC'97

BUS#1, DEV#8:

INTERNAL LAN CONTROLLER

PAGE 14

ICH2-M

LPC BUS

Decoupling

CapacitorS

PAGE 4,5,6 PAGE 6

MEMORY BUS

SODIMM 0

SODIMM 1

HUB_ILNK

PAGE 14,15,16

AC_LINK0

HDD CONN.

SECOND MODULE

CD-ROM

CONN.

USB CONN.

AMP & AC97

CODEC

CONN.

PAGE 17

PAGE 17

PAGE 17

PAGE 18

PAGE 27

CLOCK

CIRCUIT

PAGE 11

DC/DC

CIRCUIT

PAGE 30-34

PAGE 22

PAGE 25

PAGE 23

KB BIOS

RTC BATT &

ON/OFF BTN

INT KBD

PS/2

KEYBOARD &

MOUSE CONN.

NS PC87570EXT

KBD

T-PAD

CONN.

SUSPEND

CKT

PAGE 26PAGE 23PAGE 25

NS PC87393

X Bus

LPC-TO-X Bus

& S/IO

PAGE 21PAGE 22

SIO

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

PIO

FDD.

PAGE 17PAGE 24PAGE 24

Head

Phone

PAGE 28 PAGE 28 PAGE 28

MicLine in

Title

Size Document Number Rev

Date: Sheet of

Compal Electronics, Inc.

System Block Diagram

888L2 Main Board

2 42Thursday, January 11, 2001

2.0

Page 3

Revision History

# Description Version

Date

1

2 2000/9/20 Second Release

3 2000/11/3 Third Release

4 2000/12/27 Fouth Release

5 2001/01/11 2.0fifth release (QT)

First Release 0.12000/7/21

(EVT-SST)

(DVT1-PT1)

(DVT2-PT2)

(ST)

0.2A

0.2C1

1B

Chip information

GMCH2-M FW82815EM

Version S-spec. Q-spec.

A0

A1

SL4MP

ICH2-M FW82801BAM

Version S-spec. Q-spec.

A0

B0

B1

SL45HQ

SL4HN

B2 QA56, QA57

VCH FW82807AA

Version S-spec. Q-spec.

A0 Q989

A1 QA76

A2 QB41ES

QA38

QA75

Q908, Q909, Q910, Q911, Q912

Q967, Q968

QA36, QA37

EVT

(SST)

GMCH2-M QA38ES (A0)

Q967ES (B0)ICH2-M

VCH Q989ES (A0)

DVT1

(PT1)

GMCH2-M

ICH2-M

VCH

DVT2 (PT2)

QA75ES (A1)

QA57ES (B2)

Q076ES (A1)

ST

GMCH2-M

ICH2-M

VCH

QT same as ST

A1

B2

A2

Title

Revision History

Size Document Number Rev

888L2 Main Board

Date: Sheet of

Compal Electronics, Inc.

3 42Thursday, January 11, 2001

2.0

Page 4

A

HA#[3..31]<7>

+CPU_IO

4 4

3 3

2 2

1 1

R243 56.2_1%1 2

R42 1.5K1 2

R107 1501 2

R106 1501 2

R44 1.5K

R293 1.5K12

+CPU_IO

BSEL0

+CPU_IO

BSEL1

+2_5V_CLK

RP32 8P4R-1.5K1 8

+CPU_IO

R100 1.5K12

R101 56.2_1%12

BSEL[1:0] STSEM BUS FREQUENCY

00

*

01

10

11

12

R26

10K_0402

1 2

R105

@10K_0402

1 2

12

R104

100_0402

R210 1.5K

2 7

3 6

4 5

66MHZ

100MHZ

RESERVED

133MHZ

A

CPURST#

FLUSH#

PICD0_CPU

PICD1_CPU

FERR#

RCPUSLP#

CPU_PWRGD<14>

12

STPCLK#<14>

HREQ#0<7>

HREQ#1<7>

HREQ#2<7>

HREQ#3<7>

HREQ#4<7>

BPRI#<7>

BNR#<7>

HLOCK#<7>

HITM#<7>

DEFER#<7>

HTRDY#<7>

A20M#<14>

FERR#<14>

IGNNE#<14>

INTR<14>

NMI<14>

HA#[3..31]

HA#3

L3

HA#4

K3

HA#5

J2

HA#6

L4

HA#7

L1

HA#8

K5

HA#9

K1

HA#10

J1

HA#11

J3

HA#12

K4

HA#13 HD#10

G1

HA#14

H1

HA#15

E4

HA#16

F1

HA#17

F4

HA#18

F2

HA#19

E1

HA#20

C4

HA#21

D3

HA#22

D1

HA#23

E2

HA#24

D5

HA#25

D4

HA#26

C3

HA#27

C1

HA#28

B3

HA#29

A3

HA#30

B2

HA#31

C2

A4

A5

B4

C5

T2

V4

V2

W3

W5

W2

ADS#<7>

HIT#<7>

RS#0<7>

RS#1<7>

RS#2<7>

FERR#

SMI#<14>

ITP_TDO

ITP_TDI

ITP_TMS

ITP_TRST#

ITP_TCK

ITP_PREQ#

GTL_PRDY#

BSEL0

BSEL1

RCPUSLP#

THERMDA

THERMDC

AB2

AA1

AB1

Y2

E6

V21

AD9

R21710_0402 12

C6

U4

T4

R1

V1

Y4

U3

AA21

Y21

W21

W19

U2

U1

AA2

W1

Y1

AD10

AC12

AC13

V5

AB10

AC15

AD13

AD14

AA14

AA11

AB20

W20

AA12

AB15

AB18

AC19

AC11

AB12

AA15

AB16

COPPERMINE

ITP_TDO<13>

ITP_TDI<13>

ITP_TMS<13>

ITP_TRST#<13>

ITP_TCK<13>

ITP_PREQ#<13>

GTL_PRDY#<13>

U5A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

RP#

ADS#

AERR#

AP0#

AP1#

BERR#

BINIT#

IERR#

BREQ0#

BPRI#

BNR#

LOCK#

HIT#

HITM#

DEFER#

BP2#

BP3#

BPM0#

BPM1#

TRDY#

RS0#

RS1#

RS2#

RSP#

A20M#

FERR#

IGNNE#

PWRGOOD

SMI#

TDO

TDI

TMS

TRST#

TCK

PREQ#

PRDY#

BSEL0

BSEL1

INTR/LINT0

NMI/LINT1

STPCLK#

SLP#

THERMDA

THERMDC

B

REQUEST

PHASE

SIGNALS

ERROR

SIGNALS

ARBITRATION

PHASE

SIGNALS

SNOOP PHASE

SIGNALS

RESPONSE

PHASE

SIGNALS

PC

COMPATIBILITY

SIGNALS

DIAGNOSTIC

& TEST

SIGNALS

EXECUTION

CONTROL

SIGNALS

THERMAL DIODE

ITP_TDO

ITP_TDI

ITP_TMS

ITP_TRST#

ITP_TCK

ITP_PREQ#

GTL_PRDY#

B

COPPERMINE

DATA

PHASE

SIGNALS

C

HD[0..63]

HD#0

D10

D0#

HD#1

D11

D1#

HD#2

C7

D2#

HD#3

C8

D3#

HD#4

B9

D4#

HD#5

A9

D5#

HD#6

C10

D6#

HD#7

B11

D7#

HD#8

C12

D8#

HD#9

B13

D9#

A14

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DEP0#

DEP1#

DEP2#

DEP3#

DEP4#

DEP5#

DEP6#

DEP7#

DBSY#

DRDY#

PICCLK

PICD1

PICD0

FLUSH#

RESET#

BCLK

EDGCTRLN

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

INIT#

HD#11

B12

HD#12

E12

HD#13

B16

HD#14

A13

HD#15

D13

HD#16

D15

HD#17

D12

HD#18

B14

HD#19

E14

HD#20

C13

HD#21

A19

HD#22

B17

HD#23

A18

HD#24

C17

HD#25

D17

HD#26

C18

HD#27

B19

HD#28

D18

HD#29

B20

HD#30

A20

HD#31

B21

HD#32

D19

HD#33

C21

HD#34

E18

HD#35

C20

HD#36

F19

HD#37

D20

HD#38

D21

HD#39

H18

HD#40

F18

HD#41

J18

HD#42

F21

HD#43

E20

HD#44

H19

HD#45

E21

HD#46

J20

HD#47

H21

HD#48

L18

HD#49

G20

HD#50

P18

HD#51

G21

HD#52

K18

HD#53

K21

HD#54

M18

HD#55

L21

HD#56

R19

HD#57

K19

HD#58

T20

HD#59

J21

HD#60

L20

HD#61

M19

HD#62

U18

HD#63

R18

V20

T21

U21

R21

V18

P21

P20

U19

AA3

T1

R102 @33_040212C97 @15PF

AA18

PICD1_CPU

Y20

PICD0_CPU

AB21

AA10

FLUSH#

AC9

CPURST#

A6

M3

AA16

R261

110_1%

R214

@33_0402

1 2

12

C209

1 2

@15PF

C

R103 0_040212

R99 0_040212

VCH_VID0

VCH_VID1

VCH_VID2

VCH_VID3

VCH_VID4

DBSY# <7>

DRDY# <7>

INIT# <14>

CPURST# <7,13>

CLK_HOST_CPU <11>

1 2

HD#[0..63] <7>

RP42

8P4R-0

1 8

2 7

3 6

4 5

1 2

@0_0402

1K_0402

R429

R19

@1K_0402

PICD1

PICD0

1 2

1 2

1 2

R18

R22

1K_0402

D

+3VS

RP40

8P4R-10K

1 8

2 7

3 6

4 5

1 2

R30 @10K

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3 VID3

CPU_VID4

R_VID0

R_VID1

R_VID2

R_VID3

R_VID4

R24

1K_0402

1 2

1 2

R27

1K_0402

+3VS

U4

4 5

8 9

14 15

18 19

22 23

1

SN74CBT3383

* 900MHZ

* 850MHZ

*

+3VS

R245 10K_0402

12

C312

2200PF

D

+3VS

C310

.1UF

1 2

THERMDA

THERMDC

1 2

1 2

R258 1K_0402

CLK_APIC_CPU <11>

PICD1 <14>

PICD0 <14>

E

RP41

8P4R-1K

1 8

2 7

3 6

4 5

1 2

R20 1K

VR_HI/LO#

CPU_VID[0..4]

VCH_VID[0..4]

VID[0..4]

C0A0

C1A1

C2A2

C3A3

C4A4

VCC

GNDBX

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

23

67

1011

1617

2021

24

1213

VR_HI/LO# <15,30>

+3VS

B0 D0

B1 D1

B2 D2

B3 D3

B4 D4

BE#

VID[4:0] CPU VCC

00000

00001

00010

00011

00100

00101

00110

00111

01000

01001

01010

01011

01100

01101

01110

01111

1 2

R246 1K_0402

Title

Size Document Number Rev

Date: Sheet of

2.00

1.95

1.90

1.85

1.80

1.75

1.70

1.65

1.60

1.55

1.50

1.45

1.40

1.35

1.30

NO CPU

2

15

NC

NC

STBY#

NC

NC

ALERT#

DXP

DXNNCADD1

ADD0

678910

VCC

SMBC

SMBD

U20MAX1617A

16

13

5

1

3

4

Compal Electronics, Inc.

COPPERMINE-A

888L2 Main Board

GND

GND

CPU_VID[0..4] <5>

VCH_VID[0..4] <12>

VID[0..4] <30>

VID0

VID1

VID2

VID4

+5VS

12

C22

.1UF

VID[4:0] CPU VCC

10000 1.275

10001

10010

10011

10100

10101

10110

10111

11000

11001

11010

11011

11100

11101

11110

11111

14

SMB_EC_CK1 <12,22,23,31>

12

SMB_EC_DA1 <12,22,23,31>

11

Address: 1001_110x

E

1.250

1.225

1.200

1.175

1.150

1.125

1.100

1.075

1.050

1.025

1.000

0.975

0.950

0.925

NO CPU

4 42Thursday, January 11, 2001

2.0

Page 5

A

1 2

+CPU_IO

L47

Murata LQG21N4R7K10

10UF_10V_1206

+GTLREF

4 4

3 3

+2_5V_CLK

C194

.1UF

1 2

2 2

1 1

1K_1%

1 2

R209

1.5K_1%

R215

+CPU_IO

12

+GTLREF

C336

.1UF

12

C208

.1UF

12

C32

12

C217

.1UF

IST_CPU_PERF#<15>

R262

A

12

C339

.1UF

1.5K

C34

.1UF

12

C35

22UF_10V_1206

12

C250

.1UF

+2_5V_CLK

R25

2K_1%

1 2

R28

2K_1%

1 2

12

+VCCT_VCCA

+VCCT_VSSA

12

C263

.1UF

+CPU_CORE

R96

56.2_1%

1 2

12

C205

.1UF

+CMOSREF

+TESTHI

TESTLO1

1 2

C202

.1UF

+CLKREF

R29

1K_0402

12

TESTLO2

R23

1K_0402

1 2

L2

M2

E5

E16

E17

F5

F17

U5

Y17

Y18

H8

H10

H12

H14

H16

J7

J9

J11

J13

J15

K8

K10

K12

K14

K16

L7

L9

L11

L13

L15

M8

M10

M12

M14

M16

N7

N9

N11

N13

N15

P8

P10

P12

P14

P16

R7

R9

R11

R13

R15

T8

T10

T12

T14

T16

U7

U9

U11

U13

U15

AB19

P2

AA9

AD18

R2

AD19

AD17

Y5

N5

AD20

H4

AA17

G4

COPPERMINE

U5B

VCCA

VSSA

VREF0

VREF1

VREF2

VREF3

VREF4

VREF5

VREF6

VREF7

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

RSVD

CLKREF

CMOSREF1

CMOSREF2

GHI#

RTTIMPEDP

TESTHI

TESTLO1

TESTLO2

TESTP1

TESTP2

TESTP3

TESTP4

B

PLL ANALOG VOLTAGE

COPPERMINE

POWER,

GROUND,

RESERVED

SIGNALS

B

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

C

A2

A7

A8

A12

A21

B1

B5

B6

B7

B8

B10

B15

B18

C9

C11

C15

C16

C19

D2

D6

D7

D9

E3

E7

E8

E9

E10

E11

E13

E19

F3

F6

F7

F8

F9

F10

F11

F12

F13

F14

F15

F16

F20

G3

G19

H2

H7

H9

H11

H13

H15

H20

J4

J8

J10

J12

J14

J16

J19

K2

K7

K9

K11

K13

K15

K20

L5

L8

L10

L12

L14

L16

L19

M7

M9

M11

M13

M15

M20

N2

N3

N4

N8

N10

N12

N14

N16

N18

N19

N20

P5

P7

P9

P11

P13

P15

P19

R3

R4

R5

R8

R10

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

+CPU_IO

+CPU_CORE

CPU_VID0<4>

CPU_VID1<4>

CPU_VID2<4>

CPU_VID3<4>

CPU_VID4<4>

C

U5C

G6

VCCT0

G7

VCCT1

G8

VCCT2

G9

VCCT3

G10

VCCT4

G11

VCCT5

G12

VCCT6

G13

VCCT7

G14

VCCT8

G15

VCCT9

G16

VCCT10

G17

VCCT11

H6

VCCT12

VCCT13

VCCT14

VCCT15

VCCT16

VCCT17

VCCT18

VCCT19

VCCT20

VCCT21

VCCT22

VCCT23

VCCT24

VCCT25

VCCT26

VCCT27

VCCT28

VCCT29

VCCT30

VCCT31

VCCT32

VCCT33

VCCT34

VCCT35

VCCT36

VCCT37

VCCT38

VCCT39

VCCT40

VCCT41

VCCT42

VCCT43

VCCT44

VCCT45

VCCT46

VCCT47

VCCT48

VCCT49

VCCT50

VCCT51

VCCT52

VCCT53

VCCT54

VCCT55

VCCT56

VCCT57

VCCT58

VCCT59

VCCT60

VCCT61

VCCT62

VCCT63

VCCT64

VCCT65

VCCT66

VCCT67

VCCT68

VCCT69

VCCT70

VCCT71

VID0

VID1

VID2

VID3

VID4

COPPERMINE

POWER, GROUND AND NC

H17

J6

J17

K6

K17

L6

L17

M6

M17

N6

N17

P1

P6

P17

R6

R17

T6

T17

U6

U17

V6

V7

V8

V9

V10

V11

V12

V13

V14

V15

V16

V17

W6

W7

W8

W9

W10

W11

W12

W13

W14

W15

W16

W17

Y6

Y7

Y8

AA6

AA7

AA8

AB6

AB7

AB8

AC6

AC7

AC8

AD6

AD7

AD8

AD2

AD3

AD4

AC4

AB4

COPPERMINE

uPGA2 and uBGA2 PIN P1:

for low voltage Cumine CPU: connect to +CPU_CORE, only uBGA2 package.

for normal Cumine CPU: connect to +CPU_IO.

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS159

VSS160

VSS161

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

D

R12

R14

R16

R20

T3

T5

T7

T9

T11

T13

T15

T18

T19

U8

U10

U12

U14

U16

U20

V3

V19

W4

W18

Y3

Y9

Y10

Y11

Y12

Y13

Y14

Y15

Y16

Y19

AA4

AA13

AA20

AB3

AB5

AB9

AB11

AB13

AB14

AB17

AC1

AC2

AC5

AC10

AC14

AC16

AC18

AC21

AD1

AD5

AD16

AD21

A15

A16

A17

C14

D8

D14

D16

E15

G2

G5

G18

H3

H5

J5

M4

M5

P3

P4

AA5

AA19

AC3

AC17

AC20

AD15

D

E

Title

Size Document Number Rev

Date: Sheet of

Compal Electronics, Inc.

COPPERMINE-B

888L2 Main Board

5 42Thursday, January 11, 2001

E

2.0

Page 6

A

4 4

B

C

D

E

12

C289

.1UF_0402

12

C304

.1UF_0402

+CPU_CORE +CPU_CORE+CPU_CORE

12

+ C110

+CPU_CORE

12

+

220UF_D_4V

6.3V

C185

220UF_D_4V

6.3V

12

+ C113

12

+

220UF_D_4V

6.3V

C427

220UF_D_4V

6.3V

+CPU_IO

+CPU_IO

12

C251

.1UF_0402

12

C299

.1UF_0402

12

+ C105

12

+

220UF_D_4V

6.3V

C183

220UF_D_4V

6.3V

12

C286

.1UF_0402

12

C337

.1UF_0402

12

12

12

C300

.1UF_0402

12

C256

.1UF_0402

+ C271

220UF_D_4V

6.3V

C296

+

220UF_D_4V

6.3V

12

C273

.1UF_0402

12

C272

.1UF_0402

12

+ C33

+CPU_CORE

12

+

12

C309

.1UF_0402

12

C192

.1UF_0402

220UF_D_4V

6.3V

C420

220UF_D_4V

6.3V

12

C285

.1UF_0402

12

C249

.1UF_0402

12

+ C321

12

+

12

C311

12

C55

220UF_D_4V

6.3V

C409

220UF_D_4V

6.3V

.1UF_0402

1UF

12

C342

.1UF_0402

12

C182

1UF

12

+ C386

12

+

220UF_D_4V

6.3V

C406

220UF_D_4V

6.3V

12

C343

.1UF_0402

12

+ C188

220UF_D_4V

12

12

12

C344

.1UF_0402

+ C184

220UF_D_4V

6.3V

C173

+

220UF_D_4V

6.3V

+CPU_CORE

12

12

C334

10PF

C332

10PF

12

C353

10PF

12

C381

10PF

12

C422

.1UF

12

C100

.1UF

12

C31

.1UF

C101

C99

.1UF

.1UF

12

12

+CPU_CORE +CPU_CORE

12

12

C345

3 3

C392

1UF

1UF

12

C391

12

C237

1UF

1UF

12

12

C36

.1UF

C423

.1UF

12

C244

.1UF

12

C102

.1UF

12

C103

.1UF

+CPU_CORE

12

C267

.1UF_0402

12

C268

.1UF_0402

12

C278

.1UF_0402

12

C277

.1UF_0402

12

C276

.1UF_0402

12

C279

.1UF_0402

12

C292

.1UF_0402

12

C291

.1UF_0402

12

C290

.1UF_0402

+CPU_CORE

12

C275

.1UF_0402

2 2

12

C305

.1UF_0402

12

C303

.1UF_0402

12

C293

.1UF_0402

12

C265

.1UF_0402

12

C266

.1UF_0402

12

C269

.1UF_0402

12

C301

.1UF_0402

12

C302

.1UF_0402

+CPU_CORE

12

C316

.1UF_0402

12

C320

.1UF_0402

12

C319

.1UF_0402

12

C328

.1UF_0402

12

C330

.1UF_0402

12

C315

.1UF_0402

12

C318

.1UF_0402

12

12

C421

.1UF

12

C329

.1UF_0402

C98

.1UF

+CPU_CORE

12

12

C505

C504

1 1

1UF

1UF

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Size Document Number Rev

Date: Sheet of

Compal Electronics, Inc.

CPU BYPASS

888L2 Main Board

E

6 42Thursday, January 11, 2001

2.0

Page 7

5

HD#[0..63]<4>

D D

C C

B B

+CPU_IO

12

R299

1K_1%

12

R314

2K_1%

C424

.1UF

A A

HD#[0..63]

U7A

HD#0

AA1

AD11

AD10

AF12

AB11

AB10

AC10

AF10

AD14

AD12

AB12

AE11

AE15

AF11

AF13

AB14

AF14

AB13

AB15

AE13

AC14

AD13

AD15

AF16

AF15

AC12

HD#0

AB2

HD#1

AF2

HD#2

AD4

HD#3

AB1

HD#4

AB3

HD#5

AA3

HD#6

AC4

HD#7

AC1

HD#8

AF3

HD#9

AD1

HD#10

AE3

HD#11

AD2

HD#12

AD3

HD#13

AF1

HD#14

AA4

HD#15

AD6

HD#16

AC3

HD#17

AE1

HD#18

AB6

HD#19

AF4

HD#20

AE5

HD#21

AC8

HD#22

AB5

HD#23

AF5

HD#24

AC6

HD#25

AF6

AF8

AD8

AD5

AB7

AF7

AD7

AB8

AE7

AE9

AB9

AF9

AD9

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

GMCH2v0

HOST

VGA_LMD28

VGA_LDQM3

VGA_LMD29

AGP_ADSTB0

AGP_ADSTB1

AGP_SBSTB

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

+GTLREF

C400

.1UF

5

4

HA#[3..31]

U6

GTLREFA

AA10

GTLREFB

AA7

HCLKIN

H3

RSTIN#

AA5

CPURST#

L4

HLOCK#

M3

DEFER#

G1

ADS#

N4

BNR#

M5

BPRI#

J3

DBSY#

J1

DRDY#

K1

HIT#

L3

HITM#

K3

HTRDY#

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

RS#0

RS#1

RS#2

HA#3

R4

HA#4

P1

HA#5

T2

HA#6

R3

HA#7

N5

HA#8

P5

HA#9

R1

HA#10

U1

HA#11

P2

HA#12

T1

HA#13

T3

HA#14

P3

HA#15

T5

HA#16

R5

HA#17

V5

HA#18

Y2

HA#19

V3

HA#20

W1

HA#21

U4

HA#22

V2

HA#23

W3

HA#24

W4

HA#25

U5

HA#26

Y5

HA#27

Y3

HA#28

U3

HA#29

Y1

HA#30

W5

HA#31

V1

HREQ#0

M1

HREQ#1

N1

HREQ#2

M2

HREQ#3

L5

HREQ#4

N3

RS#0

K2

RS#1

L1

RS#2

H1

For external AGP bus pull up/down resistors.

VGA_LMA7

VGA_LMD11 VGA_LCS#

VGA_LMD12

VGA_LMD30 VGA_LMD24

1 2

R391 8.2K_0402

1 2

R393 8.2K_0402

1 2

R395 8.2K_0402

1 2

R397 8.2K_0402

1 2

R399 8.2K_0402

1 2

R400 8.2K_0402

4

HA#[3..31] <4>

@33_0402

1 2

+GTLREF

PCIRST# <12,14,19,21,29>

CPURST# <4,13>

HLOCK# <4>

DEFER# <4>

ADS# <4>

BNR# <4>

BPRI# <4>

DBSY# <4>

DRDY# <4>

HIT# <4>

HITM# <4>

HTRDY# <4>

+3VS

+3VS +3VS

RP38

1

2

3

4

5

10P8R-8.2K

+3VS

C408 @18PFR296

CLK_HOST_GMCH <11>

1 2

R195 10K_0402

1 2

R204 10K_0402

HREQ#[0..4]

RS#[0..2]

10

9

VGA_LMA10

8

7

6

AGP_ADSTB#0

AGP_ADSTB#1

AGP_SBSTB#

VGA_LMA6

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

LTVDA

LTVCL

HREQ#[0..4] <4>

RS#[0..2] <4>

VGA_LMD27

R392 8.2K_0402

R394 8.2K_0402

R396 8.2K_0402

R398 100K_0402

+3VS

1 2

R255 4.7K_0402

GMBSDA<12>

GMBSCL<12>

+3VS

R79 4.7K_0402

1 2

1 2

1 2

1 2

3

VGA_LCKE<13>

VGA_LCAS#<13>

VGA_LTCLK1<13>

VGA_LTCLK0<13>

VGA_LRAS#<13>

VGA_LCS#<13>

1 2

1 2

R73 36.5_1%

R265

Place 10 ohm within 0.5" of

GMCH ball 'R22' and route

trace 1.5" to ball 'P22'

3

VGA_LDQM0

VGA_LMD4

VGA_LMD7

VGA_LMD3

VGA_LMD6

VGA_LMD2

VGA_LMD5

VGA_LMD1

VGA_LMD0

VGA_LMA4

VGA_LDQM1

VGA_LMA2

VGA_LMD8

VGA_LMA5

VGA_LMD9

VGA_LMA1

VGA_LMA8

VGA_LMD14

VGA_LMA11

VGA_LMD15

VGA_LMA9

VGA_LMD16

VGA_LMA0

VGA_LMD17

VGA_LCKE

VGA_LMD18

VGA_LCAS#

VGA_LMD19

VGA_LTCLK1

VGA_LMD20

VGA_LTCLK0

VGA_LMD21

VGA_LMA3

VGA_LMD10

VGA_LMD13

VGA_LRAS#

VGA_LMA10

VGA_LMD11

VGA_LMD12

VGA_LMA7

VGA_LCS#

VGA_LMA6

VGA_LMD27

VGA_LMD24

AGP_ADSTB0

AGP_ADSTB#0

AGP_ADSTB1

AGP_ADSTB#1

AGP_SBSTB

AGP_SBSTB#

VGA_LMD30

+AGPREF_2GMCH

GRCOMP

10_0402

1 2

+AGPREF_2GMCH

C356

@22PF

W21

W24

W22

W26

AE26

AD25

AC26

AA24

AD26

AB24

U7C

K26

G_AD0/LDQM0

J22

G_AD1/LMD4

K25

G_AD2/LMD7

J21

G_AD3/LMD3

L24

G_AD4/LMD6

J20

G_AD5/LMD2

L26

G_AD6/LMD5

K23

G_AD7/LMD1

K22

G_AD8/LMD0

M25

G_AD9/LMA4

M24

G_AD10/LDQM1

M26

G_AD11/LMA2

M21

G_AD12/LMD8

N24

G_AD13/LMA5

N22

G_AD14/LMD9

N26

G_AD15/MA1

T26

G_AD16/LMA8

T22

G_AD17/LMD14

U24

G_AD18/LMA11/LBA

T23

G_AD19/LMD15

U26

G_AD20/LMA9

T24

G_AD21/LMD16

V24

G_AD22/LMA0

U21

G_AD23/LMD17

V25

G_AD24/LCKE

V21

G_AD25/LMD18

V26

G_AD26/LCAS#

G_AD27/LMD19

G_AD28/LTCLK1

G_AD29/LMD20

G_AD30/LTCLK0

Y21

G_AD31/LMD21

H23

G_C/BE#0/LMA3

N21

G_C/BE#1/LMD10

T25

G_C/BE#2/LMD13

Y26

G_C/BE#3/LRAS#

R26

G_FRAME#/LMA10

P26

G_DEVSEL#/LMD11

P23

G_IRDY#/LMD12

P21

G_TRDY#/LMA7

P25

G_STOP#/LCS#

R24

G_PAR/LMA6

G_REQ#/LMD27

G_GNT#

PIPE#/LMD24

M22

AD_STB0

L23

AD_STB#0

U22

AD_STB1

V23

AD_STB#1

Y23

SB_STB

SB_STB#

RBF#/LMD30

WBF#

J24

AGPREF

J26

GRCOMP

G10

NC

R22

LOCLK

P22

LRCLK

+3VS

1 2

12

GMCH2v0

VGA_LMA[0..11]<13>

VGA_LMD[0..31]<13>

VGA_LDQM[0..3]<13>

R76

300_1%_0402

R74

200_1%_0402

C76

470PF_0402

C75

470PF_0402

AGP

12

12

2

HUB

R77

82_0402

R75

82_0402

2

TVCLKIN/STALL

CLKOUT0

CLKOUT1

LTVVSYNC

DVO

LTVHSYNC

DCLKREF

HLPSTRB

HLPSTRB#

HLZCOMP

SBA0/LMD31

SBA1/LMD25

SBA2/LDQM2

SBA3/LMD26

SBA4/LMD23

SBA5/LWE#

SBA6/LMD22

SBA7/LGM_FRQ_SEL

ST0/LMD28

ST1/LDQM3

ST2/LMD29

VGA_LMA[0..11]

VGA_LMD[0..31]

VGA_LDQM[0..3]

CLK_DOT_GMCH

1

LTVD0

LTVD1

LTVD2

LTVD3

LTVD4

LTVD5

LTVD6

LTVD7

LTVD8

LTVD9

LTVD10

LTVD11

BLANK#

LTVDA

LTVCK

DDCK

DDDA

IWASTE

IREF

VSYNC

HSYNC

GREEN

BLUE

HLCLK

HL10

HLREF

RED

HL0

HL1

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

AD16

AF17

AE17

AD17

AF18

AD18

AF20

AD20

AC20

AF21

AE21

AD21

AB19

AC18

AE19

AF19

AC16

AB17

AA20

AB21

AB18

AA18

AE24

Y20

AD23

AF22

AF23

AD22

AE22

AE23

F22

H24

H26

H25

G24

F24

E26

E25

D26

D25

D24

C26

H21

G25

F26

+GMCH_HLCOMP

H20

AB22

AB25

AB23

AB26

AA22

AA26

Y22

Y25

AD24

AC24

AC23

DVO_D0

DVO_D1

DVO_D2

DVO_D3

DVO_D4

DVO_D5

DVO_D6

DVO_D7

DVO_D8

DVO_D9

DVO_D10

DVO_D11

DVO_BL#

DVO_CLKOUT

DVO_VSYNC

DVO_HSYNC

LTVDA

LTVCL

CLK_DOT_GMCH

R92 174_1%1 2

CRT_VSYNC

CRT_HSYNC

CRT_R

CRT_G

CRT_B

CLK_HUB_GMCH

HL0

HL1

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

HL10

HL_STB

HL_STB#

R71 36.5_1%

VGA_LMD31

VGA_LMD25

VGA_LDQM2

VGA_LMD26

VGA_LMD23

VGA_LWE#

VGA_LMD22

VGA_LFSEL

VGA_LMD28

VGA_LDQM3

VGA_LMD29

HL[0..10]

DVO_D[0..11]

DVO_BL# <12>

DVO_CLKOUT <12>

DVO_CLK# <12>

DVO_CLK <12>

DVO_VSYNC <12>

DVO_HSYNC <12>

LTVDA <12>

LTVCL <12>

3VDDCCL <13>

3VDDCDA <13>

CRT_VSYNC <13>

CRT_HSYNC <13>

CRT_R <13>

CRT_G <13>

CRT_B <13>

HL_STB <14>

HL_STB# <14>

1 2

VGA_LWE# <13>

VGA_LFSEL <8,13>

HL[0..10] <14>

DVO_D[0..11] <12>

DVO_CLKOUT

CLK_DOT_GMCH <11>

+HUBREF_GMCH

+1_8VS

MODIFY ON 6/11

300_1%_0402

12

C355

.01UF

TYPEDET# +VDDQ AGP-REF

0

1

CLK_HUB_GMCH

12

R263

@33_0402

C317

@18PF

Title

Size Document Number Rev

Date: Sheet of

Compal Electronics, Inc.

GMCH2-M - 1/3

888L2 Main Board

12

R267

@33_0402

12

C370

@22PF

1.5V

3.3V

CLK_HUB_GMCH <11>

1

7 42Thursday, January 11, 2001

R47

@33_0402

1 2

12

C62

@10PF

+1_8VS

R72

R70

300_1%_0402

0.5VDDQ

0.4VDDQ

12

12

2.0

Page 8

5

4

3

2

1

Power-Up Strap Options

Pin Name Strap Description Configuration InternalInterface

SCAS# Host Freq. "H" : 133MHz (Default)

"L" : 100MHz

SWE# System"H" : 100MHz (Default)Host Freq.

D D

SMAA11 IOQ Depth

"H" : 4 (Default) System

"L" : 1

SMAA10 "H" : Normal SystemALL Z

SMAA9

FSB P-MOS Kicker Enable System"H" : Enabled (Default)

"L" : Disabled (Cumine)

SMAC6#

SMAC5#

*

VGA_LFSEL#

C C

B B

A A

Enable VCH Serial

Programming Mode

Enable Quick Start

Support

"L" : Disabled

"L" : Enabled (Default) System

(Quick Start Mode)

"H" : Disabled

(Stop Grant Mode)

Local Memory Freq. Select "H" : 133MHz (Default)

"L" : 100MHz

RP2 8P4R-10

MD32

MD33 MD2

MD34

MD35

MD36

MD37

MD38 MD5

MD39

MD43

MD42

MD41

MD40

MD47

MD46

MD45 MD13

MD44

MD20

MD21

MD22

MD23

MD16

MD17

MD18

MD19

MD28

MD29

MD30

MD31

MD24

MD25

MD26

MD27

45

36

27

18

45

36

27

18

RP3 8P4R-10

RP4 8P4R-10

4 5

3 6

2 7

1 8

4 5

3 6

2 7

1 8

RP5 8P4R-10

RP10 8P4R-10

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

RP31 8P4R-10

RP15 8P4R-10

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

RP13 8P4R-10

5

MMD32

MMD33

MMD34

MMD35

MMD36

MMD37

MMD38

MMD39

MMD43

MMD42

MMD41

MMD40

MMD47

MMD46

MMD45

MMD44

MMD20

MMD21

MMD22

MMD23

MMD16

MMD17

MMD18

MMD19

MMD28

MMD29

MMD30

MMD31

MMD24

MMD25

MMD26

MMD27

MD3

MD0

MD7

MD6

MD4

MD8

MD9

MD10

MD11

MD14

MD12

MD60

MD61

MD62

MD63

MD59

MD58

MD57

MD56

MD52

MD53

MD54

MD55

MD48

MD49

MD50

MD51

RP27 8P4R-10

45

36

27

18

45

36

27

18

RP28 8P4R-10

RP29 8P4R-10

4 5

3 6

2 7

1 8

4 5

3 6

2 7

1 8

RP7 8P4R-10

RP33 8P4R-10

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

RP34 8P4R-10

RP11 8P4R-10

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

RP12 8P4R-10

MMD3

MMD2

MMD1MD1

MMD0

MMD7

MMD6

MMD5

MMD4

MMD8

MMD9

MMD10

MMD11

MMD15MD15

MMD14

MMD13

MMD12

MMD60

MMD61

MMD62

MMD63

MMD59

MMD58

MMD57

MMD56

MMD52

MMD53

MMD54

MMD55

MMD48

MMD49

MMD50

MMD51

System

Memory

Memory"L" : 66MHz

Memory

Memory"L" : All Z

Memory

System"H" : Enabled (Default)

Memory

Memory

AGP/LM i815/i815-m

4

PULL_UP

MMD0

MMD1

MMD2

PULL_UP

PULL_UP

PULL_UP

PULL_UP

PULL_UP

PULL_UP

VGA_LFSEL<7,13>

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

MMD3

MMD4

MMD5

MMD6

MMD7

MMD8

MMD9

MMD10

MMD11

MMD12

MMD13

MMD14

MMD15

MMD16

MMD17

MMD18

MMD19

MMD20

MMD21

MMD22

MMD23

MMD24

MMD25

MMD26

MMD27

MMD28

MMD29

MMD30

MMD31

MMD32

MMD33

MMD34

MMD35

MMD36

MMD37

MMD38

MMD39

MMD40

MMD41

MMD42

MMD43

MMD44

MMD45

MMD46

MMD47

MMD48

MMD49

MMD50

MMD51

MMD52

MMD53

MMD54

MMD55

MMD56

MMD57

MMD58

MMD59

MMD60

MMD61

MMD62

MMD63

3

RMWEA#

SCASA#

SBS0

MMA9

MAC#5

MAC#6

CSA#4

VGA_LFSEL#

U7B

D23

SMD0

C23

SMD1

D22

SMD2

F21

SMD3

E21

SMD4

G20

SMD5

F20

SMD6

D20

SMD7

F19

SMD8

E19

SMD9

D19

SMD10

E18

SMD11

B18

SMD12

F18

SMD13

G18

SMD14

D17

SMD15

A3

SMD16

A1

SMD17

C1

SMD18

F2

SMD19

G3

SMD20

D6

SMD21

C5

SMD22

B4

SMD23

D4

SMD24

C2

SMD25

D3

SMD26

E4

SMD27

F5

SMD28

G4

SMD29

J6

SMD30

K5

SMD31

A26

SMD32

A25

SMD33

B24

SMD34

A24

SMD35

B23

SMD36

A23

SMD37

C22

SMD38

A22

SMD39

D21

SMD40

B21

SMD41

A21

SMD42

C20

SMD43

B20

SMD44

A20

SMD45

C19

SMD46

A19

SMD47

A4

SMD48

A2

SMD49

B1

SMD50

E1

SMD51

G2

SMD52

E6

SMD53

D5

SMD54

C4

SMD55

B3

SMD56

D2

SMD57

E3

SMD58

F4

SMD59

F6

SMD60

G5

SMD61

H4

SMD62

J4

SMD63

GMCH2v0

R285 @10K_04021 2

R281 10K_04021 2

R292 10K_04021 2

R301 10K_04021 2

R305 10K_04021 2

R307 @10K_04021 2

R290 @10K_04021 2

R68 @10K_040212

SMAA0

SMAA1

SMAA2

SMAA3

SMAA4

SMAA5

SMAA6

SMAA7

SMAA8

SMAA9

SMAA10

SMAA11

SMAA12

SMAB#4

SMAB#5

SMAB#6

SMAB#7

SMAC#4

SMAC#5

SMAC#6

SMAC#7

MEMORY

SCSA#0

SCSA#1

SCSA#2

SCSA#3

SCSA#4

SCSA#5

SCSB#0

SCSB#1

SCSB#2

SCSB#3

SCSB#4

SCSB#5

SRAS#

SCAS#

SWE#

SCKE0

SCKE1

SCKE2

SCKE3

SCKE4

SCKE5

SCLK

SDQM0

SDQM1

SDQM2

SDQM3

SDQM4

SDQM5

SDQM6

SDQM7

SRCOMP

SBS0

SBS1

MMA1

B16

MMA2

F12

MMA3

A16

B12

A12

C11

A11

MMA8

D12

MMA9

C13

MMA10

E11

MMA11

A13

MMA12

B7

MAB#4_R

B15

MAB#5_R

A15

MAB#6_R

C14

MAB#7_R

A14

B10

SMAC#5

A10

SMAC#6

C10

SMAC#7

A9

SBS0

B13

SBS1

D11

D15

A17

CSA#2

D14

CSA#3

E14

CSA#4

E13

CSA#5

B17

F9

F8

D10

D9

B9

A8

SRASA#

C16

SCASA#

D18

RMWEA#

E16

D8

E8

CKE2

E9

CKE3

D7

C8

C7

F7

DQMA#0

D16

DQMA#1

F15

DQMA#2

A7

DQMA#3

A6

DQMA#4

A18

DQMA#5

C17

DQMA#6

B6

DQMA#7

A5

SRCOMP

G7

2

MMA0

D13

MAB#6_R

MAB#7_R

MAB#4_R

MAB#5_R

SMAC#6SMAC#4

SMAC#7

SMAC#4

SMAC#5

SBS0 <10>

SBS1 <10>

CSA#2 <10>

CSA#3 <10>

CSA#4 <10>

CSA#5 <10>

SRASA# <10>

SCASA# <10>

RMWEA# <10>

CKE2 <10>

CKE3 <10>

CKE4 <10>

CKE5 <10>

DQMA#0 <10>

DQMA#1 <10>

DQMA#2 <10>

DQMA#3 <10>

DQMA#4 <10>

DQMA#5 <10>

DQMA#6 <10>

DQMA#7 <10>

R297 36.5_1%1 2

MD[0..63]<10>

MMA0 <10>

MMA1 <10>

MMA2 <10>

MMA3 <10>

MMA8 <10>

MMA9 <10>

MMA10 <10>

MMA11 <10>

MAB#6

1 8

MAB#7

2 7

MAB#4

3 6

MAB#5

4 5

RP8 8P4R-10

RP9 8P4R-10

Title

Size Document Number Rev

Date: Sheet of

MAC#6

1 8

MAC#7

2 7

MAC#4

3 6

MAC#5

4 5

1 2

R315 @33_0402

MD[0..63]

GMCH2-M - 2/3

888L2 Main Board

CLK_MEM_GMCH <11>

+3V

MMA12 <10>

MAB#6 <10>

MAB#7 <10>

MAB#4 <10>

MAB#5 <10>

MAC#6 <10>

MAC#7 <10>

MAC#4 <10>

MAC#5 <10>

C410 @22PF

Compal Electronics, Inc.

8 42Thursday, January 11, 2001

1

2.0

Page 9

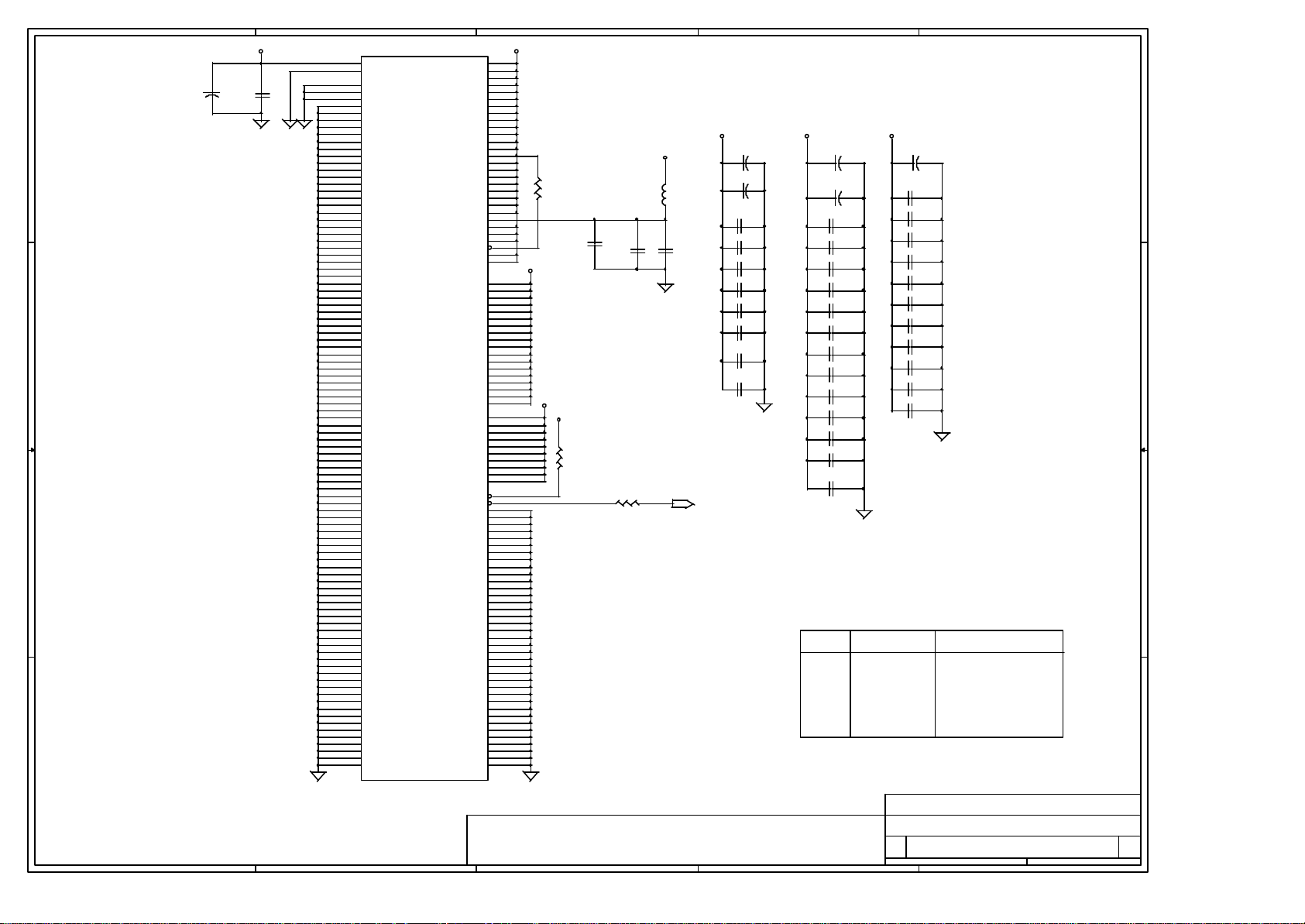

5

22UF_6.3V_1210_X5R

D D

C C

B B

A A

5

+1_8VS

+

C118

+VCCDPLL

12

C418

.1UF

AE25

AF24

AC11

AC13

AC15

AC17

AC19

AC21

AC25

AE10

AE12

AE14

AE16

AE18

AE20

W23

W25

AA12

AA14

AA16

J7

K7

E22

Y8

AB4

M13

AC2

AC5

AC7

AC9

AE2

AE4

AE6

AE8

B26

C3

C6

C9

C12

C15

C18

C21

C24

D1

E5

E10

E12

E15

E17

E20

F1

F3

F11

F13

T21

U2

U7

K24

V4

V6

V20

V22

W2

Y4

Y6

Y10

Y19

AA2

AA9

P11

P12

P13

P14

P15

P16

R2

R6

R11

R12

R13

R14

R15

R16

R23

R25

T4

T11

T12

T13

T14

T15

T16

L15

L16

L22

L25

M4

M11

M12

4

U7D

VCC1_8/VCCDPLL

GND/VSSDPLL

GND/VSSDACA1

GND/VSSDACA2

GND/VSSBA

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GMCH2v0

4

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCCDA/(VCC1_8)

VCCBA/(VCC1_8)

VCCDACA1/(VCC1_8)

VCCDACA2/(VCC1_8)

VCC1_8

VCC1_8

VSUS_3.3_1

VSUS_3.3_2

VSUS_3.3_3

VSUS_3.3_4

VSUS_3.3_5

VSUS_3.3_6

VSUS_3.3_7

VSUS_3.3_8

VSUS_3.3_9

VSUS_3.3_10

VSUS_3.3_11

VSUS_3.3_12

VSUS_3.3_13

VSUS_3.3_14

VSUS_3.3_15

VSUS_3.3_16

VSUS_3.3_17

VSUS_3.3_18

POWER/GND

INTRPT#

AGPBUSY#

R319

0_0402

+VCCDA

10UF_10V_1206

+3VS

12

R280

10K_0402

3

12

C407

R112 0_04021 2

3

12

C367

.1UF

+1_8VS

L16

68nH

1 2

12

C399

22UF_10V_1206

+3VS +1_8VS +3V

C274

+

22UF_6.3V_1210_X5R

+

C482

22UF_6.3V_1210_X5R

C371

.1UF

C358

.1UF

C325

.1UF

C359

.1UF

C326

.1UF

C324

82PF

C357

82PF

C354

82PF

AGP_BUSY# <15>

+1_8VS

W6

G26

M6

P6

Y9

Y18

AA8

AA11

AA13

AA15

AA17

AA19

AB16

AB20

AC22

AD19

12

C25

E24

F23

G22

K6

Y7

AA21

E23

AF26

AF25

AA6

HCLK# C431

V7

T6

+3V

B2

B5

B8

B11

B14

B19

B22

B25

E2

F10

F14

F17

G6

G8

G19

H2

H5

+3VS

H7

K20

VDDQ

Y24

VDDQ

L21

VDDQ

M23

VDDQ

U25

VDDQ

N25

VDDQ

R21

VDDQ

U20

VDDQ

U23

VDDQ

W20

VDDQ

Y17

E7

M14

GND

M15

GND

M16

GND

N2

GND

N6

GND

N11

GND

N12

GND

N13

GND

N14

GND

N15

GND

N16

GND

N23

GND

P4

GND

AA23

GND

F16

GND

F25

GND

G9

GND

G17

GND

G21

GND

G23

GND

P24

GND

H6

GND

H22

GND

J2

GND

J5

GND

J23

GND

J25

GND

K4

GND

K21

GND

L2

GND

L6

GND

L11

GND

L12

GND

L13

GND

L14

GND

AA25

GND

W7

GND

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

2

C119

+

22UF_6.3V_1210_X5R

C104

+

1 2

150UF_6.3V_E

C398 .1UF

C109 .1UF

C417 82PF

C415 .1UF

C416 .1UF

C414 82PF

C413 .1UF

C372 .1UF

C383 82PF

C377 .1UF

C346 .1UF

1 2

C483 .1UF_0402

1 2

C484 .1UF_0402

C120

1 2

150UF_6.3V_E

C432

C393

C404

C394

C428

C126

C433

C419

C333

C352

PIN# DT_GMCH GMCH2-M

E7

AA6

VSS (GND)

V_1.8 (1.8V)

Y17 VSS (GND) INTRPT# (INPUT)

AC18 LTVCLKIN (INPUT) LTVCLKIN/STALL (INPUT)

Title

Size Document Number Rev

2

Date: Sheet of

+

.01UF

.01UF

82PF

.01UF

.01UF

82PF

.01UF

.01UF

82PF

.01UF

.01UF

AGPBUSY# (OUTPUT)

RESERVED (1.8V)

Compal Electronics, Inc.

GMCH2-M - 3/3

888L2 Main Board

1

9 42Thursday, January 11, 2001

1

2.0

Page 10

1

MD31

MD30

MD29

MD28

MD27

A A

MMA0<8>

MMA1<8>

MMA2<8>

R93

6.8_0402

5PF

1 2

1 2

C86

CLK_MEM2<11> CLK_MEM4<11>

B B

C C

D D

SRASA#<8>

CSA#3<8>

MAB#6<8> MAB#7 <8>

MMA8<8> SBS0 <8>

MMA9<8>

MMA10<8>

SMB_ICH_DAT_M0<11>

MD26

MD25

MD24

DQMA#3

DQMA#2 DQMA#7

MMA0

MMA1

MMA2

MD23

MD22

MD21

MD20

MD19

MD18

MD17

MD16

RMWEA#

MD47

MD46

MD45

MD44

MD43

MD42

MD41

MD40

MAB#6

MMA8

MMA9

MMA10

DQMA#5

DQMA#4 DQMA#0

MD39

MD38

MD37

MD36

MD35

MD34

MD33

MD32

+3V +3V+3V

12

C107

1000PF

2

+3V +3V

JP17

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

VSS

DQ0

DQ1

DQ2

DQ3

VCC

DQ4

DQ5

DQ6

DQ7

VSS

CE0#

CE1#

VCC

A0

A1

A2

VSS

DQ8

DQ9

DQ10

DQ11

VCC

DQ12

DQ13

DQ14

DQ15

VSS

RESVD/DQ64

RESVD/DQ65

RFU/CLK0

VCC

RFU

WE#

RE0#

RE1#

OE#/RESVD

VSS

RESVD/DQ66

RESVD/DQ67

VCC

DQ16

DQ17

DQ18

DQ19

VSS

DQ20

DQ21

DQ22

DQ23

VCC

A6

A8

VSS

A9

A10

VCC

CE2#/RESVD

CE3#/RESVD

VSS

DQ24

DQ25

DQ26

DQ27

VCC

DQ28

DQ29

DQ30

DQ31

VSS

SDA

VCC

SO-DIMM144_R

DQ32

DQ33

DQ34

DQ35

VCC

DQ36

DQ37

DQ38

DQ39

CE4#

CE5#

VCC

DQ40

DQ41

DQ42

DQ43

VCC

DQ44

DQ45

DQ46

DQ47

RESVD/DQ68

RESVD/DQ69

RFU/CKE0

VCC

RFU

RFU/CKE1

RFU

RFU

RFU/CLK1

RESVD/DQ70

RESVD/DQ71

VCC

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

VCC

A11/BA0

A12/BA1

A13/A11

VCC

CE6#/RESVD

CE7#/RESVD

DQ56

DQ57

DQ58

DQ59

VCC

DQ60

DQ61

DQ62

DQ63

VCC

VSS

VSS

A3

A4

A5

VSS

VSS

VSS

VSS

A7

VSS

VSS

VSS

SCL

DIMM1

REVERSE

H=4.0mm

12

12

C50

1000PF

C58

.1UF

12

C66

.1UF

12

C40

.1UF

12

12

12

C90

C51

C94

.1UF

.1UF

.1UF

3

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

12

C67

1000PF

12

C77

.1UF

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

DQMA#6

MMA3

MAB#4

MAB#5

MD63

MD62

MD61

MD60

MD59

MD58

MD57

MD56

MMA12

MMA13

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MAB#7

SBS0

SBS1

MMA11

DQMA#1

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

12

C95

1000PF

MMA3 <8>

MAB#4 <8>

MAB#5 <8>

CKE2 <8>

SCASA# <8>

CKE3 <8>

MMA12 <8>CSA#2<8>

12

R84

6.8_0402

12

C84

5PF

SBS1 <8>

MMA11 <8>

SMB_ICH_CLK_M <11>

12

C437

10UF_10V_1206

4

MMA13

12

R86

1K_0402

CLK_MEM3 <11> CLK_MEM5 <11>

5

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

DQMA#6

DQMA#7

MMA0<8>

MMA1<8>

MMA2<8>

C81

1 2

1 2

R89 6.8_0402

5PF

SRASA#<8>

RMWEA#<8>

CSA#4<8>

CSA#5<8>

MAC#6<8> MAC#7 <8>

MMA8<8>

MMA9<8>

MMA10<8>

SMB_ICH_DAT_M1<11>

MMA0

MMA1

MMA2

MD63

MD62

MD61

MD60

MD59

MD58

MD57

MD56

RMWEA#

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MAC#6

MMA8

MMA9

DQMA#1

DQMA#0

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

SMB_ICH_DAT_M1

6

+3V

JP16

1

VSS

3

DQ0

5

DQ1

7

DQ2

9

DQ3

11

VCC

13

DQ4

15

DQ5

17

DQ6

19

DQ7

21

VSS

23

CE0#

25

CE1#

27

VCC

29

A0

31

A1

33

A2

35

VSS

37

DQ8

39

DQ9

41

DQ10

43

DQ11

45

VCC

47

DQ12

49

DQ13

51

DQ14

53

DQ15

55

VSS

57

RESVD/DQ64

59

RESVD/DQ65

61

RFU/CLK0

63

VCC

65

RFU

67

WE#

69

RE0#

71

RE1#

73

OE#/RESVD

75

VSS

77

RESVD/DQ66

79

RESVD/DQ67

81

VCC

83

DQ16

85

DQ17

87

DQ18

89

DQ19

91

VSS

93

DQ20

95

DQ21

97

DQ22

99

DQ23

101

VCC

103

A6

105

A8

107

VSS

109

A9

111

A10

113

VCC

115

CE2#/RESVD

117

CE3#/RESVD

119

VSS

121

DQ24

123

DQ25

125

DQ26

127

DQ27

129

VCC

131

DQ28

133

DQ29

135

DQ30

137

DQ31

139

VSS

141

SDA

143

VCC

SO-DIMM144

DQ32

DQ33

DQ34

DQ35

VCC

DQ36

DQ37

DQ38

DQ39

CE4#

CE5#

VCC

DQ40

DQ41

DQ42

DQ43

VCC

DQ44

DQ45

DQ46

DQ47

RESVD/DQ68

RESVD/DQ69

RFU/CKE0

VCC

RFU

RFU/CKE1

RFU

RFU

RFU/CLK1

RESVD/DQ70

RESVD/DQ71

VCC

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

VCC

A11/BA0

A12/BA1

A13/A11

VCC

CE6#/RESVD

CE7#/RESVD

DQ56

DQ57

DQ58

DQ59

VCC

DQ60

DQ61

DQ62

DQ63

VCC

7

+3V

2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SCL

MD31

4

MD30

6

MD29

8

MD28

10

12

MD27

14

MD26

16

MD25

18

MD24

20

22

DQMA#3

24

DQMA#2

26

28

MMA3

30

A3

MAC#4

32

A4

MAC#5

34

A5

36

MD23

38

MD22

40

MD21

42

MD20

44

46

MD19

48

MD18

50

MD17

52

MD16

54

56

58

60

62

64

66

68

MMA12

70

MMA13

72

74

76

78

80

82

MD47

84

MD46

86

MD45

88

MD44

90

92

MD43

94

MD42

96

MD41

98

MD40

100

102

MAC#7

104

A7

SBS0

106

108

SBS1

110

MMA11MMA10

112

114

DQMA#5

116

DQMA#4

118

120

MD39

122

MD38

124

MD37

126

MD36

128

130

MD35

132

MD34

134

MD33

136

MD32

138

140

SMB_ICH_CLK_M

142

144

12

12

R85

6.8_0402

MMA3 <8>

MAC#4 <8>

MAC#5 <8>

CKE4 <8>

SCASA# <8>

CKE5 <8>RMWEA#<8>

MMA12 <8>

C85

5PF

SBS0 <8>

SBS1 <8>

MMA11 <8>

8

DIMM2

C61

1000PF

12

C56

.1UF

H=5.2mm

12

C92

.1UF

12

12

12

C96

C91

.1UF

.1UF

For SO-DIMM2

C106

.1UF

12

C93

1000PF

12

C108

.1UF

12

C74

1000PF

12

C436

10UF_10V_1206

MD[0..63]<8>

DQMA#[0..7]<8>

MD[0..63]

DQMA#[0..7]

+3V +3V +3V

12

12

C39

1000PF

.1UF

12

C48

For SO-DIMM1

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

1

2

3

4

5

6

Title

Size Document Number Rev

B

Date: Sheet of

Compal Electronics, Inc.

P10-SODIMM0/1.SCH

888L2 Main Board

7

10 42Thursday, January 11, 2001

8

2.0

Page 11

A

B

C

D

E

L14

+3VS

4 4

CLK_14M_ICH<15>

CLK_14M_SIO<21>

PCI_STP#<15>

CLK_PCI_ICH<14>

CLK_PCI_PCM<19>

CLK_PCI_FWH<14>

CLK_PCI_SIO<21>

CLK_PCI_MINI<29>

CLK_USB_ICH<15>

3 3

CLK_DOT_GMCH<7>

SLP_S1#<15,22>

SMB_ICH_DAT<15>

SMB_ICH_CLK<15>

1 2

BLM21A601SPT

4.7UF_10V_0805

R82 33_040212

R81 33_040212

12

12

C65

C72

.1UF

R46 0_04021 2

12

C63

.1UF

+3V_CLK

12

12

C57

.1UF

R62 33_04021 2

R61 33_0402

R59 @33_04021 2

R55 33_04021 2

R53 22_04021 2

R51 33_04021 2

R49 33_04021 2

C64

.1UF

C78

18PF

C71

18PF

1 2

+3V_CLK

12

C68

.1UF

12

12

12

+3V_CLK

12

C80

C73

.1UF

.1UF

CK133-XIN

12

R65

12

2M

SEL0

SEL1

CLK_14M

R45

10K_0402

Y1

14.318MHZ

PCISTP#

CLK_ICH

CLK_PCI1

CLK_FWH

CLK_SIO

CLK_MDM

CLK_USB

CLK_DOT

1 2

CK133-XOUT

R508.2K_0402

3

4

28

29

1

11

12

13

15

16

18

19

20

25

26

32

30

31

23

X1

GNDA

X2

SEL0

SEL1(TRIST#)

REF0/(SEL1)

PCI_STP#/(VCC3)

PCI_F(PCI0_ICH)

PCI1

PCI2

PCI3

PCI4

PCI5

PCI6

USB(48M)

DOT(48M)

TEST#/(VCC3)

PWR_DWN#

SDATA

SCLK

GND

GND

6

5

22332

VCC3

VDDA

GND

GND

1417243541

102127

44

37

VCC3

VCC3

VCC3

VCC3

VCC3/(SDRAM6)

VCH_CLK/(SDRAM7)

DCLK/(VCC3)

CPU_STP#(DCLK)

GND

GND

GND

GND

GND

CK133-SOLANO2-M

48

47

56

51

VCC3

CPU2(ITP)

SDRAM0

SDRAM1

SDRAM2

SDRAM3

SDRAM4

SDRAM5

3V66_AGP

53

VCC2

VCC2

APIC0

APIC1

CPU0

CPU1

3V66_1

3V66_0

+2_5V_CLKS

12

C79

.1UF

U6

55

54

52

50

49

46

45

43

42

40

39

36

9

8

7

38

34

12

C83

.1UF

APIC0

APIC1

HCLK1

HCLK2

SDRAM2

SDRAM3

SDRAM4

SDRAM5

OSCVCH

CLK_3V66_1

CLK_3V66_0

DCLK

L15

BLM21A601SPT

12

C82

4.7UF_10V_0805

R88 33_04021 2

R87 47_0402

1 2

R83 33_04021 2

R69 33_04021 2

R58 10_04021 2

R60 10_0402

1 2

R56 10_04021 2

R57 10_04021 2

R52 33_04021 2

R64 33_04021 2

R67 33_04021 2

R54 33_04021 2

12

+2_5V_CLK

CLK_APIC_CPU <4>

CLK_APIC_ICH <14>

CLK_HOST_CPU <4>

CLK_HOST_GMCH <7>

CLK_MEM2 <10>

CLK_MEM3 <10>

CLK_MEM4 <10>

CLK_MEM5 <10>

CLK_OSC_VCH <12>

CLK_HUB_GMCH <7>

CLK_HUB_ICH <15>

CLK_MEM_GMCH <8>

CPU_STP# <15>

+3V_CLK

12

SEL0SEL1 PSB SDRAM

00

66 100

+3V_CLK

12

R41

12

+3V_CLK

12

10K_0402

SEL0

R43

@1K_0402

R40

@10K_0402

SEL1

+3VS

12

R38

4.7K_0402

SMB_ICH_DAT<15>

2 2

12

R37

10K_0402

SEL_DIMM0<15>

SEL_DIMM1<15>

G

2

Q9

13

D

S

2N7002

+3V

12

12

R35

10K_0402

12

R32

10K_0402

SMB_ICH_DAT_M0 <10>

SMB_ICH_DAT_M1 <10>

SMB_ICH_CLK_M <10>SMB_ICH_CLK<15>

R33

10K_0402

G

2

13

D

S

Q8

2N7002

+5VS

G

2

Q10

13

D

S

2N7002

Pin #

1

11

29

33

36

37

38

CK-Solano

W218 C9835

REF0/SEL1

VCC3

Tristate#

VCC3

DCLK

SDRAM7 SDRAM7

SDRAM6

VCC3

*

0 1

C9815

REF/SEL1

Tristate#

VCC3

DCLK

SDRAM6

VCC3

01

133 133

11

133 100

CK-Solano2-m

W224

REF

PCI_STP#VCC3

SEL1

TEST#

CPU_STP#34

VCH_CLK

VCC3

DCLK

100100

REF

PCI_STP#

SEL1

TEST#

CPU_STP#

VCH_CLK

VCC3

DCLK

1 1

R39

1K_0402

1 2

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

A

B

C

D

Title

Size Document Number Rev

Date: Sheet of

Compal Electronics, Inc.

Clock Synthesizer

888L2 Main Board

11 42Thursday, January 11, 2001

E

2.0

Page 12

5

U15A

E3

P0

E2

P1

E1

P2

F3

P3

F2

P4

F1

P5

+1_8VS

12

+3VS

C169

.1UF

2

G

B+

12

12

D

13

S

G3

G2

G1

H3

H2

H1

J3

J2

J1

K3

K2

K1

L3

L2

L1

M3

M2

M1

N1

N2

P2

N3

P3

M4

N4

P4

M5

N5

P5

M6

C1

B2

D2

D3

A2

A13

C9

D4

D6

D9

E4

F11

G4

H4

J4

K4

L6

C6

L10

C10

C7

L11

C11

C8

R183

100K_0402

R190

75K

Q28

2N7002

P6

P7

P8

P9

P10

P11

P12

P13

P14

P15

P16

P17

P18

P19

P20

P21

P22

P23

P24

P25

P26

P27

P28

P29

P30

P31

P32

P33

P34

P35

FLM

LP

DE

SHFCLK

VCC3.3

VCC3.3

VCC3.3

VCC3.3

VCC3.3

VCC3.3

VCC3.3

VCC3.3

VCC3.3

VCC3.3

VCC3.3

VCC3.3

VCC3.3

VCC3.3

PLL_VCC

LVDSPLL_VCC

DC_CKT_CKT

PLL_VSS

LVDSPLL_VSS

DC_CKT_VSS

VCH

D D

C C

B B

+5V

A A

DVOrCLKOUT0

DVOrCLKOUT1

Q24

1

2

3 6

FDS4435

4

FDS4435: P CHANNAL

5

DVOrVSYNC

DVOrHSYNC

DVOrBLANK#

DVOrCLKIN

DVOrDATA0

DVOrDATA1

DVOrDATA2

DVOrDATA3

DVOrDATA4

DVOrDATA5

DVOrDATA6

DVOrDATA7

DVOrDATA8

DVOrDATA9

DVOrDATA10

DVOrDATA11

YA0P

YA0M

YA1P

YA1M

YA2P

YA2M

YA3P

YA3M

CLKAP

CLKAM

YB0P

YB0M

YB1P

YB1M

YB2P

YB2M

YB3P

YB3M

CLKBP