Page 1

A

1 1

2 2

B

C

D

E

Compal Confidential

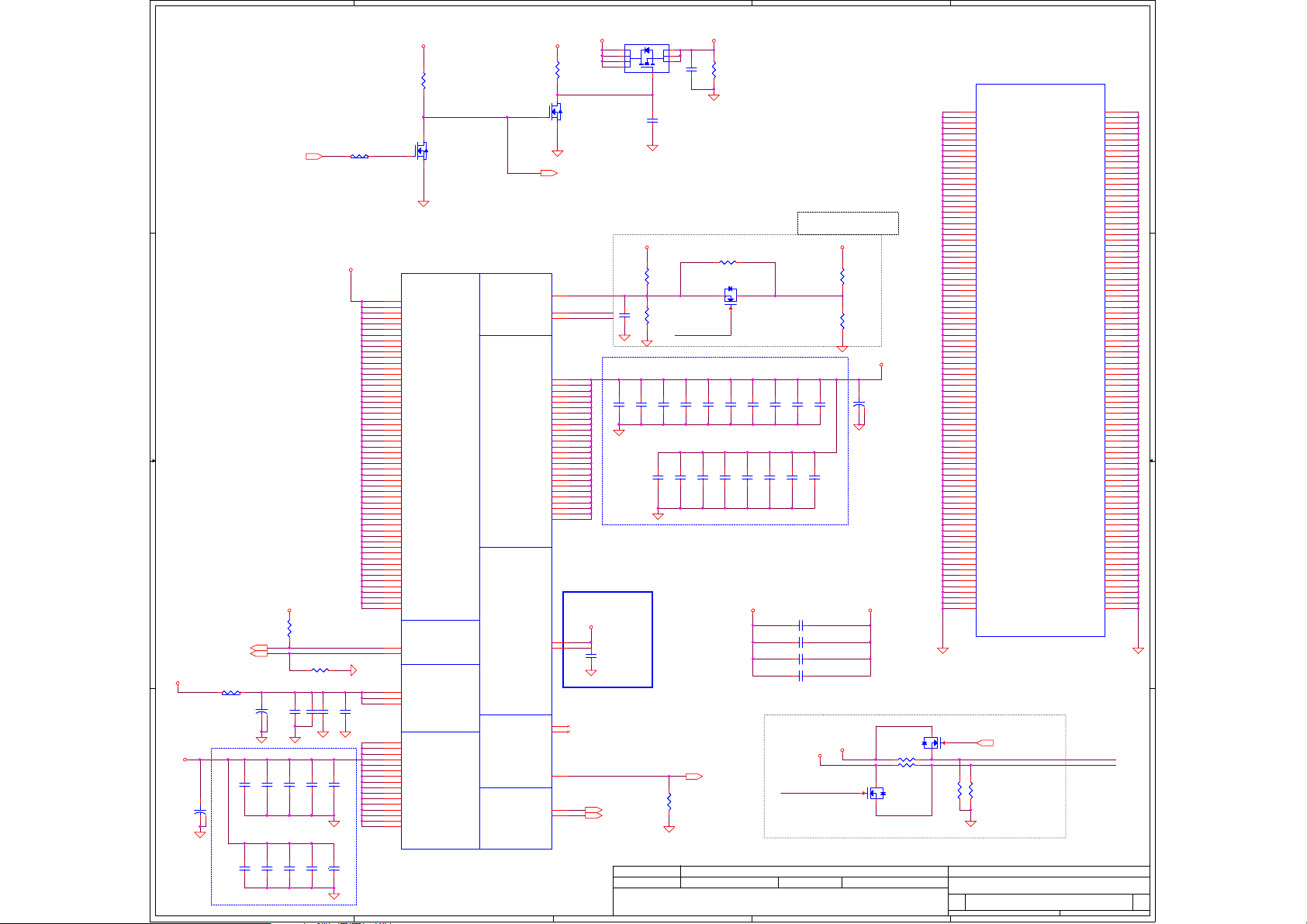

VAL40 MB Schematic Document

LA-8226P

3 3

Rev: 1.0

2012.07.06

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

C

2011/07/12 2012/12/31

2011/07/12 2012/12/31

2011/07/12 2012/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

Cover Sheet

Cover Sheet

Cover Sheet

LA-8226P

LA-8226P

LA-8226P

E

1.0

1.0

1 58Monday, July 09, 2012

1 58Monday, July 09, 2012

1 58Monday, July 09, 2012

1.0

of

of

of

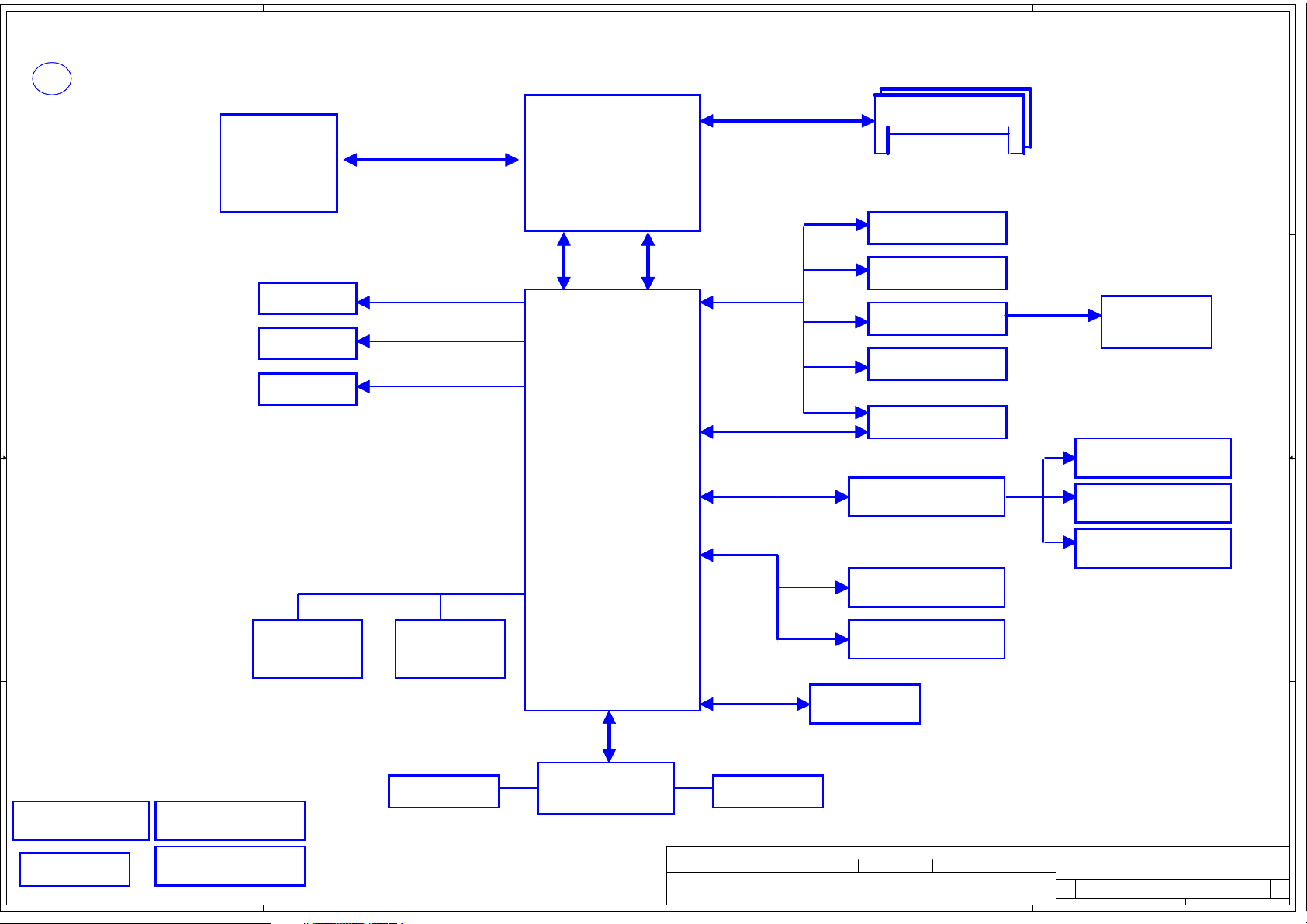

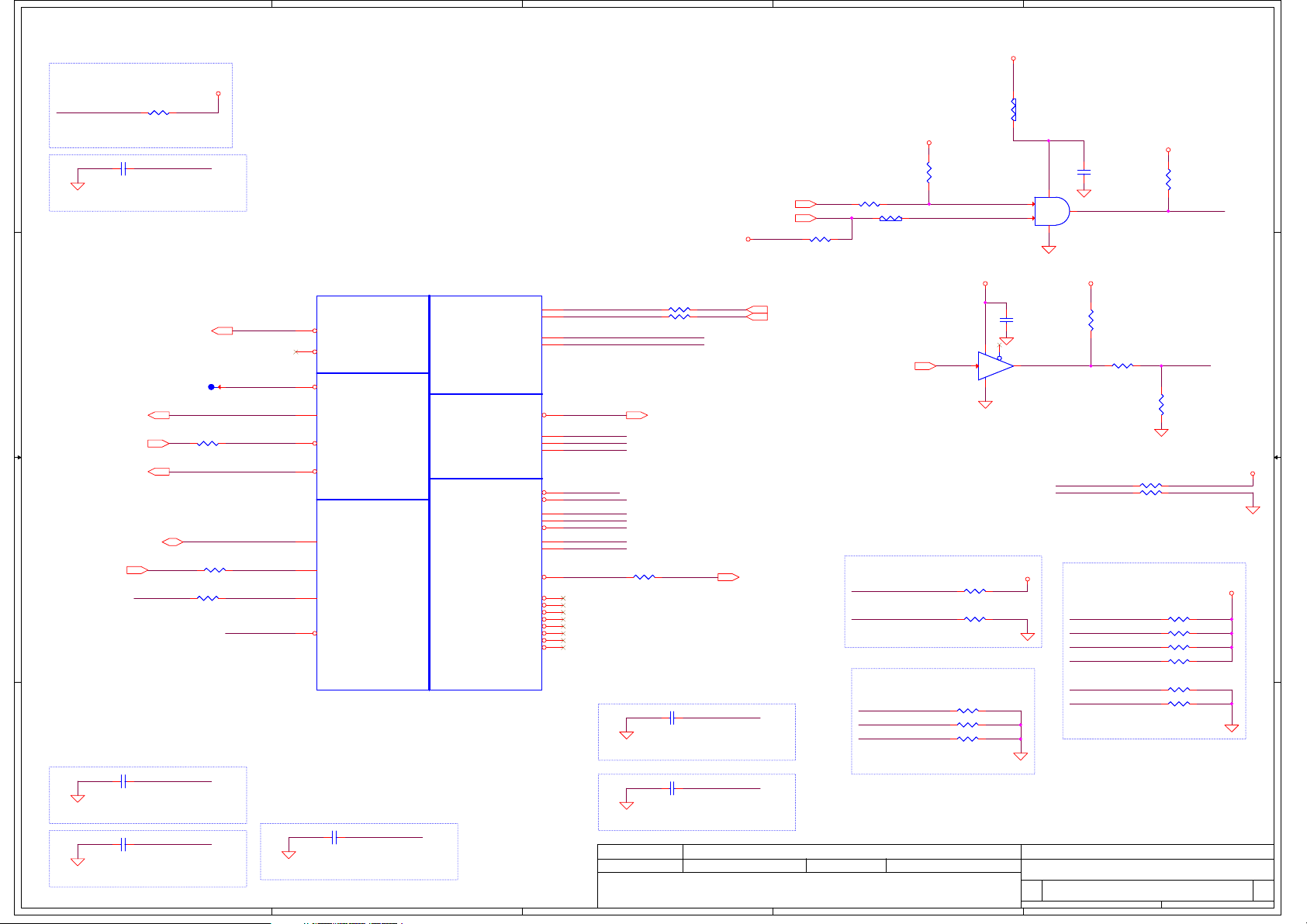

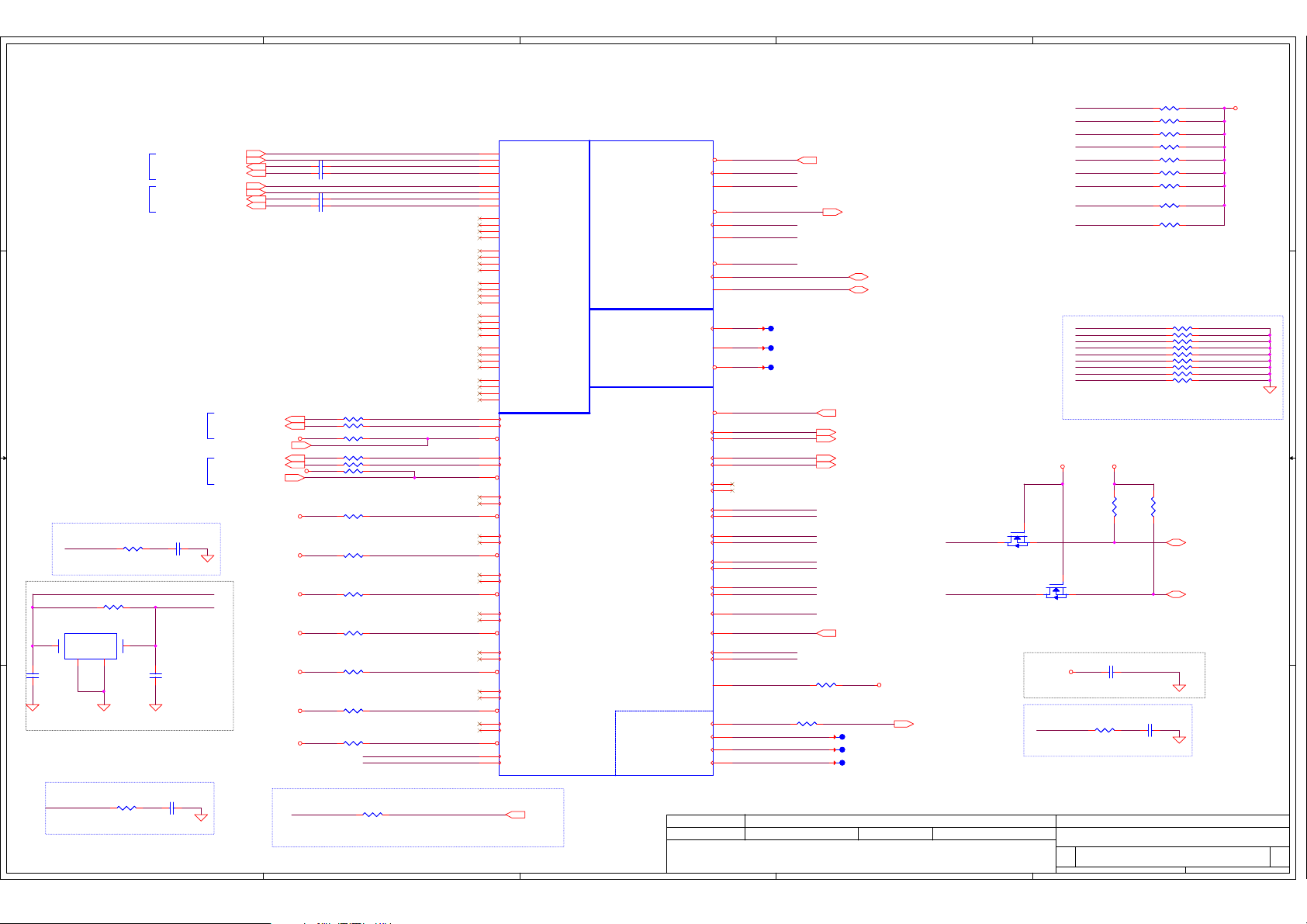

Page 2

1

2

3

4

5

Compal Confidential

ZZZ1

ZZZ1

PCB-MB

PCB-MB

PCB P/N for Load BOM

DA80000V100

DA80000V100

A A

NV

N13M-GE1

PEG 16X

Gb1B-64

23x23mm

Page 20 ~ 28

LCD conn

B B

CRT Conn

HDMI

C C

Page 30

Page 30

Page 35

LVDS, EDID, DISPOFF#, PWM

RGB, HV Sync, DDC

HDMI, DDC

PCI-e

ort 1

LAN/CRT Board

10/100/1000 LAN

Realtek GbE

RTL8111F

Page 32

port 2p

Mini Card-1

WLAN

Bluetooth

Page 40

VAL40

Intel

Ivy Bridge ULV

Processor

BGA 1023

Intel

PCH

HM76

Page 4 ~ 9

Page 12 ~ 19

LPC BUS

DMI x4

100MHz

5GB/s

+VCC_CORE, +VCCP,

+VCC_GFXCORE_AVG, +1.5V_CPU_VD DQ,

+1.8VS, _VCCSA

FDI x8

(UMA)

100MHz

2.7GT/s

PANTHER-POINT

FCBGA 989 Balls

+1.05VS, +1.8VS, +3VS,

+3V_PCH, +5V_PCH, +RTCVCC,

+VCCAFDI_VRM

DDR3 1333/1600MHz 1.5V

Dual Channel

port 2

port 11

USB2.0

port 3

port 10

port 0,1

USB3.0

Azalia

SATA

SPI

port 1,2

port 0

port 2

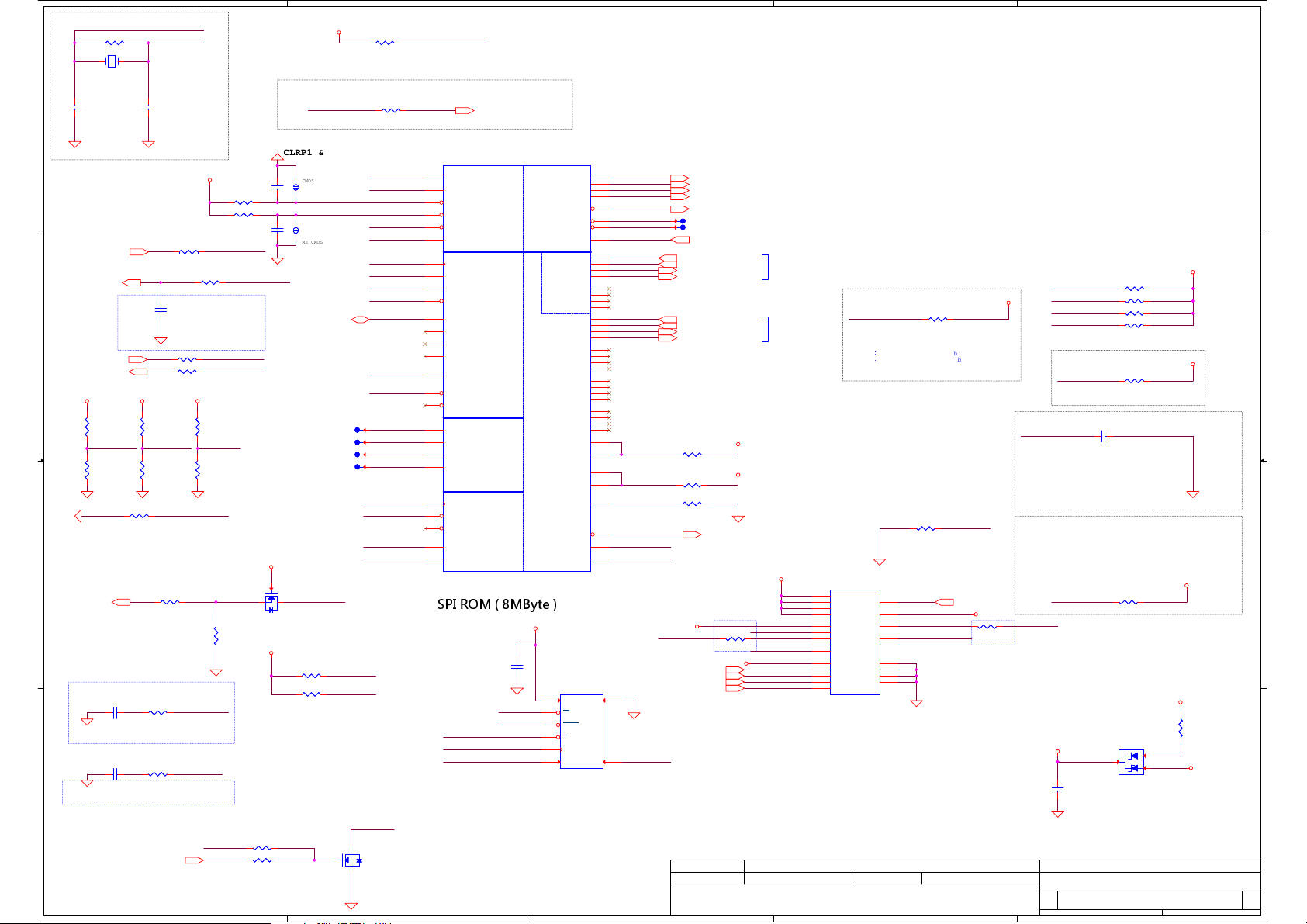

SPI ROM

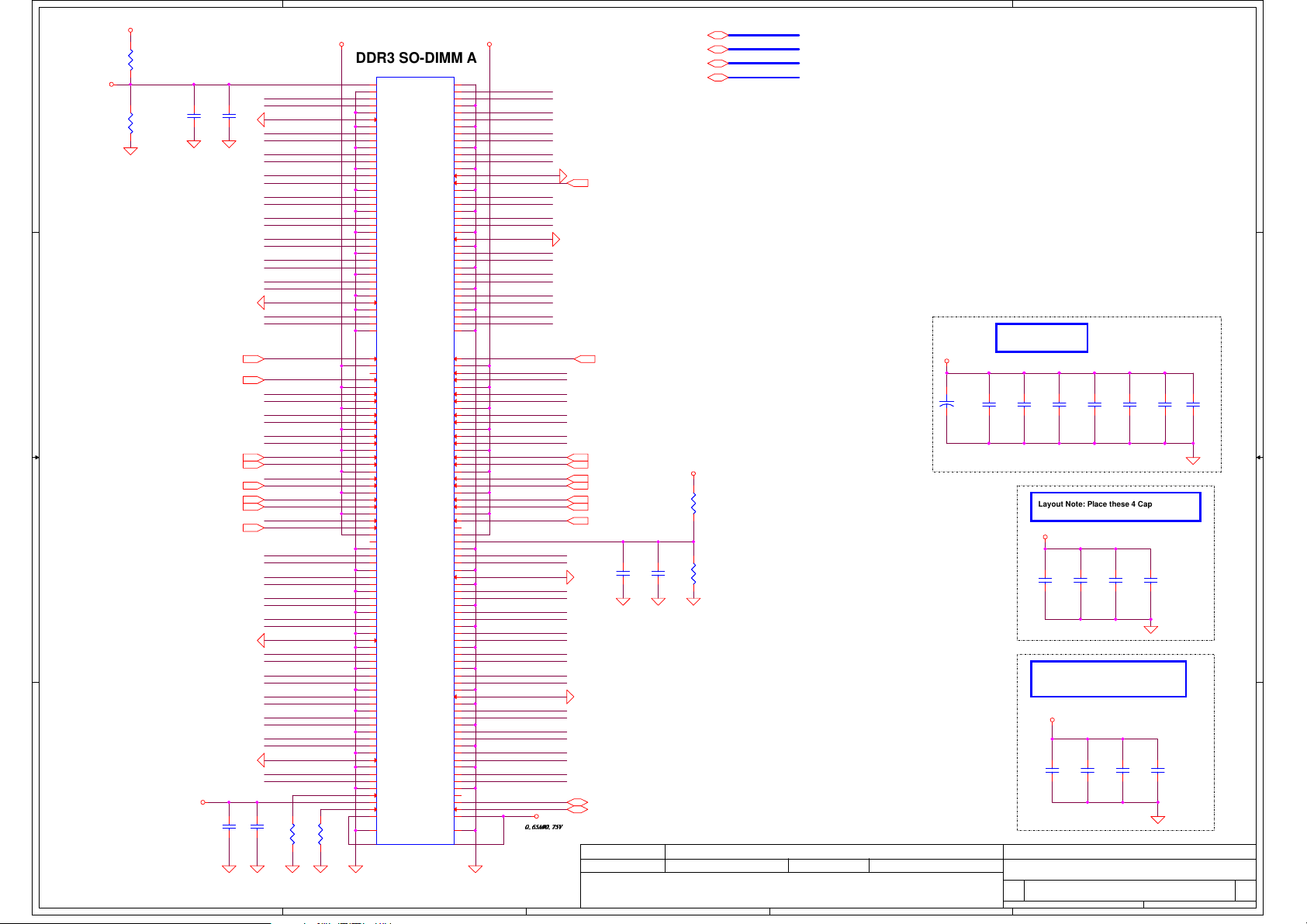

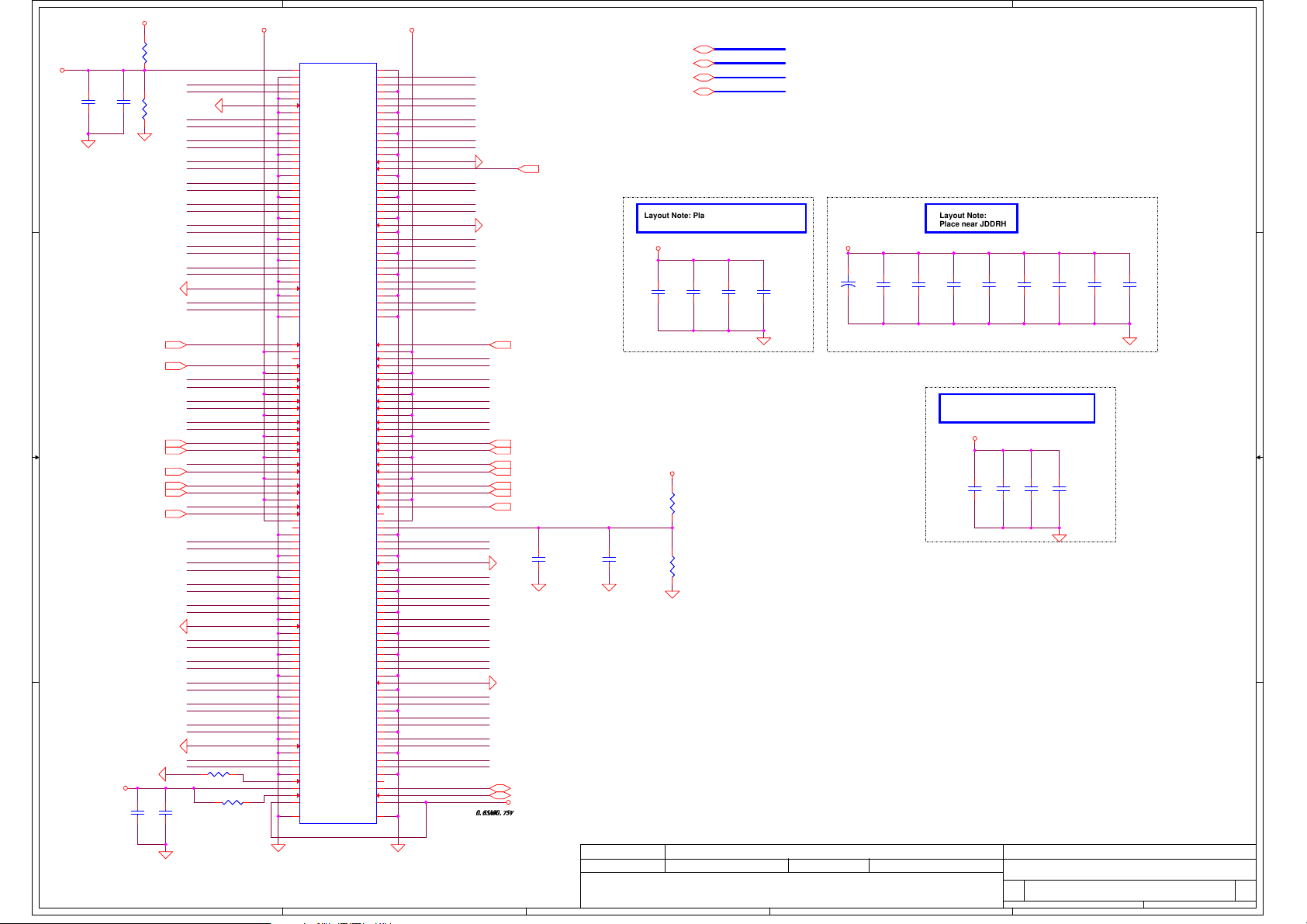

DDR3-SO-DIMM X 2

BANK 0, 1, 2, 3

+1.5V, +0.75VS

Page 10, 11

USB conn x1

USB Board

Camera

Page 33

Page 30

Card Reader

RTS5137

MiniCard-1

Page 34

Page 40

USB3.0 conn x2

Page 36

Realtek

ALC269

Page 33

2.5" SATA HDD Connector

Page 31

SATA ODD Connector

Page 31

8MB

Page 12

Memory Card Slot

SD/MMC

Audio Jack (HP)

Audio Jack (MIC)

Speaker Connector

Page 34

Page 33

Page 33

Page 33

D D

DC/DC Interface CKT.

Page 29,41

Fan Control

Page 37

External board

LS-8221P

USB/B

LS-8227P

MIC/B

1

Page 33

Page 30

Click Pad CONN.

2

ENE KB9012QF

+3VLP/+3VALW

page 39

Int. KBD

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

Page 38Page 38

Compal Secret Data

Compal Secret Data

2011/07/12 2012/12/31

2011/07/12 2012/12/31

2011/07/12 2012/12/31

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

4

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Block Diagram

Block Diagram

Block Diagram

LA-8226P

LA-8226P

LA-8226P

5

2 58Monday, July 09, 2012

2 58Monday, July 09, 2012

2 58Monday, July 09, 2012

1.0

1.0

1.0

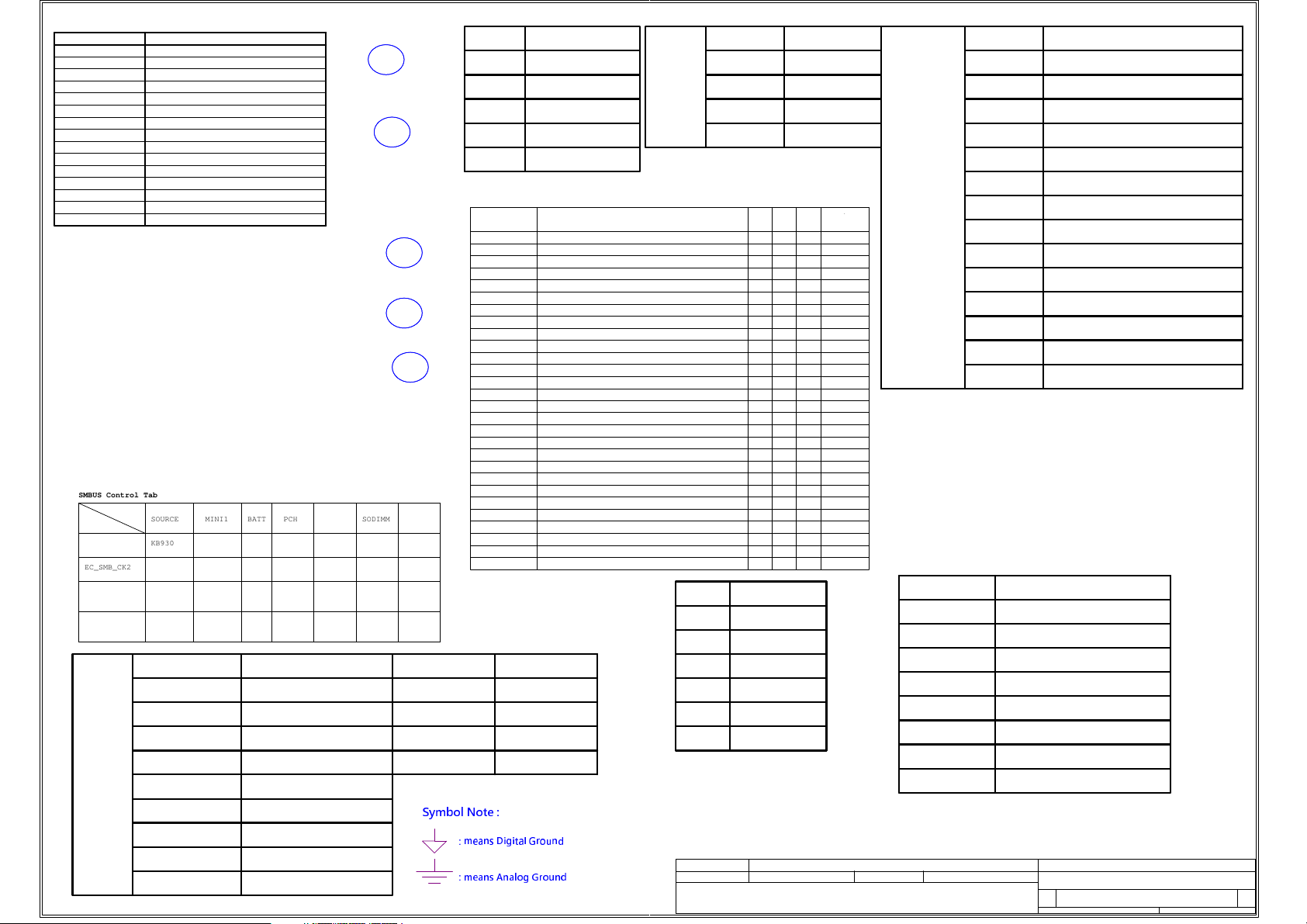

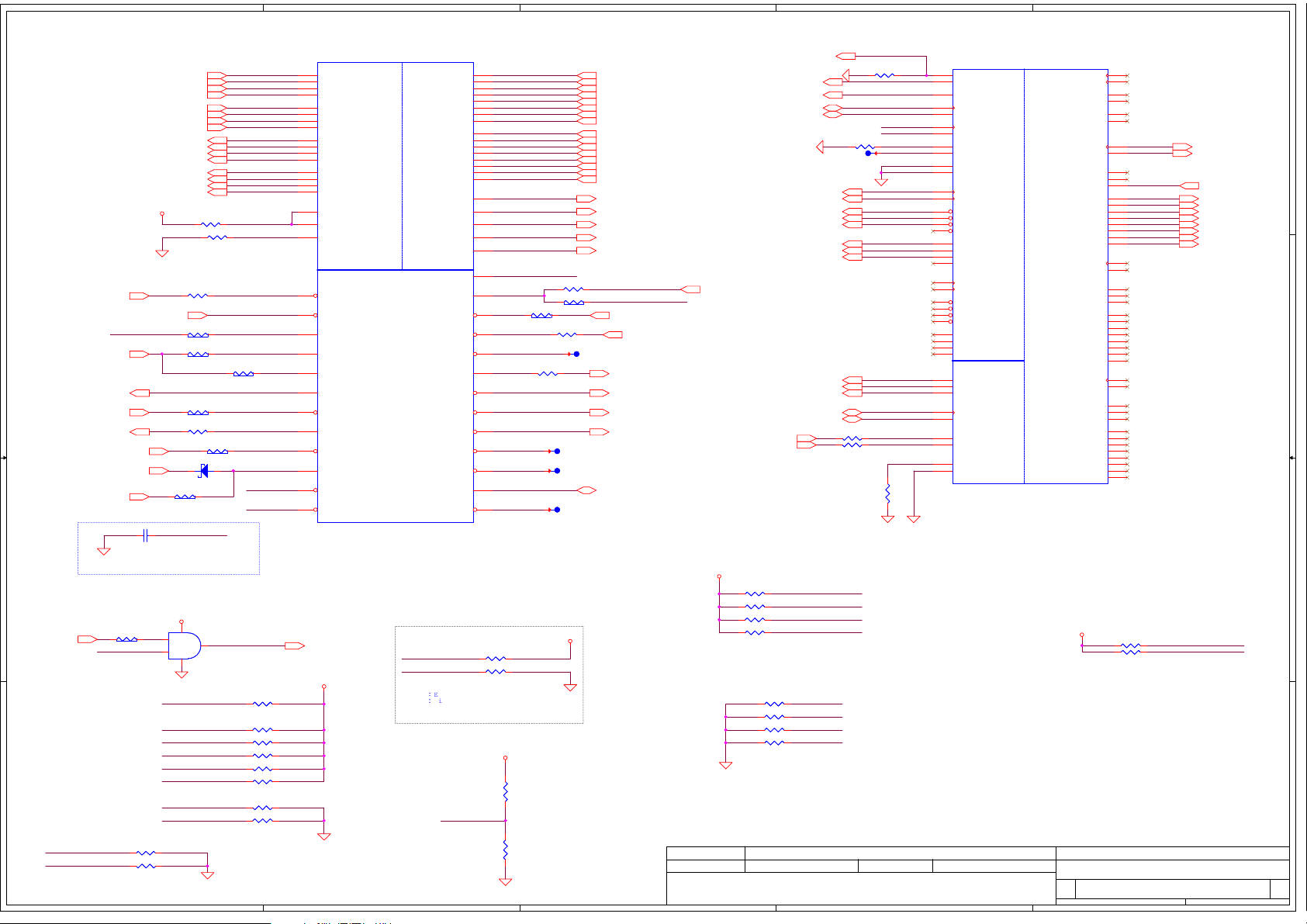

Page 3

A

BTO Option Table

DIS@ VGA componet

X76L07@ VRAM Hynix 2Gbx8 256Mx8

GCLK@ G-CLK

GCLKDIS@

GCLKUMA@ G-CLK + SLG3NB244

NONGCLK@ NONE G-CLK

AI@ AI Charger

NAI@ Non AI Charger

46@ HDMI royalty rule

I33110@ CPU BGA i3-3110M 2.4G/3M

32350@

CPU BOM Config

i3-3110MI33310@

i3-2370MI32370@

i3-2350MI32350@

BOM Config : DIS

K45B(i3-3110M)

* K45B(i3-2370M)

BOM Config : UMA

K45B(i3-3110M)

K45B(i3-2370M)

* K45B(i3-2350M)

1 1

SMBUS Control Table

EC_SMB_CK1

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

PCH_SMBCLK

PCH_SMBDATA PCH

PCH_SMLCLK

PCH_SMLDATA

BTO ItemBOM Structure

N13M-GE1_GB1b-64GE8@

G-CLK + SLG3NB300

CPU BGA i3-2370M 2.4G/3MI32370@

CPU BGA i3-2350M 2.3G/3MI

CR

SA00005M830 (INT I3-3110M 2.4G/3M SR0N2 BGA)

2.4G

HR

2.4G

SA000059I60 (INT I3-2370M 2.4G/3M SR0DQ BGA)

HR

2.3G

SA00004QXA0 (INT I3-2350M 2.3G/3M SR0DQ BGA)

DIS@/GE8@/X7607@/GCLK@/GCLKDIS@/I33110@/NAI@

DIS@/GE8@/X7607@/GCLK@/GCLKDIS@/I32370@/NAI@

GCLK@/GCLKUMA@/I33110@/NAI@

CLK@/GCLKUMA@/I32370@/NAI@

G

GCLK@/GCLKUMA@/I32350@/NAI@

SOURCE

KB930

KB930

PCH

MINI1 BATT SODIMM

X

X

V

X X

PCH

X

V

X

V

X

X

X

DESTINATIONDIFFERENTIAL

CLKOUT_PCIE0

MINI CARD WLAN

None

USB3.0 controller

None

None

CLK

CLKOUT_PCIE1

CLKOUT_PCIE2

CLKOUT_PCIE3

CLKOUT_PCIE4

CLKOUT_PCIE5

NoneCLKOUT_PCIE6

CLKOUT_PCIE7 None

CLKOUT_PEG_B

None

VRAMX8X8

N13M-GE1 x8

CPU

EC

X

X

X

V

ZZZ7

X76L07@ZZZ7

X76L07@

CLKOUT

PCI0

VRAM 2G HYN

VRAM 2G HYN

U10

GE8@U10

GE8@

PCI1

PCI2

PCI3

N13M-GE1 GB1b x8

N13M-GE1 GB1b x8

PCI4

Voltage Rails

Power Plane Description

UCPU1

I33110@UCPU1

I33110@

i3-3110M

i3-3110M

UCPU1

I32370@UCPU1

I32370@

i3-2370M

i3-2370M

UCPU1

I32350@UCPU1

I32350@

i3-2350M

i3-2350M

DGPU

X

X

X

V

X

V

X

V

VIN

BATT+

B+

+3VLP 3.3V power rail for 51ON power management ON ON ON ON

+3VALW ON3.3V always on power rail

+LAN_IO OFFON3.3V power rail for ethernet

+3VS_WLAN ON OFF3.3V power rail for WLAN/BT Combo

+3V_PCH ON OFF OFF3.3V power rail for PCH suspend well plane

+3VS 3.3V power rail for DDR SPI,PCH,HDD,Audio,Card Reader ON

+3VSG

+LCDVDD ON OFF OFF

+5VALW ON

+5V_PCH

+5VS OFFON OFF5V power rail for HDD,AUDIO,FAN,Touch PAD

+5VS_ODD

+1.8VS

+1.05VS ON

+VCCP

+1.05VSG

+1.5V

+1.5V_CPU_VDDQ

+1.5VSG

+1.5VS

+0.75VS

+VCCSA

+VCC_CORE

+VCC_GFXCORE_AXG

+VGA_CORE CORE Voltage for N13P Graphics ON OFF OFF ON OFF OFF OFF

FLEX CLOCKS DESTINATION

CLKOUTFLEX010/100/1G LAN

CLKOUTFLEX1

CLKOUTFLEX2

CLKOUTFLEX3

CLK_SD_48M

None

None

None

Symbol Note :

: means Digital Ground

: means Analog Ground

DESTINATION

PCH_LOOPBACK

EC

PCH

None USB2

LPC Debug Port

USB3 PORT

1

2

3

4

None

DESTINATION

USB2.0+3.0

USB2.0+3.0

None

None

USB2 PORT

0

1

2

3

4

5

6

7

8

9

10 Bluetooth

11

12

13

DESTINATION

10/100/1G LAN

MINI CARD WLAN

None

USB3.0 controller

None

None

None

None

Adapter power supply (19V)

Battery power supply (12.6V)

AC or battery power rail for power circuit

3.3V power rail for LCD

5V always on power rail

5V power rail for PCH suspend well plane

5V power rail for SATA ODD

1.8V power rail for CPU,PCH

1.05V power rail for PCH

1.05V power rail for CPU VCCIO,PCH

1.05V power rail for N13P

1.5V power rail for DDR3 system memory

1.5V power rail CPU VDDQ

1.5V power rail for N13P,VRAM

1.5V power rail for PCH,WLAN/BT combo

0.75V power rail for DDR VREF

VCCSA for CPU system agent

CORE Voltage for CPU

1.5V power rail for N13P,VRAM

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

A

SATA

SATA0

SATA1

SATA2

SATA3

SATA4

SATA5

Issued Date

Issued Date

Issued Date

Deep

S0 S3 S5

S3

N/A N/A N/A

N/A N/A N/A N/A

ON OFF OFF3.3V power rail for VGA

ON OFF

ON

ON

ON

ON

ON

ON OFF OFF OFF

ON OFF OFF OFF

ON OFF OFF OFF

ON

ON

ON

N/A

N/A

N/AN/AN/A

ON ON AC/ON; DC/OFF

OFF

ON

OFF OFF

ON

OFF OFF OFF

OFF

OFF

ON AC/ON; DC/OFF

ON

ON OFF

OFF

OFF

OFF

OFF OFF OFF

OFF OFF OFF

OFF OFF

OFF OFF OFF

ON

OFF OFF OFF

OFF

OFF

OFF

ON

OFF

OFF

OFF

OFF

OFFON

OFF

OFF

OFFOFF

DESTINATION

HDD

None

ODD

None

None

None

Compal Secret Data

Compal Secret Data

2011/07/12 2012/12/31

2011/07/12 2012/12/31

2011/07/12 2012/12/31

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

PCH

PCI EXPRESS

Lane 1

Lane 2

Lane 3

Lane 4

Lane 5

Lane 6

Lane 7

Lane 8

DESTINATION

USB2.0+3.0

USB2.0+3.0

Card Reader

None

None

None

None

None

None

JMINI1 (WLAN)

CAMERA

None

None

Compal Electronics, Inc.

Title

Title

Title

Notes List

Notes List

Notes List

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

LA-8226P

LA-8226P

LA-8226P

Date: Sheet of

Date: Sheet of

Date: Sheet of

3 58Monday, July 09, 2012

3 58Monday, July 09, 2012

3 58Monday, July 09, 2012

1.0

1.0

1.0

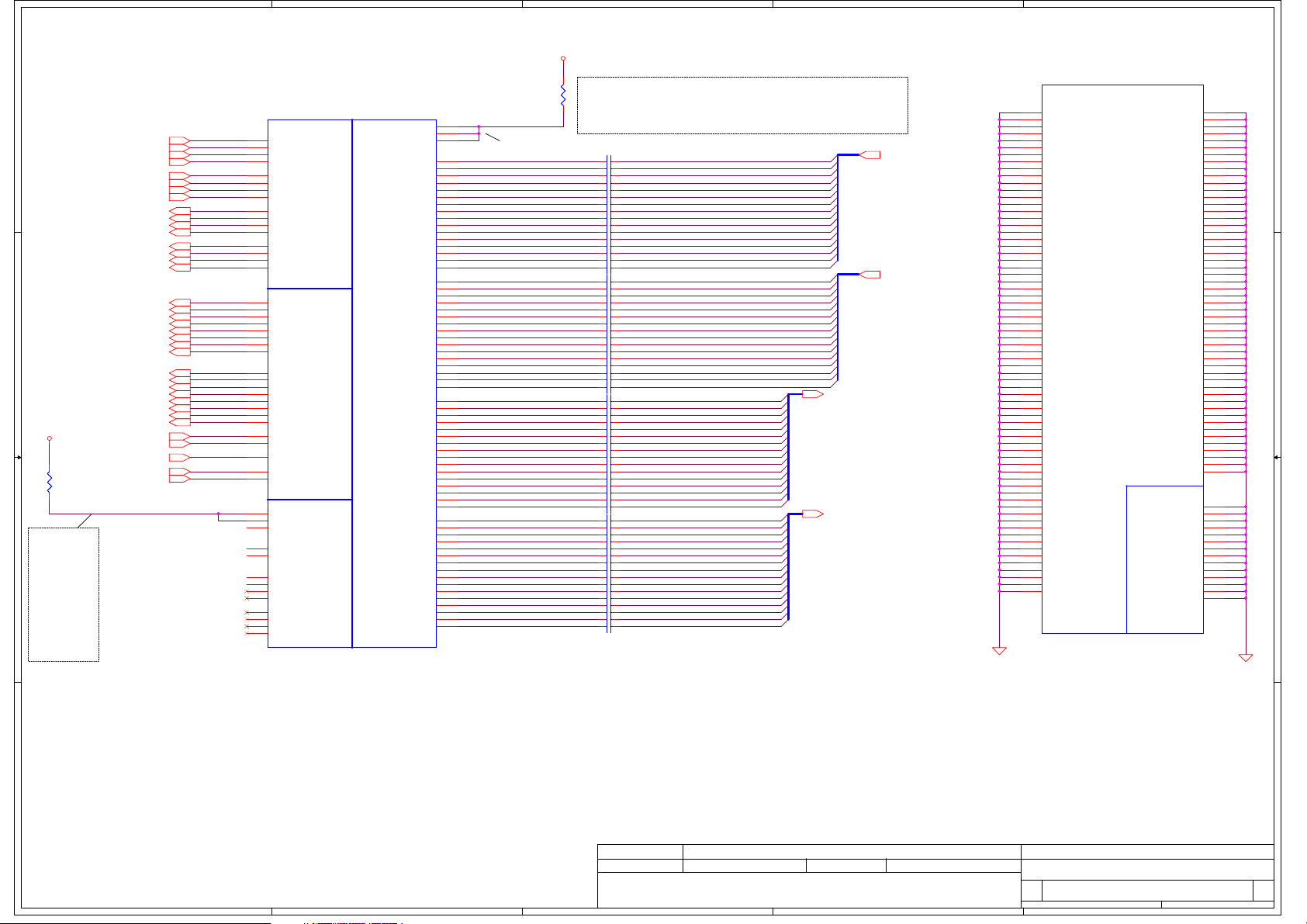

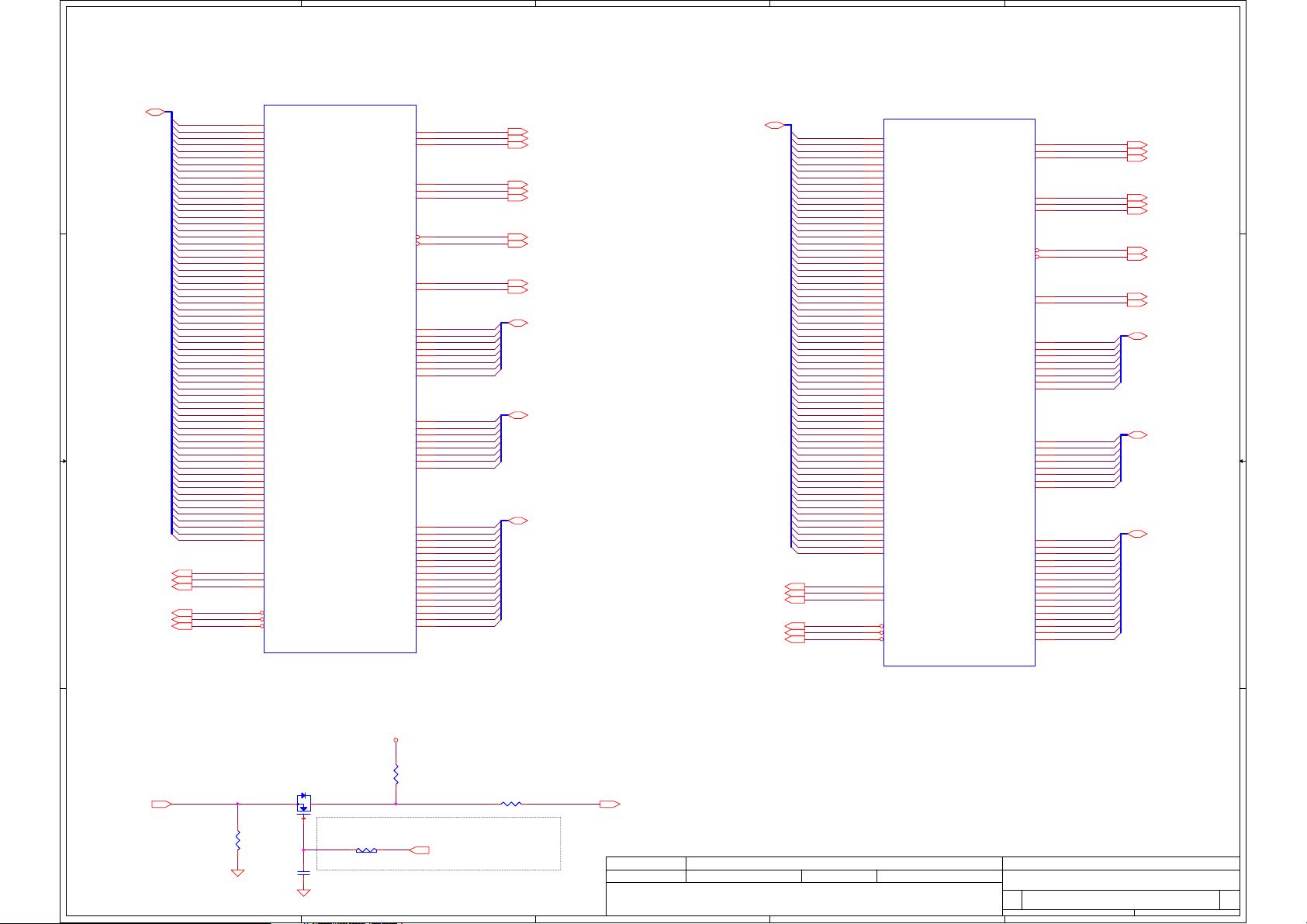

Page 4

5

UCPU1A

D D

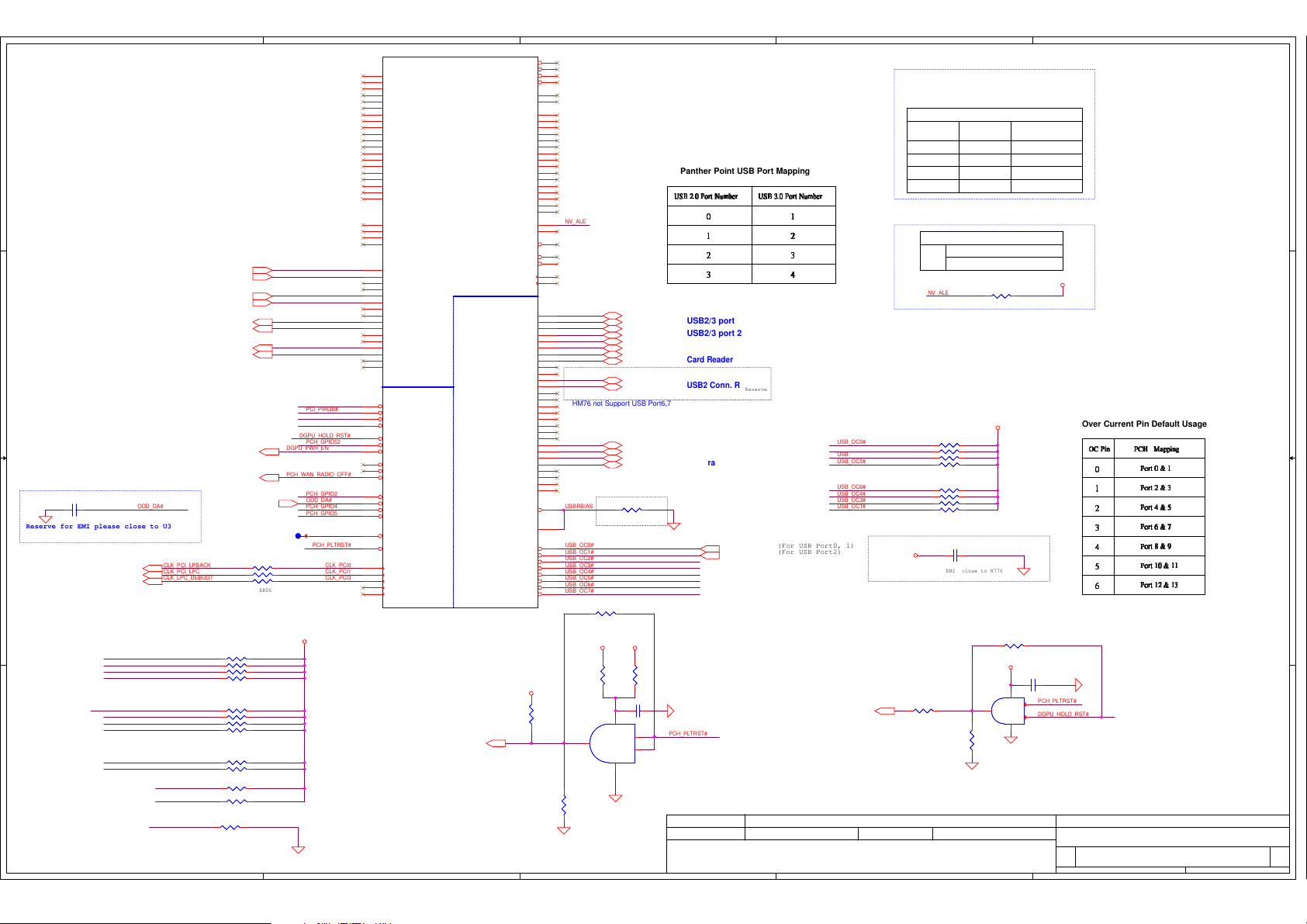

DMI_CRX_PTX_N014

DMI_CRX_PTX_N114

DMI_CRX_PTX_N214

DMI_CRX_PTX_N314

DMI_CRX_PTX_P014

DMI_CRX_PTX_P114

DMI_CRX_PTX_P214

DMI_CRX_PTX_P314

14

DMI_CTX_PRX_N0

14

DMI_CTX_PRX_N1

14

DMI_CTX_PRX_N2

14

DMI_CTX_PRX_N3

14

DMI_CTX_PRX_P0

14

DMI_CTX_PRX_P1

14

DMI_CTX_PRX_P2

14

DMI_CTX_PRX_P3

14

FDI_CTX_PRX_N0

14

FDI_CTX_PRX_N1

14

FDI_CTX_PRX_N2

14

FDI_CTX_PRX_N3

14

FDI_CTX_PRX_N4

14

FDI_CTX_PRX_N5

14

C C

+1.05VS

12

R2

R2

24.9_0402_1%

24.9_0402_1%

eDP_COMPIO

and ICOMPO

signals

should be

shorted

B B

near balls

and routed

with

typical

impedance

<25 mohms

FDI_CTX_PRX_N6

14

FDI_CTX_PRX_N7

14

FDI_CTX_PRX_P0

14

FDI_CTX_PRX_P1

14

FDI_CTX_PRX_P2

14

FDI_CTX_PRX_P3

14

FDI_CTX_PRX_P4

14

FDI_CTX_PRX_P5

14

FDI_CTX_PRX_P6

14

FDI_CTX_PRX_P7

FDI_FSYNC014

FDI_FSYNC114

FDI_INT14

FDI_LSYNC014

FDI_LSYNC114

FDI_CTX_PRX_N0

FDI_CTX_PRX_N1

FDI_CTX_PRX_N2

FDI_CTX_PRX_N3

FDI_CTX_PRX_N4

FDI_CTX_PRX_N5

FDI_CTX_PRX_N6

FDI_CTX_PRX_N7

FDI_CTX_PRX_P0

FDI_CTX_PRX_P1

FDI_CTX_PRX_P2

FDI_CTX_PRX_P3

FDI_CTX_PRX_P4

FDI_CTX_PRX_P5

FDI_CTX_PRX_P6

FDI_CTX_PRX_P7

FDI_FSYNC0

FDI_FSYNC1

FDI_INT

FDI_LSYNC0

FDI_LSYNC1

EDP_COMP

UCPU1A

M2

DMI_RX#[0]

P6

DMI_RX#[1]

P1

DMI_RX#[2]

P10

DMI_RX#[3]

N3

DMI_RX[0]

P7

DMI_RX[1]

P3

DMI_RX[2]

P11

DMI_RX[3]

K1

DMI_TX#[0]

M8

DMI_TX#[1]

N4

DMI_TX#[2]

R2

DMI_TX#[3]

K3

DMI_TX[0]

M7

DMI_TX[1]

P4

DMI_TX[2]

T3

DMI_TX[3]

U7

FDI0_TX#[0]

W11

FDI0_TX#[1]

W1

FDI0_TX#[2]

AA6

FDI0_TX#[3]

W6

FDI1_TX#[0]

V4

FDI1_TX#[1]

Y2

FDI1_TX#[2]

AC9

FDI1_TX#[3]

U6

FDI0_TX[0]

W10

FDI0_TX[1]

W3

FDI0_TX[2]

AA7

FDI0_TX[3]

W7

FDI1_TX[0]

T4

FDI1_TX[1]

AA3

FDI1_TX[2]

AC8

FDI1_TX[3]

AA11

FDI0_FSYNC

AC12

FDI1_FSYNC

U11

FDI_INT

AA10

FDI0_LSYNC

AG8

FDI1_LSYNC

AF3

eDP_COMPIO

AD2

eDP_ICOMPO

AG11

eDP_HPD#

AG4

eDP_AUX#

AF4

eDP_AUX

AC3

eDP_TX#[0]

AC4

eDP_TX#[1]

AE11

eDP_TX#[2]

AE7

eDP_TX#[3]

AC1

eDP_TX[0]

AA4

eDP_TX[1]

AE10

eDP_TX[2]

AE6

eDP_TX[3]

IVY-BRIDGE_BGA1023

IVY-BRIDGE_BGA1023

@

@

DMI Intel(R) FDI

DMI Intel(R) FDI

eDP

eDP

ER01

4

R1

R1

24.9_0402_1%

24.9_0402_1%

G3

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

G1

G4

H22

PCIE_GTX_CRX_N15

J21

PCIE_GTX_CRX_N14

B22

PCIE_GTX_CRX_N13

D21

PCIE_GTX_CRX_N12

A19

PCIE_GTX_CRX_N11

D17

PCIE_GTX_CRX_N10

B14

PCIE_GTX_CRX_N9

D13

PCIE_GTX_CRX_N8

A11

PCIE_GTX_CRX_N7

B10

PCIE_GTX_CRX_N6

G8

PCIE_GTX_CRX_N5

A8

PCIE_GTX_CRX_N4

B6

PCIE_GTX_CRX_N3

H8

PCIE_GTX_CRX_N2

E5

PCIE_GTX_CRX_N1

K7

PCIE_GTX_CRX_N0

K22

PCIE_GTX_CRX_P15

K19

PCIE_GTX_CRX_P14

C21

PCIE_GTX_CRX_P13

D19

PCIE_GTX_CRX_P12

C19

PCIE_GTX_CRX_P11

D16

PCIE_GTX_CRX_P10

C13

PCIE_GTX_CRX_P9

D12

PCIE_GTX_CRX_P8

C11

PCIE_GTX_CRX_P7

C9

PCIE_GTX_CRX_P6

F8

PCIE_GTX_CRX_P5

C8

PCIE_GTX_CRX_P4

C5

PCIE_GTX_CRX_P3

H6

PCIE_GTX_CRX_P2

F6

PCIE_GTX_CRX_P1

K6

PCIE_GTX_CRX_P0

G22

PCIE_CTX_GRX_N15

C23

PCIE_CTX_GRX_N14

D23

PCIE_CTX_GRX_N13

F21

PCIE_CTX_GRX_N12

H19

PCIE_CTX_GRX_N11

C17

PCIE_CTX_GRX_N10

K15

PCIE_CTX_GRX_N9

F17

PCIE_CTX_GRX_N8

F14

PCIE_CTX_GRX_N7

A15

PCIE_CTX_GRX_N6

J14

PCIE_CTX_GRX_N5

H13

PCIE_CTX_GRX_N4

M10

PCIE_CTX_GRX_N3

F10

PCIE_CTX_GRX_N2

D9

PCIE_CTX_GRX_N1

J4

PCIE_CTX_GRX_N0

F22

PCIE_CTX_GRX_P15

A23

PCIE_CTX_GRX_P14

D24

PCIE_CTX_GRX_P13

E21

PCIE_CTX_GRX_P12

G19

PCIE_CTX_GRX_P11

B18

PCIE_CTX_GRX_P10

K17

PCIE_CTX_GRX_P9

G17

PCIE_CTX_GRX_P8

E14

PCIE_CTX_GRX_P7

C15

PCIE_CTX_GRX_P6

K13

PCIE_CTX_GRX_P5

G13

PCIE_CTX_GRX_P4

K10

PCIE_CTX_GRX_P3

G10

PCIE_CTX_GRX_P2

D8

PCIE_CTX_GRX_P1

K4

PCIE_CTX_GRX_P0

PEG_COMP

12 mils

3

+1.05VS

12

PEG_ICOMPI and RCOMPO signals s hould be shorte d and routed

with - max leng th = 500 mils - typical impedan ce = 43 mohms

PEG_ICOMPO sign als should be ro uted with - max length = 500 mi ls

- typical imped ance = 14.5 mohm s

1 2

C1 0.22U_0402_10V6KDIS@ C1 0.22U_0402_10V6KDIS@

1 2

C2 0.22U_0402_10V6KDIS@ C2 0.22U_0402_10V6KDIS@

1 2

C3 0.22U_0402_10V6KDIS@ C3 0.22U_0402_10V6KDIS@

1 2

C4 0.22U_0402_10V6KDIS@ C4 0.22U_0402_10V6KDIS@

1 2

C5 0.22U_0402_10V6KDIS@ C5 0.22U_0402_10V6KDIS@

1 2

C6 0.22U_0402_10V6KDIS@ C6 0.22U_0402_10V6KDIS@

1 2

C7 0.22U_0402_10V6KDIS@ C7 0.22U_0402_10V6KDIS@

1 2

C8 0.22U_0402_10V6KDIS@ C8 0.22U_0402_10V6KDIS@

1 2

C9 0.22U_0402_10V6KDIS@ C9 0.22U_0402_10V6KDIS@

1 2

C10 0.22U_0402_10V6KDIS@ C10 0.22U_0402_10V6KDIS@

1 2

C11 0.22U_0402_10V6KDIS@ C11 0.22U_0402_10V6KDIS@

1 2

C12 0.22U_0402_10V6KDIS@ C12 0.22U_0402_10V6KDIS@

1 2

C13 0.22U_0402_10V6KDIS@ C13 0.22U_0402_10V6KDIS@

1 2

C14 0.22U_0402_10V6KDIS@ C14 0.22U_0402_10V6KDIS@

1 2

C15 0.22U_0402_10V6KDIS@ C15 0.22U_0402_10V6KDIS@

1 2

C16 0.22U_0402_10V6KDIS@ C16 0.22U_0402_10V6KDIS@

1 2

C17 0.22U_0402_10V6KDIS@ C17 0.22U_0402_10V6KDIS@

1 2

C18 0.22U_0402_10V6KDIS@ C18 0.22U_0402_10V6KDIS@

1 2

C19 0.22U_0402_10V6KDIS@ C19 0.22U_0402_10V6KDIS@

1 2

C20 0.22U_0402_10V6KDIS@ C20 0.22U_0402_10V6KDIS@

1 2

C21 0.22U_0402_10V6KDIS@ C21 0.22U_0402_10V6KDIS@

1 2

C22 0.22U_0402_10V6KDIS@ C22 0.22U_0402_10V6KDIS@

1 2

C23 0.22U_0402_10V6KDIS@ C23 0.22U_0402_10V6KDIS@

1 2

C24 0.22U_0402_10V6KDIS@ C24 0.22U_0402_10V6KDIS@

1 2

C25 0.22U_0402_10V6KDIS@ C25 0.22U_0402_10V6KDIS@

1 2

C26 0.22U_0402_10V6KDIS@ C26 0.22U_0402_10V6KDIS@

1 2

C27 0.22U_0402_10V6KDIS@ C27 0.22U_0402_10V6KDIS@

1 2

C28 0.22U_0402_10V6KDIS@ C28 0.22U_0402_10V6KDIS@

1 2

C29 0.22U_0402_10V6KDIS@ C29 0.22U_0402_10V6KDIS@

1 2

C30 0.22U_0402_10V6KDIS@ C30 0.22U_0402_10V6KDIS@

1 2

C31 0.22U_0402_10V6KDIS@ C31 0.22U_0402_10V6KDIS@

1 2

C32 0.22U_0402_10V6KDIS@ C32 0.22U_0402_10V6KDIS@

1 2

C33 0.22U_0402_10V6KDIS@ C33 0.22U_0402_10V6KDIS@

1 2

C34 0.22U_0402_10V6KDIS@ C34 0.22U_0402_10V6KDIS@

1 2

C35 0.22U_0402_10V6KDIS@ C35 0.22U_0402_10V6KDIS@

1 2

C36 0.22U_0402_10V6KDIS@ C36 0.22U_0402_10V6KDIS@

1 2

C37 0.22U_0402_10V6KDIS@ C37 0.22U_0402_10V6KDIS@

1 2

C38 0.22U_0402_10V6KDIS@ C38 0.22U_0402_10V6KDIS@

1 2

C39 0.22U_0402_10V6KDIS@ C39 0.22U_0402_10V6KDIS@

1 2

C40 0.22U_0402_10V6KDIS@ C40 0.22U_0402_10V6KDIS@

1 2

C41 0.22U_0402_10V6KDIS@ C41 0.22U_0402_10V6KDIS@

1 2

C42 0.22U_0402_10V6KDIS@ C42 0.22U_0402_10V6KDIS@

1 2

C43 0.22U_0402_10V6KDIS@ C43 0.22U_0402_10V6KDIS@

1 2

C44 0.22U_0402_10V6KDIS@ C44 0.22U_0402_10V6KDIS@

1 2

C45 0.22U_0402_10V6KDIS@ C45 0.22U_0402_10V6KDIS@

1 2

C46 0.22U_0402_10V6KDIS@ C46 0.22U_0402_10V6KDIS@

1 2

C47 0.22U_0402_10V6KDIS@ C47 0.22U_0402_10V6KDIS@

1 2

C48 0.22U_0402_10V6KDIS@ C48 0.22U_0402_10V6KDIS@

1 2

C49 0.22U_0402_10V6KDIS@ C49 0.22U_0402_10V6KDIS@

1 2

C50 0.22U_0402_10V6KDIS@ C50 0.22U_0402_10V6KDIS@

1 2

C51 0.22U_0402_10V6KDIS@ C51 0.22U_0402_10V6KDIS@

1 2

C52 0.22U_0402_10V6KDIS@ C52 0.22U_0402_10V6KDIS@

1 2

C53 0.22U_0402_10V6KDIS@ C53 0.22U_0402_10V6KDIS@

1 2

C54 0.22U_0402_10V6KDIS@ C54 0.22U_0402_10V6KDIS@

1 2

C55 0.22U_0402_10V6KDIS@ C55 0.22U_0402_10V6KDIS@

1 2

C56 0.22U_0402_10V6KDIS@ C56 0.22U_0402_10V6KDIS@

1 2

C57 0.22U_0402_10V6KDIS@ C57 0.22U_0402_10V6KDIS@

1 2

C58 0.22U_0402_10V6KDIS@ C58 0.22U_0402_10V6KDIS@

1 2

C59 0.22U_0402_10V6KDIS@ C59 0.22U_0402_10V6KDIS@

1 2

C60 0.22U_0402_10V6KDIS@ C60 0.22U_0402_10V6KDIS@

1 2

C61 0.22U_0402_10V6KDIS@ C61 0.22U_0402_10V6KDIS@

1 2

C62 0.22U_0402_10V6KDIS@ C62 0.22U_0402_10V6KDIS@

1 2

C63 0.22U_0402_10V6KDIS@ C63 0.22U_0402_10V6KDIS@

1 2

C64 0.22U_0402_10V6KDIS@ C64 0.22U_0402_10V6KDIS@

PCIE_GTX_C_CRX_N15

PCIE_GTX_C_CRX_N14

PCIE_GTX_C_CRX_N13

PCIE_GTX_C_CRX_N12

PCIE_GTX_C_CRX_N11

PCIE_GTX_C_CRX_N10

PCIE_GTX_C_CRX_N9

PCIE_GTX_C_CRX_N8

PCIE_GTX_C_CRX_N7

PCIE_GTX_C_CRX_N6

PCIE_GTX_C_CRX_N5

PCIE_GTX_C_CRX_N4

PCIE_GTX_C_CRX_N3

PCIE_GTX_C_CRX_N2

PCIE_GTX_C_CRX_N1

PCIE_GTX_C_CRX_N0

PCIE_GTX_C_CRX_P15

PCIE_GTX_C_CRX_P14

PCIE_GTX_C_CRX_P13

PCIE_GTX_C_CRX_P12

PCIE_GTX_C_CRX_P11

PCIE_GTX_C_CRX_P10

PCIE_GTX_C_CRX_P9

PCIE_GTX_C_CRX_P8

PCIE_GTX_C_CRX_P7

PCIE_GTX_C_CRX_P6

PCIE_GTX_C_CRX_P5

PCIE_GTX_C_CRX_P4

PCIE_GTX_C_CRX_P3

PCIE_GTX_C_CRX_P2

PCIE_GTX_C_CRX_P1

PCIE_GTX_C_CRX_P0

PCIE_CTX_C_GRX_N15

PCIE_CTX_C_GRX_N14

PCIE_CTX_C_GRX_N13

PCIE_CTX_C_GRX_N12

PCIE_CTX_C_GRX_N11

PCIE_CTX_C_GRX_N10

PCIE_CTX_C_GRX_N9

PCIE_CTX_C_GRX_N8

PCIE_CTX_C_GRX_N7

PCIE_CTX_C_GRX_N6

PCIE_CTX_C_GRX_N5

PCIE_CTX_C_GRX_N4

PCIE_CTX_C_GRX_N3

PCIE_CTX_C_GRX_N2

PCIE_CTX_C_GRX_N1

PCIE_CTX_C_GRX_N0

PCIE_CTX_C_GRX_P15

PCIE_CTX_C_GRX_P14

PCIE_CTX_C_GRX_P13

PCIE_CTX_C_GRX_P12

PCIE_CTX_C_GRX_P11

PCIE_CTX_C_GRX_P10

PCIE_CTX_C_GRX_P9

PCIE_CTX_C_GRX_P8

PCIE_CTX_C_GRX_P7

PCIE_CTX_C_GRX_P6

PCIE_CTX_C_GRX_P5

PCIE_CTX_C_GRX_P4

PCIE_CTX_C_GRX_P3

PCIE_CTX_C_GRX_P2

PCIE_CTX_C_GRX_P1

PCIE_CTX_C_GRX_P0

PCIE_GTX_C_CRX_N[0..15]

PCIE_GTX_C_CRX_P[0..15]

PCIE_CTX_C_GRX_N[0..15]

PCIE_CTX_C_GRX_P[0..15]

20

20

2

UCPU1I

UCPU1I

BG17

VSS[181]

BG21

VSS[182]

BG24

VSS[183]

BG28

VSS[184]

BG37

VSS[185]

BG41

VSS[186]

20

20

BG45

VSS[187]

BG49

VSS[188]

BG53

VSS[189]

BG9

VSS[190]

C29

VSS[191]

C35

VSS[192]

C40

VSS[193]

D10

VSS[194]

D14

VSS[195]

D18

VSS[196]

D22

VSS[197]

D26

VSS[198]

D29

VSS[199]

D35

VSS[200]

D4

VSS[201]

D40

VSS[202]

D43

VSS[203]

D46

VSS[204]

D50

VSS[205]

D54

VSS[206]

D58

VSS[207]

D6

VSS[208]

E25

VSS[209]

E29

VSS[210]

E3

VSS[211]

E35

VSS[212]

E40

VSS[213]

F13

VSS[214]

F15

VSS[215]

F19

VSS[216]

F29

VSS[217]

F35

VSS[218]

F40

VSS[219]

F55

VSS[220]

G51

VSS[221]

G6

VSS[222]

G61

VSS[223]

H10

VSS[224]

H14

VSS[225]

H17

VSS[226]

H21

VSS[227]

H4

VSS[228]

H53

VSS[229]

H58

VSS[230]

J1

VSS[231]

J49

VSS[232]

J55

VSS[233]

K11

VSS[234]

K21

VSS[235]

K51

VSS[236]

K8

VSS[237]

L16

VSS[238]

L20

VSS[239]

L22

VSS[240]

L26

VSS[241]

L30

VSS[242]

L34

VSS[243]

L38

VSS[244]

L43

VSS[245]

L48

VSS[246]

L61

VSS[247]

M11

VSS[248]

M15

VSS[249]

IVY-BRIDGE_BGA1023

IVY-BRIDGE_BGA1023

@

@

ER01

VSS

VSS

1

VSS_NCTF_1

VSS_NCTF_2

VSS_NCTF_3

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_8

VSS_NCTF_9

VSS_NCTF_10

VSS_NCTF_11

NCTF

NCTF

VSS_NCTF_12

VSS_NCTF_13

VSS_NCTF_14

VSS[250]

VSS[251]

VSS[252]

VSS[253]

VSS[254]

VSS[255]

VSS[256]

VSS[257]

VSS[258]

VSS[259]

VSS[260]

VSS[261]

VSS[262]

VSS[263]

VSS[264]

VSS[265]

VSS[266]

VSS[267]

VSS[268]

VSS[269]

VSS[270]

VSS[271]

VSS[272]

VSS[273]

VSS[274]

VSS[275]

VSS[276]

VSS[277]

VSS[278]

VSS[279]

VSS[280]

VSS[281]

VSS[282]

VSS[283]

VSS[284]

VSS[285]

VSS[286]

VSS[287]

VSS[288]

VSS[289]

VSS[290]

VSS[291]

VSS[292]

VSS[293]

VSS[294]

VSS[295]

VSS[296]

VSS[297]

VSS[298]

VSS[299]

VSS[300]

VSS[301]

M4

M58

M6

N1

N17

N21

N25

N28

N33

N36

N40

N43

N47

N48

N51

N52

N56

N61

P14

P16

P18

P21

P58

P59

P9

R17

R20

R4

R46

T1

T47

T50

T51

T52

T53

T55

T56

U13

U8

V20

V61

W13

W15

W18

W21

W46

W8

Y4

Y47

Y58

Y59

G48

A5

A57

BC61

BD3

BD59

BE4

BE58

BG5

BG57

C3

C58

D59

E1

E61

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

3

2011/07/12 2012/12/31

2011/07/12 2012/12/31

2011/07/12 2012/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

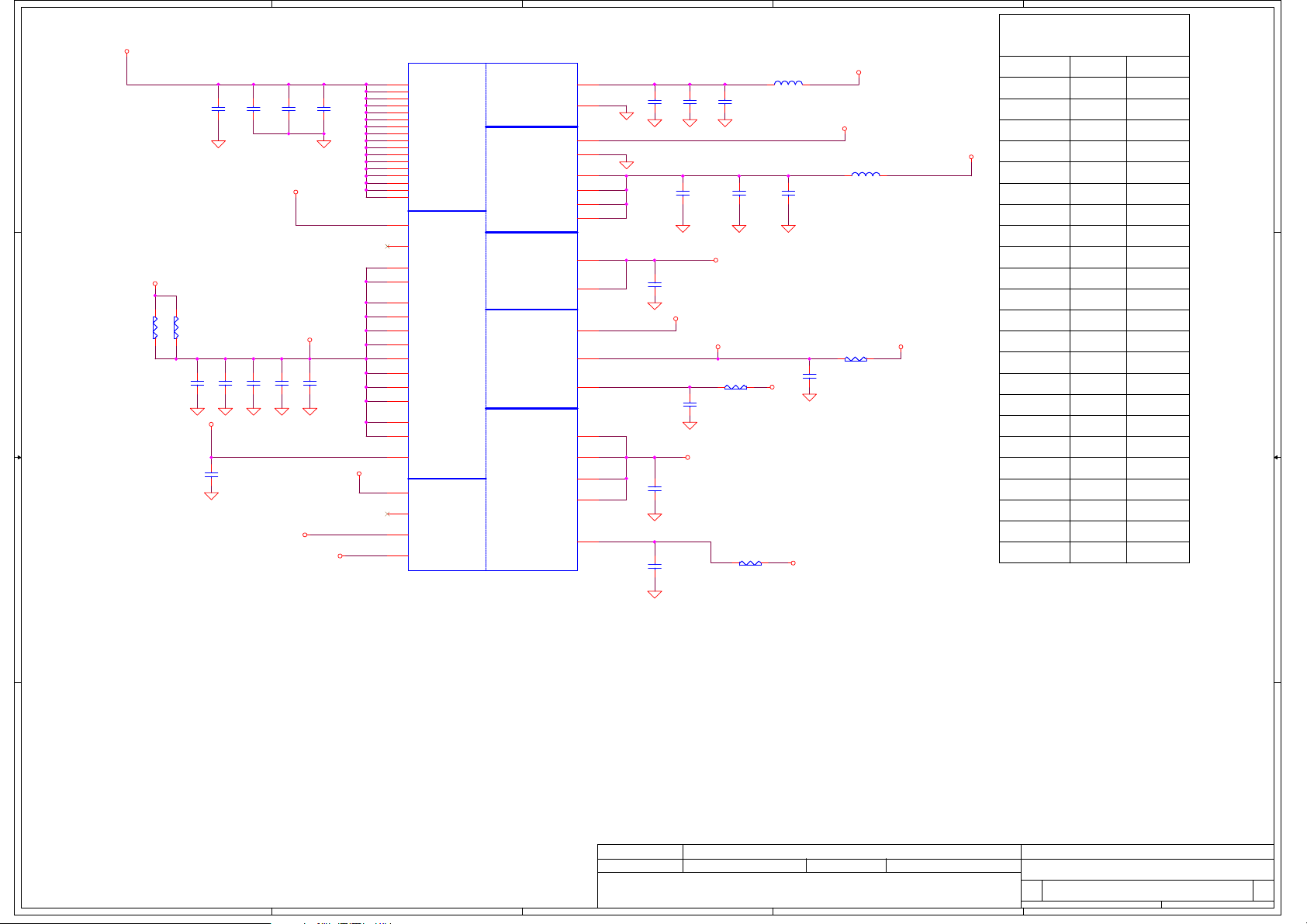

PROCESSOR(1/6) DMI,FDI,PEG

PROCESSOR(1/6) DMI,FDI,PEG

PROCESSOR(1/6) DMI,FDI,PEG

LA-8226P

LA-8226P

LA-8226P

1

4 58Monday, July 09, 2012

4 58Monday, July 09, 2012

4 58Monday, July 09, 2012

1.0

1.0

1.0

Page 5

5

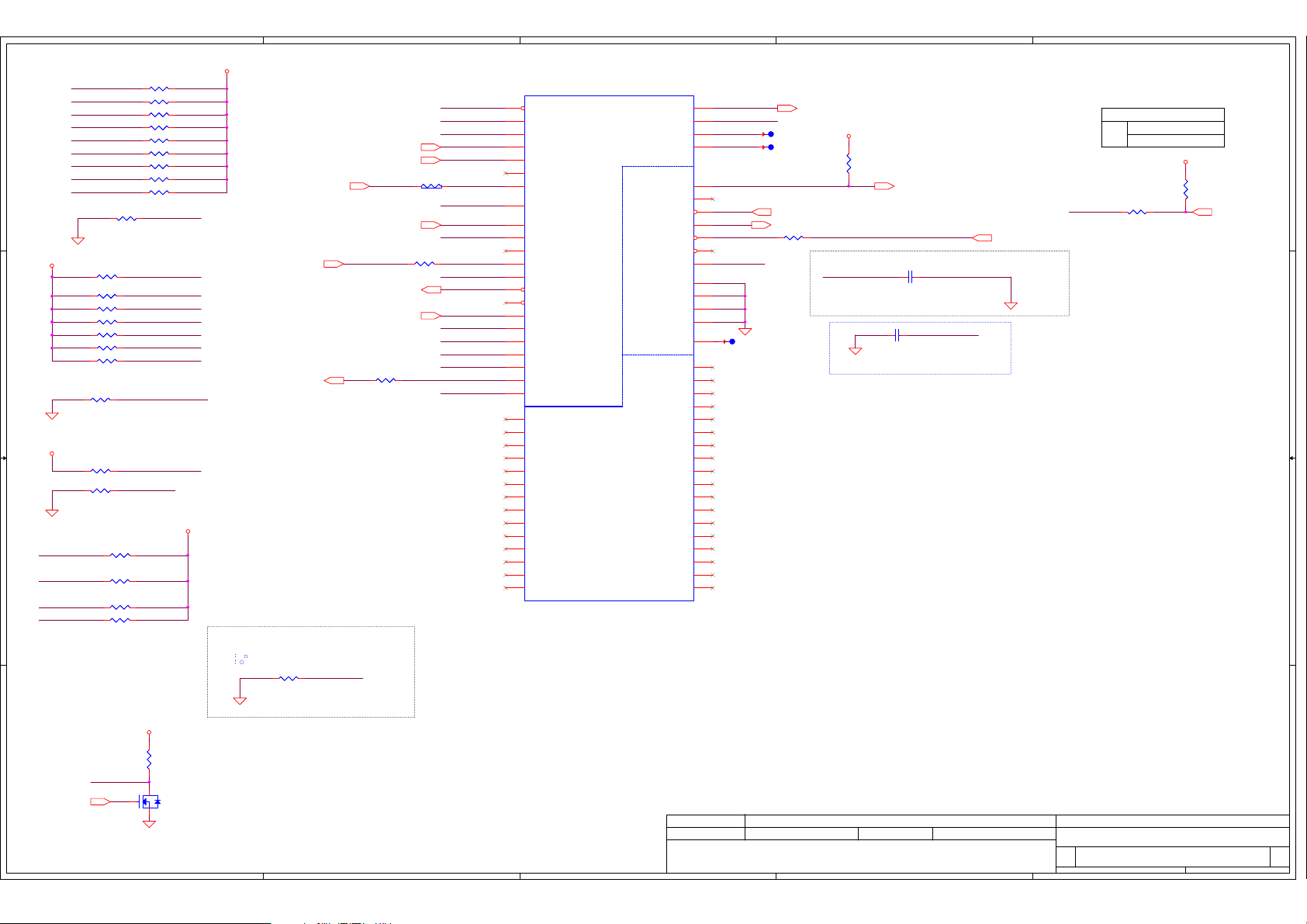

Processor Pullups

H_PROCHOT#

D D

@

@

1 2

1 2

C68 100P_0402_50V8J

C68 100P_0402_50V8J

H_PECI

+1.05VS

R1662_0402_5% R1662_0402_5%

Reserve for EMI please close to JCPU1

4

3

1 2

R9

14

SYSTEM_PWROK

PM_DRAM_PWR GD14

+3V_PCH

200_0402_1%

200_0402_1%

R9

1 2

R14

R14

2

+3VS

12

10K_0402_5%

10K_0402_5%

0_0402_5%@

0_0402_5%@

1 2

R11 0_0402_5%R11 0_0402_5%

R3

R3

S_PWG

D_PWG

+3V_PCH

R576

R576

1 2

0_0402_5%

0_0402_5%

1

2

ER03

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

2

5

U1

U1

P

A

4

O

B

G

74AHC1G09GW TSSOP 5P

74AHC1G09GW TSSOP 5P

3

1

+1.5V_CPU_VDDQ

C65

C65

12

R4

R4

200_0402_1%

200_0402_1%

VDDPWRGOOD

UCPU1B

UCPU1B

MISC THERMAL PWR MANAGEMENT

16

H_SNB_IVB#

C C

R23

R23

H_THERMTRIP#

R684

R684

1 2

33_0402_5%

33_0402_5%

R36

R36

H_CATERR#

H_PECI

H_PROCHOT#_R

H_PM_SYNC

H_CPUPWRGD_R

VDDPWRGOOD_R

BUF_CPU_RST#

T1

T1

PAD @

PAD @

39

H_PECI

H_CPUPWRGD

1 2

56_0402_5%

56_0402_5%

1 2

130_0402_1%

130_0402_1%

H_PROCHOT#39

16

H_THERMTRIP#

14

H_PM_SYNC

B B

H_CPUPWRGD16

VDDPWRGOOD

F49

PROC_SELECT#

C57

PROC_DETECT#

C49

CATERR#

A48

PECI

C45

PROCHOT#

D45

THERMTRIP#

C48

PM_SYNC

B46

UNCOREPWRGOOD

BE45

SM_DRAMPWR OK

D44

RESET#

MISC THERMAL PWR MANAGEMENT

DPLL_REF_CLK

DPLL_REF_CLK#

CLOCKS

CLOCKS

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

DDR3

MISC

DDR3

MISC

JTAG & BPM

JTAG & BPM

BCLK

BCLK#

PRDY#

PREQ#

TCK

TMS

TRST#

TDO

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

TDI

J3

CLK_CPU_DMI_R

H2

CLK_CPU_DMI#_R

AG3

CLK_CPU_DPLL_R

AG1

CLK_CPU_DPLL#_R

AT30

H_DRAMRST#

BF44

SM_RCOMP0

BE43

SM_RCOMP1

BG43

SM_RCOMP2

N53

XDP_PRDY#

N55

XDP_PREQ#

L56

XDP_TCK

L55

XDP_TMS

J58

XDP_TRST#

M60

XDP_TDI_R

L59

XDP_TDO_R

K58

XDP_DBRESET#_R1

G58

E55

E59

G55

G59

H60

J59

J61

1 2

R18 0_0402_5%R18 0_0402_5%

1 2

R19 0_0402_5%R19 0_0402_5%

H_DRAMRST#

1 2

R37 0_0402_5%R37 0_0402_5%

6

CLK_CPU_DMI

CLK_CPU_DMI#

XDP_DBRESET#_R

13

13

PLT_RST#15,32,39,40

14

XDP_DBRESET#_R1

H_CPUPWRGD_R

+3VS

1

5

P

NC

A2Y

G

SN74LVC1G07DCKR_SC70-5

SN74LVC1G07DCKR_SC70-5

3

1 2

R241K_0402_5% R241K_0402_5%

1 2

R2510K_0402_5% R2510K_0402_5%

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C69

C69

2

U2

U2

4

BUFO_CPU_RST# BUF_CPU_RST#

+3VS

DDR3 Compensation Signals

IVY-BRIDGE_BGA1023

IVY-BRIDGE_BGA1023

@

@

ER01

1 2

@

@

C70 100P_0402_50V8J

C70 100P_0402_50V8J

H_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

1 2

1 2

1 2

R34140_0402_1% R34140_0402_1%

R3825.5_0402_1% R3825.5_0402_1%

R39200_0402_1% R39200_0402_1%

+1.05VS

12

R15

R15

75_0402_5%

75_0402_5%

R17

R17

1 2

43_0402_1%

43_0402_1%

12

R21

R21

CLK_CPU_DPLL#_R

CLK_CPU_DPLL_R

1 2

1 2

R22

R22

PU/PD for JTAG signals

XDP_TMS

XDP_TDI_R

XDP_PREQ#

XDP_TDO_R

XDP_TCK

XDP_TRST#

1 2

1 2

1 2

1 2

1 2

1 2

@

@

R20

R20

0_0402_5%

0_0402_5%

1K_0402_1%

1K_0402_1%

1K_0402_1%

1K_0402_1%

+1.05VS

+1.05VS

R2651_0402_5% R2651_0402_5%

R2751_0402_5% R2751_0402_5%

R2851_0402_5% @ R2851_0402_5% @

R2951_0402_5% R2951_0402_5%

R3251_0402_5% R3251_0402_5%

R3351_0402_5% R3351_0402_5%

Reserve for EMI please close to JCPU1

1 2

1 2

VDDPWRGOOD_R

H_CPUPWRGD_R

5

1 2

@

@

C426 100P_0402_50V8J

C426 100P_0402_50V8J

BUF_CPU_RST#

Reserve for EMI please close to JCPU1

4

1 2

@

@

C71 100P_0402_50V8J

C71 100P_0402_50V8J

XDP_DBRESET#_R1

Reserve for EMI please close to JCPU1

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

3

2011/07/12 2012/12/31

2011/07/12 2012/12/31

2011/07/12 2012/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Custom

Custom

Custom

Date: Sheet

Date: Sheet of

2

Date: Sheet of

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Compal Electronics, Inc.

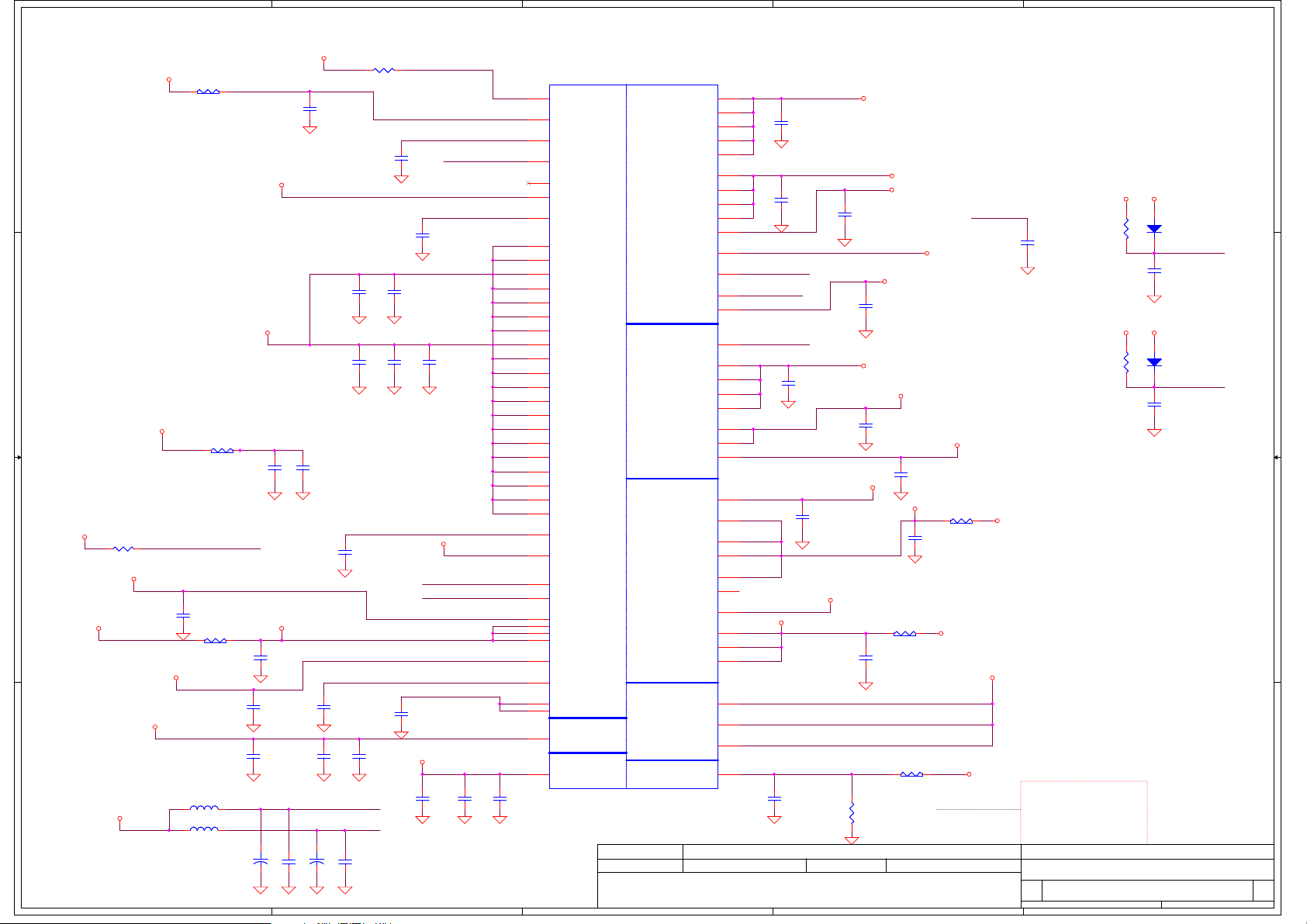

PROCESSOR(2/6) PM,XDP,CLK

PROCESSOR(2/6) PM,XDP,CLK

PROCESSOR(2/6) PM,XDP,CLK

LA-8226P

LA-8226P

LA-8226P

1

of

5 58Monday, July 09, 2012

5 58Monday, July 09, 2012

5 58Monday, July 09, 2012

1.0

1.0

1.0

@

@

C72 100P_0402_50V8J

A A

C72 100P_0402_50V8J

Reserve for EMI please close to JCPU1

C421 100P_0402_50V8JC421 100P_0402_50V8J

Reserve for EMI please close to JCPU1

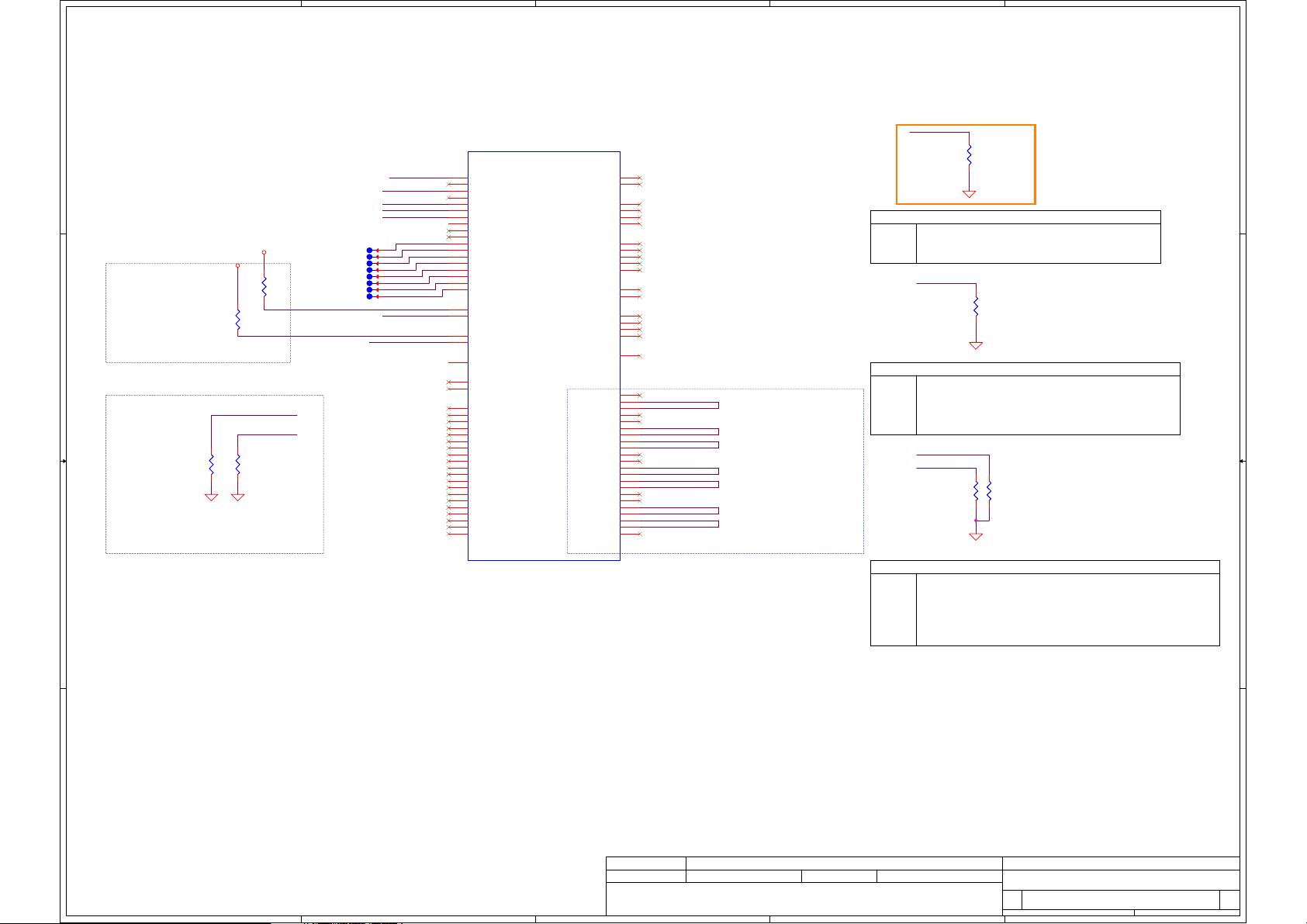

Page 6

5

UCPU1C

10

DDR_A_D[0..63]

D D

C C

10

10

10

10

10

10

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_A_CAS#

DDR_A_RAS#

DDR_A_WE#

B B

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

UCPU1C

AG6

SA_DQ[0]

AJ6

SA_DQ[1]

AP11

SA_DQ[2]

AL6

SA_DQ[3]

AJ10

SA_DQ[4]

AJ8

SA_DQ[5]

AL8

SA_DQ[6]

AL7

SA_DQ[7]

AR11

SA_DQ[8]

AP6

SA_DQ[9]

AU6

SA_DQ[10]

AV9

SA_DQ[11]

AR6

SA_DQ[12]

AP8

SA_DQ[13]

AT13

SA_DQ[14]

AU13

SA_DQ[15]

BC7

SA_DQ[16]

BB7

SA_DQ[17]

BA13

SA_DQ[18]

BB11

SA_DQ[19]

BA7

SA_DQ[20]

BA9

SA_DQ[21]

BB9

SA_DQ[22]

AY13

SA_DQ[23]

AV14

SA_DQ[24]

AR14

SA_DQ[25]

AY17

SA_DQ[26]

AR19

SA_DQ[27]

BA14

SA_DQ[28]

AU14

SA_DQ[29]

BB14

SA_DQ[30]

BB17

SA_DQ[31]

BA45

SA_DQ[32]

AR43

SA_DQ[33]

AW48

SA_DQ[34]

BC48

SA_DQ[35]

BC45

SA_DQ[36]

AR45

SA_DQ[37]

AT48

SA_DQ[38]

AY48

SA_DQ[39]

BA49

SA_DQ[40]

AV49

SA_DQ[41]

BB51

SA_DQ[42]

AY53

SA_DQ[43]

BB49

SA_DQ[44]

AU49

SA_DQ[45]

BA53

SA_DQ[46]

BB55

SA_DQ[47]

BA55

SA_DQ[48]

AV56

SA_DQ[49]

AP50

SA_DQ[50]

AP53

SA_DQ[51]

AV54

SA_DQ[52]

AT54

SA_DQ[53]

AP56

SA_DQ[54]

AP52

SA_DQ[55]

AN57

SA_DQ[56]

AN53

SA_DQ[57]

AG56

SA_DQ[58]

AG53

SA_DQ[59]

AN55

SA_DQ[60]

AN52

SA_DQ[61]

AG55

SA_DQ[62]

AK56

SA_DQ[63]

BD37

SA_BS[0]

BF36

SA_BS[1]

BA28

SA_BS[2]

BE39

SA_CAS#

BD39

SA_RAS#

AT41

SA_WE#

IVY-BRIDGE_BGA1023

IVY-BRIDGE_BGA1023

@

@

ER01

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_CK[0]

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

4

AU36

AV36

AY26

AT40

AU40

BB26

BB40

BC41

AY40

BA41

AL11

AR8

AV11

AT17

AV45

AY51

AT55

AK55

AJ11

AR10

AY11

AU17

AW45

AV51

AT56

AK54

BG35

BB34

BE35

BD35

AT34

AU34

BB32

AT32

AY32

AV32

BE37

BA30

BC30

AW41

AY28

AU26

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDRA_CLK0

DDRA_CLK0#

DDRA_CKE0

DDRA_CLK1

DDRA_CLK1#

DDRA_CKE1

DDRA_SCS0#

DDRA_SCS1#

DDRA_ODT0

DDRA_ODT1

DDR_A_DQS#[0..7]

DDR_A_DQS[0..7]

DDR_A_MA[0..15]

3

11

10

10

10

10

10

10

10

10

10

10

10

10

10

DDR_B_D[0..63]

11

DDR_B_BS0

11

DDR_B_BS1

11

DDR_B_BS2

11

DDR_B_CAS#

11

DDR_B_RAS#

11

DDR_B_WE#

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

2

UCPU1D

UCPU1D

AL4

SB_DQ[0]

AL1

SB_DQ[1]

AN3

SB_DQ[2]

AR4

SB_DQ[3]

AK4

SB_DQ[4]

AK3

SB_DQ[5]

AN4

SB_DQ[6]

AR1

SB_DQ[7]

AU4

SB_DQ[8]

AT2

SB_DQ[9]

AV4

SB_DQ[10]

BA4

SB_DQ[11]

AU3

SB_DQ[12]

AR3

SB_DQ[13]

AY2

SB_DQ[14]

BA3

SB_DQ[15]

BE9

SB_DQ[16]

BD9

SB_DQ[17]

BD13

SB_DQ[18]

BF12

SB_DQ[19]

BF8

SB_DQ[20]

BD10

SB_DQ[21]

BD14

SB_DQ[22]

BE13

SB_DQ[23]

BF16

SB_DQ[24]

BE17

SB_DQ[25]

BE18

SB_DQ[26]

BE21

SB_DQ[27]

BE14

SB_DQ[28]

BG14

SB_DQ[29]

BG18

SB_DQ[30]

BF19

SB_DQ[31]

BD50

SB_DQ[32]

BF48

SB_DQ[33]

BD53

SB_DQ[34]

BF52

SB_DQ[35]

BD49

SB_DQ[36]

BE49

SB_DQ[37]

BD54

SB_DQ[38]

BE53

SB_DQ[39]

BF56

SB_DQ[40]

BE57

SB_DQ[41]

BC59

SB_DQ[42]

AY60

SB_DQ[43]

BE54

SB_DQ[44]

BG54

SB_DQ[45]

BA58

SB_DQ[46]

AW59

SB_DQ[47]

AW58

SB_DQ[48]

AU58

SB_DQ[49]

AN61

SB_DQ[50]

AN59

SB_DQ[51]

AU59

SB_DQ[52]

AU61

SB_DQ[53]

AN58

SB_DQ[54]

AR58

SB_DQ[55]

AK58

SB_DQ[56]

AL58

SB_DQ[57]

AG58

SB_DQ[58]

AG59

SB_DQ[59]

AM60

SB_DQ[60]

AL59

SB_DQ[61]

AF61

SB_DQ[62]

AH60

SB_DQ[63]

BG39

SB_BS[0]

BD42

SB_BS[1]

AT22

SB_BS[2]

AV43

SB_CAS#

BF40

SB_RAS#

BD45

SB_WE#

IVY-BRIDGE_BGA1023

IVY-BRIDGE_BGA1023

@

@

SB_CK[0]

SB_CK#[0]

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

ER01

BA34

AY34

AR22

BA36

BB36

BF27

BE41

BE47

AT43

BG47

AL3

AV3

BG11

BD17

BG51

BA59

AT60

AK59

AM2

AV1

BE11

BD18

BE51

BA61

AR59

AK61

BF32

BE33

BD33

AU30

BD30

AV30

BG30

BD29

BE30

BE28

BD43

AT28

AV28

BD46

AT26

AU22

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

1

DDRB_CLK0

DDRB_CLK0#

DDRB_CKE0

DDRB_CLK1

DDRB_CLK1#

DDRB_CKE1

DDRB_SCS0#

DDRB_SCS1#

DDRB_ODT0

DDRB_ODT1

DDR_B_DQS#[0..7]

DDR_B_DQS[0..7]

DDR_B_MA[0..15]

11

11

11

11

11

11

11

11

11

11

11

11

11

+1.5V

12

R40

R40

1K_0402_5%

ER03

R440_0402_5% R440_0402_5%

1K_0402_5%

4

EC_DRAMRST_CNTRL_PCH39

Instant ON

1 2

R41 1K_0402_5%R41 1K_0402_5%

DDR3_DRAMRST#

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

10,11

Compal Secret Data

Compal Secret Data

2011/07/12 2012/12/31

2011/07/12 2012/12/31

2011/07/12 2012/12/31

3

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(3/6) DDRIII

PROCESSOR(3/6) DDRIII

PROCESSOR(3/6) DDRIII

LA-8226P

LA-8226P

LA-8226P

1

6 58Monday, July 09, 2012

6 58Monday, July 09, 2012

6 58Monday, July 09, 2012

1.0

1.0

1.0

Q6

Q6

BSS138_SOT23

BSS138_SOT23

D

S

D

S

H_DRAMRST#5

A A

H_DRAMRST# DDR3_DRAMRST#_R

12

R42

R42

4.99K_0402_1%

4.99K_0402_1%

5

13

G

G

2

1

C73

C73

0.047U_0402_16V4Z

0.047U_0402_16V4Z

2

1 2

Page 7

5

4

3

2

1

CFG Straps for Processor

D D

UCPU1E

UCPU1E

CFG0

CFG2

CFG4

CFG5

CFG6

+VCC_GFXCORE_AXG

PR02

49.9_0402_1%

49.9_0402_1%

C C

Please place as close as JCPU1

R51

R51

49.9_0402_1%

49.9_0402_1%

@

@

+VCC_CORE

12

R46

R46

@

@

VSS_AXG_VAL_SENSE

VSS_VAL_SENSE

12

12

@

@

12

R48

R48

49.9_0402_1%

49.9_0402_1%

@

@

R52

R52

49.9_0402_1%

49.9_0402_1%

T38PAD @T38PAD @

T39PAD @T39PAD @

T40PAD @T40PAD @

T41PAD @T41PAD @

T42PAD @T42PAD @

T43PAD @T43PAD @

T10PAD @T10PAD @

T11PAD @T11PAD @

VCC_VAL_SENSE

VCC_AXG_VAL_SENSE

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

VSS_VAL_SENSE

VSS_AXG_VAL_SENSE

Please place as close as JCPU1

B B

B50

CFG[0]

C51

CFG[1]

B54

CFG[2]

D53

CFG[3]

A51

CFG[4]

C53

CFG[5]

C55

CFG[6]

H49

CFG[7]

A55

CFG[8]

H51

CFG[9]

K49

CFG[10]

K53

CFG[11]

F53

CFG[12]

G53

CFG[13]

L51

CFG[14]

F51

CFG[15]

D52

CFG[16]

L53

CFG[17]

H43

VCC_VAL_SENSE

K43

VSS_VAL_SENSE

H45

VAXG_VAL_SENSE

K45

VSSAXG_VAL_SENSE

F48

VCC_DIE_SENSE

H48

RSVD6

K48

RSVD7

BA19

RSVD8

AV19

RSVD9

AT21

RSVD10

BB21

RSVD11

BB19

RSVD12

AY21

RSVD13

BA22

RSVD14

AY22

RSVD15

AU19

RSVD16

AU21

RSVD17

BD21

RSVD18

BD22

RSVD19

BD25

RSVD20

BD26

RSVD21

BG22

RSVD22

BE22

RSVD23

BG26

RSVD24

BE26

RSVD25

BF23

RSVD26

BE24

RSVD27

IVY-BRIDGE_BGA1023

IVY-BRIDGE_BGA1023

@

@

ER01

RESERVED

RESERVED

DC_TEST_A58

DC_TEST_A59

DC_TEST_C59

DC_TEST_A61

DC_TEST_C61

DC_TEST_D61

DC_TEST_BD61

DC_TEST_BE61

DC_TEST_BE59

DC_TEST_BG61

DC_TEST_BG59

DC_TEST_BG58

DC_TEST_BG4

DC_TEST_BG3

DC_TEST_BE3

DC_TEST_BG1

DC_TEST_BE1

DC_TEST_BD1

BCLK_ITP

BCLK_ITP#

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

DC_TEST_A4

DC_TEST_C4

DC_TEST_D3

DC_TEST_D1

N59

N58

N42

L42

L45

L47

M13

M14

U14

W14

P13

AT49

K24

AH2

AG13

AM14

AM15

N50

A4

C4

D3

D1

A58

A59

C59

A61

C61

D61

BD61

BE61

BE59

BG61

BG59

BG58

BG4

BG3

BE3

BG1

BE1

BD1

ER01

DC_TEST_C4_D3

DC_TEST_A59_C59

DC_TEST_A61_C61

DC_TEST_BE59_BE61

DC_TEST_BG59_BG61

DC_TEST_BE3_BG3

DC_TEST_BE1_BG1

These pins are for solder joint

reliability and non-critical to

function. For BGA only.

PEG Static Lane Reversal - CFG2 is for the 16x

Display Port Presence Strap

PCIE Port Bifurcation Straps

CFG[6:5]

CFG2

12

R45

R45

1K_0402_1%

1K_0402_1%

1:(Default) Nor mal Operation; L ane #

CFG2

definition matc hes socket pin m ap definition

0:Lane Reversed

CFG4

12

R47

@R47

@

1K_0402_1%

1K_0402_1%

1 : Disabled; N o Physical Displ ay Port

CFG4

attached to Emb edded Display Po rt

0 : Enabled; An external Displa y Port device i s

connected to th e Embedded Displ ay Port

CFG6

CFG5

12

12

R49

1K_0402_1%

1K_0402_1%

R49

@

@

R50

@R50

@

1K_0402_1%

1K_0402_1%

11: (Default) x 16 - Device 1 fu nctions 1 and 2 disabled

10: x8, x8 - De vice 1 function 1 enabled ; fun ction 2

disabled

01: Reserved - (Device 1 functi on 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functio ns 1 and 2 enab led

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/07/12 2012/12/31

2011/07/12 2012/12/31

2011/07/12 2012/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(4/6) RSVD,CFG

PROCESSOR(4/6) RSVD,CFG

PROCESSOR(4/6) RSVD,CFG

LA-8226P

LA-8226P

LA-8226P

7 58Monday, July 09, 2012

7 58Monday, July 09, 2012

7 58Monday, July 09, 2012

1

1.0

1.0

1.0

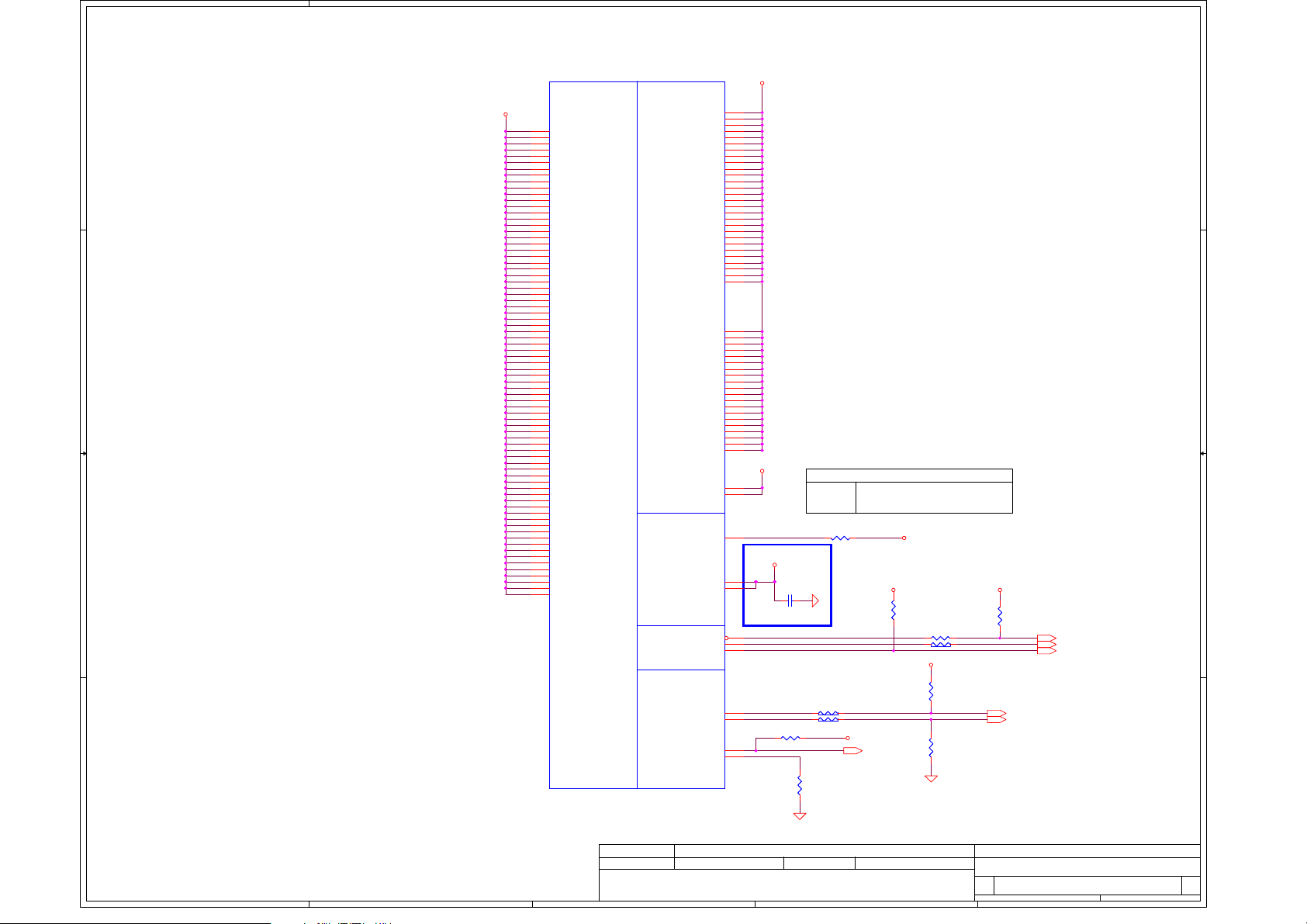

Page 8

5

4

3

2

1

POWER

ER01

POWER

CORE SUPPLY

CORE SUPPLY

VCCIO[1]

VCCIO[3]

VCCIO[4]

VCCIO[5]

VCCIO[6]

VCCIO[7]

VCCIO[8]

VCCIO[9]

VCCIO[10]

VCCIO[11]

VCCIO[12]

VCCIO[13]

VCCIO[14]

VCCIO[15]

VCCIO[16]

VCCIO[17]

VCCIO[18]

VCCIO[19]

VCCIO[20]

VCCIO[21]

VCCIO[22]

VCCIO[23]

VCCIO[24]

VCCIO[25]

VCCIO[26]

VCCIO[27]

VCCIO[28]

VCCIO[29]

VCCIO[30]

VCCIO[31]

VCCIO[32]

PEG IO AND DDR IO

PEG IO AND DDR IO

VCCIO[33]

VCCIO[34]

VCCIO[35]

VCCIO[36]

VCCIO[37]

VCCIO[38]

VCCIO[39]

VCCIO[40]

VCCIO[41]

VCCIO[42]

VCCIO[43]

VCCIO[44]

VCCIO[45]

VCCIO[46]

VCCIO[47]

VCCIO[48]

VCCIO[49]

VCCIO50

VCCIO51

VCCIO_SEL

VCCPQE[1]

VCCPQE[2]

RAILS

RAILS

VIDALERT#

VIDSCLK

VIDSOUT

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

SENSE LINES SVID QUIET

SENSE LINES SVID QUIET

UCPU1F

ULV type

DC 33A

D D

+VCC_CORE

INTEL Recommend VCC

4*470UF,12*22uF(0805) and 35*2.2uF(0402)

PD0.8

CAP at P.51

C C

B B

A A

UCPU1F

A26

VCC[1]

A29

VCC[2]

A31

VCC[3]

A34

VCC[4]

A35

VCC[5]

A38

VCC[6]

A39

VCC[7]

A42

VCC[8]

C26

VCC[9]

C27

VCC[10]

C32

VCC[11]

C34

VCC[12]

C37

VCC[13]

C39

VCC[14]

C42

VCC[15]

D27

VCC[16]

D32

VCC[17]

D34

VCC[18]

D37

VCC[19]

D39

VCC[20]

D42

VCC[21]

E26

VCC[22]

E28

VCC[23]

E32

VCC[24]

E34

VCC[25]

E37

VCC[26]

E38

VCC[27]

F25

VCC[28]

F26

VCC[29]

F28

VCC[30]

F32

VCC[31]

F34

VCC[32]

F37

VCC[33]

F38

VCC[34]

F42

VCC[35]

G42

VCC[36]

H25

VCC[37]

H26

VCC[38]

H28

VCC[39]

H29

VCC[40]

H32

VCC[41]

H34

VCC[42]

H35

VCC[43]

H37

VCC[44]

H38

VCC[45]

H40

VCC[46]

J25

VCC[47]

J26

VCC[48]

J28

VCC[49]

J29

VCC[50]

J32

VCC[51]

J34

VCC[52]

J35

VCC[53]

J37

VCC[54]

J38

VCC[55]

J40

VCC[56]

J42

VCC[57]

K26

VCC[58]

K27

VCC[59]

K29

VCC[60]

K32

VCC[61]

K34

VCC[62]

K35

VCC[63]

K37

VCC[64]

K39

VCC[66]

K42

VCC[67]

L25

VCC[68]

L28

VCC[69]

L33

VCC[70]

L36

VCC[71]

L40

VCC[72]

N26

VCC[73]

N30

VCC[74]

N34

VCC[75]

N38

VCC[76]

IVY-BRIDGE_BGA1023

IVY-BRIDGE_BGA1023

@

@

+1.05VS

8.5A

AF46

AG48

AG50

AG51

AJ17

AJ21

AJ25

AJ43

AJ47

AK50

AK51

AL14

AL15

AL16

AL20

AL22

AL26

AL45

AL48

AM16

AM17

AM21

AM43

AM47

AN20

AN42

AN45

AN48

AA14

AA15

AB17

AB20

AC13

AD16

AD18

AD21

AE14

AE15

AF16

AF18

AF20

AG15

AG16

AG17

AG20

AG21

AJ14

AJ15

+1.05VS

W16

W17

BC22

VCCIO_SEL

+1.05VS

AM25

AN22

A44

B43

C44

F43

G43

AN16

AN17

1 2

C74

C74

1U_0402_6 .3V6K

1U_0402_6 .3V6K

<BOM Structure>

<BOM Structure>

H_CPU_SVIDALRT#

H_CPU_SVIDCLK

VR_SVID_DAT

Place the PU

resistors close to CPU

VCCSENSE_R

VSSSENSE_R

R60 10_0402_1%R60 10_04 02_1%

INTEL Recommend VCCIO

2*330UF,10*10uF(0603) and 26*1uF(0402)

PD0.8

CAP at P.51

VCCIO_SEL after Ivy bridge ES2 Voltage support

1/NC : (Default) +1.05VS_VTT

BC22

*

0: +1.0VS_VTT

@

@

1 2

R75 10K_0402_5%

R75 10K_0402_5%

ER01

130_0402_ 1%

130_0402_ 1%

1 2

R58 0_0402_5%R58 0_0402_5%

1 2

R59 0_0402_5%R59 0_0402_5%

12

+1.05VS

12

R62

R62

10_0402_1 %

10_0402_1 %

R56

R56

VCCIO_SENSE

12

+3VS

ER01

1 2

R55 43_0402_1%R55 43_0402 _1%

1 2

R53 0_0402_5%R53 0_0402_5%

+VCC_CORE

12

R57

R57

100_0402_ 1%

100_0402_ 1%

12

R61

R61

100_0402_ 1%

100_0402_ 1%

48

+1.05VS+1.05VS

12

Place the PU

resistors close to CPU

R54

R54

75_0402_5 %

75_0402_5 %

VR_SVID_ALRT#

VR_SVID_CLK

VR_SVID_DAT

51

VCCSENSE

51

VSSSENSE

51

51

51

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/07/12 2012/12/31

2011/07/12 2012/12/31

2011/07/12 2012/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(5/6) PWR,BYPASS

PROCESSOR(5/6) PWR,BYPASS

PROCESSOR(5/6) PWR,BYPASS

LA-8226P

LA-8226P

LA-8226P

8 58Monday, July 09, 20 12

8 58Monday, July 09, 20 12

8 58Monday, July 09, 20 12

1

1.0

1.0

1.0

Page 9

5

D D

CPU1.5V_S3_GATE39

1 2

R66 0_0402_5%R66 0_0402_5%

+VCC_GFXCORE_AXG

DC 29A

C C

B B

+VCC_GFXCORE_AXG

12

R67

ER08

C262

C262

330U_D2_2VM_R6M

330U_D2_2VM_R6M

1

C97

C97

12

+

+

2 3

Place TOP IN BGA

C246

C246

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

12

12

C250

C250

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

12

12

5

R67

100_0402_1%

100_0402_1%

R68

R68

100_0402_1%

100_0402_1%

C263

C263

10U_0603_6.3V6M

10U_0603_6.3V6M

12

C254

C254

1U_0402_6.3V6K

1U_0402_6.3V6K

12

C252

C252

10U_0603_6.3V6M

10U_0603_6.3V6M

12

12

+1.8VS_VCCPLL

10U_0603_6.3V6M

10U_0603_6.3V6M

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C95

C95

2

C248

C248

1U_0402_6.3V6K

1U_0402_6.3V6K

12

C251

C251

10U_0603_6.3V6M

10U_0603_6.3V6M

12

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C96

C96

2

C249

C249

1U_0402_6.3V6K

1U_0402_6.3V6K

C247

C247

10U_0603_6.3V6M

10U_0603_6.3V6M

Place near CPU

51

VCC_AXG_SENSE

51

VSS_AXG_SENSE

+1.8VS

Place BOT OUT Conn

+VCCSA

A A

R242

R242

1 2

0_0805_5%

0_0805_5%

@

@

C245

C245

330U_D2_2VM_R6M

330U_D2_2VM_R6M

1

+

+

C85

C85

2 3

ER01

12

Place BOT OUT BGA

C253

C253

12

ER08

@

@

1.2A

6A

2

UCPU1G

UCPU1G

AA46

VAXG[1]

AB47

VAXG[2]

AB50

VAXG[3]

AB51

VAXG[4]

AB52

VAXG[5]

AB53

VAXG[6]

AB55

VAXG[7]

AB56

VAXG[8]

AB58

VAXG[9]

AB59

VAXG[10]

AC61

VAXG[11]

AD47

VAXG[12]

AD48

VAXG[13]

AD50

VAXG[14]

AD51

VAXG[15]

AD52

VAXG[16]

AD53

VAXG[17]

AD55

VAXG[18]

AD56

VAXG[19]

AD58

VAXG[20]

AD59

VAXG[21]

AE46

VAXG[22]

N45

VAXG[23]

P47

VAXG[24]

P48

VAXG[25]

P50

VAXG[26]

P51

VAXG[27]

P52

VAXG[28]

P53

VAXG[29]

P55

VAXG[30]

P56

VAXG[31]

P61

VAXG[32]

T48

VAXG[33]

T58

VAXG[34]

T59

VAXG[35]

T61

VAXG[36]

U46

VAXG[37]

V47

VAXG[38]

V48

VAXG[39]

V50

VAXG[40]

V51

VAXG[41]

V52

VAXG[42]

V53

VAXG[43]

V55

VAXG[44]

V56

VAXG[45]

V58

VAXG[46]

V59

VAXG[47]

W50

VAXG[48]

W51

VAXG[49]

W52

VAXG[50]

W53

VAXG[51]

W55

VAXG[52]

W56

VAXG[53]

W61

VAXG[54]

Y48

VAXG[55]

Y61

VAXG[56]

F45

VAXG_SENSE

G45

VSSAXG_SENSE

BB3

VCCPLL[1]

BC1

VCCPLL[2]

BC4

VCCPLL[3]

L17

VCCSA[1]

L21

VCCSA[2]

N16

VCCSA[3]

N20

VCCSA[4]

N22

VCCSA[5]

P17

VCCSA[6]

P20

VCCSA[7]

R16

VCCSA[8]

R18

VCCSA[9]

R21

VCCSA[10]

U15

VCCSA[11]

V16

VCCSA[12]

V17

VCCSA[13]

V18

VCCSA[14]

V21

VCCSA[15]

W20

VCCSA[16]

IVY-BRIDGE_BGA1023

IVY-BRIDGE_BGA1023

@

@

4

12

R65

R65

100K_0402_5%

100K_0402_5%

RUN_ON_CPU1.5VS3#

61

Q4A

Q4A

2N7002KDWH_SOT363-6

2N7002KDWH_SOT363-6

POWER

POWER

SENSE

SENSE

4

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

VREF

VREF

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

GRAPHICS

GRAPHICS

LINES

LINES

QUIET RAILS

QUIET RAILS

VDDQ_SENSE

1.8V RAIL

1.8V RAIL

VSS_SENSE_VDDQ

VCCSA_SENSE

SENSE LINES

SENSE LINES

SA RAIL

SA RAIL

VCCSA_VID[0]

VCCSA_VID[1]

VCCSA VID

lines

VCCSA VID

lines

ER01

SM_VREF

VDDQ[1]

VDDQ[2]

VDDQ[3]

VDDQ[4]

VDDQ[5]

VDDQ[6]

VDDQ[7]

VDDQ[8]

VDDQ[9]

VDDQ[10]

VDDQ[11]

VDDQ[12]

VDDQ[13]

VDDQ[14]

VDDQ[15]

VDDQ[16]

VDDQ[17]

VDDQ[18]

VDDQ[19]

VDDQ[20]

VDDQ[21]

VDDQ[22]

VDDQ[23]

VDDQ[24]

VDDQ[25]

VDDQ[26]

VCCDQ[1]

VCCDQ[2]

+1.5V_CPU_VDDQ

+1.5V +1.5V_CPU_VDDQ

Q7

+5VALW+5VALW

R63

R63

36.5K_0402_1%

36.5K_0402_1%

1 2

34

Q4B

Q4B

5

2N7002KDWH_SOT363-6

2N7002KDWH_SOT363-6

RUN_ON_CPU1.5VS3#

AY43

BE7

BG7

AJ28

AJ33

AJ36

AJ40

AL30

AL34

AL38

AL42

AM33

AM36

AM40

AN30

AN34

AN38

AR26

AR28

AR30

AR32

AR34

AR36

AR40

AV41

AW26

BA40

BB28

BG33

+1.5V_CPU_VDDQ

AM28

AN26

BC43

BA43

U10

D48

D49

RUN_ON_CPU1.5VS3

+V_DDR_REFA_R

+V_DDR_REFB_R

Q7

AO4304L_SO8

AO4304L_SO8

8

7

6

5

41

+1.5V_CPU_VDDQ

12

0.1U_0402_16V4Z

0.1U_0402_16V4Z

12

1

C149

C149

2

5A

C243

C243

C239

C239

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

12

12

ER01

ER01

12

C75

C75

1U_0402_6.3V6K

1U_0402_6.3V6K

<BOM Structure>

<BOM Structure>

50

H_VCCSA_VID0

50

H_VCCSA_VID1

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC. AND CONTAINS CONF IDENTIAL