Page 1

A

1 1

B

C

D

E

PCA70/61

2 2

LA-7521P

Sugar Bay

REV 0.2

Schematic

3 3

LA-7522P REV 0.1

Intel Processor(Sandy Bridge) / PCH(Cougar Point)

Tuesday, April 12, 2011 Rev 0.2

4 4

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CON SENT O F COMPAL ELECTRONICS, INC.

2010/10/1 2011/11/01

C

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

D

Date: Sheet

Compal Electronics, Inc.

Cover Page

PCA70 LA-7521P M/B

164Tuesday, April 12, 2011

E

0.1

of

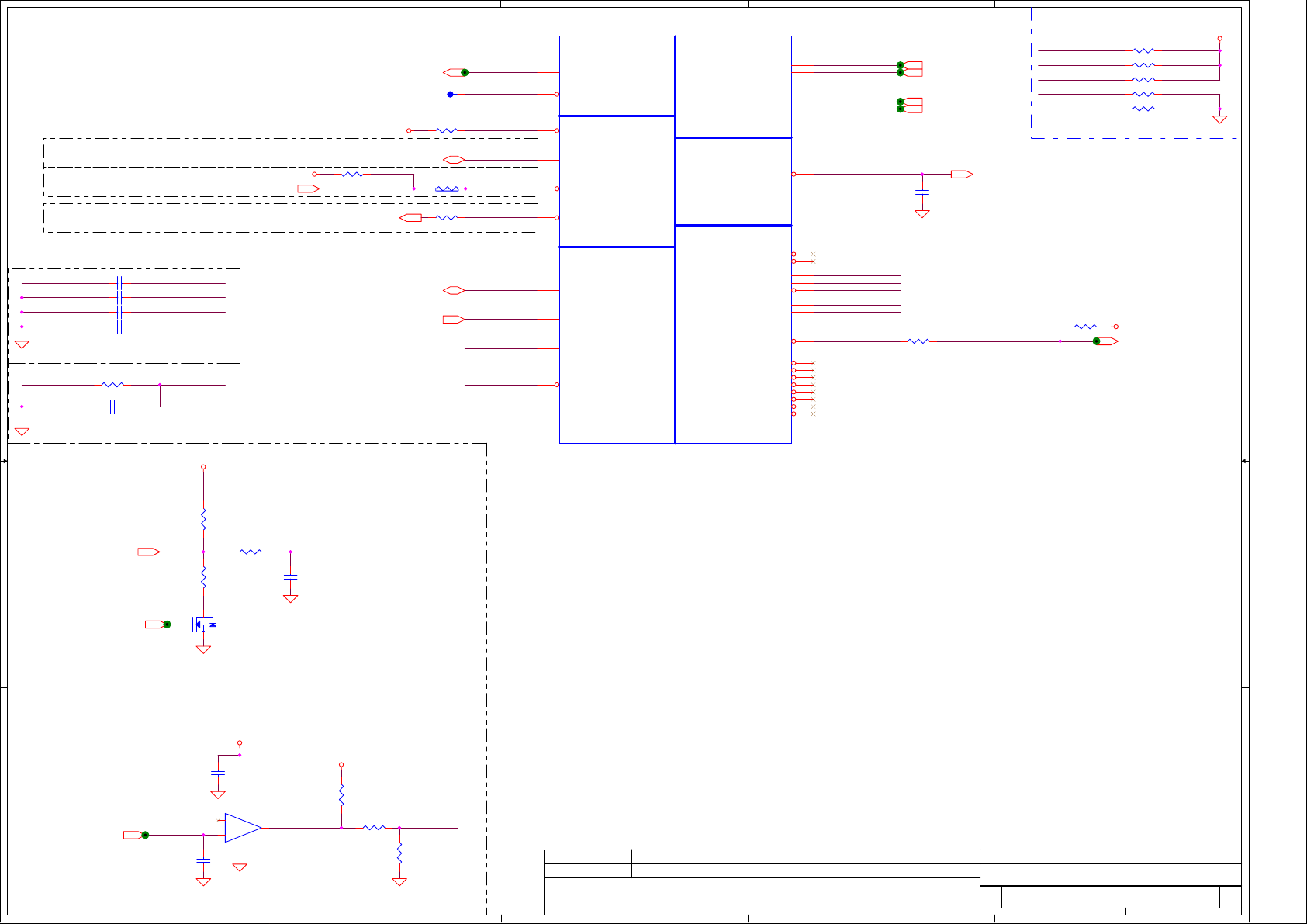

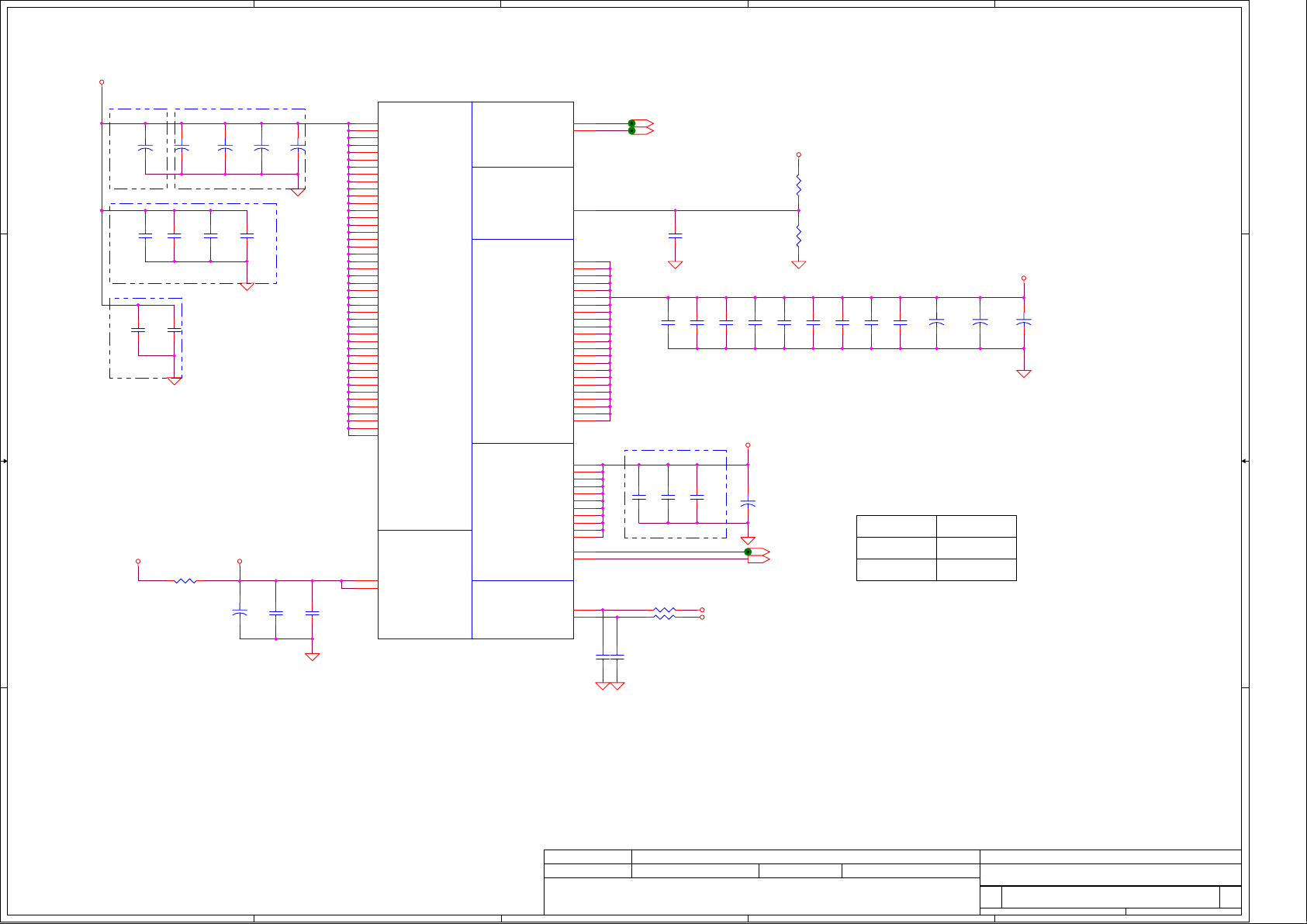

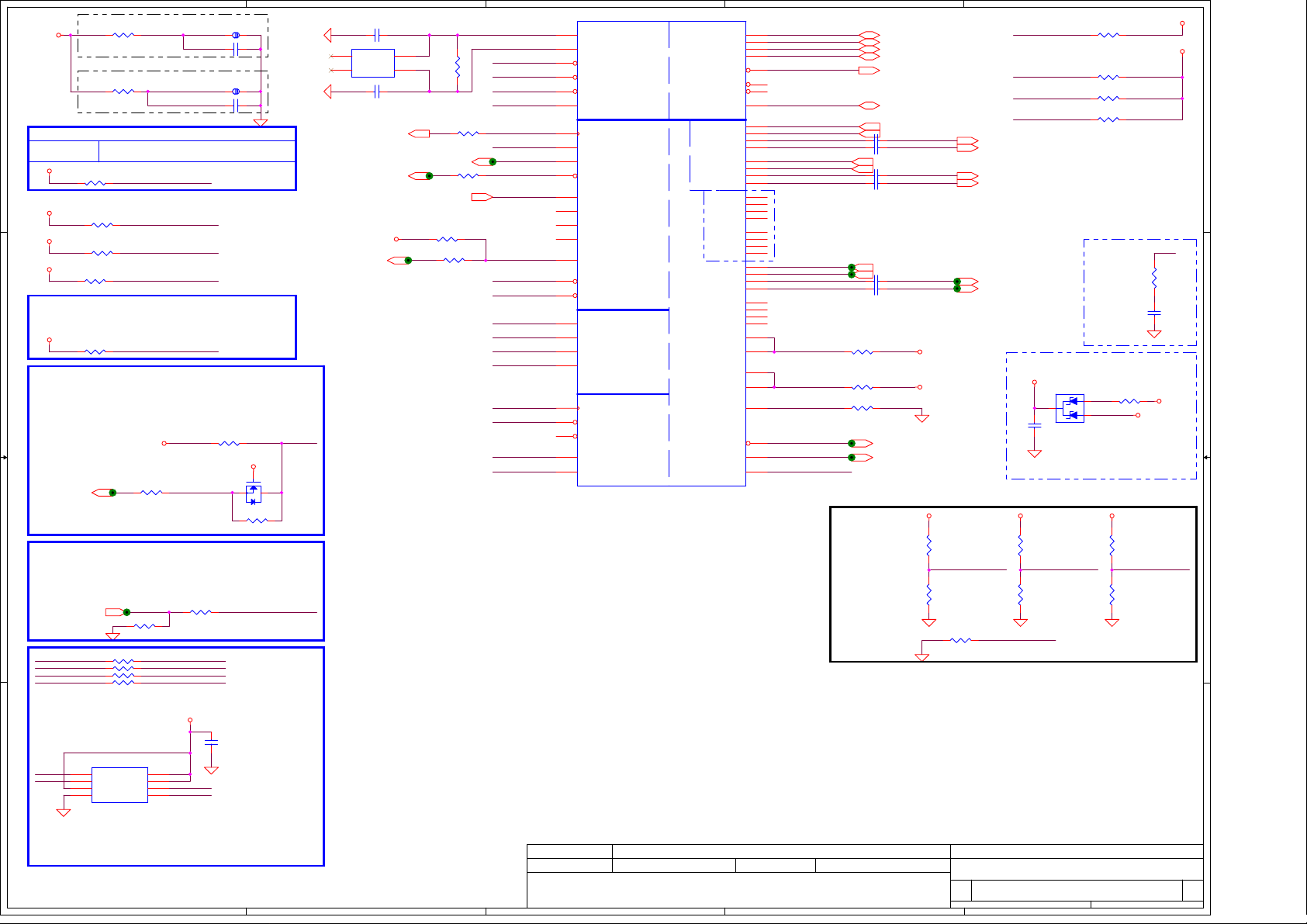

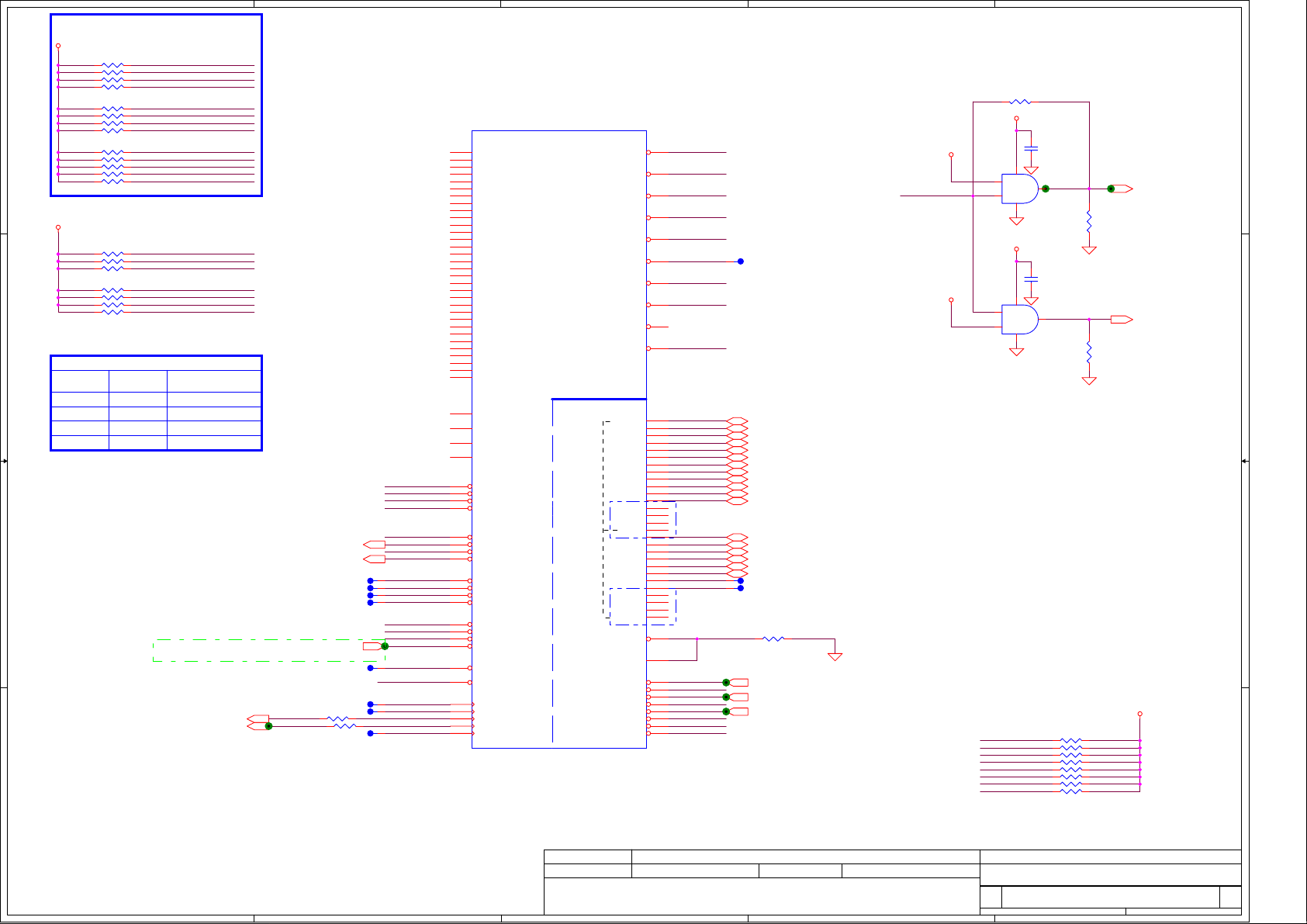

Page 2

A

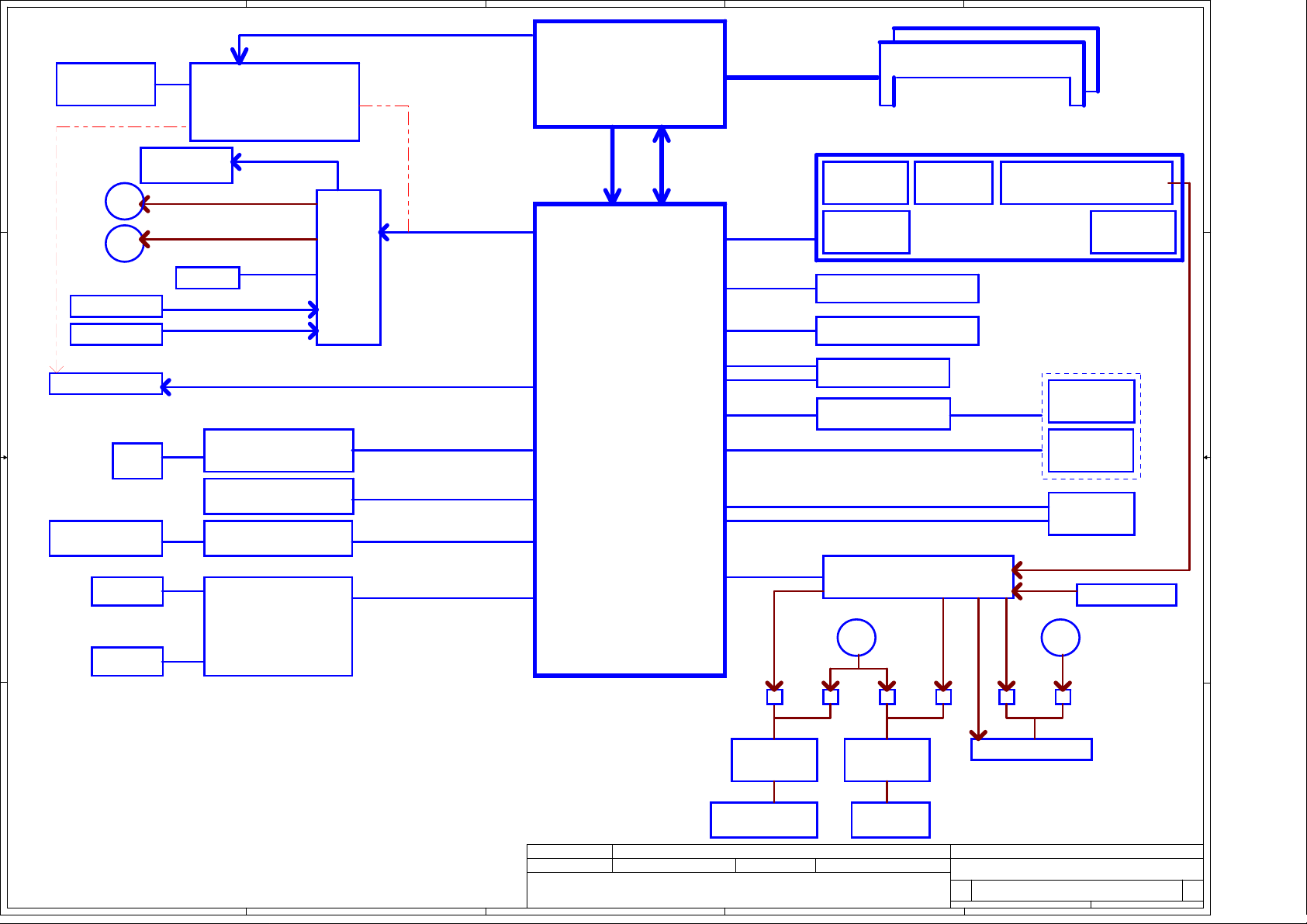

DDR3 VRAM

512M/1GB(GV)

1GB/2GB(GS)

1 1

HDMI(IFPE)

VGA Chip

NV N12P-GV

NV N12P-GS(default)

B

PCI-Express 16X

HDMI

(IFPC)

C

Intel CPU

Sandy Bridge

Desktop

LGA1155

D

Memory BUS(DDRIII)

Dual Channel

1.5V DDRIII 1066/1333 MT/s

E

204pin DDRIII-SO-DIMM X2

H1

2 ch. LVDS

Conn.

LVDS I/F

Scale

RTD2482D

FDI X8

2.7GT/s

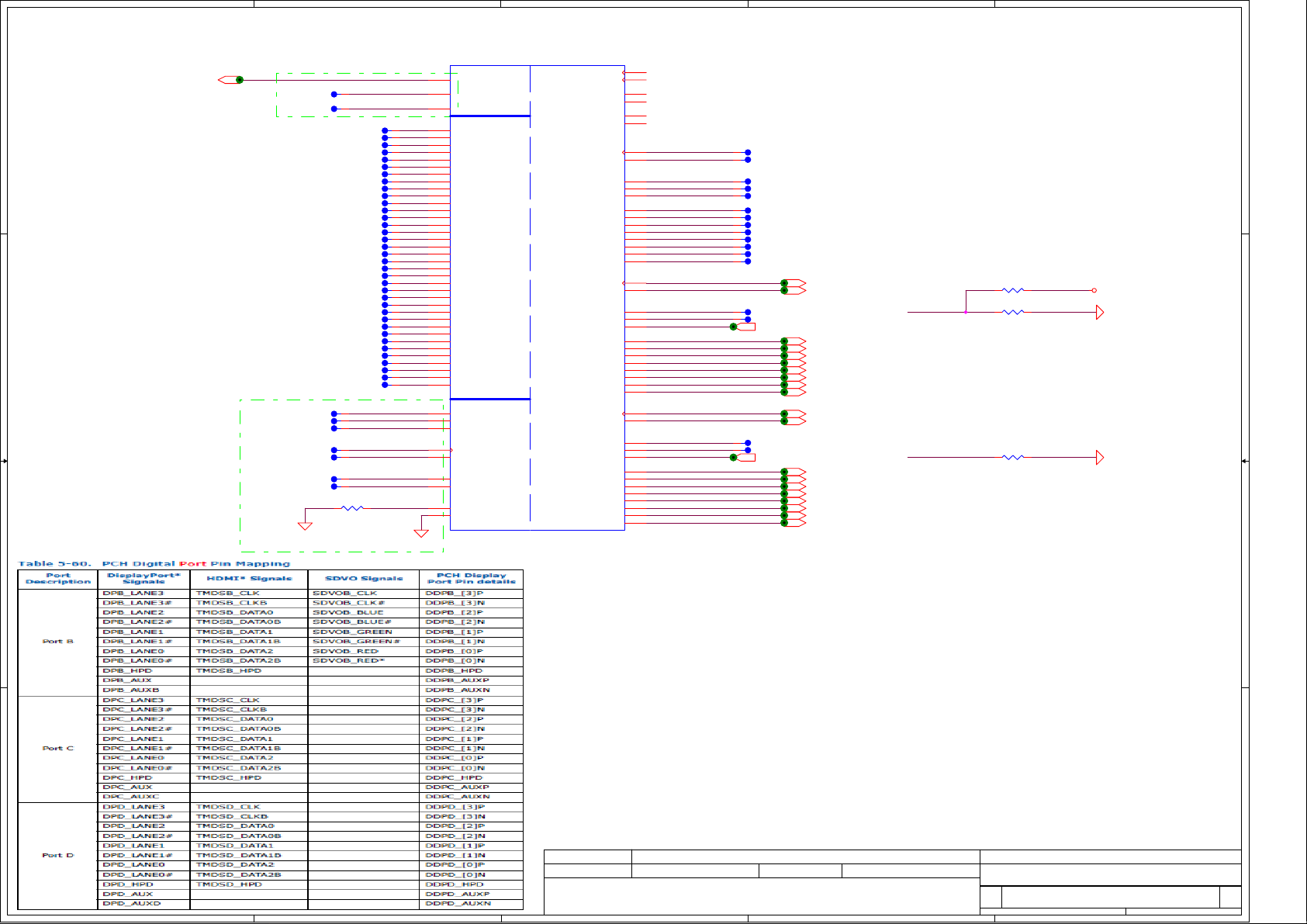

DDPC

DMI X4

5GT/s

USB 2.0 X 6

USB-Port 0 USB-Port 1

USB-Port 2

0.3MP CAM (1.3M reserve)

w/ DMic & ALS

Touch Panel

L1

SPI ROM

HDMI IN conn.

2 2

D-sub IN conn.

HDMI OUT conn.

LAN

RJ45

RTL8111E 10/100/1G

PCIe Mini Card

WLAN

Card reader IC

conn.

3 3

(SD/MMC/SDHC)

CIR

SPI

HDMI

RGB

EC

ENE KB930

DDPD

Intel PCH

Cougar Point

H61

SATA port 0

SATA port 1

USB 2.0

PCI-E

PCIe 1x

3.5" SATA HDD Conn.

SATA ODD Conn.

TV Tuner Card

USB3.0 Controller

USB 3.0

USB-Port 3

ASM1042

PCIe 1x

PCIe 1x

FCBGA-942

JMB3853 in 1 CardReader

PCIe 1x

LPC BUS

USB 2.0 X2 (reserve)

USB 2.0

SATA port 4

HD Audio

5.1ch HDA Audio Codec

ALC663

USB-Port 4

USB-Port 5

& eSATA

D-Mic.

MIC Jack

H1L1

SPI ROM

SPI

LFEOUT

FRONT

HPOUT

SPDIFOUT

C C

SPK AMP

EUA2113

4 4

2.5mm jack

for 10W woofer

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/10/1 2011/11/01

C

Compal Secret Data

Deciphered Date

C C

EUA2113

6W SPK *2

Conn

D

Date: Sheet

C C

HP/SPDIF JackSPK AMP

Title

Size Document Number Rev

Compal Electronics, Inc.

Block Diagram

PCA70 LA-7521P M/B

264Tuesday, April 12, 2011

E

of

0.1

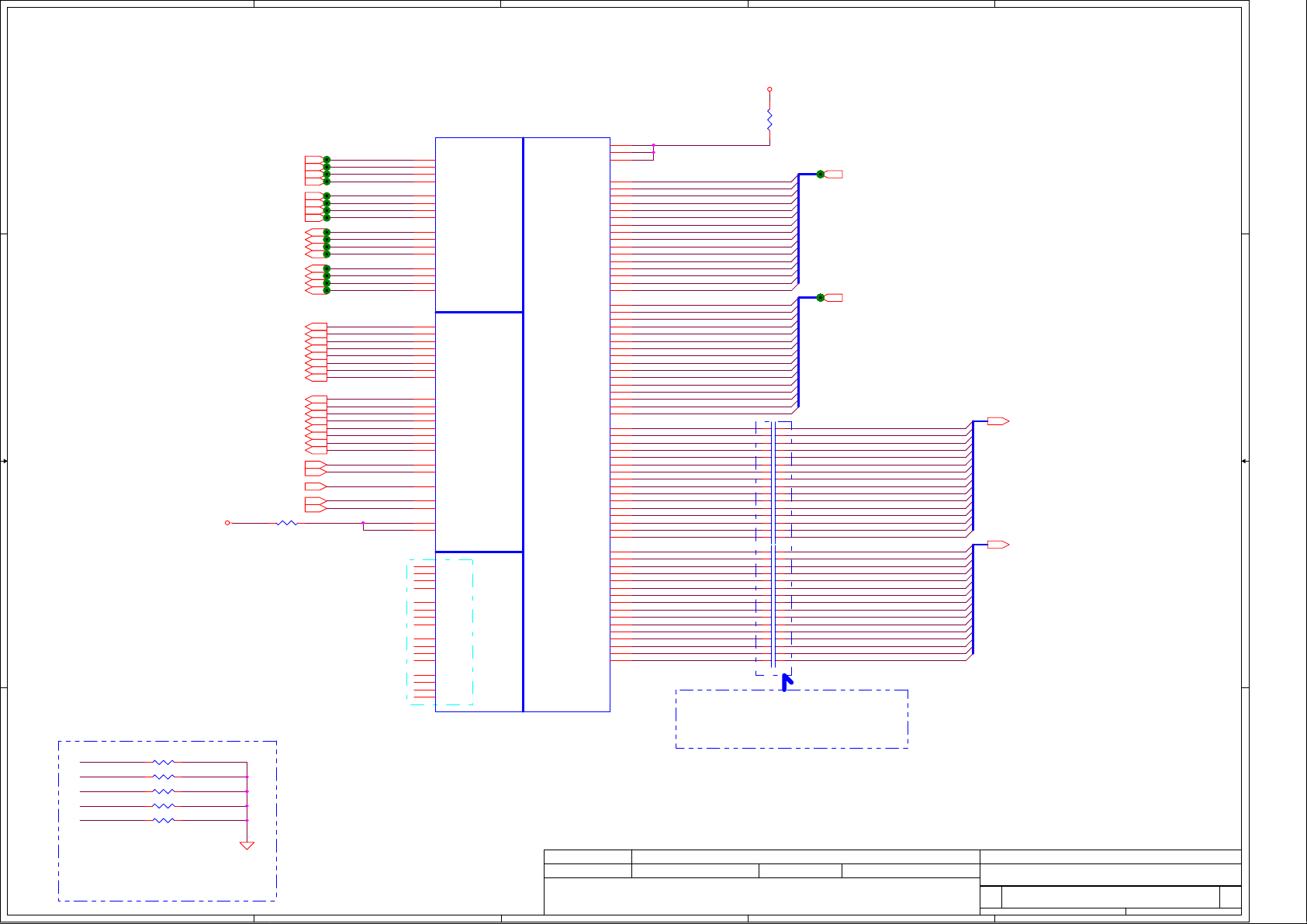

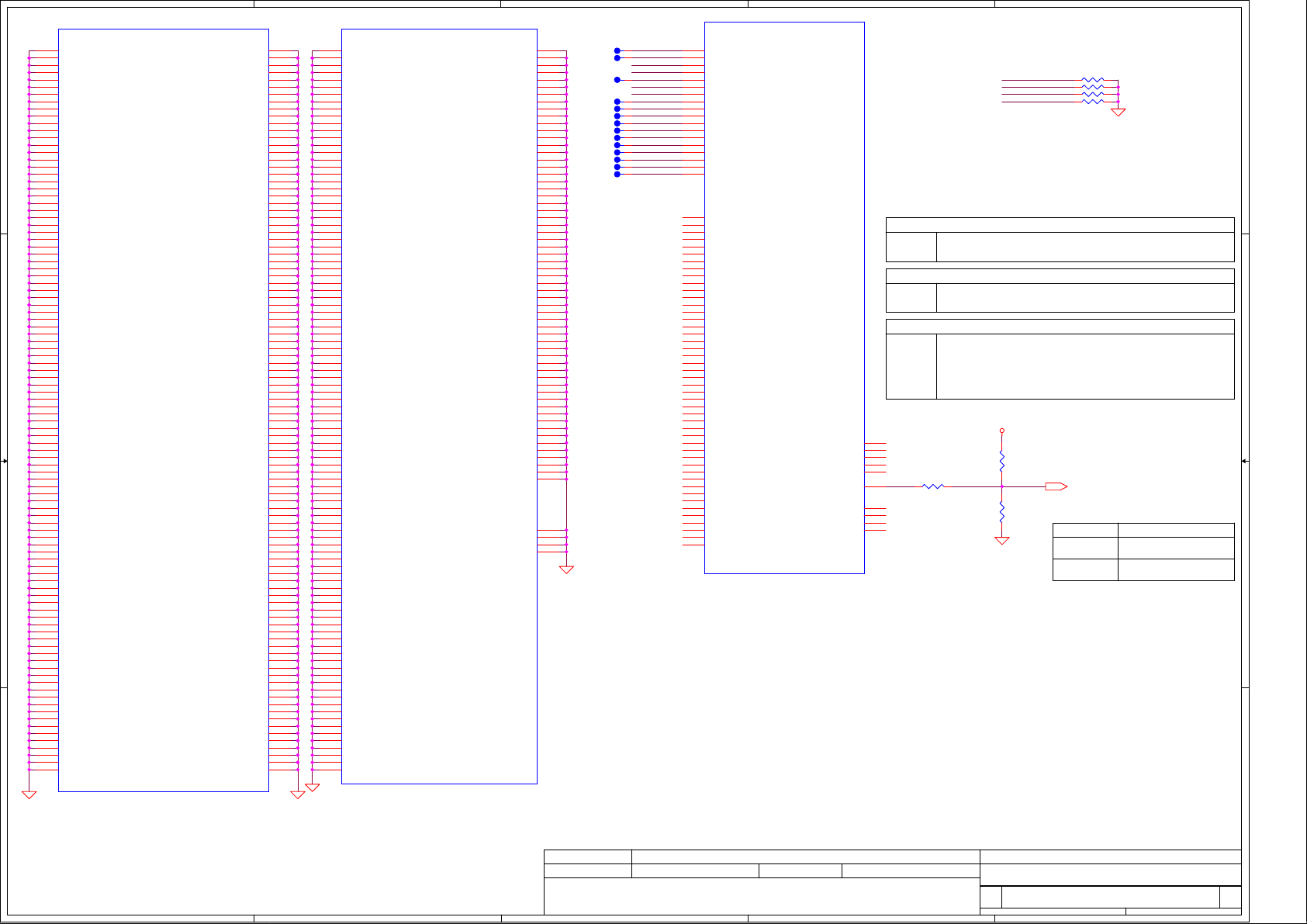

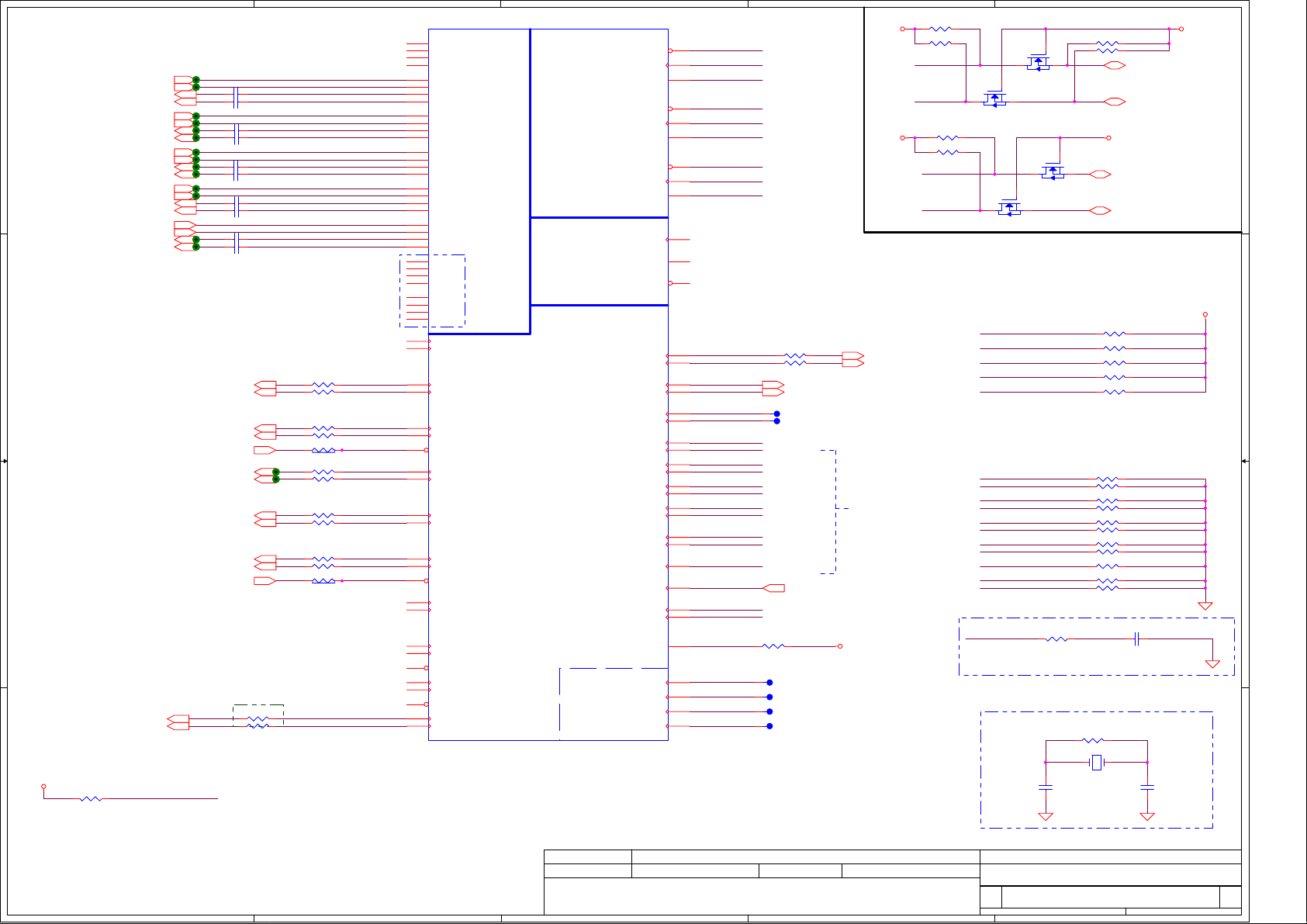

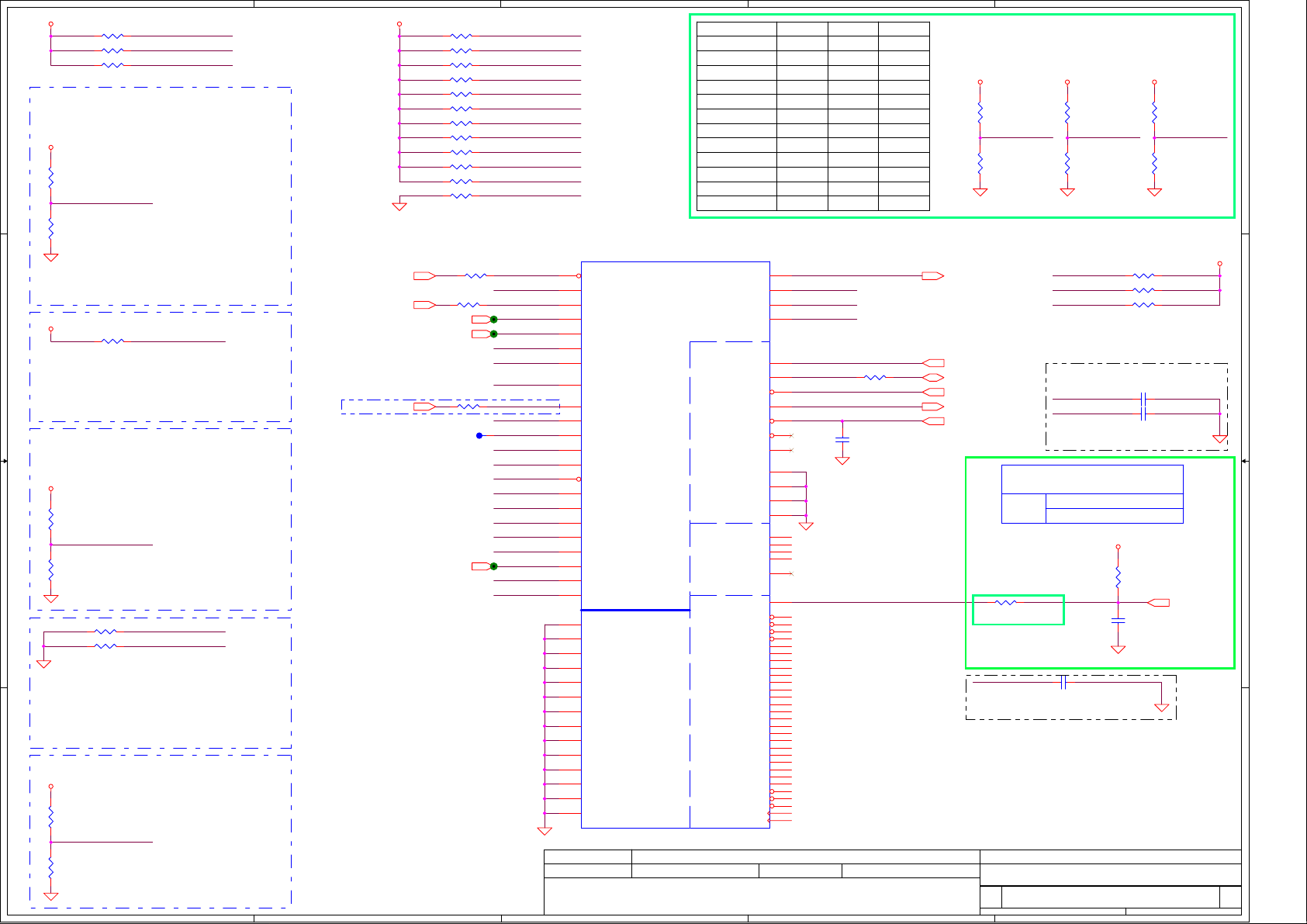

Page 3

5

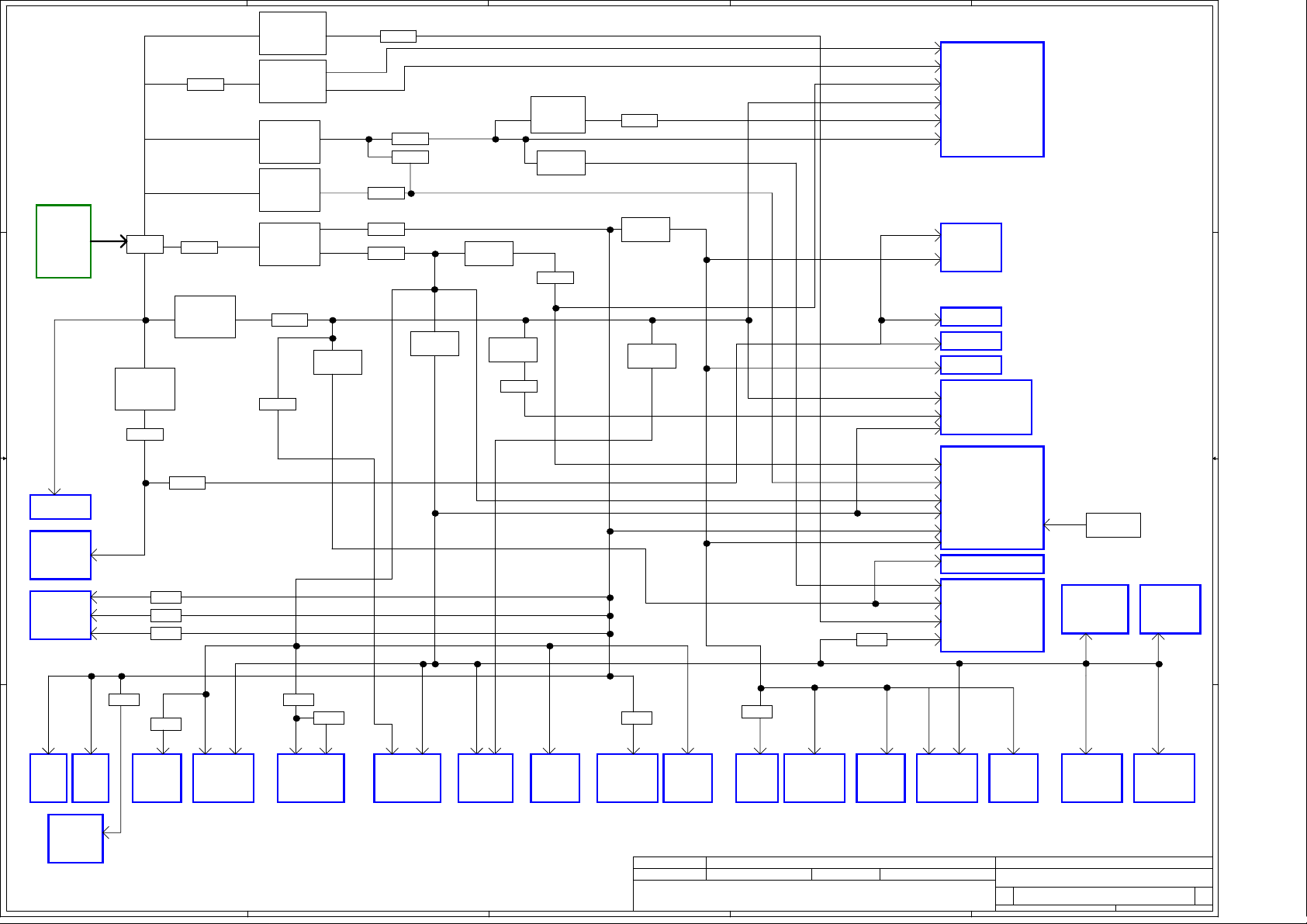

PU16

TPS51212DSCR

Bead

D D

NCP5911MNTBG

PU6

+1.05VS_VCCIOP

PU11~PU15

VIN

TPS51212DSCR

PU9

TPS51212DSCR

+5VALWP

JDCIN1

B+

JUMP

8205_B+ PU2

RT8205EGQW

+3VALWP

+VGA_COREP

+CPU_CORE

+GFX_CORE

+1.05VSP

4

JUMP

JUMP

JUMP

JUMP

JUMP

JUMP

+VGA_CORE

+1.05VS_VCCIO

+1.05VS_VPCH

+5VALW

+3VALW

PU6

APL5930KAI

APL5610CI

AP4800BGM

+1.8VSP

PU5

+VCCSAP +VCCSA

+1.05VGS

U63

3

JUMP

AP4800BGM

Q61

+5VS

2

+CPU_CORE

+GFX_CORE

+1.8VS

+1.05VS_VCCIO

1.5V

+VCCSA

+12VS

+5VS

1

Intel Sandy Bridge

CPU

SATA HDD

JUMP

+1.8VS

+0.75VS

+1.8VS

+1.05VS_VPCH

+3VALW

+3VS

+5VALW

+5VS

+1.5VGS

+1.05VGS

+1.5VGS

+VGA_CORE

+3VGS

MOS

+5VS

SATA ODD

+12VS

+12VS

+5VS

+1.5V

+3VS

Audio codec

ALC663

FAN1

FAN2

FAN3

DDR3 SODIMM X 4

Intel Gougar Point

PCH

VRAM X 8

N12P-GT-A1

VGA

+3VS+5VS

+5VS

HDMI-OUT

Title

Size Docum e nt N u m be r Re v

Date: Sheet

+RTCVCC

Battery

Media card

controller

RTC

JMB385

+3VS

+3VS

Bluetooth

Compal Electronics, Inc.

Power Tree

PCA70 LA-7521P M/B

1

LVDS

ASM1442

+3VS

CAM

364Tuesday, April 12, 2011

+3VS

of

0.1

PU7

TPS51212DSCR

C C

PU3

TPS54331DR

+12VALWP

JUMP

+1.5VP

MOS

JUMP

+1.5VS

+1.5V

U65

AP4800BGM

+1.5VGS

Q60

AP4800BGM

+3VS

PU6

APL5930KAI

+0.75VP

JUMP

+0.75VS

+1.5V

PU19

APL5930KAI

+1.2VUSB

+12VALW

+12VS

B+

LCD

Converter

MOS

+3VS

AMP X 2

EUA2113

B B

+USB_VCCB

USB2.0 X 3

USB3.0 X 2

+USB_VCCA

+USB30_VCCA

+5VALW

HDMI-IN Mini Card x2

CRT-IN

A A

eSATA/USB

Conn.

+5VALW

U83

+3V_LAN

+USB_VCCC

5

U34

U33

U46

MOS

LAN

RTL8111E

+3VALW

SW&Power/B

Conn

+3VS

+3VALW

MOS

Scaler

U23

+1.2V_SCA

+3VS

+3VS1.5VS

+1.2VUSB+3V_SCA

USB3.0

ASM1042

4

EC

KB930

+3VALW

+5VALW

+3VS

+5VALW

+5VS

MOS

+LCDVDD

LVDS CONNRTD2482D

+3VALW

Scaler

3

CIR

Security Cl assification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INF ORMATION IT CONTAI NS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WR ITT EN CO NSE NT OF COMPAL ELECTRONICS, INC.

MOS

B-CAS

+5VS

Touchscreen

Compal Secret Data

Deciphered Date

2

+5VS_L_BCAS

2010/10/1 2011/11/01

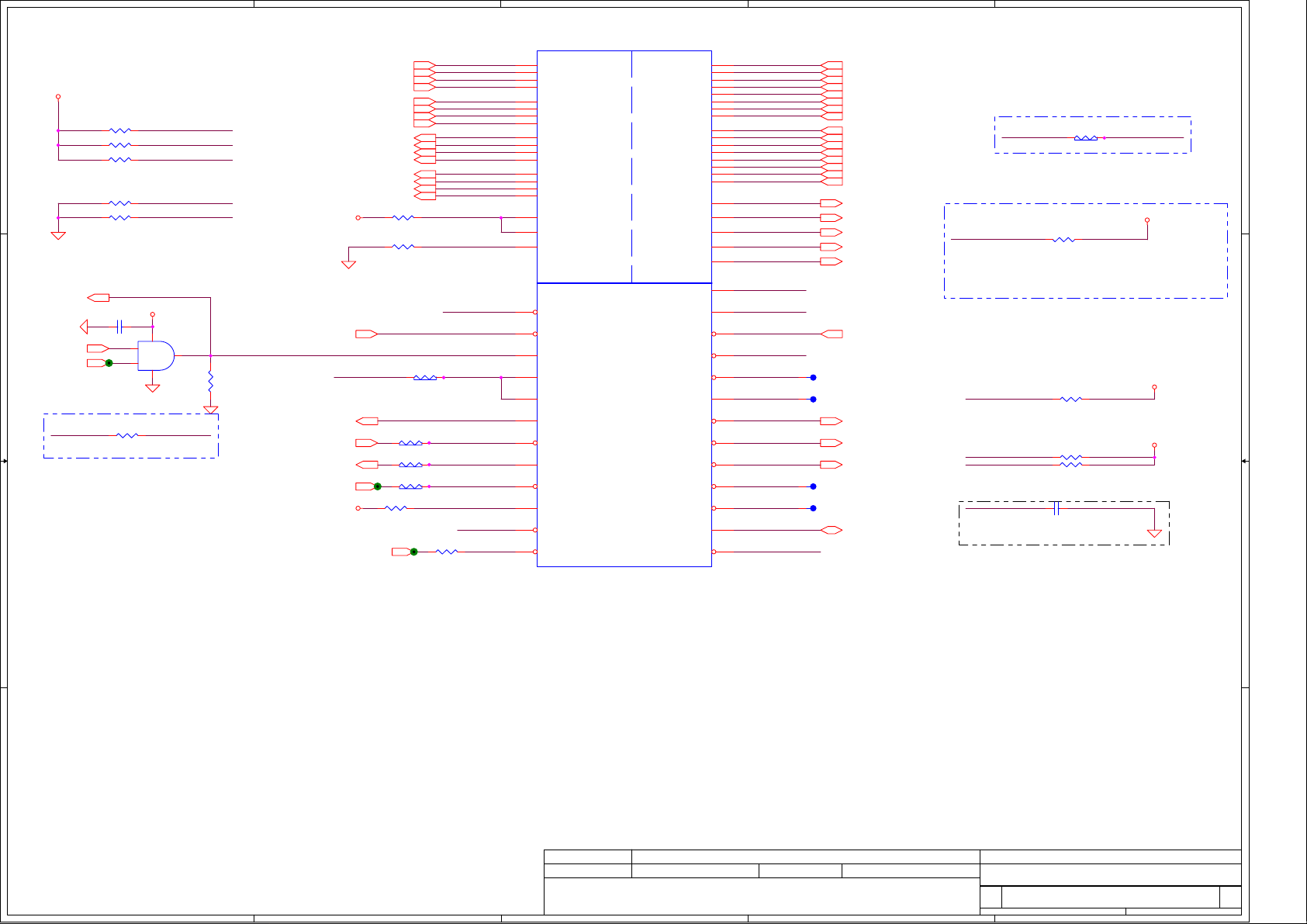

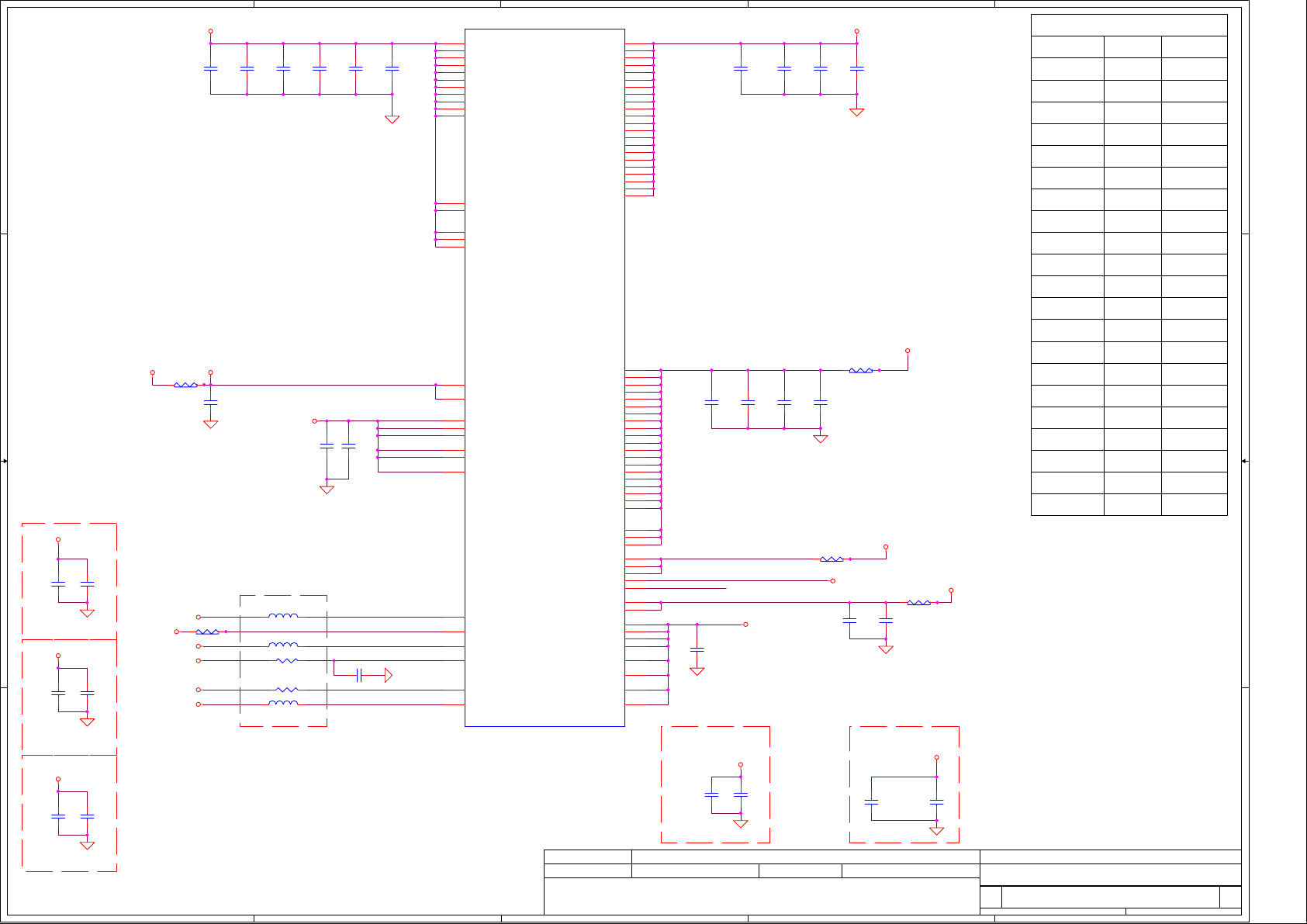

Page 4

A

B

C

D

E

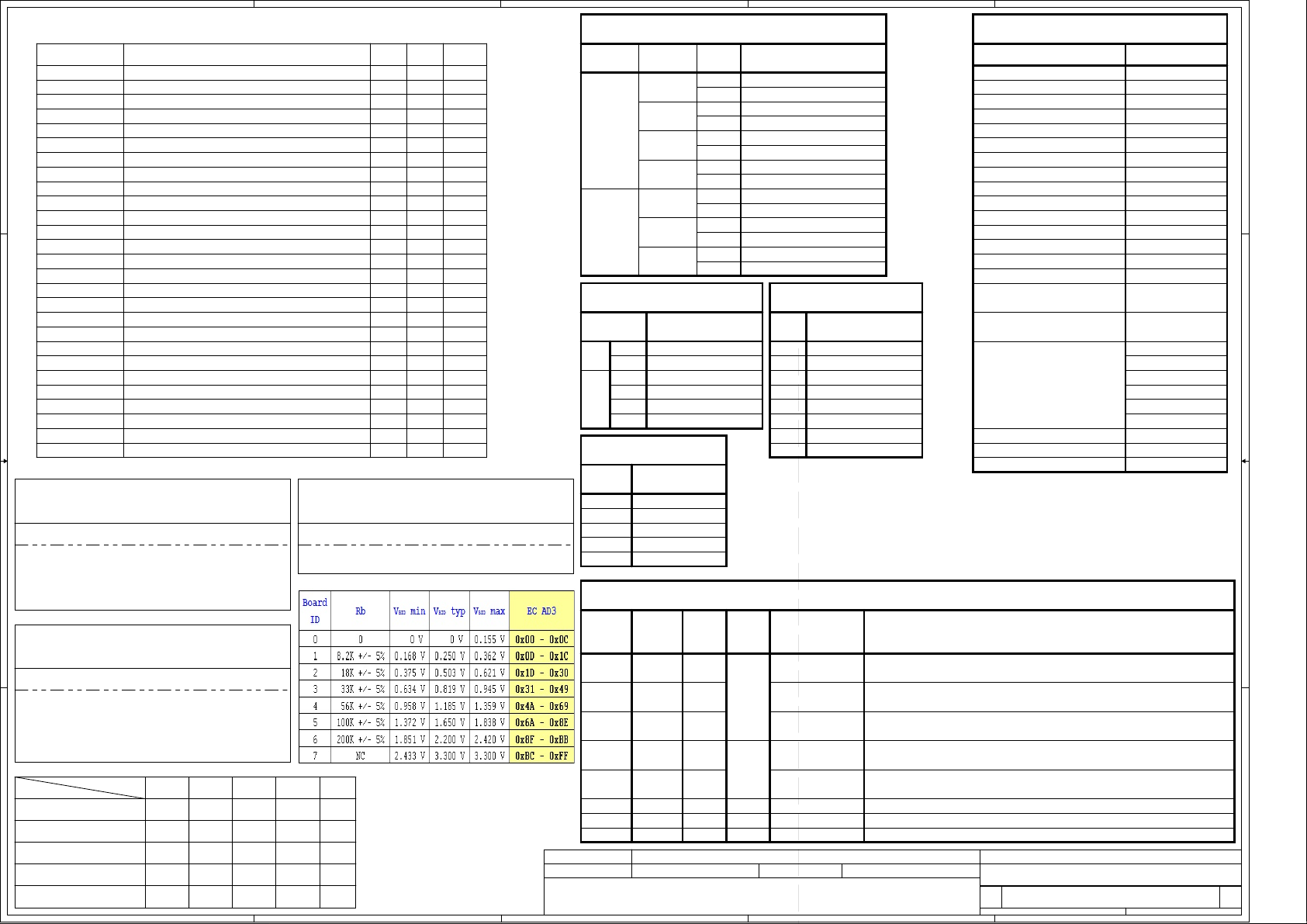

Voltage Rails

Power Plane Description

VIN

B+

+CPU_CORE

1 1

+VCCSA ON OFF OFFSystem Agent core voltage for CPU

+1.05VS_VCCIO 1.05V power rail for CPU

+1.05VS_VPCH 1.05V power rail for PCH

+0.75VS 0.75V power rail for DDR terminator

+1.5V

+1.5VS

+1.8VS 1.8V switched power rail

+3VALW 3.3V alwa y s on powe r ra il once AC plug in

+3V_LAN 3.3V power rail for LAN ON

+3VS

+3V_SCA 3.3V switched pow er rail for scaler O N

+1.2V_SCA N/AN/A

+1.2V_USB 1.2V power rail for USB3.0 O FFON OFF

+5VS 5V switched power rail OFF OFF

2 2

+RTCVCC RTC power

+3VGS ON OFF OFF

+1.05VGS

+1.5VGS

+12VALW 12V always on power rail once AC plug in

+12VS 5V switched power rail O FF O FF

Note : ON * m e a n s t h a t t hi s p ow e r pl a ne is ON only with AC power available, otherwise it is OFF.

Adapter power supply (19V)

AC power rail for power circuit.

Core voltage for CPU

1.5V power rail for DDRIII

1.5V switched power rail

3.3V switched power rail

1.2V switched power rail for scaler ON

5V always on power rail once AC plug in+5VALW

5V switched power rail for panel+LCDVDD ON N/A N/A

3.3V power rail for GPU

Graphics power rail for GPU

1.05VS switched power rail for GPU

1.5VS power rail for GPU and VRAM

PCH SM Bus Address

HEX

Device

+3VS

+3VS

3 3

DDR(JDDRL2)

DDR(JDDRH1)

Address

1010 000X b

1010 010X b

S0 S3 S5

N/A

N/A

N/A

OFF

OFF

OFF

ON

OFF

OFF

ON

ON

OFF

N/A N/A

ONON

N/A

N/A

OFF

OFF

OFF

OFF

ON

OFF

N/A

ON

ON OFF+GFX _COR E Graphics voltage for CPU

ONONOFF

ON OFF OFF

ON OFF

ON OFF

ON

ON

ON

ON OFF

ON

ON ON ON

ON OFF OFF+VGA_CORE

ON OFF OFF

ON OFF OFF

ONONN/A N/A

EC SM Bus2 Address

DevicePower Power

Scaler

HEX Address

0000_0101b

USB Port Table

USB 2.0 USB 1.1 Port

UHCI0

UHCI1

EHCI1

UHCI2

UHCI3

UHCI4

EHCI2

UHCI5

UHCI6

SATA Port Table

Port Device

0

6G

3G

HDD

1

ODD

2

Disabled on H61

3

Disabled on H61

4

eSATA+USB Conn

5

NC

BOARD ID Table

Board

ID

0

*

1

2

3

4

PCB

Revision

0.1

0.2

Device

0

Co-lay w/USB30 PORT0

1

Co-lay w/USB30 PORT1

2

Touch Screen

3

Web Camera

4

eSATA+USB Conn

5

USB Conn 6

6

Disabled on H61

7

Disabled on H61

8

USB Conn 4

9

USB Conn 3

10

Mini Card(TV Tuner)

11

Blue Tooth

12

Disabled on H61

13

Disabled on H61

PCIE Port Table

1

2

3

4

5

6

7

8

DevicePort

NC

USB30

WLAN

TV

Card reader

LAN

Disabled on H61

Disabled on H61

BOM Structure Table

BTO Item BOM Structure

ME components CONN@

UMA Only UMA@

USB30 USB30@

D-sub IN VGAIN@

HDMI IN HDMIIN@

HDMI OUT HDMIO@

HDMI OUT from DIS HDMIOD@

HDMI OUT from UMA HDMIOU@

VGA w/o Senergy DISO@

BCAS TV@

VRAM select X76@

VRAM 1G Hynix

X7630488L01

VRAM 1G Samsung

X7630488L02

SKU IO Select

Unpop @

LA-7522P 8 Layer PCB 8LPCB@

GS@VGA-N12P-GS

GV@VGA-N12P-GV

DIS@DISCRETE ONLY

USB20@No USB30 SKU

X76_HY1G@

X76_SAM1G@

GPIO69_H@

GPIO69_L@

GPIO70_H@

GPIO70_L@

GPIO71_H@

GPIO71_L@

6LOCB@LA-7521P 6 Layer PCB

SKU ID(Project) Table

Project

_ID2

PCH SML1 Bus Address

HEX

AddressDevicePower

VGA Ext. thermal sensor

(defaulta)

SIGNAL

STATE

4 4

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SLP_S3#

HIGH HIGH HIGH

LOW

LOW LOW

A

SLP_S4#

HIGH

1001_1010b

1001_1110bVGA Int. thermal sensor

SLP_S5# +VALW

HIGHHIGHHIGH

HIGH

HIGH

LOWLOWLOW OFF

ON

ON

ON

ON

OFF

+VS

ON

ON

OFF

OFF

B

(GPIO69)

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CON SENT O F COMPAL ELECTRONICS, INC.

Project

_ID1

(GPIO70)

00 0

0

0

01 1

10 0

Project

Project

_ID0

(GPIO71)

0

1

PCA70

1

0

PCA61

SKU

UMA

USB30 w/o HDMI

4319D588L03

DIS-Hynix

USB30 w/ HDMI

4319D588L04

UMA

USB30 w/ HDMI

4319D588L05

DIS-Hynix

USB30 w/ HDMI

4319D588L11

UMA

USB20 w/ HDMI

4319D588L12

10 1 X

11 0 X

2010/10/1 2011/11/01

C

Compal Secret Data

Deciphered Date

UMA@ USB30@ GPIO69_L@ GPIO70_L@ GPIO71_L@

GS@ DIS@ USB30@ VGAIN@ HDMIO@ HDMIOD@ DISO@

8LPCB@

8LPCB@

X76_HY1G@

GPIO69_L@ GPIO70_L@ GPIO71_H@

HDMIIN@

HDMIIN@UMA@ USB30@ VGAIN@ HDMIO@ HDMIOU@ DEBUG@

8LPCB@

GPIO69_L@ GPIO71_L@

GPIO70_H@

HDMIIN@GV@ DIS@ USB30@ VGAIN@ HDMIO@ HDMIOD@ DISO@

6LOCB@

GPIO69_L@ GPIO71_H@

GPIO70_H@

HDMIIN@UMA@ USB20@ VGAIN@ HDMIO@ HDMIOU@ DEBUG@

GPIO69_H@ GPIO70_L@

GPIO71_L@6LOCB@

X11 1

Title

Size Document Number Rev

Custom

D

Date: Sheet

Compal Electronics, Inc.

Notes List

PCA70 LA-7521P M/B

464Tuesday, April 12, 2011

E

0.1

of

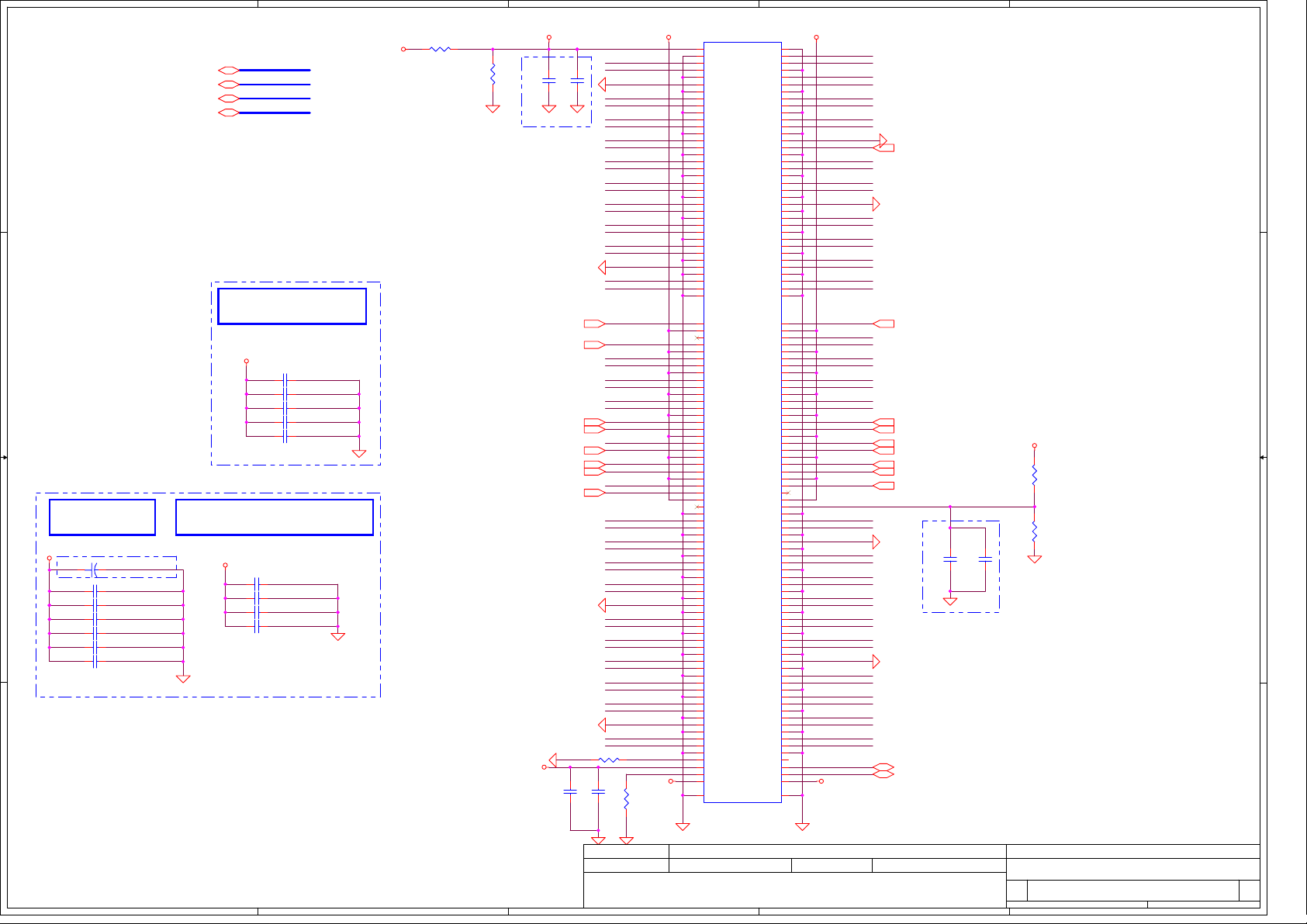

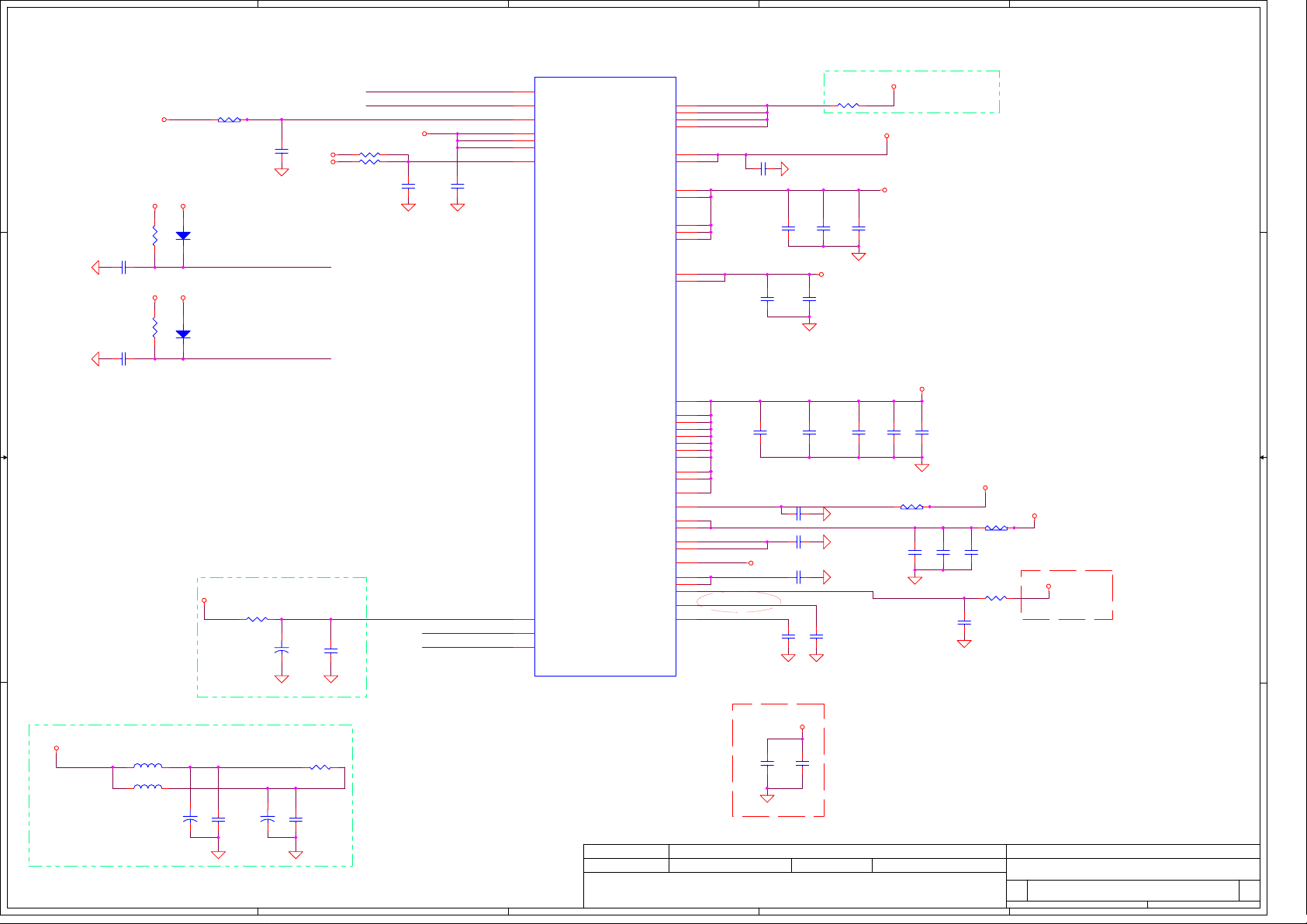

Page 5

5

D D

PECI 10mil spacing and

Max Length < 15"

R12 follow CDB R42PR add

0ohm serial resistor

R14 follow CDB R34PR add

0ohm serial resistor

12

R1310K_0402_5%

C20.1U_0402_16V4Z

H_PECI

H_SNB_IVB#

H_PROCHOT#_R

H_PM_SYNC

H_PWRGOOD

+1.5V

1 2

C1591 0.1U_0402_16V4Z

1 2

C1592 0.1U_0402_16V4Z

1 2

C1593 0.1U_0402_16V4Z

1 2

ESD request Close to CPU as possible

C C

Place C2 close to CPU J40 as

close as possible.

C1594 0.1U_0402_16V4Z

1 2

+1.05VS_VCCIO

H_PROCHOT#[49]

R8 51_0402_5%

+1.05VS_VCCIO

12

H_THERMTRIP#[18]

4

H_SNB_IVB#[18]

H_PM_SYNC[15]

H_PWRGOOD[18]

T1PAD

R1070

@

1K_0402_5%

12

H_PECI[18,49]

R12 0_0402_5%@

12

1 2

R14 0_0402_5%

PM_DRAM_PWRGD_R

H_SNB_IVB#

TP_SKTOCC#

H_CATERR#

H_PECI

H_PROCHOT#_R

H_THERMTRIP#_R

H_PM_SYNC

H_PWRGOOD

BUF_CPU_RST#

JCPU1B

PROC_SELECT#

K32

PROC_SEL

AJ33

SKTOCC#

E37

CATERR#

J35

PECI

H34

PROCHOT#

G35

THERMTRIP#

E38

PM_SYNC

J40

UNCOREPWRGOOD

AJ19

SM_DRAMPWROK

F36

RESET#

Sandy Bridge_rPGA_Rev1p0

3

MISCTHERMALPWR MANAGEMENT

BCLK[0]

BCLK#[0]

BCLK_ITP

BCLK_ITP#

CLOCKS

SM_DRAMRST#

DDR3

MISC

PRDY#

PREQ#

TCK

TMS

TRST#

TDO

DBR#

BPM#[0]

BPM#[1]

JTAG & BPM

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

TDI

W2

W1

C40

D40

AW18

K38

K40

M40

L38

J39

L40

L39

E39

H40

H38

G38

G40

G39

F38

E40

F40

100 MHz

CLK_CPU_DMI

CLK_CPU_DMI#

120 MHz

CLK_BCLK_ITP

CLK_BCLK_ITP#

XDP_TCK_R

XDP_TMS_R

XDP_TRST#_R

XDP_TDI_R

XDP_TDO_R

XDP_DBRESET#_R

2

CLK_CPU_DMI [14]

CLK_CPU_DMI# [14]

CLK_BCLK_ITP [14]

CLK_BCLK_ITP# [14]

1

@

0.1U_0402_16V4Z

2

R23 0_0402_5%@

1 2

Close to CPU side

C3

SM_DRAMRST# [11,12]

XDP_DBRESET#

1

PU/PD for JTAG signals

XDP_TMS_R

XDP_TDI_R

XDP_TDO_R

XDP_TCK_R

XDP_TRST#_R

R1 51_0402_5%

R2 51_0402_5%

R3 51_0402_5%

R4 51_0402_5%

R6 51_0402_5%

R22 10K_0402_5%

12

+3VS

XDP_DBRESET# [15]

+1.05VS_VCCIO

12

12

12

12

12

12

R33

200_0402_5%

PM_DRAM_PWRGD_R

DRAMPWROK[15]

B B

SUSP[51,57]

2

G

1 2

R24

12

130_0402_5%

R35

@

39_0402_5%

13

D

Q1

SSM3K7002BF 1N SC59-3

@

S

1

C1

1000P_0402_50V7K

2

@

Change Buffered Reset to 1G07(Buffer with open-drain output) 10/7

+3VS

C6

0.1U_0402_16V4Z

A A

PLT_RST#[17,22,45,49]

PLT_RST#

C1612

0.1U_0402_16V4Z

5

1

2

5

1

NC

2

A

2

3

1

U2

P

4

Y

G

SN74LVC1G07DCKR_SC70-5

+1.05VS_VCCIO

12

R42

75_0402_5%

R43

BUFO_CPU_RST# BUF_CPU_RST#

43_0402_1%

1 2

4

12

R44

0_0402_5%

@

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CON SENT O F COMPAL ELECTRONICS, INC.

2010/10/1 2011/11/01

3

Compal Secret Data

Deciphered Date

2

Title

Size Document Number Rev

Custom

Date: Sheet

Compal Electronics, Inc.

Sandy Bridge_JTAG/XDP/FAN

PCA70 LA-7521P M/B

1

of

564Tuesday, April 12, 2011

0.1

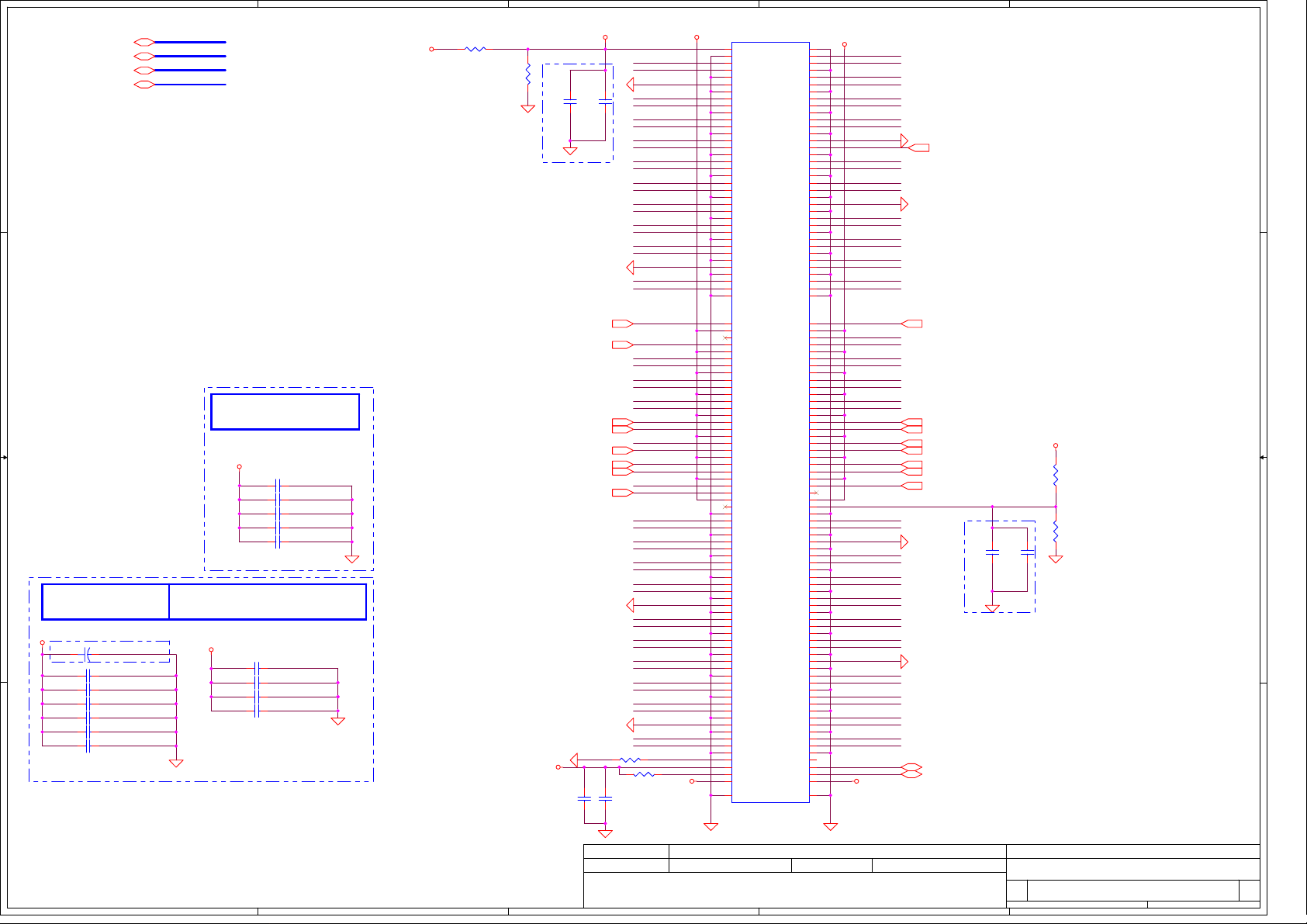

Page 6

5

D D

DMI_PTX_CRX_N0[15]

DMI_PTX_CRX_N1[15]

DMI_PTX_CRX_N2[15]

DMI_PTX_CRX_N3[15]

DMI_PTX_CRX_P0[15]

DMI_PTX_CRX_P1[15]

DMI_PTX_CRX_P2[15]

DMI_PTX_CRX_P3[15]

DMI_CTX_PRX_N0[15]

DMI_CTX_PRX_N1[15]

DMI_CTX_PRX_N2[15]

DMI_CTX_PRX_N3[15]

DMI_CTX_PRX_P0[15]

DMI_CTX_PRX_P1[15]

DMI_CTX_PRX_P2[15]

DMI_CTX_PRX_P3[15]

FDI_CTX_PRX_N0[15]

FDI_CTX_PRX_N1[15]

FDI_CTX_PRX_N2[15]

C C

+1.05VS_VCCIO

FDI_COMP signals should be shorted

near balls and routed with width

B B

10mils, length<250mils.

FDI_CTX_PRX_N3[15]

FDI_CTX_PRX_N4[15]

FDI_CTX_PRX_N5[15]

FDI_CTX_PRX_N6[15]

FDI_CTX_PRX_N7[15]

FDI_CTX_PRX_P0[15]

FDI_CTX_PRX_P1[15]

FDI_CTX_PRX_P2[15]

FDI_CTX_PRX_P3[15]

FDI_CTX_PRX_P4[15]

FDI_CTX_PRX_P5[15]

FDI_CTX_PRX_P6[15]

FDI_CTX_PRX_P7[15]

FDI_FSYNC0[15]

FDI_FSYNC1[15]

FDI_INT[15]

FDI_LSYNC0[15]

FDI_LSYNC1[15]

R46 24.9_0402_1%

1 2

7/20 PE_RX[0~3]/PE_RX#[0~3]

PE_TX[0~3] /PE_T X#[0~3] o nly

use on Server/Workstation.

Close to CPU

FDI_INT

FDI_FSYNC0

FDI_FSYNC1

A A

FDI_LSYNC0

FDI_LSYNC1

@

1 2

R47 1K_0402_5%

@

1 2

R48 1K_0402_5%

@

1 2

R49 1K_0402_5%

@

1 2

R50 1K_0402_5%

@

1 2

R51 1K_0402_5%

4

DMI_PTX_CRX_N0

DMI_PTX_CRX_N1

DMI_PTX_CRX_N2

DMI_PTX_CRX_N3

DMI_PTX_CRX_P0

DMI_PTX_CRX_P1

DMI_PTX_CRX_P2

DMI_PTX_CRX_P3

DMI_CTX_PRX_N0

DMI_CTX_PRX_N1

DMI_CTX_PRX_N2

DMI_CTX_PRX_N3

DMI_CTX_PRX_P0

DMI_CTX_PRX_P1

DMI_CTX_PRX_P2

DMI_CTX_PRX_P3

FDI_CTX_PRX_N0

FDI_CTX_PRX_N1

FDI_CTX_PRX_N2

FDI_CTX_PRX_N3

FDI_CTX_PRX_N4

FDI_CTX_PRX_N5

FDI_CTX_PRX_N6

FDI_CTX_PRX_N7

FDI_CTX_PRX_P0

FDI_CTX_PRX_P1

FDI_CTX_PRX_P2

FDI_CTX_PRX_P3

FDI_CTX_PRX_P4

FDI_CTX_PRX_P5

FDI_CTX_PRX_P6

FDI_CTX_PRX_P7

FDI_FSYNC0

FDI_FSYNC1

FDI_INT

FDI_LSYNC0

FDI_LSYNC1

FDI_COMP

JCPU1A

W4

DMI_RX#[0]

V4

DMI_RX#[1]

Y4

DMI_RX#[2]

AA5

DMI_RX#[3]

W5

DMI_RX[0]

V3

DMI_RX[1]

Y3

DMI_RX[2]

AA4

DMI_RX[3]

V6

DMI_TX#[0]

W8

DMI_TX#[1]

Y7

DMI_TX#[2]

AA8

DMI_TX#[3]

V7

DMI_TX[0]

W7

DMI_TX[1]

Y6

DMI_TX[2]

AA7

DMI_TX[3]

AC7

FDI_TX#[0]

AC3

FDI_TX#[1]

AD1

FDI_TX#[2]

AD3

FDI_TX#[3]

AD6

FDI_TX#[4]

AE8

FDI_TX#[5]

AF2

FDI_TX#[6]

AG1

FDI_TX#[7]

AC8

FDI_TX[0]

AC2

FDI_TX[1]

AD2

FDI_TX[2]

AD4

FDI_TX[3]

AD7

FDI_TX[4]

AE7

FDI_TX[5]

AF3

FDI_TX[6]

AG2

FDI_TX[7]

AC5

FDI_FSYNC[0]

AE5

FDI_FSYNC[1]

AG3

FDI_INT

AC4

FDI_LSYNC[0]

AE4

FDI_LSYNC[1]

AE2

FDI_COMPIO

AE1

FDI_ICOMPO

P3

PE_RX[0]

R2

PE_RX[1]

T4

PE_RX[2]

U2

PE_RX[3]

P4

PE_RX#[0]

R1

PE_RX#[1]

T3

PE_RX#[2]

U1

PE_RX#[3]

P8

PE_TX[0]

T7

PE_TX[1]

R6

PE_TX[2]

U5

PE_TX[3]

P7

PE_TX#[0]

T8

PE_TX#[1]

R5

PE_TX#[2]

U6

PE_TX#[3]

Sandy Bridge_rPGA_Rev1p0

PEG_COMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PCI EXPRESS* - GRAPHICS

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

DMI

Intel(R) FDI

PCI-EXPRESS

3

B4

B5

C4

PCIE_GTX_C_CRX_N15

B12

PCIE_GTX_C_CRX_N14

D11

PCIE_GTX_C_CRX_N13

C9

PCIE_GTX_C_CRX_N12

E9

PCIE_GTX_C_CRX_N11

B7

PCIE_GTX_C_CRX_N10

C5

PCIE_GTX_C_CRX_N9

A6

PCIE_GTX_C_CRX_N8

E1

PCIE_GTX_C_CRX_N7

F3

PCIE_GTX_C_CRX_N6

G1

PCIE_GTX_C_CRX_N5

H4

PCIE_GTX_C_CRX_N4

J2

PCIE_GTX_C_CRX_N3

K4

PCIE_GTX_C_CRX_N2

L2

PCIE_GTX_C_CRX_N1

M4

PCIE_GTX_C_CRX_N0

N2

PCIE_GTX_C_CRX_P15

B11

PCIE_GTX_C_CRX_P14

D12

PCIE_GTX_C_CRX_P13

C10

PCIE_GTX_C_CRX_P12

E10

PCIE_GTX_C_CRX_P11

B8

PCIE_GTX_C_CRX_P10

C6

PCIE_GTX_C_CRX_P9

A5

PCIE_GTX_C_CRX_P8

E2

PCIE_GTX_C_CRX_P7

F4

PCIE_GTX_C_CRX_P6

G2

PCIE_GTX_C_CRX_P5

H3

PCIE_GTX_C_CRX_P4

J1

PCIE_GTX_C_CRX_P3

K3

PCIE_GTX_C_CRX_P2

L1

PCIE_GTX_C_CRX_P1

M3

PCIE_GTX_C_CRX_P0

N1

PCIE_CTX_GRX_N15

C14

PCIE_CTX_GRX_N14

E13

PCIE_CTX_GRX_N13

G13

PCIE_CTX_GRX_N12

F11

PCIE_CTX_GRX_N11

J13

PCIE_CTX_GRX_N10

D7

PCIE_CTX_GRX_N9

C3

PCIE_CTX_GRX_N8

E5

PCIE_CTX_GRX_N7

F7

PCIE_CTX_GRX_N6

G9

PCIE_CTX_GRX_N5

G6

PCIE_CTX_GRX_N4

K8

PCIE_CTX_GRX_N3

J6

PCIE_CTX_GRX_N2

M7

PCIE_CTX_GRX_N1

L5

PCIE_CTX_GRX_N0

N6

PCIE_CTX_GRX_P15

C13

PCIE_CTX_GRX_P14

E14

PCIE_CTX_GRX_P13

G14

PCIE_CTX_GRX_P12

F12

PCIE_CTX_GRX_P11

J14

PCIE_CTX_GRX_P10

D8

PCIE_CTX_GRX_P9

D3

PCIE_CTX_GRX_P8

E6

PCIE_CTX_GRX_P7

F8

PCIE_CTX_GRX_P6

G10

PCIE_CTX_GRX_P5

G5

PCIE_CTX_GRX_P4

K7

PCIE_CTX_GRX_P3

J5

PCIE_CTX_GRX_P2

M8

PCIE_CTX_GRX_P1

L6

PCIE_CTX_GRX_P0

N5

PEG_ICOMPI and RCOMPO signals should be shorted and routed with

- max length = 500 mils

- typical imp e d a nce = 43 m ohm (4 mils/15mils)

Intel confirm

pull high is

correct

PEG_COMP

Typ- suggest 220nF. The change in AC capacitor

value from 100nF to 220nF is to enable

compatibility with future platforms having PCIE

Gen3 (8GT/s)

+1.05VS_VCCIO

R45

24.9_0402_1%

C7 0.1U_0402_16V7KDIS@

C8 0.1U_0402_16V7KDIS@

C9 0.1U_0402_16V7KDIS@

C10 0.1U_0402_16V7KDIS@

C11 0.1U_0402_16V7KDIS@

C12 0.1U_0402_16V7KDIS@

C13 0.1U_0402_16V7KDIS@

C14 0.1U_0402_16V7KDIS@

C15 0.1U_0402_16V7KDIS@

C16 0.1U_0402_16V7KDIS@

C17 0.1U_0402_16V7KDIS@

C18 0.1U_0402_16V7KDIS@

C19 0.1U_0402_16V7KDIS@

C20 0.1U_0402_16V7KDIS@

C21 0.1U_0402_16V7KDIS@

C22 0.1U_0402_16V7KDIS@

C23 0.1U_0402_16V7KDIS@

C24 0.1U_0402_16V7KDIS@

C25 0.1U_0402_16V7KDIS@

C26 0.1U_0402_16V7KDIS@

C27 0.1U_0402_16V7KDIS@

C28 0.1U_0402_16V7KDIS@

C29 0.1U_0402_16V7KDIS@

C30 0.1U_0402_16V7KDIS@

C31 0.1U_0402_16V7KDIS@

C32 0.1U_0402_16V7KDIS@

C33 0.1U_0402_16V7KDIS@

C34 0.1U_0402_16V7KDIS@

C35 0.1U_0402_16V7KDIS@

C36 0.1U_0402_16V7KDIS@

C37 0.1U_0402_16V7KDIS@

C38 0.1U_0402_16V7KDIS@

PEG_ICOMPO signals should be routed with

- max length = 500 mils

- typical imp e d ance = 14.5 m ohm (12 mils/15mils)

12

SHORT B4 & C4 TOGETHER, ROUTE AS A SINGLETRACE TO R?

ROUTE B5 TO R? AS A SEPERATE TRACE

PCIE_GTX_C_CRX_N[0..15] [22]

PCIE_GTX_C_CRX_P[0..15] [22]

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

2

PCIE_CTX_C_GRX_N15

PCIE_CTX_C_GRX_N14

PCIE_CTX_C_GRX_N13

PCIE_CTX_C_GRX_N12

PCIE_CTX_C_GRX_N11

PCIE_CTX_C_GRX_N10

PCIE_CTX_C_GRX_N9

PCIE_CTX_C_GRX_N8

PCIE_CTX_C_GRX_N7

PCIE_CTX_C_GRX_N6

PCIE_CTX_C_GRX_N5

PCIE_CTX_C_GRX_N4

PCIE_CTX_C_GRX_N3

PCIE_CTX_C_GRX_N2

PCIE_CTX_C_GRX_N1

PCIE_CTX_C_GRX_N0

PCIE_CTX_C_GRX_P15

PCIE_CTX_C_GRX_P14

PCIE_CTX_C_GRX_P13

PCIE_CTX_C_GRX_P12

PCIE_CTX_C_GRX_P11

PCIE_CTX_C_GRX_P10

PCIE_CTX_C_GRX_P9

PCIE_CTX_C_GRX_P8

PCIE_CTX_C_GRX_P7

PCIE_CTX_C_GRX_P6

PCIE_CTX_C_GRX_P5

PCIE_CTX_C_GRX_P4

PCIE_CTX_C_GRX_P3

PCIE_CTX_C_GRX_P2

PCIE_CTX_C_GRX_P1

PCIE_CTX_C_GRX_P0

1

PCIE_CTX_C_GRX_N[0..15] [22]

PCIE_CTX_C_GRX_P[0..15] [22]

Leverage LA-6831 and

LA6951(B520) used 1000P

connect to GND to

substitute for 1K ohm PD

resistor.

5

4

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CON SENT O F COMPAL ELECTRONICS, INC.

2010/10/1 2011/11/01

3

Compal Secret Data

Deciphered Date

2

Title

Size Document Number Rev

Custom

Date: Sheet

Compal Electronics, Inc.

Sandy Bridge_ DMI/PEG/FDI

PCA70 LA-7521P M/B

664Tuesday, April 12, 2011

1

of

0.1

Page 7

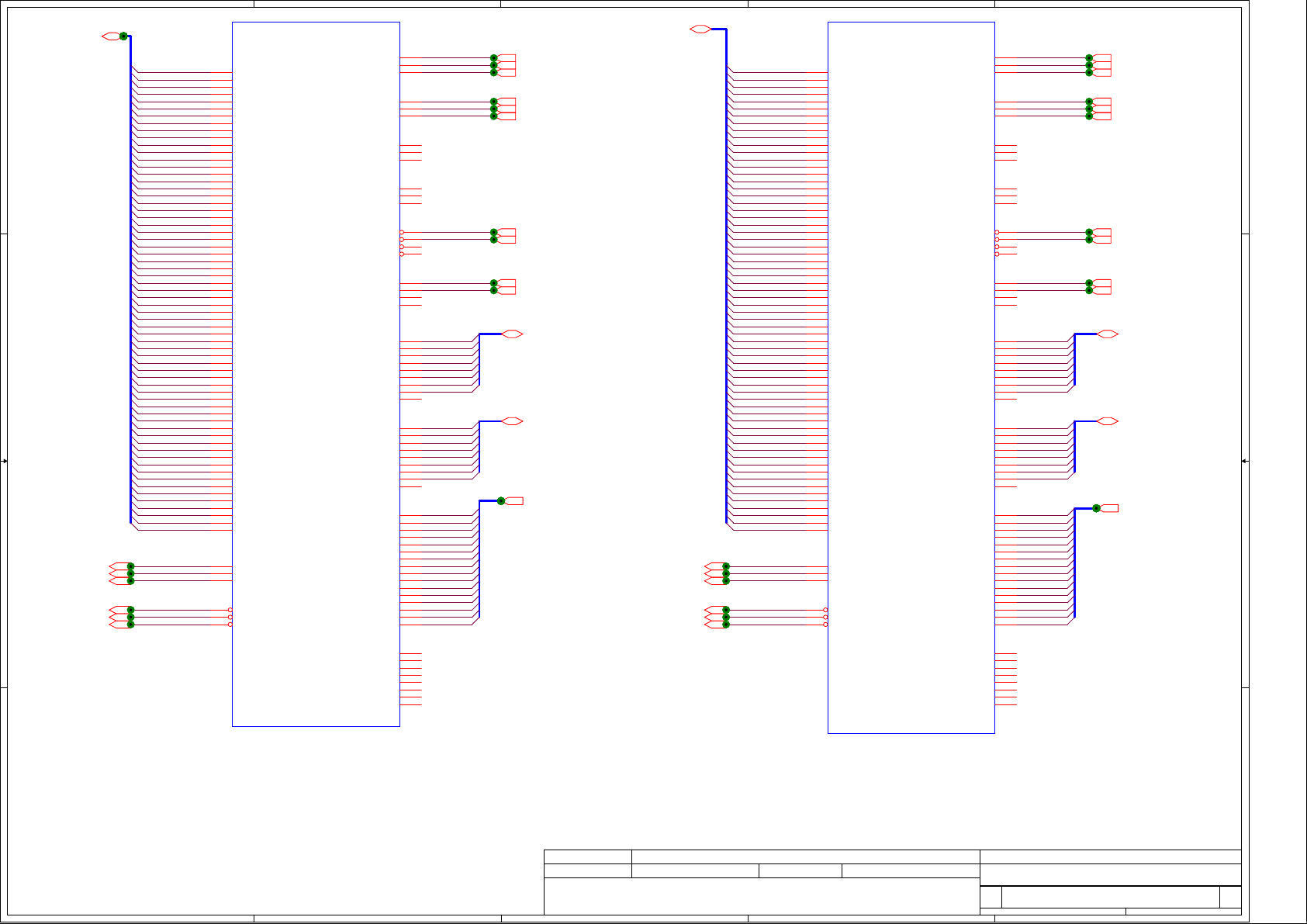

5

DDR_A_D[0..63][11]

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

D D

C C

DDR_A_BS0[11]

B B

DDR_A_BS1[11]

DDR_A_BS2[11]

DDR_A_CAS#[11]

DDR_A_RAS#[11]

DDR_A_WE#[11]

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_A_CAS#

DDR_A_RAS#

DDR_A_WE#

JCPU1C

AJ3

SA_DQ[0]

AJ4

SA_DQ[1]

AL3

SA_DQ[2]

AL4

SA_DQ[3]

AJ2

SA_DQ[4]

AJ1

SA_DQ[5]

AL2

SA_DQ[6]

AL1

SA_DQ[7]

AN1

SA_DQ[8]

AN4

SA_DQ[9]

AR3

SA_DQ[10]

AR4

SA_DQ[11]

AN2

SA_DQ[12]

AN3

SA_DQ[13]

AR2

SA_DQ[14]

AR1

SA_DQ[15]

AV2

SA_DQ[16]

AW3

SA_DQ[17]

AV5

SA_DQ[18]

AW5

SA_DQ[19]

AU2

SA_DQ[20]

AU3

SA_DQ[21]

AU5

SA_DQ[22]

AY5

SA_DQ[23]

AY7

SA_DQ[24]

AU7

SA_DQ[25]

AV9

SA_DQ[26]

AU9

SA_DQ[27]

AV7

SA_DQ[28]

AW7

SA_DQ[29]

AW9

SA_DQ[30]

AY9

SA_DQ[31]

AU35

SA_DQ[32]

AW37

SA_DQ[33]

AU39

SA_DQ[34]

AU36

SA_DQ[35]

AW35

SA_DQ[36]

AY36

SA_DQ[37]

AU38

SA_DQ[38]

AU37

SA_DQ[39]

AR40

SA_DQ[40]

AR37

SA_DQ[41]

AN38

SA_DQ[42]

AN37

SA_DQ[43]

AR39

SA_DQ[44]

AR38

SA_DQ[45]

AN39

SA_DQ[46]

AN40

SA_DQ[47]

AL40

SA_DQ[48]

AL37

SA_DQ[49]

AJ38

SA_DQ[50]

AJ37

SA_DQ[51]

AL39

SA_DQ[52]

AL38

SA_DQ[53]

AJ39

SA_DQ[54]

AJ40

SA_DQ[55]

AG40

SA_DQ[56]

AG37

SA_DQ[57]

AE38

SA_DQ[58]

AE37

SA_DQ[59]

AG39

SA_DQ[60]

AG38

SA_DQ[61]

AE39

SA_DQ[62]

AE40

SA_DQ[63]

AY29

SA_BS[0]

AW28

SA_BS[1]

AV20

SA_BS[2]

AV30

SA_CAS#

AU28

SA_RAS#

AW29

SA_WE#

Sandy Bridge_rPGA_Rev1p0

DDR SYSTEM MEMORY A

4

SA_CK[0]

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CK[2]

SA_CK#[2]

SA_CKE[2]

SA_CK[3]

SA_CK#[3]

SA_CKE[3]

SA_CS#[0]

SA_CS#[1]

SA_CS#[2]

SA_CS#[3]

SA_ODT[0]

SA_ODT[1]

SA_ODT[2]

SA_ODT[3]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS#[8]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_DQS[8]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

SA_ECC_CB[0]

SA_ECC_CB[1]

SA_ECC_CB[2]

SA_ECC_CB[3]

SA_ECC_CB[4]

SA_ECC_CB[5]

SA_ECC_CB[6]

SA_ECC_CB[7]

3

DDR_B_D[0..63][12]

DDRA_CLK0

AY25

DDRA_CLK0#

AW25

DDRA_CKE0

AV19

DDRA_CLK1 DDRB_CLK1

AU24

DDRA_CLK1# DDRB_CLK1#

AU25

DDRA_CKE1 DDRB_CKE1

AT19

AW27

AY27

AU18

AV26

AW26

AV18

DDRA_SCS0# DDRB_SCS0#

AU29

DDRA_SCS1#

AV32

AW30

AU33

DDRA_ODT0 DDRB_ODT0

AV31

DDRA_ODT1

AU32

AU30

AW33

DDR_A_DQS#0

AK2

DDR_A_DQS#1

AP2

DDR_A_DQS#2

AV4

DDR_A_DQS#3

AW8

DDR_A_DQS#4

AV36

DDR_A_DQS#5

AP39

DDR_A_DQS#6

AK39

DDR_A_DQS#7

AF39

AV12

DDR_A_DQS0

AK3

DDR_A_DQS1

AP3

DDR_A_DQS2

AW4

DDR_A_DQS3

AV8

DDR_A_DQS4

AV37

DDR_A_DQS5

AP38

DDR_A_DQS6

AK38

DDR_A_DQS7

AF38

AV13

DDR_A_MA0

AV27

DDR_A_MA1

AY24

DDR_A_MA2

AW24

DDR_A_MA3

AW23

DDR_A_MA4

AV23

DDR_A_MA5

AT24

DDR_A_MA6

AT23

DDR_A_MA7

AU22

DDR_A_MA8

AV22

DDR_A_MA9

AT22

DDR_A_MA10

AV28

DDR_A_MA11

AU21

DDR_A_MA12

AT21

DDR_A_MA13

AW32

DDR_A_MA14

AU20

DDR_A_MA15

AT20

AU12

AU14

AW13

AY13

AU13

AU11

AY12

AW12

DDRA_CLK0 [11] DDRB_CLK0 [12]

DDRA_CLK0# [11]

DDRA_CKE0 [11] DDRB_CKE0 [12]

DDRA_CLK1 [11]

DDRA_CLK1# [11] DDRB_CLK1# [12]

DDRA_CKE1 [11]

DDRA_SCS0# [11]

DDRA_SCS1# [11] DDRB_SCS1# [12]

DDRA_ODT0 [11] DDRB_ODT0 [12]

DDRA_ODT1 [11] DDRB_ODT1 [12]

DDR_A_DQS#[0..7] [11]

DDR_A_DQS[0..7] [11]

DDR_A_MA[0..15] [11]

DDR_B_BS0[12]

DDR_B_BS1[12]

DDR_B_BS2[12]

DDR_B_CAS#[12]

DDR_B_RAS#[12]

DDR_B_WE#[12]

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_B_BS0

DDR_B_BS1

DDR_B_BS2

DDR_B_CAS#

DDR_B_RAS#

DDR_B_WE#

AG7

AG8

AG5

AG6

AM7

AM10

AL10

AM6

AM9

AP7

AR7

AP10

AR10

AP6

AR6

AP9

AR9

AM12

AM13

AR13

AP13

AL12

AL13

AR12

AP12

AR28

AR29

AL28

AL29

AP28

AP29

AM28

AM29

AP32

AP31

AP35

AP34

AR32

AR31

AR35

AR34

AM32

AM31

AL35

AL32

AM34

AL31

AM35

AL34

AH35

AH34

AE34

AE35

AJ35

AJ34

AF33

AF35

AP23

AM24

AW17

AK25

AP24

AR25

AJ9

AJ8

AJ6

AJ7

AL7

AL6

AL9

2

JCPU1D

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

Sandy Bridge_rPGA_Rev1p0

AL21

SB_CK[0]

AL22

SB_CK#[0]

AU16

SB_CKE[0]

AL20

SB_CK[1]

AK20

SB_CK#[1]

AY15

SB_CKE[1]

AL23

SB_CK[2]

AM22

SB_CK#[2]

AW15

SB_CKE[2]

AP21

SB_CK[3]

AN21

SB_CK#[3]

AV15

SB_CKE[3]

AN25

SB_CS#[0]

AN26

SB_CS#[1]

AL25

SB_CS#[2]

AT26

SB_CS#[3]

AL26

SB_ODT[0]

AP26

SB_ODT[1]

AM26

SB_ODT[2]

AK26

SB_ODT[3]

AH6

SB_DQS#[0]

AL8

SB_DQS#[1]

AP8

SB_DQS#[2]

AN12

SB_DQS#[3]

AN28

SB_DQS#[4]

AR33

SB_DQS#[5]

AM33

SB_DQS#[6]

AG34

SB_DQS#[7]

AN15

SB_DQS#[8]

AH7

SB_DQS[0]

AM8

SB_DQS[1]

AR8

SB_DQS[2]

AN13

SB_DQS[3]

AN29

SB_DQS[4]

AP33

SB_DQS[5]

AL33

SB_DQS[6]

AG35

SB_DQS[7]

DDR SYSTEM MEMORY B

SB_ECC_CB[0]

SB_ECC_CB[1]

SB_ECC_CB[2]

SB_ECC_CB[3]

SB_ECC_CB[4]

SB_ECC_CB[5]

SB_ECC_CB[6]

SB_ECC_CB[7]

SB_DQS[8]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

AN16

AK24

AM20

AM19

AK18

AP19

AP18

AM18

AL18

AN18

AY17

AN23

AU17

AT18

AR26

AY16

AV16

AL16

AM16

AP16

AR16

AL15

AM15

AR15

AP15

DDRB_CLK0

DDRB_CLK0#

DDRB_CKE0

DDRB_SCS1#

DDRB_ODT1

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

1

DDRB_CLK0# [12]

DDRB_CLK1 [12]

DDRB_CKE1 [12]

DDRB_SCS0# [12]

DDR_B_DQS#[0..7] [12]

DDR_B_DQS[0..7] [12]

DDR_B_MA[0..15] [12]

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CON SENT O F COMPAL ELECTRONICS, INC.

2010/10/1 2011/11/01

3

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet

Compal Electronics, Inc.

Sandy Bridge_DDR3

PCA70 LA-7521P M/B

764Tuesday, April 12, 2011

1

0.1

of

Page 8

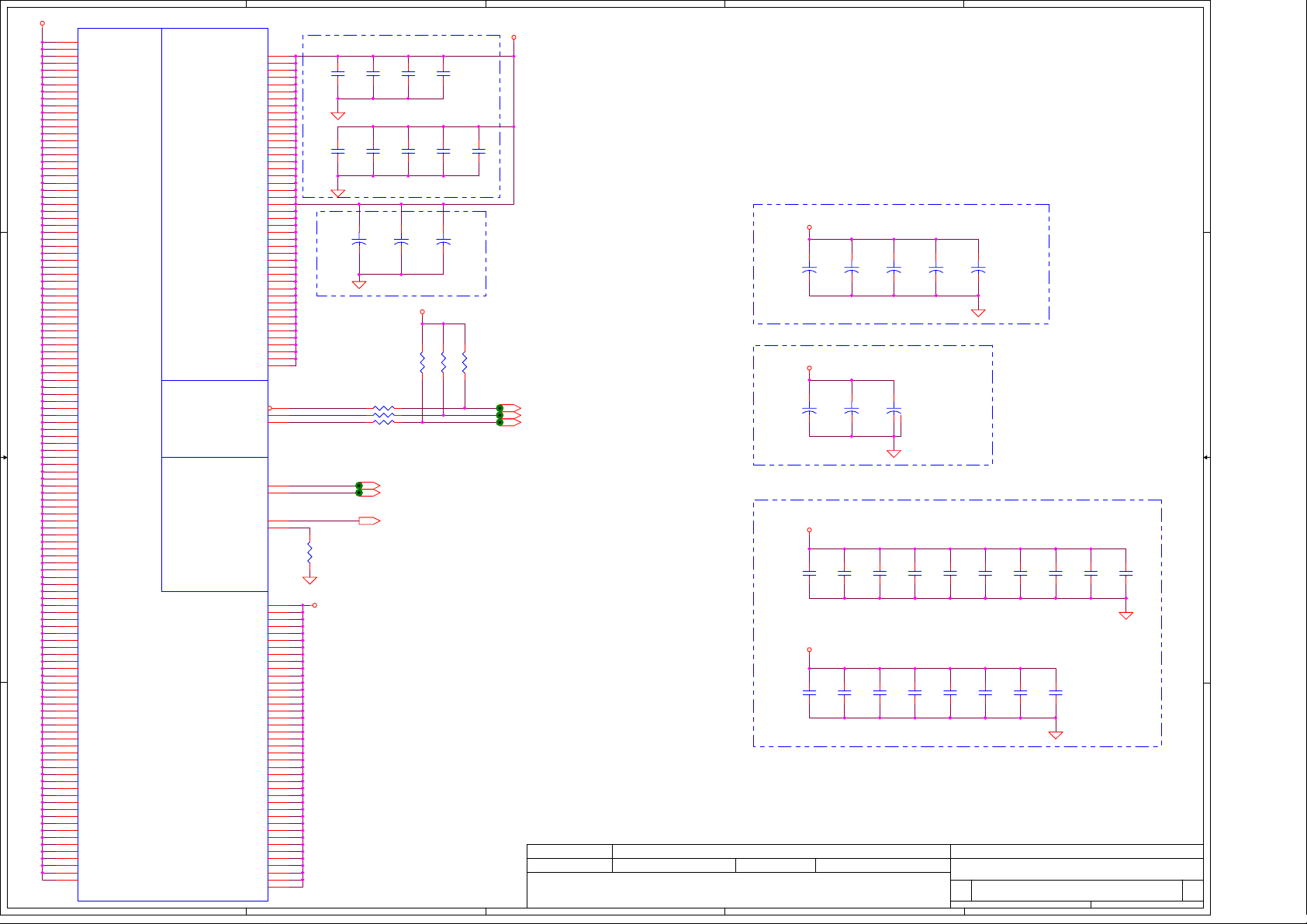

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

VCC101

VCC102

VCC103

VCC104

VCC105

VCC106

VCC107

VCC108

VCC109

VCC110

VCC111

VCC112

VCC113

VCC114

VCC115

VCC116

VCC117

VCC118

VCC119

VCC120

5

POWER

CORE SUPPLY

VSS_SENSE_VCCIO

5

PEG AND DDR

VCC_SENSE

VCCIO_SENSE

VSSIO_SENSE

SENSE LINES SVID

8.5A

VCCIO1

VCCIO2

VCCIO3

VCCIO4

VCCIO5

VCCIO6

VCCIO7

VCCIO8

VCCIO9

VCCIO10

VCCIO11

VCCIO12

VCCIO13

VCCIO14

VCCIO15

VCCIO16

VCCIO17

VCCIO18

VCCIO19

VCCIO20

VCCIO21

VCCIO22

VCCIO23

VCCIO24

VCCIO25

VCCIO26

VCCIO27

VCCIO28

VCCIO29

VCCIO30

VCCIO31

VCCIO32

VCCIO33

VCCIO34

VCCIO35

VCCIO36

VCCIO37

VCCIO38

VCCIO39

VCCIO40

VCCIO41

VCCIO42

VCCIO43

VCCIO44

VCCIO45

VIDALERT#

VIDSCLK

VIDSOUT

VSS_SENSE

VCC121

VCC122

VCC123

VCC124

VCC125

VCC126

VCC127

VCC128

VCC129

VCC130

VCC131

VCC132

VCC133

VCC134

VCC135

VCC136

VCC137

VCC138

VCC139

VCC140

VCC141

VCC142

VCC143

VCC144

VCC145

VCC146

VCC147

VCC148

VCC149

VCC150

VCC151

VCC152

VCC153

VCC154

VCC155

VCC156

VCC157

VCC158

VCC159

VCC160

VCC161

TOP Socket Cavity

22U_0805_6.3V6M

A11

A7

C39

AA3

AB8

AF8

AG33

AJ16

AJ17

AJ26

AJ28

AJ32

AK15

AK17

C43

AK19

AK21

AK23

AK27

AK29

22U_0805_6.3V6M

AK30

B9

D10

D6

E3

E4

G3

G4

C48

J3

J4

560U_2.5V_M

J7

J8

L3

L4

L7

M13

N3

N4

N7

R3

R4

HR's R52=130 ohm

R7

U3

SB CRB suggst 110ohm

U4

U7

V8

W3

R55 43_0402_1%

H_CPU_SVIDALRT#

A37

VR_SVID_CLK_R

C37

VR_SVID_DAT_R

B37

A36

B36

VCCIO_SENSE

AB4

AB3

12

R56

100_0402_1%

J24

+CPU_CORE

J25

J27

J28

J30

K15

K16

K18

K19

K21

K22

K24

K25

K27

K28

K30

L13

L14

L15

L16

L18

L19

L21

L22

L24

L25

L27

L28

L30

M14

M15

M16

M18

M19

M21

M22

M24

M25

M27

M28

M30

+CPU_CORE

D D

C C

B B

A A

JCPU1F

76A (Quad Core 65W)

A12

A13

A14

A15

A16

A18

A24

A25

A27

A28

B15

B16

B18

B24

B25

B27

B28

B30

B31

B33

B34

C15

C16

C18

C19

C21

C22

C24

C25

C27

C28

C30

C31

C33

C34

C36

D13

D14

D15

D16

D18

D19

D21

D22

D24

D25

D27

D28

D30

D31

D33

D34

D35

D36

E15

E16

E18

E19

E21

E22

E24

E25

E27

E28

E30

E31

E33

E34

E35

F15

F16

F18

F19

F21

F22

F24

F25

F27

F28

F30

F31

F32

F33

F34

G15

G16

G18

G19

G21

G22

G24

G25

G27

G28

G30

G31

G32

G33

H13

H14

H15

H16

H18

H19

H21

H22

H24

H25

H27

H28

H30

H31

H32

J12

J15

J16

J18

J19

J21

J22

Sandy Bridge_rPGA_Rev1p0

4

22U_0805_6.3V6M

1

1

C40

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

C44

2

2

1

+

C49

2

560U_2.5V_M

R52

110_0402_5%

1 2

1 2

1 2

R1037 0_0402_5%

R1038 0_0402_5%

4

1

C41

C42

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C46

C45

2

22U_0805_6.3V6M

1

+

C50

2

560U_2.5V_M

+1.05VS_VCCIO

90.9_0402_1%

12

@

R53

VCCSENSE [58]

VSSSENSE [ 58]

VCCIO_SENSE [54]

1

2

1

C47

2

22U_0805_6.3V6M

1

+

2

12

12

R54

75_0402_5%

+1.05VS_VCCIO

+1.05VS_VCCP Decoupling:

3X 560U (6m ohm), 9X 22U

1

2

Pull high resistor close to CPU

SVID signal 50 ohm impedance

spacing >12mil length 3-6"

VR_SVID_ALRT# [58]

VR_SVID_CLK [58]

VR_SVID_DAT [58]

Security Classification

Issued Date

THIS SHEET OF EN GINEER ING DR AWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED B Y OR D ISCLOS ED T O ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

+CPU_CORE Decoupling:

5X 560U (4m ohm), 2X330U, 18X 22U

C51

560U_2.5V_M

330U_D2_2V_Y

22U_0805_6.3V6M

2010/10/1 2011/11/01

3

Compal Secret Data

Deciphered Date

2

TOP Socket Edge

+CPU_CORE

1

+

2

C52

560U_2.5V_M

1

+

2

1

+

2

C53

560U_2.5V_M

C54

560U_2.5V_M

1

+

2

1

+

C59

560U_2.5V_M

2

Bottom Socket Edge

+CPU_CORE

1

1

C55

@

+

2

C56

@

330U_D2_2V_Y

1

+

+

C58

330U_D2_2VM_R6M

2

2 3

14 pcs in TOP and 4pcs in BOT Socket Cavity

+CPU_CORE

22U_0805_6.3V6M

1

1

C67

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

C77

2

2

Sandy Bridge_POWER-1

1

C61

C60

2

22U_0805_6.3V6M

+CPU_CORE

22U_0805_6.3V6M

1

C70

C71

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

C62

2

2

1

1

C72

2

2

22U_0805_6.3V6M

2

22U_0805_6.3V6M

1

C63

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C73

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

C64

2

1

C74

2

Date: Sheet

C66

C65

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C75

C76

2

22U_0805_6.3V6M

Title

Size Docum ent Number Rev

Custom

Compal Electronics, Inc.

PCA70 LA-7521P M/B

C68

1

1

C69

2

22U_0805_6.3V6M

1

1

2

0.1

of

864Tuesday, April 12, 2011

Page 9

5

4

3

2

1

+GFX_CORE Decoupling:

2X 470U (4m ohm), 12X 22U

Bottom

+GFX_CORE

Socket

Edge

D D

C80

@

330U_D2_2VM_R6M

Top Socket Cavity

22U_0805_6.3V6M

C82

UMA@

Bottom Socket Edge

22U_0805_6.3V6M

UMA@

C99

C C

Top Socket Edge

330U_D2_2VM_R6M

1

1

+

+

UMA@

C1588

2

2

330U_D2_2VM_R6M

22U_0805_6.3V6M

UMA@

1

1

C84

C83

UMA@

2

2

22U_0805_6.3V6M

UMA@

1

1

C100

2

2

22U_0805_6.3V6M

1

+

@

C78

2

UMA@

1

1

C85

2

2

22U_0805_6.3V6M

1

+

UMA@

C79

2

560U_2.5V_M

1

+

UMA@

C81

560U_2.5V_M

2

AB33

AB34

AB35

AB36

AB37

AB38

AB39

AB40

AC33

AC34

AC35

AC36

AC37

AC38

AC39

AC40

W33

W34

W35

W36

W37

W38

U33

U34

U35

U36

U37

U38

U39

U40

Y33

Y34

Y35

Y36

Y37

Y38

T33

T34

T35

T36

T37

T38

T39

T40

JCPU1G

35A

VCCAXG1

VCCAXG2

VCCAXG3

VCCAXG4

VCCAXG5

VCCAXG6

VCCAXG7

VCCAXG8

VCCAXG9

VCCAXG10

VCCAXG11

VCCAXG12

VCCAXG13

VCCAXG14

VCCAXG15

VCCAXG16

VCCAXG17

VCCAXG18

VCCAXG19

VCCAXG20

VCCAXG21

VCCAXG22

VCCAXG23

VCCAXG24

VCCAXG25

VCCAXG26

VCCAXG27

VCCAXG28

VCCAXG29

VCCAXG30

VCCAXG31

VCCAXG32

VCCAXG33

VCCAXG34

VCCAXG35

VCCAXG36

VCCAXG37

VCCAXG38

VCCAXG39

VCCAXG40

VCCAXG41

VCCAXG42

VCCAXG43

VCCAXG44

VCCPLL Decoupling:

1X 220U, 2X 10U

+1.8VS

B B

R65 0_0805_5%

+1.8VS_VCCPLL

12

C105

220U_6.3V_M

10U_0805_10V6K

1

1

+

C106

2

2

1

C107

@

2

10U_0805_10V6K

1.5A

AK11

VCCPLL1

AK12

VCCPLL2

Sandy Bridge_rPGA_Rev1p0

POWER

SENSE

VREFMISC DDR3 -1.5V RAILS

GRAPHICS

SA RAIL

1.8V RAIL

VCCAXG_SENSE

VSSAXG_SENSE

LINES

SM_VREF

4.75A

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VDDQ19

VDDQ20

VDDQ21

VDDQ22

VDDQ23

8.8A

VCCSA1

VCCSA2

VCCSA3

VCCSA4

VCCSA5

VCCSA6

VCCSA7

VCCSA8

VCCSA9

VCCSA10

VCCSA11

VCCSA_SENSE

VCCSA_VID

FC_AH1

FC_AH4

L32

M32

+V_SM_VREF should

have 20 mil trace width

AJ22

AJ13

AJ14

AJ20

AJ23

AJ24

AR20

AR21

AR22

AR23

AR24

AU19

AU23

AU27

AU31

AV21

AV24

AV25

AV29

AV33

AW31

AY23

AY26

AY28

22U_0805_6.3V6M

TOP Socket Cavity

10U_0805_10V6K

H10

H11

H12

J10

C101

K10

K11

L11

L12

M10

M11

M12

T2

P34

AH1

AH4

+VREF_DQB_R

+VREF_DQA_R

C108 0.1U_0402_16V4Z

1

1

2

2

10U_0805_10V6K

C109 0.1U_0402_16V4Z

VCC_AXG_SENSE [58]

VSS_AXG_SENSE [58]

+1.5V

12

R61

100_0402_1%

+V_SM_VREF

C86

22U_0805_6.3V6M

C90

1

C102

2

1

0.1U_0402_16V4Z

2

1

1

C91

2

2

22U_0805_6.3V6M

10U_0805_10V6K

1

1

C103

@

2

2

22U_0805_6.3V6M

1

C92

2

C93

+VCCSA

1

+

2

12

R62

100_0402_1%

1

1

C94

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C95

1

1

C96

@

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C97

@

+VCCSA Decoupling:

1X 560U, 2X 10U

C104

560U_2.5V_M

VCCSA_SENSE [56]

VCCSAP_VID1 [56]

1

C98

@

2

22U_0805_6.3V6M

0

1

2

1

1 2

1 2

R66 0_0402_5%

R67 0_0402_5%

R66,R67 should place close to DIMM for

+VREF_DQB

+VREF_DQA

minimum stubs trace

330U_D2_2VM_R6M

1

+

C88

C87

2

330U_D2_2VM_R6M

+VCCSAVCCSA_VID1

0.925 V

(Default)

0.85 V

+1.5V

+1.5V Decoupling:

1

1

+

C89

2

3X 330U , 9X 22U

+

@

330U_D2_2VM_R6M

2

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CON SENT O F COMPAL ELECTRONICS, INC.

2010/10/1 2011/11/01

3

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet

Compal Electronics, Inc.

Sandy Bridge_POWER-2

PCA70 LA-7521P M/B

964Tuesday, April 12, 2011

1

0.1

of

Page 10

5

JCPU1H

A17

VSS1

A23

VSS2

A26

VSS3

A29

VSS4

A35

VSS5

AA33

VSS6

AA34

VSS7

AA35

VSS8

AA36

VSS9

AA37

VSS10

AA38

D D

C C

B B

A A

VSS11

AA6

VSS12

AB5

VSS13

AC1

VSS14

AC6

VSS15

AD33

VSS16

AD36

VSS17

AD38

VSS18

AD39

VSS19

AD40

VSS20

AD5

VSS21

AD8

VSS22

AE3

VSS23

AE33

VSS24

AE36

VSS25

AF1

VSS26

AF34

VSS27

AF36

VSS28

AF37

VSS29

AF40

VSS30

AF5

VSS31

AF6

VSS32

AF7

VSS33

AG36

VSS34

AH2

VSS35

AH3

VSS36

AH33

VSS37

AH36

VSS38

AH37

VSS39

AH38

VSS40

AH39

VSS41

AH40

VSS42

AH5

VSS43

AH8

VSS44

AJ12

VSS45

AJ15

VSS46

AJ18

VSS47

AJ21

VSS48

AJ25

VSS49

AJ27

VSS50

AJ36

VSS51

AJ5

VSS52

AK1

VSS53

AK10

VSS54

AK13

VSS55

AK14

VSS56

AK16

VSS57

AK22

VSS58

AK28

VSS59

AK31

VSS60

AK32

VSS61

AK33

VSS62

AK34

VSS63

AK35

VSS64

AK36

VSS65

AK37

VSS66

AK4

VSS67

AK40

VSS68

AK5

VSS69

AK6

VSS70

AK7

VSS71

AK8

VSS72

AK9

VSS73

AL11

VSS74

AL14

VSS75

AL17

VSS76

AL19

VSS77

AL24

VSS78

AL27

VSS79

AL30

VSS80

AL36

VSS81

AL5

VSS82

AM1

VSS83

AM11

VSS84

AM14

VSS85

AM17

VSS86

AM2

VSS87

AM21

VSS88

AM23

VSS89

AM25

VSS90

AM27

VSS91

AM3

VSS92

AM30

VSS93

AM36

VSS94

AM37

VSS95

AM38

VSS96

AM39

VSS97

AM4

VSS98

AM40

VSS99

AM5

VSS100

Sandy Bridge_rPGA_Rev1p0

VSS

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

AN10

AN11

AN14

AN17

AN19

AN22

AN24

AN27

AN30

AN31

AN32

AN33

AN34

AN35

AN36

AN5

AN6

AN7

AN8

AN9

AP1

AP11

AP14

AP17

AP22

AP25

AP27

AP30

AP36

AP37

AP4

AP40

AP5

AR11

AR14

AR17

AR18

AR19

AR27

AR30

AR36

AR5

AT1

AT10

AT12

AT13

AT15

AT16

AT17

AT2

AT25

AT27

AT28

AT29

AT3

AT30

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AT39

AT4

AT40

AT5

AT6

AT7

AT8

AT9

AU1

AU15

AU26

AU34

AU4

AU6

AU8

AV10

AV11

AV14

AV17

AV3

AV35

AV38

AV6

AW10

AW11

AW14

AW16

AW36

AW6

AY11

AY14

AY18

AY35

AY4

AY6

AY8

B10

B13

B14

B17

B23

B26

B29

B32

B35

B38

B6

C11

C12

C17

C20

C23

C26

C29

C32

C35

C7

C8

D17

D2

D20

D23

D26

D29

D32

D37

D39

D4

D5

D9

E11

E12

E17

E20

E23

E26

E29

E32

E36

E7

E8

F1

F10

F13

F14

F17

F2

F20

F23

F26

F29

F35

F37

F39

F5

F6

F9

G11

G12

G17

G20

G23

G26

G29

G34

G7

G8

H1

H17

H2

H20

H23

H26

H29

H33

H35

H37

H39

H5

H6

H9

J11

J17

J20

J23

J26

J29

J32

K1

K12

K13

K14

K17

K2

K20

K23

4

JCPU1I

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

VSS286

VSS287

VSS288

VSS289

VSS290

VSS291

VSS292

VSS293

VSS294

VSS295

VSS296

VSS297

VSS298

VSS299

VSS300

Sandy Bridge_rPGA_Rev1p0

VSS

VSS301

VSS302

VSS303

VSS304

VSS305

VSS306

VSS307

VSS308

VSS309

VSS310

VSS311

VSS312

VSS313

VSS314

VSS315

VSS316

VSS317

VSS318

VSS319

VSS320

VSS321

VSS322

VSS323

VSS324

VSS325

VSS326

VSS327

VSS328

VSS329

VSS330

VSS331

VSS332

VSS333

VSS334

VSS335

VSS336

VSS337

VSS338

VSS339

VSS340

VSS341

VSS342

VSS343

VSS344

VSS345

VSS346

VSS347

VSS348

VSS349

VSS350

VSS351

VSS352

VSS353

VSS354

VSS355

VSS356

VSS357

VSS358

VSS359

VSS360

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

K26

K29

K33

K35

K37

K39

K5

K6

L10

L17

L20

L23

L26

L29

L8

M1

M17

M2

M20

M23

M26

M29

M33

M35

M37

M39

M5

M6

M9

N8

P1

P2

P36

P38

P40

P5

P6

R33

R35

R37

R39

R8

T1

T5

T6

U8

V1

V2

V33

V34

V35

V36

V37

V38

V39

V40

V5

W6

Y5

Y8

A4

AV39

AY37

B3

T236PAD

T15 PAD

T16 PAD

T17 PAD

T18 PAD

T19 PAD

T20 PAD

T21 PAD

T22 PAD

T23 PAD

T24 PAD

T25 PAD

T26 PAD

T27 PAD

3

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6 CFG5

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

JCPU1E

H36

CFG[0]

J36

CFG[1]

J37

CFG[2]

K36

CFG[3]

L36

CFG[4]

N35

CFG[5]

L37

CFG[6]

M36

CFG[7]

J38

CFG[8]

L35

CFG[9]

M38

CFG[10]

N36

CFG[11]

N38

CFG[12]

N39

CFG[13]

N37

CFG[14]

N40

CFG[15]

G37

CFG[16]

G36

CFG[17]

AB6

RSVD1

AB7

RSVD2

AD37

RSVD3

AE6

RSVD4

AF4

RSVD5

AG4

RSVD6

AJ11

RSVD7

AJ29

RSVD8

AJ30

RSVD9

AJ31

RSVD10

AN20

RSVD11

AP20

RSVD12

AT11

RSVD13

AT14

RSVD14

AU10

RSVD15

AV34

RSVD16

AW34

RSVD17

AY10

RSVD18

C38

RSVD19

C39

RSVD20

D38

RSVD21

H7

RSVD22

H8

RSVD23

J33

RSVD24

J34

RSVD25

J9

RSVD26

K34

RSVD27

K9

RSVD28

L31

RSVD29

L33

RSVD30

L34

RSVD31

L9

RSVD32

M34

RSVD33

N33

RSVD34

N34

RSVD35

P35

RSVD36

P37

RSVD37

P39

RSVD38

R34

RSVD39

R36

RSVD40

R38

RSVD41

R40

RSVD42

J31

RSVD43

AD34

RSVD44

AD35

RSVD45

K31

RSVD46

Sandy Bridge_rPGA_Rev1p0

RESERVED

VCCIO_SEL

RSVD_NCTF1

RSVD_NCTF2

RSVD_NCTF3

RSVD_NCTF4

NCTF1

NCTF2

NCTF3

NCTF4

NCTF5

2

CFG Straps for Processor

(CFG[17:0] internal pull high to VCCIO)

PEG Static x16 Lane Numbering Reversal.

CFG2

PEG Static x4 Lane Numbering Reversal.

CFG3

1: Normal Operation

0:Lane numbers Reversed

*

1: Normal Operation

*

0:Lane numbers Reversed

PCIE Port Bifurcation Straps

11: 1x16 PCI Express (Default)

*

CFG[6:5]

10: 2x8 PCI Express

01: Reserved

00: 1 x 8, 2 x 4 : PCI Express

A38

AU40

AW38

C2

D1

P33

AV1

AW2

AY3

B39

R1664

0_0402_5%

1 2

+5VS

1 2

1 2

CFG2

R70 1K_0402_1%

CFG3

CFG6

R1576

10K_0402_1%

R1577

5.1K_0402_1%

1 2

R71 1K_0402_1%@

1 2

R73 1K_0402_1%@

1 2

R74 1K_0402_1%@

1 2

VCCIO_SEL [54]

VCCIO_SEL

1

Reserve for PW

VCCIO

0

1

1.00V

1.05V

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CON SENT O F COMPAL ELECTRONICS, INC.

2010/10/1 2011/11/01

3

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet

Compal Electronics, Inc.

Sandy Bridge_GND/RSVD/CFG

PCA70 LA-7521P M/B

1

of

10 64Tuesday, April 12, 2011

0.1

Page 11

5

DDR_A_DQS[0..7][7]

DDR_A_DQS#[0..7][7]

DDR_A_D[0..63][7]

D D

C C

Layout Note:

Place near JDDRL1

+1.5V

B B

A A

+

C143 390U_2.5V_M_R10

1 2

C145 10U_0805_6.3V6M

1 2

C147 10U_0805_6.3V6M

1 2

C149 10U_0805_6.3V6M

1 2

C151 10U_0805_6.3V6M

1 2

C152 10U_0805_6.3V6M

1 2

C153 10U_0805_6.3V6M

1 2

DDR_A_MA[0..15][7]

Layout Note:

Place near JDDRL1.203 and 204

+0.75VS

C134 10U_0805_6.3V6M

1 2

C135 1U_0402_6.3V6K

1 2

C136 1U_0402_6.3V6K

1 2

C139 1U_0402_6.3V6K

1 2

C140 1U_0402_6.3V6K

1 2

Layout Note : P la ce these 4 Caps near

Command and Control signals of JDDRL1

+1.5V

C144 0.1U_0402_16V4Z

1 2

C146 0.1U_0402_16V4Z

1 2

C148 0.1U_0402_16V4Z

1 2

C150 0.1U_0402_16V4Z

1 2

4

+1.5V

R91

1K_0402_1%

1 2

1K_0402_1%

3

CHA SO-DIMM 0(A0)

+0.75VS

12

R98

10K_0402_5%

+1.5V

JDDRL2

VREF_DQ1VSS1

3

VSS2

5

DQ0

7

DQ1

9

VSS4

11

DM0

13

VSS5

15

DQ2

17

DQ3

19

VSS7

21

DQ8

23

DQ9

25

VSS9

27

DQS#1

DQS129RESET#

VSS1131VSS12

33

DQ10

35

DQ11

VSS1337VSS14

39

DQ16

41

DQ17

VSS1543VSS16

45

DQS#2

47

DQS2

49

VSS18

51

DQ18

53

DQ19

55

VSS20

57

DQ24

59

DQ25

VSS2261DQS#3

63

DM3

VSS2365VSS24

67

DQ26

69

DQ27

VSS2571VSS26

73

CKE0

75

VDD1

77

NC1

79

BA2

81

VDD3

83

A12/BC#

85

A9

87

VDD5

89

A8

91

A5

93

VDD7

95

A3

97

A1

99

VDD9

101

CK0

103

CK0#

105

VDD11

107

A10/AP

109

BA0

111

VDD13

113

WE#

115

CAS#

117

VDD15

119

A13

121

S1#

123

VDD17

125

NCTEST

127

VSS27

129

DQ32

131

DQ33

133

VSS29

135

DQS#4

137

DQS4

139

VSS32

141

DQ34

143

DQ35

145

VSS34

147

DQ40

149

DQ41

151

VSS36

153

DM5

155

VSS37

157

DQ42

159

DQ43

161

VSS39

163

DQ48

165

DQ49

167

VSS41

169

DQS#6

171

DQS6

173

VSS44

175

DQ50

177

DQ51

179

VSS46

181

DQ56

183

DQ57

185

VSS48

187

DM7

189

VSS49

191

DQ58

193

DQ59

195

VSS51

197

SA0

199

VDDSPD

201

SA1

203

VTT1

205

G1

TYCO_2-2013290-1

CONN@

DQS#0

DQS0

DQ12

DQ13

VSS10

DQ14

DQ15

DQ20

DQ21

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS3

DQ30

DQ31

VDD2

VDD4

VDD6

VDD8

VDD10

VDD12

VDD14

ODT0

VDD16

ODT1

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

+VREF_DQA

12

R93

2.2U_0603_6.3V6K

0.1U_0402_16V4Z

C114

1

2

Close to JDDRL.1

DDR_A_BS2[7]

DDRA_CLK0[7]

DDRA_CLK0#[7]

DDR_A_BS0[7]

DDR_A_WE#[7]

DDR_A_CAS#[7]

DDRA_SCS1#[7]

+3VS

2.2U_0603_6.3V6K

C154

+VREF_DQA

DDR_A_D0

DDR_A_D1

C115

1

2

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_D18

DDR_A_D19

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDRA_CKE0 DDRA_CKE1

DDR_A_BS2

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

DDRA_CLK0# DDRA_CLK1#

DDR_A_MA10

DDR_A_BS0

DDR_A_WE#

DDR_A_CAS#

DDR_A_MA13

DDRA_SCS1#

DDR_A_D32

DDR_A_D33

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_D34

DDR_A_D35

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D48

DDR_A_D49

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_D50

DDR_A_D51

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

R97 10K_0402_5%

1 2

0.1U_0402_16V4Z

C155

1

1

2

2

DQ4

DQ5

VSS3

VSS6

DQ6

DQ7

VSS8

DM1

DM2

CKE1

CK1

CK1#

RAS#

NC2

DM4

DM6

SDA

SCL

VTT2

+1.5V

2

DDR_A_D4

4

DDR_A_D5

6

8

DDR_A_DQS#0

10

DDR_A_DQS0

12

14

DDR_A_D6

16

DDR_A_D7

18

20

DDR_A_D12

22

DDR_A_D13

24

26

28

SM_DRAMRST#

30

32

DDR_A_D14

34

DDR_A_D15

36

38

DDR_A_D20

40

DDR_A_D21

42

44

46

48

DDR_A_D22

50

DDR_A_D23

52

54

DDR_A_D28

56

DDR_A_D29

58

60

DDR_A_DQS#3

62

DDR_A_DQS3

64

66

DDR_A_D30

68

DDR_A_D31

70

72

74

76

DDR_A_MA15

78

A15

A14

A11

A7

A6

A4

A2

A0

BA1

S0#

G2

DDR_A_MA14

80

82

DDR_A_MA11

84

DDR_A_MA7

86

88

DDR_A_MA6

90

DDR_A_MA4

92

94

DDR_A_MA2

96

DDR_A_MA0

98

100