Page 1

A

1 1

2 2

B

C

D

E

Compal Confidential

PBL22 MB Schematic Document

LA-7391P

3 3

Rev: 0.2

2011.04.07

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEER I N G D R AW ING IS THE PROPRIETARY PR OPER T Y OF C OMPAL ELECTRONICS, INC . AN D C ON T AINS CONFIDENTIAL

THIS SHEET OF ENGINEER I N G D R AW ING IS THE PROPRIETARY PR OPER T Y OF C OMPAL ELECTRONICS, INC . AN D C ON T AINS CONFIDENTIAL

THIS SHEET OF ENGINEER I N G D R AW ING IS THE PROPRIETARY PR OPER T Y OF C OMPAL ELECTRONICS, INC . AN D C ON T AINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2009/12/01 2011/12/31

2009/12/01 2011/12/31

2009/12/01 2011/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

Cover Sheet

Cover Sheet

Cover Sheet

LA-7391P

LA-7391P

LA-7391P

E

0.2

0.2

0.2

of

of

of

164Thursday, April 07, 2011

164Thursday, April 07, 2011

164Thursday, April 07, 2011

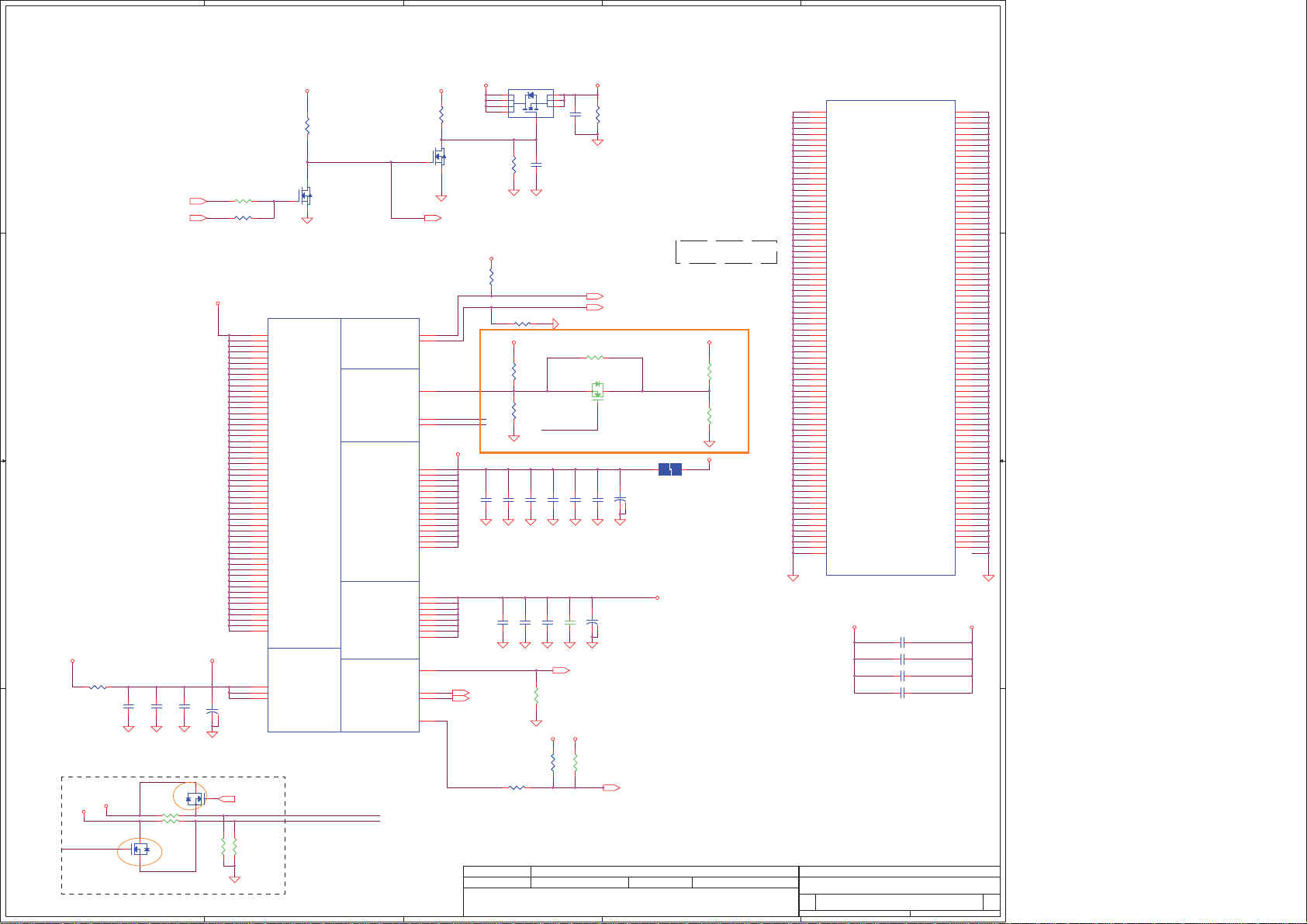

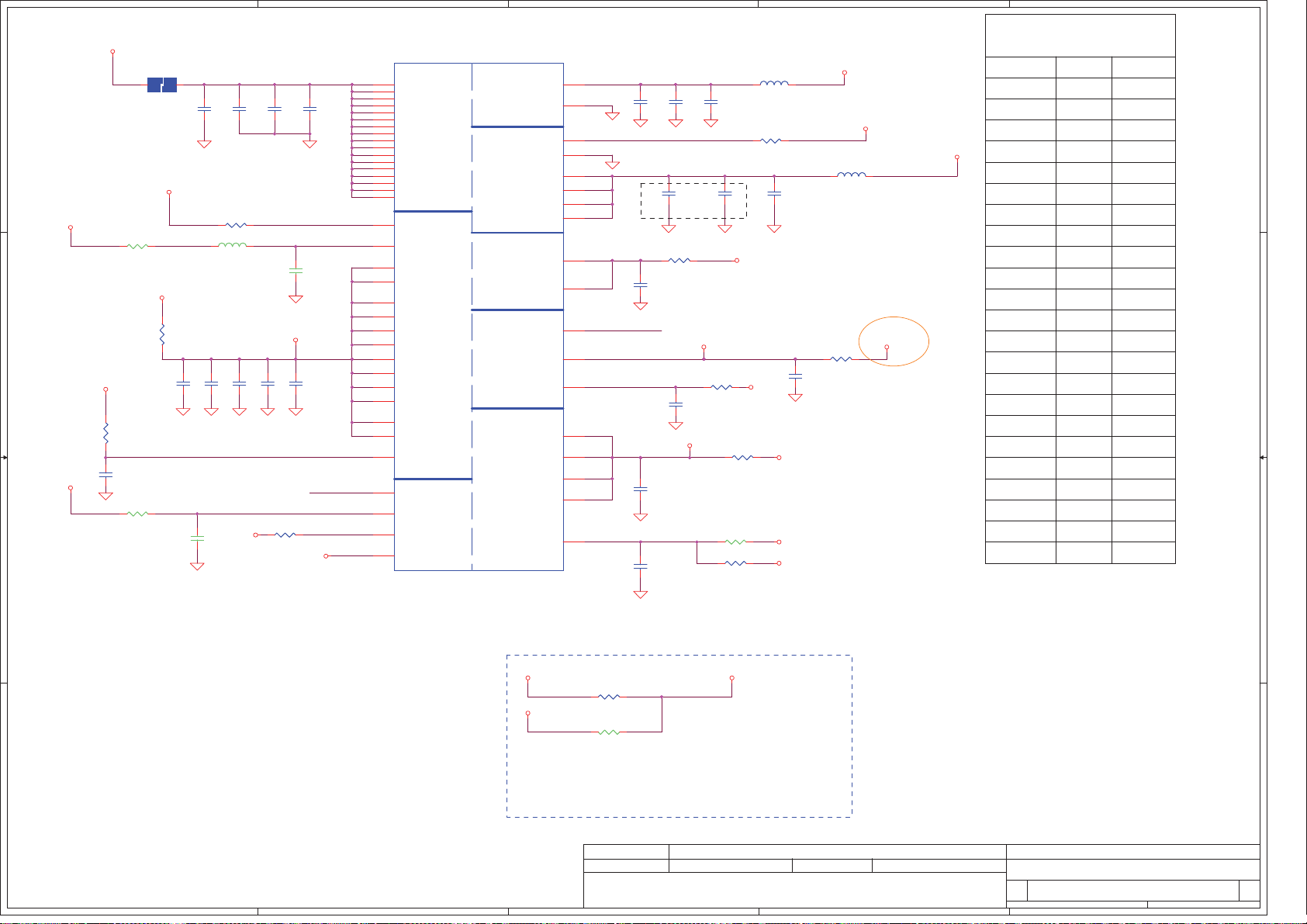

Page 2

A

B

C

D

E

Compal Confidential

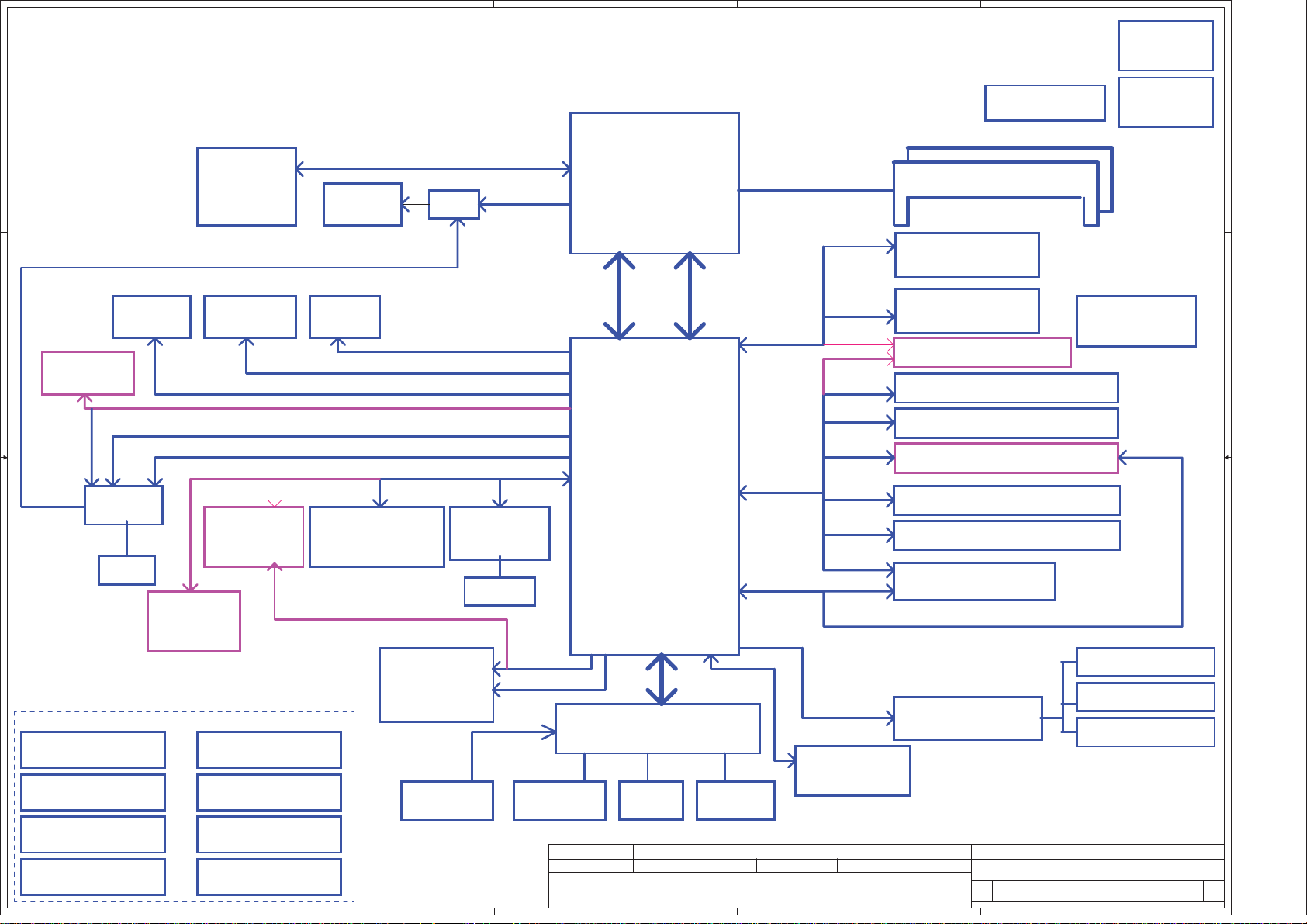

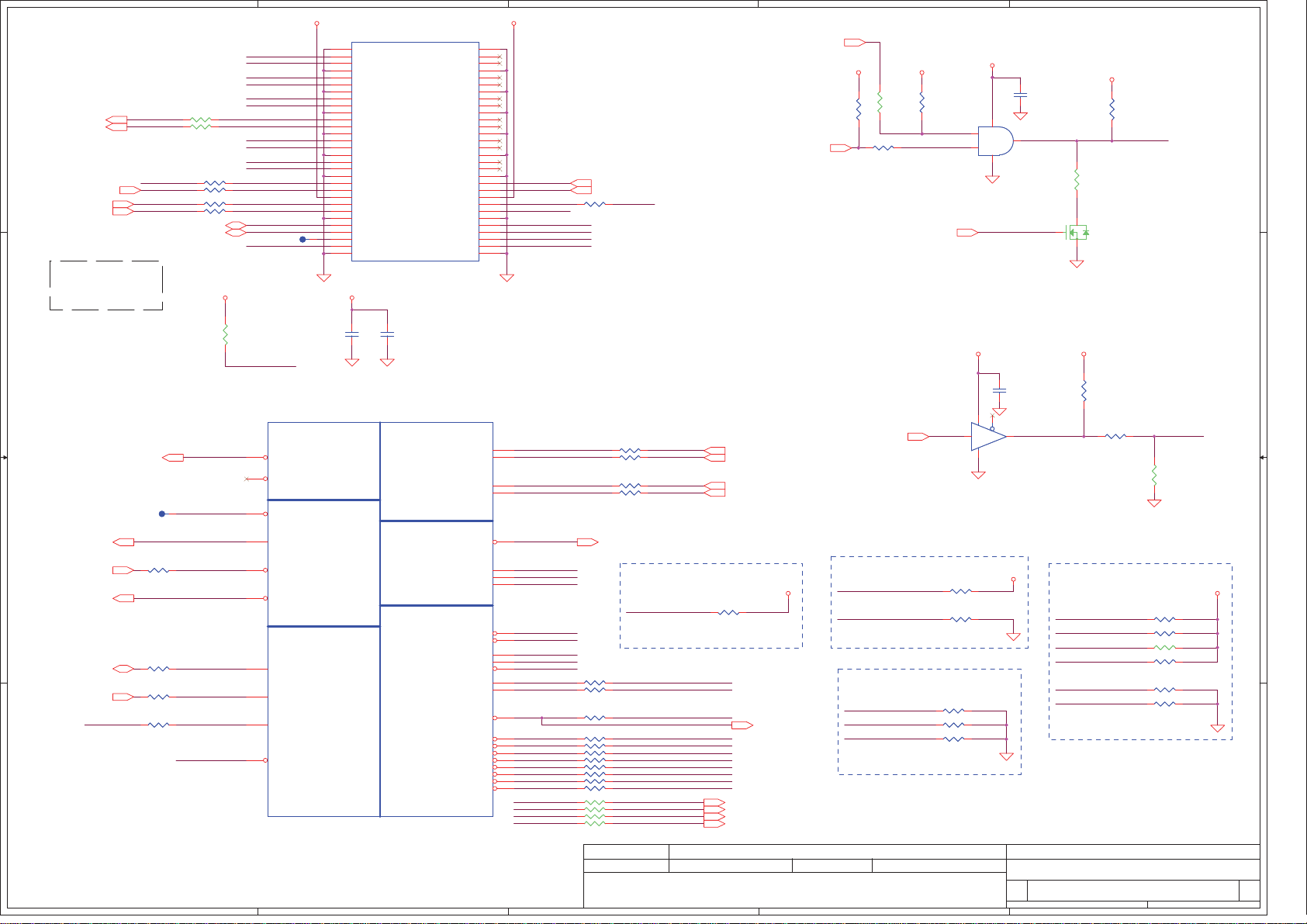

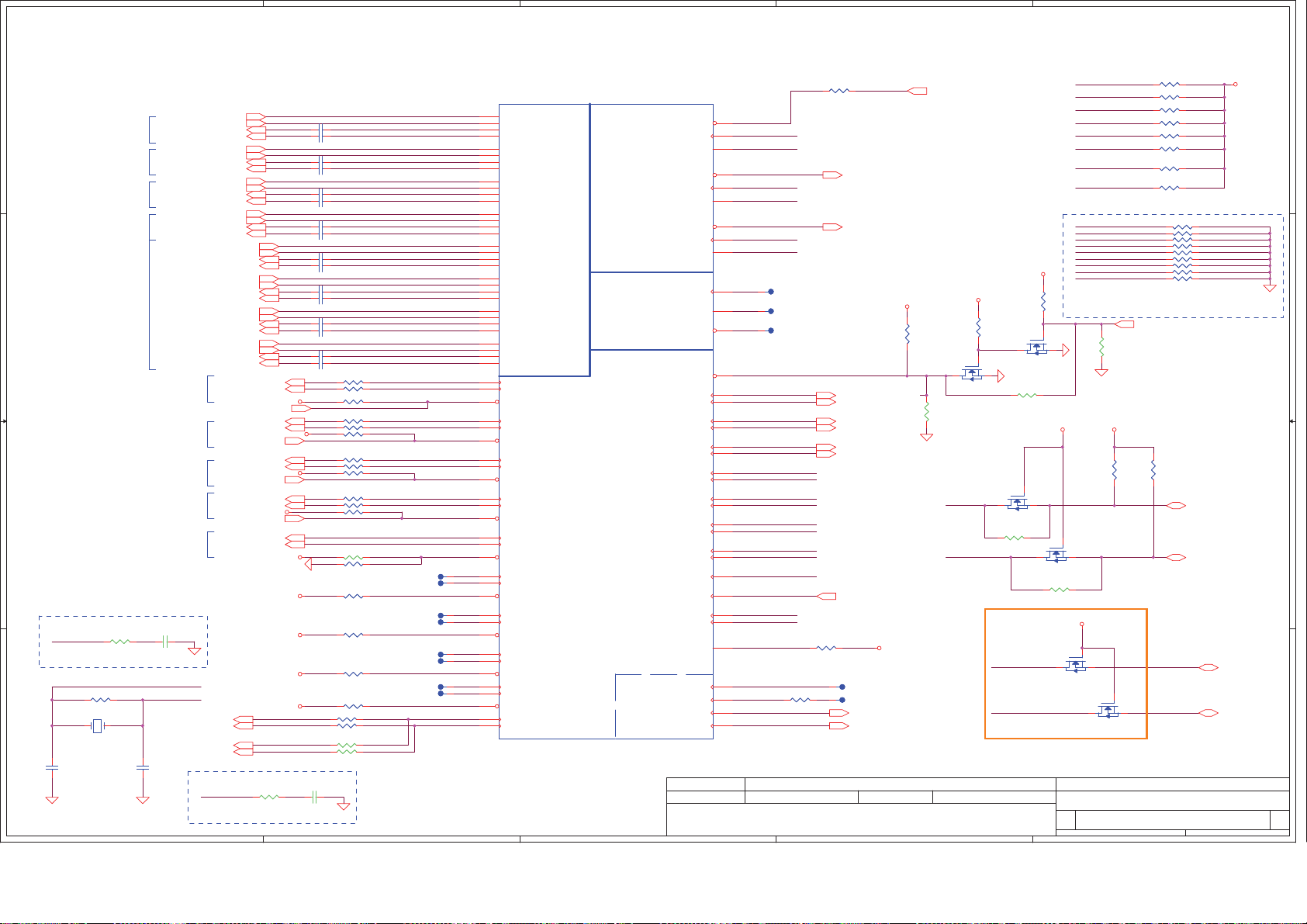

Project Code : PBL22

Chief River

CPU XDP

Conn.

P.5

File Name : LA-7391P

P.38

P.51

E

PCH XDP

Conn.

USB board

Port 0

Audio board

Audio board

Audio board

of

of

of

264Thursday, April 07, 2011

264Thursday, April 07, 2011

264Thursday, April 07, 2011

P.15

0.2

0.2

0.2

Fan Control

1 1

PEG x16 (DIS)

GEN 1/2/3

N12P-GE

64*16 1GB

P.24-35

LVDS Conn.

P.38 P.44 P.37

2 2

eDP Conn.

CRT Conn.HDMI Conn.

P.36

OPTIMUS/UMA

SW

DP Conn.

IO board

Port 5-8

Light Peak

P.52-53

3 3

P.54

CIO

7 in 1 card

Port 2

Express Card

IO board

Port 4

Mini Card-1

WLAN (Half)

+Blue Tooth combo

USB2.0 port 10

Port 3

P.51

Reader

IO board

Mini Card-1

WWAN (full)

Reserved for

Sub-board

IO board (LS-7391P)

IO Board to Board :LS-7394P

4 4

Audio Board : LS-7392P

USB (Port,11)

Light Peak Board : LS-7393P

USB (Port,10)

P.47

P.46

P.46

A

Function Board: LS-6002P

PWR Button Board:LS-6003P

USB Board : LS7395P

FPC Cable : LF7391P

P.50

P.48

P.46

P.46

m-SATA

ENE 3810

B

eDP (UMA)

CRT

HDMI

LVDS

DisplayPort

DisplayPort

PCI-E x4

PCI-E x1

Port 1

LAN(GbE)

RTL8111E-VB

RJ45

P.42

USB2.0 port 5

SATA Port1

P.51

P.47

Touch Pad Int.KBD

(UMA)

100MHz

2.7GT/s

ENE KB930/Co-lay KB9012

P.50 P.50 P.50

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEER I N G D R AW ING IS THE PROPRIETARY PR OPER T Y OF C OMPAL ELECTRONICS, INC . AN D C ON T AINS CONFIDENTIAL

THIS SHEET OF ENGINEER I N G D R AW ING IS THE PROPRIETARY PR OPER T Y OF C OMPAL ELECTRONICS, INC . AN D C ON T AINS CONFIDENTIAL

THIS SHEET OF ENGINEER I N G D R AW ING IS THE PROPRIETARY PR OPER T Y OF C OMPAL ELECTRONICS, INC . AN D C ON T AINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Intel

Ivy Bridge

Processor

rPGA 989 Socket

Intel

Cougar Point

Panther Point

PCH

BGA 989 Balls

LPC Bus

2009/12/01 2011/12/31

2009/12/01 2011/12/31

2009/12/01 2011/12/31

C

P.4~9

DMI x4FDI x8

100MHz

5GB/s

P15~22

EC ROM

Memory Bus

Dual Channel

1.5V DDR3 1866MHz

SATA

USB2.0

USB 3.0

HD Audio

SPI

P.49

SYS BIOS ROM

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Port 0

Port 2

Port 4

Port 1

Port 8

Port 9

Port 0

Port 8

Port 4

Port 2

Port 2

204pin DDRIII SO-DIMM x2

BANK 0, 1, 2, 3

SATA HDD-1 Conn.

SATA 3.0

SATA ODD Conn.

SATA 2.0

ESATA+ USB 2.0

USB 2.0 Conn.

on right side

USB 2.0 Conn./light peak

on right side

USB 2.0 /USB 3.0 Conn.

Camera

Mini Card-1 (WLAN& BTcombo)

( Half )

USB 2.0/USB 3.0 Conn.

On Left Side

Audio Codec

Realtek ALC269

P.15

D

Audio board

Title

Title

Title

Chief River-Block Diagram

Chief River-Block Diagram

Chief River-Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

Date: Sheet

P.45

P.36

IO board

P.46

Compal Electronics, Inc.

LA-7391P

P.48

P.11, 12

Reserved USB2.0

/ USB 3.0

Port3

Audio board

light peak board

IO board

Int. Speaker

Audio Jack x2

( HeadPhone, MIC)

Digital MIC

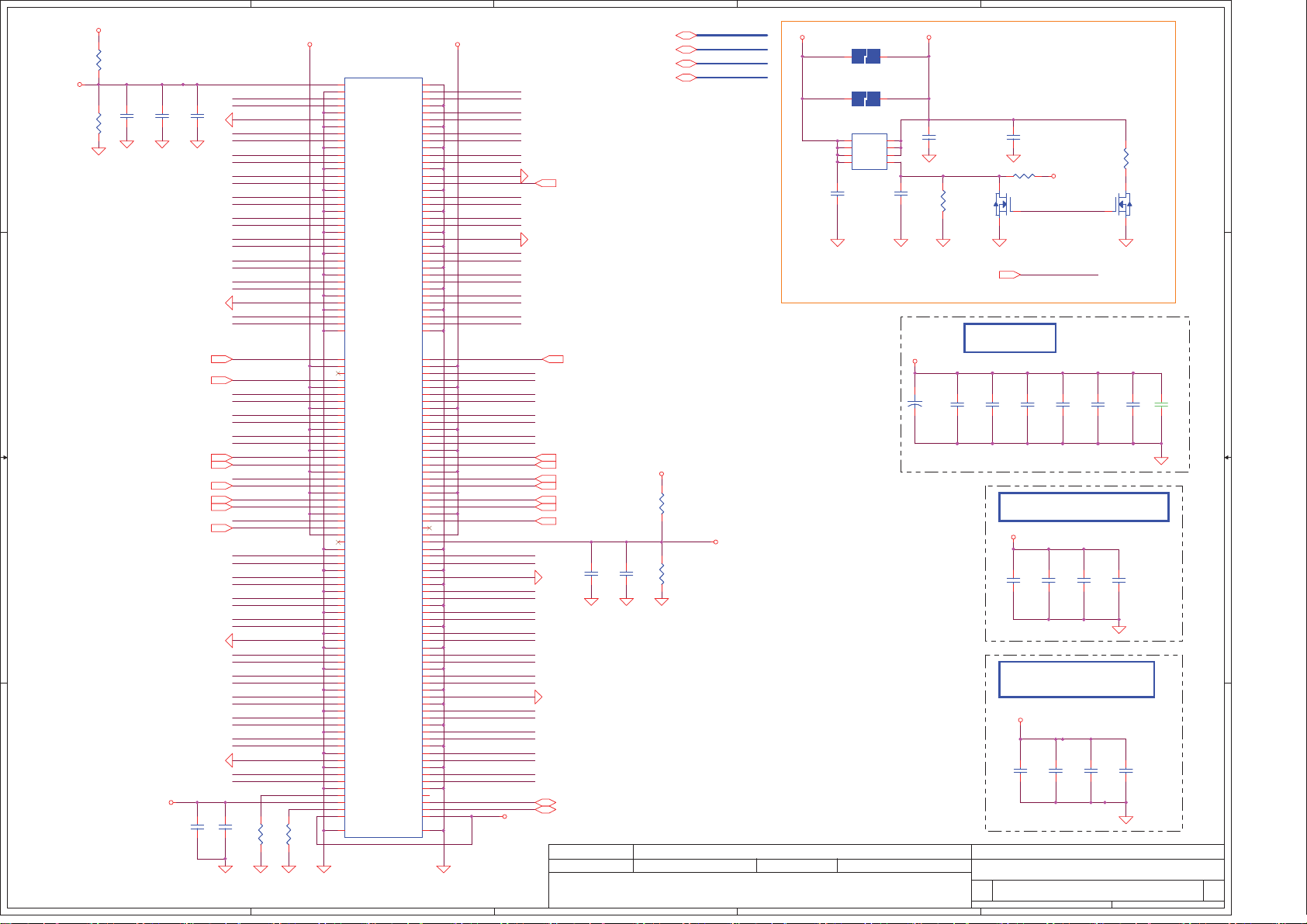

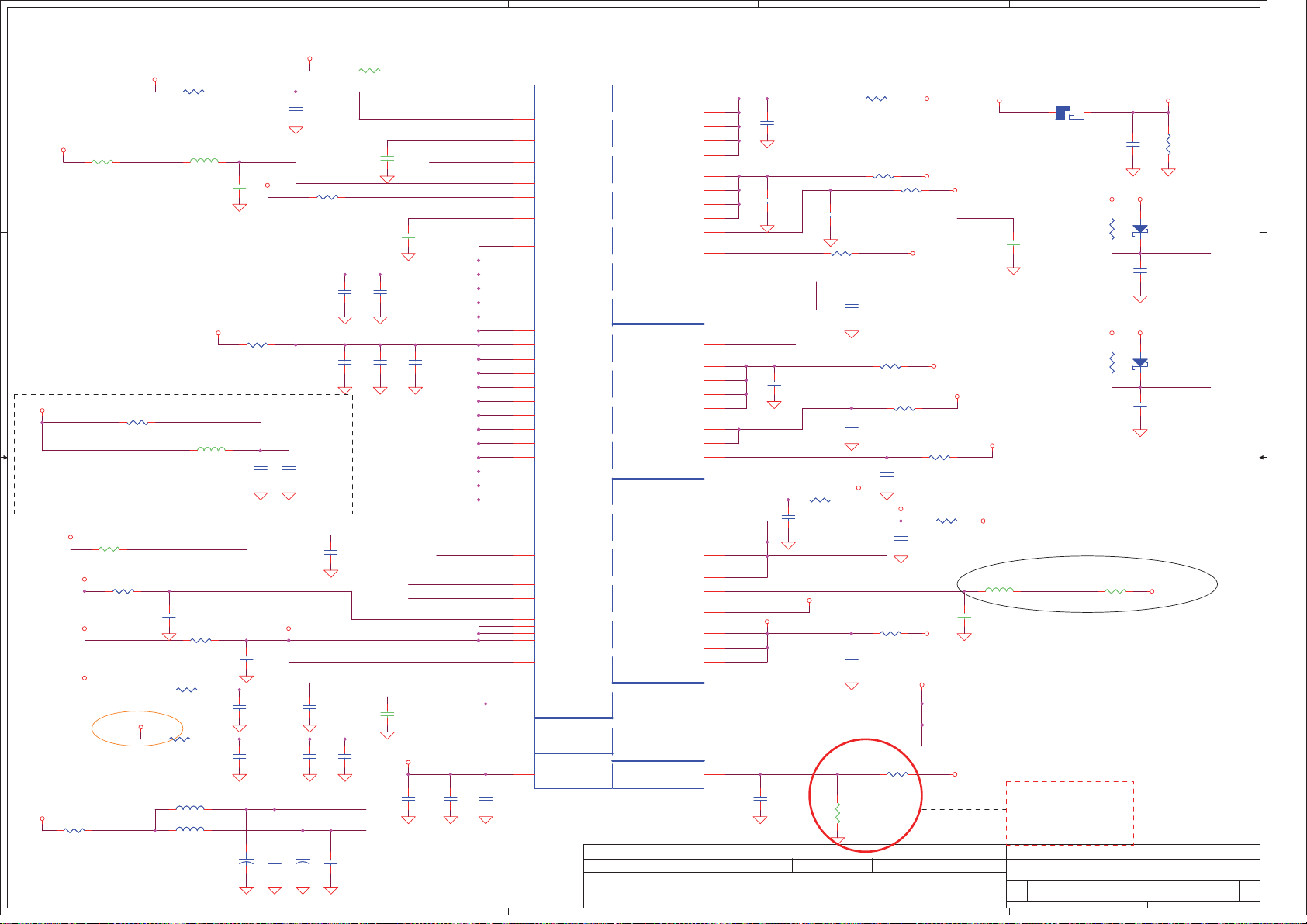

Page 3

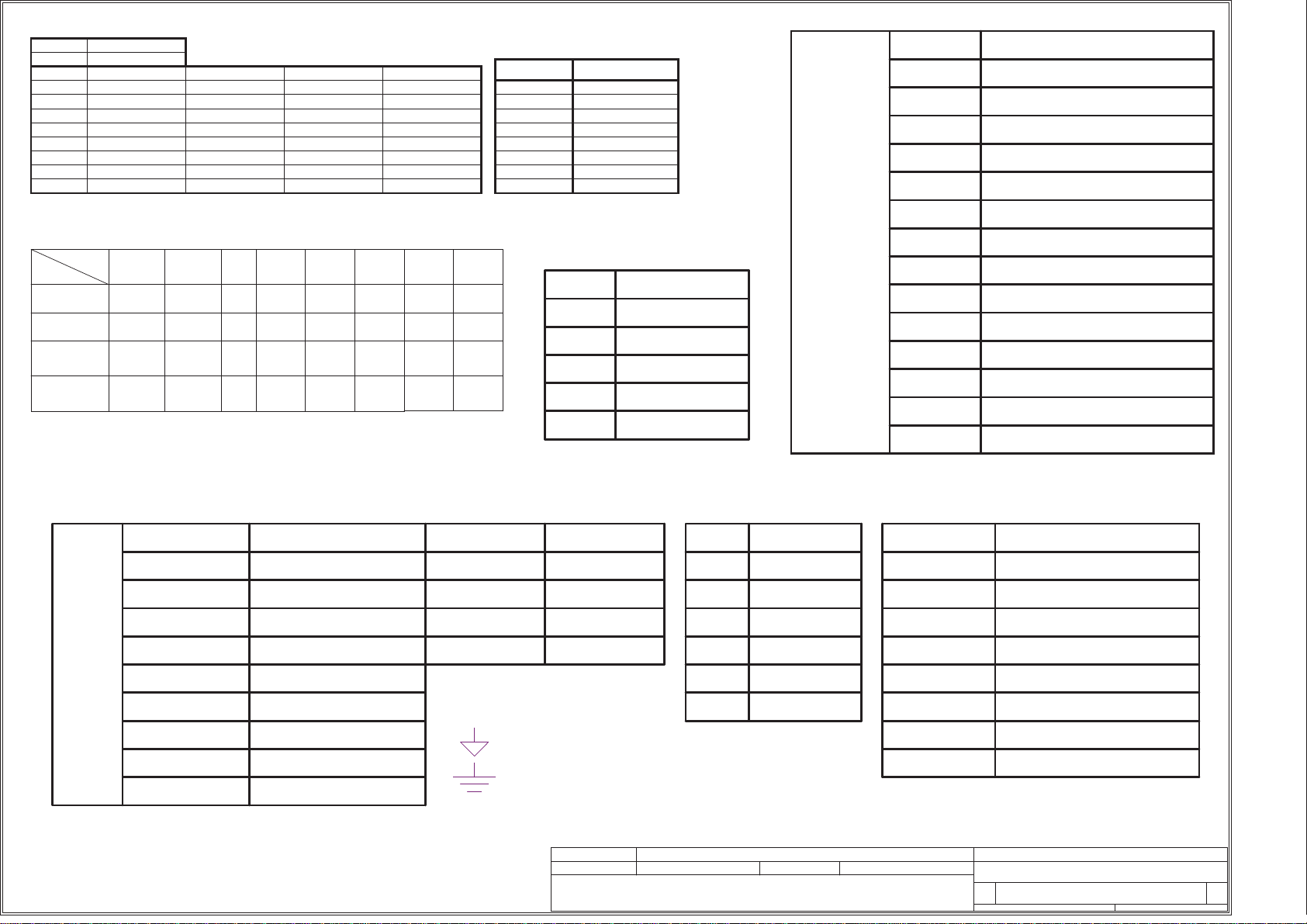

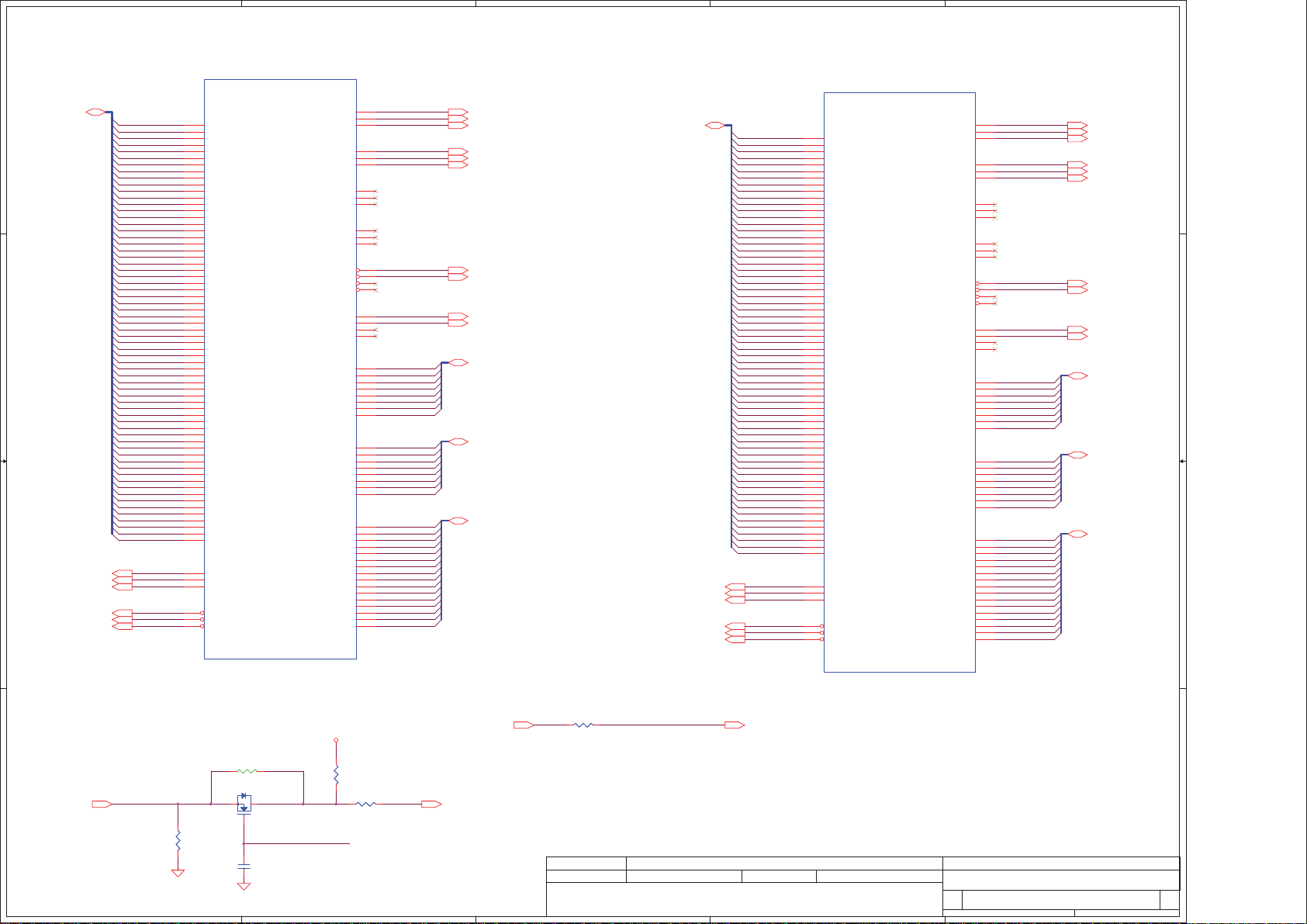

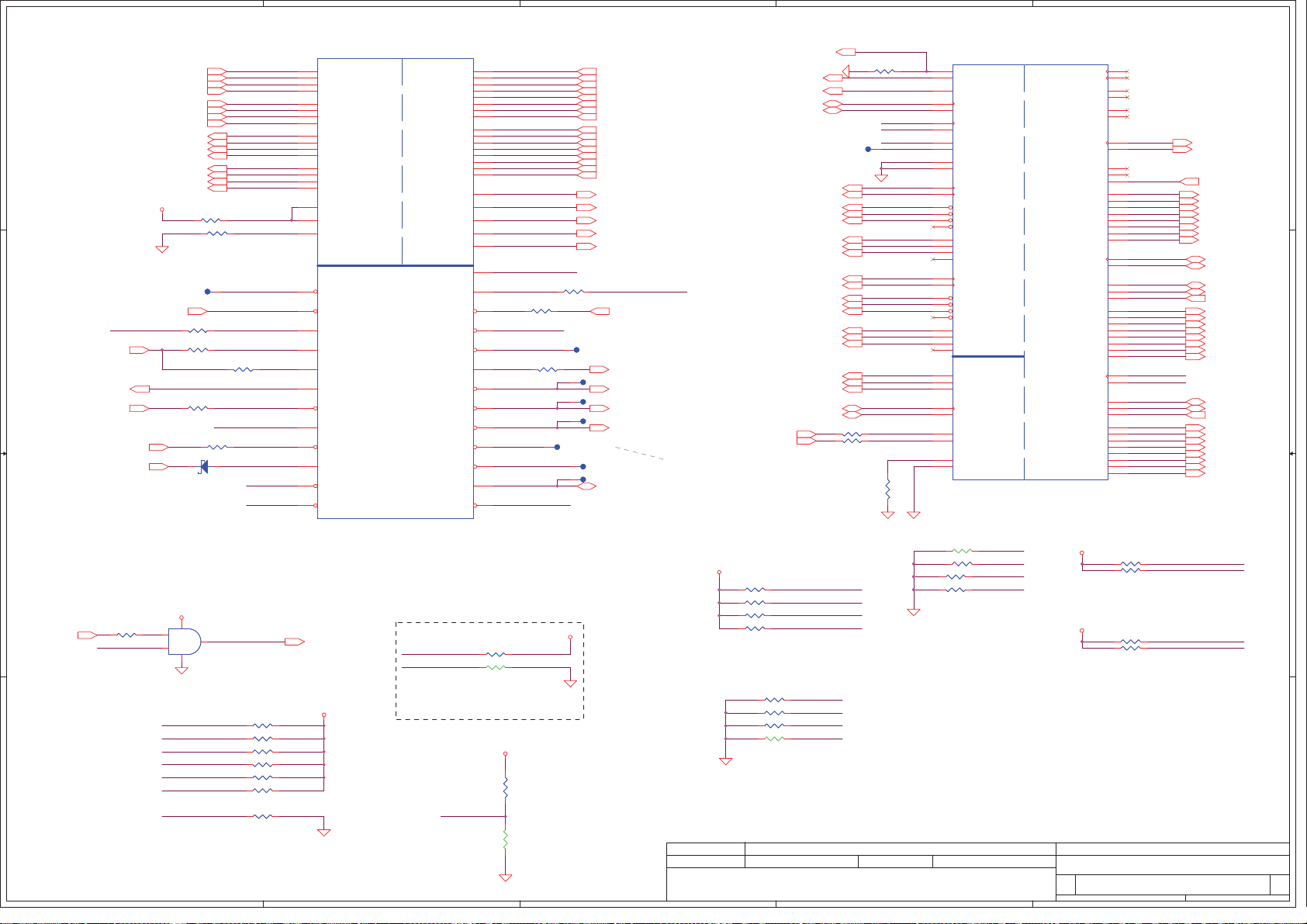

Board ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 NC

100K +/- 5%Ra

Rb V min

00 V

8.2K +/- 5% 0.168V 0.250 V 0.362 V

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

AD_BID

0.436 V

0.712 V

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

V typ

AD_BID

0 V 0 V

0.503 V

0.819 V

1.185 V 1.264 V

2.200 V

3.300 V

V

AD_BID

0.538 V

0.875 V

2.341 V

3.300 V

max

BOARD ID Table

Board ID

0

1

2

3

4

5

6

7

PCB Revision

0.1

A

USB PORT#

0

1

2

3

4

USB2/3 (Ext Right Side Up)

ESATA ( Ext Right Side Up)

USB2/3 (Ext Left Side Down)

USB2/3 (Ext FPC board)

JMINI1 (WLAN)

DESTINATION

Bluetooth

5

SMBUS Control Table

SOURCE

EC_SMB_CK1

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

PCH_SMBCLK

PCH_SMBDATA PCH

PCH_SMLCLK

PCH_SMLDATA

KB930

KB930

PCH

MIINI1 BATT SODIMM

X

X

VV

MINI2

V

XX

X

XX

EXPRESS

CARD

X

XX

X

V

XX

X

V

X

DGPU

Internal

Thermal

sensor

JXDP1

JXDP2

XX

V

X

V

X

V

X

CLKOUT

PCI0

PCI1

PCI2

PCI3

DESTINATION

PCH_LOOPBACK

EC

Debug Port

LPC Debug Port

PCH

6

7

8

9

10

11

12

PCI4

1 1

UMA: UMA@/XDP@/UO@

None

13

JMINI2 (WWAN)

None

None

CAMERA

JUSB3 ( Ext Right Side Down)

EXPRESS CARD

JUSB4 ( Ext Right Side Down)

None

None

OPTIMUS: XDP@/D@/UO@

DISCRETE:XDP@D@/DIS@

CLK

CLKOUT_PCIE0

CLKOUT_PCIE1

CLKOUT_PCIE2

CLKOUT_PCIE3

CLKOUT_PCIE4

DESTINATIONDIFFERENTIAL

10/100/1G LAN

EXPRESS CARD

CARD READER

Light Peak

FLEX CLOCKS DESTINATION

CLKOUTFLEX0

CLKOUTFLEX1

CLKOUTFLEX2

CLKOUTFLEX3

None

CLK_14MMINI CARD-1 WLAN

27M_CLK

27M_SSC

SATA

SATA0

SATA1

SATA2

SATA3

SATA4

DESTINATION

HDD

m-SATA

ODD

None

ESATA

PCI EXPRESS

Lane 1

Lane 2

Lane 3

Lane 4

Lane 5

DESTINATION

10/100/1G LAN

MINI CARD-1 WLAN

EXPRESS CARD

CARD READER

Light Peak

CLKOUT_PCIE5

CLKOUT_PCIE7

CLKOUT_PEG_B

None

NoneCLKOUT_PCIE6

None

None

6\PERO1RWH

PHDQV'LJLWDO*URXQG

PHDQV$QDORJ*URXQG

SATA5

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEER I NG DRAWING IS THE PROPR IETARY PROPERTY OF COMPAL ELECT R ONICS, INC. AND C ONTAINS CONFIDENT IAL

THIS SHEET OF ENGINEER I NG DRAWING IS THE PROPR IETARY PROPERTY OF COMPAL ELECT R ONICS, INC. AND C ONTAINS CONFIDENT IAL

THIS SHEET OF ENGINEER I NG DRAWING IS THE PROPR IETARY PROPERTY OF COMPAL ELECT R ONICS, INC. AND C ONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, I NC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, I NC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, I NC.

A

2009/12/01 2011/12/31

2009/12/01 2011/12/31

2009/12/01 2011/12/31

None

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Lane 6

Lane 7

Lane 8

Light Peak

Light Peak

Light Peak

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Notes List

Notes List

Notes List

LA-7391P

LA-7391P

LA-7391P

of

of

of

364Thursday, April 07, 2011

364Thursday, April 07, 2011

364Thursday, April 07, 2011

0.2

0.2

0.2

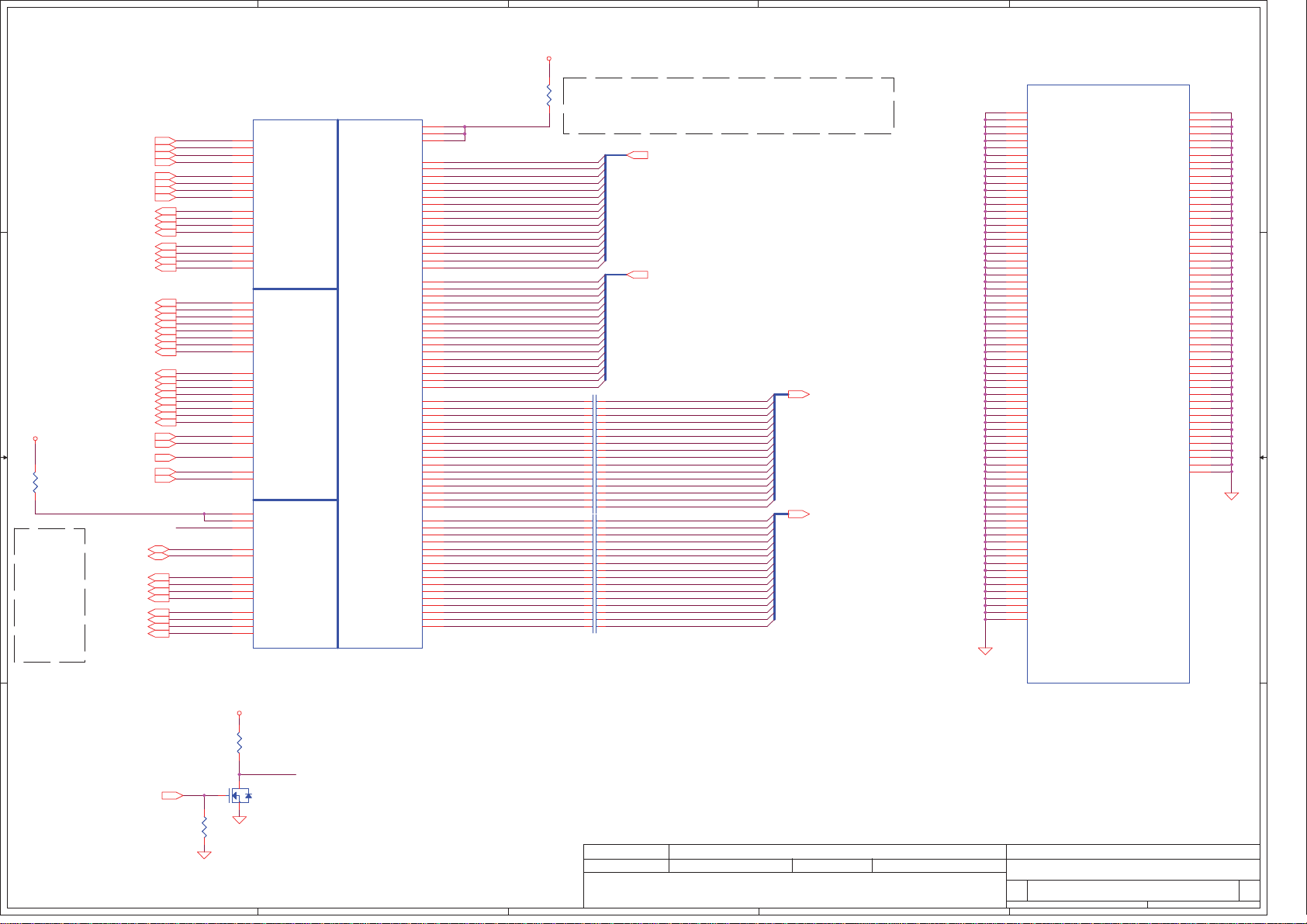

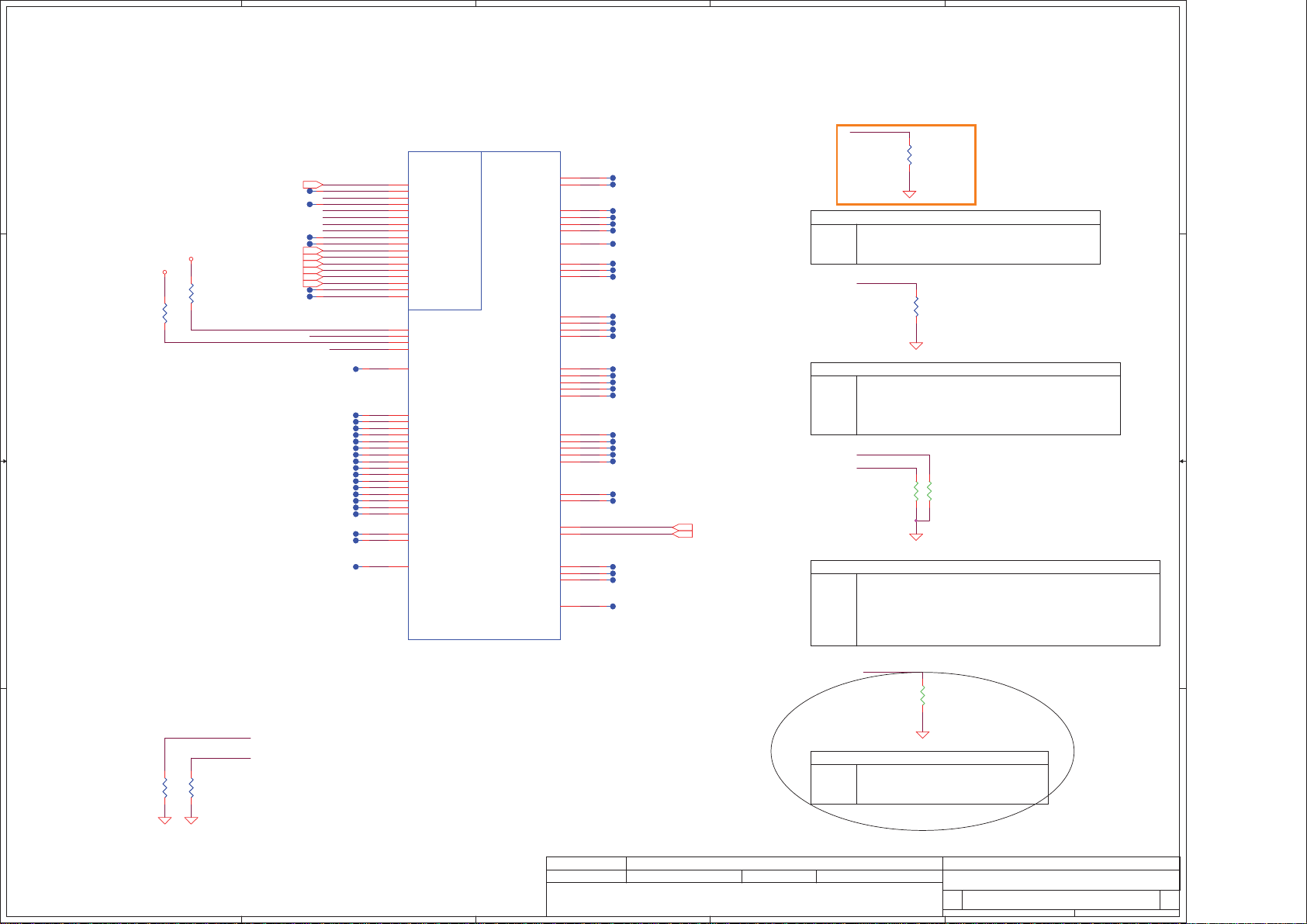

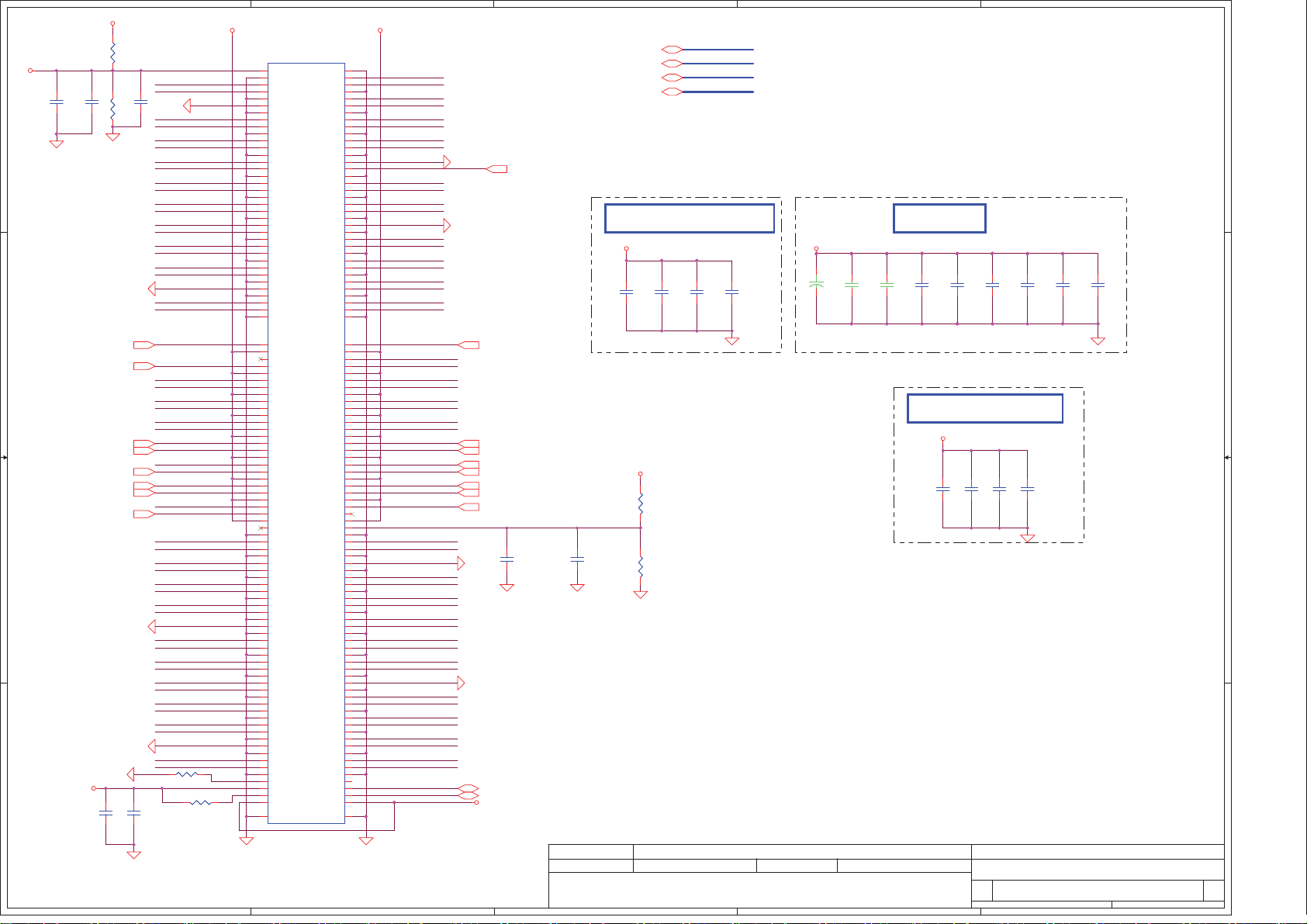

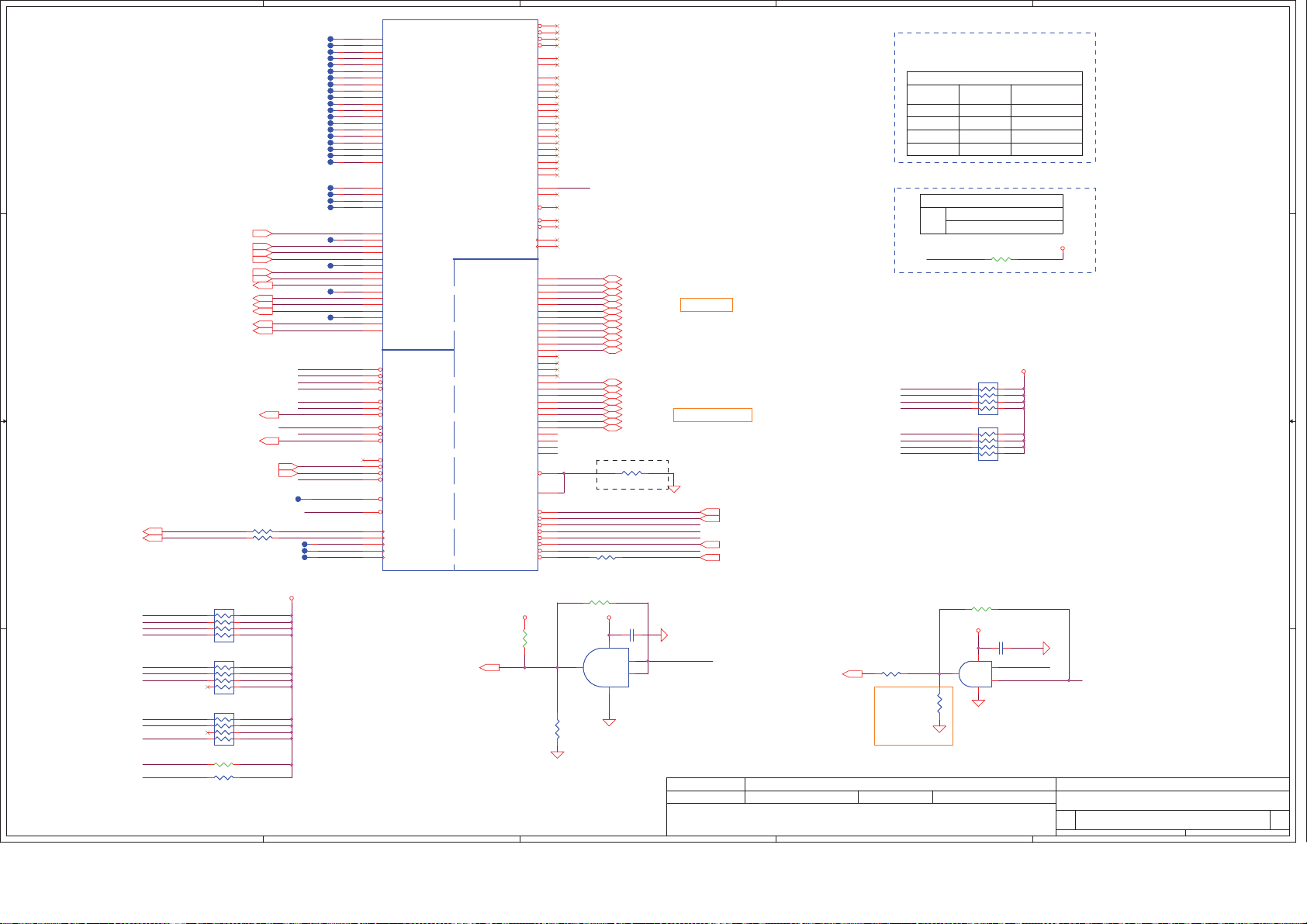

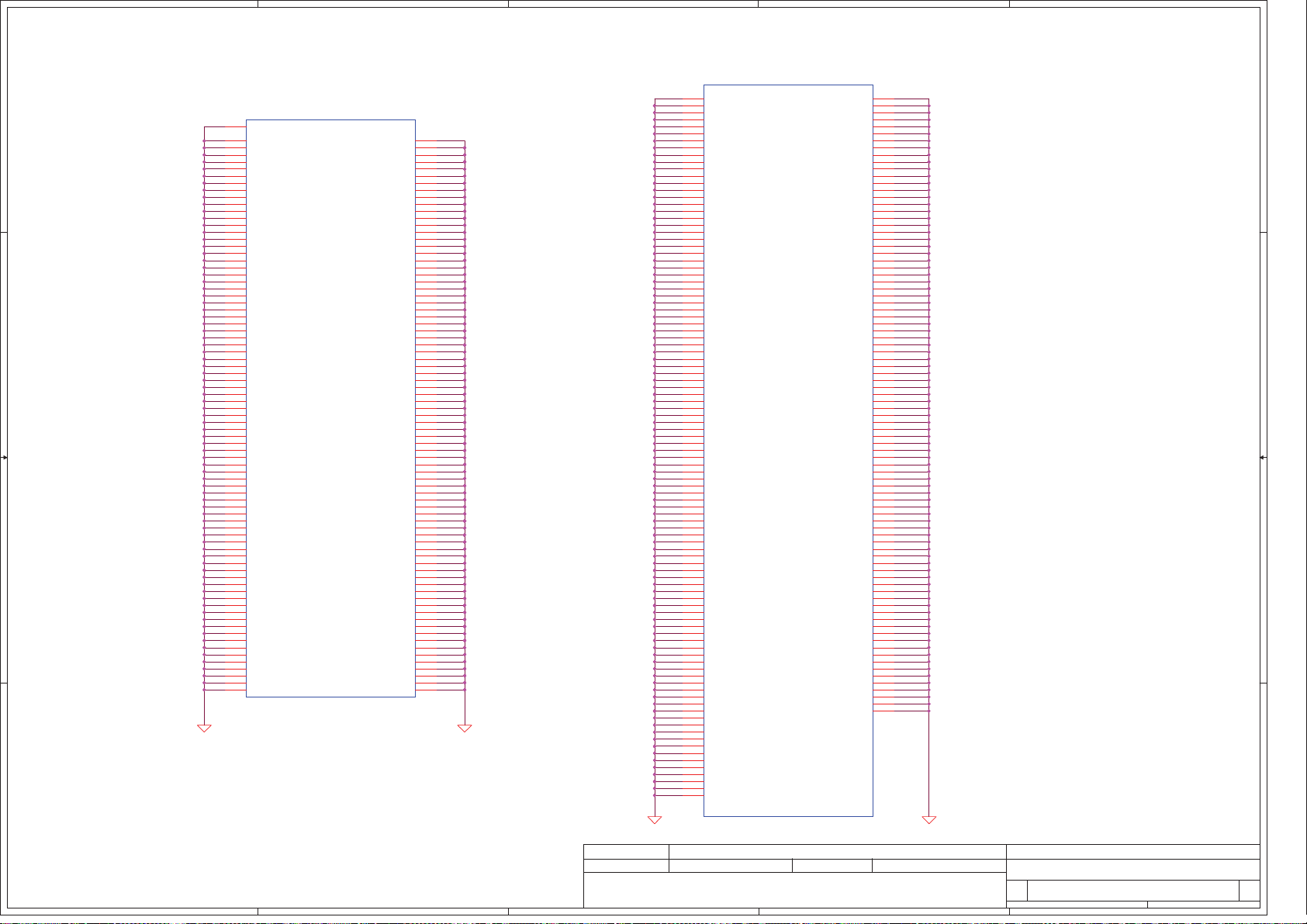

Page 4

5

JCPU1A

D D

DMI_CRX_PTX_N017

DMI_CRX_PTX_N117

DMI_CRX_PTX_N217

DMI_CRX_PTX_N317

DMI_CRX_PTX_P017

DMI_CRX_PTX_P117

DMI_CRX_PTX_P217

DMI_CRX_PTX_P317

DMI_CTX_PRX_N017

DMI_CTX_PRX_N117

DMI_CTX_PRX_N217

DMI_CTX_PRX_N317

DMI_CTX_PRX_P017

DMI_CTX_PRX_P117

DMI_CTX_PRX_P217

DMI_CTX_PRX_P317

FDI_CTX_PRX_N017

FDI_CTX_PRX_N117

FDI_CTX_PRX_N217

FDI_CTX_PRX_N317

FDI_CTX_PRX_N417

FDI_CTX_PRX_N517

RC2

RC2

FDI_CTX_PRX_N617

FDI_CTX_PRX_N717

FDI_CTX_PRX_P017

FDI_CTX_PRX_P117

FDI_CTX_PRX_P217

FDI_CTX_PRX_P317

FDI_CTX_PRX_P417

FDI_CTX_PRX_P517

FDI_CTX_PRX_P617

FDI_CTX_PRX_P717

FDI_FSYNC017

FDI_FSYNC117

FDI_INT17

FDI_LSYNC017

FDI_LSYNC117

EDP_AUXP41

EDP_AUXN41

EDP_TXP041

EDP_TXP141

EDP_TXP241

EDP_TXP341

EDP_TXN041

EDP_TXN141

EDP_TXN241

EDP_TXN341

C C

+V1.05S_VCCP

12

24.9_0402_1%

24.9_0402_1%

eDP_COMPIO

and ICOMPO

signals

should be

shorted

B B

near balls

and routed

with

typical

impedance

<25 mohms

FDI_CTX_PRX_N0

FDI_CTX_PRX_N1

FDI_CTX_PRX_N2

FDI_CTX_PRX_N3

FDI_CTX_PRX_N4

FDI_CTX_PRX_N5

FDI_CTX_PRX_N6

FDI_CTX_PRX_N7

FDI_CTX_PRX_P0

FDI_CTX_PRX_P1

FDI_CTX_PRX_P2

FDI_CTX_PRX_P3

FDI_CTX_PRX_P4

FDI_CTX_PRX_P5

FDI_CTX_PRX_P6

FDI_CTX_PRX_P7

FDI_FSYNC0

FDI_FSYNC1

FDI_INT

FDI_LSYNC0

FDI_LSYNC1

EDP_COMP

EDP_HPD#

JCPU1A

B27

DMI_RX#[0]

B25

DMI_RX#[1]

A25

DMI_RX#[2]

B24

DMI_RX#[3]

B28

DMI_RX[0]

B26

DMI_RX[1]

A24

DMI_RX[2]

B23

DMI_RX[3]

G21

DMI_TX#[0]

E22

DMI_TX#[1]

F21

DMI_TX#[2]

D21

DMI_TX#[3]

G22

DMI_TX[0]

D22

DMI_TX[1]

F20

DMI_TX[2]

C21

DMI_TX[3]

A21

FDI0_TX#[0]

H19

FDI0_TX#[1]

E19

FDI0_TX#[2]

F18

FDI0_TX#[3]

B21

FDI1_TX#[0]

C20

FDI1_TX#[1]

D18

FDI1_TX#[2]

E17

FDI1_TX#[3]

A22

FDI0_TX[0]

G19

FDI0_TX[1]

E20

FDI0_TX[2]

G18

FDI0_TX[3]

B20

FDI1_TX[0]

C19

FDI1_TX[1]

D19

FDI1_TX[2]

F17

FDI1_TX[3]

J18

FDI0_FSYNC

J17

FDI1_FSYNC

H20

FDI_INT

J19

FDI0_LSYNC

H17

FDI1_LSYNC

A18

eDP_COMPIO

A17

eDP_ICOMPO

B16

eDP_HPD#

C15

eDP_AUX

D15

eDP_AUX#

C17

eDP_TX[0]

F16

eDP_TX[1]

C16

eDP_TX[2]

G15

eDP_TX[3]

C18

eDP_TX#[0]

E16

eDP_TX#[1]

D16

eDP_TX#[2]

F15

eDP_TX#[3]

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

CONN@

CONN@

+V1.05S_VCCP

12

RC3

RC3

1K_0402_5%

1K_0402_5%

DMI

DMI

Intel(R) FDI

Intel(R) FDI

eDP

eDP

4

+V1.05S_VCCP

12

RC1

RC1

24.9_0402_1%

24.9_0402_1%

PEG_COMP

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

J22

J21

H22

PCIE_GTX_C_CRX_N15

K33

PCIE_GTX_C_CRX_N14

M35

PCIE_GTX_C_CRX_N13

L34

PCIE_GTX_C_CRX_N12

J35

PCIE_GTX_C_CRX_N11

J32

PCIE_GTX_C_CRX_N10

H34

PCIE_GTX_C_CRX_N9

H31

PCIE_GTX_C_CRX_N8

G33

PCIE_GTX_C_CRX_N7

G30

PCIE_GTX_C_CRX_N6

F35

PCIE_GTX_C_CRX_N5

E34

PCIE_GTX_C_CRX_N4

E32

PCIE_GTX_C_CRX_N3

D33

PCIE_GTX_C_CRX_N2

D31

PCIE_GTX_C_CRX_N1

B33

PCIE_GTX_C_CRX_N0

C32

PCIE_GTX_C_CRX_P15

J33

PCIE_GTX_C_CRX_P14

L35

PCIE_GTX_C_CRX_P13

K34

PCIE_GTX_C_CRX_P12

H35

PCIE_GTX_C_CRX_P11

H32

PCIE_GTX_C_CRX_P10

G34

PCIE_GTX_C_CRX_P9

G31

PCIE_GTX_C_CRX_P8

F33

PCIE_GTX_C_CRX_P7

F30

PCIE_GTX_C_CRX_P6

E35

PCIE_GTX_C_CRX_P5

E33

PCIE_GTX_C_CRX_P4

F32

PCIE_GTX_C_CRX_P3

D34

PCIE_GTX_C_CRX_P2

E31

PCIE_GTX_C_CRX_P1

C33

PCIE_GTX_C_CRX_P0

B32

PCIE_CTX_GRX_N15

M29

PCIE_CTX_GRX_N14

M32

PCIE_CTX_GRX_N13

M31

PCIE_CTX_GRX_N12

L32

PCIE_CTX_GRX_N11

L29

PCIE_CTX_GRX_N10

K31

PCIE_CTX_GRX_N9

K28

PCIE_CTX_GRX_N8

J30

PCIE_CTX_GRX_N7

J28

PCIE_CTX_GRX_N6

H29

PCIE_CTX_GRX_N5

G27

PCIE_CTX_GRX_N4

E29

PCIE_CTX_GRX_N3

F27

PCIE_CTX_GRX_N2

D28

PCIE_CTX_GRX_N1

F26

PCIE_CTX_GRX_N0

E25

PCIE_CTX_GRX_P15

M28

PCIE_CTX_GRX_P14

M33

PCIE_CTX_GRX_P13

M30

PCIE_CTX_GRX_P12

L31

PCIE_CTX_GRX_P11

L28

PCIE_CTX_GRX_P10

K30

PCIE_CTX_GRX_P9

K27

PCIE_CTX_GRX_P8

J29

PCIE_CTX_GRX_P7

J27

PCIE_CTX_GRX_P6

H28

PCIE_CTX_GRX_P5

G28

PCIE_CTX_GRX_P4

E28

PCIE_CTX_GRX_P3

F28

PCIE_CTX_GRX_P2

D27

PCIE_CTX_GRX_P1

E26

PCIE_CTX_GRX_P0

D25

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PCI EXPRESS* - GRAPHICS

PCI EXPRESS* - GRAPHICS

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_ICOMPI and RCOMPO signals should be shorted and routed

with - max length = 500 mils - typical impedance = 43 mohms

PEG_ICOMPO signals should be routed with - max length = 500 mils

- typical impedance = 14.5 mohms

CC1 0.22U_0402_10V6KD@CC1 0.22U_0402_10V6KD@

1 2

CC2 0.22U_0402_10V6KD@CC2 0.22U_0402_10V6KD@

1 2

CC3 0.22U_0402_10V6KD@CC3 0.22U_0402_10V6KD@

1 2

CC4 0.22U_0402_10V6KD@CC4 0.22U_0402_10V6KD@

1 2

CC5 0.22U_0402_10V6KD@CC5 0.22U_0402_10V6KD@

1 2

CC6 0.22U_0402_10V6KD@CC6 0.22U_0402_10V6KD@

1 2

CC7 0.22U_0402_10V6KD@CC7 0.22U_0402_10V6KD@

1 2

CC8 0.22U_0402_10V6KD@CC8 0.22U_0402_10V6KD@

1 2

CC9 0.22U_0402_10V6KD@CC9 0.22U_0402_10V6KD@

1 2

CC10 0.22U_0402_10V6KD@CC10 0.22U_0402_10V6KD@

1 2

CC11 0.22U_0402_10V6KD@CC11 0.22U_0402_10V6KD@

1 2

CC12 0.22U_0402_10V6KD@CC12 0.22U_0402_10V6KD@

1 2

CC13 0.22U_0402_10V6KD@CC13 0.22U_0402_10V6KD@

1 2

CC14 0.22U_0402_10V6KD@CC14 0.22U_0402_10V6KD@

1 2

CC15 0.22U_0402_10V6KD@CC15 0.22U_0402_10V6KD@

1 2

CC16 0.22U_0402_10V6KD@CC16 0.22U_0402_10V6KD@

1 2

CC17 0.22U_0402_10V6KD@CC17 0.22U_0402_10V6KD@

1 2

CC18 0.22U_0402_10V6KD@CC18 0.22U_0402_10V6KD@

1 2

CC19 0.22U_0402_10V6KD@CC19 0.22U_0402_10V6KD@

1 2

CC20 0.22U_0402_10V6KD@CC20 0.22U_0402_10V6KD@

1 2

CC21 0.22U_0402_10V6KD@CC21 0.22U_0402_10V6KD@

1 2

CC22 0.22U_0402_10V6KD@CC22 0.22U_0402_10V6KD@

1 2

CC23 0.22U_0402_10V6KD@CC23 0.22U_0402_10V6KD@

1 2

CC24 0.22U_0402_10V6KD@CC24 0.22U_0402_10V6KD@

1 2

CC25 0.22U_0402_10V6KD@CC25 0.22U_0402_10V6KD@

1 2

CC26 0.22U_0402_10V6KD@CC26 0.22U_0402_10V6KD@

1 2

CC27 0.22U_0402_10V6KD@CC27 0.22U_0402_10V6KD@

1 2

CC28 0.22U_0402_10V6KD@CC28 0.22U_0402_10V6KD@

1 2

CC29 0.22U_0402_10V6KD@CC29 0.22U_0402_10V6KD@

1 2

CC30 0.22U_0402_10V6KD@CC30 0.22U_0402_10V6KD@

1 2

CC31 0.22U_0402_10V6KD@CC31 0.22U_0402_10V6KD@

1 2

CC32 0.22U_0402_10V6KD@CC32 0.22U_0402_10V6KD@

1 2

3

PCIE_GTX_C_CRX_N[0..15] 24

PCIE_GTX_C_CRX_P[0..15] 24

PAY ATTENTION ON PCIE SWAP WHEN REVIEW

PCIE_CTX_C_GRX_N15

PCIE_CTX_C_GRX_N14

PCIE_CTX_C_GRX_N13

PCIE_CTX_C_GRX_N12

PCIE_CTX_C_GRX_N11

PCIE_CTX_C_GRX_N10

PCIE_CTX_C_GRX_N9

PCIE_CTX_C_GRX_N8

PCIE_CTX_C_GRX_N7

PCIE_CTX_C_GRX_N6

PCIE_CTX_C_GRX_N5

PCIE_CTX_C_GRX_N4

PCIE_CTX_C_GRX_N3

PCIE_CTX_C_GRX_N2

PCIE_CTX_C_GRX_N1

PCIE_CTX_C_GRX_N0

PCIE_CTX_C_GRX_P15

PCIE_CTX_C_GRX_P14

PCIE_CTX_C_GRX_P13

PCIE_CTX_C_GRX_P12

PCIE_CTX_C_GRX_P11

PCIE_CTX_C_GRX_P10

PCIE_CTX_C_GRX_P9

PCIE_CTX_C_GRX_P8

PCIE_CTX_C_GRX_P7

PCIE_CTX_C_GRX_P6

PCIE_CTX_C_GRX_P5

PCIE_CTX_C_GRX_P4

PCIE_CTX_C_GRX_P3

PCIE_CTX_C_GRX_P2

PCIE_CTX_C_GRX_P1

PCIE_CTX_C_GRX_P0

2

PCIE_CTX_C_GRX_N[0..15] 24

PCIE_CTX_C_GRX_P[0..15] 24

JCPU1I

JCPU1I

T35

VSS161

T34

VSS162

T33

VSS163

T32

VSS164

T31

VSS165

T30

VSS166

T29

VSS167

T28

VSS168

T27

VSS169

T26

VSS170

P9

VSS171

P8

VSS172

P6

VSS173

P5

VSS174

P3

VSS175

P2

VSS176

N35

VSS177

N34

VSS178

N33

VSS179

N32

VSS180

N31

VSS181

N30

VSS182

N29

VSS183

N28

VSS184

N27

VSS185

N26

VSS186

M34

VSS187

L33

VSS188

L30

VSS189

L27

VSS190

L9

VSS191

L8

VSS192

L6

VSS193

L5

VSS194

L4

VSS195

L3

VSS196

L2

VSS197

L1

VSS198

K35

VSS199

K32

VSS200

K29

VSS201

K26

VSS202

J34

VSS203

J31

VSS204

H33

VSS205

H30

VSS206

H27

VSS207

H24

VSS208

H21

VSS209

H18

VSS210

H15

VSS211

H13

VSS212

H10

VSS213

H9

VSS214

H8

VSS215

H7

VSS216

H6

VSS217

H5

VSS218

H4

VSS219

H3

VSS220

H2

VSS221

H1

VSS222

G35

VSS223

G32

VSS224

G29

VSS225

G26

VSS226

G23

VSS227

G20

VSS228

G17

VSS229

G11

VSS230

F34

VSS231

F31

VSS232

F29

VSS233

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

CONN@

CONN@

VSS

VSS

1

F22

VSS234

F19

VSS235

E30

VSS236

E27

VSS237

E24

VSS238

E21

VSS239

E18

VSS240

E15

VSS241

E13

VSS242

E10

VSS243

E9

VSS244

E8

VSS245

E7

VSS246

E6

VSS247

E5

VSS248

E4

VSS249

E3

VSS250

E2

VSS251

E1

VSS252

D35

VSS253

D32

VSS254

D29

VSS255

D26

VSS256

D20

VSS257

D17

VSS258

C34

VSS259

C31

VSS260

C28

VSS261

C27

VSS262

C25

VSS263

C23

VSS264

C10

VSS265

C1

VSS266

B22

VSS267

B19

VSS268

B17

VSS269

B15

VSS270

B13

VSS271

B11

VSS272

B9

VSS273

B8

VSS274

B7

VSS275

B5

VSS276

B3

VSS277

B2

VSS278

A35

VSS279

A32

VSS280

A29

VSS281

A26

VSS282

A23

VSS283

A20

VSS284

A3

VSS285

EDP_HPD#

13

D

D

QC1

QC1

A A

CPU_EDP_HPD41

5

2

G

G

12

RC4

RC4

100K_0402_5%

100K_0402_5%

2N7002_SOT23-3

2N7002_SOT23-3

S

S

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEER I N G D R AW ING IS THE PROPRIETARY PR OPER T Y OF C OMPAL ELECTRONICS, INC . AN D C ON T AINS CONFIDENTIAL

THIS SHEET OF ENGINEER I N G D R AW ING IS THE PROPRIETARY PR OPER T Y OF C OMPAL ELECTRONICS, INC . AN D C ON T AINS CONFIDENTIAL

THIS SHEET OF ENGINEER I N G D R AW ING IS THE PROPRIETARY PR OPER T Y OF C OMPAL ELECTRONICS, INC . AN D C ON T AINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2009/12/01 2011/12/31

2009/12/01 2011/12/31

2009/12/01 2011/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

PROCESSOR(1/6) DMI,FDI,PEG

PROCESSOR(1/6) DMI,FDI,PEG

PROCESSOR(1/6) DMI,FDI,PEG

LA-7391P

LA-7391P

LA-7391P

1

of

of

of

464Thursday, April 07, 2011

464Thursday, April 07, 2011

464Thursday, April 07, 2011

0.2

0.2

0.2

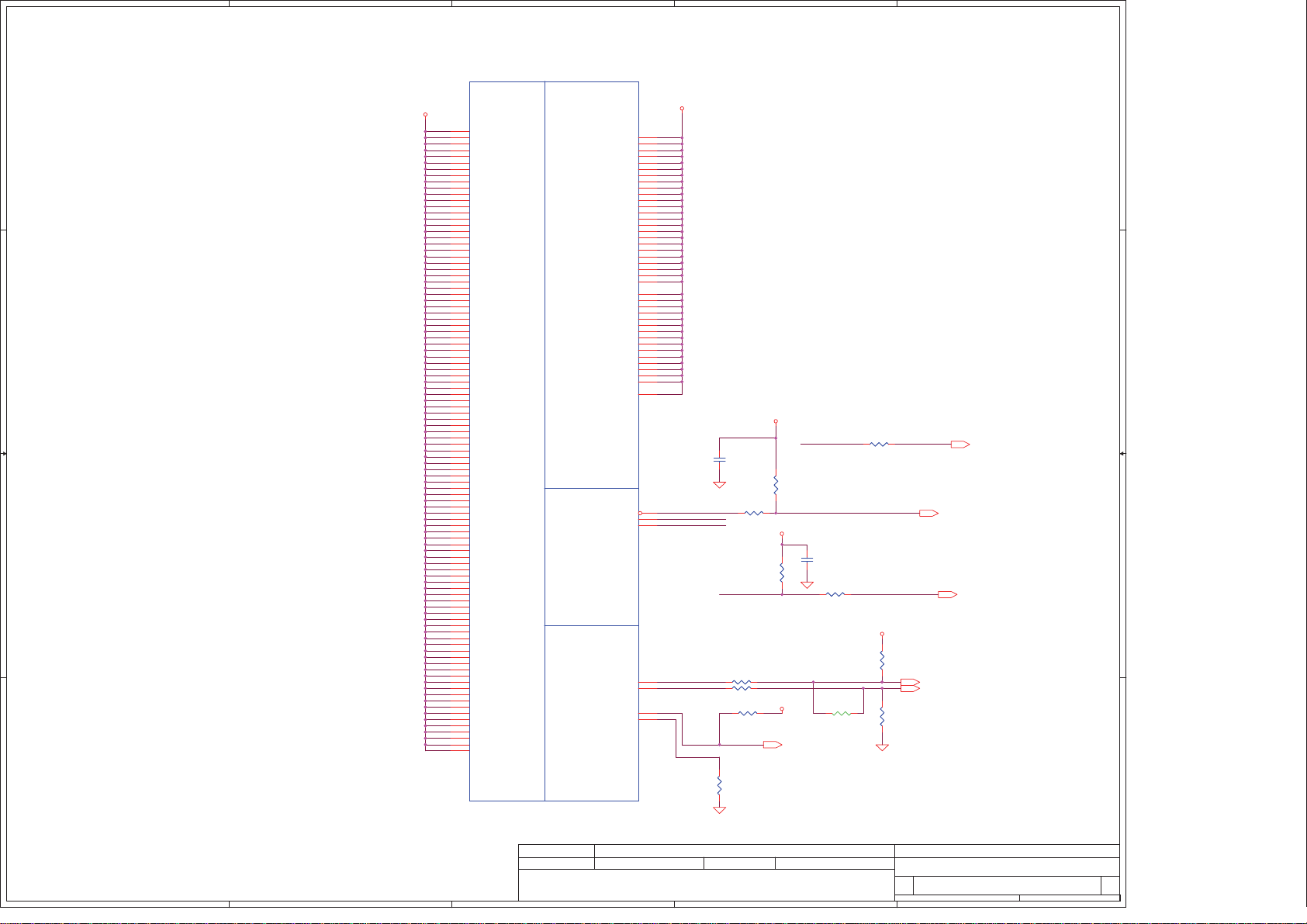

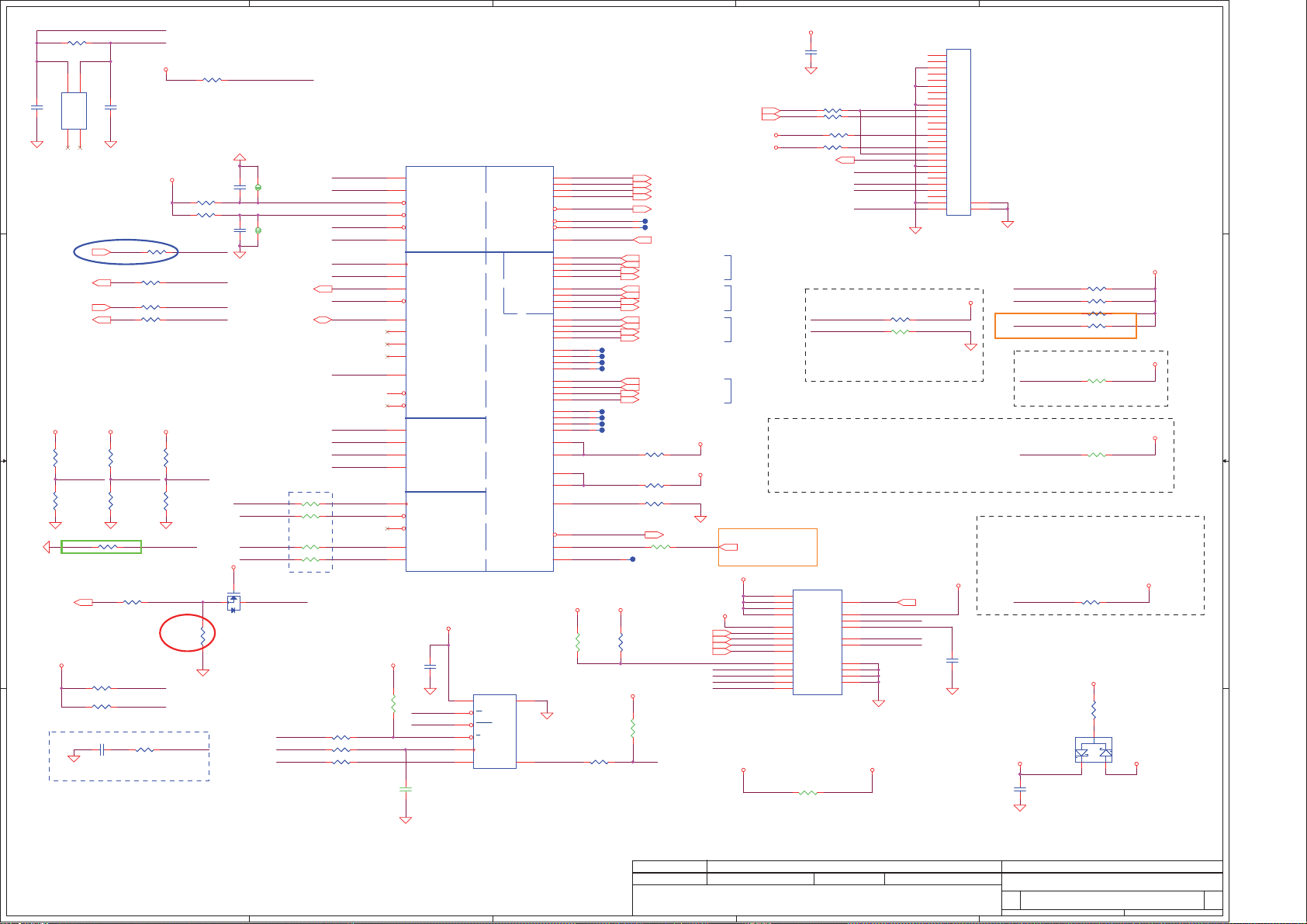

Page 5

5

XDP_PREQ#

XDP_PRDY#

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

CFG10_R

RC150_0402_5% @ RC150_0402_5% @

D D

C C

B B

A A

CFG107

CFG117

CFG07

VGATE17,49,64

The resistor

for HOOK2 should be

placed such that the

stub is very small

on CFG0 net

H_PECI19,49

H_PROCHOT#49,56

H_THERMTRIP#19

H_PM_SYNC17

H_CPUPWRGD19

VDDPWRGOOD

CFG0

H_SNB_IVB#19

T0501PAD~D @T0501PAD~D @

5

H_CPUPWRGD

1K_0402_5%~D

1K_0402_5%~D

RC42

RC42

1 2

56_0402_5%

56_0402_5%

RC50

RC50

1 2

0_0402_5%

0_0402_5%

RC54

RC54

1 2

0_0402_5%

0_0402_5%

RC58

RC58

1 2

130_0402_1%

130_0402_1%

12

CFG11_R

RC170_0402_5% @ RC170_0402_5% @

12

XDP_BPM#4

XDP_BPM#5

XDP_BPM#6

XDP_BPM#7

RC24

RC24

1K_0402_5%~D

1K_0402_5%~D

1 2

1 2

RC26 0_0402_5%~D

RC26 0_0402_5%~D

RC27

1 2

1 2

RC29 0_0402_5%~D

RC29 0_0402_5%~D

PCH_SMBDATA11,12,16,47,51

PCH_SMBCLK11,12,16,47,51

H_CATERR#

H_PROCHOT#_R

H_THERMTRIP#

H_PM_SYNC_R

H_CPUPWRGD_R

VDDPWRGOOD_R

BUF_CPU_RST#

XDP@

XDP@

XDP@

XDP@

XDP@RC27

XDP@

XDP@

XDP@

H_CPUPWRGD_XDP

CFD_PWRBTN#_XDP

XDP_HOOK2

SYS_PWROK_XDP

XDP_TCK

12

@

@

RC34

RC34

1K_0402_5%~D

1K_0402_5%~D

SYS_PWROK_XDP

C26

AN34

AL33

AN33

AL32

AN32

AM34

AP33

AR33

+V1.05S_VCCP +V1.05S_VCCP

T0502PAD~D @T0502PAD~D @

+V1.05S_VCCP+3VALW

XDP@

XDP@

JCPU1B

JCPU1B

PROC_SELECT#

SKTOCC#

CATERR#

PECI

PROCHOT#

THERMTRIP#

PM_SYNC

UNCOREPWRGOOD

V8

SM_DRAMPWROK

RESET#

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

CONN@

CONN@

4

JXDP1

CONN@JXDP1

CONN@

1

GND0

3

OBSFN_A0

5

OBSFN_A1

7

GND2

9

OBSDATA_A0

11

OBSDATA_A1

13

GND4

15

OBSDATA_A2

17

OBSDATA_A3

19

GND6

21

OBSFN_B0

23

OBSFN_B1

25

GND8

27

OBSDATA_B0

29

OBSDATA_B1

31

GND10

33

OBSDATA_B2

35

OBSDATA_B3

37

GND12

39

PWRGOOD/HOOK0

41

HOOK1

43

VCC_OBS_AB

45

HOOK2

47

HOOK3

49

GND14

51

SDA

53

SCL

55

TCK1

57

TCK0

59

GND16

SAMTE_BSH-030-01-L-D-A

SAMTE_BSH-030-01-L-D-A

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

XDP@

XDP@

CC34

CC34

2

OBSDATA_C0

OBSDATA_C1

OBSDATA_C2

OBSDATA_C3

OBSDATA_D0

OBSDATA_D1

OBSDATA_D2

OBSDATA_D3

ITPCLK/HOOK4

ITPCLK#/HOOK5

VCC_OBS_CD

RESET#/HOOK6

DBR#/HOOK7

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

CC35

CC35

2

Place near JXDP1

MISCTHERMALPWR MANAGEMENT

MISCTHERMALPWR MANAGEMENT

CLOCKS

CLOCKS

DDR3

MISC

DDR3

MISC

JTAG & BPM

JTAG & BPM

4

GND1

OBSFN_C0

OBSFN_C1

GND3

GND5

GND7

OBSFN_D0

OBSFN_D1

GND9

GND11

GND13

GND15

TD0

TRST#

TDI

TMS

GND17

BCLK

BCLK#

DPLL_REF_CLK

DPLL_REF_CLK#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PRDY#

PREQ#

TCK

TMS

TRST#

TDO

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

TDI

CLK_CPU_ITP

CLK_CPU_ITP#

XDP_RST#_R

XDP_DBRESET#

XDP_TDO

XDP_TRST#

XDP_TDI

XDP_TMS

CLK_CPU_DMI_R

A28

CLK_CPU_DMI#_R

A27

CLK_CPU_DPLL_R

A16

CLK_CPU_DPLL#_R

A15

H_DRAMRST#

R8

SM_RCOMP0

AK1

SM_RCOMP1

A5

SM_RCOMP2

A4

XDP_PRDY#

AP29

XDP_PREQ#

AP27

XDP_TCK

AR26

XDP_TMS

AR27

XDP_TRST#

AP30

XDP_TDI_R

AR28

XDP_TDO_R

AP26

XDP_DBRESET#_R

AL35

XDP_BPM#0_R

AT28

XDP_BPM#1_R

AR29

XDP_BPM#2_R

AR30

XDP_BPM#3_R

AT30

XDP_BPM#4_R

AP32

XDP_BPM#5_R

AR31

XDP_BPM#6_R

AT31

XDP_BPM#7_R

AR32

XDP_BPM#4

XDP_BPM#5

XDP_BPM#6

XDP_BPM#7

3

SYSTEM_PWROK17

RC11

RC11

200_0402_1%

200_0402_1%

PM_DRAM_PWRGD17

CLK_CPU_ITP 16

CLK_CPU_ITP# 16PBTN_OUT#15,17,49

PLT_RST#

XDP@

XDP@

12

RC28 1K_0402_5%

RC28 1K_0402_5%

RC39 0_0402_5%RC39 0_0402_5%

1 2

RC36 0_0402_5%RC36 0_0402_5%

1 2

RC37 0_0402_5%RC37 0_0402_5%

1 2

RC41 0_0402_5%RC41 0_0402_5%

1 2

H_DRAMRST# 6

Processor Pullups

H_PROCHOT#

RC51 0_0402_5%XDP@RC51 0_0402_5%XDP@

1 2

RC52 0_0402_5%XDP@RC52 0_0402_5%XDP@

1 2

RC57 0_0402_5%XDP@RC57 0_0402_5%XDP@

1 2

RC60 0_0402_5%XDP@RC60 0_0402_5%XDP@

1 2

RC62 0_0402_5%XDP@RC62 0_0402_5%XDP@

1 2

RC63 0_0402_5%XDP@RC63 0_0402_5%XDP@

1 2

RC64 0_0402_5%XDP@RC64 0_0402_5%XDP@

1 2

RC65 0_0402_5%XDP@RC65 0_0402_5%XDP@

1 2

RC66 0_0402_5%XDP@RC66 0_0402_5%XDP@

1 2

RC67 0_0402_5%XDP@RC67 0_0402_5%XDP@

1 2

RC68 0_0402_5%XDP@RC68 0_0402_5%XDP@

1 2

RC69 0_0402_5%@RC69 0_0402_5%@

1 2

RC70 0_0402_5%@RC70 0_0402_5%@

1 2

RC71 0_0402_5%@RC71 0_0402_5%@

1 2

RC72 0_0402_5%@RC72 0_0402_5%@

1 2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEER I N G D R AW ING IS THE PROPRIETARY PR OPER T Y OF C OMPAL ELECTRONICS, INC . AN D C ON T AINS CONFIDENTIAL

THIS SHEET OF ENGINEER I N G D R AW ING IS THE PROPRIETARY PR OPER T Y OF C OMPAL ELECTRONICS, INC . AN D C ON T AINS CONFIDENTIAL

THIS SHEET OF ENGINEER I N G D R AW ING IS THE PROPRIETARY PR OPER T Y OF C OMPAL ELECTRONICS, INC . AN D C ON T AINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

XDP_DBRESET#

3

CLK_CPU_DMI 16

CLK_CPU_DMI# 16

CLK_CPU_DPLL 16

CLK_CPU_DPLL# 16

+V1.05S_VCCP

1 2

XDP_TDI

XDP_TDO

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

XDP_BPM#4

XDP_BPM#5

XDP_BPM#6

XDP_BPM#7

2009/12/01 2011/12/31

2009/12/01 2011/12/31

2009/12/01 2011/12/31

RC4462_0402_5% RC4462_0402_5%

XDP_DBRESET#_R 15,17

CFG12 7

CFG13 7

CFG14 7

CFG15 7

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

+3V_PCH +3VS

12

12

12

RC12

RC12

@

@

0_0402_5%

0_0402_5%

1 2

RC21 0_0402_5%RC21 0_0402_5%

D_PWG

STUFF R0570

UNSTUFF R0569

RUN_ON_CPU1.5VS3#9,11,55

PLT_RST#18,42,47,49,51,52

XDP_DBRESET#_R

H_CPUPWRGD_R

DDR3 Compensation Signals

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

2

RC13

RC13

10K_0402_5%

10K_0402_5%

1 2

1 2

1 2

1 2

1 2

1

+3VALW

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

CC33

CC33

1

2

5

UC1

UC1

1

P

A

4

O

2

B

G

74AHC1G09GW TSSOP 5P

74AHC1G09GW TSSOP 5P

3

RUN_ON_CPU1.5VS3#

+3VS

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

CC36

CC36

2

1

5

UC2

UC2

P

BUFO_CPU_RST# BUF_CPU_RST#

4

NC

A2Y

G

SN74LVC1G07DCKR_SC70-5

SN74LVC1G07DCKR_SC70-5

3

+3VS

RC431K_0402_5% RC431K_0402_5%

RC4510K_0402_5% RC4510K_0402_5%

RC56140_0402_1% RC56140_0402_1%

RC5925.5_0402_1% RC5925.5_0402_1%

RC61200_0402_1% RC61200_0402_1%

Title

Title

Title

PROCESSOR(2/6) PM,XDP,CLK

PROCESSOR(2/6) PM,XDP,CLK

PROCESSOR(2/6) PM,XDP,CLK

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

LA-7391P

LA-7391P

LA-7391P

Date: Sheet

Date: Sheet

Date: Sheet

+1.5V_CPU_VDDQ

12

RC14

RC14

200_0402_1%

200_0402_1%

VDDPWRGOOD

@

@

RC25

RC25

39_0402_1%

39_0402_1%

1 2

13

D

D

@

@

QC2

QC2

2

G

G

2N7002_SOT23-3

2N7002_SOT23-3

S

S

+V1.05S_VCCP

12

RC38

RC38

75_0402_5%

75_0402_5%

RC35

RC35

1 2

43_0402_1%

43_0402_1%

12

PU/PD for JTAG signals

XDP_TMS

XDP_TDI_R

XDP_PREQ#

XDP_TDO_R

XDP_TCK

XDP_TRST#

1 2

1 2

1 2

1 2

1 2

1 2

Compal Electronics, Inc.

1

@

@

RC40

RC40

0_0402_5%

0_0402_5%

564Thursday, April 07, 2011

564Thursday, April 07, 2011

564Thursday, April 07, 2011

RC4651_0402_5% RC4651_0402_5%

RC4751_0402_5% RC4751_0402_5%

RC4851_0402_5% @ RC4851_0402_5% @

RC4951_0402_5% RC4951_0402_5%

RC5351_0402_5% RC5351_0402_5%

RC5551_0402_5% RC5551_0402_5%

+V1.05S_VCCP

of

of

of

0.2

0.2

0.2

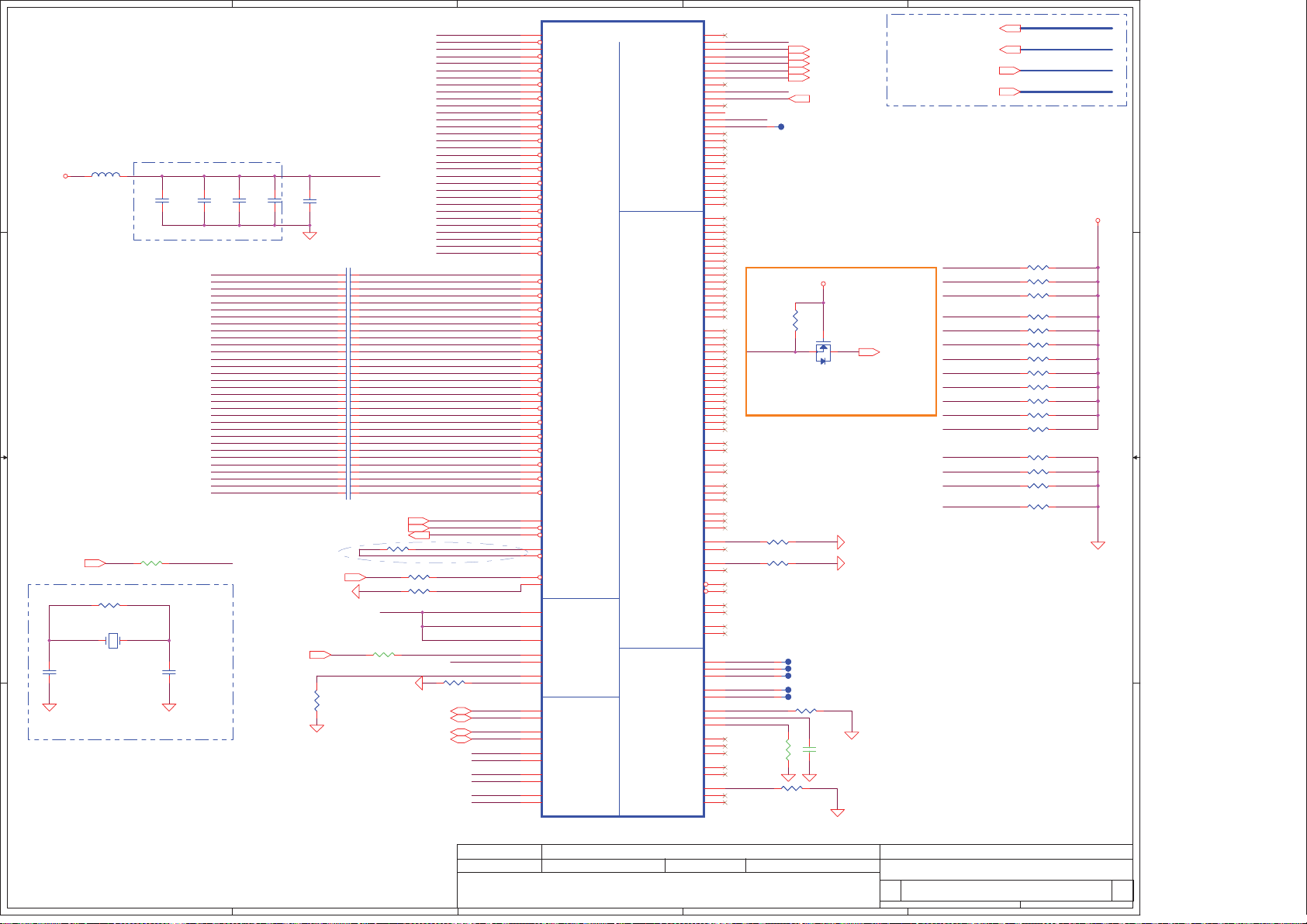

Page 6

5

JCPU1C

JCPU1C

DDR_A_D[0..63]11

D D

C C

B B

DDR_A_BS011

DDR_A_BS111

DDR_A_BS211

DDR_A_CAS#11

DDR_A_RAS#11

DDR_A_WE#11

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

C5

SA_DQ[0]

D5

SA_DQ[1]

D3

SA_DQ[2]

D2

SA_DQ[3]

D6

SA_DQ[4]

C6

SA_DQ[5]

C2

SA_DQ[6]

C3

SA_DQ[7]

F10

SA_DQ[8]

F8

SA_DQ[9]

G10

SA_DQ[10]

G9

SA_DQ[11]

F9

SA_DQ[12]

F7

SA_DQ[13]

G8

SA_DQ[14]

G7

SA_DQ[15]

K4

SA_DQ[16]

K5

SA_DQ[17]

K1

SA_DQ[18]

J1

SA_DQ[19]

J5

SA_DQ[20]

J4

SA_DQ[21]

J2

SA_DQ[22]

K2

SA_DQ[23]

M8

SA_DQ[24]

N10

SA_DQ[25]

N8

SA_DQ[26]

N7

SA_DQ[27]

M10

SA_DQ[28]

M9

SA_DQ[29]

N9

SA_DQ[30]

M7

SA_DQ[31]

AG6

SA_DQ[32]

AG5

SA_DQ[33]

AK6

SA_DQ[34]

AK5

SA_DQ[35]

AH5

SA_DQ[36]

AH6

SA_DQ[37]

AJ5

SA_DQ[38]

AJ6

SA_DQ[39]

AJ8

SA_DQ[40]

AK8

SA_DQ[41]

AJ9

SA_DQ[42]

AK9

SA_DQ[43]

AH8

SA_DQ[44]

AH9

SA_DQ[45]

AL9

SA_DQ[46]

AL8

SA_DQ[47]

AP11

SA_DQ[48]

AN11

SA_DQ[49]

AL12

SA_DQ[50]

AM12

SA_DQ[51]

AM11

SA_DQ[52]

AL11

SA_DQ[53]

AP12

SA_DQ[54]

AN12

SA_DQ[55]

AJ14

SA_DQ[56]

AH14

SA_DQ[57]

AL15

SA_DQ[58]

AK15

SA_DQ[59]

AL14

SA_DQ[60]

AK14

SA_DQ[61]

AJ15

SA_DQ[62]

AH15

SA_DQ[63]

AE10

SA_BS[0]

AF10

SA_BS[1]

V6

SA_BS[2]

AE8

SA_CAS#

AD9

SA_RAS#

AF9

SA_WE#

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

CONN@

CONN@

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_CLK[0]

SA_CLK#[0]

SA_CKE[0]

SA_CLK[1]

SA_CLK#[1]

SA_CKE[1]

RSVD_TP[1]

RSVD_TP[2]

RSVD_TP[3]

RSVD_TP[4]

RSVD_TP[5]

RSVD_TP[6]

SA_CS#[0]

SA_CS#[1]

RSVD_TP[7]

RSVD_TP[8]

SA_ODT[0]

SA_ODT[1]

RSVD_TP[9]

RSVD_TP[10]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

4

AB6

AA6

V9

AA5

AB5

V10

AB4

AA4

W9

AB3

AA3

W10

AK3

AL3

AG1

AH1

AH3

AG3

AG2

AH2

C4

G6

J3

M6

AL6

AM8

AR12

AM15

D4

F6

K3

N6

AL5

AM9

AR11

AM14

AD10

W1

W2

W7

V3

V2

W3

W6

V1

W5

AD8

V4

W4

AF8

V5

V7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDRA_CLK0 11

DDRA_CLK0# 11

DDRA_CKE0 11

DDRA_CLK1 11

DDRA_CLK1# 11

DDRA_CKE1 11

DDRA_SCS0# 11

DDRA_SCS1# 11

DDRA_ODT0 11

DDRA_ODT1 11

DDR_A_DQS#[0..7] 11

DDR_A_DQS[0..7] 11

DDR_A_MA[0..15] 11

3

DDR_B_D[0..63]12

DDR_B_BS012

DDR_B_BS112

DDR_B_BS212

DDR_B_CAS#12

DDR_B_RAS#12

DDR_B_WE#12

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

2

JCPU1D

JCPU1D

C9

SB_DQ[0]

A7

SB_DQ[1]

D10

SB_DQ[2]

C8

SB_DQ[3]

A9

SB_DQ[4]

A8

SB_DQ[5]

D9

SB_DQ[6]

D8

SB_DQ[7]

G4

SB_DQ[8]

F4

SB_DQ[9]

F1

SB_DQ[10]

G1

SB_DQ[11]

G5

SB_DQ[12]

F5

SB_DQ[13]

F2

SB_DQ[14]

G2

SB_DQ[15]

J7

SB_DQ[16]

J8

SB_DQ[17]

K10

SB_DQ[18]

K9

SB_DQ[19]

J9

SB_DQ[20]

J10

SB_DQ[21]

K8

SB_DQ[22]

K7

SB_DQ[23]

M5

SB_DQ[24]

N4

SB_DQ[25]

N2

SB_DQ[26]

N1

SB_DQ[27]

M4

SB_DQ[28]

N5

SB_DQ[29]

M2

SB_DQ[30]

M1

SB_DQ[31]

AM5

SB_DQ[32]

AM6

SB_DQ[33]

AR3

SB_DQ[34]

AP3

SB_DQ[35]

AN3

SB_DQ[36]

AN2

SB_DQ[37]

AN1

SB_DQ[38]

AP2

SB_DQ[39]

AP5

SB_DQ[40]

AN9

SB_DQ[41]

AT5

SB_DQ[42]

AT6

SB_DQ[43]

AP6

SB_DQ[44]

AN8

SB_DQ[45]

AR6

SB_DQ[46]

AR5

SB_DQ[47]

AR9

SB_DQ[48]

AJ11

SB_DQ[49]

AT8

SB_DQ[50]

AT9

SB_DQ[51]

AH11

SB_DQ[52]

AR8

SB_DQ[53]

AJ12

SB_DQ[54]

AH12

SB_DQ[55]

AT11

SB_DQ[56]

AN14

SB_DQ[57]

AR14

SB_DQ[58]

AT14

SB_DQ[59]

AT12

SB_DQ[60]

AN15

SB_DQ[61]

AR15

SB_DQ[62]

AT15

SB_DQ[63]

AA9

SB_BS[0]

AA7

SB_BS[1]

R6

SB_BS[2]

AA10

SB_CAS#

AB8

SB_RAS#

AB9

SB_WE#

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

CONN@

CONN@

1

AE2

SB_CLK[0]

AD2

SB_CLK#[0]

R9

SB_CKE[0]

AE1

SB_CLK[1]

AD1

SB_CLK#[1]

R10

SB_CKE[1]

AB2

RSVD_TP[11]

AA2

RSVD_TP[12]

T9

RSVD_TP[13]

AA1

RSVD_TP[14]

AB1

RSVD_TP[15]

T10

RSVD_TP[16]

AD3

SB_CS#[0]

AE3

SB_CS#[1]

AD6

RSVD_TP[17]

AE6

RSVD_TP[18]

AE4

SB_ODT[0]

AD4

SB_ODT[1]

AD5

RSVD_TP[19]

AE5

RSVD_TP[20]

DDR_B_DQS#0

D7

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

F3

K6

N3

AN5

AP9

AK12

AP15

C7

G3

J6

M3

AN6

AP8

AK11

AP14

AA8

T7

R7

T6

T2

T4

T3

R2

T5

R3

AB7

R1

T1

AB10

R5

R4

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

DDRB_CLK0 12

DDRB_CLK0# 12

DDRB_CKE0 12

DDRB_CLK1 12

DDRB_CLK1# 12

DDRB_CKE1 12

DDRB_SCS0# 12

DDRB_SCS1# 12

DDRB_ODT0 12

DDRB_ODT1 12

DDR_B_DQS#[0..7] 12

DDR_B_DQS[0..7] 12

DDR_B_MA[0..15] 12

+1.5V

@

@

1 2

RC75 0_0402_5%~D

RC75 0_0402_5%~D

QC3

QC3

BSS138_SOT23

BSS138_SOT23

D

S

D

S

H_DRAMRST#5

A A

H_DRAMRST#

RC78

RC78

4.99K_0402_1%~D

4.99K_0402_1%~D

5

12

13

G

G

2

DRAMRST_CNTRL

1

CC37

CC37

0.047U_0402_16V4Z~D

0.047U_0402_16V4Z~D

2

DDR3_DRAMRST#_R

12

RC76

RC76

1K_0402_5%~D

1K_0402_5%~D

1 2

RC77 1K_0402_5%RC77 1K_0402_5%

DG 0.5

4

DRAMRST_CNTRL_PCH16

SM_DRAMRST# 11,12

1 2

RC73 0_0402_5%~DRC73 0_0402_5%~D

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

3

DRAMRST_CNTRL

2009/12/01 2011/12/31

2009/12/01 2011/12/31

2009/12/01 2011/12/31

DRAMRST_CNTRL 9

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

Title

Title

Size Document Num b er Rev

Size Document Num b er Rev

Size Document Num b er Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

PROCESSOR(3/6) DDRIII

PROCESSOR(3/6) DDRIII

PROCESSOR(3/6) DDRIII

LA-7391P

LA-7391P

LA-7391P

1

664Thursday, April 07, 2011

664Thursday, April 07, 2011

664Thursday, April 07, 2011

of

of

of

0.2

0.2

0.2

Page 7

5

4

3

2

1

CFG Straps for Processor

D D

JCPU1E

JCPU1E

T0749 PAD~D@T0749 PAD~D@

T0750 PAD~D@T0750 PAD~D@

T0704 PAD~D@T0704 PAD~D@

T0705 PAD~D@T0705 PAD~D@

T0701 PAD~D@T0701 PAD~D@

T0702 PAD~D@T0702 PAD~D@

T0706 PAD~D@T0706 PAD~D@

T0707 PAD~D@T0707 PAD~D@

T0708 PAD~D@T0708 PAD~D@

T0709 PAD~D@T0709 PAD~D@

T0710 PAD~D@T0710 PAD~D@

T0711 PAD~D@T0711 PAD~D@

T0703 PAD~D@T0703 PAD~D@

T0712 PAD~D@T0712 PAD~D@

T0713 PAD~D@T0713 PAD~D@

T0714 PAD~D@T0714 PAD~D@

T0715 PAD~D@T0715 PAD~D@

T0716 PAD~D@T0716 PAD~D@

T0717 PAD~D@T0717 PAD~D@

T0719 PAD~D@T0719 PAD~D@

T0720 PAD~D@T0720 PAD~D@

T0721 PAD~D@T0721 PAD~D@

T0722 PAD~D@T0722 PAD~D@

T0723 PAD~D@T0723 PAD~D@

T0728 PAD~D@T0728 PAD~D@

T0730 PAD~D@T0730 PAD~D@

CLK_RES_ITP 16

CLK_RES_ITP# 16

T0744 PAD~D@T0744 PAD~D@

T0745 PAD~D@T0745 PAD~D@

T0746 PAD~D@T0746 PAD~D@

T0748 PAD~D@T0748 PAD~D@

PEG Static Lane Reversal - CFG2 is for the 16x

Display Port Presence Strap

PCIE Port Bifurcation Straps

CFG[6:5]

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD37

RSVD38

RSVD39

RSVD40

RSVD_NCTF1

RSVD_NCTF2

RSVD_NCTF3

RSVD_NCTF4

RSVD_NCTF5

RSVD_NCTF6

RSVD_NCTF7

RSVD_NCTF8

RSVD_NCTF9

RSVD51

RSVD52

BCLK_ITP

BCLK_ITP#

AH27

AH26

L7

AG7

AE7

AK2

W8

AT26

AM33

AJ27

T8

J16

H16

G16

AR35

AT34

AT33

AP35

AR34

B34

A33

A34

B35

C35

AJ32

AK32

AN35

AM35

AT2

AT1

AR1

B1

KEY

CFG

CFG

RESERVED

RESERVED

VCC_DIE_SENSE

VSS_DIE_SENSE

RSVD_NCTF10

RSVD_NCTF11

RSVD_NCTF12

RSVD_NCTF13

CFG05

T0751PAD~D @T0751PAD~D @

T0752PAD~D @T0752PAD~D @

T0753PAD~D @T0753PAD~D @

T0754PAD~D @T0754PAD~D @

+VCC_GFXCORE_ AXG

+VCC_CORE

12

RC80

RC80

49.9_0402_1%

49.9_0402_1%

12

RC81

RC81

49.9_0402_1%

49.9_0402_1%

C C

B B

VCC_AXG_VAL_SENSE

CFG105

CFG115

CFG125

CFG135

CFG145

CFG155

T0755PAD~D @T0755PAD~D @

T0756PAD~D @T0756PAD~D @

VCC_VAL_SENSE

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

VSS_AXG_VAL_SENSE

VSS_VAL_SENSE

T0718PAD~D @T0718PAD~D @

T0724PAD~D @T0724PAD~D @

T0725PAD~D @T0725PAD~D @

T0726PAD~D @T0726PAD~D @

T0727PAD~D @T0727PAD~D @

T0729PAD~D @T0729PAD~D @

T0731PAD~D @T0731PAD~D @

T0732PAD~D @T0732PAD~D @

T0733PAD~D @T0733PAD~D @

T0734PAD~D @T0734PAD~D @

T0735PAD~D @T0735PAD~D @

T0736PAD~D @T0736PAD~D @

T0737PAD~D @T0737PAD~D @

T0738PAD~D @T0738PAD~D @

T0739PAD~D @T0739PAD~D @

T0740PAD~D @T0740PAD~D @

T0741PAD~D @T0741PAD~D @

T0742PAD~D @T0742PAD~D @

T0743PAD~D @T0743PAD~D @

T0747PAD~D @T0747PAD~D @

AK28

CFG[0]

AK29

CFG[1]

AL26

CFG[2]

AL27

CFG[3]

AK26

CFG[4]

AL29

CFG[5]

AL30

CFG[6]

AM31

CFG[7]

AM32

CFG[8]

AM30

CFG[9]

AM28

CFG[10]

AM26

CFG[11]

AN28

CFG[12]

AN31

CFG[13]

AN26

CFG[14]

AM27

CFG[15]

AK31

CFG[16]

AN29

CFG[17]

AJ31

VAXG_VAL_SENSE

AH31

VSSAXG_VAL_SENSE

AJ33

VCC_VAL_SENSE

AH33

VSS_VAL_SENSE

AJ26

RSVD5

F25

RSVD8

F24

RSVD9

F23

RSVD10

D24

RSVD11

G25

RSVD12

G24

RSVD13

E23

RSVD14

D23

RSVD15

C30

RSVD16

A31

RSVD17

B30

RSVD18

B29

RSVD19

D30

RSVD20

B31

RSVD21

A30

RSVD22

C29

RSVD23

J20

RSVD24

B18

RSVD25

J15

RSVD27

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

CONN@

CONN@

CFG2

12

RC79

RC79

1K_0402_1%~D

1K_0402_1%~D

1:(Default) Normal Operation; Lane #

CFG2

definition matches socket pin map definition

0:Lane Reversed

CFG4

12

RC82

RC82

1K_0402_1%~D

1K_0402_1%~D

1 : Disabled; No Physical Display Port

CFG4

attached to Embedded Display Port

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

CFG6

CFG5

1K_0402_1%~D

1K_0402_1%~D

RC83

@RC83

@

12

12

RC84

@RC84

@

1K_0402_1%~D

1K_0402_1%~D

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2

disabled

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

CFG7

12

RC85

@RC85

@

1K_0402_1%~D

1K_0402_1%~D

No discribe in CPU EDS 1.5

Need PWR add new circuit on 1.05V(refer CRB)

VSS_AXG_VAL_SENSE

VSS_VAL_SENSE

12

RC86

RC86

49.9_0402_1%

A A

49.9_0402_1%

12

RC87

RC87

49.9_0402_1%

49.9_0402_1%

PEG DEFER TRAINING

1: (Default) PEG Train immediately

CFG7

following RESETB de assertion

0: PEG Wait for BIOS for training

INTEL 12/28 recommand

to add RC120, RC121, RC122, RC123

Please place as close as JCPU1

5

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOU T PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

3

2009/12/01 2011/12/31

2009/12/01 2011/12/31

2009/12/01 2011/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

Size Document Num b er Rev

Size Document Num b er Rev

Size Document Num b er Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

PROCESSOR(4/6) RSVD,CFG

PROCESSOR(4/6) RSVD,CFG

PROCESSOR(4/6) RSVD,CFG

LA-7391P

LA-7391P

LA-7391P

764Thursday, April 07, 2011

764Thursday, April 07, 2011

764Thursday, April 07, 2011

1

0.2

0.2

0.2

of

of

of

Page 8

5

D D

C C

B B

A A

4

JCPU1F

JCPU1F

+VCC_CORE

97A

AG35

VCC1

AG34

VCC2

AG33

VCC3

AG32

VCC4

AG31

VCC5

AG30

VCC6

AG29

VCC7

AG28

VCC8

AG27

VCC9

AG26

VCC10

AF35

VCC11

AF34

VCC12

AF33

VCC13

AF32

VCC14

AF31

VCC15

AF30

VCC16

AF29

VCC17

AF28

VCC18

AF27

VCC19

AF26

VCC20

AD35

VCC21

AD34

VCC22

AD33

VCC23

AD32

VCC24

AD31

VCC25

AD30

VCC26

AD29

VCC27

AD28

VCC28

AD27

VCC29

AD26

VCC30

AC35

VCC31

AC34

VCC32

AC33

VCC33

AC32

VCC34

AC31

VCC35

AC30

VCC36

AC29

VCC37

AC28

VCC38

AC27

VCC39

AC26

VCC40

AA35

VCC41

AA34

VCC42

AA33

VCC43

AA32

VCC44

AA31

VCC45

AA30

VCC46

AA29

VCC47

AA28

VCC48

AA27

VCC49

AA26

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

CONN@

CONN@

3

POWER

POWER

PEG AND DDR

PEG AND DDR

CORE SUPPLY

CORE SUPPLY

VSS_SENSE_VCCIO

SENSE LINES SVID

SENSE LINES SVID

VCCIO1

VCCIO2

VCCIO3

VCCIO4

VCCIO5

VCCIO6

VCCIO7

VCCIO8

VCCIO9

VCCIO10

VCCIO11

VCCIO12

VCCIO13

VCCIO14

VCCIO15

VCCIO16

VCCIO17

VCCIO18

VCCIO19

VCCIO20

VCCIO21

VCCIO22

VCCIO23

VCCIO24

VCCIO25

VCCIO26

VCCIO27

VCCIO28

VCCIO29

VCCIO30

VCCIO31

VCCIO32

VCCIO33

VCCIO34

VCCIO35

VCCIO36

VCCIO37

VCCIO38

VCCIO39

VCCIO40

VIDALERT#

VIDSCLK

VIDSOUT

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

+V1.05S_VCCP

8.5A

AH13

AH10

AG10

AC10

Y10

U10

P10

L10

J14

J13

J12

J11

H14

H12

H11

G14

G13

G12

F14

F13

F12

F11

E14

E12

E11

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

J23

H_CPU_SVIDALRT#

AJ29

H_CPU_SVIDCLK

AJ30

H_CPU_SVIDDAT

AJ28

Place the PU

resistors close to CPU

VCCSENSE_R

AJ35

VSSSENSE_R

AJ34

B10

A10

2

+V1.05S_VCCP

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

CC49

CC49

1 2

43_0402_1%

43_0402_1%

RC96

RC96

10_0402_1%

10_0402_1%

RC98

RC98

10_0402_1%

10_0402_1%

+V1.05S_VCCP

RC91

RC91

+V1.05S_VCCP

12

12

RC89

RC89

75_0402_5%

75_0402_5%

12

VCCIO_SENSE 60

2

RC90

RC90

130_0402_1%~D

130_0402_1%~D

H_CPU_SVIDDAT

1 2

RC94 0_0402_5% ~DRC94 0_0402_5% ~D

1 2

RC95 0_0402_5% ~DRC95 0_0402_5% ~D

12

H_CPU_SVIDCLK

Place the PU

resistors close to CPU

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

2

RC92 0_0402_5%~DRC92 0_0402_5%~D

CC50

CC50

1 2

RC121

RC121

1 2

100_0402_1%~D

100_0402_1%~D

@

@

1 2

RC88 0_0402_5%~DRC88 0_0402_5%~D

+VCC_CORE

12

12

RC93

RC93

100_0402_1%~D

100_0402_1%~D

RC97

RC97

100_0402_1%~D

100_0402_1%~D

VR_SVID_ALRT# 64

VCCSENSE 64

VSSSENSE 64

1

VR_SVID_CLK 64

VR_SVID_DAT 64

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PRO PR IETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CO N FIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PRO PR IETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CO N FIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PRO PR IETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CO N FIDENTIAL

AND TRADE SECRET INFORMAT ION. TH IS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMAT ION. TH IS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMAT ION. TH IS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY TH I R D PARTY WITHOUT PRIOR W R I TTEN CONSENT OF COMPAL ELECT R ON I C S, INC.

MAY BE USED BY OR DISCLOSED TO ANY TH I R D PARTY WITHOUT PRIOR W R I TTEN CONSENT OF COMPAL ELECT R ON I C S, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY TH I R D PARTY WITHOUT PRIOR W R I TTEN CONSENT OF COMPAL ELECT R ON I C S, INC.

3

2009/12/01 2011/12/31

2009/12/01 2011/12/31

2009/12/01 2011/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

PROCESSOR(5/6) PWR,BYPASS

PROCESSOR(5/6) PWR,BYPASS

PROCESSOR(5/6) PWR,BYPASS

LA-7391P

LA-7391P

LA-7391P

864Thursday, April 07, 2011

864Thursday, April 07, 2011

864Thursday, April 07, 2011

of

of

1

of

0.2

0.2

0.2

Page 9

5

4

3

2

1

+1.5V_CPU_VDDQ

+1.5V +1.5V_CPU_VDDQ

+VSBP+3VALW

12

RC101

D D

RC103

@RC103

@

SUSP#47,49,55,59,60,61,65

CPU1.5V_S3_GATE49

C C

B B

1 2

0_0402_5%~D

0_0402_5%~D

RC104

RC104

1 2

0_0402_5%~D

0_0402_5%~D

+VCC_GFXCORE_AXG

33A

AR24

AR23

AR21

AR20

AR18

AR17

AN24

AN23

AN21

AN20

AN18

AN17

AM24

AM23

AM21

AM20

AM18

AM17

AK24

AK23

AK21

AK20

AK18

AK17

AH24

AH23

AH21

AH20

AH18

AH17

AT24

AT23

AT21

AT20

AT18

AT17

AP24

AP23

AP21

AP20

AP18

AP17

AL24

AL23

AL21

AL20

AL18

AL17

AJ24

AJ23

AJ21

AJ20

AJ18

AJ17

+1.8VS +1.8VS_VCCPLL

RC119

RC119

0_0805_5%

0_0805_5%

1 2

A A

+V_DDR_REFA

+V_DDR_REFB

DRAMRST_CNTRL

10U_0805_6.3VAM

10U_0805_6.3VAM

1

2

RC115 0_0402_5%~D@RC115 0_0402_5%~D@

RC116 0_0402_5%~D@RC116 0_0402_5%~D@

2

G

G

CC58

CC58

13

D

D

S

S

1U_0402_6.3V6K

1U_0402_6.3V6K

1

CC59

CC59

2

1 2

1 2

QC8

QC8

BSS138_SOT23

BSS138_SOT23

1

2

1U_0402_6.3V6K

1U_0402_6.3V6K

CC60

CC60

13

D

D

G

G

S

S

RC117

RC117

1K_0402_1%

1K_0402_1%

330U_D2_2VM_R6M

330U_D2_2VM_R6M

1

CC61

CC61

+

+

2 3

QC7

QC7

BSS138_SOT23

BSS138_SOT23

2

12

@

@

1.5A

B6

A6

A2

DRAMRST_CNTRL 6

12

RC118

RC118

1K_0402_1%

1K_0402_1%

@

@

RC101

100K_0402_5%~D

100K_0402_5%~D

RUN_ON_CPU1.5VS3#

61

QC5A

QC5A

2N7002DW-7-F_SOT363-6~D

2N7002DW-7-F_SOT363-6~D

2

POWER

JCPU1G

JCPU1G

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

VAXG37

VAXG38

VAXG39

VAXG40

VAXG41

VAXG42

VAXG43

VAXG44

VAXG45

VAXG46

VAXG47

VAXG48

VAXG49

VAXG50

VAXG51

VAXG52

VAXG53

VAXG54

VCCPLL1

VCCPLL2

VCCPLL3

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

CONN@

CONN@

+V_DDR_REFA_R

+V_DDR_REFB_R

POWER

GRAPHICS

GRAPHICS

1.8V RAIL

1.8V RAIL

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

SENSE

LINES

SM_VREF

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

VREFMISC

VREFMISC

DDR3 -1.5V RAILS

DDR3 -1.5V RAILS

SA RAIL

SA RAIL

VCCSA_SENSE

VCCSA_VID[0]

VCCSA_VID[1]

VCCIO_SEL

M3 Circuit (Processor Generated SO-DIMM VREF_DQ)

5

4

12

RC99

RC99

100K_0402_5%~D

100K_0402_5%~D

RUN_ON_CPU1.5VS3

3

QC5B

QC5B

5

2N7002DW-7-F_SOT363-6~D

2N7002DW-7-F_SOT363-6~D

4

RUN_ON_CPU1.5VS3# 5, 11,55

AK35

AK34

+V_SM_VREF_CNT

AL1

+V_DDR_REFA_R

B4

+V_DDR_REFB_R

D1

+1.5V_CPU_VDDQ

5A

AF7

VDDQ1

AF4

VDDQ2

AF1

VDDQ3

AC7

VDDQ4

AC4

VDDQ5

AC1

VDDQ6

Y7

VDDQ7

Y4

VDDQ8

Y1

VDDQ9

U7

VDDQ10

U4

VDDQ11

U1

VDDQ12

P7

VDDQ13

P4

VDDQ14

P1

VDDQ15

6A

M27

VCCSA1

M26

VCCSA2

L26

VCCSA3

J26

VCCSA4

J25

VCCSA5

J24

VCCSA6

H26

VCCSA7

H25

VCCSA8

H23

C22

C24

A19

H_VCCSA_VID0 63

H_VCCSA_VID1 63

H_VCCP_SELH_VCCP_SELH_VCCP_SELH_VCCP_SELH_VCCP_SELH_VCCP_SELH_VCCP_SELH_VCCP_SELH_VCCP_SELH_VCCP_SEL

IVY Bridge drives VCCIO_SEL low

VCCP_PWRCTRL:0

Sandy Bridge is NC for A19

VCCP_PWRCTRL:1

Security Classifica t i on

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INF ORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INF ORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INF ORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

AO4728L_SO8~D

AO4728L_SO8~D

8

7

6

5

12

+VCC_GFXCORE_AXG

12

RC105

RC105

10_0402_1%

10_0402_1%

RC106

RC106