Page 1

COMPAL CONFIDENTIAL

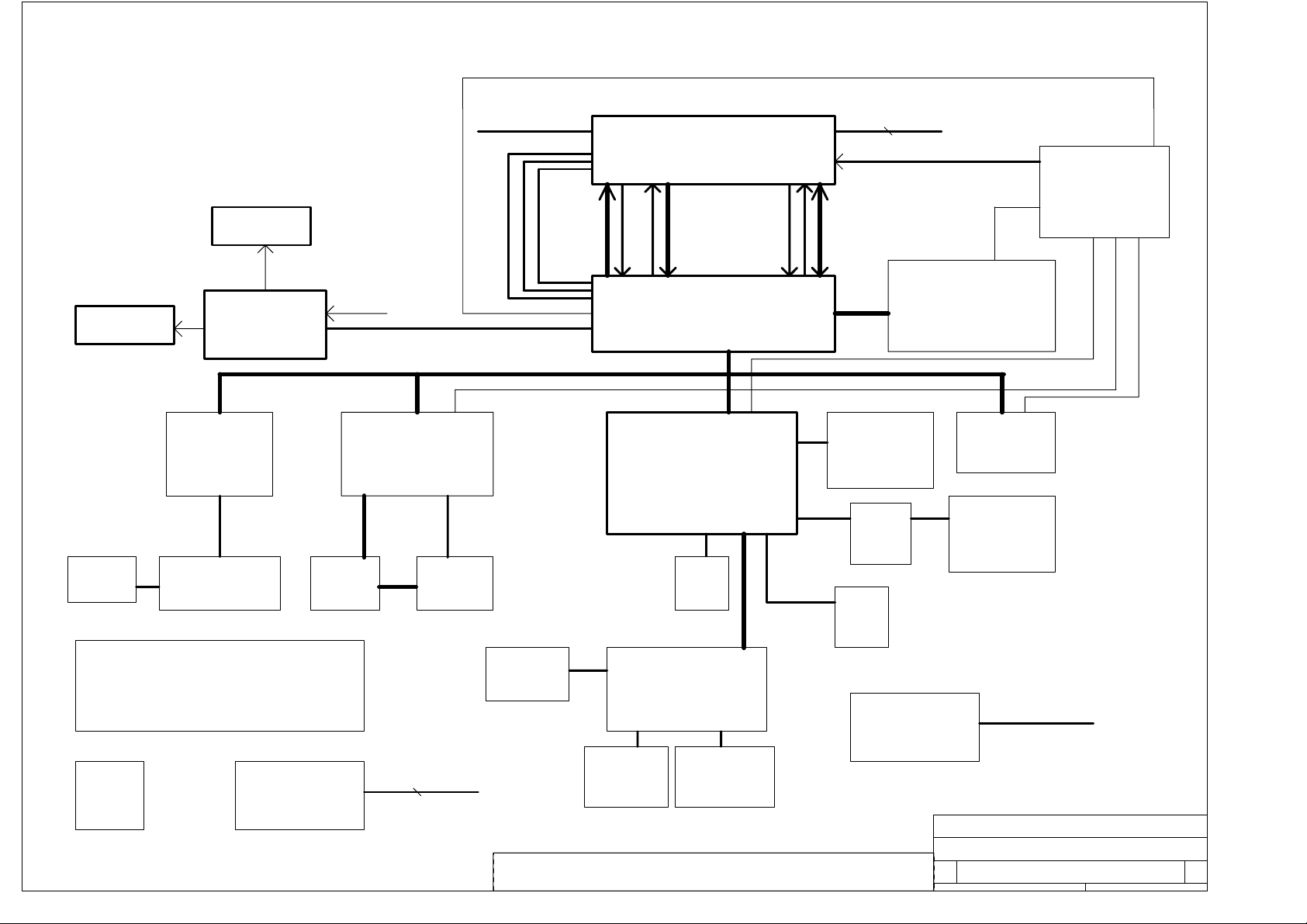

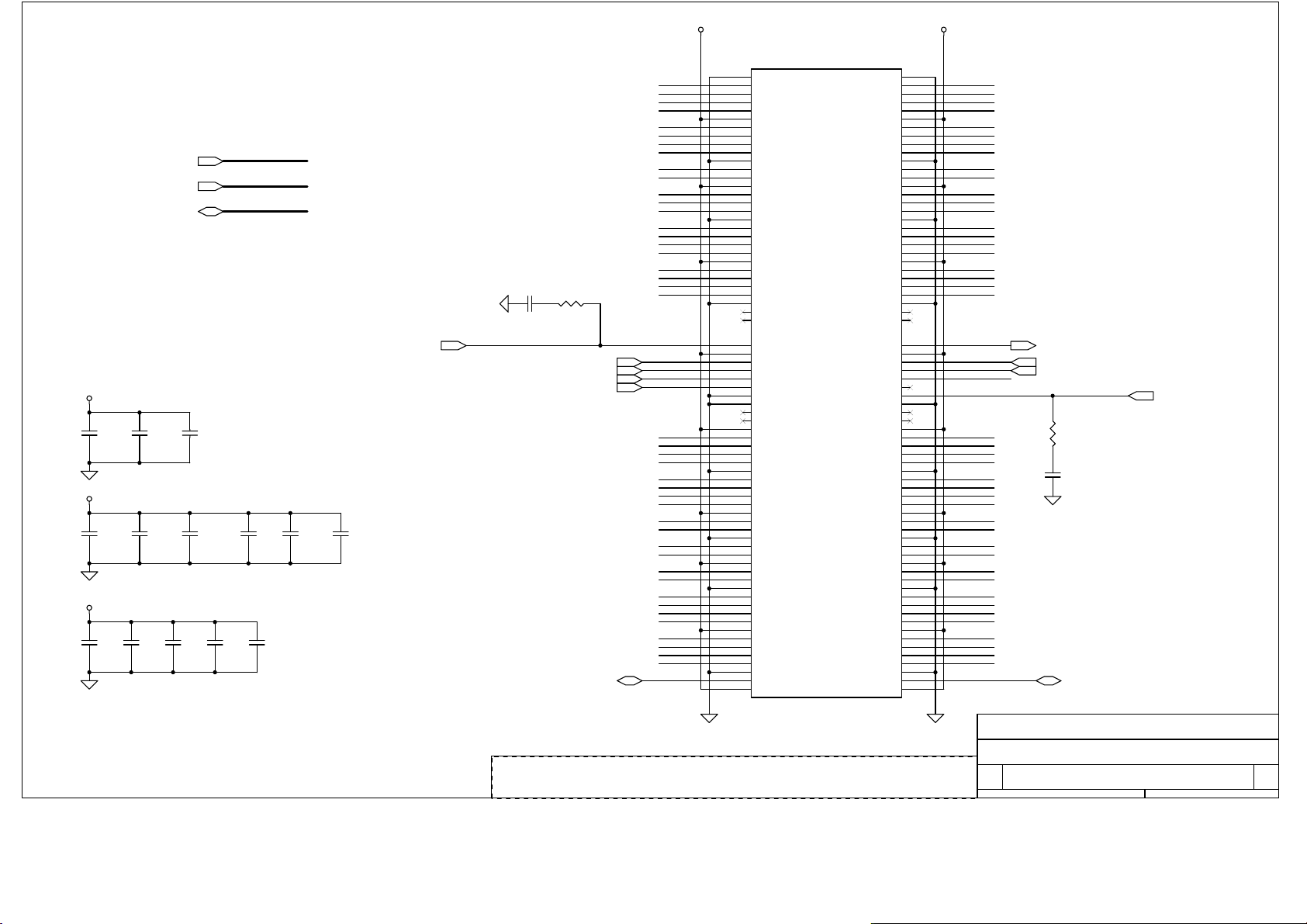

N32NN6 LA736B/C DISCRETE MODEL

AMD MOBILE K7 + ALI M1647 & M1535+

VER1.0 (w/ LCL)

LA-736B AND LA-736C DIFFERENCE IN PAGE 41(P.I.R) FOR DETAIL!

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

Compal Electronics, inc.

Title

SCHEMATIC, M/B LA-736/736B/736C

Size Document Number Rev

401168

Date: Sheet

145Monday, September 10, 2001

of

1F

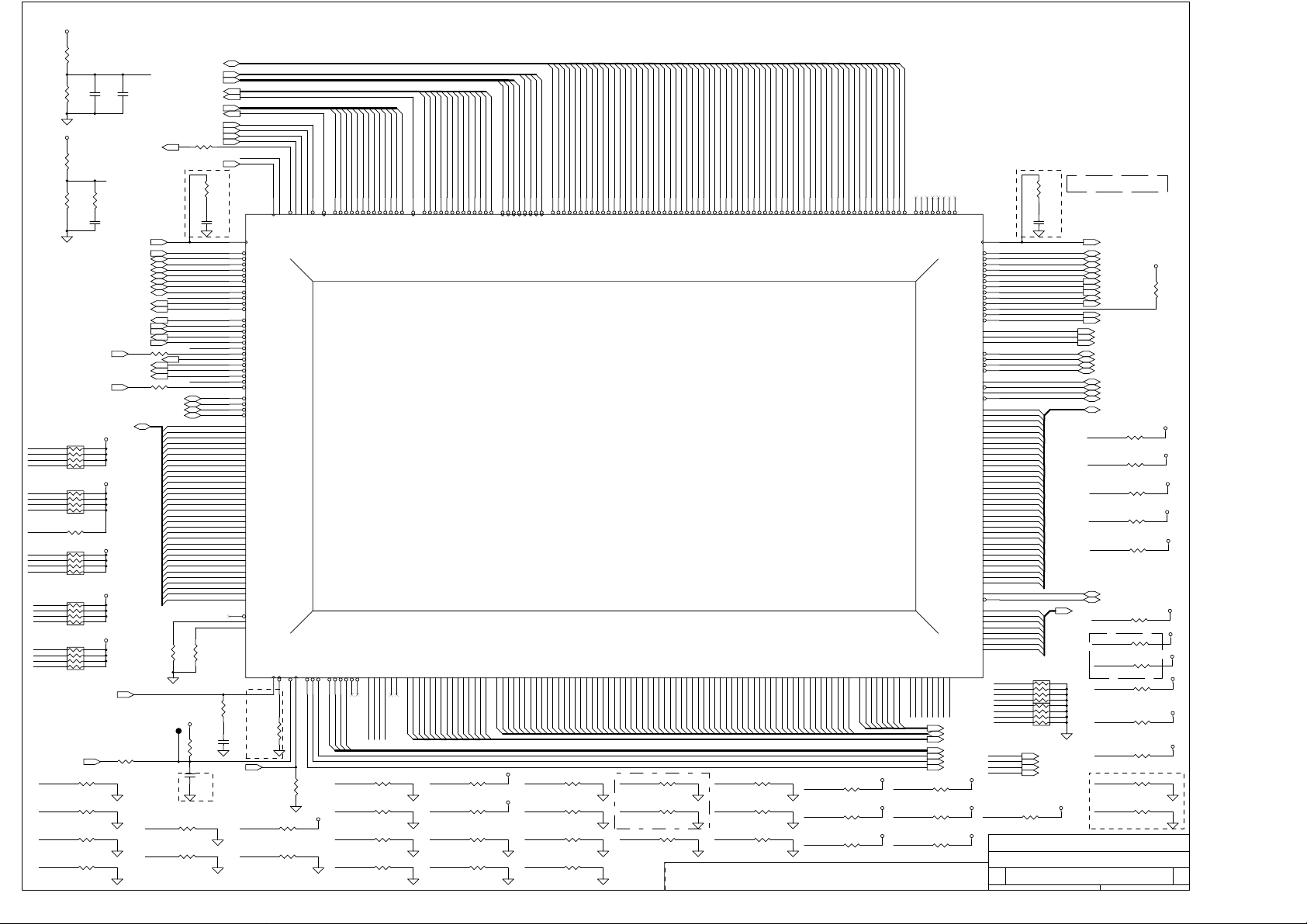

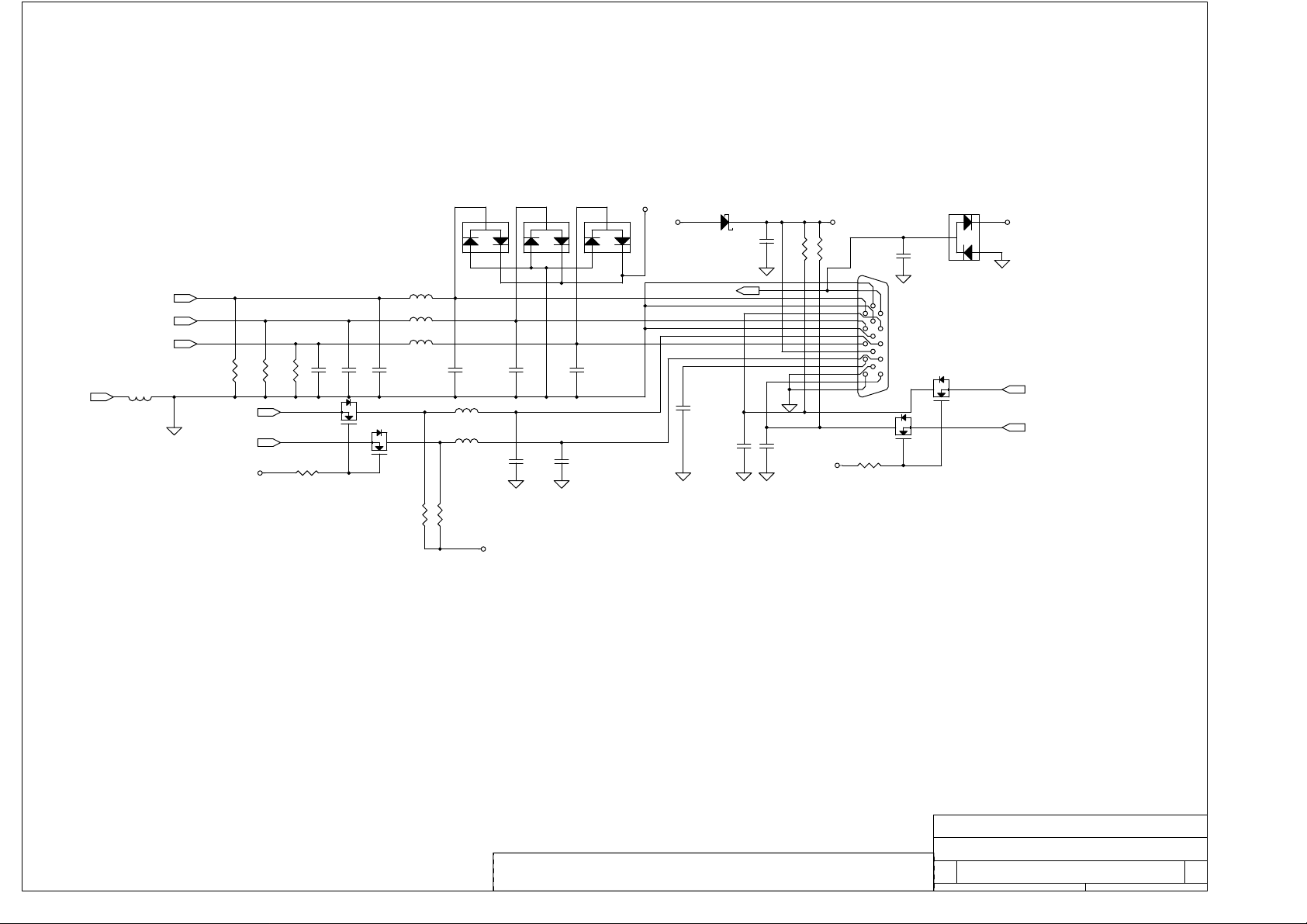

Page 2

MODEL NAME : N32N AMD K7 M/B LA-736C

REV:1.A

CRT CONN.

page 9

AUDIO

ESS 1988

PAGE 26

EQ

PAGE 28

DOT MATRIX LCD CONN.

FDD CONN.

TOUCH PAD CONN.

INTERNAL K/B CONN.

PIR

PAGE 37

AMP

AUDIO JACK

TV OUT

page 10

VGA Board

CONN.

page 8

PAGE 23

POWER

CIRCUIT

PAGE 30,33,34,35,36

14.3M_VGA

AGP Bus

CARD-BUS

CONTROLLER

TI1420 Solt1/2

PAGE 19

POWER

PAGE 20

COREFB +/-

CARDBUSPCMCIA

SLOT

PAGE 20

VID & FID

PROCRDY

CFWDRST

CONNECT

AMD K7(Socket A) CPU

page 3,4

Address

OUT[14:2]#

AOCLK# AICLK#

Address

IN[14:2]#

SDATAIN

CLK[3:0]#

SDATAOUT

CLK[3:0]#

COREFB +/-

CPUCLK +/-

SDATA[0..63]#

ALI

M1647

PAGE 5,6

PCI BUS

M1535 FOR LA-736B

ALI

ALI

M1535+ FOR LA-736C

PAGE 15,16

ISA/PCI BUS

PULLUP/DOWN

PAGE 14

USB

PAGE 17PAGE 27

ISA BUS

RESET

PS2 CKT

PAGE 29

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

EMBEDDED CONTLR.

NS PC87570

PAGE 24

DC-DC

INTERFACE

RTC BATT

PAGE 30

I/O BUFFER

BIOS

PAGE 25

HDD CONN.

PAGE 21

OZ163

PAGE 22

PIO

SIO

PAGE 17

VID & FID

POWER GOOD

PAGE 31,32

CLOCK GEN.

ICS9248-171

PAGE 7

SODIMM 1

PAGE 12

SODIMM 2

PAGE 13

MINI_PCI

SLOT

PAGE 18

CD-ROM

CONN.

PAGE 21

VID & FID

Compal Electronics, inc.

Title

SCHEMATIC, M/B LA-736/736B/736C

Size Document Number Rev

401168

Date: Sheet

245Monday, September 10, 2001

of

1F

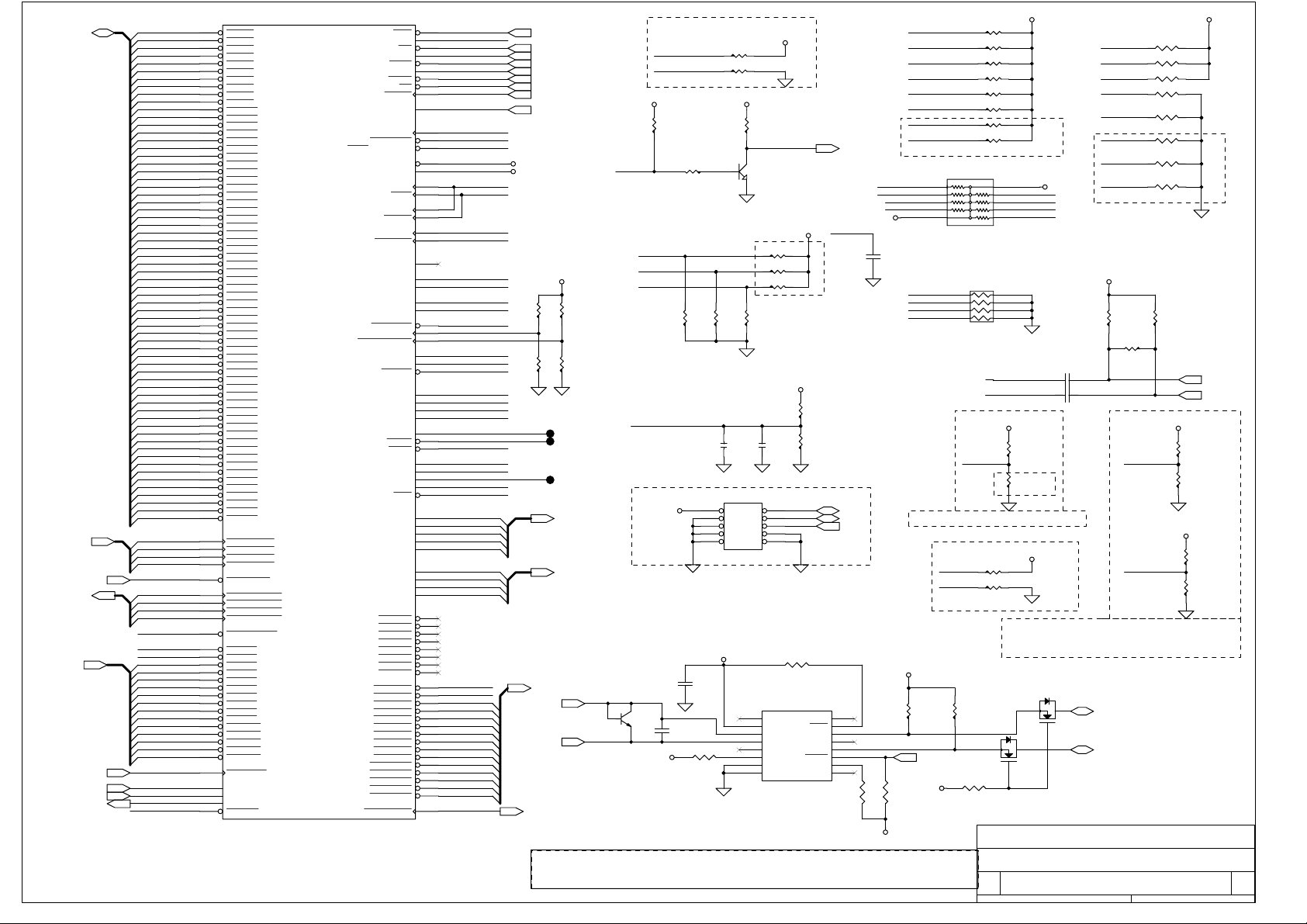

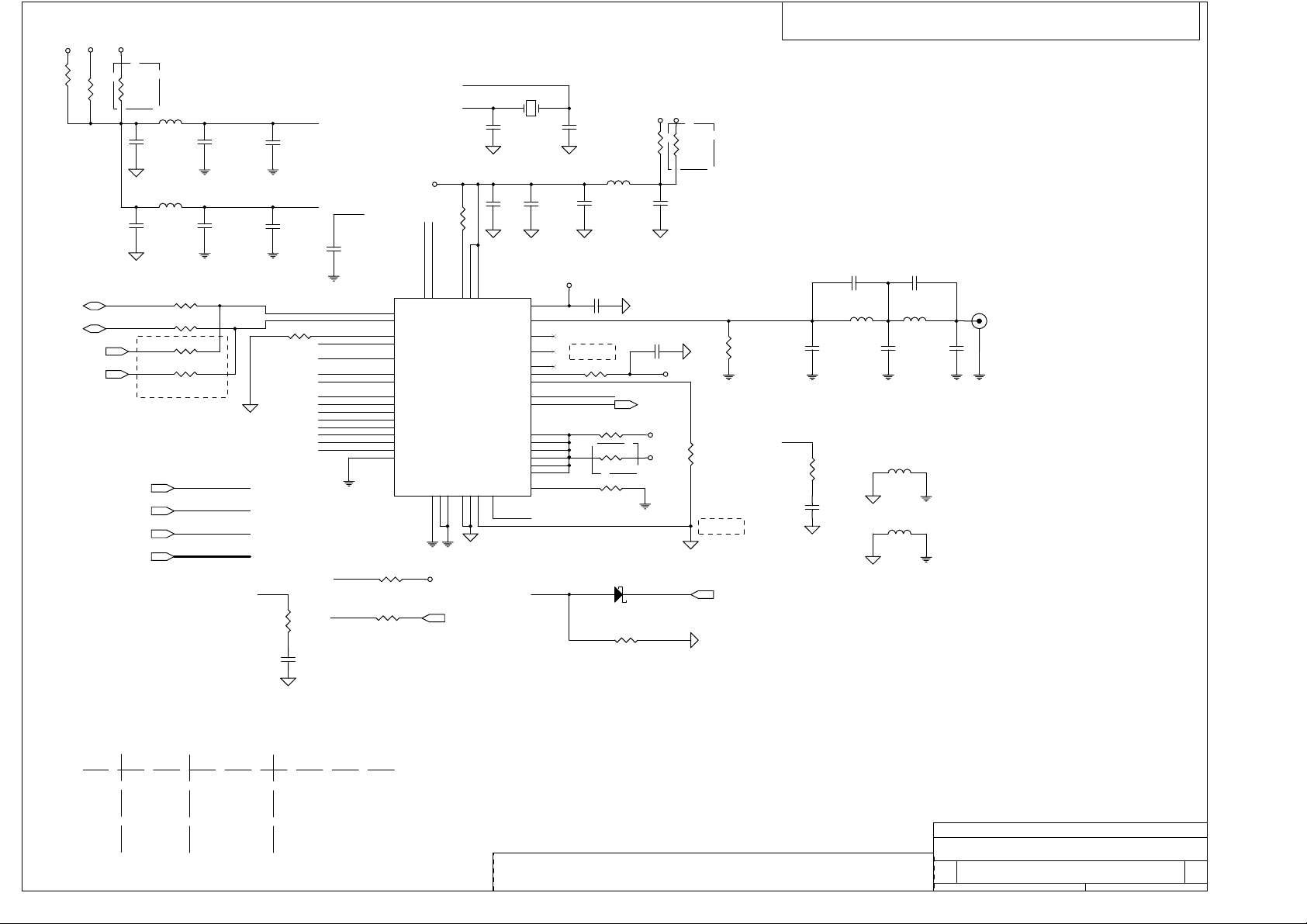

Page 3

JP6A

SDATA#[0..63]5

DICLK#[0..3]7

DIVAL#5

DOCLK#[0..3]5

AIN#[2..14]5

AICLK#7

CFWDRST5

CONNECT5

PROCRDY5

SDATA#0

SDATA#1

SDATA#2

SDATA#3

SDATA#4

SDATA#5

SDATA#6

SDATA#7

SDATA#8

SDATA#9

SDATA#10

SDATA#11

SDATA#12

SDATA#13

SDATA#14

SDATA#15

SDATA#16

SDATA#17

SDATA#18

SDATA#19

SDATA#20

SDATA#21

SDATA#22

SDATA#23

SDATA#24

SDATA#25

SDATA#26

SDATA#27

SDATA#28

SDATA#29

SDATA#30

SDATA#31

SDATA#32

SDATA#33

SDATA#34

SDATA#35

SDATA#36

SDATA#37

SDATA#38

SDATA#39

SDATA#40

SDATA#41

SDATA#42

SDATA#43

SDATA#44

SDATA#45

SDATA#46

SDATA#47

SDATA#48

SDATA#49

SDATA#50

SDATA#51

SDATA#52

SDATA#53

SDATA#54

SDATA#55

SDATA#56

SDATA#57

SDATA#58

SDATA#59

SDATA#60

SDATA#61

SDATA#62

SDATA#63

DICLK#0

DICLK#1

DICLK#2

DICLK#3

DIVAL#

DOCLK#0

DOCLK#1

DOCLK#2

DOCLK#3

DOVAL#

AIN#0

AIN#1

AIN#2

AIN#3

AIN#4

AIN#5

AIN#6

AIN#7

AIN#8

AIN#9

AIN#10

AIN#11

AIN#12

AIN#13

AIN#14

CFWDRST

CONNECT

PROCRDY

FILVAL#

AA35

W37

W35

Y35

U35

U33

S37

S33

AA33

AE37

AC33

AC37

Y37

AA37

AC35

S35

Q37

Q35

N37

J33

G33

G37

E37

G35

Q33

N33

L33

N35

L37

J37

A37

E35

E31

E29

A27

A25

E21

C23

C27

A23

A35

C35

C33

C31

A29

C29

E23

C25

E17

E13

E11

C15

A13

C21

A21

E19

C19

C17

A11

A17

A15

W33

J35

E27

E15

AN33

AE35

C37

A33

C11

AL31

AJ29

AL29

AG33

AJ37

AL35

AE33

AJ35

AG37

AL33

AN37

AL37

AG35

AN29

AN35

AN31

AJ33

AJ21

AL23

AN23

AJ31

E9

C9

A9

SDATA0

SDATA1

SDATA2

SDATA3

SDATA4

SDATA5

SDATA6

SDATA7

SDATA8

SDATA9

SDATA10

SDATA11

SDATA12

SDATA13

SDATA14

SDATA15

SDATA16

SDATA17

SDATA18

SDATA19

SDATA20

SDATA21

SDATA22

SDATA23

SDATA24

SDATA25

SDATA26

SDATA27

SDATA28

SDATA29

SDATA30

SDATA31

SDATA32

SDATA33

SDATA34

SDATA35

SDATA36

SDATA37

SDATA38

SDATA39

SDATA40

SDATA41

SDATA42

SDATA43

SDATA44

SDATA45

SDATA46

SDATA47

SDATA48

SDATA49

SDATA50

SDATA51

SDATA52

SDATA53

SDATA54

SDATA55

SDATA56

SDATA57

SDATA58

SDATA59

SDATA60

SDATA61

SDATA62

SDATA63

SDATAINCLK0

SDATAINCLK1

SDATAINCLK2

SDATAINCLK3

SDATAINVAL

SDATAOUTCLK0

SDATAOUTCLK1

SDATAOUTCLK2

SDATAOUTCLK3

SDTATOUTVAL

SADDIN0

SADDIN1

SADDIN2

SADDIN3

SADDIN4

SADDIN5

SADDIN6

SADDIN7

SADDIN8

SADDIN9

SADDIN10

SADDIN11

SADDIN12

SADDIN13

SADDIN14

SADDINCLK

CLKFWDRST

CONNECT

PROCRDY

SFILLVAL

A20M

FERR

INIT

INTR

IGNNE

NMI

RESET

SMI

STPCLK

PWROK

PICCLK

PICD0/BYPASSCLK

PICD1/BYPASSCLK

COREFB-

COREFB+

CLKIN

CLKIN

RSTCLK

RSTCLK

K7CLKOUT

K7CLKOUT

ANALOG

SYSVREFMODE

VREF_SYS

PLLBYPASS

PLLBYPASSCLK

PLLBYPASSCLK

PLLMON1

PLLMON2

PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

DBRDY

DBREQ

FLUSH

TCK

TDO

TMS

TRST

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

SCHECK0

SCHECK1

SCHECK2

SCHECK3

SCHECK4

SCHECK5

SCHECK6

SCHECK7

SADDOUT0

SADDOUT1

SADDOUT2

SADDOUT3

SADDOUT4

SADDOUT5

SADDOUT6

SADDOUT7

SADDOUT8

SADDOUT9

SADDOUT10

SADDOUT11

SADDOUT12

SADDOUT13

SADDOUT14

SADDOUTCLK

ZN

ZP

TDI

AE1

AG1

AJ3

AL1

AJ1

AN3

AG3

AN5

AC1

AE3

N1

N3

N5

AG13

AG11

AN17

AL17

AN19

AL19

AL21

AN21

AJ13

AA5

W5

AC5

AE5

AJ25

AN15

AL15

AN13

AL13

AC3

S1

S5

S3

Q5

AA1

AA3

AL3

Q1

U1

U5

Q3

U3

L1

L3

L5

L7

J7

W1

W3

Y1

Y3

U37

Y33

L35

E33

E25

A31

C13

A19

J1

J3

C7

A7

E5

A5

E7

C1

C5

C3

G1

E1

A3

G5

G3

E3

PPGA_462

A20M#

FERR

INIT#

INTR

IGNNE#

NMI

CPURST#

SMI#

STPCLK#

APICCLK

APICD0

APICD1

COREFB-

COREFB+

CPUCK

CPUCK#

CLKOUT

CLKOUT#

VREFMODE

VREF_SYS

ZN

ZP

PLLBP#

PLLMON1

PLLMON2

PLLTEST#

SCANCLK1

SCANCLK2

SINTVAL

SSHIFTEN

DBRDY

DBREQ#

FLUSH#

TCK

TDI

TDO

TMS

TRST#

PVID0

PVID1

PVID2

PVID3

PVID4

FID0

FID1

FID2

FID3

AOUT#0

AOUT#1

AOUT#2

AOUT#3

AOUT#4

AOUT#5

AOUT#6

AOUT#7

AOUT#8

AOUT#9

AOUT#10

AOUT#11

AOUT#12

AOUT#13

AOUT#14

AOCLK#

A20M# 15,24

CPUINIT 15

INTR 15

IGNNE# 15

NMI 15

CPURST# 5,15

SMI# 15

STPCLK# 15

PWROKCPU 29

COREFBCOREFB+

+CPU_CORE

R439

100_1%_0402

100_1%_0402

R440

100_1%_0402

R447

R448

100_1%_0402

1

TP1

1

TP2

1

TP3

PVID[0..4] 32

FID[0..3] 31

AOUT#[2..14] 5

THERMDA4

THERMDC4

AOCLK# 5

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

10 Miles

2

@MMBT3904

10 Miles

Near socket-A

COREFB+

COREFB-

+CPU_CORE

R423

820_0402

FERR

APICCLK

APICD0

APICD1

VREF_SYS is set at 50%

of VCC_CORE to CPU

VREF_SYS

R968

1K

R441

1K_0402

.01UF_0402

R414 @10K_0402

R417 0_0402

2

R442

1K_0402

C585

FOR A-TEST RESERVE

JP7

+5VALW

HEADER 5X2

+3V

12

C587

C588

@2200PF_0402

1 2

+3V

@.1UF_0402

R462

1 2

@1K_0402

1

Q52

3

+CPU_CORE

+3VS

R424

4.7K

FERR#

Q50

1

3

MMBT2222A

+3VS

R436 @330_0402

R437 @330_0402

R438 @330_0402

DEL BY AMD SUGGESTION

R443

1K_0402

+CPU_CORE

C586

0.1UF

12

34

56

78

910

ATF#

R459

1 2

@10K_0402

U18

1

NC

2

VCC

3

SMBCLK

DXP

4

DXN

5

SMBDATA

NC

6

ADD1

7

GND

8 9

GND NC

@NE1617DS

RESERVE FOR MOBILE K7

R449

100_1%_0402

R450

100_1%_0402

NC

STBY

NC

ALERT

ADD0

@1K_0402

FERR# 15

+CPU_CORE

NMI

Reduce NMI

noise for

C3

SMD 22..25,36

SMC 22..25,36

ATF# 25

16

15

14

13

12

11

10

12

R463

DBREQ#

TCK

TMS

TDI

TRST#

PLLTEST#

FLUSH#

PLLBP#

1

2

3

4

5

SSHIFTEN

SINTVAL

SCANCLK2

SCANCLK1

RP1

10P8R_680

1 8

2 7

3 6

4 5

A20M#

IGNNE#

INIT#

C1189

560PF_0402

VREFMODE=Low=No voltage scaling

ZN

ZP

Change Value by tunning

+3V

R460

@4.7K_0402

ATF# 25

12

+3VS

+3V

R464

@10K_0402

1 2

+CPU_CORE

R411 510_0402

R412 510_0402

R415 510_0402

R418 510_0402

R420 510_0402

R421 510_0402

R932 820_0402

R933 820_0402

RP2

8P4R-270

10

9

8

7

6

INTRCPURST#

NMI

SMI#

STPCLK#

+CPU_CORE

Near socket-A

CPUCK

C583 680PF_0402

CPUCK#

C584 680PF_0402

+CPU_CORE +CPU_CORE

R451

+CPU_CORE

R456 36.5 1%

R457 36.5 1%

S

Q53

G

@2N7002

2

@1K_0402

R453

1.5K_0402

Trace lengths of CLKOUT and CLKOUT#

are between 2" and 3"

Q51

@2N7002

S

G

2

D

13

VREFMODE

R461

@4.7K_0402

R465

@10K_0402

D

13

PLLMON1

PLLMON2

AIN#1

AOUT#0

AOUT#1

FILVAL#

AIN#0

DOVAL#

+CPU_CORE

R444

60.4 1%

R446

301 1%

CLKOUT

CLKOUT#

SMC 22..25,36

SMD 22..25,36

Compal Electronics, inc.

Title

SCHEMATIC, M/B LA-736/736B/736C

Size Document Number Rev

401168

Date: Sheet of

+CPU_CORE

R413 56_0402

R416 56_0402

R432 820_0402

R422 @1K_0402

R427 @1K_0402

R429 820_0402

R419 820_0402

R434 820_0402

R445

60.4 1%

R452

100_1%_0402

R454

100_1%_0402

+CPU_CORE

R455

100_1%_0402

R458

100_1%_0402

345Monday, September 10, 2001

CPUCLK 7

CPUCLK# 7

1F

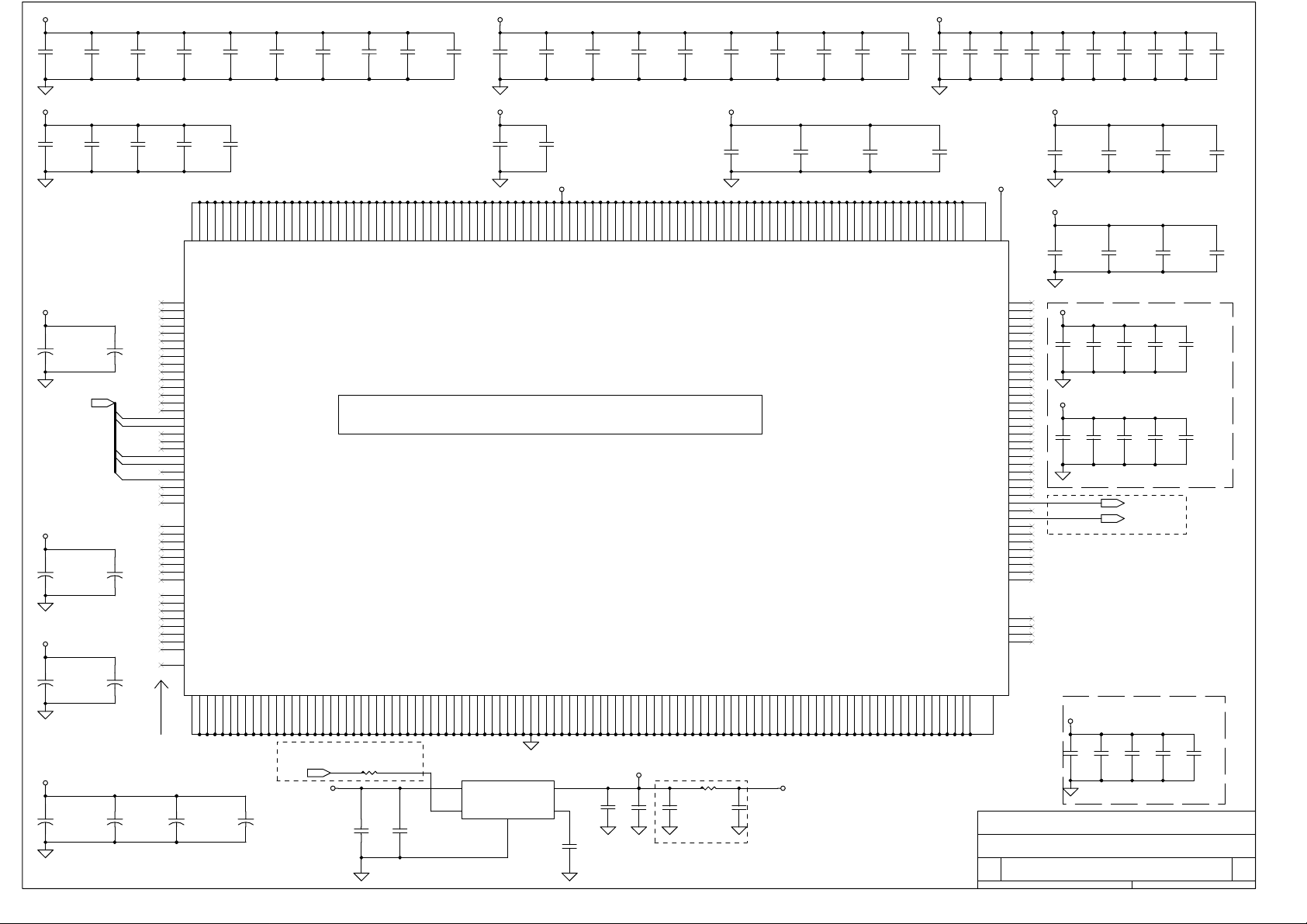

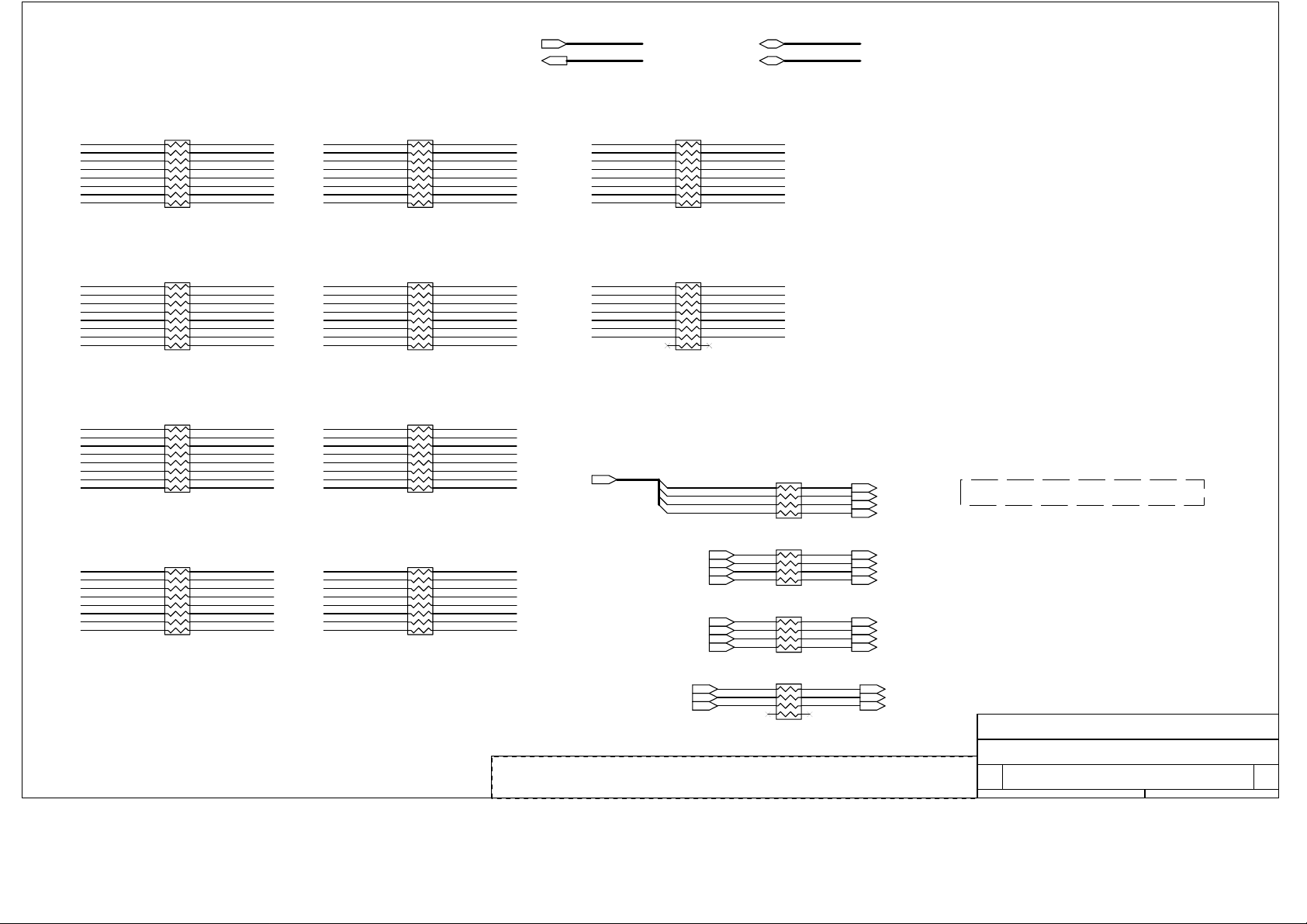

Page 4

+CPU_CORE

+CPU_CORE +CPU_CORE

12

C589

0.22UF

+CPU_CORE

12

C619

0.22UF

12

0.22UF

12

0.22UF

C590

C620

12

C591

0.22UF

12

C621

2.2UF

Located at Socket-A Cap

0.22UF(0603) X 22

0.22UF(0603) X3 FOR RESERVE

0.1UF(0603) X 2

0.01UF(0603) X 8

1UF(0805) X 8

10UF(1206) X 4

AMD recommandation

220UF X10

+CPU_CORE

+

C656

220UF_4V_D

SVID[0..4]32

+CPU_CORE

+

C658

220UF_4V_D

+CPU_CORE

+

C1163

220UF_4V_D

+

C657

220UF_4V_D

+

C1162

220UF_4V_D

+

C1164

220UF_4V_D

SVID0

SVID4

SVID2

SVID3

SVID1

AD30

AD8

AF10

AF28

AF30

AF32

AF6

AF8

AH30

AH8

AJ9

AK8

AL9

AM8

F30

H10

H28

H30

H32

K30

AJ7

AL7

AN7

G25

G17

AG7

AG15

AG29

AA7

AG9

AG17

AG27

G15

G23

AH6

12

0.22UF

12

0.22UF

F8

H6

H8

K8

G9

N7

Y7

G7

Q7

VCC_SRAM1

VCC_SRAM2

VCC_SRAM3

VCC_SRAM4

VCC_SRAM5

VCC_SRAM6

VCC_SRAM7

VCC_SRAM8

VCC_SRAM9

VCC_SRAM11

VCC_SRAM13

VCC_SRAM14

VCC_SRAM16

VCC_SRAM17

VCC_SRAM19

VCC_SRAM20

VCC_SRAM21

VCC_SRAM22

VCC_SRAM23

VCC_SRAM24

VCC_SRAM25

VCC_SRAM26

VCC_SRAM27

VCC_SRAM28

VCC_SRAM29

VCC_SRAM30

VCC_SRAM31

KEY4

KEY6

KEY8

KEY10

KEY12

KEY14

KEY16

KEY18

KEY

KEY

KEY

KEY

KEY

KEY

KEY

KEY

AMD

12

C592

0.22UF

12

C622

0.22UF

H12

H16

H20

H24M8P30R8T30V8X30Z8AB30

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_CORE5

VCC_CORE6

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

H14

H18

H22

H26

M30P8R30T8V30X8Z30

C593

C623

VCC_CORE7

VSS7

VCC_CORE8

VCC_CORE9

VSS8

VSS9

VCC_CORE10

VCC_CORE11

VSS10

VSS11

12

C594

0.22UF

AF14

VCC_CORE12

VSS12

AB8

AF12

AF18

VCC_CORE13

VCC_CORE14

VSS13

VSS14

AF16

12

12

C597

0.22UF

AH22

AH18

VCC_CORE29

VSS30

AH32

AH28

AH14

VCC_CORE30

VCC_CORE31

VSS31

VSS32

AH24

AH10

VCC_CORE32

VSS33

AH20

AH4

VCC_CORE33

VSS34

AH16

AH2

VCC_CORE34

VSS35

AH12

12

C598

0.22UF

AF36

AF34

VCC_CORE35

VSS37

AF4

AF2

AD6

VCC_CORE36

VCC_CORE37

VSS38

VSS39

AD36

+CPU_CORE

AM26

AD4

AD2

VCC_CORE38

VCC_CORE39

VCC_CORE40

VSS40

VSS41

VSS42

AD34

AD32

AB6

AF22

VCC_CORE15

VSS15

AF20

AF26

VCC_CORE16

VSS16

AF24

AM34

VCC_CORE17

VSS17

AM36

12

0.22UF

AK36

VCC_CORE18

VSS18

AK32

C596

C595

0.22UF

AK34

AK30

AK26

AK22

AK18

AK14

AK10

AL5

AH26

AM30

VCC_CORE19

VCC_CORE20

VCC_CORE21

VCC_CORE22

VCC_CORE23

VCC_CORE24

VCC_CORE25

VCC_CORE26

VCC_CORE27

VCC_CORE28

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

VSS19

VSS20

VSS21

VSS22

VSS23

VSS25

VSS26

VSS27

VSS28

VSS29

AK28

AK24

AK20

AK16

AK12

AK4

AK2

AH36

AM32

AH34

12

C599

0.22UF

12

C632

.1UF_0402

AB36

AB34

AB32Z6Z4Z2X36

VCC_CORE41

VCC_CORE42

VCC_CORE43

VSS43

VSS44

VSS45

AB4

AB2

Z36

+CPU_CORE

VCC_CORE44

VCC_CORE45

VCC_CORE46

VSS46

VSS47

VSS48

Z34

Z32X6AM28X4X2

12

C600

0.22UF

12

C633

.1UF_0402

X34

AM22

VCC_CORE47

VCC_CORE48

VCC_CORE49

VSS49

VSS50

VSS51

12

0.22UF

X32V6V4V2T36

VCC_CORE50

VCC_CORE51

VCC_CORE52

VCC_CORE53

VSS52

VSS53

VSS54

VSS55

V36

V34

V32T6T4T2R36

C601

T34

VCC_CORE54

VSS56

T32R6R4R2AM18

VCC_CORE55

VCC_CORE56

VCC_CORE57

VSS57

VSS58

VSS59

R34

AM24

12

C602

0.22UF

VCC_CORE58

VCC_CORE59

VCC_CORE60

VSS60

VSS61

VSS62

R32P6P4P2M36

P36

VCC_CORE61

VSS63

P34

P32M4M6M2K36

VCC_CORE62

VCC_CORE63

VCC_CORE64

VSS64

VSS65

VSS66

M34

12

C603

0.22UF

K34

VCC_CORE65

VCC_CORE66

VCC_CORE67

VSS67

VSS68

VSS69

M32K6K4K2AM20

12

0.22UF

+CPU_CORE

12

K32H4H2

VCC_CORE68

VCC_CORE69

VCC_CORE70

VSS70

VSS71

VSS72

H36

H34

C604

C634

10UF_10V_1206

AM14

F36

F34

F32

F28

VCC_CORE71

VCC_CORE72

VCC_CORE73

VCC_CORE74

VCC_CORE75

VSS73

VSS74

VSS75

VSS76

VSS77

F26

F22

F18

F14

F10F6F4F2AM16

12

0.22UF

F24

VCC_CORE76

VCC_CORE77

VSS78

VSS79

C605

F20

VCC_CORE78

VSS80

F16

VCC_CORE79

VSS81

12

F12

12

C606

0.22UF

C635

10UF_10V_1206

D32

D28

AM10

D24

D20

VCC_CORE80

VCC_CORE81

VCC_CORE82

VCC_CORE83

VCC_CORE84

VSS82

VSS83

VSS84

VSS85

VSS86

D36

D34

D30

D26

D22

D16

D12D8D4D2B36

VCC_CORE85

VCC_CORE86

VCC_CORE87

VSS87

VSS88

VSS89

D18

D14

12

C607

0.22UF

0.22UF

12

C636

10UF_10V_1206

VCC_CORE88

VCC_CORE89

VCC_CORE90

VSS90

VSS91

VSS92

D10D6B34

AM12

B32

VCC_CORE91

VCC_CORE92

VSS93

VSS94

B30

AM2

VCC_CORE93

VSS95

B26

12

B28

VCC_CORE94

VSS96

B22

C608

B24

VCC_CORE95

VSS97

B18

B20

B14

12

C609

1000PF_0402

12

C637

10UF_10V_1206

B16

B12B8B4

VCC_CORE96

VCC_CORE97

VCC_CORE98

VSS98

VSS99

VSS100

B10B6B2

.1UF_0402

AJ5

VCC_CORE99

VCC_CORE100

VSS101

VSS102

AM4

AK6

12

C610

VCC_CORE101

BP0_CUT

BP1_CUT

BP2_CUT

BP3_CUT

VSS103

VSS104

AM6

12

+VCCA2.5

AC7

AJ23

VCC_Z

VCC_A

NC1

NC2

NC3

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

NC25

NC27

NC28

NC29

NC30

NC31

NC32

NC33

NC34

NC35

NC36

NC37

NC42

NC43

NC44

NC45

VSS_Z

AE7

12

C611

.01UF_0402

JP6B

PPGA_462

AA31

AC31

AE31

AG23

AG25

AG31

AG5

AJ11

AJ15

AJ17

AJ19

AJ27

AL11

AN11

AN9

G11

G13

G27

G29

G31

J31

J5

L31

N31

Q31

S31

S7

U31

U7

W31

W7

Y31

Y5

AG19

G21

AG21

G19

AN27

AL27

AN25

AL25

12

C612

C613

.1UF_0402

1000PF_0402

+CPU_CORE

C638

1UF_10V_0603

+CPU_CORE

C642

1UF_10V_0603

+CPU_CORE

12

C646

39PF_0402

+CPU_CORE

12

C651

560PF_0402

THERMDA

THERMDC

9/04/2000 CHANGE BACK

+CPU_CORE

12

12

C615

C614

1000PF_0402

.01UF_0402

C639

1UF_10V_0603

C643

1UF_10V_0603

12

12

C648

C647

39PF_0402

39PF_0402

12

12

C652

C653

560PF_0402

560PF_0402

THERMDA 3

THERMDC 3

ONE INCH SPACING ALONG THE PLANE EDGE

12

C616

.01UF_0402

C640

1UF_10V_0603

C644

1UF_10V_0603

12

C649

39PF_0402

12

C654

560PF_0402

560PF_0402

12

12

C617

1000PF_0402

.01UF_0402

C641

1UF_10V_0603

C645

1UF_10V_0603

12

C650

39PF_0402

12

C655

C618

AMD Socket-A processors will not

implement a pin at location AH6.

+CPU_CORE

+

C668

220UF_4V_D

12

+

C669

220UF_4V_D

12

+

C670

220UF_4V_D

12

+

C671

220UF_4V_D

CONTROL ON/OFF

+3VS

R466 0-0402

C672

39PF_0402

C673

1UF_10V_0603

VR_ON25,35

(2.5V Output)

U19

SI9183BT-25

1

VIN

3

SD#

VSS

2

2.5V,if 1GHz need 100mA

+VCCA2.5

5

VOUT

BP

C674

.1UF_0402

4

12

C665

C664

.01UF_0402

4.7UF_10V_0805

C666

39PF_0402

Near socket-A

pin AJ23

R467 0

C667

39PF_0402

+VCCP2.5

Compal Electronics, inc.

Title

SCHEMATIC, M/B LA-736/736B/736C

Size Document Number Rev

401168

Date: Sheet of

VCCA for cpu internal PLL power source!

12

C659

1000PF_0402

12

12

C660

1000PF_0402

1000PF_0402

FOR EMI RESERVE

C661

12

12

C662

1000PF_0402

1000PF_0402

445Monday, September 10, 2001

C663

1F

Page 5

PFRAME#

PIRDY#

PTRDY#

PSTOP#

PDEVSEL#

SERR#

PLOCK#

PCIREQ#

SERR#

REQ#_0

REQ#_1

REQ#_2

REQ#_3

GNT#_0

GNT#_1

GNT#_2

GNT#_3

GNT#_4

GNT#_5

REQ#_4

REQ#_5

Near M1647

+3VS

+3VS

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

SUS_STAT#8,15,16

C/BE#0

C/BE#1

C/BE#2

C/BE#3

R468

11K 1%

R469

5.9K 1%

R470

120

CPUCLK_NB

R473

120

AGP_BUSY#8,15

AGP_STP#8,15

RP3

8P4R-2.7K

RP4

8P4R-2.7K

R959 560

RP5

8P4R-2.7K

RP6

8P4R-2.7K

RP7

8P4R-2.7K

R949

1 2

2.2K-0402

R950

1 2

2.2K-0402

R952

1 2

2.2K-0402

R954

1 2

2.2K-0402

C675

.047UF

R474

@10

C677

+3VS

+3VS

+3VS

+3VS

+3VS

DCLK_NB7

CPUCLK_NBVR

C676

0.1uF

@10PF

PCLK_NB7

PCIRST#10,14,15,18..21,26

FRAME#15,18,19,26

IRDY#15,18,19,26

TRDY#15,18,19,26

STOP#15,18,19,26

DEVSEL#15,18,19,26

SERR#15,18,19

PHLD#14,15

PHLDA#14,15

PCIREQ#8

AD[0..31]15,18,19,26,31

R1024 0-0402

1 2

Under M1647

(Solder

side)

CPURST#3,15

PAR15,18,19,26

REQ#018

REQ#118

REQ#226

REQ#319

R476

1 2

GNT#018

GNT#118

GNT#226

GNT#319

R477

1 2

SUSPEND#

ST0

ST1

SDATA#[0..63]3

DOCLK#[0..3]3

@0

@0

C/BE#015,18,19,26

C/BE#115,18,19,26

C/BE#215,18,19,26

C/BE#315,18,19,26

AD0

AD1AD1

AD2AD2AD2

AD3

AD4AD4

AD5AD5AD5

AD6AD6AD6AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

R478

10K

TP5

+3VALW

1

C1204 @?PF

ADD FOR SUSPEND ISSUE

R951

1 2

2.2K-0402

R953

1 2

2.2K-0402

DICLK_NB#[0..3]7

AOUT#[2..14]3

AOCLK#3

AIN#[2..14]3

AICLK_NB#7

DIVAL#3

PROCRDY3

CONNECT3

CFWDRST3

R984 @0_0402

CPUCLK_NB7

PAR

SERR#

PLOCK#

PHLD#

PHLDA#

GNT#_0

PDEVSEL#

PCIREQ#

REQ#_0

REQ#_1

REQ#_2

REQ#_3

REQ#_4

REQ#_5

GNT#_1

GNT#_2

GNT#_3

GNT#_4

GNT#_5

TESTMODE

TESTEN1

R479

R491

10K

R471

@0

ACNBP

C678

@10PF

PFRAME#

PIRDY#

PTRDY#

PSTOP#

10K

Near M1647

ACNBS

RTCCLK8,16,20

CPUCLK_NBVR

Near M1647

F9

PCICLK

G6

PCIRST#

D6

FRAME#

A5

IRDY#

B5

TRDY#

A4

STOP#

C5

DEVSEL#

A3

PAR

C4

SERR#/CLKRUN#

B4

LOCK#

E5

PHLD#

F5

PHLDA#

F6

AREQ#

D10

PREQ0#

B10

PREQ1#

E11

PREQ2#

C11

PREQ3#

A11

PREQ4#

B12

PREQ5#

C10

PGNT0#

A10

PGNT1#

D11

PGNT2#

B11

PGNT3#

C12

PGNT4#

A12

PGNT5#

D3

CBE0#

C3

CBE1#

B6

CBE2#

C8

CBE3#

F1

AD0

F4

AD1

F2

AD2

F3

AD3

E2

AD4

E1

AD5

E3

AD6

D1

AD7

D2

AD8

C1

AD9

C2

AD10

B1

AD11

D4

AD12

B2

AD13

A2

AD14

B3

AD15

D7

AD16

A6

AD17

C7

AD18

B7

AD19

F8

AD20

A7

AD21

E8

AD22

D8

AD23

B8

AD24

A8

AD25

D9

AD26

E9

AD27

C9

AD28

B9

AD29

F10

AD30

A9

AD31

E6

NC

AE2

TESTMODE

AF2

NT_TESTEN

R485

@0

C680

@10PF

AD11

AD5

V21

U21

HCLK

DCLK

W21

Y21

DCLK_NBJ

R505

1 2

10K-0402

R511

1 2

2.2K-0402

AD[5..31] M1647 HARDWARE STRAPPING

AICLK#

AIN#4

AIN#2

AIN#7

AIN#3

AIN#8

AIN#5

AIN#6

W26

C13

A13

E12

C14

A14

B17

A17

B16

A18

E13

E15

D13

SAIN2#

SAIN3#

SAIN4#

SAIN5#

SAIN6#

SAIN7#

SAICLK#

CLKFRST

CPURST#

SDINVAL#

CONNECT

PROCRDY

VREF_HCLK

?

PCI Interface

SUSPEND#

CLK32KI

MWE#

SRAS#

SCAS#

DCLK#

CS0#

CS1#

CS2#

CS3#

CS4#

AC20

AA9

RAS#0

AB9

RAS#1

AB8

RAS#2

AC8

RAS#3

**

AD12

AD13

AD14

AD15

AB7

CS5#

AA8

Y23

CCKE0

1 2

1 2

1 2

1 2

AB5

AC5

AB10

AA10

R490

10K

R492

10K

+3VS

AIN#9

AIN#10

AIN#11

C15

A16

C17

SAIN8#

SAIN9#

SAIN10#

CKE0

CKE1

CKE2

Y26

AB22

Y25

CCKE1

CCKE3

CCKE2

R493

@2.2K-0402

R499

2.2K-0402

R506

2.2K-0402

R512

2.2K-0402

AIN#12

AIN#13

B14

SAIN11#

SAIN12#

CKE3

CKE4

AB21

AIN#14

B15

SAIN13#

CKE5

Y24

A15

SAIN14#

AA11

MMA0

AOCLK#

U25

SAOCLK#

MA0

MA1

AB11

MMA1

AB12

MMA2

AOUT#2

R25

MA2

AB15

MMA3

AOUT#3

AOUT#4

R26

N22

SAOUT2#

SAOUT3#

MA3

MA4

AC14

AB14

MMA4

MMA5

AOUT#5

AOUT#6

T26

R24

SAOUT4#

SAOUT5#

MA5

MA6

AC17

AA16

MMA6

MMA7

AD17

AD18

AD19

AOUT#8

AOUT#7

V26

T25

SAOUT6#

SAOUT7#

MA7

MA8

AB16

AA18

MMA9

MMA8

AOUT#9

AOUT#11

AOUT#10

T24

P25

P26

SAOUT8#

SAOUT9#

SAOUT10#

MA9

MA10

MA11

AA17

AA19

AB19

MMA11

MMA10

MMA12

R494

1 2

10K-0402

R500

1 2

10K-0402

R507

1 2

2.2K-0402

R513

1 2

2.2K-0402

AOUT#12

AOUT#13

U26

V25

SAOUT11#

SAOUT12#

SAOUT13#

MA12

BA0

BA1

AB17

AB18

MMA14

MMA13

DOCLK#3

DOCLK#0

DOCLK#1

DICLK_NB#1

DICLK_NB#2

DICLK_NB#0

AOUT#14

V24

SAOUT14#

C20

D22

SDICLK0#

SDICLK1#

DICLK_NB#3

F24

L25

SDICLK2#

SDICLK3#

DOCLK#2

D16

D24

SDOCLK0#

SDOCLK1#

G23

N25

SDOCLK2#

SDOCLK3#

SDATA#0

SDATA#1

A20

F18

SDATA0#

SDATA#2

SDATA#3

A21

B20

SDATA1#

SDATA2#

SDATA#5

SDATA#4

B21

A22

SDATA3#

SDATA4#

SDATA#7

SDATA#6

B22

C23

SDATA5#

SDATA6#

SDATA#9

SDATA#8

F17

B18

SDATA7#

SDATA8#

SDATA#10

E16

SDATA9#

CPU Interface

M1647-SDR

Northbridge

SDR SDRAM Interface

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

AD3

MMD0

AF3

MMD1

+3VS

+3VS

AF4

MMD2

AE5

MMD3

MMD4

AC6

AF6

AE7

AE8

AC9

AF9

AE10

AD11

MMD6

MMD7

MMD9

MMD5

MMD8

MMD11

MMD10

AD20AD16

1 2

AD21

1 2

AD22

1 2

AD23

1 2

AC12

AF12

MMD12

MMD14

MMD13

R495

@2.2K-0402

R501

@2.2K-0402

R508

@2.2K-0402

R514

@2.2K-0402

AE13

AD14

MMD15

AF17

MMD16

AF18

MMD17

AE19

MMD18

MD19

AD20

MMD20

MMD19

AF20

SDATA#19

SDATA#22

SDATA#20

SDATA#12

SDATA#13

SDATA#14

SDATA#11

SDATA#17

SDATA#15

SDATA#18

SDATA#21

SDATA#16

C18

D17

B19

A19

D18

A23

B23

A24

A25

B26

C26

D26

SDATA10#

SDATA11#

SDATA12#

SDATA13#

SDATA14#

SDATA15#

SDATA16#

SDATA17#

SDATA18#

SDATA19#

SDATA20#

SDATA21#

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

AE21

AE22

AC23

MMD21

MMD23

MMD22

Modify by 4/10 Tunning Time

MD31

AF23

AE24

AF25

AE26

AC24

AC26

AB26

AA25

AE3

MMD32

MMD27

MMD26

MMD25

MMD28

MMD29

MMD24

MMD31

MMD30

R496

AD24

1 2

2.2K-0402

R502

AD25

1 2

2.2K-0402

R509

AD26

1 2

@2.2K-0402

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

SDATA#23

SDATA#24

C25

D19

SDATA22#

SDATA23#

SDATA24#

MD32

MD33

MD34

AD4

AD5

MMD34

MMD33

SDATA#25

SDATA#26

SDATA#27

E19

D20

SDATA25#

SDATA26#

MD35

MD36

AF5

AE6

MMD37

MMD36

MMD35

SDATA#29

SDATA#28

F19

E20

SDATA27#

SDATA28#

MD37

MD38

AD7

AD8

MMD39

MMD38

SDATA#31

SDATA#30

F20

E23

SDATA29#

SDATA30#

MD39

MD40

AF8

AE9

MMD40

MMD41

SDATA#32

SDATA#33

E22

F23

F22

SDATA31#

SDATA32#

MD41

MD42

AD10

AF10

AF11

MMD42

MMD43

AD27

AD28

AD29

SDATA#34

SDATA#35

G21

H22

SDATA33#

SDATA34#

SDATA35#

MD43

MD44

MD45

AE12

AD13

MMD45

MMD44

1 2

1 2

1 2

SDATA#38

SDATA#37

SDATA#36

J22

H21

G24

SDATA36#

SDATA37#

SDATA38#

MD46

MD47

MD48

AF13

AE14

AE18

MMD46

MMD47

MMD48

R497

@2.2K-0402

R503

@2.2K-0402

R510

@2.2K-0402

SDATA#40

SDATA#39

SDATA#41

J26

D25

E26

SDATA39#

SDATA40#

MD49

MD50

AD19

AF19

AE20

MMD51

MMD49

MMD50

SDATA#43

SDATA#42

SDATA#44

E25

F26

SDATA41#

SDATA42#

SDATA43#

MD51

MD52

MD53

AC21

AD22

MMD52

MMD54

MMD53

SDATA#45

SDATA#46

G26

G25

J21

SDATA44#

SDATA45#

MD54

MD55

AF22

AE23

AD23

MMD55

MMD56

SDATA#48

SDATA#47

H26

J23

SDATA46#

SDATA47#

SDATA48#

MD56

MD57

MD58

AF24

AE25

MMD57

MMD58

AD20

AD21

AD22

M1647 North Bridge (1/2)

SDATA#49

SDATA#50

SDATA#51

M25

K21

K23

SDATA49#

SDATA50#

MD59

MD60

AD26

AC25

AB24

MMD61

MMD59

MMD60

1 2

1 2

1 2

SDATA#52

SDATA#53

L23

M24

SDATA51#

SDATA52#

SDATA53#

MD61

MD62

MD63

AA23

AA26

MMD63

MMD62

R985

10K-0402

R987

10K-0402

R990

10K-0402

SDATA#54

M23

SDATA#57

SDATA#55

SDATA#56

M22

H25

SDATA54#

SDATA55#

SDATA56#

DQM0

DQM1

AC15

AF15

CAS#0

CAS#1

CAS#2

SDATA#58

SDATA#59

J25

J24

SDATA57#

SDATA58#

DQM2

DQM3

AE16

AD17

CAS#4

CAS#3

+3VS

+3VS

+3VS

SDATA#60

K26

K24

SDATA59#

SDATA60#

DQM4

DQM5

AE15

AD16

CAS#5

SDATA#63

SDATA#61

SDATA#62

C21

E17

B24

D21

H23

F25

N26

SCHECK0#

SCHECK1#

SCHECK2#

SCHECK3#

SCHECK4#

SCHECK5#

AGPDEVSEL#

K25

SCHECK6#

AGPFRAME#

AGPIRDY#

AGPTRDY#

AGPSTOP#

TYPEDET#

AD_STB0#

AD_STB1#

L22

L26

SDATA61#

SDATA62#

M26

SDATA63#

AGP Interface

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS0

AB25

DQS1

AD25

DQS2

AF21

AC18

AF14

DQS4

DQS3

R986

1 2

10K-0402

R988

1 2

10K-0402

R991

1 2

10K-0402

DQS7

AE11

AF7

AE4

DQS5

DQS6

DQS7

CAS#[0..7] 11

MMD[0..63] 11

MMA[0..14] 11

RAS#[0..3] 11

RRMWEA# 11

SCAS#0 11

SRAS#0 11

AF16

CAS#6

DQM6

CAS#7

DQM7

AE17

AD23

AD26

AD27

H6

SCHECK7#

GCLK

U1

V3

V2

V1

W2

H3

GREQ#

G1

GGNT#

Y3

GSERR#

W1

AGPPAR

J2

PIPE#

G2

K2

WBF#

J1

RBF#

H1

ST0

H2

ST1

J3

ST2

U5

GCBE0#

Y2

GCBE1#

U2

GCBE2#

M5

GCBE3#

AB1

AD_STB0

AB2

R3

AD_STB1

P1

GAD0

W6

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

SB_STB

SB_STB#

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

U20A

+3VS

AE1

V4

AD1

V5

AD2

V6

AC1

AA1

U6

AA2

T4

AA3

T5

Y1

R5

R4

U3

P5

T1

N4

T2

N5

R1

L4

P2

L5

P3

K4

N1

K5

N2

L1

L2

K1

H4

L3

J6

M3

J5

M1

J4

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

CCKE0

CCKE1

CCKE2

CCKE3

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GSBA0

GSBA1

GSBA2

GSBA3

GSBA4

GSBA5

GSBA6

GSBA7

RP70 8P4R-10K

RP71 8P4R-10K

Strapping Pin Set: 7C

+3VS

AD28

1 2

+3VS

Compal Electronics, inc.

Title

SCHEMATIC, M/B LA-736/736B/736C

Size Document Number Rev

401168

Date: Sheet

Near M1647

R472

33

ACNBG

C679

10PF

Modify by 4/10 Tunning Time

1 8

2 7

3 6

4 5

1 8

2 7

3 6

4 5

CKE0 12

CKE1 12

CKE2 13

CKE3 13

+3VS

R989

10K-0402

LA-736B : R472 USE 0 Ohm

AGPCLK_NB 7

GFRAME# 8

GIRDY# 8

GTRDY# 8

GDEVSEL# 8

GSTOP# 8

GREQ# 8

GGNT# 8

GSERR# 8

GPAR 8

PIPE# 8

2X AGP

WBF# 8

4X AGP NEED PULL LOW

RBF# 8

ST0 8

ST1 8

ST2 8

GC/BE#0 8

GC/BE#1 8

GC/BE#2 8

GC/BE#3 8

AD_STBA 8

AD_STBA# 8

AD_STBB 8

AD_STBB# 8

GAD[0..31] 8

R998

AD6

1 2

10K-0402

R999

AD7

1 2

10K-0402

R1000

AD8

1 2

10K-0402

R1001

AD9

1 2

10K-0402

R1002

AD10

1 2

AD6~10,12,24,25,29~31

strapping for C3

GSBA[0..7] 8

10K-0402

SBSTB 8

SBSTB# 8

R1003

AD12

1 2

10K-0402

R1004

AD24

1 2

@10K-0402

R1005

AD25

1 2

@10K-0402

R1006

AD29

1 2

10K-0402

R1007

AD30

1 2

10K-0402

R1008

AD31

1 2

@10K-0402

R1026

AD30

1 2

@2.2K-0402

R1025

AD31

1 2

2.2K-0402

RESERVE BY 2/19

545Monday, September 10, 2001

of

+VDDQ

R475

10K

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

1F

Page 6

M1647 North Bridge (2/2)

+VDDQ

VREF_GC8

R515

+VCC_2.5

R517

Near M1647

+CPU_CORE

Near M1647

Modify By 6/5/2001

4.7

4.7

R520

4.7_0805

C715

1000PF

C681

1000PF

C690

1000PF

VDDPM_CPU1

C716

0.1UF

+VDDQ

AGP 2X

+CPU_CORE

C742

0.1UF

150_1%

+VCC_2.5

VDDPM_AGP1

C682

0.1UF

VDDPM_AGP2

C691

0.1UF

+VCC_2.5

R521

4.7_0805

VDDPM_CPU2

C717

C718

1000PF

0.1UF

LA-736B :R522 USED 270_1% ;

R23 USED 180_1%

AGP 2X,R522,R523 USE 270 1%,180 1%

R522

AGP 4X,R522,R523 USE 100 1%,100

1.5K_1%

1%

R523

C730

C731

1000PF

1K_1%

0.1UF

Near M1647

10 MILES

R526100_1%

R527

C743

1000PF

C744

C732

0.1UF

Near M1647

R516

4.7_0805

R518

CHB2012B800_0805

R519

4.7

Near M1647

R936 @0

Close the Node

1000P

VREF_CPU

C683

1000PF

C692

1000PF

C694

1000PF

C684

0.1UF

C693

0.1UF

+CPU_CORE

C695

0.1UF

+VCC_2.5

+VDDQ

+3V

+3V

+3V

+5V

+VDDQ

R524 150 1%_0805

Change Value by tunning

+CPU_CORE

R525 120 1%_0805

Change Value by tunning

R528 10K-0402

R529 10K-0402

R530 10K-0402

AVDD_MEM

AVDD_CPU

AVDD_AGP

VCC_CORENB

VCC2_5NB

VCC_AGPNB

3V_DRAMNB

3V_PCINB

3V_DRAMNB

VCC_DRAMNB

SENSE_AGP

VDDPM_AGP1

VDDPM_AGP2

VREF_AGP

SENSE_CPU

VDDPM_CPU1

VDDPM_CPU2

VREF_MEM1

VREF_MEM2

VREF_MEM3

AC10

AC11

AC13

AC16

AC19

AB20

AC22

AB23

AB13

AA20

AA21

W22

W23

T22

T23

D12

D15

E18

E21

D23

B25

G22

K22

N23

N24

T21

K10

K11

K16

K17

L10

L17

T10

T17

U10

U11

U16

U17

AB4

AC3

AC7

E10

L21

F16

F11

AA4

AA5

AA6

U23

U22

V23

V22

P23

D14

F21

P22

E14

AA7

AB6

H5

G4

M4

P4

U4

W4

W5

E4

D5

E7

L6

T6

F7

Y6

Y5

K6

Y4

AVDD_MEM

VDDPL_MEM

AVDD_CPU

M1647-SDR

VDDPL_CPU

AVDD_AGP

Power

VDDIO_S2K

VDDIO_S2K

VDDIO_S2K

VDDIO_S2K

VDDIO_S2K

VDDIO_S2K

VDDIO_S2K

VDDIO_S2K

VDDIO_S2K

VDDIO_S2K

VDDIO_S2K

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDDIO_AGP

VDDIO_AGP

VDDIO_AGP

VDDIO_AGP

VDDIO_AGP

VDDIO_AGP

VDDIO_AGP

VDDIO_AGP

VDDIO_MEM

VDDIO_MEM

VDDIO_MEM

VDDIO_MEM

VDDIO_MEM

VDDIO_MEM

VDDIO_MEM

VDDIO_MEM

VDDIO_MEM

VDDIO_PCI

VDDIO_PCI

VDDIO_PCI

VDDIO_PCI

VDDPD_S2K

VDDPD_S2K

VDDPD_AGP

VDDPD_AGP

VDD5V

VDD5V

SENSE_AGP

VDDPM1_AGP

VDDPM2_AGP

GNDPM

VREF_AGP

VREF_AGP

SHLD_AGP

SENSE_CPU

VDDPM1_CPU

VDDPM2_CPU

GNDPM

VREF_CPU

VREF_CPU

VREF_CPU

SHLD_CPU

SHLD_CPU

VREF_MEM

VREF_MEM

VREF_MEM

SHLD_MEM

SHLD_MEM

GNDPL

GNDPL

AGND

AGND

AGND

AA22

R23

R22

Y22

G5

B13

GND

C16

GND

C19

GND

C22

GND

C24

GND

A26

GND

E24

GND

H24

GND

L24

GND

P24

GND

U24

GND

W24

GND

W25

GND

AC4

GND

AD6

GND

AD9

GND

AD12

GND

AD15

GND

AD18

GND

AD21

GND

AA24

GND

AD24

GND

AF26

GND

G3

GND

K3

GND

M2

GND

N3

GND

R2

GND

T3

GND

W3

GND

AB3

GND

AC2

GND

AF1

GND

A1

GND

C6

GND

L12

G/T

L13

G/T

L14

G/T

L15

G/T

L16

G/T

M11

G/T

M12

G/T

M13

G/T

M14

G/T

M15

G/T

M16

G/T

N11

G/T

N12

G/T

N13

G/T

N14

G/T

N15

G/T

N16

G/T

P16

G/T

P15

G/T

P14

G/T

P13

G/T

P12

G/T

P11

G/T

T16

G/T

T15

G/T

T14

G/T

T13

G/T

T12

G/T

T11

G/T

R16

G/T

R15

G/T

R14

G/T

R13

G/T

R12

G/T

R11

G/T

L11

G/T

K12

G/T

K13

G/T

K14

G/T

K15

G/T

U12

G/T

U13

G/T

U14

G/T

U15

G/T

M10

G/T

M17

G/T

N10

G/T

N17

G/T

P10

G/T

P17

G/T

R10

G/T

R17

G/T

3V_PCINB

12

+

C685

22UF_10V_1206

3V_DRAMNB

12

+

C696

47UF_6.3V_B

VCC2_5NB

12

+

C1165

22UF_10V_1206

VCC_CORENB

12

+

C719

22UF_10V_1206

VCC_CORENB

C727

0.1UF

VCC_AGPNB

12

+

C733

47UF_6.3V_B

VCC_AGPNB

C745

0.1UF

C686

1000PF

C687

0.1UF

C688

1000PF

C689

0.1UF

PLACE NEAR M1647

C697

0.1UF

C698

1000PF

C699

0.1UF

PLACE NEAR M1647

C707

0.1UF

C708

1000PF

C709

0.1UF

C710

1000PF

PLACE NEAR M1647

C721

0.1UF

C722

1000PF

0.1UF

C720

1000PF

C723

PLACE UNDER M1647 SOLDER SIDE

C728

1000PF

PLACE NEAR M1647

C734

0.1UF

C735

1000PF

C736

0.1UF

PLACE ON M1647 SOLDER SIDE

C746

1000PF

C747

0.1UF

C748

1000PF

C700

1000PF

C737

1000PF

C701

0.1UF

C711

0.1UF

C724

1000PF

VCC_DRAMNB

C729

0.1UF

C738

0.1UF

C749

1000PF

C712

1000PF

C725

0.1UF

C703

C702

0.1UF

1000PF

VCC2_5NB

C713

0.1UF

PLACE ON M1647 SOLDER SIDE

C726

1000PF

C740

C739

0.1UF

1000PF

C704

1000PF

C714

1000PF

C741

1000PF

C705

0.1UF

C706

1000PF

NOTE : R524,R525 Value

depend on PCB impedance X 3

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

126

A

M1647 NORTHBRIDGE

35x35mm

528 BALLS

AF

TOPSIDE VIEW

U20B

Compal Electronics, inc.

Title

SCHEMATIC, M/B LA-736/736B/736C

Size Document Number Rev

401168

Date: Sheet of

645Monday, September 10, 2001

1F

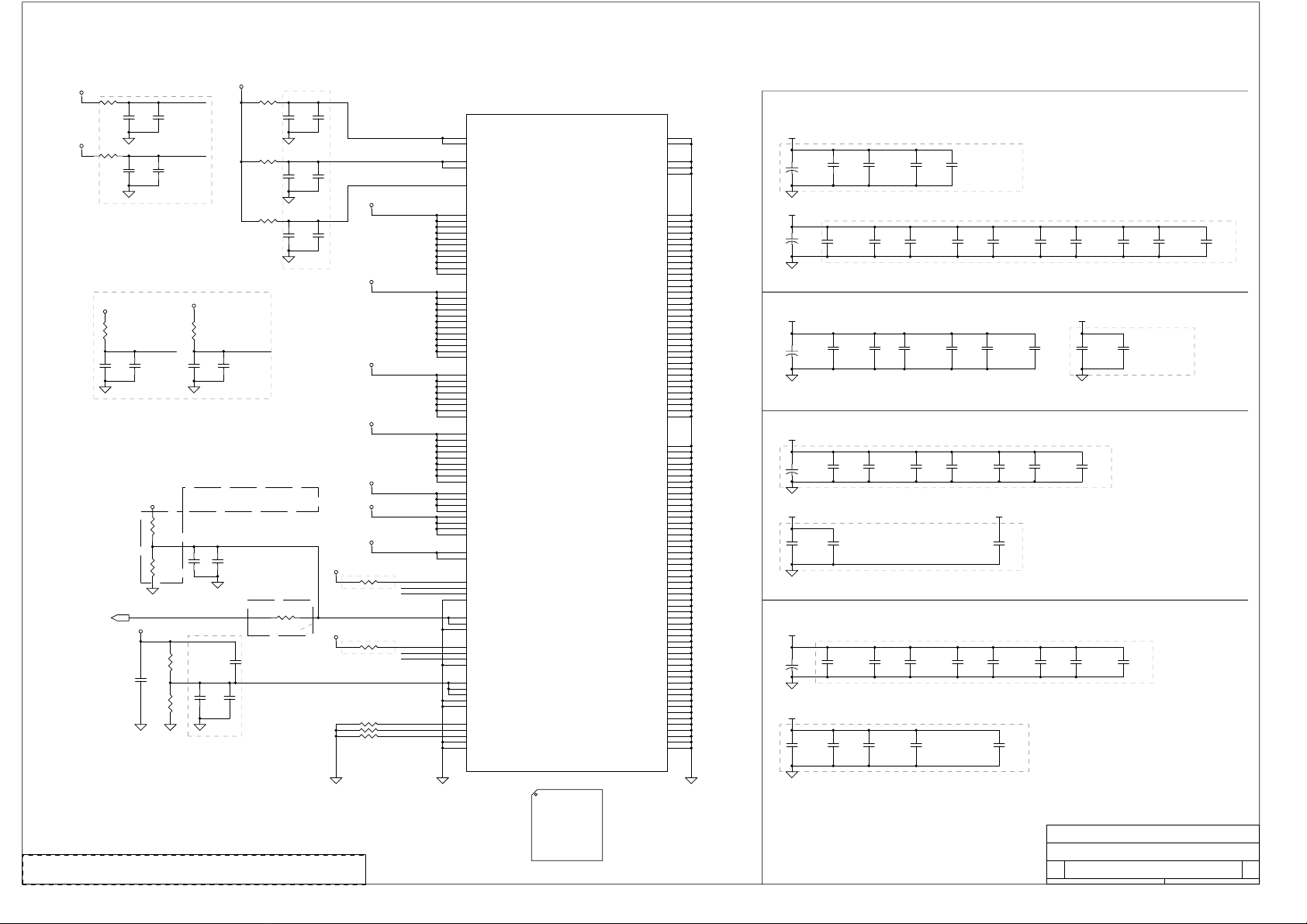

Page 7

PLACE NEAR CLOCK GENERATOR

+3VS

L1

1 2

CHB3216U121_1206

VDD3_3

C750

22UF_10V_1206

C751

.1UF

FOR S1 FUNCTION

PCI_STP#16

+3VS

Place close to CLK gen

RCPUCLK

RCPUCLK#

RCPUCLK_NB

C760 @22PF

C761 @22PF

C762 @22PF

16,24

C1170

.01UF

C752

.1UF

CPU_STP#

R935 10K

+3VS

C1171

.01UF

R551 0

R552 0

R553 @0

R554 @0

C753

.1UF

C1172

.01UF

D12

21

RB751V

R934 10K

C754

.1UF

+3VS

1 8

C1173

.01UF

2 7

3 6

SCK_CLK12

SDA_CLK12

4 5

C755

.1UF

RP8

8P4R-10K

C1174

.01UF

RP9

1 8

2 7

3 6

4 5

8P4R-10K

Place close to CLK

gen and series

terminator

Note : S0 ~ S1 & CPU ON C0~C3,THE CPU CLOCK CAN'T STOPPED

C756

.1UF

C1175

.01UF

FS3

FS2

FS1

FS0

Clock Generator

U21

6

VDD

8

C757

.1UF

MODE

R550

10K

VDD

17

VDD

21

VDD

28

VDD

35

VDD

40 39

VDD SDRAM2

1

DG_STOP#

3

GND

11

GND

16

GND

23

GND

29

GND

34

GND

41

GND

48

GND

25

SDRAM12

26

SDRAM11

27

SDRAM10/PCI_STOP#

18

MODE/PCICLK3

24

SCLK

44

SDATA

4 5

X1 X2

Y1

C758

10PF

1 2

XTAL-14.318MHZ

CLOCK FREQUENCY TABLE

FS3 FS2 FS1 FS0 CPU SDRAM PCICLK AGP SPREAD

0 0 1 1 100.00 100.00 33.33 66.66

0 1 0 0 100.00 133.33 33.33 66.66

1 0 1 1 100.00 100.00 33.33 66.66

1 1 0 0 100.00 133.33 33.33 66.66

CPUCLKT0

CPUCKLC0

CPUCLKT1

SDRAM0

SDRAM1

SDRAM3

SDRAM4

SDRAM5

SDRAM6

SDRAM7

SDRAM8

SDRAM9

FS1/AGP0

FS2/PCICLK_F

PCICLK0

PCICLK1

PCICLK2

PCICLK4

PCICLK5

FS3/48MHZ

FS0/REF0

ICS9248AF-171

Place close

to CLK gen

RCPUCLK

47

RCPUCLK#

46

RCPUCLK_NB

45

RDCLK_NB

43

RDCLK0

42

RDCLK1

RDCLK2

38

RDCLK3 CLK_SDRAM3

37

36

33

32

31

30

FS1

9

RAGPCLK

10

AGP1

PD#

FS2

12

13

RPCLK_PCM

14

RPCLK_MINI

15

RPCLK_AUD PCLK_AUD

19

20

FS3

22

7

2

XOUTXIN

C759

10PF

R531 10

R532 10

R533 0

R534 22

R535 22

R536 22

R537 22

R538 22

Change Kenny

5/31/2001

R539 22

R540 22

R541 33

R542 22

R543 22

R544 33

R545 22

R546 22

R547 22

R548

1 2

22

R549

1 2

0-0402

0 ~ 0.5% DOWN SPREAD

0 ~ 0.5% DOWN SPREAD

VR_POK 29,32

+/- 0.25 %

+/- 0.25 %

CPUCLK

CPUCLK#

CPUCLK_NB

DCLK_NB

CLK_SDRAM0

CLK_SDRAM1

CLK_SDRAM2

AGPCLK_NB

GCLK_O

PCLK_NB

PCLK_1535

PCLK_PCM

PCLK_MINI

48M

14MOSCFS0

14MTV

CPUCLK 3

CPUCLK# 3

CPUCLK_NB 5

DCLK_NB 5

CLK_SDRAM0 12

CLK_SDRAM1 12

CLK_SDRAM2 13

CLK_SDRAM3 13

AGPCLK_NB 5

GCLK_O 8

PCLK_NB 5

PCLK_1535 15

PCLK_PCM 19

PCLK_MINI 18

PCLK_AUD 26

48M 15

14MOSC 16

14MTV 10

LCL

Place these component near middle of

DICLK#0

DICLK#1

trace.

L44 10nH

L48 10nH

L50 10nH

C1196

5PF

L45 10nH

L49 10nH

L51 10nH

C1197

5PF

12

12

12

C1195

5PF

DICLK_NB#0

12

DICLK_NB#1

12

AICLK_NB#

12

No data traces should be routed

within 20mil of the L.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

DICLK_NB#0 5

DICLK_NB#1 5

AICLK_NB# 5

DICLK#[0..3]3

AICLK#3

Place these component near middle of

trace.

DICLK#2

DICLK#3

L42 10nH

L46 10nH

12

12

C1193

5PF

C1194

5PF

L43 10nH

L47 10nH

DICLK_NB#2

12

DICLK_NB#3

12

Compal Electronics, inc.

Title

Size Document Number Rev

Date: Sheet

DICLK_NB#2 5

DICLK_NB#3 5

SCHEMATIC, M/B LA-736/736B/736C

401168

745Monday, September 10, 2001

1F

of

Page 8

JP8

R578

@0

R580

@1K 1%

12

34

56

78

910

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

41 42

43 44

45 46

47 48

49 50

51 52

53 54

55 56

57 58

59 60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79 80

CONT-80P

VREF_CG

PID0 16

PID1 16

PID2 16

PID3 16

AGP_STP# 5,15

GSERR# 5

+5V

+3V

ENVEE 25

BKOFF# 24

DISPOFF# 23

GPIO0_VGA

+12VS

+3VS

+5VS

+VDDQ

VREF_CG

VREF_GC

+3V

12

C778

10UF_10V_1206

+VDDQ

12

C780

10UF_10V_1206

VREF_GC 6

M_SEN#9,24

CRTGND9

CRTGND9

HSYNC9

VSYNC9

DDC_DATA9,10

DDC_CLK9,10

TVD[0..7]10

G9

R9

B9

SUS_STAT#5,15,16

VGA_SUSP#24

SUSP30

CLKRUN#14,15,18,19

DEV_RST#10,19,20

PIRQC#14,15,26

PIRQB#14,15,18,19

PIRQA#14,15,19

DAC_CONTR24

M_SEN#

CRTGND

G

R

B

CRTGND

HSYNC

VSYNC

DDC_DATA

DDC_CLK

AGP_BUSY#

TVD[0..7]

12

C781

@560PF

R574

@75 1%

R579

@75 1%

12

C782

@560PF

TVHS

TVVS

TVD7

TVD6

TVD5

TVD4

TVD3

TVD2

TVD1

TVD0

R572

@1K 1%

TVCLK10

TVHS10

TVVS10

+VDDQ

G_VREF1

G_VREF2

ST[0..2]GAD[0..31] GSBA[0..7]

GPAR5

GFRAME#5

GIRDY#5

GTRDY#5

GDEVSEL#5

GREQ#5

GGNT#5

GSTOP#5

SBSTB5

RBF#5

GC/BE#35

AD_STBB5

GC/BE#25

GPAR

GFRAME#

GIRDY#

GTRDY#

GDEVSEL#

GREQ#

GGNT#

GSTOP#

GSBA5

GSBA6

GSBA4

GSBA7

SBSTB

ST15

RBF#

GAD25 GAD1

GAD30

GAD24

GAD29

GC/BE#3

GAD26

GAD31

GAD27

GAD28

GAD23

GAD17

GAD20

GAD16

GC/BE#2

GAD18

GAD22

GAD21

GAD19 GAD9

GREQ#5

PCIREQ#5

GSBA[0..7]5ST[0..2]5GAD[0..31]5

JP9

79 80

77

78

75

76

73

74

71

72

69

70

67

68

65

66

63

64

61

62

59 60

57 58

55 56

53 54

51 52

49 50

47 48

45 46

43 44

41 42

39 40

37 38

35 36

33 34

31 32

29 30

27 28

25 26

23 24

21 22

19 20

17 18

15 16

13 14

11 12

910

78

56

34

12

CONT-80P

+3V

R577

10K

AGP_BUSY#

1

2

D14

@RB751V

3

D15 @RB717F

R581

0

AD_STBA#

AD_STBB#

PIPE#

SBSTB#

WBF#

GCLKO

GSBA3

GSBA0

GSBA1

GSBA2

ST0ST1

ST2

GAD4

GAD2

GAD3

GC/BE#0

GAD0

GAD7

GAD5

GAD6

GAD8

GAD13

GAD12

GAD10

GC/BE#1

GAD15

GAD11

GAD14

+3VS

21

R575

10K

AD_STBA# 5

AD_STBB# 5

PIPE# 5

SBSTB# 5

RTCCLK 5,16,20

WBF# 5

ST0 5

ST2 5

GC/BE#0 5

AD_STBA 5

GC/BE#1 5

GGREQ# 16AGP_BUSY#5,15

GCLKO

12

GCLK_O 7

C779

@22PF

AGP BUS PULL/DOWN RESISTER

GFRAME#

GIRDY#

GTRDY#

GDEVSEL#

GSTOP#

GREQ#

GPAR

RBF#

PIPE#

GGNT#

WBF#

GSERR#

ST2

AD_STBA

AD_STBB

SBSTB

AD_STBA#

AD_STBB#

SBSTB#

R555 8.2K

R556 8.2K

R557 8.2K

R558 8.2K

R559 8.2K

R560 8.2K

R561 8.2K

R562 8.2K

R563 8.2K

R564 8.2K

R565 8.2K

R566 8.2K

R567 8.2K

R568 8.2K

R569 8.2K

R570 8.2K

R571 8.2K

R573 8.2K

R576 8.2K

+VDDQ

+VDDQ

Change by 8/28/2000 ALI Suggest

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

Compal Electronics, inc.

Title

SCHEMATIC, M/B LA-736/736B/736C

Size Document Number Rev

401168

Date: Sheet

845Monday, September 10, 2001

of

1F

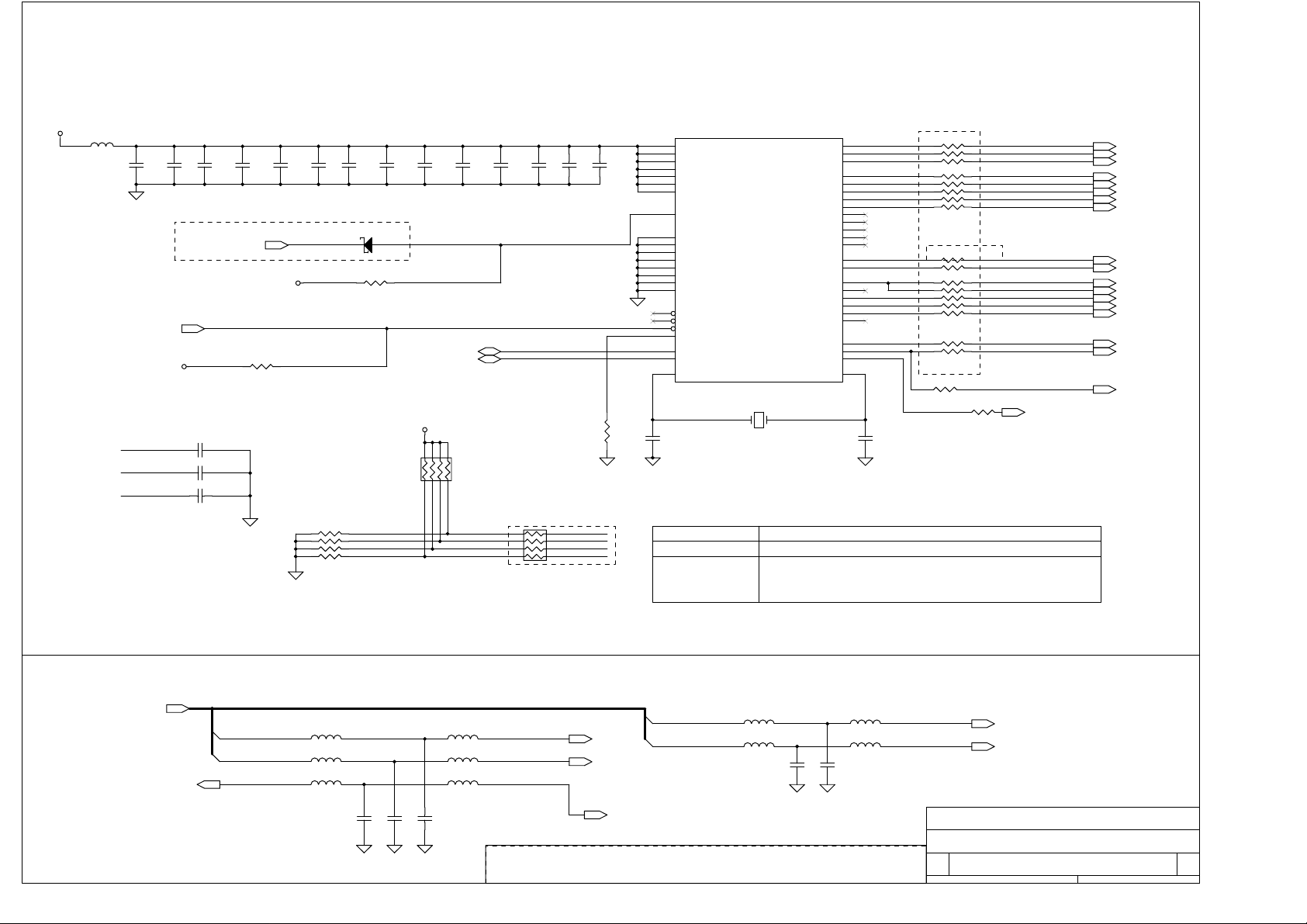

Page 9

CRTVDD

1

D18

DAN217

2

CRT Connector

R8

G8

B8

L6

CRTGND8

12

0_0805

R

G

B

R585

1 2

+12VS

R586

75

75

1 2

R584

75

HSYNC8

VSYNC8

C785

10PF

1 2

HSYNC

2N7002

VSYNC

R588

1 2

0

C786

C787

12

12

10PF

10PF

D

S

13

Q55

G

S

2

L2

1 2

CB-2012D-800T_0805

L3

1 2

CB-2012D-800T_0805

L4

1 2

CB-2012D-800T_0805

12

D

13

Q57

G

2N7002

2

R589

@10K

CB-1608D-121T

1 2

1 2

12

C788

10PF

L5

1 2

CB-1608D-121T

L7

1 2

R590

@10K

CRTVDD

1

D19

DAN217

2

3

12

C789

10PF

12

C794

68PF

1

D20

DAN217

2

3

12

C790

10PF

12

C795

68PF

+5VS

3

12

D16

2 1

RB491D

M_SEN#8,24

C791

100PF

220PF

C792

C783

.1UF

12

D17

CRTVDD +5VALW

R582

2.2K

C793

220PF

12

12

+12VS

R583

2.2K

6

11

1

7

12

2

8

13

3

9

14

4

10

15

5

Q56

2N7002

R587

1 2

0

12

JP10

CRT-15P

D

1 3

2

G

C784

68PF

D

1 3

S

12

12

1

2

DAN217

S

G

DDC_DATA

Q54

2N7002

DDC_CLK

3

2

DDC_DATA 8,10

DDC_CLK 8,10

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

Compal Electronics, inc.

Title

SCHEMATIC, M/B LA-736/736B/736C

Size Document Number Rev

401168

Date: Sheet

945Monday, September 10, 2001

of

1F

Page 10

R1009

@0

SDA_TV12

SCK_TV12

+3V

1 2

DDC_DATA8,9

DDC_CLK8,9

+5V +3VS

R591

@0

1 2

TVD[0..7]8

R592

0

Modify By 4/ 1 0 , F or Power Consumption

1 2

CB-1608D-121T

1 2

L8

12

C798

10UF_10V_1206

CB-1608D-121T

1 2

12

C801

10UF_10V_1206

R597 0

R598 0

12

C799

10UF_10V_1206

L9

12

C802

10UF_10V_1206

CLK_GND CLK_GND

R593 @0

1 2

R594 @0

1 2

1 2

1 2

Modify by 11/03/2K

USE VGA DIRECTORY

TVCLK8

TVHS8

TVVS8

TVCLK

TVHS

TVVS

TVD[0..7]

Modify By 4/10,For Power Consumption

DACVDD

C800

.1UF

1 2

DAC_GNDDAC_GND

TVCLK

CLKVDD

C803

.1UF

1 2

R595

1K

12

VLF

C808

560PF

1 2

CLK_GND

26

27

7

9

39

40

41

6

4

3

2

1

44

43

42

29

R604

10K

R1013

@0

Add R1009~R1013 for TVout leakage on C3

R605

@22

C817

@10PF

12

REV

TVCLK

TVHS

TVVS

TVD7

TVD6

TVD5

TVD4

TVD3

TVD2

TVD1

TVD0

DAC_GND

TVRST#

TVRST#

DVDD

SD

SC

D8/SUSP

D9

XCLK

HS

VS

D7

D6

D5

D4

D3

D2

D1

D0

SUBSTRATE

CLK_GND

12

12

R958

@0

CLKVDD

DACVDD

31

25

VDD

AVDD

AGND

GND

GND

34

19238

DAC_GND

+3VS

DEV_RST# 8,19,20

XTALO

14MTV2

C796

@27PF

12

VLF

51630

VLF

DGND

182836

DVDD

DGND

DVDD

DGND

Y2

1 2

12

@14.318MHZ

C804

.1UF

1 2

V5SF

CVBS/B

Y/R

C/G

CSYNC

DVDD

ADDR

XTALO

XTALI

D10

D11

D12

D13

D14

D15

IRSET

RESET#

TVXPRESS_LQFP

TVRST#

1 2

U22

C805

.1UF

38

20

22

21

17

35

37

33

32

10

11

12

13

14

15

24

TVRST#

12

C797

@10PF

CB-1608D-121T

1 2

12

10UF_10V_1206

DVDD

C811 .1UF

Stuff For

TVXpress

XTALO

14MTV2

REV

@22K

2 1

L10

C806

12

R5990

R600

22K

R603

560_1%

12

R1012

RB751V

D21

R606

@0

12

12

12

+3VS

+3V

R1010

R1011

@0

0

Modify By 4/10,For Power Consumption

1 2

1 2

12

C807

10UF_10V_1206

C812 .1UF

12

DVDD

14MTV 7

+3VS

12

+3V

Modify By 4/10, For Power

Consumption

DAC_GND

12

R601

ADD FOR TVXPRESS

SET "C0H/C1H"

12

R596

75

4.7K

Clean GND

required

PCIRST# 5,14,15,18..21,26

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C810

1 2

@27PF

L12

1 2

CB-1608D-121T

C815

@270PF

1 2

L13 CB-2012D-601T

1 2

DAC_GND

L14 CB-2012D-601T

1 2

CLK_GND

1 2

JP11

RCA JACK

DAC_GNDDAC_GNDDAC_GNDDAC_GND

C813

150PF

14MTV2

CB-1608D-121T

1 2

12

R602

@22

C816

@10PF

C809

1 2

47PF

L11

1 2

C814

270PF

CONFIGURATION

PART

TVXpress

R591

R599

R601

R603

C808

D21

R606

R958 OPEN STUFF

NOTE :CH7004 ADDR SET 76H BY PIN 29 "LOW"

STUFFR592

OPEN STUFF

STUFF

STUFF

560 1%

560PF

STUFF

OPEN

CH7004

OPEN

OPEN

360 1%

OPEN

OPEN

STUFF

NOTE

USE +3VSOPEN

USE +5VS

FOR TVXPRESS ADDR SET "C0H/C1H"

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

Compal Electronics, inc.

Title

SCHEMATIC, M/B LA-736/736B/736C

Size Document Number Rev

401168

Date: Sheet

10 45Monday, September 10, 2001

of

1F

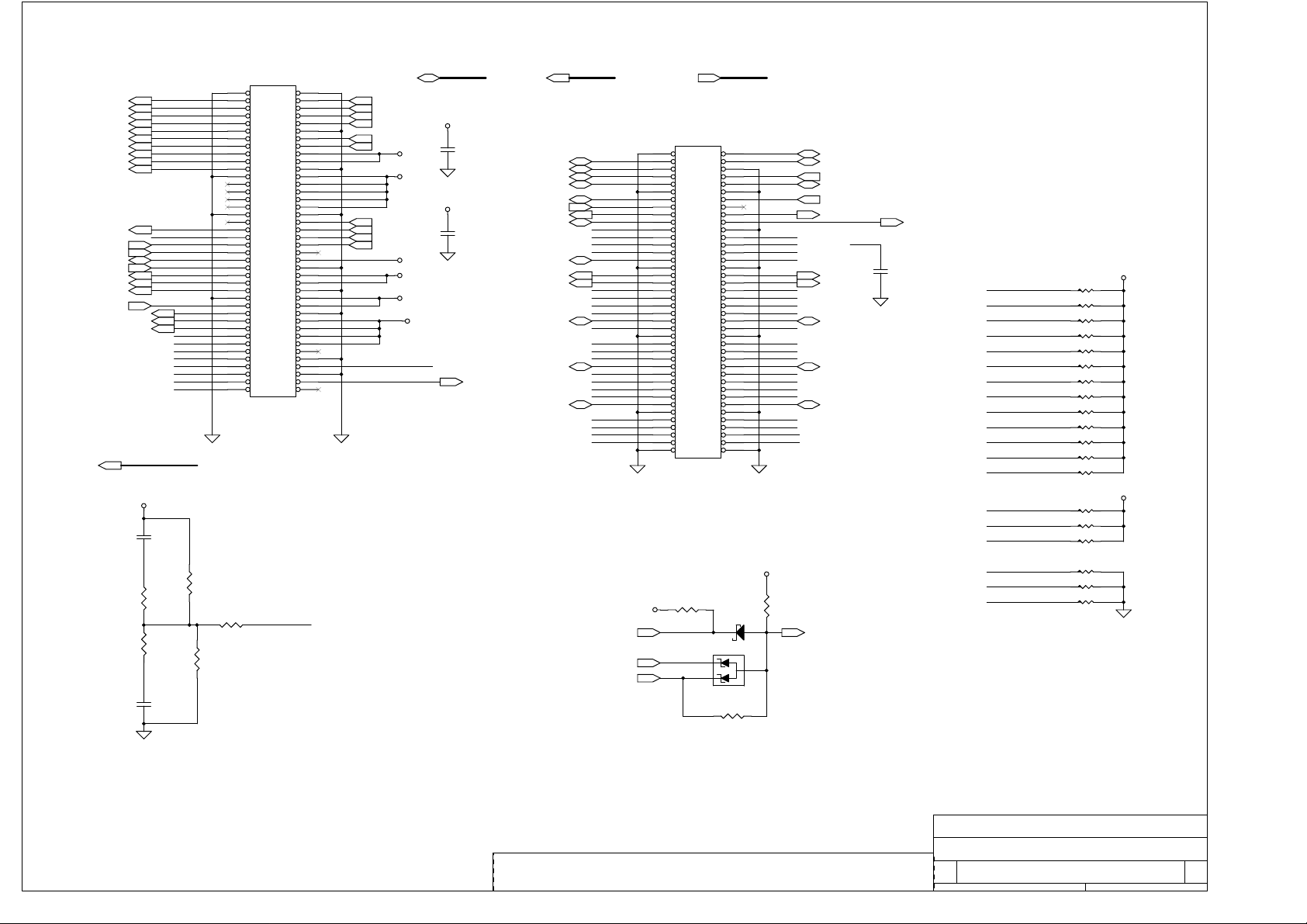

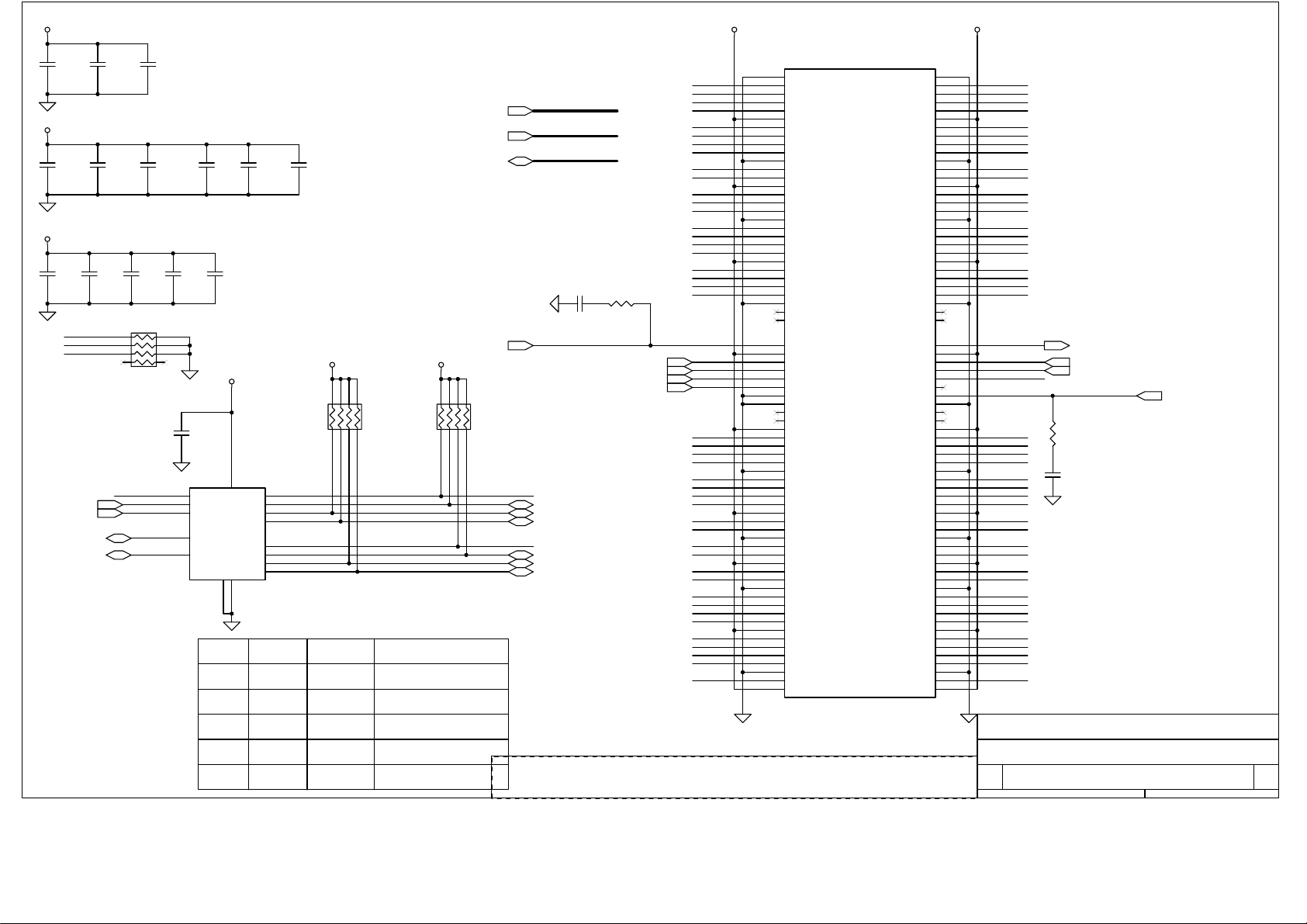

Page 11

MMA[0..14]5

MA[0..14]12,13

MMA[0..14]

MA[0..14]

MMD[0..63]5

MD[0..63]12,13

MMD[0..63]

MD[0..63]

MMD0

MMD1

MMD2

MMD3

MMD4

MMD5

MMD6

MMD7

MMD8

MMD9

MMD10

MMD11

MMD12

MMD13

MMD14

MMD15

MMD16

MMD17

MMD18

MMD19

MMD20

MMD21

MMD22

MMD23

MMD24

MMD25

MMD26

MMD27

MMD28

MMD29

MMD30

MMD31

16

15

14

13

12

11

10

16

15

14

13

12

11

10

16

15

14

13

12

11

10

16

15

14

13

12

11

10

RP10

16P8R-10

RP13

16P8R-10

RP16

16P8R-10

RP20

16P8R-10

MD0

1

MD1

2

MD2

3

MD3

4

MD4

5

MD5

6

MD6

7

MD7

89

MD8

1

MD9

2

MD10

3

MD11

4

MD12

5

MD13

6

MD14

7

MD15

89

MD16

1

MD17

2

MD18

3

MD19

4

MD20

5

MD21

6

MD22

7

MD23

89

MD24

1

MD25

2

MD26

3

MD27

4

MD28

5

MD29

6

MD30

7

MD31

89

MMD32

MMD33

MMD34

MMD35

MMD36

MMD37

MMD38

MMD39

MMD40

MMD41

MMD42

MMD43

MMD44

MMD45

MMD46

MMD47

MMD48

MMD49

MMD50

MMD51

MMD52

MMD53

MMD54

MMD55

MMD56

MMD57

MMD58

MMD59

MMD60

MMD61

MMD62

MMD63

16

15

14

13

12

11

10

16

15

14

13

12

11

10

16

15

14

13

12

11

10

16

15

14

13

12

11

10

RP11

16P8R-10

RP14

16P8R-10

RP17

16P8R-10

RP21

16P8R-10

MD32

1

MD33

2

MD34

3

MD35

4

MD36

5

MD37

6

MD38

7

MD39

89

MD40

1

MD41

2

MD42

3

MD43

4

MD44

5

MD45

6

MD46

7

MD47

89

MD48

1

MD49

2

MD50

3

MD51

4

MD52

5

MD53

6

MD54

7

MD55

89

MD56

1

MD57

2

MD58

3

MD59

4

MD60

5

MD61

6

MD62

7

MD63

89

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS,INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION . THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS,INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS,INC.

RAS#[0..3]5

MMA0

MMA1

MMA2

MMA3

MMA4

MMA5

MMA6

MMA7

MMA8

MMA9

MMA10

MMA11

MMA12

MMA13

MMA14

RP12

16

15

14

13

12

11

10

16P8R-10

RP15

16

15

14

13

12

11

10

16P8R-10

CAS#05

CAS#15 RCAS#1 12,13

CAS#25

CAS#35

CAS#45

CAS#55

CAS#65

CAS#75

SRAS#05

RRMWEA#5

1

2

3

4

5

6

7

89

1

2

3

4

5

6

7

89

RAS#0

RAS#1

RAS#2

RAS#3

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

CAS#0

CAS#1

CAS#2

CAS#3

CAS#4

CAS#5

CAS#6

CAS#7

RP18

1 8

2 7

3 6

4 5

8P4R-10

RP19

1 8

2 7

3 6

4 5

8P4R-10

RP22

1 8

2 7

3 6

4 5

8P4R-10

RP23

1 8

2 7

3 6

4 5

8P4R-10

RCAS#0

RCAS#1

RCAS#2

RCAS#3

RCAS#4

RCAS#5

RCAS#6

RCAS#7

SRASA#SRAS#0

SCASA#SCAS#0

RRAS#0 12

RRAS#1 12

RRAS#2 13

RRAS#3 13

RCAS#0 12,13

RCAS#2 12,13

RCAS#3 12,13

RCAS#4 12,13

RCAS#5 12,13

RCAS#6 12,13

RCAS#7 12,13

SRASA# 12,13

SCASA# 12,13SCAS#05