Page 1

A

1 1

B

C

D

E

Compal Confidential

2 2

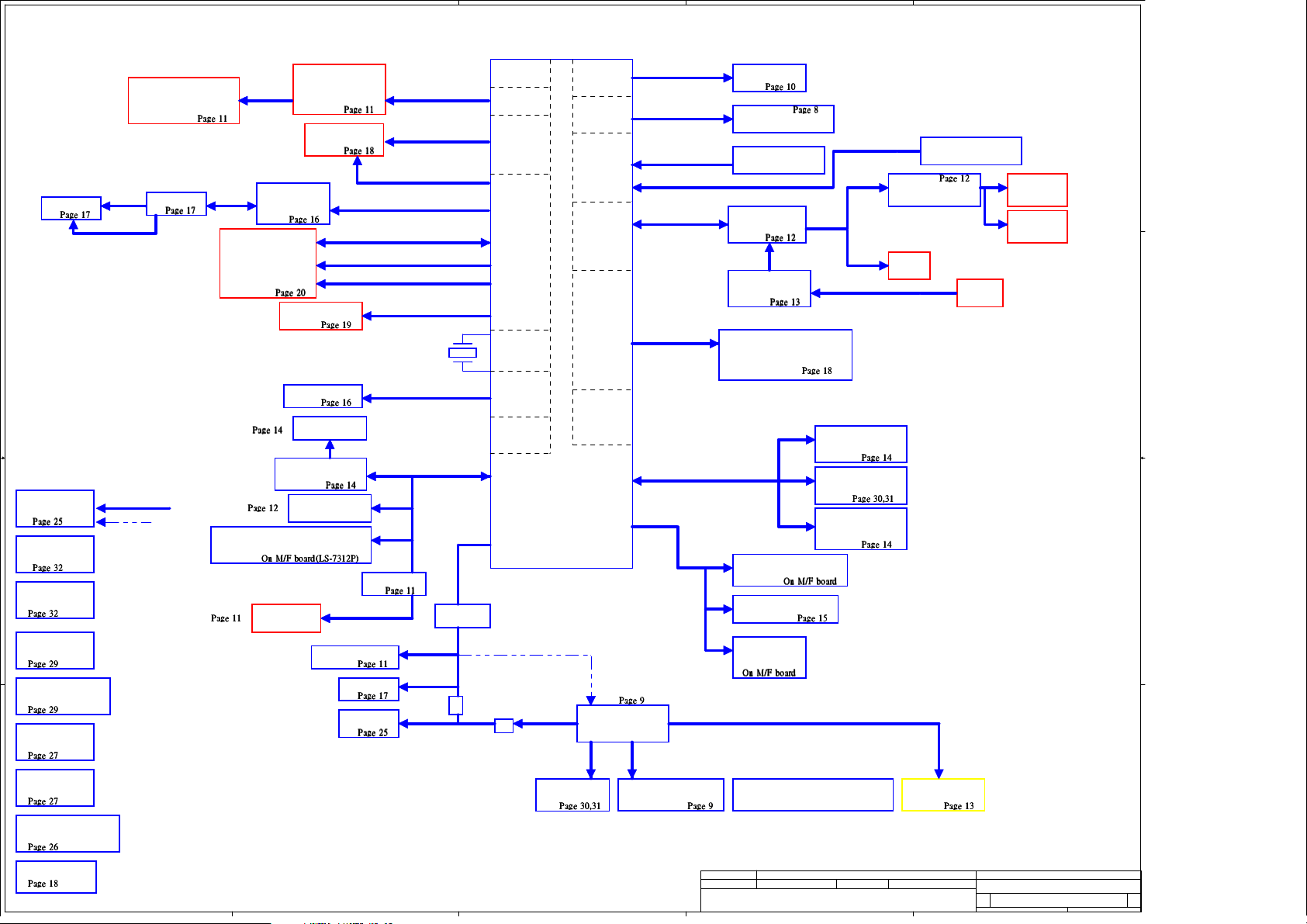

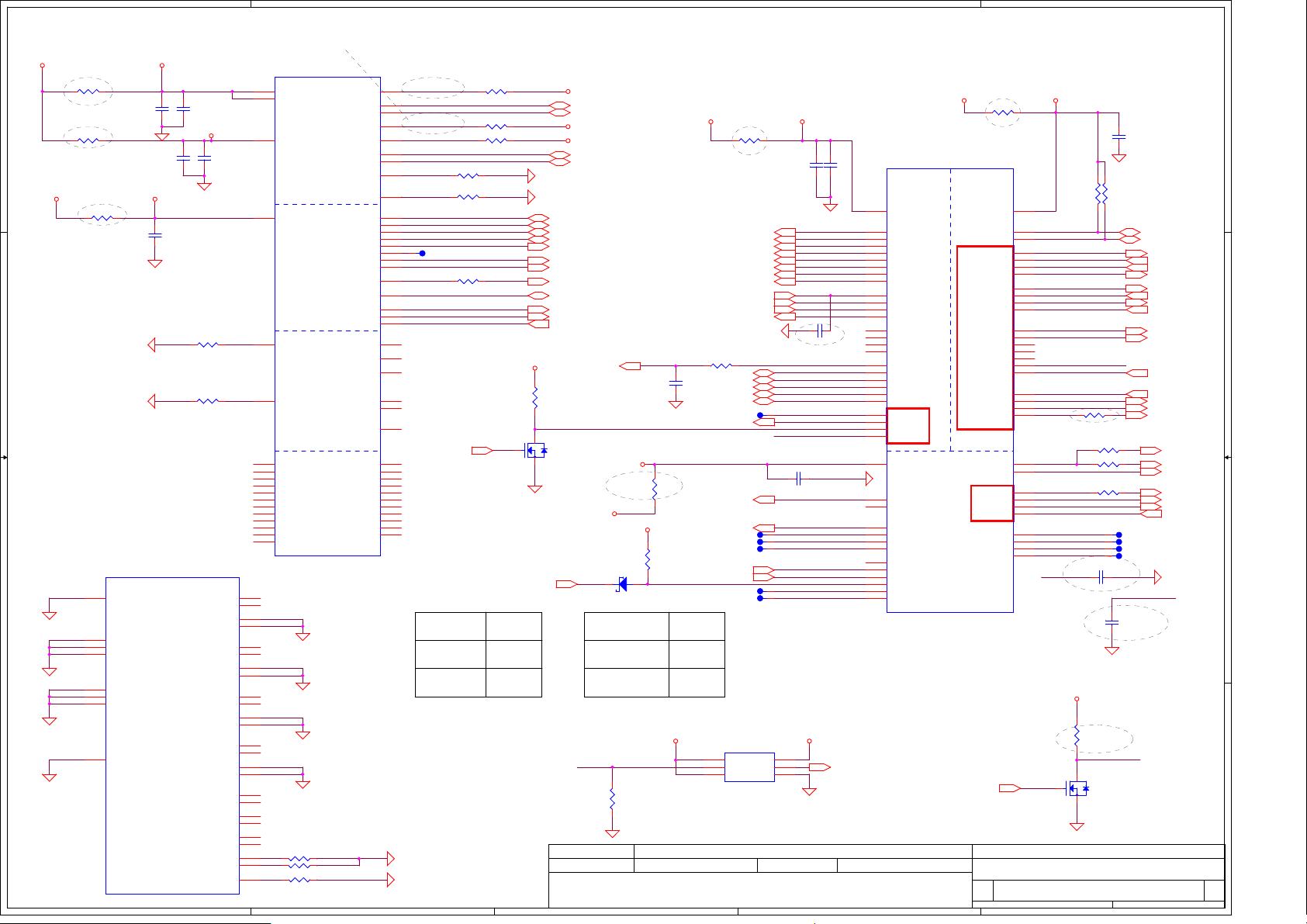

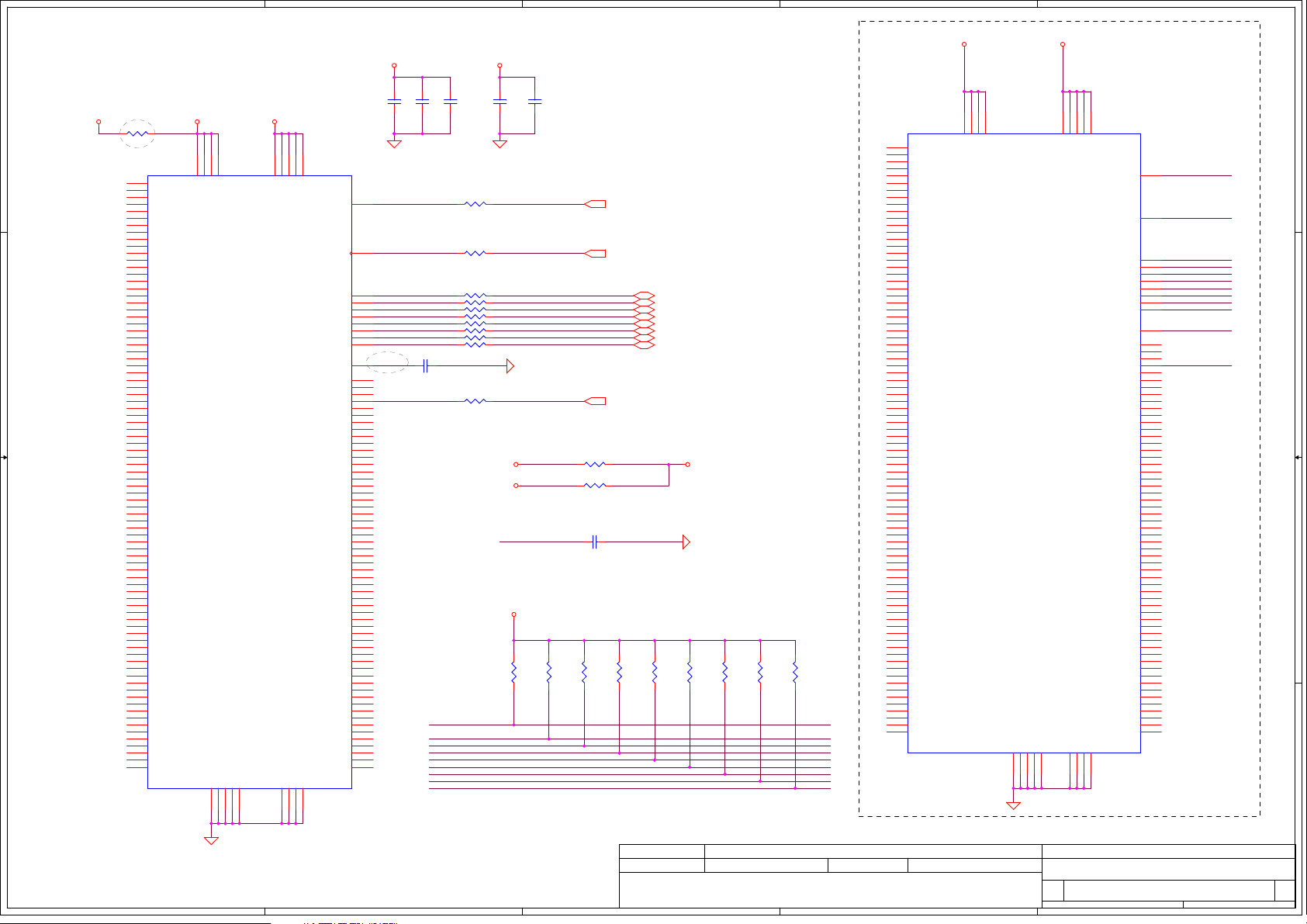

Schematics Document

NVDIA TEGRA 250 Platform

T20 + LPDDR2

3 3

LA-7311P

2011-02-24

REV:0.2

4 4

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Compal Secret Data

Deciphered Date

D

2010/11/052011/11/5

Title

Size Docume nt Number Re v

C

Date : Sheet of

Compal Electronics, Inc.

Cover Page

Thur sday, Februa ry 24, 2 011

LA-7311P

E

1

0.2

32

Page 2

A

B

C

D

E

LVDS bridge

10.1" LVDS panel

HSD HSD101PWW1

1 1

(1280 x 800)

P a g e

P a g e 1 1

P a g e P a g e

1 1

1 11 1

TI SN75LVDS83BZ

P a g e

P a g e 1 1

1 1

P a g e P a g e

1 11 1

HD MI Con n.

P a g e

P a g e 1 8

1 8

P a g e P a g e

1 81 8

RGB (1. 8V)

HD MI

U3H

U3G

U3I

VGA

LC D

HD MI

DDC _I2 C(5V)

ULP I t o U SB

1 7

1 71 7

P a g e

P a g e 1 1

P a g e P a g e

US B2

SM SC U SB3 315

WIF I / BT m odu le

Azu rewa ve N H-611

P a g e

P a g e 1 4

P a g e P a g e

P a g e

P a g e 1 2

1 2

P a g e P a g e

1 21 2

Lig ht Sen sor

Lit eon AL 300 0A

O n M / F b o a r d

O n M / F b o a r d ( L S - 7 3 1 2 P )

O n M / F b o a r dO n M / F b o a r d

1 1

1 11 1

Tou ch Screen

P a g e

P a g e 1 6

1 6

P a g e P a g e

1 61 6

P a g e

P a g e 2 0

2 0

P a g e P a g e

2 02 0

GPS Mod ule

BC M4 75 1

SDI O C ard Sl ot

Accele romete r

1 4

1 41 4

KX TF 9-4 100

GYR O

MP U- 3050

Au dio Cod ec

Wolfs on WM 890 3

( L S - 7 3 1 2 P )

( L S - 7 3 1 2 P )( L S - 7 3 1 2 P )

10.1" LVDS panel

P a g e

P a g e 1 9

1 9

P a g e P a g e

1 91 9

P a g e

P a g e 1 6

1 6

P a g e P a g e

1 61 6

P a g e

P a g e 1 4

1 4

P a g e P a g e

1 41 4

I2C LS- 731 3P

GEN 1_I 2C( 3.3V)

P a g e

P a g e 1 1

P a g e P a g e

3G car d

P a g e

P a g e 1 7

P a g e P a g e

BAT T

P a g e

P a g e 2 5

P a g e P a g e

ULP I (1 .8V)

SDI O1( 1.8 V)

DAP 4(1. 8V)

UAR T3 ( 1.8V )

UAR T2 ( 1.8V )

12 MHz

GEN 1_I 2C( 1.8V)

P a g e

P a g e 1 1

1 1

P a g e P a g e

1 11 1

1 1

1 11 1

1 7

1 71 7

2 5

2 52 5

SDI O3( 3.3 V)

GEN 2_I 2C( 1.8V)

I2 C L S

AP_ SMB (3. 3V)

R

@

U3J U3K

UL PI

SDI O1

UART

U3B

OS C,P LL,

key bo ard

U3NU3O

PCI e&S DIO

U3A

core & fu se

Nvidia Tegra T20

R

3G car d

1 7

1 71 7

AP_ SMB (3. 3V)

S IM

US B

SMBUS

P a g e

P a g e 1 7

P a g e P a g e

SIM ca rd

P a g e

P a g e 1 7

P a g e P a g e

2 2

BATT IN

P a g e

P a g e 2 5

2 5

P a g e P a g e

2 52 5

PANEL_ PWR_P

RT92 97GQW

P a g e

P a g e 3 2

3 2

P a g e P a g e

3 3

4 4

3 23 2

+1.8V /+1.2V

TPS6 2560DRVR*2

P a g e

P a g e 3 2

3 2

P a g e P a g e

3 23 2

+3V_3 G LDO

APL5916KAI

P a g e

P a g e 2 9

2 9

P a g e P a g e

2 92 9

+3V_ 3G

SY803 3BDBC*3

P a g e

P a g e 2 9

2 9

P a g e P a g e

2 92 9

+5VALWP

TPS61 030RSA R

P a g e

P a g e 2 7

2 7

P a g e P a g e

2 72 7

+3VALWP

TPS63 020DS JR

P a g e

P a g e 2 7

2 7

P a g e P a g e

2 72 7

CHARGER

SMB13 6ET-13 57Y_CSP30

P a g e

P a g e 2 6

2 6

P a g e P a g e

2 62 6

DC IN

P a g e

P a g e 1 8

1 8

P a g e P a g e

1 81 8

A

B

U3C

NAND Ctr l

U3D

DD R

U3E

U3F

MI PI

VI& DSI /CS I

U3L

AUDIO

U3M

USB + mini-B connector

U3P

U3Q

HSI C

ENE KBC KB930/

EC_SMB

IO3731 Co-Layout

EC_RESMUE

PM U

TI TPS 658 621

P a g

P a g e 3 0 , 3 1

P a gP a g

SPI ROM

MX 25 L1 005AM C-12 G

e 3 0 , 3 1 P a g e 9

e 3 0 , 3 1e 3 0 , 3 1

C

DDR 2 X 32 (1.2 V)

CSI A (1 .2V)

CSI B (1 .2V)

DAP 1(1. 8V)

US B

CAM _I2 C(1 .8V)

P a g e 9

P a g e 9

P a g e 9P a g e 9

SPI

Sa ndi sk 16 GeM MC

P a g e

P a g e 1 0

1 0

P a g e P a g e

1 01 0

P a g e 8

P a g e 8

P a g e

P a g e 1 2

P a g e P a g e

P a g e

P a g e 1 3

P a g e P a g e

O n M / F b

O n M / F b o a r d

O n M / F bO n M / F b

o a r d

o a r do a r d

1 2

1 21 2

P a g e 8P a g e 8

1 3

1 31 3

P a g e

P a g e 1 8

1 8

P a g e P a g e

1 81 8

Co mpa ss

AKM 8975 C

PM U

TI TPS 658 621

Tem pera tur e Se nso r

On Sem i N CT1 008

o a r d

o a r do a r d

P a g e

P a g e 1 5

1 5

P a g e P a g e

1 51 5

Compal Secret Data

D

P a g e

P a g e 1 4

P a g e P a g e

P a g

P a g e 3 0 , 3 1

P a gP a g

P a g e

P a g e 1 4

P a g e P a g e

Deciphered Date

e 3 0 , 3 1

e 3 0 , 3 1e 3 0 , 3 1

SPK R AMP

Rea lte k A LC 105- GR

HeadPhone

1 4

1 41 4

1 4

1 41 4

LPD DR2

51 2MB or 1 GB

5M CA MER A M odule

OV5 640

Audi o Co dec

Wolfs on WM 890 3

Ech o C ancel lati on

FM 201 8

Micr o US B ty pe A/B

Hos t/C lie nt/Cha rgi ng

PWR _I2 C(1 .8V )

1.3 M C AME RA Mod ule

OV9 740

5M CA MER A M odule

OV 564 0

LED FLAS H

LUW -FQ6N

O n M / F b

O n M / F b o a r d

O n M / F bO n M / F b

EC_SMB

PROX/ on M/F board(LS-7312P & LS-7314P)

P a g e 9 P a g e

P a g e 9P a g e 9

IQS128-00000TSR/

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1.3 M C AME RA Mod ule

OV9 740

P a g e

P a g e 1 2

P a g e P a g e

Analog MIC

Ech o C ancel lati on

FM 201 8

P a g e 1 3

P a g e P a g e

2010/11/052011/11/5

1 2

1 21 2

INT Sp eak er

INT Sp eak er

1 3

1 31 3

Compal Electronics, Inc.

Title

NVIDIA Vent ana System

Size Document Number Rev

Custo m

Date: Sheet of

Thurs day, F ebrua ry 24, 2011

E

2

32

0.2

Page 3

5

IME

_I2C

D D

4

3

2

1

Voltage Rails

Power Plane Desc ript ion

VIN

B+

+1.2VS_SM0

+1.0VS_SM1

+1.1VS_LDO1

+1.2VS_LDO2

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

CPU voltage f or CPU

AVDD_PLL p ower rail

T20 RT C power rail

PWR_I2C address

Device

PMU

E-Compass CAM ERA 1.3M

Temperature sensor

Addr ess

0110 100x b

1001 100x b

+1.8VS_LDO4 T20 system power rail

+3.3VS_LDO3

T20 US B power rail

+2.85VS_LDO5 Core voltage for EMMC

C C

+2.85VS_LDO6

+3.3VS_LDO7

+1.8VS_LDO8

+2.85VS_LDO9

+3VALW

+3VS

+5VALW

+1.8VS

Core voltage for CAMERA

T20 HDMI p ower rail

T20 HDMI PLL power rail

T20 DDR RX power rail

3.3V always on power rail

3.3V switched power rail for standby mode

5V alwa ys on power rail

1.8V always on power rail

1.8V switched power rail for standby mode+1.8VS_S3

GEN1_I2C

Device Addr ess

Aud io C odec

Light s ensor

Gyro

0011 010x b

1000 100x b

1101 000x b

GEN2_I2C AP_SMB

Addr essDevice

RTC po wer+3.3VS_RTC

EC_SMB

B B

Proximity Sensor

Echo Cancellation

BATT

Addr essDevice

1000 100x b

1100 000x b

CAM_I2C address

Device

CAM ERA 5M

Addr ess

0110 110x b

1001 000x b

TS_I2C

To uch Pane l

Device Addr ess

LCD

3G CARD

BATT

LED FLASH

Addr essDevice

0100 110x b

IME_I2C

Device Addr ess

G-sensor

0001 111x b

DDC_I2C

HDMI_DDC_I2C

Device Addr ess

HDMI EDID

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

Compal Secret Data

Deciphered Date

2010/11/052011/11/5

2

Title

Size Docu ment Numb er Re v

Cus tom

Dat e: Sheet o f

Thur sday, Feb ruary 24, 2011

1010 000x b

Compal Electronics, Inc.

Notes List

LA-7311P

3

1

0.2

32

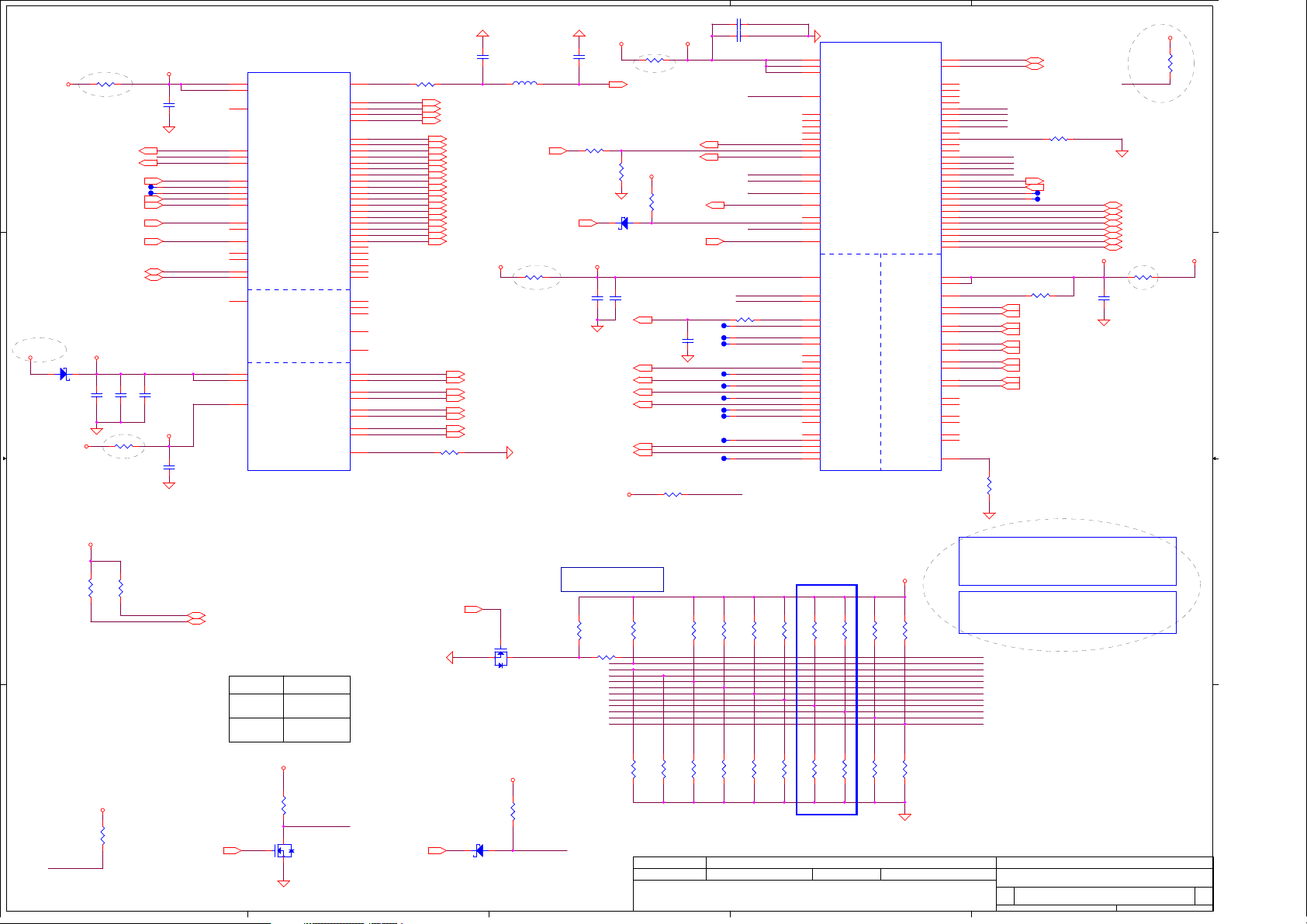

Page 4

5

Change to 0805_20110112.

+1.8VS

R107 0_0805_5%

D D

LVDS _SHTDN#[11]

EN_V DD_PNL[11 ]

GYRO _INT[14]

COMP ASS_DR DY[14]

TEMP_ALERT#[14]

HDMI _HPD_ R[18 ]

DDC _SCL_ R[18]

DDC _SDA_ R[18]

Change net name to meet power rail_20110111.

C C

+3.3VS_LDO7

RB751V -40 SOD-323

+AVDD_ HDMI

D15

2 1

+1.8VS_LDO8

R211 0_0805_5%

Change to 0805_20110112.

1

C11

2

12

ALS_INT[21]

1

2

2.2U_0 402_6.3VMZ

+VDDIO _LCD

C2

TP173

TP15

1

C1216

C12

2

0.1U_040 2_10V6K

+AVDD_HD MI_PLL

12

0.1U_040 2_10V6K

39P 5 0V J NP O 0402

1

2

1

2

80mA

SAR_ EN#

ACCE L_INT

EN_V DD_BL

ALS_INT

100mA

100mA

C13

0.1U_040 2_10V6K

U1D

1.8V 1.8V

U22

AD24

AA24

AB21

AC25

AA25

W25

AD23

AC24

AC23

W23

AH17

3.3V

AA15

1.8V

AA12

V22

Y24

U24

V24

V23

Y22

Y23

Y15

VDDIO_LCD1

VDDIO_LCD2

LCD_M1

LCD_PWR0

LCD_PWR1

LCD_PWR2

LCD_SCK

LCD_CS0#

LCD_CS1#

LCD_SDOUT

LCD_SDIN

LCD_DC0

LCD_DC1

HDMI_INT#

CRT_HSYNC

CRT_VSYNC

DDC_SCL

DDC_SDA

AVDD_VDAC

AVDD_HDMI_1

AVDD_HDMI_2

AVDD_HDMI_PLL

T20_23X23

LCD

CRT

HDMI

LCD_PCLK

LCD_WR#

LCD_HSYNC

LCD_VSYNC

VDAC_VREF

VDAC_RSET

HDMI_TXCN

HDMI_TXCP

HDMI_TXD0N

HDMI_TXD0P

HDMI_TXD1N

HDMI_TXD1P

HDMI_TXD2N

HDMI_TXD2P

HDMI_RSET

LCD_DE

LCD_D00

LCD_D01

LCD_D02

LCD_D03

LCD_D04

LCD_D05

LCD_D06

LCD_D07

LCD_D08

LCD_D09

LCD_D10

LCD_D11

LCD_D12

LCD_D13

LCD_D14

LCD_D15

LCD_D16

LCD_D17

LCD_D18

LCD_D19

LCD_D20

LCD_D21

LCD_D22

LCD_D23

VDAC_R

VDAC_G

VDAC_B

V28

AE24

U23

AD27

AD26

AA26

AC26

AC27

AC28

AD25

AD28

Y26

Y27

Y28

Y25

AA28

AA27

U25

U28

U27

U26

V27

V26

AB25

AA23

AB23

AA22

V25

AC22

AB17

AB18

AE19

AC17

AE18

AF17

AG17

AE16

AE17

AC18

AD18

AH18

AG18

AF18

4

LCD_ PCLK_L

LCD _DE

LC D_HS YNC

LCD _VSY NC

LCD _D00

LCD _D01

LCD _D02

LCD _D03

LCD _D04

LCD _D05

LCD _D06

LCD _D07

LCD _D08

LCD _D09

LCD _D10

LCD _D11

LCD _D12

LCD _D13

LCD _D14

LCD _D15

LCD _D16

LCD _D17

HDMI_T XCN

HDMI_TXCP

HDMI_T XD0N

HDMI_TXD0 P

HDMI_T XD1N

HDMI_TXD1 P

HDMI_T XD2N

HDMI_TXD2 P

HDMI_R SET

R1042 47_0402_1%

GPS_ PWRON# [19 ]

LCD_ DE [11]

LCD_HSYNC [ 11]

LCD _VSY NC [11]

LCD_ D00 [11]

LCD_ D01 [11]

LCD_ D02 [11]

LCD_ D03 [11]

LCD_ D04 [11]

LCD_ D05 [11]

LCD_ D06 [11]

LCD_ D07 [11]

LCD_ D08 [11]

LCD_ D09 [11]

LCD_ D10 [11]

LCD_ D11 [11]

LCD_ D12 [11]

LCD_ D13 [11]

LCD_ D14 [11]

LCD_ D15 [11]

LCD_ D16 [11]

LCD_ D17 [11]

12

R21 1K_0402_1%

LCD_ PCLK_R

12

3

1 2

C4 0.1U_0 402_25V4Z

50mA

1

C134

2

L3

27NH +-5% L QG15HS27N J02D 0402

12P_0402 _50V4Z

1 2

PWR_ OFF_AP[9]

SIM_DET[ 9,17]

+1.8VS _LDO6

Change to 0805_20110112. Change to 0805_20110112.

HDMI_TX CN [18]

HDMI_TXCP [ 18]

HDMI_T XD0N [18]

HDMI_TXD0P [ 18]

HDMI_T XD1N [18]

HDMI_TXD1P [ 18]

HDMI_T XD2N [18]

HDMI_TXD2P [ 18]

12

R134 0_0805_5%

+VDDIO _MMC

1

C131

2

12P_0402 _50V4Z

R957

47K_0402_1%

R960

57.6K_0 402_1%

RB751V -40 SOD- 323

+VDDIO _VI

1

C7

2

2.2U_0 402_6.3VMZ

CAM1 _PWDN[15]

CAM2 _PWDN[21]

CAM2_RST#[21]

CAM1_RST#[15]

VGP4[21]

VGP5[21]

+VDDIO _VI

R127 0_0805_5%

Change to 0805_20110112.

12

12

100K_0402 _5%

D29

1

2

+VDD IO_NA ND

12

LCD_ PCLK [11]

HSMMC_ CLK[10]

EN_V DDIO_S D[16]

+VDD IO_NA ND

R117

HSMMC_ CMD[10]

1 2

21

SDIO3_C D#[1 6]

C8

0.1U_040 2_10V6K

VI_MC LK_R [15]

1 2

R11 10K_0402_5%

@

C1217

1 2

C3 2.2U_0 402_6.3VMZ

TP44

1

TP45

TP46

2

39P 5 0V J NP O 0402

TP48

TP50

TP53

TP57

TP58

TP59

TP60

VI_MCLK

NAND _ALE

HSMMC_ CLK

PWR_ OFF_A P_R

NAN D_RE#

NA ND_WE#

NAN D_CLE

HSMMC_ CMD

SIM_DE T_R

EXIT_LP0

CAM_ I2C_SCL

CAM_ I2C_SDA

R931

12

0_0402_5%

VI_ HSY NC

VI_ VSYN C

CAM1 _PWDN

VI_ D03

CAM2 _PWDN

VI_ D05

CAM2_RST #

VI_ D07

CAM1_RST #

VI_ D09

EN_V DDIO_ VID_OC#

VGP3

VGP6

VI_MC LK

VI_P CLK

AD12

AC12

AB12

AC10

AF12

2

U1E

Y7

VDDIO_NAND_1

Y8

VDDIO_NAND_2

Y9

VDDIO_NAND_3

AH3

GMI_ADV#

AF5

GMI_CS0#

GMI_CS1#

GMI_CS2#

AC6

GMI_CS3#

GMI_CS4#

GMI_CS5#

AD5

GMI_CS6#

AD9

GMI_CS7#

AG9

GMI_OE#

AF6

GMI_WR#

AF3

GMI_CLK

AC9

GMI_DPD

AC7

GMI_RST#

AF1

GMI_WAIT

AF2

GMI_WP#

GMI_IORDY

VI MIPI

L21

VDDIO_VI

H28

CAM_I2C_SCL

H27

CAM_I2C_SDA

L24

VI_MCLK

L28

VI_PCLK

L25

VI_HSYNC

K25

VI_VSYNC

H23

VI_D00

H25

VI_D01

J23

VI_D02

J28

VI_D03

J24

VI_D04

J27

VI_D05

J25

VI_D06

J26

VI_D07

K23

VI_D08

L26

VI_D09

L23

VI_D10

M22

VI_D11

L22

VI_GP0

M23

VI_GP3

J22

VI_GP4

L27

VI_GP5

M24

VI_GP6

T20_23X23

NAND

GEN2_I2C_SCL

GEN2_I2C_SDA

GMI_AD0

GMI_AD1

GMI_AD2

GMI_AD3

GMI_AD4

GMI_AD5

GMI_AD6

GMI_AD7

GMI_AD8

GMI_AD9

GMI_AD10

GMI_AD11

GMI_AD12

GMI_AD13

GMI_AD14

GMI_AD15

GMI_AD16

GMI_AD17

GMI_AD18

GMI_AD19

GMI_AD20

GMI_AD21

GMI_AD22

GMI_AD23

GMI_AD24

GMI_AD25

GMI_AD26

GMI_AD27

AVDD_DSI_CSI_1

AVDD_DSI_CSI_2

DSI_CSI_RUP

CSI_CLKAN

CSI_CLKAP

CSI_D1AN

CSI_D1AP

CSI_D2AN

CSI_D2AP

CSI_CLKBN

CSI_CLKBP

CSI_D1BN

CSI_D1BP

DSI_CLKAN

DSI_CLKAP

DSI_D1AN

DSI_D1AP

DSI_D2AN

DSI_D2AP

DSI_CSI_RDN

AD11

AD6

AG5

AE9

AF11

AG6

AH8

AG11

AF9

AF8

AE6

AE12

AH12

AH6

AH11

AG3

AH9

AH5

AG12

AD3

AE5

AG8

AD8

AE7

AC5

AE11

AE8

AC11

AE10

AC8

AA17

Y16

AF21

AH26

AG26

AD20

AE20

AH23

AG23

AB20

AC20

AH24

AG24

AD21

AC21

AF20

AG20

AH21

AG21

AH20

1

Add pull hi gh to +VDDI O_NAND to follow PBJ20 latest design_20110210.

GEN2 _I2C_SC L

GEN2 _I2C_SD A

NAN D_D4

NAN D_D5

NAN D_D6

NAN D_D7

SDIO 3_WP

GMI_AD 12

GMI_AD 13

GMI_AD 14

GMI_AD 15

UART4 _CTS#

UART4 _RTS#

HSMMC_DA T0

HSMMC_DA T1

HSMMC_DA T2

HSMMC_DA T3

HSMMC_DA T4

HSMMC_DA T5

HSMMC_DA T6

HSMMC_DA T7

80mA

+AVD D_DSI _CSI_R

R51

49.9_04 02_1%

1 2

GEN2 _I2C_SC L [ 15]

GEN2 _I2C_SDA [ 15]

12

R152 0_0402_5%

UART4_TXD [11 ]

UART4_RXD [11]

TP54

TP55

12

R1023 453_0402_1 %

CSI_CLK A_N [15]

CSI_CLKA_ P [ 15]

CSI_D1A _N [15]

CSI_D1A_P [1 5]

CSI_D2A _N [15]

CSI_D2A_P [1 5]

CSI_CLK B_N [21]

CSI_CLKB_ P [ 21]

CSI_D1B _N [21]

CSI_D1B_P [2 1]

10K_0402_5%

UART4 _RXD

use deb ug

+AVDD_ DSI_CSI

R128 0_0805_5%

1

C10

0.1U_04 02_25V4Z

2

+VDD IO_NA ND

HSMMC_DAT 0 [ 10]

HSMMC_DAT 1 [ 10]

HSMMC_DAT 2 [ 10]

HSMMC_DAT 3 [ 10]

HSMMC_DAT 4 [ 10]

HSMMC_DAT 5 [ 10]

HSMMC_DAT 6 [ 10]

HSMMC_DAT 7 [ 10]

R1385

1 2

+1.2V

12

+VDDIO _VI

B B

R38

2.2K_04 02_1%

R39

2.2K_04 02_1%

1 2

1 2

CAM_ I2C_SCL

CAM_ I2C_SDA

CAM_I 2C_SCL [15, 21]

CAM_I 2C_SDA [15 ,21]

FORC E_RECOVE RY[9]

G

2

13

D

S

Q15

BSS138 W-7-F_SOT323-3~D

Nam e Act ive

EC_ WAKE #

low

EXI T_LP 0 Hig h

+VDDIO _NAND

2

G

100K_0402_5 %

R112

1 2

13

D

S

EXIT_LP0

Q45

BSS138 W-7-F_SOT323-3~ D

P_INT[9,2 3]

4

A A

ALS_INT

+VDDIO _LCD

12

R1022

100K_0402_5 %

T20_WAKE#[9]

5

D30

21

RB751V -40 SOD-323

+VDDIO _LCD

100K_0402 _5%

R1316

1 2

H:force _recover mode

L:norma l mode

12

R17

47K_0402_1%

1 2

47K_0402_1%

SAR_ EN#

B D

R18

1 2

100K_0402 _5%

R20

R63

1 2

100K_0402 _5%

3

R68

1 2

100K_0402 _5%

R69

R70

@

10K_0402_ 5%

1 2

1 2

100K_0402 _5%

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

R65

R66

@

@

1 2

1 2

100K_0402 _5%

100K_0402 _5%

R30

R29

10K_0402_ 5%

10K_0402_ 5%

1 2

1 2

R64

@

1 2

100K_0402 _5%

R35

10K_0402_ 5%

1 2

Compal Secret Data

R42

1 2

100K_0402 _5%

R31

@

10K_0402_ 5%

1 2

A C

Deciphered Date

R40

R41

@

@

1 2

1 2

100K_0402 _5%

100K_0402 _5%

R36

R32

10K_0402_ 5%

10K_0402_ 5%

1 2

1 2

2

+VDDIO_MMC

R19

@

1 2

100K_0402 _5%

R34

10K_0402_ 5%

1 2

2010/11/052011/11/5

NAN D_RE#

NAND_W E#

NAND_C LE

NAND_A LE

GMI_AD12

GMI_AD13

GMI_AD14

GMI_AD15

NAND _D4

NAND _D5

NAND _D6

NAND _D7

eMMC bo ot

GMI_AD1 2 1

GMI_AD1 3

GMI_AD1 4

GMI_AD1 5

RAM

NAND_D4

NAND_D5

0

0

1

0

0

0

0

S-8GS -16G T-16G K -16G

ELPIDA

ELPIDA

512MB

1GB

1

0

0

0

BCBOM

AC

0

0

1 0

0

Hynix

512MB

0 1

1

AD BD

Add 4 sk u ty pe tabl e_20 1101 11.

Title

Size Docume nt Number Re v

C

Date : Sheet of

Compal Electronics, Inc.

T20(1/4)LCD/CRT/HDMI/NAND

Thur sday, Februa ry 24, 2 011

LA-7311P

1

0

0

1

Hynix

1GB

1

4

0.2

32

Page 5

5

D D

U1B

+1.8VS_LDO4

60mA

SKU2

SKU3

SKU4

SKU5

1 2

0_0402_5%

1 2

0_0402_5%

1 2

0_0402_5%

1 2

0_0402_5%

+AVDD_PLL_P_C +AVDD_P LLU

R212

R213

R214

R215

1

C28

C24

2

0.1U_0402_25 V4Z

+1.8VS_SYS

+1.8VS_LDO4

SLEEP_MODE

SLEEP_MODE2

SLEEP_MODE1

MODE

MODE1

(A6)

(B5)

1

1 1

1

1

0

1

0

00

1 2

R151 1K_0402_1%

TS_RESET_RTS_RESET TS_RESET_3V3

+1.1VS_LDO1

C C

B B

A A

220Ω @100MHz

L1

FBMA-10-100505-221T_0402

1 2

+AVDD_PLLX +AVDD_PLLM

1

1

C25

2

2

0.1U_0402_25 V4Z

0.1U_0402_25 V4Z

R210

0_0402_5%

1 2

@

R203 10K_0402_5%

@

R208 10K_0402_5%

@

R207 10K_0402_5%

MODE2

(A3)

0

1

11

1

+1.8VS_SYS

SN74AVC1T4 5DCKR_SC70-6

5

1

C27

2

0.1U_0402_25 V4Z

12

12

12

POP R208

POP R207

POP R203

POP R203

/R207

U87

1

VCCA

3

A

5

DIR

5mA

+AVDD_OSC

1

C30

2

BOM

NCSKU1

VCCB

1.8V

H12

1

C15

2

4.7U_0603_ 6.3V6K

1.1V

H14

1.1V

AA18

1.1V 1.8V

1.1V

H15

12

R216

0_0402_5%

1.8V

G18

0.1U_0402_ 25V4Z

6

4

B

2

GND

OSC, PLL, SYS

AVDD_OSC

AVDD_PLLA_P_C

AVDD_PLLU

L7

AVDD_PLLX

AVDD_PLLM

Y1

AVDD_PLLE

VDDIO_SYS

T20_23X23

+3VS

1 2

R204 33_0402_1%

4

XTAL_IN

XTAL_OUT

AVDD_PLL_S_LF

PWR_I2C_SCL

PWR_I2C_SDA

SYS_RESET#

CLK_32K_IN

PWR_INT#

CORE_PWR_REQ

CPU_PWR_REQ

SYS_CLK_REQ

CLK_32K_OUT

KB_COL0

KB_COL1

KB_COL2

KB_COL3

KB_COL4

KB_COL5

KB_COL6

KB_COL7

KB_ROW00

KB_ROW01

KB_ROW02

KB_ROW03

KB_ROW04

KB_ROW05

KB_ROW06

KB_ROW07

KB_ROW08

KB_ROW09

KB_ROW10

KB_ROW11

KB_ROW12

KB_ROW13

KB_ROW14

KB_ROW15

JTAG_RTCK

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

JTAG_TRST#

OWR

TEST_MODE_EN

4

T20_XTAL_IN

E3

T20_XTAL_OUT

E2

PLL_S_PLL_LF

G12

PWR_ I2C_SCL

C1

PWR_ I2C_SDA

C2

SYS_RESET# _R

D17

CLK_32K_ IN

B14

D14

R1290 0_0402_5%

CORE_P WR_REQ

G14

CPU_PW R_REQ

C14

SYS_CL K_REQ

D7

CLK_32K_OUT

D5

SLEEP_MODE

A6

D6

A5

SLEEP_MODE1

B5

C5

B3

SLEEP_MODE2

A3

TS_RESET

C3

DOCK_O N

C12

IR_INT

B12

A12

D11

A11

B11

DISABL E_CHRGR

C11

C9

B9

A9

D8

A8

B8

C8

C6

B6

JTAG_RTCK

A17

JTAG_TCK

B17

JTAG_TDI

B15

JTAG_TDO

C15

JTAG_TMS

C17

JTAG_TRST#

A15

SNN_OW R

G11

A14

TS_RESET_3V3_R [11 ]

3

1 2

C16 8P_0402_50V8J

R43

2M_0402_5%

1 2

1

Change back to 0201 fo r placemen t concern_20110117.

C26

2

R226 0_0402_5%

R45

0.1U_0402_25 V4Z

2.2K_0201_1%

12

12

CORE_P WR_REQ [9,3 1]

CPU_PW R_REQ [31 ]

TP27

CLK_32K_OUT [1 9,20]

LOCK [2 1]

VOL_DOW N [21]

VOL_UP [2 1]

TP174

TP175

TP36

WF_W AKE# [20]

KB_ROW14 [21]

GYRO_A CCEL_INT [1 4]

12

R48

10K_0402_5%

TP28

Y1

IN1NC

OUT3NC

12MHZ 9PF X3S012000B91H-X

1 2

C23 8P_0402_50V8J

+1.8V

R46

2.2K_0201_1%

1 2

1 2

CLK_32K_I N [9,31]

PWR_INT # [31]

TP127

TP128

TP129

TP130

TP131

TP132

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

4

PWR_ I2C_SCL [14, 31]

PWR_ I2C_SDA [14, 31]

SYS_RESET# [ 10,19,31]

Change to 0 805_20110112.

+1.2V

Change to 0 805_20110112.

1 2

0_0805_5%

DDR_A _D0[8]

DDR_A _D1[8]

DDR_A _D2[8]

DDR_A _D3[8]

DDR_A _D4[8]

DDR_A _D5[8]

DDR_A _D6[8]

DDR_A _D7[8]

DDR_A _D8[8]

DDR_A _D9[8]

DDR_A_ D10[8]

DDR_A_ D11[8]

DDR_A_ D12[8]

DDR_A_ D13[8]

DDR_A_ D14[8]

DDR_A_ D15[8]

DDR_A_ D16[8]

DDR_A_ D17[8]

DDR_A_ D18[8]

DDR_A_ D19[8]

DDR_A_ D20[8]

DDR_A_ D21[8]

DDR_A_ D22[8]

DDR_A_ D23[8]

DDR_A_ D24[8]

DDR_A_ D25[8]

DDR_A_ D26[8]

DDR_A_ D27[8]

DDR_A_ D28[8]

DDR_A_ D29[8]

DDR_A_ D30[8]

DDR_A_ D31[8]

R179

1 2

0_0805_5%

R129

+VDD_DDR _RX+2.85VS_LDO9

C86

200mA

+1.2V_LP DDR2

1

2

4.7U_0603_ 6.3V6K

DDR_A _D0

DDR_A _D1

DDR_A _D2

DDR_A _D3

DDR_A _D4

DDR_A _D5

DDR_A _D6

DDR_A _D7

DDR_A _D8

DDR_A _D9

DDR_A_ D10

DDR_A_ D11

DDR_A_ D12

DDR_A_ D13

DDR_A_ D14

DDR_A_ D15

DDR_A_ D16

DDR_A_ D17

DDR_A_ D18

DDR_A_ D19

DDR_A_ D20

DDR_A_ D21

DDR_A_ D22

DDR_A_ D23

DDR_A_ D24

DDR_A_ D25

DDR_A_ D26

DDR_A_ D27

DDR_A_ D28

DDR_A_ D29

DDR_A_ D30

DDR_A_ D31

U1C

H20

VDDIO_DDR_01

J12

VDDIO_DDR_02

J13

VDDIO_DDR_03

J14

VDDIO_DDR_04

J15

VDDIO_DDR_05

J16

VDDIO_DDR_06

J17

VDDIO_DDR_07

J18

VDDIO_DDR_08

J19

VDDIO_DDR_09

J20

VDDIO_DDR_10

J21

VDDIO_DDR_11

K20

VDDIO_DDR_12

L16

VDDIO_DDR_13

L17

VDDIO_DDR_14

L20

VDDIO_DDR_15

M17

VDDIO_DDR_16

M18

VDDIO_DDR_17

M20

VDDIO_DDR_18

N18

VDDIO_DDR_19

N20

VDDIO_DDR_20

P20

VDDIO_DDR_21

R20

VDDIO_DDR_22

T20

VDDIO_DDR_23

U20

VDDIO_DDR_24

V20

VDDIO_DDR_25

2.85V

H17

VDD_DDR_RX

F20

DDR_DQ00

E18

DDR_DQ01

D18

DDR_DQ02

F18

DDR_DQ03

F17

DDR_DQ04

E21

DDR_DQ05

D21

DDR_DQ06

F21

DDR_DQ07

E17

DDR_DQ08

D15

DDR_DQ09

F16

DDR_DQ10

E14

DDR_DQ11

F13

DDR_DQ12

D16

DDR_DQ13

D12

DDR_DQ14

D13

DDR_DQ15

F23

DDR_DQ16

F25

DDR_DQ17

H22

DDR_DQ18

G25

DDR_DQ19

F22

DDR_DQ20

D24

DDR_DQ21

H24

DDR_DQ22

E23

DDR_DQ23

F9

DDR_DQ24

F12

DDR_DQ25

E12

DDR_DQ26

E9

DDR_DQ27

F10

DDR_DQ28

G8

DDR_DQ29

F11

DDR_DQ30

G9

DDR_DQ31

T20_23X23

Compal Secret Data

Deciphered Date

C31

4.7U_0603_ 6.3V6K

DDR2

2

1

2

DDR_COMP_PU

DDR_COMP_PD

2010/11/052011/11/5

2

1

C145

2

4.7U_0603_ 6.3V6K

DDR_DM0

DDR_DM1

DDR_DM2

DDR_DM3

DDR_DQS0N

DDR_DQS0P

DDR_DQS1N

DDR_DQS1P

DDR_DQS2N

DDR_DQS2P

DDR_DQS3N

DDR_DQS3P

DDR_A00

DDR_A01

DDR_A02

DDR_A03

DDR_A04

DDR_A05

DDR_A06

DDR_A07

DDR_A08

DDR_A09

DDR_A10

DDR_A11

DDR_A12

DDR_A13

DDR_A14

DDR_RAS#

DDR_CAS#

DDR_WE#

DDR_BA0

DDR_BA1

DDR_BA2

DDR_CS0#

DDR_CS1#

DDR_ODT0

DDR_CKE0

DDR_CKE1

DDR_CLK#

DDR_CLK

THERMD_N

THERMD_P

DDR_QUSE0

DDR_QUSE1

DDR_QUSE2

DDR_QUSE3

+1.2V_LP DDR2

1

1

C147

C146

2

4.7U_0603_ 6.3V6K

DDR_A_DM 0

F19

DDR_A_DM 1

E15

DDR_A_DM 2

G23

DDR_A_DM 3

D9

D19

E20

F14

F15

E24

F24

E11

D10

A20

C24

D20

B20

F26

C26

C27

F28

A26

A23

D23

C20

C18

E28

C28

B23

H26

F27

B26

A24

B24

E25

C23

M_ODT

B21

A21

C21

E27

E26

E6

F7

Add net nam e +1.2V_DD R_COMP_PU_2 0110216.

+1.2V_DDR _COMP_PU

E8

F8

DDR_QU SE0

G15

DDR_QU SE1

G17

DDR_QU SE2

A18

DDR_QU SE3

B18

1

C148

2

2

4.7U_0603_ 6.3V6K

4.7U_0603_ 6.3V6K

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_ RAS#

DDR_A_ CAS#

DDR_A_W E#

DDR_A_BS #0

DDR_A_BS #1

DDR_A_BS #2

TP158

1 2

R9 0_0402_5%

1 2

R8 0_0402_5%

Title

Size Docume nt Number Re v

Cust om

Date : Sheet of

1

1

C149

2

4.7U_0603_ 6.3V6K

DDR_A_DM 0 [8]

DDR_A_DM 1 [8]

DDR_A_DM 2 [8]

DDR_A_DM 3 [8]

DDR_A_ DQS#0 [8]

DDR_A_ DQS0 [8]

DDR_A_ DQS#1 [8]

DDR_A_ DQS1 [8]

DDR_A_ DQS#2 [8]

DDR_A_ DQS2 [8]

DDR_A_ DQS#3 [8]

DDR_A_ DQS3 [8]

DDR_A_MA0 [8]

DDR_A_MA1 [8]

DDR_A_MA2 [8]

DDR_A_MA3 [8]

DDR_A_MA4 [8]

DDR_A_MA5 [8]

DDR_A_MA6 [8]

DDR_A_MA7 [8]

DDR_A_MA8 [8]

DDR_A_MA9 [8]

TP153

TP154

TP155

TP156

TP157

TP159

TP160

TP161

TP162

TP163

TP164

M_CS#0 [8]

M_CS#1 [8]

M_CKE0 [8]

M_CKE1 [8]

M_CLK_DDR# 0 [8]

M_CLK_DDR 0 [8]

THERMD_N [ 14]

THERMD_P [1 4]

1 2

R6 49.9_0402_1%

1 2

R49 49.9_0402_1%

+1.2V

Compal Electronics, Inc.

T20(2/4)OSC/PLL/SYS/DDR

Thurs day, Febr uary 24, 2011

LA-7311P

1

5

0.2

32

Page 6

A

B

C

D

E

Add net nam e +AVDD_USB _R_20110216.

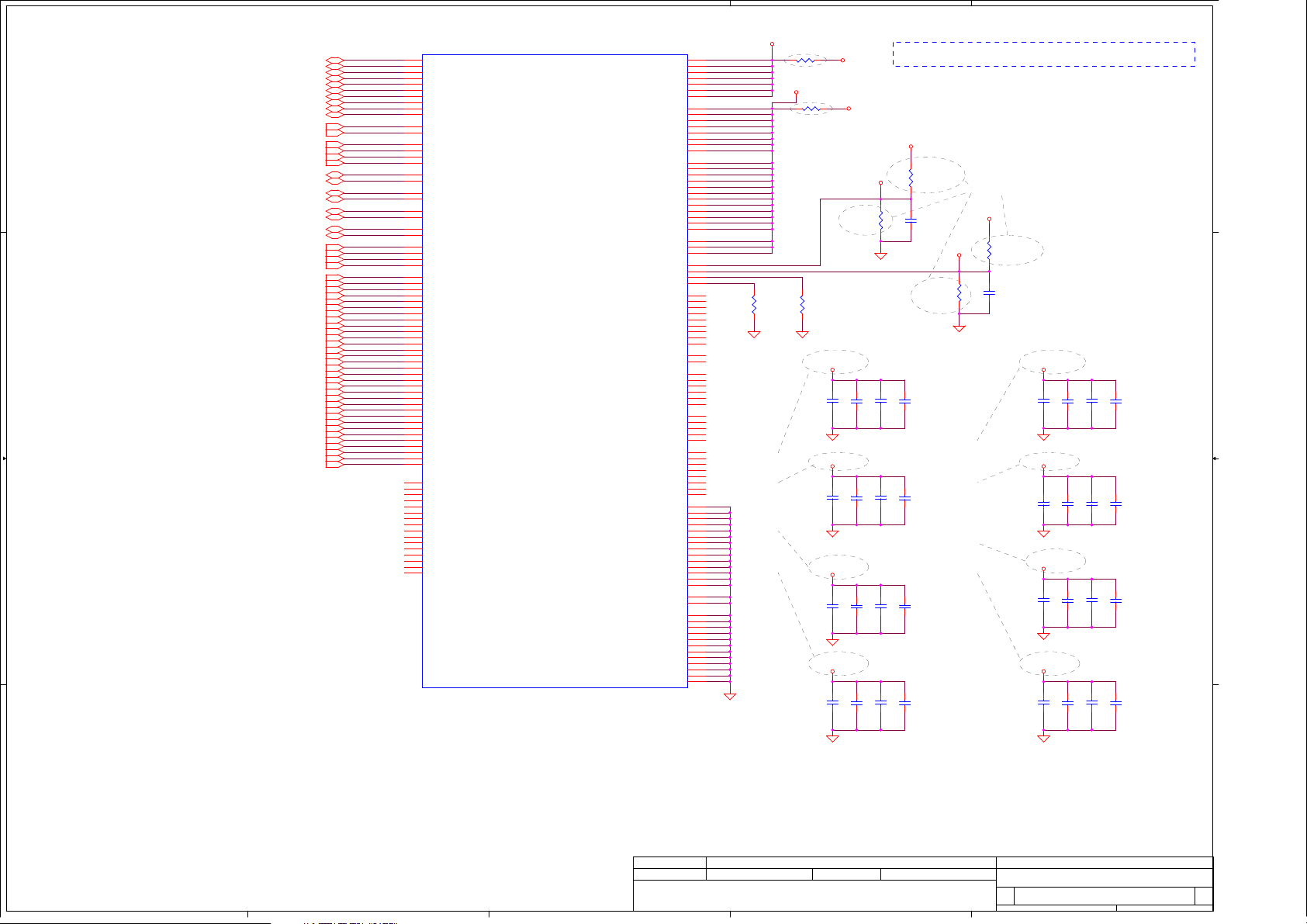

U1F

AVDD_USB_1

AVDD_USB_2

AVDD_USB_PLL

VDDIO_SDIOP1SDIO3_DATA0

SDIO

VDDIO_HSIC

AVDD_IC_USB

HSIC

DNC_0001

DNC_0002

DNC_0003

DNC_0004

DNC_0005

DNC_0006

DNC_0007

DNC_0008

DNC_0009

DNC_0010

DNC_0011

DNC_0012

T20_23X23

1 2

1 2

1 2

R33 2.49K_0402_1%

USB

HSIC_STROBE

NC

USB1_VBUS

USB1_DN

USB1_DP

USB1_ID

USB3_VBUS

USB3_DN

USB3_DP

USB3_ID

USB_REXT

SDIO3_DATA1

SDIO3_DATA2

SDIO3_DATA3

SDIO3_DATA4

SDIO3_DATA5

SDIO3_DATA6

SDIO3_DATA7

SDIO3_CLK

SDIO3_CMD

GPIO_PV4

GPIO_PV5

GPIO_PV6

HSIC_DATA

HSIC_REXT

IC_DN

IC_DP

IC_REXT

DNC_00013

DNC_00014

DNC_00015

DNC_00016

DNC_00017

DNC_00018

DNC_00019

DNC_00020

DNC_00021

DNC_00022

DNC_00023

Add net nam e +USB1_VBU S_R_20110216.

+USB1_VBUS_R

AD17

USB1_D N

AC14

USB1_DP

AD14

+AVDD_ USB_R

AE14

+USB3_VBUS

AH14

AH15

AG15

USB3_I D

AF15

AC16

R3

U3

U4

R4

T4

T6

R5

U7

R2

R1

P7

R7

R6

AC15

AD15

AE15

AF14

AG14

AE13

AF28

D22

G20

G21

M21

M7

R21

U5

V7

W4

Y6

R1327 10K_0402_5%

USB_REXT

TP172

SDIO3_ CLK_R

R232 0_0402_5%

EC_RESUME[9,31 ]

Name Activ e

EC_RESMUE Hi gh

AP_ONKEY# Low

B

R1307 0_0402_5%

1 2

R1326 10K_0402_5%

@

R228 0_0402_5%

@

1 2

1 2

R56 1K_0402_1%

12

100K_0402_5%

EC_LOW_BAT#[9]

12

12

+VDDIO_BB

R110

2

G

+USB1_VBUS

USB1_ DN [18]

USB1_DP [ 18]

+AVDD_USB

+5VALW

USB3_ DN [18]

USB3_DP [ 18]

L:H OST

H:Client

SDIO3_DAT0 [ 16]

SDIO3_DAT1 [ 16]

SDIO3_DAT2 [ 16]

SDIO3_DAT3 [ 16]

W_DISABL E# [17]

LED_EN [ 14]

LCD_BL_ EN [11]

SDIO3_CL K [16]

SDIO3_CM D [16]

CAM_PWR_ EN [15]

TS_EN [11 ]

TSC_INT# [1 1]

SDIO1_CL K[20]

1 2

13

D

Q48

BSS138W-7-F_SOT323-3~D

S

Change to 0 805_20110112.

+VDDIO _AUDIO

+1.8VS

100K_0402_5%

D25 RB751V-40 SOD-323

L:H OST

H:Client

Micro SD

Reserve 12p F to GND fo r RF reque st_20110112.

SDIO1_ CLK

WIFI

12P_0402_50V4Z

AP_ONK EY#

+1.8VS

R108 0_0805_5%

Change to 0 805_20110112.

R122 0_0402_5%

1

SDIO1_C MD[2 0]

@

SDIO1_DAT0[2 0]

C5

SDIO1_DAT1[2 0]

SDIO1_DAT2[2 0]

2

SDIO1_DAT3[2 0]

ULPI_RESET#[16]

ULPI_DAT0[16 ]

ULPI_DAT1[16 ]

ULPI_DAT2[16 ]

ULPI_DAT3[16 ]

ULPI_DAT4[16 ]

ULPI_DAT5[16 ]

ULPI_DAT6[16 ]

ULPI_DAT7[16 ]

ULPI_CL K[16]

ULPI _DIR[ 16]

ULPI_NXT[ 16]

ULPI_STP[16]

12

TP116

50mA

12

R116

0_0805_5%

+VDDIO _AUDIO

R114

21

1 2

WIF I

WF_RST#[20 ]

CAM1_PW DN_PU[15]

TP120

TP123

TP124

CDC_ IRQ#[12 ]

HEAD_DET#[ 21]

TP133

TP126

+VDDIO_BB

12

50mA

1

1

C35

2

2

4.7U_0603_ 6.3V6K

1 2

C1477

12P_0402_50V4Z

SDIO1_ CLK_R LCD_BL_PWM_1P8

SDIO1_C MD

SDIO1_DAT0

SDIO1_DAT1

SDIO1_DAT2

SDIO1_DAT3

DEV_MODE

AP_ACOK#

1 2

C38 0.1U_0402_25 V4Z

WF_RST#

SPI1_CS0_L

SPI1_MOSI

SPI1_MISO

LOW_BAT#

EN_MIC_IN T

EN_MIC_EXT#

Name Acti ve

EC_LOW_BAT# Lo w

LOW_BAT# Low

+VDDIO_UAR T +LCDV DD

U86

1

LCD_BL_PWM_1P8

12

R22

100K_0402_5%

VCCA

3

A

5

DIR

SN74AVC1T4 5DCKR_SC70-6

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

6

VCCB

4

B

2

GND

Compal Secret Data

Deciphered Date

+1.8VS

R121 0_0805_5%

Change to 0 805_20110112.

C36

@

LCD_BL_PWM [ 11]

U1G

0.1U_0402_ 25V4Z

BB UART

1.8V 1.8V

M8

VDDIO_BB

P4

ULPI_DATA0

P6

ULPI_DATA1

N4

ULPI_DATA2

L3

ULPI_DATA3

L4

ULPI_DATA4

L6

ULPI_DATA5

P5

ULPI_DATA6

N6

ULPI_DATA7

M2

ULPI_CLK

M3

ULPI_DIR

M1

ULPI_NXT

P3

ULPI_STP

L2

DAP3_DIN

L1

DAP3_DOUT

J3

DAP3_FS

M4

DAP3_SCLK

M6

SDIO1_CLK

J5

SDIO1_CMD

K6

SDIO1_DATA0

K4

SDIO1_DATA1

M5

SDIO1_DATA2

L5

SDIO1_DATA3

P2

GPIO_PV0

J7

GPIO_PV1

U6

GPIO_PV2

J6

GPIO_PV3

P21

VDDIO_AUDIO

R25

SPDIF_IN

N23

SPDIF_OUT

M28

SPI1_SCK

M27

SPI1_CS0#

M26

SPI1_MOSI

P26

SPI1_MISO

P24

SPI2_SCK

P23

SPI2_CS0#

P22

SPI2_CS1#

P28

SPI2_CS2#

N25

SPI2_MOSI

M25

SPI2_MISO

T20_23X23

Change back to 0201 f or placemen t concern_20110117.

GEN1_I2C_SCL

GEN1_I2C_SDA

AUDIO

VDDIO_UART

UART2_RTS#

UART2_CTS#

UART3_RTS#

UART3_CTS#

2010/11/052011/11/5

D

+VDDIO_UAR T

12

50mA

2.2K_0402_1%

H11

GEN1_I 2C_SCL

H6

GEN1_ I2C_SDA

H5

UART2_TXD

UART2_RXD

UART3_TXD

UART3_RXD

DAP4_SCLK

DAP_MCLK1

DAP_MCLK2

DAP1_SCLK

DAP2_SCLK

Date : Sheet of

H7

F4

G6

F5

UART3_TXD

F3

UART3_RXD

F2

UART3_RTS#

F1

UART3_CTS#

E4

J1

GPIO_PU0

G4

GPIO_PU1

E1

GPIO_PU2

F6

GPIO_PU3

E5

GPIO_PU4

H4

GPIO_PU5

J2

GPIO_PU6

H1

DAP4_DIN

J4

DAP4_DUT

H3

DAP4_FS

DAP1_FS

DAP1_DUT

DAP1_DIN

DAP2_FS

DAP2_DUT

DAP2_DIN

ACIN[9,26]

Title

Size Docume nt Number Re v

Cust om

DAP4_SCLK

H2

Change back to 0201 f or placemen t concern_20110117.

DAP_MCLK1

P27

DAP_MCLK2

R24

DAP1_SCLK

P25

DAP1_FS

R27

DAP1_DOUT

R28

DAP1 _DIN

R26

R23

R22

T23

T25

DAP_MCLK2

Add C1507 f or RF requ est_20110222.

Reserve 10p F for RF r equest_20110117.

+VDDIO_BB

2

G

Compal Electronics, Inc.

T20(3/4)USB/SDIO/UART/AUDIO

Thurs day, Febr uary 24, 2011

LA-7311P

1

C34

0.1U_0402_ 25V4Z

2

12

12

R57

R54

2.2K_0402_1%

R935

12

0_0201_5%

R97

0_0402_5%

@

12

R936

12

0_0402_5%

R937

12

0_0402_5%

TP111

TP112

TP113

TP114

C1507 33P 50 V J NPO 0201@

1 2

DAP_MCLK1_R

1

@

C1480

10P_0402_25V8K

2

R111

100K_0201_5%

1 2

AP_ACOK#

13

D

Q47

S

BSS138W-7-F_SOT323-3~D

E

GEN1_I2 C_SCL [11,12, 14,21]

GEN1_I 2C_SDA [11,12, 14,21]

GPS_RXD [19]

GPS_TXD [19]

GPS_CTS_L [19]

GPS_RTS_L [19]

UART3_TXD [20]

UART3_RXD [2 0]

UART3_RTS# [2 0]

UART3_CTS# [2 0]

BT_RST# [20]

BT_WAKEUP [2 0]

BT_IRQ# [2 0]

DAP4_ DIN [20]

DAP4_DOUT [ 20]

DAP4_FS [ 20]

DAP4_SCLK_ R [20]

DAP_MCLK1_FM2018 [1 3]

DAP_MCLK1_R [ 12]

DAP_MCLK2 [1 6]

DAP1_SCLK_ R [12]

DAP1_FS [ 12]

DAP1_DOUT [ 12]

DAP1_ DIN [12]

6

32

0.2

12

C32

12

39P 50 V J NPO 0402

+VDDIO _SDIO

12

U1H

AVDD_PEX_PLL

AVDD_PEX_1

AVDD_PEX_2

AVDD_PEX_3

VDD_PEX_1

VDD_PEX_2

VDD_PEX_3

VDDIO_PEX_CLK

T20_23X23

A

+AVDD_USB

100mA

12

C1219

50mA

1

C37

0.1U_0402_25 V4Z

2

PEX

1

C1218

39P 50V J NPO 0402

2

+AVDD_USB_PLL

1

1

100mA

C33

0.1U_0402_ 25V4Z

2

2

12

R58 1K_0402_1%

12

R59 1K_0402_1%

PEX_L0_TXN

PEX_L0_TXP

PEX_L0_RXN

PEX_L0_RXP

PEX_L1_TXN

PEX_L1_TXP

PEX_L1_RXN

PEX_L1_RXP

PEX_L2_TXN

PEX_L2_TXP

PEX_L2_RXN

PEX_L2_RXP

PEX_L3_TXN

PEX_L3_TXP

PEX_L3_RXN

PEX_L3_RXP

PEX_CLK_OUT1_N

PEX_CLK_OUT1_P

PEX_CLK_OUT2_N

PEX_CLK_OUT2_P

PEX_TSTCLKN

PEX_TSTCLKP

PEX_REFCLKN

PEX_REFCLKP

PEX_TERMP

3.3V

AA14

Y14

3.3V

AB11

3.3V

AB8

AB9

AA3

AB4

AB6

AC13

AC3

AE21

AE22

AE23

AF23

AF24

AF26

AF27

AD1

AD2

AA5

AA4

AC2

AC1

AA7

AA6

AA1

AA2

V4

V3

Y3

Y2

V6

V5

AC4

AD4

Y4

Y5

V1

V2

U1

R123 0_0402_5%

U2

R132 0_0402_5%

W6

+3.3VS_LDO3

Change to 0 805_20110112.

R156 0_0805_5%

1 1

R157 0_0805_5%

Change to 0 805_20110112.

+3VS

Change to 0 805_20110112.

2 2

3 3

4 4

2.2U_0603_ 6.3V6K

R135 0_0805_5%

P8

R8

R9

T9

U8

U9

V9

V8

Page 7

A

U1A

GND_001

GND_002

GND_003

GND_004

GND_005

GND_006

GND_007

GND_008

GND_009

GND_010

GND_011

GND_012

GND_013

GND_014

GND_015

GND_016

GND_017

GND_018

GND_019

GND_020

GND_021

GND_022

GND_023

GND_024

GND_025

GND_026

GND_027

GND_028

GND_029

GND_030

GND_031

GND_032

GND_033

GND_034

GND_035

GND_036

GND_037

GND_038

GND_039

GND_040

GND_041

GND_042

GND_043

GND_044

GND_045

GND_046

GND_047

GND_048

GND_049

GND_050

GND_051

GND_052

GND_053

GND_054

GND_055

GND_056

GND_057

GND_058

GND_059

GND_060

GND_061

GND_062

GND_063

GND_064

GND_065

GND_066

GND_067

GND_068

GND_069

GND_070

GND_071

GND_072

GND_073

GND_074

GND_075

GND_076

GND_077

GND_078

GND_079

GND_080

GND_081

GND_082

GND_083

GND_084

GND_085

GND_086

GND_087

GND_088

GND_089

GND_090

GND_091

GND_092

GND_093

GND_094

GND_095

GND_096

GND_097

GND_098

GND_099

GND_100

GND_101

GND_102

GND_103

GND_104

GND_105

GND_106

GND_107

GND_108

GND_109

GND_110

GND_111

GND_112

GND_113

GND_114

GND_115

GND_116

GND_117

GND_118

GND_119

GND_120

GND_121

GND_122

GND_123

GND_124

GND_125

GND_126

GND_127

GND_128

GND_129

GND_130

GND_131

GND_132

GND_133

GND_134

GND_135

GND_136

T20_23X23

CORE

A1

A2

A27

A28

AA10

AA13

AA16

AA19

AA21

AA8

AA9

1 1

2 2

3 3

4 4

A

AB24

AB27

AC19

AD10

AD13

AD16

AD19

AD22

AE25

AE27

AG10

AG13

AG16

AG19

AG22

AG25

AG27

AG28

AH27

AH28

W21

W24

W27

AB2

AB5

AD7

AE2

AE4

AG1

AG2

AG4

AG7

AH1

AH2

B1

B10

B13

B16

B19

B2

B22

B25

B27

B28

B4

B7

D2

D25

D27

D4

E10

E13

E16

E19

E22

E7

G2

G24

G27

G5

H10

H13

H16

H18

H19

H21

H8

K2

K21

K24

K27

K5

K8

L11

L12

L13

L14

L15

L18

L8

M12

N13

N14

N16

N17

N2

N21

N24

N27

N5

N8

P17

P18

R11

R14

R15

R17

R18

T11

T12

T14

T17

T18

T2

T21

T24

T27

T5

T8

U11

U12

U15

U18

U21

V11

V14

V15

V16

V21

W2

W5

W8

Y11

Y12

Y13

VDD_RTC_001

VDD_RTC_002

VDD_CPU_01

VDD_CPU_02

VDD_CPU_03

VDD_CPU_04

VDD_CPU_05

VDD_CPU_06

VDD_CPU_07

VDD_CPU_08

VDD_CPU_09

VDD_CPU_10

VDD_CPU_11

VDD_CPU_12

VDD_CPU_13

VDD_CPU_14

VDD_CPU_15

VDD_CPU_16

VDD_CPU_17

VDD_CORE_01

VDD_CORE_02

VDD_CORE_03

VDD_CORE_04

VDD_CORE_05

VDD_CORE_06

VDD_CORE_07

VDD_CORE_08

VDD_CORE_09

VDD_CORE_10

VDD_CORE_11

VDD_CORE_12

VDD_CORE_13

VDD_CORE_14

VDD_CORE_15

VDD_CORE_16

VDD_CORE_17

VDD_CORE_18

VDD_CORE_19

VDD_CORE_20

VDD_CORE_21

VDD_CORE_22

VPP_FUSE

VPP_KFUSE

VDD_CORE_SENSE

GND_CORE_SENSE

VDD_CPU_SENSE

GND_CPU_SENSE

VDD_TP

GND_TP

VGND_TP

B

1.0~1.2V

V12

V13

H9

J10

J11

J8

J9

K9

L9

M11

M9

N11

N12

P11

P12

P13

P14

R12

R13

AA20

M13

M14

M15

M16

N15

P15

P16

R16

T13

T15

T16

U13

U14

U16

U17

V17

V18

W20

Y19

Y20

Y21

AB15

AB14

Y18

Y17

N9

P9

W9

Y10

AA11

10mA

+VDD_RTC

+VDD_RTC

+1.2VS_SM0_R

VDD_KF USE

VDD_C ORE_SENSE

GND_C ORE_SENSE

VDD_C PU_SENSE

GND_C PU_SENSE

VDD_TP

GND_TP

VGND_TP

R130 0_0805_5%

Change to 0805_20110 112.

1

C43

2

1800mA

0.1U_0402_ 25V4Z

+VDD_C PU

C44

800mA

C48

4.7U_0603_ 6.3V6K

70mA

+VDD_F USE

1 2

R61 10K_0402_5%

+1.2VS_LDO2

12

1

1

1

C45

C46

2

2

4.7U_0603_ 6.3V6K

1

2

2

4.7U_0603_ 6.3V6K

4.7U_0603_ 6.3V6K

1

1

C50

C49

2

2

0.1U_0402_ 25V4Z

4.7U_0603_ 6.3V6K

3.3V

+VDD_F USE

1

2

TP29

TP30

TP31

TP32

TP33

TP34

TP35

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

0.9~1.0V

+VDD_C PU

1 2

R126 0_0805_5%

1

C47

2

0.1U_0402_ 25V4Z

1.0~1.2V

+1.2VS_SM0_R

R125 0_0805_5%

1

1

C51

C52

2

2

0.1U_0402_ 25V4Z

0.1U_0402_ 25V4Z

R124 0_0402_5%

Change ba ck to 0402_ 20110119.

C53

0.1U_0402_ 25V4Z

Issued Date

C

+1.0VS_SM1

+1.2VS_SM0

1 2

Change ne t name to m eet PMU621_ 20110112.

+3.3VS_LDO7

12

ZZZ 1

PCB_LA-7311P

Compal Secret Data

H1

HOLEA

Deciphered Date

D

H2

H3

HOLEA

HOLEA

1

1

1

2010/11/052011/11/5

D

H4

HOLEA

H5

H6

HOLEA

HOLEA

1

1

1

Add one H ole to meet ME drawing _20110111.

Title

Size Docu ment Numbe r Re v

Cus tom

Date : Sheet o f

H7

HOLEA

1

Compal Electronics, Inc.

T20(4/4)PWR_GND_NC

Thurs day, Febr uary 24, 20 11

E

FD1

1

LA-7311P

E

FD2

1

FD4

FD3

1

1

7

0.2

32

Page 8

5

4

3

2

1

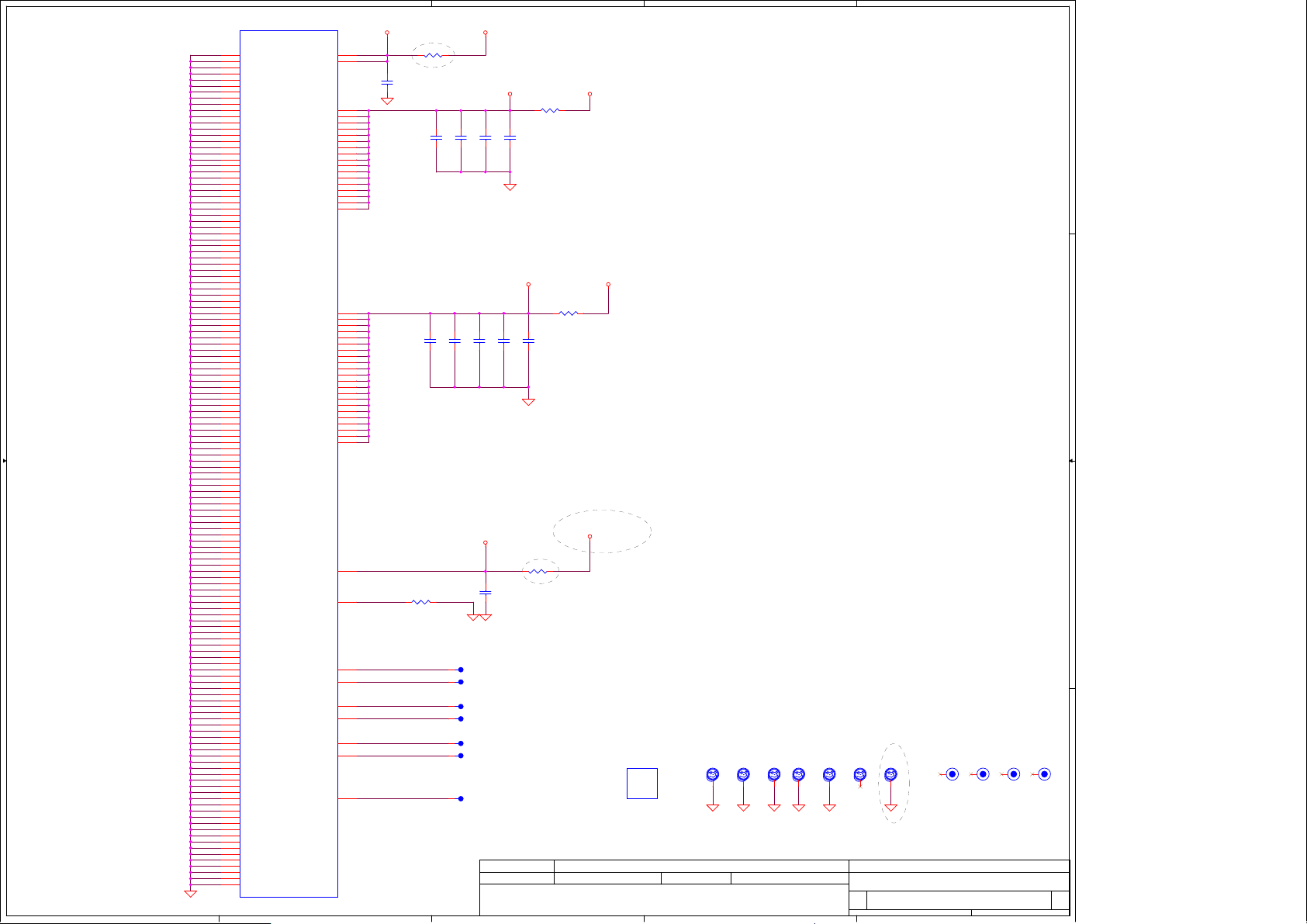

U129

DDR_A _MA9[5]

DDR_A _MA8[5]

DDR_A _MA7[5]

DDR_A _MA6[5]

DDR_A _MA5[5]

DDR_A _MA4[5]

DDR_A _MA3[5]

DDR_A _MA2[5]

DDR_A _MA1[5]

D D

C C

B B

DDR_A _MA0[5]

M_CS#0[5]

M_CS#1[5]

M_CL K_DDR0[5]

M_CL K_DDR#0[5]

M_CKE0[5]

M_CKE1[5]

DDR_ A_DQS3[5]

DDR_ A_DQS# 3[5]

DDR_ A_DQS2[5]

DDR_ A_DQS# 2[5]

DDR_ A_DQS1[5]

DDR_ A_DQS# 1[5]

DDR_ A_DQS0[5]

DDR_ A_DQS# 0[5]

DDR_ A_DM3[5]

DDR_ A_DM2[5]

DDR_ A_DM1[5]

DDR_ A_DM0[5]

DDR_ A_D31[5]

DDR_ A_D30[5]

DDR_ A_D29[5]

DDR_ A_D28[5]

DDR_ A_D27[5]

DDR_ A_D26[5]

DDR_ A_D25[5]

DDR_ A_D24[5]

DDR_ A_D23[5]

DDR_ A_D22[5]

DDR_ A_D21[5]

DDR_ A_D20[5]

DDR_ A_D19[5]

DDR_ A_D18[5]

DDR_ A_D17[5]

DDR_ A_D16[5]

DDR_ A_D15[5]

DDR_ A_D14[5]

DDR_ A_D13[5]

DDR_ A_D12[5]

DDR_ A_D11[5]

DDR_ A_D10[5]

DDR _A_D9[5]

DDR _A_D8[5]

DDR _A_D7[5]

DDR _A_D6[5]

DDR _A_D5[5]

DDR _A_D4[5]

DDR _A_D3[5]

DDR _A_D2[5]

DDR _A_D1[5]

DDR _A_D0[5]

DDR_A _MA8

DDR_A _MA7

DDR_A _MA6

DDR_A _MA5

DDR_A _MA4

DDR_A _MA3

DDR_A _MA2

DDR_A _MA1

DDR_A _MA0

M_CS#0

M_CS#1

M_CL K_DDR0

M_CL K_DDR#0

M_CKE0

M_CKE1

DDR_ A_DQS 3

DDR_ A_DQS# 3

DDR_ A_DQS 2

DDR_ A_DQS# 2

DDR_ A_DQS 1

DDR_ A_DQS# 1

DDR_ A_DQS 0

DDR_ A_DQS# 0

DDR_ A_DM3

DDR_ A_DM2

DDR_ A_DM1

DDR_ A_DM0

DDR_ A_D31

DDR_ A_D30

DDR_ A_D29

DDR_ A_D28

DDR_ A_D27

DDR_ A_D26

DDR_ A_D25

DDR_ A_D24

DDR_ A_D23

DDR_ A_D22

DDR_ A_D21

DDR_ A_D20

DDR_ A_D19

DDR_ A_D18

DDR_ A_D17

DDR_ A_D16

DDR_ A_D15

DDR_ A_D14

DDR_ A_D13

DDR_ A_D12

DDR_ A_D11

DDR_ A_D10

DD R_A_D9

DD R_A_D8

DD R_A_D7

DD R_A_D6

DD R_A_D5

DD R_A_D4

DD R_A_D3

DD R_A_D2

DD R_A_D1

DD R_A_D0

T1

CA9

T2

CA8

U1

CA7

V2

CA6

W1

CA5

AB9

CA4

AB8

CA3

AC7

CA2

AB6

CA1

AC6

CA0

AB3

CS0#

AB4

CS1#

Y2

CK

Y1

CK#

AC3

CKE0

AC4

CKE1

B18

DQS3

A19

DQS3#

AB18

DQS2

AC19

DQS2#

J22

DQS1

K23

DQS1#

R23

DQS0

P22

DQS0#

B20

DM3

AB20

DM2

L23

DM1

N23

DM0

B12

DQ31

A13

DQ30

A14

DQ29

B14

DQ28

B15

DQ27

A16

DQ26

A17

DQ25

B17

DQ24

AC17

DQ23

AB17

DQ22

AC16

DQ21

AB15

DQ20

AC14

DQ19

AB14

DQ18

AC13

DQ17

AB12

DQ16

C22

DQ15

D23

DQ14

E23

DQ13

E22

DQ12

F22

DQ11

G23

DQ10

H23

DQ9

H22

DQ8

T23

DQ7

T22

DQ6

U22

DQ5

V23

DQ4

W23

DQ3

W22

DQ2

Y22

DQ1

AA23

DQ0

A1

DNU0

A2

DNU1

A22

DNU2

A23

DNU3

B1

DNU4

B2

DNU5

B22

DNU6

B23

DNU7

AB1

DNU8

AB2

DNU9

AB22

DNU10

AB23

DNU11

AC1

DNU12

AC2

DNU13

AC22

DNU14

AC23

DNU15

MT46H64M 32L2JG-5IT-A_FBGA 168

VDD1_0

VDD1_1

VDD1_2

VDD1_3

VDD1_4

VDD1_5

VDD1_6

VDD2_0

VDD2_1

VDD2_2

VDD2_3

VDD2_4

VDD2_5

VDD2_6

VDD2_7

VDDQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDCA_0

VDDCA_1

VDDCA_2

VREFDQ

VREFCA

NC10

NC11

NC13

NC14

NC15

NC16

NC17

NC18

NC20

NC21

NC22

NC23

NC24

NC26

NC27

NC28

NC29

NC30

NC31

NC32

NC33

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSSCA0

VSSCA1

VSSQ0

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSSQ10

VSSQ11

B3

A11

A20

N22

AC20

AB5

N2

B11

B21

L22

AB21

AB10

AA2

R2

C2

B13

B16

B19

D22

G22

K22

R22

V22

AA22

AB19

AB16

AB13

AC8

W2

U2

M22

P2

P1

ZQ0

AC11

ZQ1

A3

NC0

A4

NC1

A5

NC2

A6

NC3

A7

NC4

A8

NC5

A9

NC6

A10

NC7

B4

NC8

B6

B7

B9

D1

D2

E1

E2

F1

G1

G2

H1

H2

J1

K1

K2

L1

L2

M1

N1

AC9

AC10

B10

A21

M23

AC21

AB11

AC5

AA1

R1

M2

C1

B5

B8

J2

F2

AB7

V1

A12

A15

A18

C23

F23

J23

P23

U23

Y23

AC18

AC15

AC12

+1.8 V_LPDDRDDR_A _MA9

+1.2 V_LPDDR

+1.8 V_LPDDR

12

R1372 0_0805_5%

Add 0805 0 ohm, need near LPDDR(U129)_20110112.

+1.2 V_LPDDR

R1390 0_0805_5%

Add 0805 0 ohm, need near LPDDR(U129)_20110210.

R460

240_0402_1 %

1 2

Change powe r rail name to +1.8V_LPDDR_20110112.

+1.8V

12

+1.2V

+VRAM_ VREFA

R457

7.5K_04 02_1%

R461

240_0402_1 %

1 2

+1.8 V_LPDDR +1.2 V_LPDDR

2

1

C503

C479

1

2

0.01U_04 02_25V7

0.1U_0 402_25V4Z

+1.8 V_LPDDR

2

1

C500

C478

1

2

0.01U_04 02_25V7

0.1U_0 402_25V4Z

+1.8 V_LPDDR

1

2

C477

C495

2

1

0.01U_04 02_25V7

0.1U_0 402_25V4Z

+1.8 V_LPDDR

2

1

C488

C476

1

2

0.01U_04 02_25V7

0.1U_0 402_25V4Z

EDB4032B2PB(40nm 512M) SA00004EF30

EDB8132B2PB(40nm 1G)

EDB8132B1PB(50nm 1G)

+1.2V

R456

7.5K_04 02_1%

1 2

2

0.1U_04 02_25V4Z

1

1 2

7.5K_04 02_1%

1

2

C504

C505

2

1

1U_040 2_6.3V4Z

0.1U_0 402_25V4Z

1

2

C501

C502

2

1

1U_04 02_6.3V4Z

0.1U_0 402_25V4Z

1

2

C498

C499

2

1

1U_040 2_6.3V4Z

0.1U_0 402_25V4Z

1

2

C490

C489

2

1

1U_040 2_6.3V4Z

0.1U_0 402_25V4Z

Follow PBJ2 0 12/13 comment power saving_20110106.

+VRAM_ VREFA

R459

1 2

+1.2V

R458

7.5K_04 02_1%

1 2

2

C465

0.1U_04 02_25V4Z

1

Change powe r rail name to +1.2V_LPDDR_20110210.

C455

1

C459

2

0.01U_04 02_25V7

+1.2 V_LPDDR

1

C456

2

0.01U_04 02_25V7

+1.2 V_LPDDR

1

C492

2

0.01U_04 02_25V7

+1.2 V_LPDDR

1

C506

2

0.01U_04 02_25V7

2

C460

1

0.1U_0 402_25V4Z

2

C457

1

0.1U_0 402_25V4Z

2

C494

1

0.1U_0 402_25V4Z

2

C507

1

0.1U_0 402_25V4Z

SA000048Q30

SA000048Q00

1

2

C461

C462

2

1

1U_040 2_6.3V4Z

0.1U_0 402_25V4Z

1

2

C458

C463

2

1

1U_04 02_6.3V4Z

0.1U_0 402_25V4Z

2

1

C493

C491

1

2

1U_04 02_6.3V4Z

0.1U_0 402_25V4Z

1

2

C509

C508

2

1

1U_040 2_6.3V4Z

0.1U_0 402_25V4Z

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

Compal Secret Data

Deciphered Date

2

2010/11/052011/11/5

Title

Size Docume nt Number Re v

C

Date : Sheet of

Compal Electronics, Inc.

LPDDRII-DEVICE DOWN

Thur sday, Februa ry 24, 2 011

LA-7311P

1

8

0.2

32

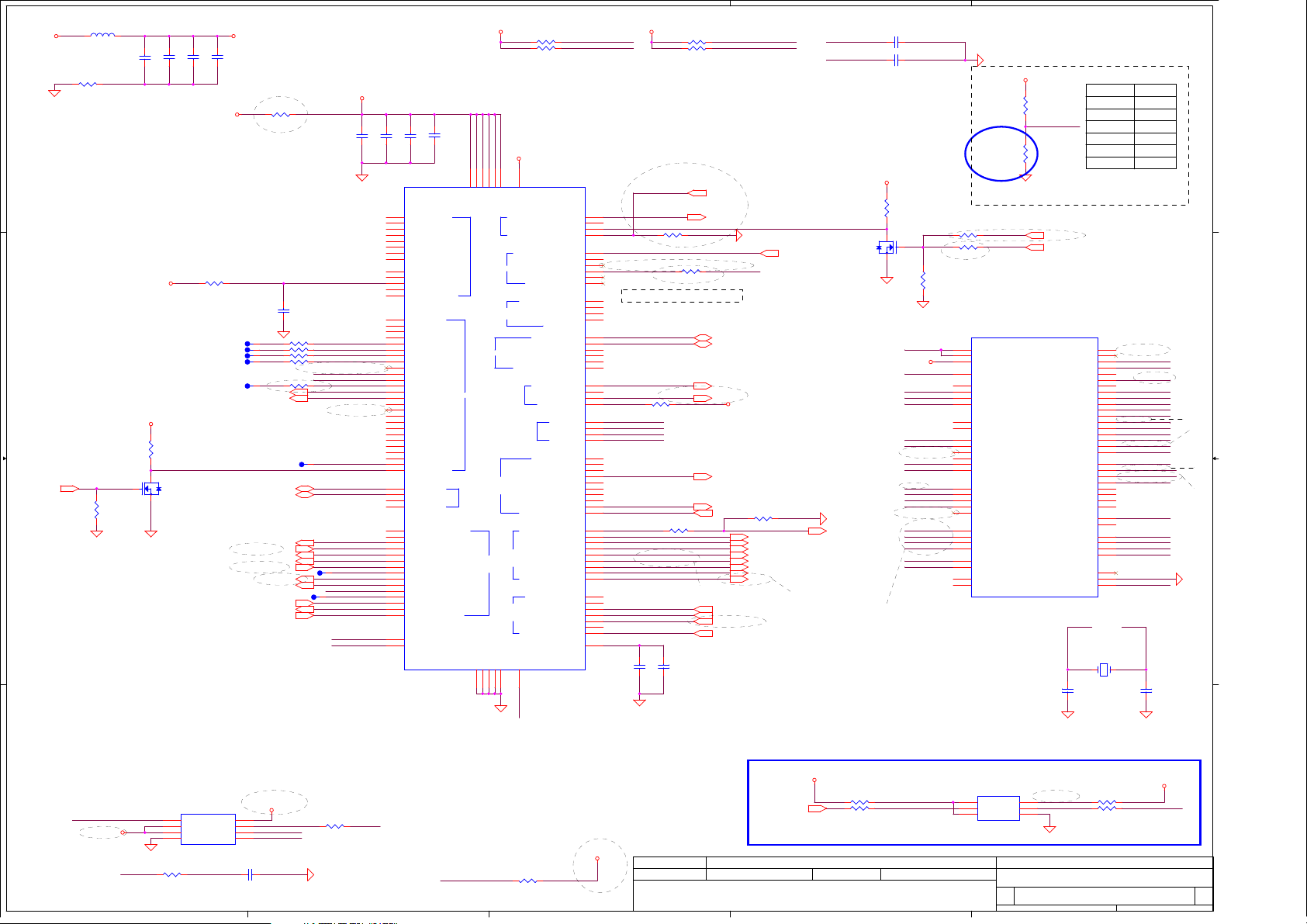

Page 9

5

L51

FBM-11-16080 8-601-T_0603

1 2

ECA GND

1 2

R1161 0_0402_5 %

D D

C C

FM2018_ EN[12]

B B

R1193

100K_0402 _5%

1 2

Change net name from POUT to POUTR_20110127.

Add 2nd P-s ensor signal pin_20110127.

1

2

C1331

C1330

2

G

C1332

2

1

0.1U_0 402_25V4Z

+3VALW

10P_0402_ 25V8K

4.7U_06 03_6.3V6K

+3VALW

R1163 47K_0402_1%

Del CHG_RST # confirm with Power team_20110216.

R170

100K_0402 _5%

1 2

13

D

Q51

BSS138 W-7-F_SOT323-3~D

S

Add P-senso r power switch_20110111.

1

C1333

2

1 2

68P_0402 _50V8J

+3VALW

1

2

+EC_ AVCC+3VALW

+3VALW_EC

1 2

R1160 0_0805_5%

Change to 0805_20110112.

2

C1336

1

0.1U_0 402_25V4Z

TP167

TP168

TP169

TP170

TP171

1 2

R1336 0_0402_5%

1 2

R1337 0_0402_5%

1 2

R1338 0_0402_5%

1 2

R1339 0_0402_5%

R1392 0_0402_5%

1 2

PANEL_D ETECT#[11 ]

PANEL _EN[32] SIM_EN # [ 17]

Del DC_OFF# confirm with EC_20110208.

T8

EC_SMB _CK1[13, 25,26]

EC_SMB _DA1[13, 25,26]

FM2018_RST #[1 3]

POUTR[23]

SYSTEM_RE SET#[ 31]

EC_LOW_ BAT#[6]

POUTL[ 21]

TOUC H_LDO_E N[11 ]

ON/ OFF#[ 21]

PWR_ SUSP_LED #[21]

TEMP_THERM#[ 14]

TP38

CAP_ EN#[21]

TP68

+3VALW _EC

2

C1324

1

0.1U_0 402_25V4Z

EC_RS T#

KSI4

KSI5

KSI6

KSI7

KSO1

KSO2

KSO3

20110218

EC_FM2 018_EN#

EC_SMB _CK1

EC_SMB _DA1

INVT_ PWM

EC_TX_P80_DATA

EC_RX_ P80_CLK

XCLKI

XCLKO

4

2

C1325

1

0.1U_0 402_25V4Z

10

12

13

37

20

38

55

56

57

58

59

60

61

62

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

81

82

77

78

79

80

14

15

16

17

18

19

25

28

29

30

31

32

34

36

122

123

1

2

C1329

C1326

2

1

0.1U_0 402_25V4Z

4.7U_0 603_6.3V6K

U134

1

GA20/GPIO00

2

KBRST#/GPIO01

3

SERIRQ#

4

LFRAME#

5

LAD3

7

LAD2

8

LAD1

LPC & MISC

LAD0

PCICLK

PCIRST#/GPIO05

ECRST#

SCI#/GPIO0E

CLKRUN#/GPIO1D

KSI0/GPIO30

KSI1/GPIO31

KSI2/GPIO32

KSI3/GPIO33

KSI4/GPIO34

KSI5/GPIO35

KSI6/GPIO36

KSI7/GPIO37

KSO0/GPIO20

KSO1/GPIO21

KSO2/GPIO22

KSO3/GPIO23

KSO4/GPIO24

Int. K/B

KSO5/GPIO25

KSO6/GPIO26

Matrix

KSO7/GPIO27

KSO8/GPIO28

KSO9/GPIO29

KSO10/GPIO2A

KSO11/GPIO2B

KSO12/GPIO2C

KSO13/GPIO2D

KSO14/GPIO2E

KSO15/GPIO2F

KSO16/GPIO48

KSO17/GPIO49

SCL1/GPIO44

SDA1/GPIO45

SCL2/GPIO46

SDA2/GPIO47

6

PM_SLP_S3#/GPIO04

PM_SLP_S5#/GPIO07

EC_SMI#/GPIO08

LID_SW#/GPIO0A

SUSP#/GPIO0B

PBTN_OUT#/GPIO0C

EC_PME#/GPIO0D

EC_THERM#/GPIO11

FAN_SPEED1/FANFB1/GPIO14

FANFB2/GPIO15

EC_TX/GPIO16

EC_RX/GPIO17

ON_OFF/GPIO18

PWR_LED#/GPIO19

NUMLED#/GPIO1A

XCLK1

XCLK0

9

22

33

VCC

VCC

VCC

PWM Output

DA O utput

PS2 Interfa ce

SPI Device I nterface

SM Bus

GPIO

GND

GND

11

24

+3VALW

1 2

R1164 47K_0402_ 1%

1 2

R1165 47K_0402_ 1%

+EC_ AVCC

67

96

111

125

VCC

VCC

VCC

AVCC

INVT_PWM/PWM1/GPIO0F

BEEP#/PWM2/GPIO10

FANPWM1/GPIO12

ACOFF/FANPWM2/GPIO13

BATT_TEMP/AD0/GPIO38

BATT_OVP/AD1/GPIO39

ADP_I/AD2/GPIO3A

AD I nput

SPI Flash R OM

GPIO

GND

GND

GND

35

94

113

AD3/GPIO3B

AD4/GPIO42

SELIO2#/AD5/GPIO43

DAC_BRIG/DA0/GPIO3C

EN_DFAN1/DA1/GPIO3D

IREF/DA2/GPIO3E

DA3/GPIO3F

PSCLK1/GPIO4A

PSDAT1/GPIO4B

PSCLK2/GPIO4C

PSDAT2/GPIO4D

TP_CLK/PSCLK3/GPIO4E

TP_DATA/PSDAT3/GPIO4F

SDICS#/GPXOA00

SDICLK/GPXOA01

SDIDO/GPXOA02

SDIDI/GPXID0

SPIDO/WR#

SPICLK/GPIO58

CIR_RX/GPIO40

CIR_RLC_TX/GPIO41

FSTCHG/SELIO#/GPIO50

BATT_CHGI_LED#/GPIO52

CAPS_LED#/GPIO53

BATT_LOW_LED#/GPIO54

SUSP_LED#/GPIO55

SYSON/GPIO56

VR_ON/XCLK32K/GPIO57

AC_IN/GPIO59

EC_RSMRST#/GPXO03

EC_LID_OUT#/GPXO04

EC_ON/GPXO05

EC_SWI#/GPXO06

ICH_PWROK/GPXO06

GPO

BKOFF#/GPXO08

WL_OFF#/GPXO09

PM_SLP_S4#/GPXID1

ENBKL/GPXID2

GPI

AGND

KB930Q F A1 LQF P 128P

69

ECA GND

SPIDI/RD#

SPICS#

GPXO10

GPXO11

GPXID3

GPXID4

GPXID5

GPXID6

GPXID7

V18R

3

+3VALW

KSO1

KSO2

21

23

SM0_PG#

26

AC OFF

27

63

64

65

BOAR D_ID_ R BOAR D_ID

66

75

76

68

70

71

72

83

84

85

86

87

88

97

98

99

3VS_EN

109

FRD# SPI_SO

119

FWR# SPI_S I

120

SPI_CLK

126

FSEL#S PICS#

128

73

74

89

90

91

92

93

95

121

127

EC_R ESUME_R

100

101

EC_O N

102

3G_LD O_EN#

103

104

105

106

107

108

110

112

114

115

116

117

118

124

R1166 2.2K_04 02_1%

R1167 2.2K_04 02_1%

Install R11 62 and add ACOFF to charger_20110218.

R1162 10K_04 02_5%

R1335 0_0402_5%

Remove R117 7~R1179 follow PBJ20_20110106

SIM_E N#

1 2

R1186 100K_0 402_5%

P_INT

1 2

R1169 0_0402_5%

FM20 18_PWR_D N#

Follow PBJ2 0 latest design_20110125.

1

2

C1338

C1337

2

1

0.1U_0 402_25V4Z

4.7U_06 03_6.3V6K

12

1 2

12

12

ACO FF [26]

STAN DBY# [21]

CHAR GE_LED0 # [ 21]

P_INT [4, 23]

ACIN [ 6,26]

HOT_RST# [2 1]

SMB136_STAT [26]

USB_DET [ 18]

2

BATT _TEM PA t race wi dth 10 m il

EC_SMB _CK1

EC_SMB _DA1

BATT_TEMP [25]

Del ADP_I c onfirm with Power team_20110216.

Follow PBJ2 0 add board ID design_20110106

AP_SMB_S CL [ 11,15 ,17,25]

AP_SMB_SD A [11,15,1 7,25]

T20_WAKE# [4]

Follow PBJ2 0 add power switch_20110110.

+3VS

Change net name from POUT to POUTR_20110127.

R1168 10K_04 02_5%

Add EN_136 to Charger IC follow PBJB0_20110212.

SIM_DET [4 ,17]

12

3G_EN [2 9]

EC_O N [21]

3G_LD O_EN [29]

FOR CE_RE COVER Y [ 4]

FM20 18_PWR_D N# [13]

PWR_ OFF_AP [4]

EC_FM2 010_LDO [13 ]

EN_13 6 [ 26]

Add SMB136_ STAT follow PBJB0_20110212.

BATT_TEMP

AC IN

BSS138 W-7-F_SOT323-3~D

Del DC_OFF# confirm with EC_20110208.

EC_RES UME [6,31 ]

12

C1328 100P_04 02_50V8J

12

C1327 100P_04 02_50V8J

R1333

100K_0402 _5%

R1334

8.2K_04 02_5%

+3VALW

R217

100K_0402 _5%

1 2

13

D

Q54

2

G

S

+3VALW_EC

+EC_A VCC

EC_RS T#

PANEL_D ETECT#

PANE L_EN

ON /OFF#

BATT_TEMP

SM0_PG#

Del ADP_I c onfirm with Power team_20110216.

3VS_EN

TEMP_THERM#

POUTR

EC_O N

HOT_RST#

EC_R ESUME_R

AP_SMB_S DA

AP_SMB_S CL

EC_SMB _DA1

EC_SMB _CK1

EC_FM2 010_LDO

AC IN

Swap Pin51 & 59 ; Pin52 & 61 for EC request_20110125.

Add SM0_PG to follow PBJ20 latest design_20110210.

R1386 0_0402_5%

1 2

1 2

R1199 0_0402_5%@

Follow PBJ2 0 reserve R1199_20110211.

R1197

100K_0402 _5%

1 2

U148

@

IO3731-A0 _LQFP64_7X7

24

VCC1

60

VCC2

15

AVCC

36

RESET#

25

GPIO14/PWM0

8

GPIO07/PWM1

26

GPIO15/PWM2

27

GPIO16/PWM3

16

GPO0E/DA0

17

GPO0F/DA1

9

GPI08/AD0

10

GPI09/AD1

11

GPI0A/AD2

12

GPI0B/AD3

13

GPI0C/AD4

14

GPI0D/AD5

7

GPIO06/OWM

28

GPIO17/CEC

30

GPIO19/DS0

31

GPIO1A/DS1

33

GPIO1C/IRQ#

51

GPIO2D/SDA0

52

GPIO2E/SCL0

59

GPIO35/SDA1/PS2_DAT3

61

GPIO36/SCL1/PS2_CLK3

63

GPIO37/PS2_CLK1

64

GPIO38/PS2_DAT1

50

CLK_OUT

49

CLK_IN

1

+3VALW

board I D R1334

1 2

BOAR D_ID

1 2

Change Boar d ID for DVT_20110218

SM0_PG [31]

CORE _PWR_R EQ [5,31]

GPIO1F/KSO0

GPIO20 /KSO1

GPIO21/KSO2

GPIO22/KSO3

GPIO02/KSO4

GPIO03/KSO5

GPIO04/KSO6

GPIO05/KSO7

GPIO23/KSO8

GPIO24/KSO9

GPIO25/KSO10

GPIO26/KSO11

GPIO27/KSO12

GPIO28/KSO13

GPIO29/KSO14

GPIO2A/KSO15

GPIO18/CIRRX/KSO16

GPIO1B/CIRTX/KSO17

GPIO31/KSI0

GPIO32/KSI1

GPIO2F/KSI2

GPIO30/KSI3

GPIO33/KSI4/EDI_CS

GPIO34/KSI5/EDI_CLK

GPIO00/KSI6/EDI_DI

GPIO01/KSI7/EDI_DO

GPIO1E/TX

GPIO1D/RX

GPIO10/SPI_CLK

GPIO11/SPI_DO

GPIO12/SPI_DI

GPIO13/SPI_CS#

NC

GND

AGND

32.768K HZ_12.5P _1TJE125DP1A000 M

1 2

1

C1334

15P_040 2_50V8J

2

0

1

2

3

4

5

37

38

39

FO RCE_RE COVER Y

40

3

4

5

6

41

42

43

44

45

46

47

48

29

32

55

56

53

54

57

58

1

2

35

34

19

20

21

22

23

62

18

X2

0

8.2K

18K

33K

56K

100K

Del CHG_RST # confirm with Power team_20110216.

EC_LOW_ BAT#

CAP_ EN#

TOUC H_LDO_E N

STAN DBY#

USB_DE T

SIM_DET

3G_EN

EN_13 6

SYSTEM_RE SET#

PWR_ OFF_AP

T20_WAKE #

SMB136_STAT

P_INT

AC OFF

POUTL

FM20 18_PWR_D N#

FM2018_RS T#

EC_TX_P80_DATA

PWR_ SUSP_LE D#

CHAR GE_LED 0#

3G_LD O_EN#

EC_FM2 018_EN#

ECA GND

XCLKOXCLKI

1

C1335

15P_040 2_50V8J

2

Add CAP_EN# confirm with EC_20110208.

Add EN_136_ STAT for EC suggest_20110215.

Add SMB136_ STAT for EC suggest_20110215.

Follow PBJ2 0 latest design_20110125. Add POUTL for RF 2nd P-sensor signal pin_20110127.

Compal Electronics, Inc.

A A

BIOS

FSEL#S PICS#

+3VALW _EC

SPI_CLK _R

R1175 0_0402_5%

Change net name from +3VALW to +3VALW_EC_20110210.

5

Change net name from +3VALW to +3VALW_EC_20110121.

U136

1

CE#

3

WP#

7

HOLD#

4

VSS

MX25L1005AMC-12 G_SOP8

@

1 2

8

VDD

6

SCK

5

SI

2

SO

@

1 2

C1339 68 P_0402_50V8J

+3VALW _EC

SPI_CLK _R SPI_C LK

FWR# SPI_S I

FRD# SPI_SO

1 2

R1174 0_0402_5%

4

EC_TX_P80_DATA

Pull high t o +3VALW for EC request_20110117.

+3VALW

12

R1176 100K_0402 _5%

3

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

+1.8VS _LDO4

CLK_3 2K_IN[5 ,31]

Compal Secret Data

@

1 2

R1171 0_0402_5%

@

1 2

R1170 0_0402_5%

Deciphered Date

2

+LDO4_1 .8V

2010/11/052011/11/5

Add net nam e +LDO4_3.3V_20110216.

U85

@

1

VCCA

A3B

5

DIR

SN74AV C1T45DCK R_SC70-6

+LDO4_3 .3V

6

VCCB

EC_C LKCLK _32K_IN _R XCLKO

4

2

GND

Title

Size Docume nt Number Re v

C

Date : Sheet of

Compal Electronics, Inc.

ENE/BIOS/LIGHT SENSOR

Thur sday, Februa ry 24, 2 011

@

1 2

R1172 0_0402_5%

@

1 2

R1173 0_0402_5%

LA-7311P

1

9

+3VALW

0.2

32

Page 10

5

4

+VDDIO_MMC

+VCORE_MMC

3

2

Add U155 fo r eMMC 14X 18 footprin t_20110216.

1

+VDDIO_MMC+VCORE_MMC

1

1

CMD

VDDi

CLK

NC