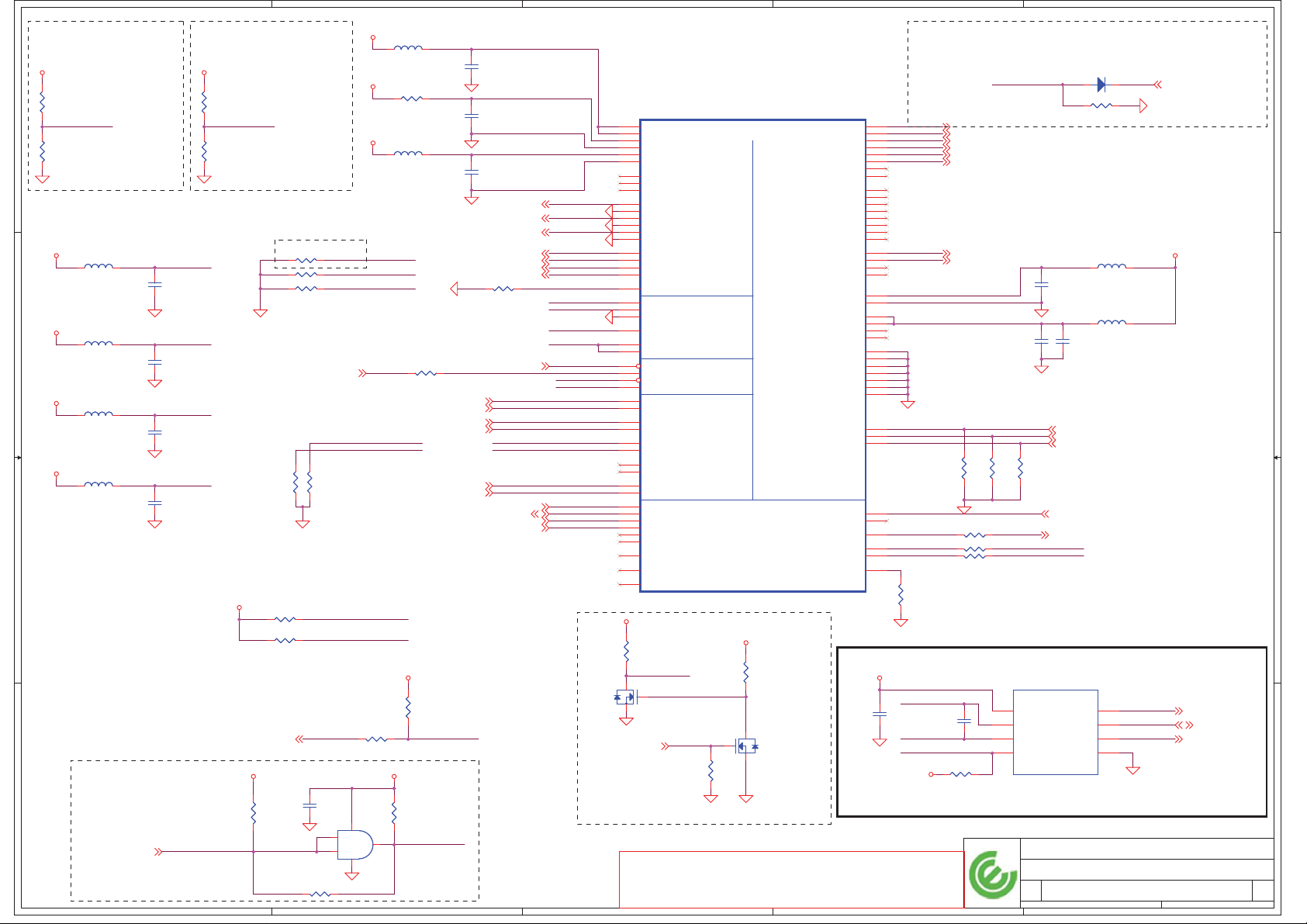

Page 1

A

B

COMPAL CONFIDENTIAL

C

D

E

MODEL NAME :

1 1

PCB NO :

BOM P/N :

LA-6132P ( DA80000I500) DAZ0DD00200

43185331L01 (K325)

NLM01

43185331L02 (K125)

43185331L03 (V105)

M10 Andros

AMD ASB2/ RS880M / SB820M

2 2

2010-05-11

REV : 1.0(A00)

@ : Nopop Component

3 3

WWAN@: WWAN function

NONWWAN@: NON WWAN function

CONN@: Connector only

4 4

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

A

B

C

D

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Cover Sheet

Cover Sheet

Cover Sheet

LA-6132P

LA-6132P

LA-6132P

145Tuesday, May 11, 2010

145Tuesday, May 11, 2010

145Tuesday, May 11, 2010

E

1.0

1.0

1.0

of

of

of

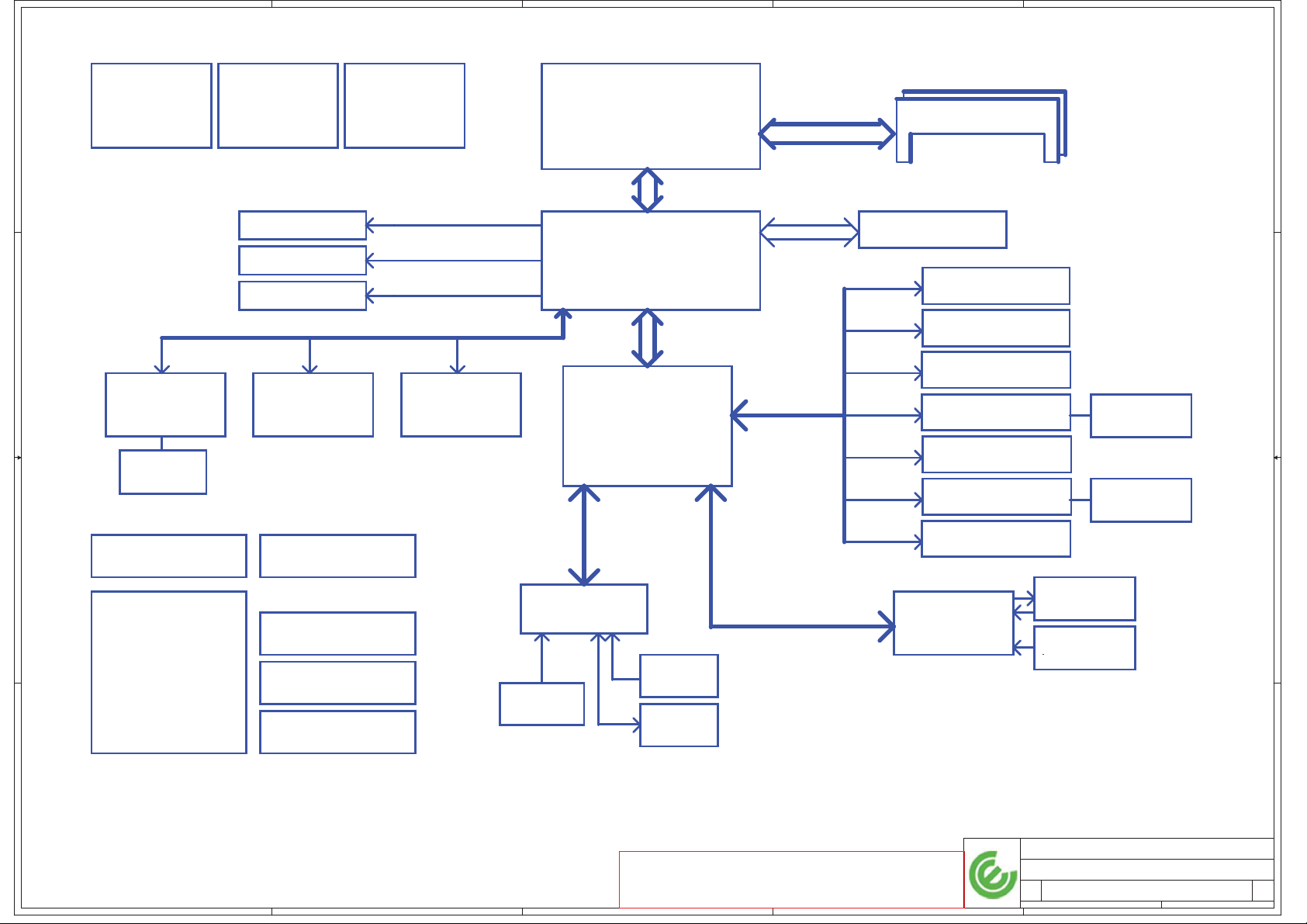

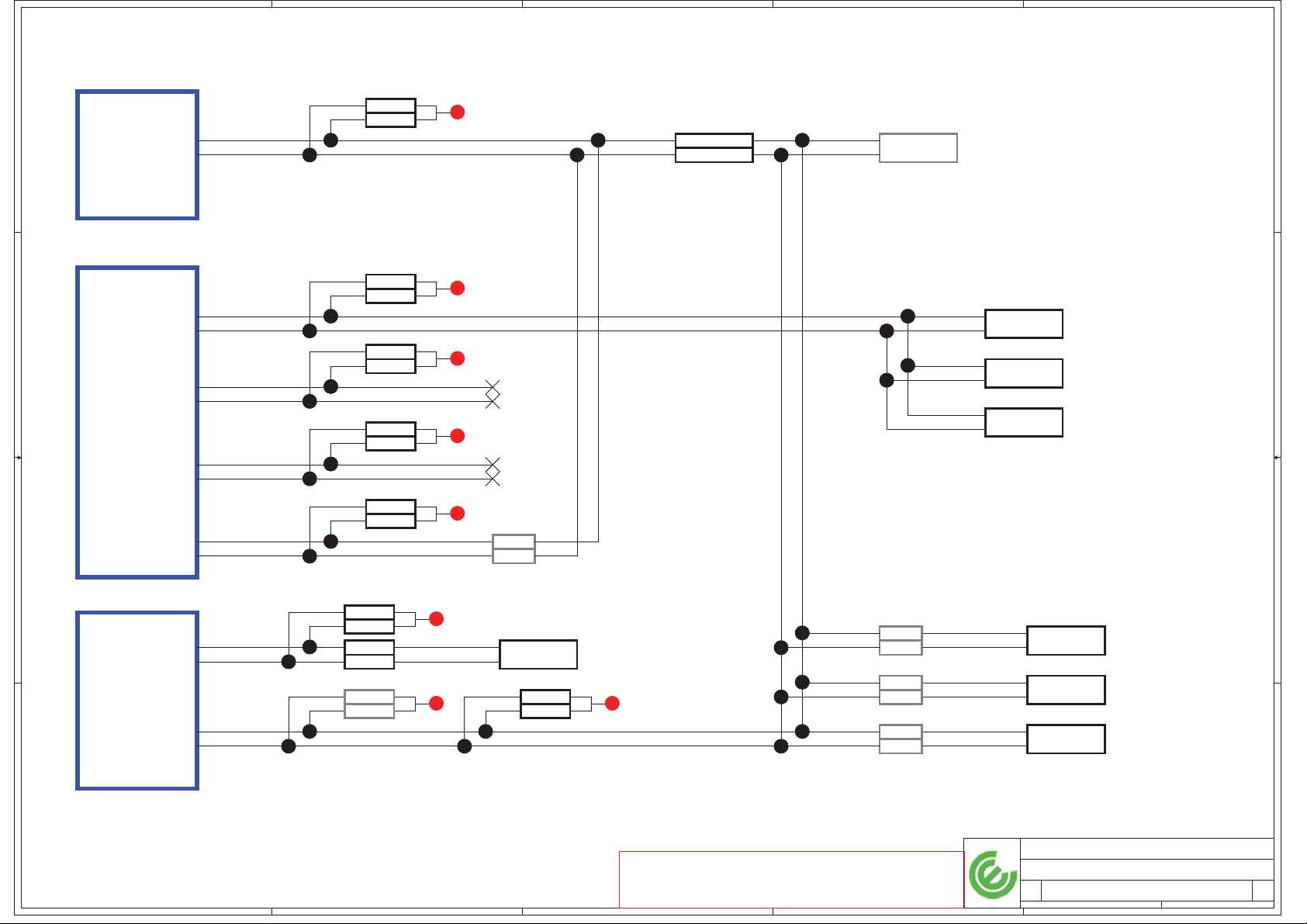

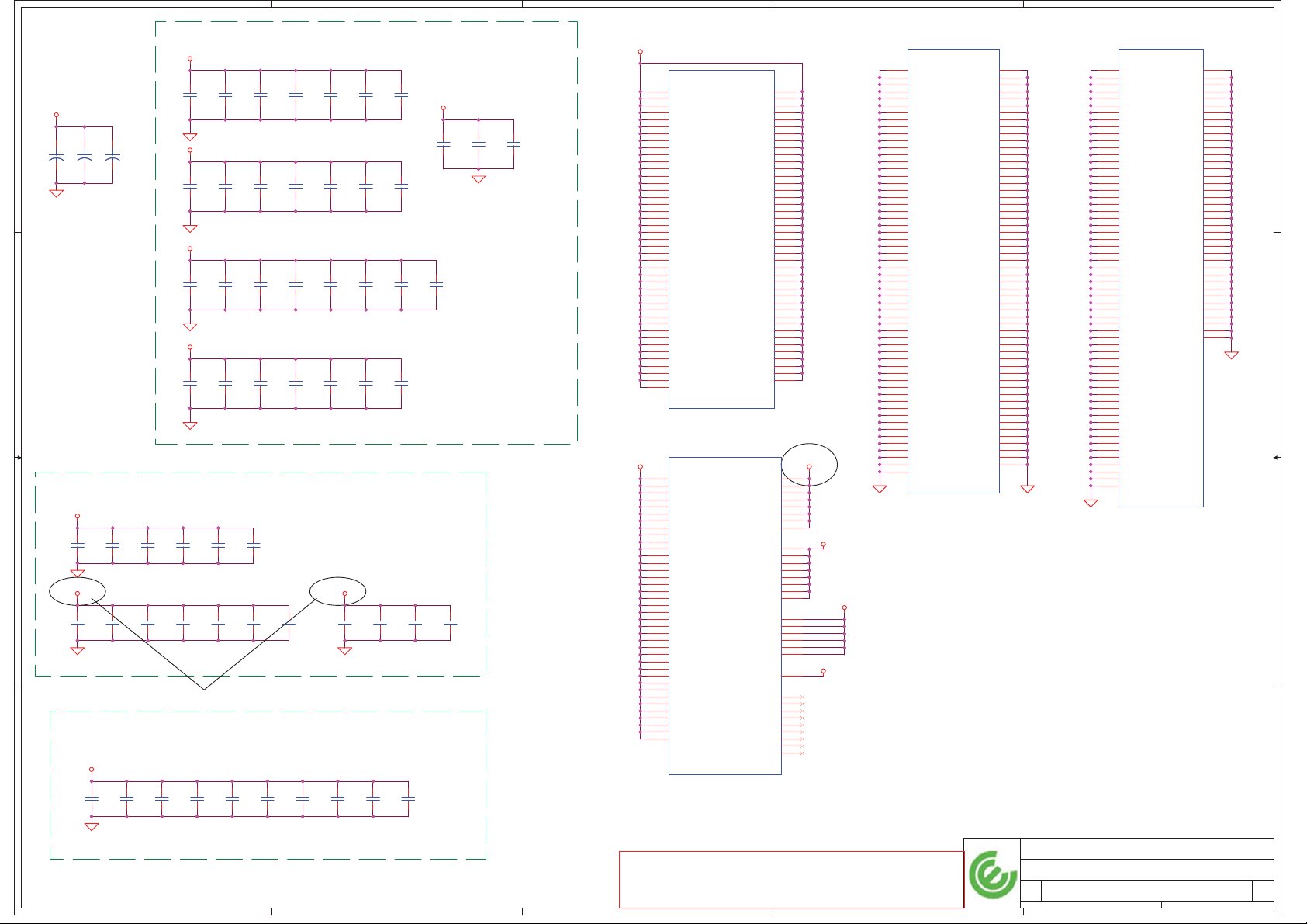

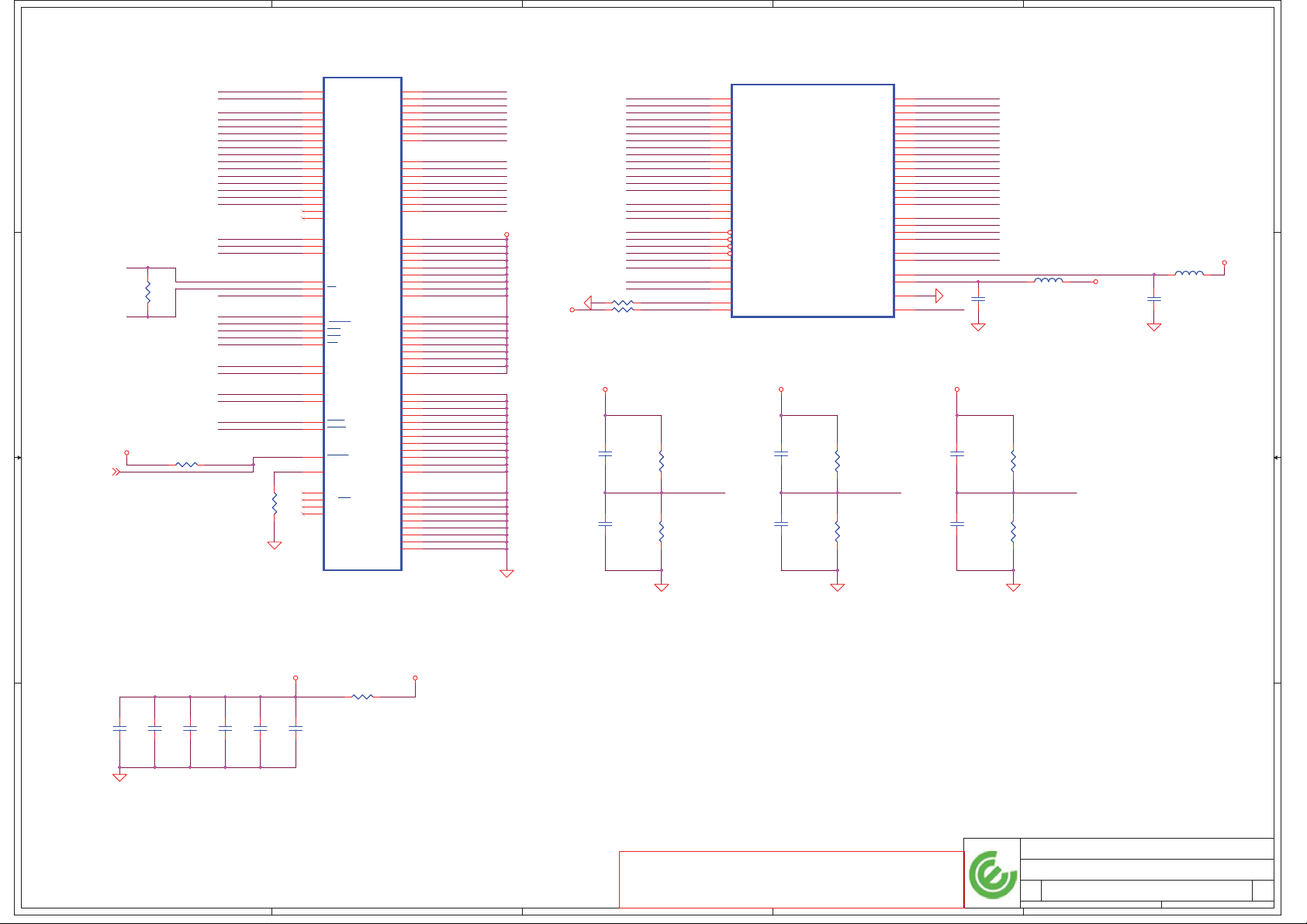

Page 2

A

B

C

D

E

Thermal Sensor

EMC1402 x 2

1 1

2 2

(CPU/NB)

Page 8/13 Page 16 Page 18

GPP PCIE0

LAN

Atheros AR8132

RJ45 conn.

Page 20

DC/DC

3 3

(Power Control)

Clock Generator

Page 20

Page 30

SB820M

Internal CKG

LVDS conn.

HDMI conn.

CRT conn.

Mini Card

WLAN WWAN

Power Button

Spread Spectrum

ECS2P8211

Page 27

Page 22

Page 24

GPP PCIE1 GPP PCIE2

LVDS

TMDS

VGA

PCI Express

Mini Card

Page 28 Page 28

Sub/B

LPC BUS

AMD ASB2

K325 / 2C / 1.3G / 2M

K125 / 1C / 1.7G / 1M

Page 6,7,8,9

Hyper Transport Link

HT3 16x16 1.0GHz up to 1.6GHz

AMD-RS880M

BGA 528

Page 12,13,14,15

A-Link Express

4 x PCIE

AMD-SB820M

BGA 605

Page 16,17,18,19

DDR3 BUS

SidePort

USB2.0

DDR3-SO-DIMM X2

DDR3 64x16Mb

128MB LFB

USB port2

USB port0,1

USB port4

USB port5

USB port6

USB port8

USB port9

Page 10, 11

Dual Channel

DDRIII 800MHz

Page 14

USB conn.

USB conn. x 2

Sub/B & Page 23

Mini Card

WLAN

Mini Card

WWAN

Bluetooth conn.

CardBus

Realtek RTS5138

Camera

Page 33

Page 28

Page 28

Page 28

Page 21

Page 27

SIM conn.

Page 28

3 in 1 conn.

Page 21

EC

Power Circuit

+3VALW / +5VALW

+1.1VALW

+0.75VS

+1.5V

+1.8V

+2.5VDDA / +CPU_VDDR

+CPU_CORE / +VDDNB

+NB_CORE

Page 36~43

4 4

BATT IN &OTP

Page 33

DC IN & DECTOR

Page 34

CHARGER

Page 35

ENE KB926

T/P conn.

Page 31

Page 26

AZ-Audio I/F

Int. KBD

Page 26

SPI ROM

Page 31

CODEC

Realtek ALC259

Sub/B

Audio Jack x 2

Digital MIC

Sub/B

Camera side

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

A

B

C

D

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Block Diagram

Block Diagram

Block Diagram

LA-6132P

LA-6132P

LA-6132P

245Monday, May 03, 2010

245Monday, May 03, 2010

245Monday, May 03, 2010

E

1.0

1.0

1.0

of

of

of

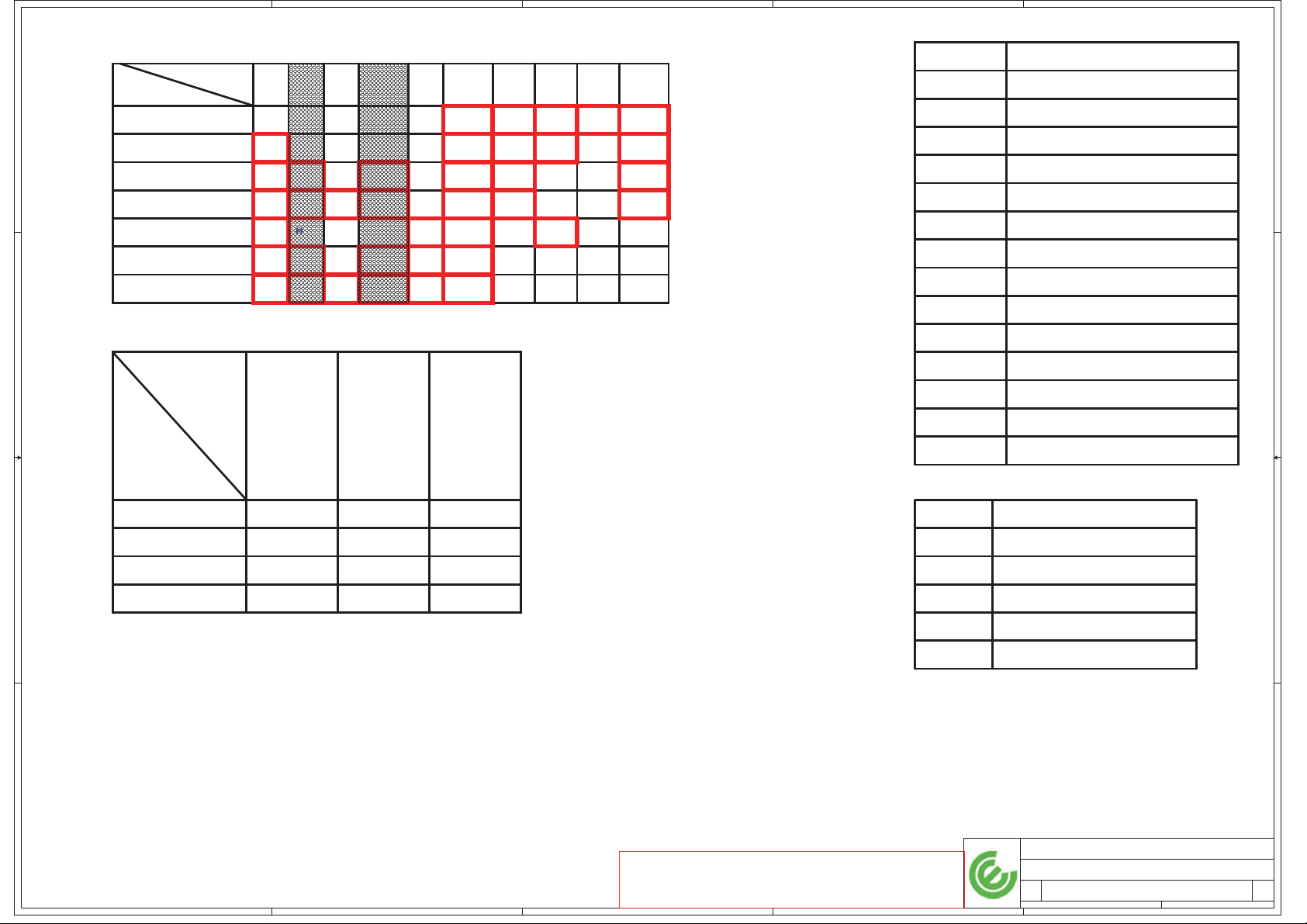

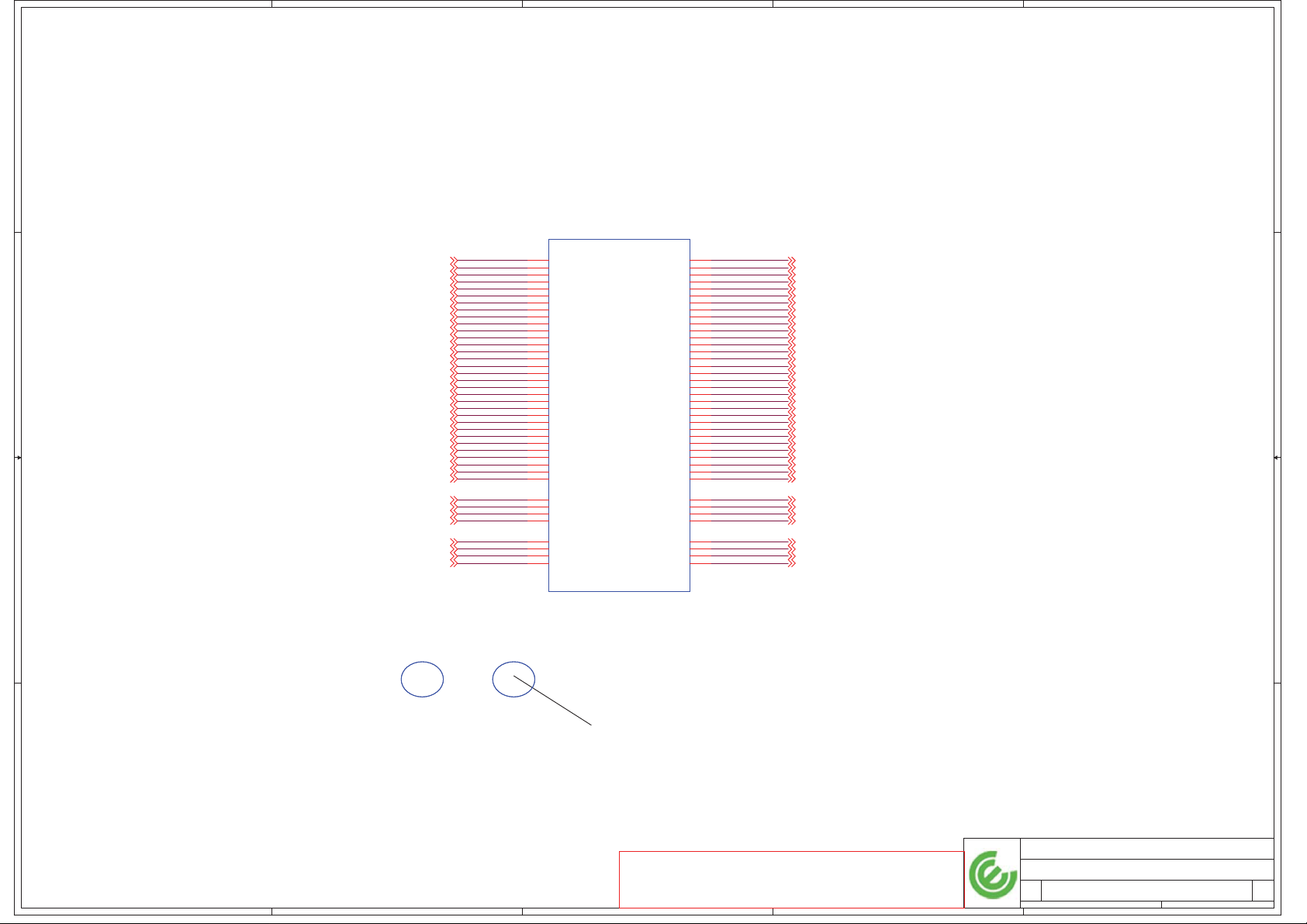

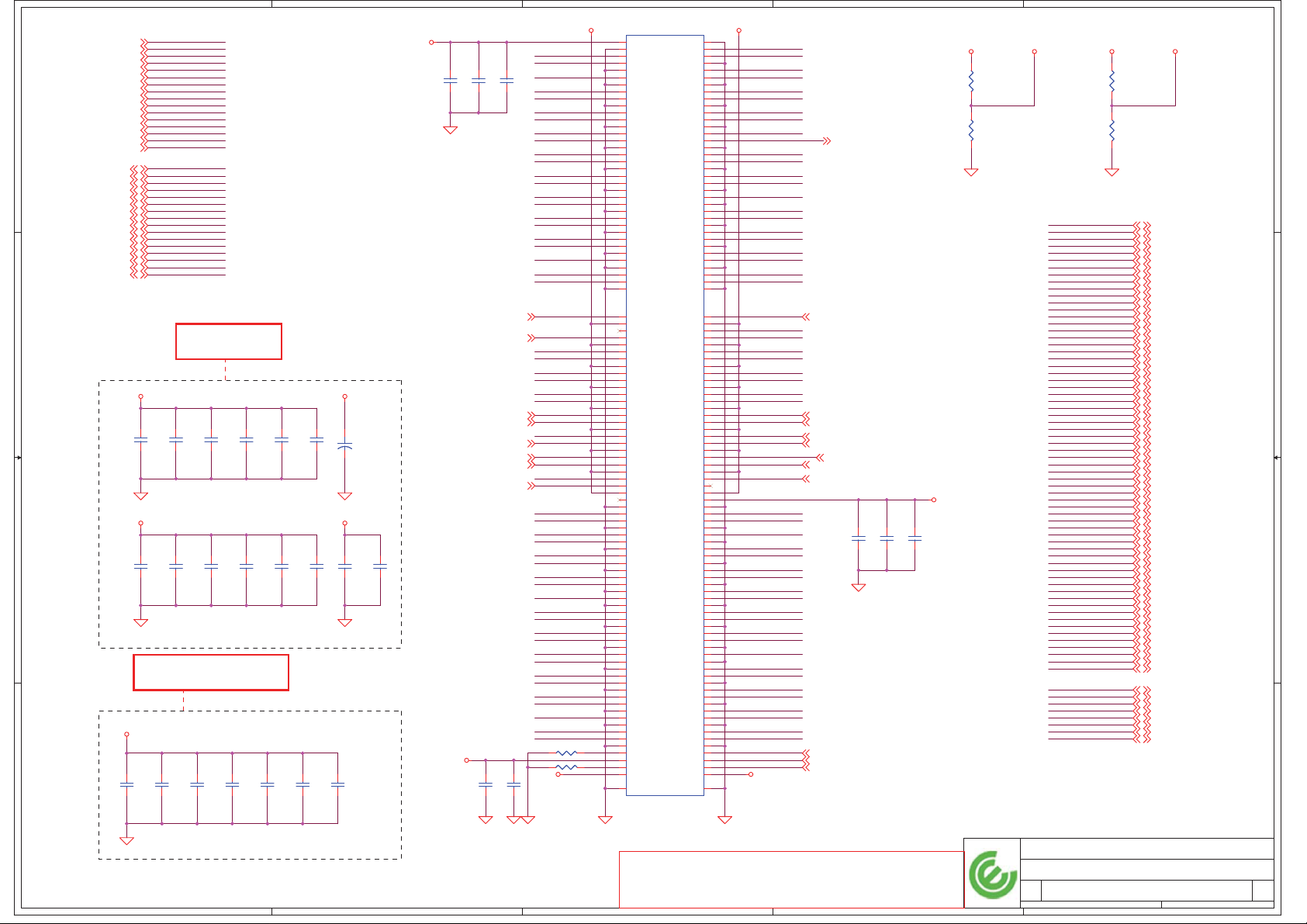

Page 3

5

4

3

2

1

SB820M

POWER STATES

State

D D

S0 (Full ON) / M0

S3 (Suspend to RAM) / M1

S4 (Suspend to DISK) / M1 ON ON ONOFF

S5 (SOFT OFF) / M1 ON ON ONOFFLOW LOW HIGHLOW

S3 (Suspend to RAM) / M-OFF

S4 (Suspend to DISK) / M-OFF

S5 (SOFT OFF) / M-OFF

Signal

SLP

SLP

S3#

S4#

HIGH HIGH HIGH

HIGH

LOW HIGH HIGH HIGH ON ON ON ONOFF

LOW

LOW HIGH HIGHLOW

LOW

LOW HIGH HIGH HIGH LOW ON ONOFF OFF OFF

LOW LOW LOW LOW ON OFF OFF OFF OFF

LOW LOW LOW LOW LOW ON OFF OFF OFF OFF

SLP

S5#

HIGH

S4

STATE#

SLP

M#

HIGH

HIGH

ALWAYS

PLANE

ON

M

PLANE

ON

SUS

RUN

PLANE

PLANE

ON ON ON

OFF

OFF

CLOCKS

USB PORT#

0

1

2

3

4

5

6

7

DESTINATION

USB (Right)

USB (Right)

USB (Left)

None

MINI CARD - WLAN

MINI CARD - WWAN

Bloetooth

None

Card Reader8

C C

PM TABLE

State

power

plane

B+

+5VALW

+3VALW

+1.1VALW

+1.5V

+5VS

+3VS

+1.8VS

+1.5VS

+1.1VS

+0.75VS

+2.5VDDA

+CPU_VDDR

+NB_CORE

+CPU_CORE

+VDDNB

9

11

12

13

Camera

None10

None

None

None

RS880M

S0

S3

B B

S5 S4/AC

S5 S4/AC don't exist

ON

ON

ON ON

ON

OFF

OFFOFF

OFFON

OFF

OFF

PCIE

Lane 1

Lane 2

Lane 3

Lane 4

Lane 5

DESTINATION

10 / 100 LAN

MINI CARD - WLAN

MINI CARD - WWAN

None

None

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Index and Config.

Index and Config.

Index and Config.

LA-6132P

LA-6132P

LA-6132P

345Monday, May 03, 2010

345Monday, May 03, 2010

345Monday, May 03, 2010

1

1.0

1.0

1.0

of

of

of

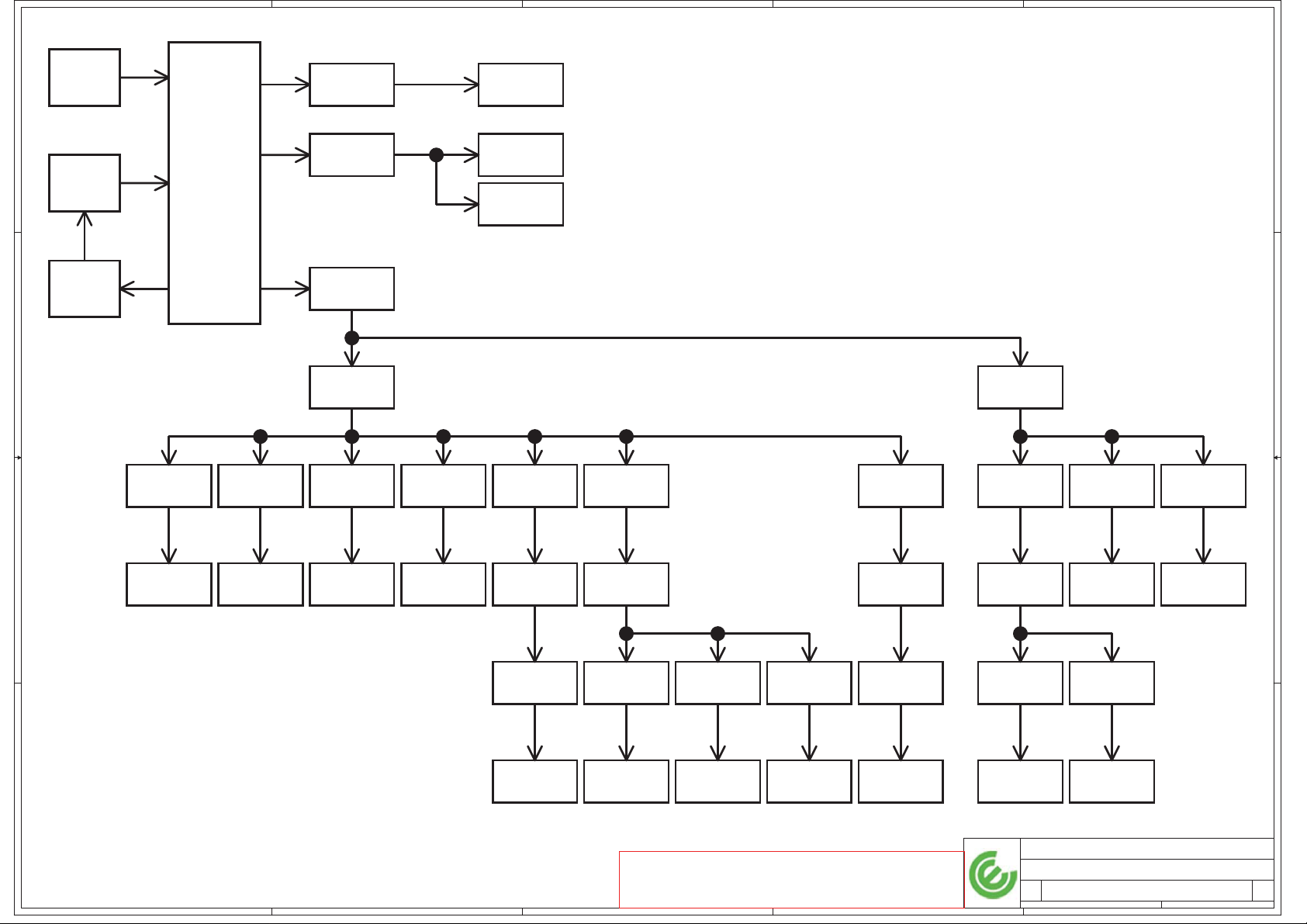

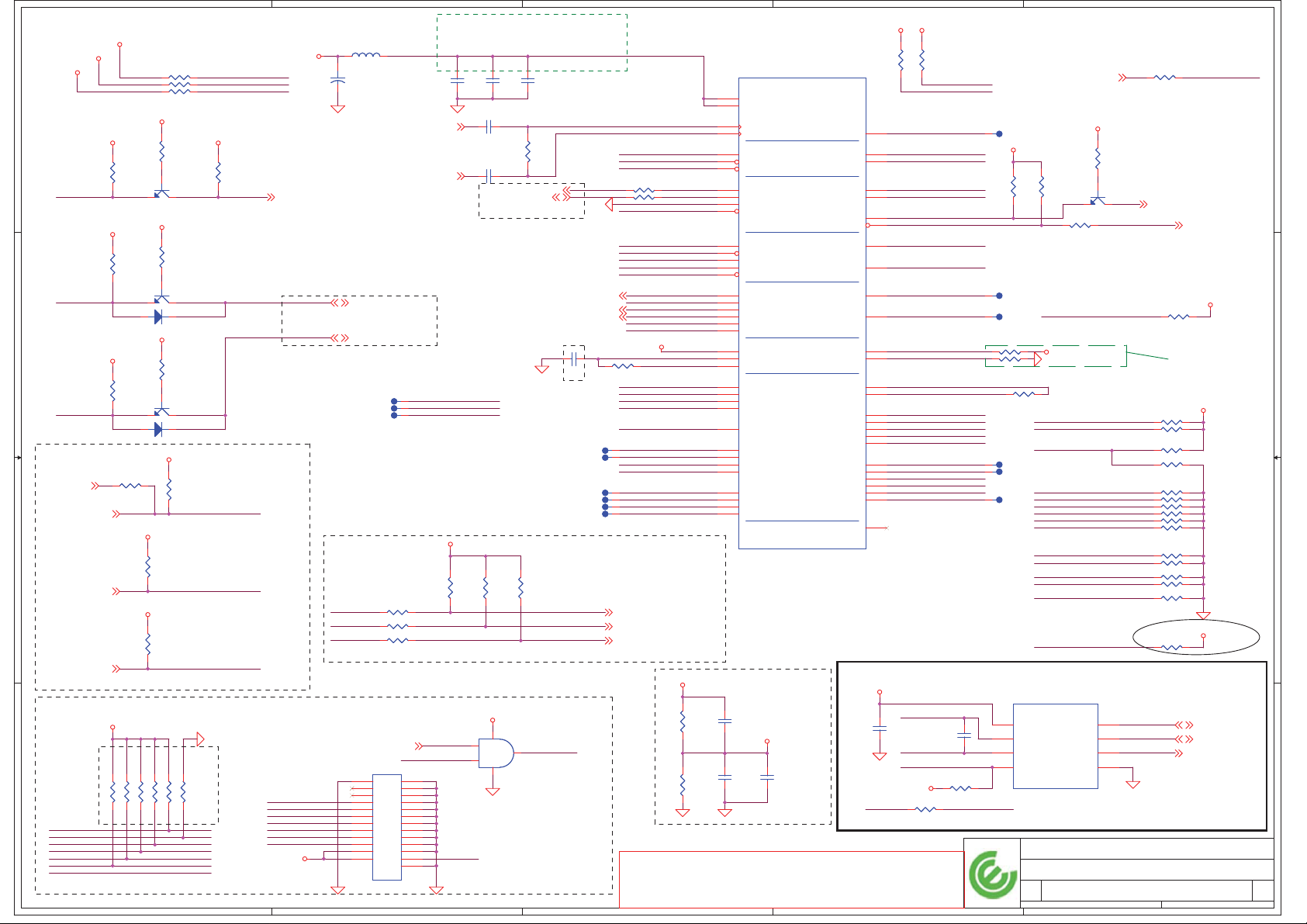

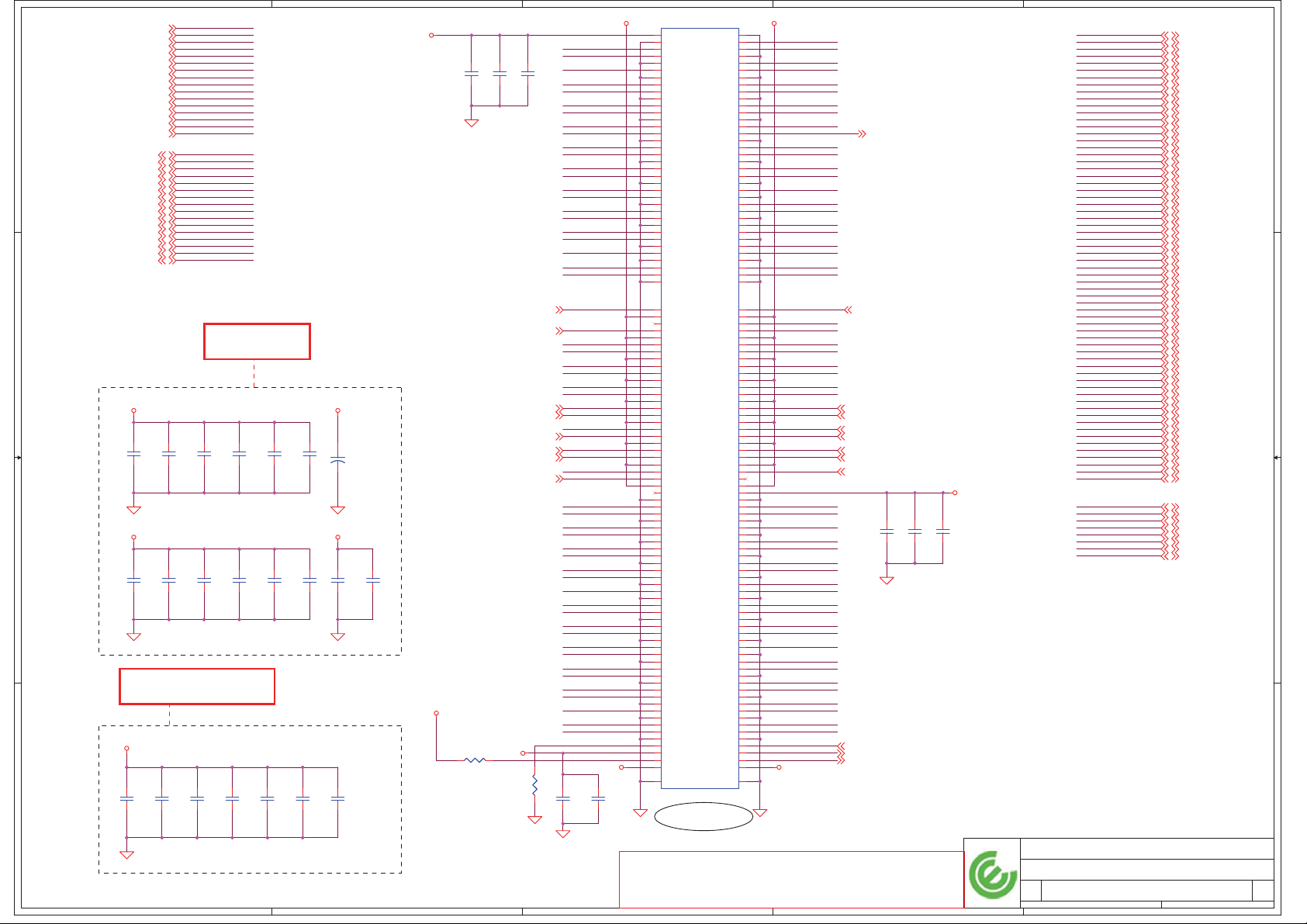

Page 4

5

4

3

2

1

ADAPTER

EN_INVPWR

INVPWR_B+SI3457

(QV6)

D D

VR_ON

ISL6265

+CPU_CORE

(PU14)

BATTERY

+PWR_SRC

+VDDNB

CHARGER

TPS51427

(PU2)

MAINPWON

C C

TPS51218

(PU15)

TPS2062

(UI13)

+5VALW

TPS2062

(UI14)

TPS2062

(UI15)

NTMS4920

(QZ3)

TPS51218

(PU10)

TPS51218

(PU7)

+3VALW

NTMS4920

(QZ8)

SI3456DY

(QZ11)

APL5912

(PU11)

SUSP#

B B

+NB_CORE

A A

USB_EN#

+USB_VCCA

+5V_ESAUSB

USB_PWR_EN#

USB_EN#

+USB_SIDE

_PWR

CAM_ON/OFF#

SUSP

+5VS

SI2301

(QO4)

+5VS_CAM

SYSON

+1.5V

SI4634DY

(QZ12)

SUSP

+1.5VS

APL5912

(PU12)

SUSP#

+CPU_VDDR

(0.9V)

APL5331

(PU8)

SUSP

+0.75VS

POK

+1.1VALW

SI4634DY

(QZ15)

SUSP

+1.1VS

SUSP

+3VS

APL5508

(PU13)

+2.5VDDA

EN_WOL#

+3V_LAN

AO3413

(QV8)

ENVDD

LCD_VCC_TEST_EN

+LCD_VDD

SUSP#

+1.8VS

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Power Rail

Power Rail

Power Rail

LA-6132P

LA-6132P

LA-6132P

445Monday, May 03, 2010

445Monday, May 03, 2010

445Monday, May 03, 2010

1

1.0

1.0

1.0

of

of

of

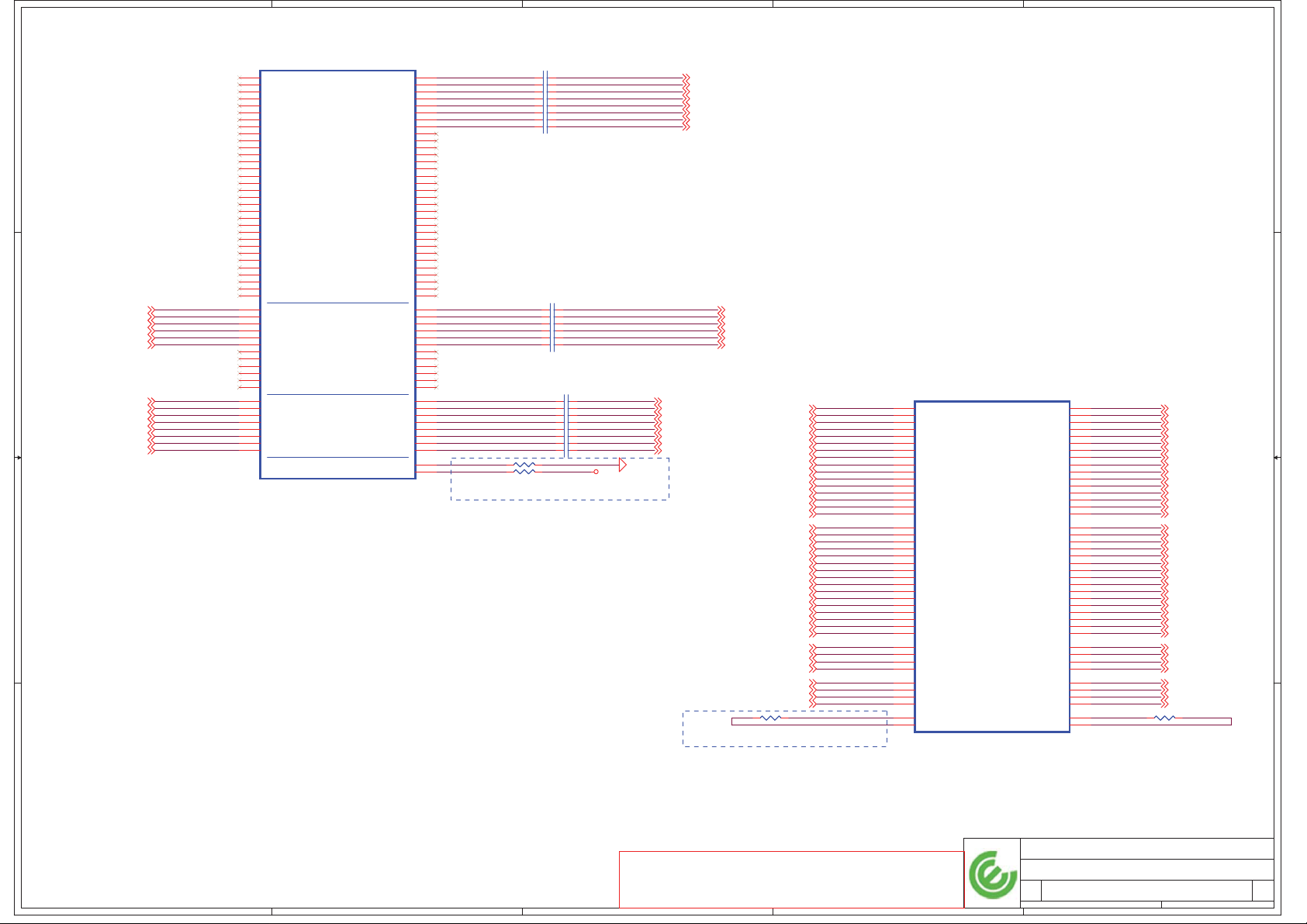

Page 5

5

4

3

2

1

1K

D D

AN4

ASB2

AN5

CPU_SIC

CPU_SID

1K

2.2K

+1.5V

+3VS

MMBT3904

MMBT3904

UT5 @

8

(CPU_Thermal)

7

SMBUS Address [TBD]

2.2K

AD22

MEM_SMBCLK

AE22

C C

MEM_SMBDATA

10K

+3VALW

10K

F5

SB_SMB_CLK1

F4

SB 820M

SB_SMB_DAT1

10K

+3VALW

10K

D25

SB_SMB_CLK2

F23

SB_SMB_DAT2

1K

+1.5V

202

200

202

200

8

7

JDIMMA

JDIMMB

UT7

(NB_Thermal)

SMBUS Address [TBD]

SMBUS Address [TBD]

SMBUS Address [TBD]

1K

B26

SB_SMB_CLK3

F26

B B

SB_SMB_DAT3

0R @

0R @

4.7K

4.7K

77

EC_SMB_CK1

78

EC_SMB_DA1

KB 926

79

EC_SMB_CK2

80

EC_SMB_DA2

A A

100R

100R

2.2K @

2.2K @

+5VALW

PJBATT

7

(BattERy conn)

6

+3VALW +3VS

2.2K

2.2K

SMBUS Address [TBD]

0R @

0R @

0R @

0R @

0R @

0R @

WWAN_SMB_CK_R

WWAN_SMB_DA_R

WWAN_SMB_CK_R

WWAN_SMB_DA_R

LAN_SMB_CK_R

LAN_SMB_DA_R

30

32

30

32

30

32

JWLAN1

JWWAN1

UL10 (LAN)

SMBUS Address [TBD]

SMBUS Address [TBD]

SMBUS Address [TBD]

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SMBus Topology

SMBus Topology

SMBus Topology

LA-6132P

LA-6132P

LA-6132P

545Monday, May 03, 2010

545Monday, May 03, 2010

545Monday, May 03, 2010

1

1.0

1.0

1.0

of

of

of

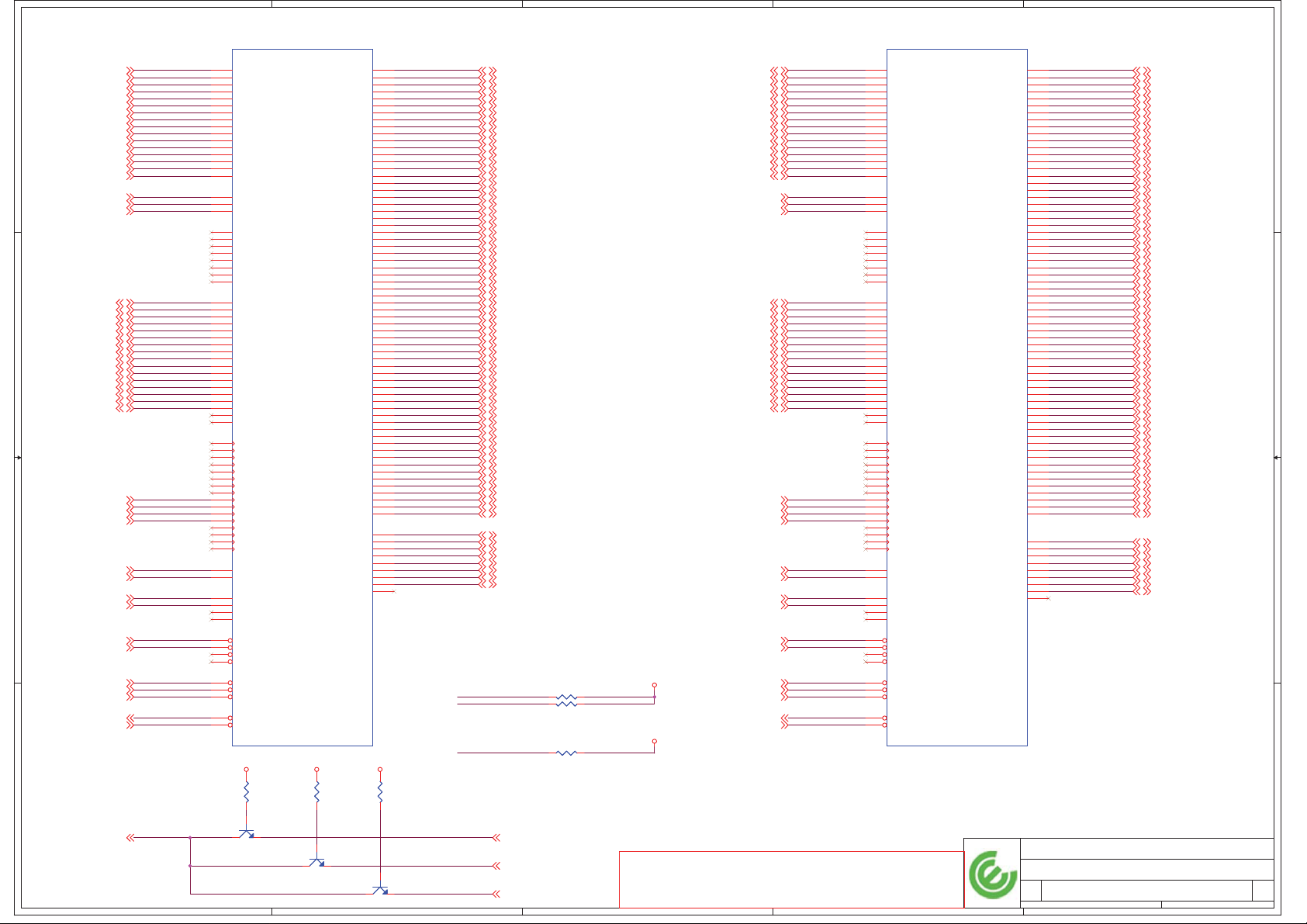

Page 6

5

D D

C C

B B

4

UU1A

K325@

UU1A

K325@

H_CADIP0<12>

H_CADIN0<12>

H_CADIP1<12>

H_CADIN1<12>

H_CADIP2<12>

H_CADIN2<12>

H_CADIP3<12>

H_CADIN3<12>

H_CADIP4<12>

H_CADIN4<12>

H_CADIP5<12>

H_CADIN5<12>

H_CADIP6<12>

H_CADIN6<12>

H_CADIP7<12>

H_CADIN7<12>

H_CADIP8<12>

H_CADIN8<12>

H_CADIP9<12>

H_CADIN9<12>

H_CADIP10<12>

H_CADIN10<12>

H_CADIP11<12>

H_CADIN11<12>

H_CADIP12<12>

H_CADIN12<12>

H_CADIP13<12>

H_CADIN13<12>

H_CADIP14<12>

H_CADIN14<12>

H_CADIP15<12>

H_CADIN15<12>

H_CLKIP0<12>

H_CLKIN0<12>

H_CLKIP1<12>

H_CLKIN1<12>

H_CTLIP0<12>

H_CTLIN0<12>

H_CTLIP1<12>

H_CTLIN1<12>

H_CADIP0

H_CADIN0

H_CADIP1

H_CADIN1

H_CADIP2

H_CADIN2

H_CADIP3

H_CADIN3

H_CADIP4

H_CADIN4

H_CADIP5

H_CADIN5

H_CADIP6

H_CADIN6

H_CADIP7

H_CADIN7

H_CADIP8

H_CADIN8

H_CADIP9

H_CADIN9

H_CADIP10

H_CADIN10

H_CADIP11

H_CADIN11

H_CADIP12

H_CADIN12

H_CADIP13

H_CADIN13

H_CADIP14

H_CADIN14

H_CADIP15

H_CADIN15

H_CLKIP0

H_CLKIN0

H_CLKIP1

H_CLKIN1

H_CTLIP0

H_CTLIN0

H_CTLIP1

H_CTLIN1

H2

H1

K2

K1

K3

K4

M2

M1

P2

P1

P3

P4

T2

T1

T3

T4

G6

G5

H4

H3

J6

J5

L6

L5

P6

P5

R7

R6

U6

U5

W7

W6

M3

M4

M8

M7

V2

V1

Y6

Y5

ASB2_BGA812

ASB2_BGA812

L0_CADIN_H0

L0_CADIN_L0

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H15

L0_CADIN_L15

L0_CLKIN_H0

L0_CLKIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

3

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

HT LINK

HT LINK

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

2

H_CADOP0

AK1

H_CADON0

AK2

H_CADOP1

AF4

H_CADON1

AF3

H_CADOP2

AF1

H_CADON2

AF2

H_CADOP3

AD4

H_CADON3

AD3

H_CADOP4

AB4

H_CADON4

AB3

H_CADOP5

AB1

H_CADON5

AB2

H_CADOP6

Y4

H_CADON6

Y3

H_CADOP7

Y1

H_CADON7

Y2

H_CADOP8

AH1

H_CADON8

AH2

H_CADOP9

AK3

H_CADON9

AK4

H_CADOP10

AH3

H_CADON10

AH4

H_CADOP11

AE9

H_CADON11

AE8

H_CADOP12

AE6

H_CADON12

AE5

H_CADOP13

AC7

H_CADON13

AC6

H_CADOP14

AB9

H_CADON14

AB8

H_CADOP15

AB6

H_CADON15

AB5

H_CLKOP0

AD1

H_CLKON0

AD2

H_CLKOP1

AF6

H_CLKON1

AF5

H_CTLOP0

V4

H_CTLON0

V3

H_CTLOP1

Y8

H_CTLON1

Y9

H_CADOP0 <12>

H_CADON0 <12>

H_CADOP1 <12>

H_CADON1 <12>

H_CADOP2 <12>

H_CADON2 <12>

H_CADOP3 <12>

H_CADON3 <12>

H_CADOP4 <12>

H_CADON4 <12>

H_CADOP5 <12>

H_CADON5 <12>

H_CADOP6 <12>

H_CADON6 <12>

H_CADOP7 <12>

H_CADON7 <12>

H_CADOP8 <12>

H_CADON8 <12>

H_CADOP9 <12>

H_CADON9 <12>

H_CADOP10 <12>

H_CADON10 <12>

H_CADOP11 <12>

H_CADON11 <12>

H_CADOP12 <12>

H_CADON12 <12>

H_CADOP13 <12>

H_CADON13 <12>

H_CADOP14 <12>

H_CADON14 <12>

H_CADOP15 <12>

H_CADON15 <12>

H_CLKOP0 <12>

H_CLKON0 <12>

H_CLKOP1 <12>

H_CLKON1 <12>

H_CTLOP0 <12>

H_CTLON0 <12>

H_CTLOP1 <12>

H_CTLON1 <12>

1

UU1

V105@UU1

K125@UU1

K125@

ASB2_BGA812

ASB2_BGA812

V105@UU1

ASB2_BGA812

ASB2_BGA812

SA00003RI0L SA00003TL0L

V105 PART NO. need apply again

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

ASB2 HT I/F & FAN

ASB2 HT I/F & FAN

ASB2 HT I/F & FAN

LA-6132P

LA-6132P

LA-6132P

645Tuesday, May 04, 2010

645Tuesday, May 04, 2010

645Tuesday, May 04, 2010

1

1.0

1.0

1.0

of

of

of

Page 7

5

UU1B

K325@

UU1B

K325@

DDR_A_MA0<10>

DDR_A_MA1<10>

DDR_A_MA2<10>

DDR_A_MA3<10>

DDR_A_MA4<10>

DDR_A_MA5<10>

DDR_A_MA6<10>

D D

C C

B B

A A

DDR_A_MA7<10>

DDR_A_MA8<10>

DDR_A_MA9<10>

DDR_A_MA10<10>

DDR_A_MA11<10>

DDR_A_MA12<10>

DDR_A_MA13<10>

DDR_A_MA14<10>

DDR_A_MA15<10>

DDR_A_BS0<10>

DDR_A_BS1<10>

DDR_A_BS2<10>

DDR_A_DQS0<10>

DDR_A_DQS#0<10>

DDR_A_DQS1<10>

DDR_A_DQS#1<10>

DDR_A_DQS2<10>

DDR_A_DQS#2<10>

DDR_A_DQS3<10>

DDR_A_DQS#3<10>

DDR_A_DQS4<10>

DDR_A_DQS#4<10>

DDR_A_DQS5<10>

DDR_A_DQS#5<10>

DDR_A_DQS6<10>

DDR_A_DQS#6<10>

DDR_A_DQS7<10>

DDR_A_DQS#7<10>

M_CLK_DDR1<10>

M_CLK_DDR#1<10>

M_CLK_DDR0<10>

M_CLK_DDR#0<10>

DDR_CKE0_DIMMA<10>

DDR_CKE1_DIMMA<10>

M_ODT0<10>

M_ODT1<10>

DDR_CS0_DIMMA#<10>

DDR_CS1_DIMMA#<10>

DDR_A_RAS#<10>

DDR_A_CAS#<10>

DDR_A_WE#<10>

DDR_A_RST#<10>

DDR_A_EVENT#<10>

CPU_MEMHOT#<18>

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS7

DDR_A_DQS#7

M_CLK_DDR1

M_CLK_DDR#1

M_CLK_DDR0

M_CLK_DDR#0

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

M_ODT0

M_ODT1

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_A_RAS#

DDR_A_CAS#

DDR_A_WE#

DDR_A_RST#

DDR_A_EVENT#

5

AC26

W29

AB29

Y30

U27

V30

U28

R27

R26

P27

AC28

T30

P28

AG28

M29

P30

AE28

AC29

R29

H27

H29

L29

L28

F29

G29

J29

K30

E12

F12

G17

H17

E25

F25

E28

F28

AG26

AH26

AH22

AG22

AG15

AH15

AJ11

AK12

J27

J26

E20

E19

D18

F19

P26

M26

W27

W26

AB27

AB26

Y28

Y27

AH17

AG17

AK18

AJ17

M28

M30

AG29

AJ30

AF27

AJ29

AF29

AH30

AE29

AH29

AC27

AF30

AE27

L27

M32

RU64

RU64

2.2K_0402_5%

2.2K_0402_5%

QU6

QU6

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MA_BANK0

MA_BANK1

MA_BANK2

MA_CHECK0

MA_CHECK1

MA_CHECK2

MA_CHECK3

MA_CHECK4

MA_CHECK5

MA_CHECK6

MA_CHECK7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

MA_DQS_H8

MA_DQS_L8

MA_CLK_H0

MA_CLK_L0

MA_CLK_H1

MA_CLK_L1

MA_CLK_H2

MA_CLK_L2

MA_CLK_H3

MA_CLK_L3

MA_CLK_H4

MA_CLK_L4

MA_CLK_H5

MA_CLK_L5

MA_CLK_H6

MA_CLK_L6

MA_CLK_H7

MA_CLK_L7

MA_CKE0

MA_CKE1

MA0_ODT0

MA0_ODT1

MA1_ODT0

MA1_ODT1

MA0_CS_L0

MA0_CS_L1

MA1_CS_L0

MA1_CS_L1

MA_RAS_L

MA_CAS_L

MA_WE_L

MA_RESET_L

FREE|MA_EVENT_L

ASB2_BGA812

ASB2_BGA812

+1.5V +1.5V

12

2

DDRIII CHANNEL A

DDRIII CHANNEL A

RU65

RU65

2.2K_0402_5%

2.2K_0402_5%

31

QU7

QU7

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DM8

12

RU66

RU66

2.2K_0402_5%

2.2K_0402_5%

2

31

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

QU8

QU8

+3VS

F11

E11

E14

E15

H12

G12

H14

H15

E17

D16

F22

D20

F15

G15

G20

G22

G23

D22

G26

F26

E22

H22

D24

H25

H26

F27

E29

F30

E26

D26

G28

D28

AJ28

AJ26

AG25

AJ25

AK30

AH27

AF25

AF23

AG23

AJ23

AF20

AF19

AK24

AF22

AJ20

AG20

AG19

AF17

AG14

AF14

AK20

AH19

AF15

AK14

AH12

AG12

AF12

AF11

AJ14

AJ12

AH11

AG11

G14

H19

E23

E27

AJ27

AK22

AK16

AL12

H30

12

2

31

4

4

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_EVENT#

DDR_B_EVENT#

SB_MEMHOT#

3

Processor DDR3 Memory Interface

DDR_A_D0 <10>

DDR_A_D1 <10>

DDR_A_D2 <10>

DDR_A_D3 <10>

DDR_A_D4 <10>

DDR_A_D5 <10>

DDR_A_D6 <10>

DDR_A_D7 <10>

DDR_A_D8 <10>

DDR_A_D9 <10>

DDR_A_D10 <10>

DDR_A_D11 <10>

DDR_A_D12 <10>

DDR_A_D13 <10>

DDR_A_D14 <10>

DDR_A_D15 <10>

DDR_A_D16 <10>

DDR_A_D17 <10>

DDR_A_D18 <10>

DDR_A_D19 <10>

DDR_A_D20 <10>

DDR_A_D21 <10>

DDR_A_D22 <10>

DDR_A_D23 <10>

DDR_A_D24 <10>

DDR_A_D25 <10>

DDR_A_D26 <10>

DDR_A_D27 <10>

DDR_A_D28 <10>

DDR_A_D29 <10>

DDR_A_D30 <10>

DDR_A_D31 <10>

DDR_A_D32 <10>

DDR_A_D33 <10>

DDR_A_D34 <10>

DDR_A_D35 <10>

DDR_A_D36 <10>

DDR_A_D37 <10>

DDR_A_D38 <10>

DDR_A_D39 <10>

DDR_A_D40 <10>

DDR_A_D41 <10>

DDR_A_D42 <10>

DDR_A_D43 <10>

DDR_A_D44 <10>

DDR_A_D45 <10>

DDR_A_D46 <10>

DDR_A_D47 <10>

DDR_A_D48 <10>

DDR_A_D49 <10>

DDR_A_D50 <10>

DDR_A_D51 <10>

DDR_A_D52 <10>

DDR_A_D53 <10>

DDR_A_D54 <10>

DDR_A_D55 <10>

DDR_A_D56 <10>

DDR_A_D57 <10>

DDR_A_D58 <10>

DDR_A_D59 <10>

DDR_A_D60 <10>

DDR_A_D61 <10>

DDR_A_D62 <10>

DDR_A_D63 <10>

DDR_A_DM0 <10>

DDR_A_DM1 <10>

DDR_A_DM2 <10>

DDR_A_DM3 <10>

DDR_A_DM4 <10>

DDR_A_DM5 <10>

DDR_A_DM6 <10>

DDR_A_DM7 <10>

DDR_A_EVENT#

DDR_B_EVENT#

SB_MEMHOT#

RU1 1K_0402_5%RU1 1K_0402_5%

RU2 1K_0402_5%RU2 1K_0402_5%

RU68 2.2K_0402_5%RU68 2.2K_0402_5%

DDR_A_EVENT# <10>

DDR_B_EVENT# <11>

SB_MEMHOT# <16>

12

12

12

+1.5V

+3VS

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

UU1C

K325@

UU1C

K325@

DDR_B_MA0<11>

DDR_B_MA1<11>

DDR_B_MA2<11>

DDR_B_MA3<11>

DDR_B_MA4<11>

DDR_B_MA5<11>

DDR_B_MA6<11>

DDR_B_MA7<11>

DDR_B_MA8<11>

DDR_B_MA9<11>

DDR_B_MA10<11>

DDR_B_MA11<11>

DDR_B_MA12<11>

DDR_B_MA13<11>

DDR_B_MA14<11>

DDR_B_MA15<11>

DDR_B_BS0<11>

DDR_B_BS1<11>

DDR_B_BS2<11>

DDR_B_DQS0<11>

DDR_B_DQS#0<11>

DDR_B_DQS1<11>

DDR_B_DQS#1<11>

DDR_B_DQS2<11>

DDR_B_DQS#2<11>

DDR_B_DQS3<11>

DDR_B_DQS#3<11>

DDR_B_DQS4<11>

DDR_B_DQS#4<11>

DDR_B_DQS5<11>

DDR_B_DQS#5<11>

DDR_B_DQS6<11>

DDR_B_DQS#6<11>

DDR_B_DQS7<11>

DDR_B_DQS#7<11>

M_CLK_DDR3<11>

M_CLK_DDR#3<11>

M_CLK_DDR2<11>

M_CLK_DDR#2<11>

DDR_CKE2_DIMMB<11>

DDR_CKE3_DIMMB<11>

M_ODT2<11>

M_ODT3<11>

DDR_CS2_DIMMB#<11>

DDR_CS3_DIMMB#<11>

DDR_B_RAS#<11>

DDR_B_CAS#<11>

DDR_B_WE#<11>

DDR_B_RST#<11>

DDR_B_EVENT#<11>

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

DDR_B_BS0

DDR_B_BS1

DDR_B_BS2

DDR_B_DQS0

DDR_B_DQS#0

DDR_B_DQS1

DDR_B_DQS#1

DDR_B_DQS2

DDR_B_DQS#2

DDR_B_DQS3

DDR_B_DQS#3

DDR_B_DQS4

DDR_B_DQS#4

DDR_B_DQS5

DDR_B_DQS#5

DDR_B_DQS6

DDR_B_DQS#6

DDR_B_DQS7

DDR_B_DQS#7

M_CLK_DDR3

M_CLK_DDR#3

M_CLK_DDR2

M_CLK_DDR#2

DDR_CKE2_DIMMB

DDR_CKE3_DIMMB

M_ODT2

M_ODT3

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

DDR_B_RAS#

DDR_B_CAS#

DDR_B_WE#

DDR_B_RST#

DDR_B_EVENT#

AC33

W33

AD32

AJ33

AE33

AD33

AN30

AM30

AN26

AM26

AL20

AM20

AM14

AN14

AD31

AD30

AB31

AB30

AB33

AB32

AA32

AA33

AN21

AM21

AN22

AM22

AH33

AK32

AH31

AK31

AF31

AJ32

AF33

AK33

AF32

AH32

AG33

M33

Y32

Y33

Y31

V31

V33

U33

V32

T33

T31

T32

P31

P33

R33

G33

H31

K32

L33

F32

G32

K31

K33

B16

A15

A21

B20

B28

A28

D33

D32

J33

H32

A22

A23

C22

B22

P32

N33

L32

ASB2_BGA812

ASB2_BGA812

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_CHECK0

MB_CHECK1

MB_CHECK2

MB_CHECK3

MB_CHECK4

MB_CHECK5

MB_CHECK6

MB_CHECK7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

MB_DQS_H8

MB_DQS_L8

MB_CLK_H0

MB_CLK_L0

MB_CLK_H1

MB_CLK_L1

MB_CLK_H2

MB_CLK_L2

MB_CLK_H3

MB_CLK_L3

MB_CLK_H4

MB_CLK_L4

MB_CLK_H5

MB_CLK_L5

MB_CLK_H6

MB_CLK_L6

MB_CLK_H7

MB_CLK_L7

MB_CKE0

MB_CKE1

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB1_ODT1

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB1_CS_L1

MB_RAS_L

MB_CAS_L

MB_WE_L

MB_RESET_L

FREE|MB_EVENT_L

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

DDRIII CHANNEL B

DDRIII CHANNEL B

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DM8

A14

C14

A17

B18

A13

B14

A16

C16

A19

C20

C24

A25

A18

C18

B24

A24

C26

A27

A30

B30

A26

B26

A29

C30

B32

C32

F31

F33

A31

B31

D31

E33

AM32

AM31

AN29

AK28

AL33

AL32

AL30

AM29

AM28

AN27

AN25

AL24

AL28

AN28

AL26

AM25

AN23

AL22

AN18

AM18

AN24

AM24

AN19

AL18

AN16

AM16

AM12

AN12

AN17

AL16

AL14

AN13

D14

A20

C28

C33

AN31

AK26

AN20

AN15

H33

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

1

DDR_B_D0 <11>

DDR_B_D1 <11>

DDR_B_D2 <11>

DDR_B_D3 <11>

DDR_B_D4 <11>

DDR_B_D5 <11>

DDR_B_D6 <11>

DDR_B_D7 <11>

DDR_B_D8 <11>

DDR_B_D9 <11>

DDR_B_D10 <11>

DDR_B_D11 <11>

DDR_B_D12 <11>

DDR_B_D13 <11>

DDR_B_D14 <11>

DDR_B_D15 <11>

DDR_B_D16 <11>

DDR_B_D17 <11>

DDR_B_D18 <11>

DDR_B_D19 <11>

DDR_B_D20 <11>

DDR_B_D21 <11>

DDR_B_D22 <11>

DDR_B_D23 <11>

DDR_B_D24 <11>

DDR_B_D25 <11>

DDR_B_D26 <11>

DDR_B_D27 <11>

DDR_B_D28 <11>

DDR_B_D29 <11>

DDR_B_D30 <11>

DDR_B_D31 <11>

DDR_B_D32 <11>

DDR_B_D33 <11>

DDR_B_D34 <11>

DDR_B_D35 <11>

DDR_B_D36 <11>

DDR_B_D37 <11>

DDR_B_D38 <11>

DDR_B_D39 <11>

DDR_B_D40 <11>

DDR_B_D41 <11>

DDR_B_D42 <11>

DDR_B_D43 <11>

DDR_B_D44 <11>

DDR_B_D45 <11>

DDR_B_D46 <11>

DDR_B_D47 <11>

DDR_B_D48 <11>

DDR_B_D49 <11>

DDR_B_D50 <11>

DDR_B_D51 <11>

DDR_B_D52 <11>

DDR_B_D53 <11>

DDR_B_D54 <11>

DDR_B_D55 <11>

DDR_B_D56 <11>

DDR_B_D57 <11>

DDR_B_D58 <11>

DDR_B_D59 <11>

DDR_B_D60 <11>

DDR_B_D61 <11>

DDR_B_D62 <11>

DDR_B_D63 <11>

DDR_B_DM0 <11>

DDR_B_DM1 <11>

DDR_B_DM2 <11>

DDR_B_DM3 <11>

DDR_B_DM4 <11>

DDR_B_DM5 <11>

DDR_B_DM6 <11>

DDR_B_DM7 <11>

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

ASB2 DDRIII MEMORY I/F

ASB2 DDRIII MEMORY I/F

ASB2 DDRIII MEMORY I/F

LA-6132P

LA-6132P

LA-6132P

745Tuesday, May 04, 2010

745Tuesday, May 04, 2010

745Tuesday, May 04, 2010

1

1.0

1.0

1.0

of

of

of

Page 8

5

+1.1VS

+1.5V

+CPU_VDDR

D D

CPU_ALERT#

C C

B B

A A

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

+1.5V

12

RU6

RU6

+1.5V

12

RU14

RU14

CPU_SID

+1.5V

12

RU22

RU22

CPU_SIC

RU60

1 2

VGATE<26,42>

0_0402_5%

0_0402_5%

CPU_PWRGD<16>

LDT_STOP#<13,16>

LDT_RST#<16>

Layout : Resistor placed close to CPU, trace reference to GND,

keep spacing 15mil to other signal.

+1.5V

@

@

12

1 2

RU57 10_0402_5%@ RU57 10_0402_5%@

1 2

RU58 10_0402_5%@ RU58 10_0402_5%@

1 2

RU59 10_0402_5%@ RU59 10_0402_5%@

+1.5V

12

RU4

RU4

@

@

2.2K_0402_5%

2.2K_0402_5%

2

1K_0402_5%

1K_0402_5%

QU2

@ QU2

@

3 1

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

+1.5V

12

RU15

RU15

2.2K_0402_5%

1K_0402_5%

1K_0402_5%

DU1 CH751H-40PT_SOD323-2DU1 CH751H-40PT_SOD323-2

1K_0402_5%

1K_0402_5%

DU2 CH751H-40PT_SOD323-2DU2 CH751H-40PT_SOD323-2

@

@

RU50220_0402_5%~D

RU50220_0402_5%~D

12

2.2K_0402_5%

2

QU4

QU4

3 1

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

2 1

+1.5V

12

RU20

RU20

2.2K_0402_5%

2.2K_0402_5%

2

QU5

QU5

3 1

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

2 1

+1.5VS

12

@RU60

@

RU28

RU28

300_0402_5%~D

300_0402_5%~D

+1.5VS

12

RU36

RU36

300_0402_5%~D

300_0402_5%~D

+1.5VS

12

RU46

RU46

300_0402_5%~D

300_0402_5%~D

@

@

@

@

@

@

RU53220_0402_5%~D

RU53220_0402_5%~D

RU54300_0402_5%~D RU54300_0402_5%~D

RU51220_0402_5%~D

RU51220_0402_5%~D

RU52220_0402_5%~D

RU52220_0402_5%~D

12

12

12

12

5

+3VS

12

RU7

RU7

SMB_ALERT#

CPU_PWRGD

LDT_STOP#

LDT_RST#

RU55300_0402_5%~D

RU55300_0402_5%~D

CPU_VLDT_SENSE

CPU_VDDIO_FB_H

CPU_VDDR_SENSE

4.7K_0402_5%

4.7K_0402_5%

+2.5VDDA

SMB_ALERT# <13,18,26>

EC_SMB_DA2

1 2

FBM_L11_201209_300L_0805

FBM_L11_201209_300L_0805

1

+

+

150U_B2_6.3VM_R45M

150U_B2_6.3VM_R45M

2

EC is PU to 3VALW

EC_SMB_CK2

CPU_SVC_R CPU_SVC

CPU_SVD_R

HDT Connector

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

+1.5V

4

LU1

LU1

CU1

CU1

CLK_HT_CPU_P<16>

CLK_HT_CPU_N<16>

EC_SMB_DA2 <20,26,28>

EC_SMB_CK2 <20,26,28>

TU21TU21

TU22TU22

TU23TU23

CPU_VDD0_RUN_FB_L

CPU_VDD0_RUN_FB_H

CPU_VDDNB_RUN_FB_H

Place close to CPU

RU44

RU44

1 2

0_0402_5%

0_0402_5%

RU45

RU45

1 2

0_0402_5%

0_0402_5%

RU47

RU47

1 2

0_0402_5%

0_0402_5%

VID Override Circuit

SB_PWRGD<13,18,26>

LDT_RST#

JPTU1 CONN@

JPTU1 CONN@

2

1

4

3

6

5

8

7

10

9

12

11

14

13

16

15

18

17

20

19

22

21

2423

26

SAMTEC_ASP-68200-07

SAMTEC_ASP-68200-07

4

LAYOUT: ROUTE VDDA TRACE APPROX.

50 mils WIDE (USE 2x25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

1

1

CU3

CU3

CU2

CU2

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1 2

CU5

CU5

169_0402_1%~D

169_0402_1%~D

1 2

CU6 3900P_0402_50V7K~DCU6 3900P_0402_50V7K~D

+1.5VS

12

RU38

RU38

RU39

RU39

1K_0402_5%

1K_0402_5%

+3VALW

SB_PWRGD

2

1

HDT_RST#

1

CU4

CU4

2

2

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

3900P_0402_50V7K~D

3900P_0402_50V7K~D

12

RU5

RU5

SB_SMB_CLK3<18>

SB_SMB_DAT3<18>

TSI to SB SMBUS3

PLACE THEM CLOSE TO

CPU WITHIN 1"

12

12

@

@

RU40

RU40

2.2K_0402_5%

2.2K_0402_5%

1K_0402_5%

1K_0402_5%

CPU_PWRGD_SVID_REGCPU_PWRGD

Close to LDT_RST# trace

5

UU6

UU6

P

B

4

Y

A

G

NC7SZ08P5X_NL_SC70-5

NC7SZ08P5X_NL_SC70-5

3

@

@

+CPU_VDDA

3300P_0402_50V7K~D

3300P_0402_50V7K~D

CPU_VDD0_RUN_FB_L<42>

CPU_VDD0_RUN_FB_H<42>

CPU_VDDNB_RUN_FB_H<42>

CU72 0.1U_0402_16V7K

CU72 0.1U_0402_16V7K

12

@

@

TU4TU4

TU5TU5

TU8TU8

TU9TU9

TU11TU11

TU12TU12

CPU_SVD

HDT_RST#

3

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

CPU_PWRGD

LDT_STOP#

LDT_RST#

@

CPU_SIC

RU90_0402_5%@RU90_0402_5%

1 2

CPU_SID

RU120_0402_5%@RU120_0402_5%

1 2

@

CPU_ALERT#

CPU_TDI

CPU_TRST#

CPU_TCK

CPU_TMS

CPU_DBREQ#

CPU_VDD0_RUN_FB_L

CPU_VLDT_SENSE

CPU_VDD0_RUN_FB_H

CPU_VDDNB_RUN_FB_H

CPU_VDDIO_FB_H

CPU_VDDR_SENSE

+CPU_M_VREF

RU21 39.2_0402_1%RU21 39.2_0402_1%

1 2

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_TEST9_ANALOGIN

CPU_TEST17_BP3

CPU_TEST16_BP2

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST7_ANALOG_T

CPU_TEST6_DIECRACKMON

CPU_TEST3

CPU_TEST2

CPU_SVC <42>

CPU_SVD <42>

CPU_PWRGD_SVID_REG <42>

+1.5V

RU49

RU49

RU56

RU56

UU1D

K325@

UU1D

K325@

A8

VDDA_1

B8

VDDA_2

A6

CLKIN_H

A7

CLKIN_L

D10

PWROK

E9

LDTSTOP_L

F9

RESET_L

AN4

SIC

AN5

SID

AM2

RSVD_SA0

AN3

ALERT_L

AM8

TDI

AL8

TRST_L

AK8

TCK

AN8

TMS

G9

DBREQ_L

D2

VSS_SENSE

E2

VLDT_SENSE

E1

VDD_SENSE

D1

VDDNB_SENSE

D3

VDDIO_SENSE

C2

VDDR_SENSE

A11

AM9

AN9

AH7

A9

B9

A5

B6

G8

F8

C8

D9

E8

C6

AK5

AJ7

M_VREF

M_ZN_H

M_ZN_L

BYPASSCLK_H

BYPASSCLK_L

PLLTEST0

PLLTEST1

ANALOGIN

BP3

BP2

BP1

BP0

ANALOG_T

DIECRACKMON

GATE0

DRAIN0

ASB2_BGA812

ASB2_BGA812

M_ZP

M_ZN

LAYOUT:PLACE CLOSE TO CPU

1

CU7

CU7

@

@

2

1 2

1K_0402_1%~D

1K_0402_1%~D

CU8

CU8

1 2

1K_0402_1%~D

1K_0402_1%~D

0.1U_0402_16V7K

0.1U_0402_16V7K

1

CU9

CU9

2

0.01U_0402_16V7K

0.01U_0402_16V7K

+CPU_M_VREF

1

2

RSVD|CORE_TYPE

MISC

MISC

THERMTRIP_L

PROCHOT_L

CPU_PRESENT_L

FBCLKOUT_H

FBCLKOUT_L

SCANSHIFTEN

PLLCHRZ_H

SINGLECHAIN

ANALOGOUT

1000P_0402_50V7K

1000P_0402_50V7K

SVC

SVD

THERMDC

THERMDA

TDO

DBRDY

RSVD3

HTREF1

HTREF0

SCANCLK1

TSTUPD

SCANEN

SCANCLK2

PLLCHRZ_L

BURNIN_L

DIG_T

M_TEST

CT1

CT1

@

@

2

+1.5V +1.5V

12

RU62

RU62

1K_0402_5%

1K_0402_5%

CPU_CORE_TYPE

M31

CPU_SVC_R

C1

CPU_SVD_R

B2

THERMDC_CPU

AL6

THERMDA_CPU

AM5

CPU_THERMTRIP#_R

AK6

CPU_PROCHOT#_R

AN6

CPU_TDO

AN7

CPU_DBRDY

H9

RSVD3

AM6

CPU_PRESENT_L

AJ9

CPU_HTREF1

V10

CPU_HTREF0

V9

CPU_TEST29_H_FBCLKOUT_P

B10

CPU_TEST29_L_FBCLKOUT_N

A10

CPU_TEST24_SCANCLK1

AK7

CPU_TEST23_TSTUPD

AG8

CPU_TEST22_SCANSHIFTEN

AK9

CPU_TEST21_SCANEN

AH9

CPU_TEST20_SCANCLK2

AM7

CPU_TEST28_H_PLLCHRZ_P

G11

CPU_TEST28_L_PLLCHRZ_N

H11

CPU_TEST27_SINGLECHAIN

AJ8

CPU_TEST26_BURNIN_L

AM4

CPU_TEST10_ANALOGOUT

D7

CPU_TEST8_DIG_T

B5

AG9

+3VS

THERMDA_CPU

1

2

2200P_0402_50V7K

2200P_0402_50V7K

THERMDC_CPU SMB_ALERT#

0.1U_0402_16V7K

0.1U_0402_16V7K

THERM#

+3VS

THERM# CPU_PROCHOT#

RT2

1 2

0_0402_5%

0_0402_5%

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

12

RU63

RU63

1K_0402_5%

1K_0402_5%

SB_SMB_CLK3

SB_SMB_DAT3

CT2

@ CT2

@

RT1

1 2

10K_0402_5%

10K_0402_5%

@RT2

@

RU10

RU10

1 2

1 2

RU23

RU23

1

2

@RT1

@

1

CPU_PROCHOT#_R

1 2

RU67 0_0402_5%RU67 0_0402_5%

10K_0402_5%

10K_0402_5%

QU1

QU1

H_THERMTRIP# <18>

CPU_PROCHOT#

RU61 1K_0402_5%RU61 1K_0402_5%

1 2

place them to CPU within 1.5"

RU24 510_0402_1%RU24 510_0402_1%

1 2

RU25 1K_0402_5%RU25 1K_0402_5%

1 2

RU26 1K_0402_5%RU26 1K_0402_5%

1 2

RU27 300_0402_5%~D@RU27 300_0402_5%~D@

1 2

RU29 510_0402_1%RU29 510_0402_1%

1 2

RU30 1K_0402_5%RU30 1K_0402_5%

1 2

RU31 1K_0402_5%RU31 1K_0402_5%

1 2

RU32 1K_0402_5%RU32 1K_0402_5%

1 2

RU33 1K_0402_5%RU33 1K_0402_5%

1 2

RU34 1K_0402_5%RU34 1K_0402_5%

1 2

RU35 300_0402_5%~D@RU35 300_0402_5%~D@

1 2

RU37 300_0402_5%~D@RU37 300_0402_5%~D@

1 2

RU41 1K_0402_5%RU41 1K_0402_5%

1 2

RU42 1K_0402_5%RU42 1K_0402_5%

1 2

RU43 0_0402_5%RU43 0_0402_5%

1 2

RU48 300_0402_5%~D@RU48 300_0402_5%~D@

1 2

EC_SMB_CK2

8

EC_SMB_DA2

7

6

5

CPU_PROCHOT# <16>

+1.5V

+1.5V

+1.1VS

EC_SMB_CK2 <20,26,28>

EC_SMB_DA2 <20,26,28>

SMB_ALERT# <13,18,26>

TU1TU1

+1.5V

12

12

RU11

RU11

1K_0402_5%

1K_0402_5%

300_0402_5%~D

300_0402_5%~D

1 2

RU13 0_0402_5%RU13 0_0402_5%

TU2TU2

CPU_PRESENT_L

TU3TU3

RU1844.2_0402_1%~D RU1844.2_0402_1%~D

RU1944.2_0402_1%~D RU1944.2_0402_1%~D

1 2

80.6_0402_1%~D

80.6_0402_1%~D

TU6TU6

TU7TU7

TU10TU10

1

2

3

4

EMC1402-1-ACZL-TR_MSOP8

EMC1402-1-ACZL-TR_MSOP8

VLDT

+1.1VS

route as differential

as short as possible

testpoint under package

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST26_BURNIN_L

CPU_TEST27_SINGLECHAIN

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST23_TSTUPD

CPU_TEST22_SCANSHIFTEN

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST18_PLLTEST1

CPU_TEST19_PLLTEST0

CPU_TEST9_ANALOGIN

CPU_TEST10_ANALOGOUT

UT5

@UT5

@

VDD

DP

DN

THERM#

SB_PROCHOT#<17>

+1.5V

RU3

RU3

1 2

2

3 1

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

SMCLK

SMDATA

ALERT#

GND

SMBus Address: 1001110X (b)

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

ASB2 CTRL & EMC1402

ASB2 CTRL & EMC1402

ASB2 CTRL & EMC1402

LA-6132P

LA-6132P

LA-6132P

845Tuesday, May 04, 2010

845Tuesday, May 04, 2010

845Tuesday, May 04, 2010

1

VLDT

1.0

1.0

1.0

of

Page 9

5

4

3

2

1

CPU BOTTOMSIDE DECOUPLING

+CPU_CORE

1

CU10

CU10

CU11

CU11

+CPU_CORE

D D

1

1

1

+

+

CU18

CU18

2

C C

+

+

CU19

CU19

CU14

CU14

2

2

@

@

330U_X_2VM_R6M

330U_X_2VM_R6M

330U_X_2VM_R6M

330U_X_2VM_R6M

+

+

330U_X_2VM_R6M

330U_X_2VM_R6M

2

+CPU_CORE

1

CU23

CU23

2

+1.5V

1

CU30

CU30

2

+1.5V

1

CU38

CU38

2

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

CU24

CU24

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

CU31

CU31

@

@

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

CU39

CU39

@

@

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

1

1

CU15

CU15

2

2

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

1

1

CU25

CU25

2

2

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

1

1

CU32

CU32

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

CU40

CU40

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

CU12

CU12

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

CU26

CU26

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

CU33

CU33

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

CU41

CU41

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

1

1

CU16

CU16

2

2

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

1

1

CU27

CU27

2

2

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

1

1

CU34

CU34

2

2

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

1

1

CU42

CU42

2

2

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

1

CU17

CU17

CU13

CU13

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

1

CU28

CU28

CU29

CU29

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

1

CU36

CU36

CU35

CU35

2

0.1U_0402_16V7K

0.1U_0402_16V7K

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

1

CU44

CU44

CU43

CU43

2

0.1U_0402_16V7K

0.1U_0402_16V7K

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

1

+VDDNB

2

180P_0402_50V8J~D

180P_0402_50V8J~D

CU20

CU20

1

2

180P_0402_50V8J~D

180P_0402_50V8J~D

1

1

CU37

CU37

2

2

0.01U_0402_16V7K

0.01U_0402_16V7K

1

2

180P_0402_50V8J~D

180P_0402_50V8J~D

1

1

CU21

CU21

2

2

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

180P_0402_50V8J~D

180P_0402_50V8J~D

1

CU22

CU22

2

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

Place close to CPU

+CPU_VDDR

1

CU45

CU45

+1.1VS

CU51

CU51

2

1

2

B B

CU47

CU47

CU46

CU46

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

CU52

CU52

CU53

CU53

2

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

CU48

CU48

2

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

1

CU54

CU54

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

1

1

CU49

CU49

CU50

CU50

2

2

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

1

1

2

Placement need check

CU56

CU56

CU55

CU55

2

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

1

2

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

1

1

CU57

CU57

2

2

180P_0402_50V8J~D

180P_0402_50V8J~D

+1.1VS

1

CU58

CU58

@

@

2

180P_0402_50V8J~D

180P_0402_50V8J~D

1

CU60

CU60

CU59

CU59

@

@

@

@

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

22U_0805_6.3V6M~D

22U_0805_6.3V6M~D

1

CU61

CU61

@

@

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

+1.5V

1

1

1

A A

1

CU63

CU63

CU62

CU62

Need discuss with AMD

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

2

CU64

CU64

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

5

CU65

CU65

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

CU66

CU66

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

CU67

CU67

2

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

1

1

CU68

CU68

2

2

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

CU69

CU69

CU70

CU70

2

180P_0402_50V8J~D

180P_0402_50V8J~D

180P_0402_50V8J~D

180P_0402_50V8J~D

1

1

CU71

CU71

2

2

180P_0402_50V8J~D

180P_0402_50V8J~D

4

180P_0402_50V8J~D

180P_0402_50V8J~D

+CPU_CORE

UU1E

K325@

UU1E

AA30

AB28

AE32

AC30

AC32

AE26

AE30

AF28

AG30

AG32

AD25

AA25

AC25

AB25

3

M10

M12

N11

N24

M27

U26

N32

U32

N30

R28

R30

R32

U29

U30

W28

W30

W32

N25

M25

D4

D5

D6

E5

E6

E7

F5

F6

F7

H7

H8

J8

E4

J10

J12

J14

J18

J20

J21

J23

J9

K10

K12

K14

K18

K20

K21

K23

N4

L11

L13

L7

L9

R4

M5

W4

N9

P15

P18

Y26

P29

Y29

V25

P25

K25

L25

T25

Y25

K325@

VDD_1

VDD_2

VDD_3

VDD_4

VDD_5

VDD_6

VDD_7

VDD_8

VDD_9

VDD_10

VDD_11

VDD_12

VDD_13

VDD_14

VDD_15

VDD_16

VDD_17

VDD_18

VDD_19

VDD_20

VDD_21

VDD_22

VDD_23

VDD_24

VDD_25

VDD_26

VDD_27

VDD_28

VDD_29

VDD_30

VDD_31

VDD_32

VDD_33

VDD_34

VDD_35

VDD_36

VDD_37

VDD_38

VDD_39

VDD_40

VDD_41

VDD_42

VDD_43

ASB2_BGA812

ASB2_BGA812

UU1F

K325@

UU1F

K325@

VDDIO_1

VDDIO_2

VDDIO_3

VDDIO_4

VDDIO_5

VDDIO_6

VDDIO_7

VDDIO_8

VDDIO_9

VDDIO_10

VDDIO_11

VDDIO_12

VDDIO_13

VDDIO_14

VDDIO_15

VDDIO_16

VDDIO_17

VDDIO_18

VDDIO_19

VDDIO_20

VDDIO_21

VDDIO_22

VDDIO_23

VDDIO_24

VDDIO_25

VDDIO_26

VDDIO_27

VDDIO_28

VDDIO_29

VDDIO_30

VDDIO_31

VDDIO_32

VDDIO_33

VDDIO_34

VDDIO_35

VDDIO_36

VDDIO_37

VDDIO_38

ASB2_BGA812

ASB2_BGA812

POWER1

POWER1

POWER2

POWER2

PROGEN_L

VDD_85

VDD_84

VDD_83

VDD_82

VDD_81

VDD_80

VDD_79

VDD_78

VDD_77

VDD_76

VDD_75

VDD_74

VDD_73

VDD_72

VDD_71

VDD_70

VDD_69

VDD_68

VDD_67

VDD_66

VDD_65

VDD_64

VDD_63

VDD_62

VDD_61

VDD_60

VDD_59

VDD_58

VDD_57

VDD_56

VDD_55

VDD_54

VDD_53

VDD_52

VDD_51

VDD_50

VDD_49

VDD_48

VDD_47

VDD_46

VDD_45

VDD_44

VLDT_A_1

VLDT_A_2

VLDT_A_3

VLDT_A_4

VLDT_B_1

VLDT_B_2

VLDT_B_3

VLDT_B_4

VDDR_1

VDDR_2

VDDR_3

VDDR_4

VDDR_5

VDDR_6

VDDR_7

VDDR_8

VDDNB_1

VDDNB_2

VDDNB_3

VDDNB_4

VDDNB_5

VDDNB_6

FREE_1

FREE_2

FREE_3

FREE_4

FREE_5

FREE_6

FREE_7

FREE_8

FREE_9

AE12

AD9

AE21

AD21

AD18

AD14

AD12

AD11

AC5

AE18

AC24

AC12

AC10

AB13

AB11

AE14

AA24

AA12

AA10

Y19

Y16

Y14

W5

W20

W18

W15

AE23

V24

V19

V16

V14

T20

T18

T15

T10

R5

R19

R16

R14

AC4

P24

P20

VLDT already check with

AMD need 1.1V

+1.1VS

F1

F2

1.5A

F3

F4

AL1

AL2

AL3

AL4

+CPU_VDDR

A12

B12

C12

0.9V, 1.5A

D12

AK10

AL10

AM10

AN10

+VDDNB

0.9V,4A

A3

A4

B3

B4

C3

C4

+CPU_VDDR

B11

G7

B7

AH8

AJ6

B25

AM3

AN11

P9

P8

18A

+1.5V

3A

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

B1

N2

N22

N23

B13

B15

B17

M21

B19

B21

B23

B27

B29

B33

C10

P10

P14

P16

P19

P7

C31

D11

D13

D15

R1

D17

D19

D21

D23

D25

D27

R15

R18

R2

R20

D29

D30

D8

E30

E32

F14

F17

R8

T14

T16

F20

T19

T24

T9

U1

F23

N1

G1

G19

G2

G25

G27

N10

2

UU1G

K325@

UU1G

K325@

VSS_1

VSS_28

VSS_29

VSS_30

VSS_2

VSS_3

VSS_4

VSS_27

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_12

VSS_13

VSS_14

VSS_15

VSS_36

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_37

VSS_38

VSS_39

VSS_40

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_115

ASB2_BGA812

ASB2_BGA812

GND1

GND1

VSS_45

VSS_44

VSS_43

VSS_42

VSS_26

VSS_25

VSS_41

VSS_24

VSS_23

VSS_22

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

W19

W1

V20

V18

M11

L8

V15

L4

L30

L26

L24

L23

L22

L21

L2

L12

L10

L1

K9

M6

K24

K22

K16

M22

K13

M24

K11

M23

J7

W16

J4

W14

J32

J30

M13

J28

U8

J25

U4

J24

U7

U2

J2

J16

J13

J11

J1

H6

H5

H28

H23

H20

J22

M9

G4

G30

N12

DELL CONFIDENTIAL/PROPRIETARY

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

UU1H

K325@

UU1H

K325@

AM19

VSS_207

AF7

VSS_167

AF26

VSS_166

AE7

VSS_165

AF8

VSS_168

AF9

VSS_169

AG1

VSS_170

AG2

VSS_171

AG27

VSS_172

AG4

VSS_173

AG5

VSS_174

AG6

VSS_175

AG7

VSS_176

AE4

VSS_164

AE25

VSS_163

AE24

VSS_162

AE22

VSS_161

AE20

VSS_160

AE2

VSS_159

AE16

VSS_158

AE13

VSS_157

AH14

VSS_177

AE11

VSS_156

AE10

VSS_155

AE1

VSS_154

AD24

VSS_153

AD23

VSS_152

AD22

VSS_151

AH20

VSS_178

AH23

VSS_179

AH25

VSS_180

AH28

VSS_181

AD20

VSS_150

AD16

VSS_149

AD13

VSS_148

AD10

VSS_147

AC9

VSS_146

AC8

VSS_145

A2

VSS_214

AC23

VSS_144

AH5

VSS_182

AJ1

VSS_183

AJ15

VSS_184

W2

VSS_116

A32

VSS_213

W8

VSS_117

Y10

VSS_118

Y15

VSS_119

Y18

VSS_120

AJ19

VSS_185

AJ2

VSS_186

AJ22

VSS_187

AJ4

VSS_188

Y20

VSS_121

Y24

VSS_122

AK11

VSS_189

AK13

VSS_190

Y7

VSS_123

AA1

VSS_124

AA11

VSS_125

ASB2_BGA812

ASB2_BGA812

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

ASB2 PWR & GND

ASB2 PWR & GND

ASB2 PWR & GND

LA-6132P

LA-6132P

LA-6132P

1

GND2

GND2

VSS_191

VSS_192

VSS_193

VSS_194

VSS_126

VSS_127

VSS_128

VSS_195

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_137

VSS_138

VSS_205

VSS_206

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_215

AK15

AK17

AK19

AK21

AA2

AA22

AA23

AK23

AA4

AA9

AB10

AB12

AB21

AB22

AB23

AB24

AK25

AK27

AK29

AJ5

AH6

AL31

AM1

AM13

AB7

AC1

AM15

AM17

AC11

AC13

AC2

AC21

AC22

AM23

AM27

AM33

AN2

AN32

AM11

945Monday, May 03, 2010

945Monday, May 03, 2010

945Monday, May 03, 2010

1.0

1.0

1.0

Page 10

5

DDR_A_MA0<7>

DDR_A_MA1<7>

DDR_A_MA2<7>

DDR_A_MA3<7>

DDR_A_MA4<7>

DDR_A_MA5<7>

DDR_A_MA6<7>

DDR_A_MA7<7>

DDR_A_MA8<7>

DDR_A_MA9<7>

DDR_A_MA10<7>

D D

C C

B B

A A

DDR_A_MA11<7>

DDR_A_MA12<7>

DDR_A_MA13<7>

DDR_A_MA14<7>

DDR_A_MA15<7>

DDR_A_DQS0<7>

DDR_A_DQS#0<7>

DDR_A_DQS1<7>

DDR_A_DQS#1<7>

DDR_A_DQS2<7>

DDR_A_DQS#2<7>

DDR_A_DQS3<7>

DDR_A_DQS#3<7>

DDR_A_DQS4<7>

DDR_A_DQS#4<7>

DDR_A_DQS5<7>

DDR_A_DQS#5<7>

DDR_A_DQS6<7>

DDR_A_DQS#6<7>

DDR_A_DQS7<7>

DDR_A_DQS#7<7>

+0.75VS

CU73

CU73

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS7

DDR_A_DQS#7

Layout Note:

Place near JDIMMA

+1.5V

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

@

@

1

CD4

CD4

2

0.1U_0402_16V7K

0.1U_0402_16V7K

CD42

CD42

1

2

1

CU75

CU75

2

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

0.1U_0402_16V7K

@

@

1

CD5

CD5

2

0.1U_0402_16V7K

0.1U_0402_16V7K

CD43

CD43

1

2

1

CU76

CU76

2

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

0.1U_0402_16V7K

0.1U_0402_16V7K

@

@

1

CD3

CD3

2

+1.5V

0.1U_0402_16V7K

0.1U_0402_16V7K

CD41

CD41

1

2

Layout Note:

Place near JDIMMA.203,204

1

CU74

CU74

2

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

5

0.1U_0402_16V7K

0.1U_0402_16V7K

@

@

1

CD6

CD6

2

0.1U_0402_16V7K

0.1U_0402_16V7K

CD44

CD44

1

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

CD52

CD52

1

2

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

0.1U_0402_16V7K

0.1U_0402_16V7K

@

@

1

CD38

CD38

2

0.1U_0402_16V7K

0.1U_0402_16V7K

CD45

CD45

1

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

CD53

CD53

1

2

0.1U_0402_16V7K

0.1U_0402_16V7K

@

@

1

CD39

CD39

2

0.1U_0402_16V7K

0.1U_0402_16V7K

CD47

CD47

CD46

CD46

1

2

@

@

10U_0603_6.3V6M

10U_0603_6.3V6M

CD16

CD16

1

2

@

@

+1.5V

1

+

+

CD15

CD15

2

+1.5V

10U_0603_6.3V6M

10U_0603_6.3V6M

1

2

1

2

4

+V_DDR_REF_DQ

330U_X_2VM_R6M

330U_X_2VM_R6M

10U_0603_6.3V6M

10U_0603_6.3V6M

CD48

CD48

1

2

@

@

4

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

1

CD2

CD2

CD1

CD1

2

@

@

+3VS

1000P_0402_50V7K

1000P_0402_50V7K

0.01U_0402_16V7K

0.01U_0402_16V7K

1

1

CD37

CD37

2

2

DDR_CKE0_DIMMA<7>

DDR_A_BS2<7>

M_CLK_DDR0<7>

M_CLK_DDR#0<7>

DDR_A_BS0<7>

DDR_A_WE#<7>

DDR_A_CAS#<7>

DDR_CS1_DIMMA#<7>

0.1U_0402_16V7K

0.1U_0402_16V7K

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

1

CD17

CD17

CD18

CD18

2

DDR_CKE0_DIMMA

DDR_CS1_DIMMA#

RD2 0_0402_5%RD2 0_0402_5%

RD3 0_0402_5%RD3 0_0402_5%

1

2

+1.5V

DDR_A_D0

DDR_A_D1

DDR_A_DM0

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_D18

DDR_A_D19

DDR_A_D24

DDR_A_D25

DDR_A_DM3

DDR_A_D26

DDR_A_D27

DDR_A_BS2

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

M_CLK_DDR0

M_CLK_DDR#0

DDR_A_MA10

DDR_A_BS0

DDR_A_WE#

DDR_A_CAS#

DDR_A_MA13

DDR_A_D32

DDR_A_D33

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_D34

DDR_A_D35

DDR_A_D40

DDR_A_D41

DDR_A_DM5

DDR_A_D42

DDR_A_D43

DDR_A_D48

DDR_A_D49

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_D50

DDR_A_D51

DDR_A_D56

DDR_A_D57

DDR_A_DM7

DDR_A_D58

DDR_A_D59

1 2

1 2

+0.75VS

3

JDIMMA

JDIMMA

VREF_DQ1VSS1

3

VSS2

5

DQ0

7

DQ1

9

VSS4

11

DM0

13

VSS5

15

DQ2

17

DQ3

19

VSS7

21

DQ8

23

DQ9

25

VSS9

27

DQS#1

DQS129RESET#

VSS1131VSS12

33

DQ10

35

DQ11

VSS1337VSS14

39

DQ16

41

DQ17

VSS1543VSS16

45

DQS#2

47

DQS2

49

VSS18

51

DQ18

53

DQ19

55

VSS20

57

DQ24

59

DQ25

VSS2261DQS#3

63

DM3

VSS2365VSS24

67

DQ26

69

DQ27

VSS2571VSS26

73

CKE0

75

VDD1

77

NC1

79

BA2

81

VDD3

83

A12/BC#

85

A9

87

VDD5

89

A8

91

A5

93

VDD7

95

A3

97

A1

99

VDD9

101

CK0

103

CK0#

105

VDD11

107

A10/AP

109

BA0

111

VDD13

113

WE#

115

CAS#

117

VDD15

119

A13

121

S1#

123

VDD17

125

NCTEST

127

VSS27

129

DQ32

131

DQ33

133

VSS29

135

DQS#4

137

DQS4

139

VSS32

141

DQ34

143

DQ35

145

VSS34

147

DQ40

149

DQ41

151

VSS36

153

DM5

155

VSS37

157

DQ42

159

DQ43

161

VSS39

163

DQ48

165

DQ49

167

VSS41

169

DQS#6

171

DQS6

173

VSS44

175

DQ50

177

DQ51

179

VSS46

181

DQ56

183

DQ57

185

VSS48

187

DM7

189

VSS49

191

DQ58

193

DQ59

195

VSS51

197

SA0

199

VDDSPD

201

SA1

203

VTT1

205

G1

FOX_AS0A626-U4RN-7F

FOX_AS0A626-U4RN-7F

CONN@

CONN@

VSS3

DQS#0

DQS0

VSS6

VSS8

DQ12

DQ13

VSS10

DQ14

DQ15

DQ20

DQ21

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS3

DQ30

DQ31

CKE1

VDD2

VDD4

VDD6

VDD8

VDD10

CK1#

VDD12

RAS#

VDD14

ODT0

VDD16

ODT1

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

VTT2

DQ4

DQ5

DQ6

DQ7

DM1

DM2

CK1

BA1

NC2

DM4

DM6

SDA

SCL

A15

A14

A11

A7

A6

A4

A2

A0

S0#

G2

+1.5V

2

4

6

8

10

12

14

16