Page 1

A

1 1

B

C

D

E

Compal Confidential

Schematics Document

2 2

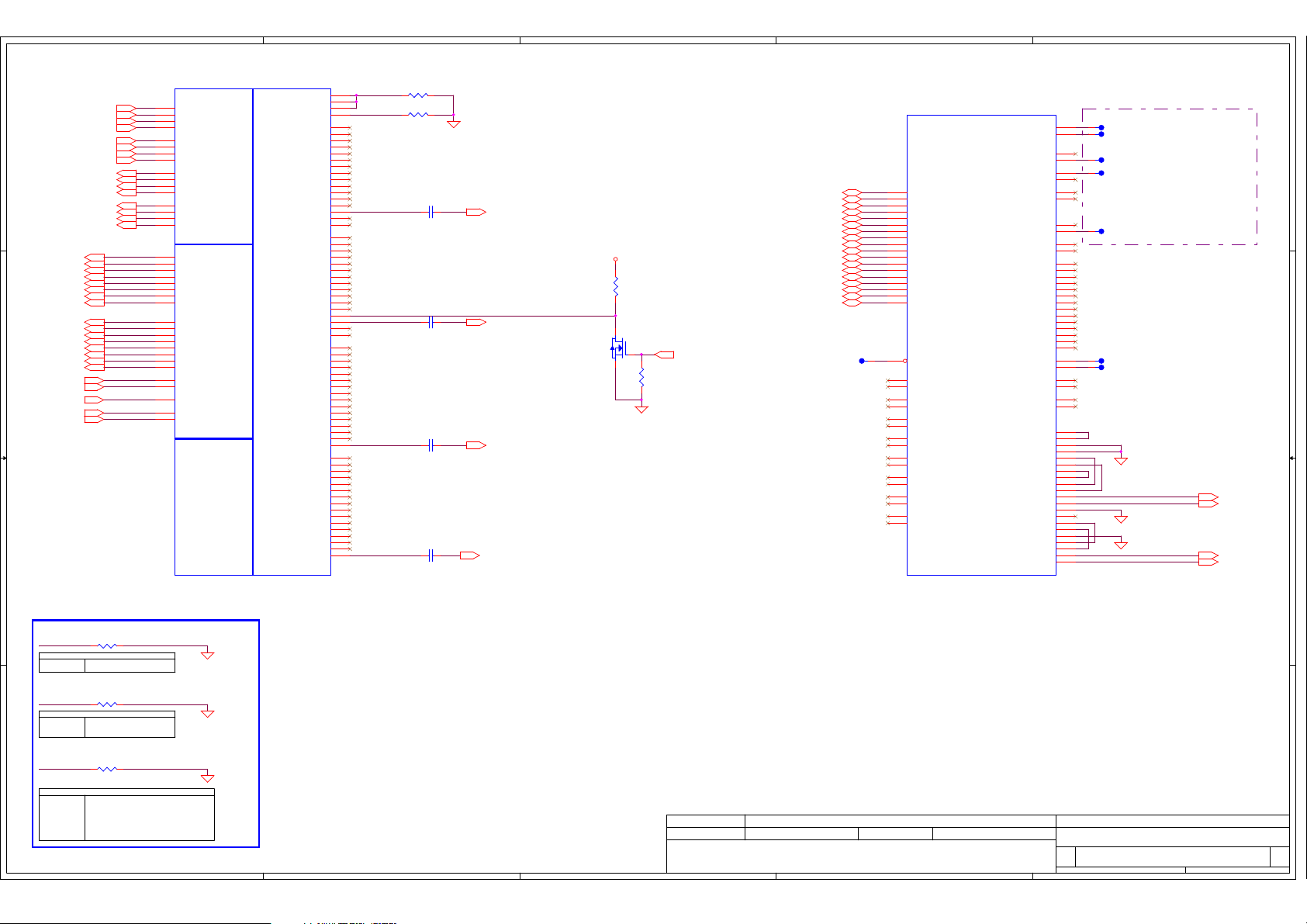

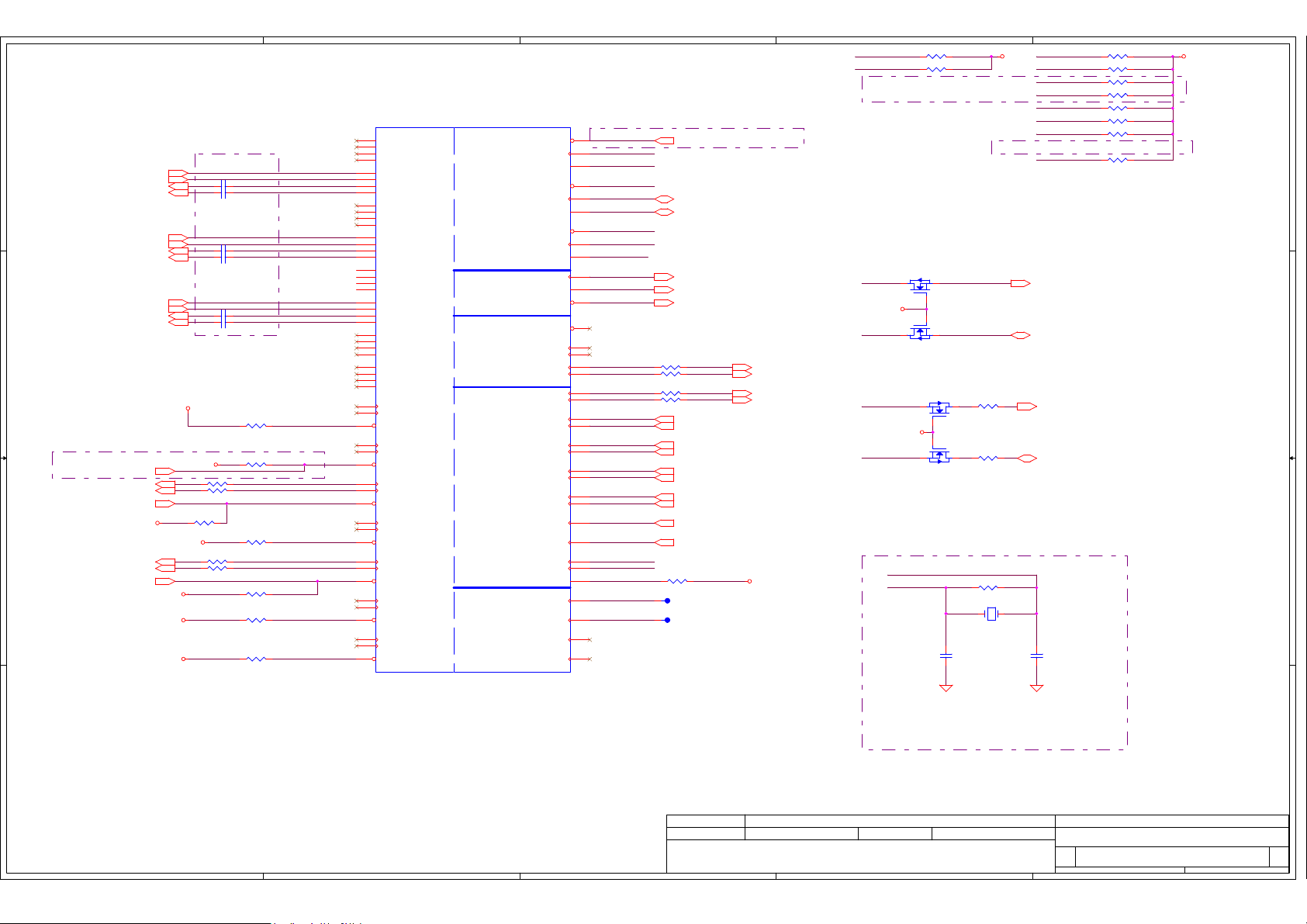

INTEL Auburndale BGA with IBEX core logic

Swatch UMA

3 3

LA-5251P

2010-01-04

REV:0.9

4 4

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/09/15 2010/12/31

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

D

Date: Sheet of

Compal Electronics, Inc.

Cover Sheet

LA-5251P

E

1 47Tues day, January 05, 2010

0.9

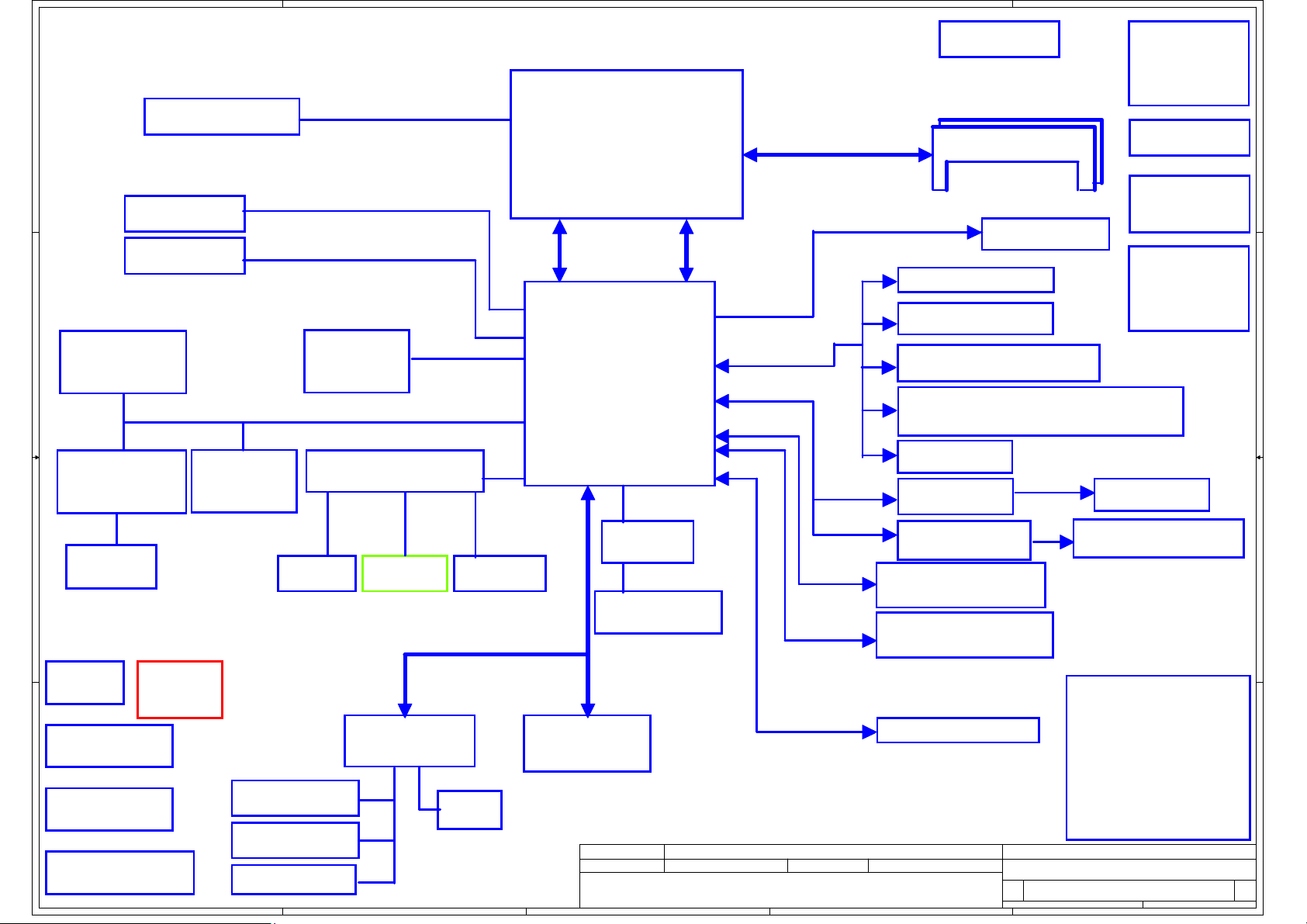

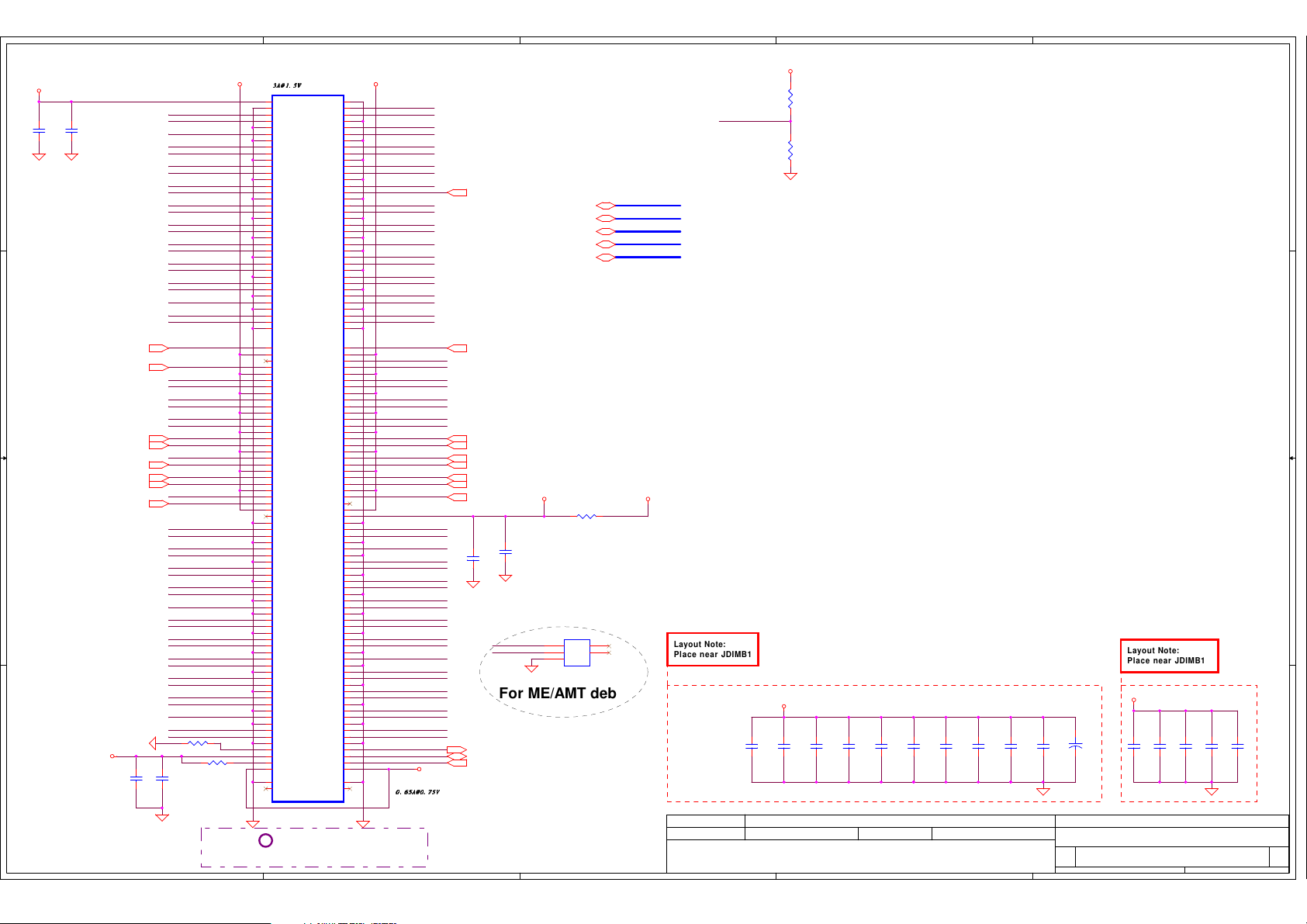

Page 2

A

Compal Confidential

File Name : LA-5251P

B

C

Swatch UMA

D

XDP Conn.

Page 4

E

Accelerometer

LI S30 2DLTR

1 1

Display port panel

Page 20

PEG-eDP

Mobile

Auburndale CPU

BG A 1288pins

DD R3-SO-DIMM X 2DDR3 1066/1333MHz 1.5V

BANK 0 , 1, 2, 3

Fan Control

Page 9,10

Page 24

Page 4

Dual Channel

VGA

Page 18

Display port

2 2

Express Card 54

PCIE *1 + USB *1

Page 23

10/100/1 000 LAN

Intel Hanksville GbE

PHY

Page 21

Page 18

WLAN Card

PCIE*1

Page 22

WWAN

+SIM Card

USB*1

Ri co R5C835

RGB

DDI_D

Page 23

USB2.0

PCI-E BUS

Controller

Page 25

DDI

PCI BUS

FDI

Intel Ibex Peak M

10 71pi ns

25mm*27mm

Page 12,13,14,15,16,17

Br aidwood

RJ45 CONN

3 3

Page 21

1394 port

Page 25

Smart Card

Page 25

SD/MM C Slot

Page 32

Page 4,5,6,7,8

DM I X4

ONFI Interface

Page 23

DDI_B

USB2.0

Azalia

SATA0

SATA1

SATA3

DP *1(Docking)

Page 29

USB *1(Docking)

Page 29

USB conn*1(Left side)

Page 24

FingerPrinter Validity VFS451

USB*1

Page 32

USB conn x 3(For I/O)-Rear side, Power USB

BT Conn USB x 1

USB x1(Camara)

MD C V1.5

Page 20

Page 28

Audio CKT

IDT 92HD75

SATA ODD Connector

Page 26

Page 22

AMP & Audio Jack

Thermal Se nsor

EMC 2 113

Page 4

CK505

Clock Generator

SL G8SP5 85V TR

Page 11

daughter board Module

Page 24

RJ11

Page 28

TPA6047A4RHBR

Page 27

NAND F lash Card

Page 23

LPC BUS

1.8" SAT A HDD Connector

Page 22

RTC CKT.

Page 12

Power OK CKT.

4 4

Power On/Off CKT.

Page 33

Page 28

LED

LED Board

Page 28

Touch Pad CONN.

Page 28

SMSC KBC 1098

page 30

Int.KBD

Page 28

TPM1.2

SLB9635TT

Page 32

SATA*1(Doc king)

Page 29

Page 29

Docking CONN.

(2) USB 1.channels

(1) Display Port Channels

(1) Line In

(1) Line Out

(1) RJ45 (10/100/1000)

(1) V GA

(1) 2 LAN indicator LED's

(1) Power Button

(1) SATA

TrackPoint CONN.

DC/DC Interface CKT.

Page 34

A

SP I ROM

Page 28

8 M B

Page 31

B

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/09/15 2010/12/31

Compal Secret Data

Deciphered Date

D

Title

Size Doc ument Number Re v

Cus tom

Date: Sheet of

Compal Electronics, Inc.

Block Diagram

LA-5251P

E

2 47Tues day, January 05, 2010

0.9

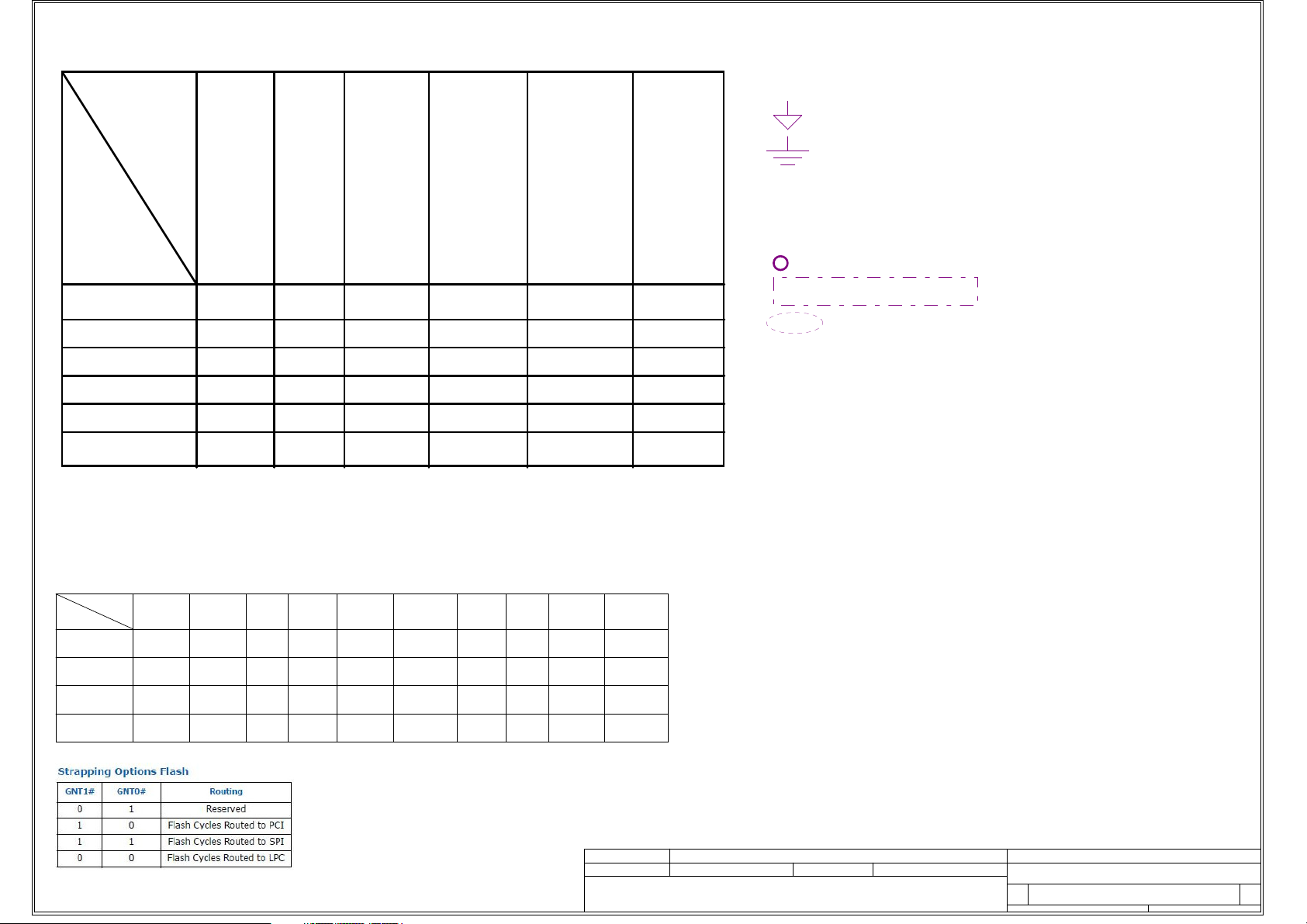

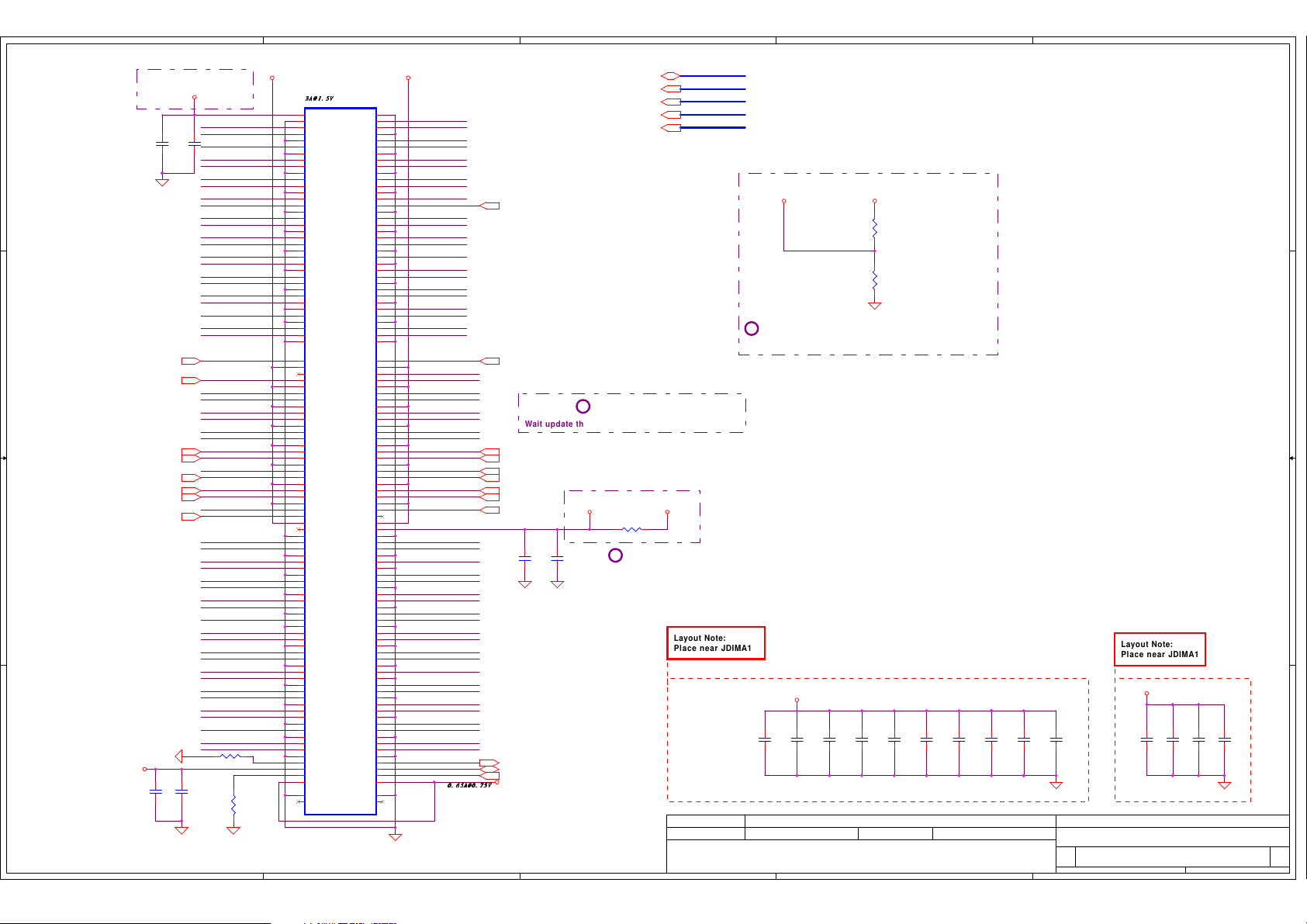

Page 3

A

Voltage Rails

State

S0

S1

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

1 1

( O MEANS ON X MEANS OFF )

+RTCVCC

power

plane

O

O

O

O

O

O

+B

+3VL +0.75V

O

O

O

O

O

X

+5VALW

+3VALW

O

O

O

O

X

X X X

+3VM

+1.05VM

O

O

O

O

X

X

+1.5V

O

X X

X

+5VS

+3VS

+1.5VS

+VCCP

+CPU_CORE

+1.05VS

+1.8VS

OO

OO

X

X

Symbol Note :

: means Digital Ground

: means Analog Ground

@ : means just reserve , no build

CONN@ : means ME part.

SV@ : means just build on SV Sku. LV Sku no build.

LV@ : means just build on LV Sku. SV Sku no build.

Lay out Note s

L

01/ 04 up da te

: Q ues ti on Are a Mark. (Wa it ch eck )

Install below 45 level BOM structure for ver. 0.1

45@ : means just put it in the BOM of 45 level.

Install below 43 level BOM structure for ver. 0.1

DEBUG@ : means just build when PCIE port 80 CARD function enable.

Remove before MP

SMBUS Control Table

SOURCE

SMB_EC_CK1

SMB_EC_DA1

SMBCLK

SMBDATA

SML0CLK

SML0DATA

SML1CLK

SML1DATA

SMSC1098

Calpella

Calpella

Calpella

BATT

V

X

X

X

THERMAL

SODIMM CLK CHIP

XDP G-SENSOR

X

X X

V V

X

X

X X

MINI CARD

X

V V

X

X

X X

DOCK

X

V

X

X

SENSOR

NIC

X X

X

V

X

X

X

V

X

V

X

V

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2008/09/15 2010/12/31

A

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

Date: Sheet of

Compal Electronics, Inc.

Notes List

LA-5251P

3 47Tues day, January 05, 2010

0.9

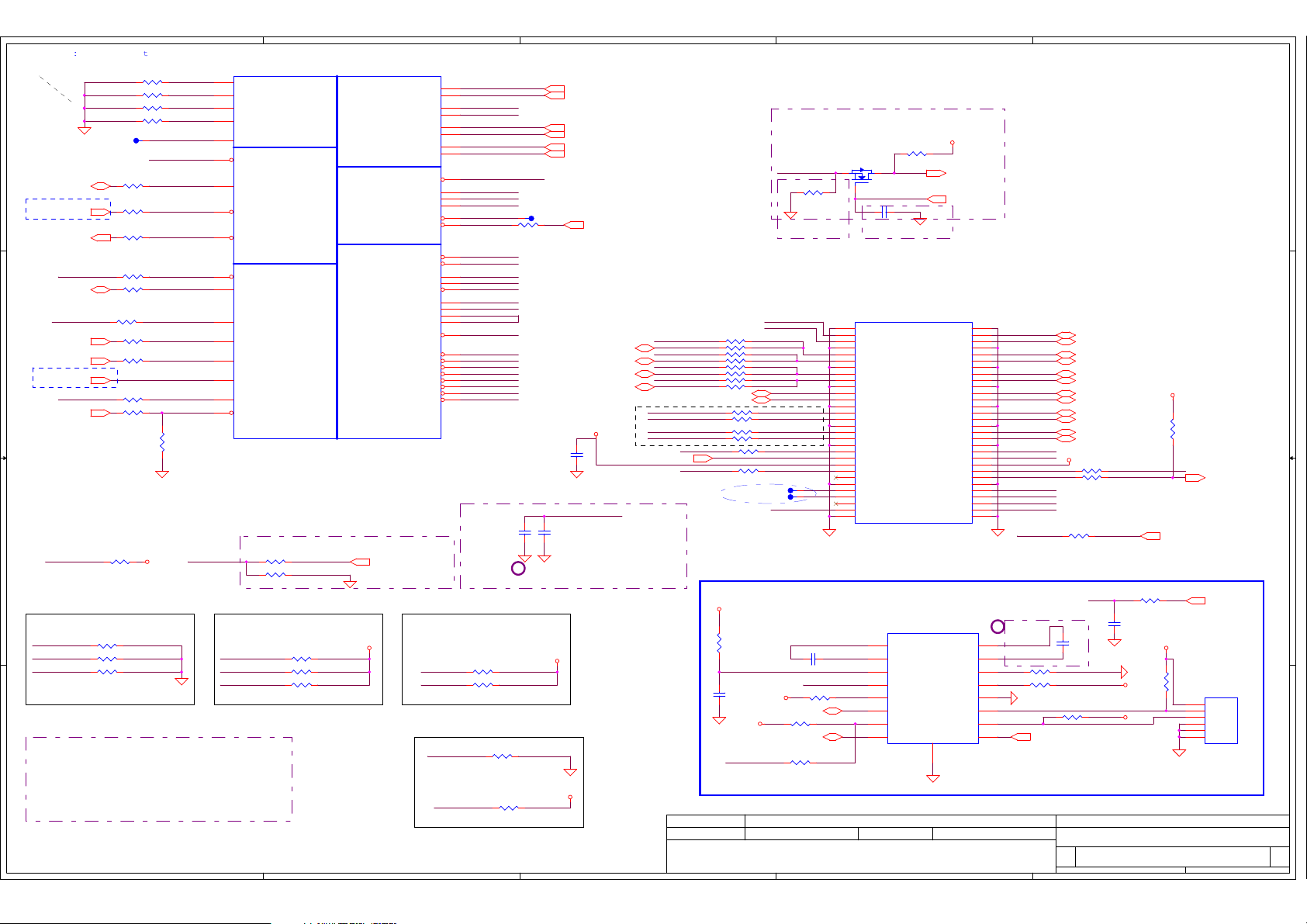

Page 4

1 2

1.5K _0402 _1%

1 2

1 2

1 2

1 2

1

1 2

1 2

1 2

1 2

T48PA D

R1 4

1 2

0_02 01_5%

R1 5

1 2

0_02 01_5%

R1 7

1 2

0_02 01_5%

R1 8

1 2

0_02 01_5%

R1 9

1 2

0_02 01_5%

R2 1

0_02 01_5%

R2 2

1 2

0_02 01_5%

R2 6

1 2

0_02 01_5%

R3 2

1 2

1 2

750_ 0402_1%

R2 01 K_02 01_5%@

H_CO MP3

R220_0 402_1%

H_CO MP2

R520_0 402_1%

H_CO MP1

R749.9 _0402 _1%

H_CO MP0

R949.9 _0402 _1%

TP_ SKTOCC#

H_ CATE RR#

H_P ECI_I SO

H_ PRO CHOT# _D

H_T HERM TRIP# _R

H_ CPUR ST#_ R

H_ PM_ SYNC _R

SYS _AGE NT_P WROK

VC CPW RGOO D_0

VD DPW RGO OD_R

0_02 01_5%

H_ PWRG D_XD P_RH_P WRGD _XDP

PLT _RST#_R

R3 3

12

R3 5

+VC CP

AD71

AC70

AD69

AE66

M71

N61

N19

N67

N17

N70

M17

AM7

Y67

AM5

H15

Y70

G3

VD DPW RGO OD_R

Processor Pullups

H_ PRO CHOT# _D

H_ CPUR ST#_ R

U1 B

COMP3

COMP2

COMP1

COMP0

PROC_DETECT

CATERR#

PECI

PROCHOT#

THERMTRIP#

RESET_OBS#

PM_SYNC

VCCPWRGOOD_1

VCCPWRGOOD_0

SM_DRAMPWROK

VTTPWRGOOD

TAPPWRGOOD

RSTIN#

INT EL_A UBURN DALE _1288

07 /08 u pda te fo r I NTEL S3 le aka ge issue.

07 /1 7 upd at e f or va lue chan ge back

1 2

R1 2 1.5K _0402_1%

1 2

R1 3 750_0 402_1%

R4 4 49.9_0 402_1%

1 2

1 2

R4 5 68_040 2_5%

1 2

R4 7 68_040 2_5%@

Misc

Thermal Power Management

Layout rule 1 0mil w idth :trace

length < 0.5 ", spa cing 20mil

A A

H_ PECI15

to power; PU to VCCP at power side also

H_ PROCH OT#40

H_T HERM TRIP#15

H_ CPUR ST#

H_ PM_S YNC14

H_ CPU PW RGD

H_ CPU PW RGD1 5

B B

PM_ DRAM _PWR GD14

from power

VTT PWRG OOD32

BUF _PLT_R ST#1 5

PM_ PWRB TN#_R

C C

DDR3 Compensation Signals

SM_ RCOMP0

R5 2 100_02 01_1%

SM_ RCOMP1 H_C ATER R#

R5 6 24.9_0 402_1%

SM_ RCOMP2

R5 8 130_04 02_1%

Layout Note:Please these

resist ors near Processor

11 /06 Ca ncel REM OTE ther mal senso r res erve .

D D

1

2

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

Clocks

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PM_EXT_TS#[0]

PM_EXT_TS#[1]

DDR3

Misc

JTAG & MBP

VC CP_1. 5VSP WRG D 32

+VC CP

2

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

PRDY#

PREQ#

TRST#

TDI_M

TDO_M

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

DBR#

CLK _CPU_ XDP

K71

CLK _CPU_ XDP#

J70

CLK_EX P

L21

CLK_ EXP#

J21

Y2

W4

SM_ DRAMR ST#

BJ12

SM_ RCOMP0

BV33

SM_ RCOMP1

BP39

SM_ RCOMP2

BV40

PM_EXTTS#0

AV66

PM_EXTTS#1

AV64

XDP _PRD Y#

U71

XDP _PREQ#

U69

XDP _TCK

T67

TCK

XDP_TMS

N65

TMS

XDP_TR ST#

P69

XDP _TDI

T69

TDI

XDP _TDO

T71

TDO

XDP _TDI_M

P71

T70

XDP _DBRES ET#

W71

XDP_B PM#0

J69

XDP_B PM#1

J67

XDP_B PM#2

J62

XDP_B PM#3

K65

XDP_B PM#4

K62

XDP_B PM#5

J64

XDP_B PM#6

K69

XDP_B PM#7

M69

C1 20

0.1U _0402 _16V4Z

CL K_CP U_BC LK

AK7

BCLK

CLK _CPU_ BCLK #

AK8

DDR Pullups

PM_EXTTS#0

1 2

R1 10K _0201_5%

PM_EXTTS#1

1 2

R3 10K _0201_5%

011 2 R em ove unin stall part s

XDP_TR ST#

1 2

R5 9 51_04 02_5%

Close to XDP

XDP _TDO

1 2

R1 0 51_04 02_5%

This s hall place near XDP

CLK _CPU_ BCLK 15

CLK _CPU_ BCLK # 15

CLK_EX P 13

CLK_EX P# 13

CL K_DP 13

CLK _DP# 1 3

T49 PAD

1 2

R1 60_0201_5%

C1

0.1U _0402 _16V4Z

@

1

1

2

2

Ad d C119 be twe en JP4 p in 37 an d 41;

L

Add C120 close to R 20.1

1

2

PM_ PWRB TN#_R

C1 19

0.1U _0402 _16V4Z

+V CCP

+V CCP

PM_EX TTS#1_R 9, 10

CF G125

CF G135

CF G145

CF G155

+VC CP

01/ 04 up dat e for ESD

3

from DDR

XDP_B PM#0

R2 3 0_02 01_5%

R2 4 0_02 01_5%@

XDP_B PM#1

R2 5 0_02 01_5%

R2 7 0_02 01_5%@

XDP_B PM#2

R2 8 0_02 01_5%

R2 9 0_02 01_5% @

XDP_B PM#3

R3 0 0_02 01_5%

XDP_B PM#4

XDP_B PM#5

XDP_B PM#6

XDP_B PM#7

R3 1 0_02 01_5% @

H_ CPU PW RGD

H_P WRGD _XDP

ESD re que st to add

PM_ PWRB TN#_R14

011 2 A dd test poin ts

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

4

07 /09 u pda te fo r I NTEL S3 le aka ge issue.

+1.5 V

R1 093

12

SM_ DRAMR ST#

R1 092

12

100K _0402_5 %@

07 /17 u pd ate

XDP _PREQ#

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

R3 6 1K_02 01_5%

+3VS

1 2

XDP _PRD Y#

CF G175

CF G165

1 2

1 2

1 2

1 2

1 2

1 2

R3 7 0 _0201 _5%

XDP _BPM#4_R

R4 30_02 01_5%

XDP _BPM#5_R

R4 80_02 01_5%

XDP _BPM#6_R

R4 00_02 01_5%

XDP _BPM#7_R

R4 10_02 01_5%

H_ CPU PW RGD_ R

PM_ PWRB TN#_R

T112PA D

T113PA D

XDP _TCK

Thermal Sensor EMC2113 with CPU PWM FAN

R5 0

68_0 402_5%

+3V S_THER

C4

1

0.1U _0402 _16V4Z

2

+3VS

H_T HERM TRIP#

C3 2200 P_0402_ 50V7K

+3VS

R7 1 10K_0 201_5%

THE RM_S CI#15

1 2

R6 2 10K_ 0201_5%

1 2

R6 3 0_020 1_5%

2008/09/15 2010/12/31

CPU XDP Connector

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

H_ THE RMDC

H_T HERM DA

1 2

FA N_PW M_R

1 2

@

Compal Secret Data

1K_ 0402_5%

61

Q52A

2N70 02DW H 2N SOT3 63-6

2

C6 .1U_ 0402_ 16V7K

1 2

08 /28 u pd ate

JP4

GND0

OBSFN_A0

OBSFN_A1

GND2

OBSDATA_A0

OBSDATA_A1

GND4

OBSDATA_A2

OBSDATA_A3

GND6

OBSFN_B0

OBSFN_B1

GND8

OBSDATA_B0

OBSDATA_B1

GND10

OBSDATA_B2

OBSDATA_B3

GND12

PWRGOOD/HOOK0

HOOK1

VCC_OBS_AB

HOOK2

HOOK3

GND14

SDA

SCL

TCK1

TCK0

GND16

SAM TE_BSH- 030-01-L-D -A CO NN@

U2

1

DN

2

DP

3

VDD

4

PWM_IN

5

ADDR_SEL

6

ALERT#

7

SYS_SHDN#

8

SMDATA

Add 0 ohm and 0.1u

OBSFN_C0

OBSFN_C1

OBSDATA_C0

OBSDATA_C1

OBSDATA_C2

OBSDATA_C3

OBSFN_D0

OBSFN_D1

OBSDATA_D0

OBSDATA_D1

OBSDATA_D2

OBSDATA_D3

ITPCLK/HOOK4

ITPCLK#/HOOK5

VCC_OBS_CD

RESET#/HOOK6

DBR#/HOOK7

GND

EMC 2113- 1-AP -TR QFN 16P

17

DRA MRST# 9,10

PC H_D DR_RS T 15

GND1

GND3

GND5

GND7

GND9

GND11

GND13

GND15

TD0

TRST#

TMS

GND17

DP2/DN3

DN2/DP3

TRIP_SET

SHDN_SEL

SMCLK

Deciphered Date

4

TDI

GND

PWM

TACH

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

CLK _CPU_ XDP

40

CLK _CPU_ XDP#

42

44

XDP _RST#_R

46

XDP _DBR ESET#_R

48

50

XDP _TDO

52

XDP_TR ST#

54

XDP _TDI

56

XDP_TMS

58

60

11 /06 u pd ate

L

REMOT E2+

16

REMOT E2-

15

14

13

12

FAN _PWM _OUT

11

TA CH

10

9

XDP _RST#_R

Clo se to U 2

R5 1

2.05K_0402_1%

R5 5

15K_0402_5%

SMB _CLK_S3 9 ,10, 11,13 ,24SMB_D ATA_S39,10 ,11, 13,24

5

CF G8 5

CF G9 5

CF G0 5

CF G1 5

CF G2 5

CF G3 5

CF G10 5

CF G11 5

CF G4 5

CF G5 5

CF G6 5

CF G7 5

+V CCP

1K_ 0201_5%

R3 8

1 2

1 2

R3 9 0_020 1_5%

1 2

R4 2 0 _0201_ 5%

2

1

R6 1

Title

Size D ocum ent N umber Re v

Cu stom

Da te: She et o f

PLT_ RST#

@

FA N_PW M_R

2

1

C5

2200 P_0402_ 50V7K

10K_0201_5%

Compal Electronics, Inc.

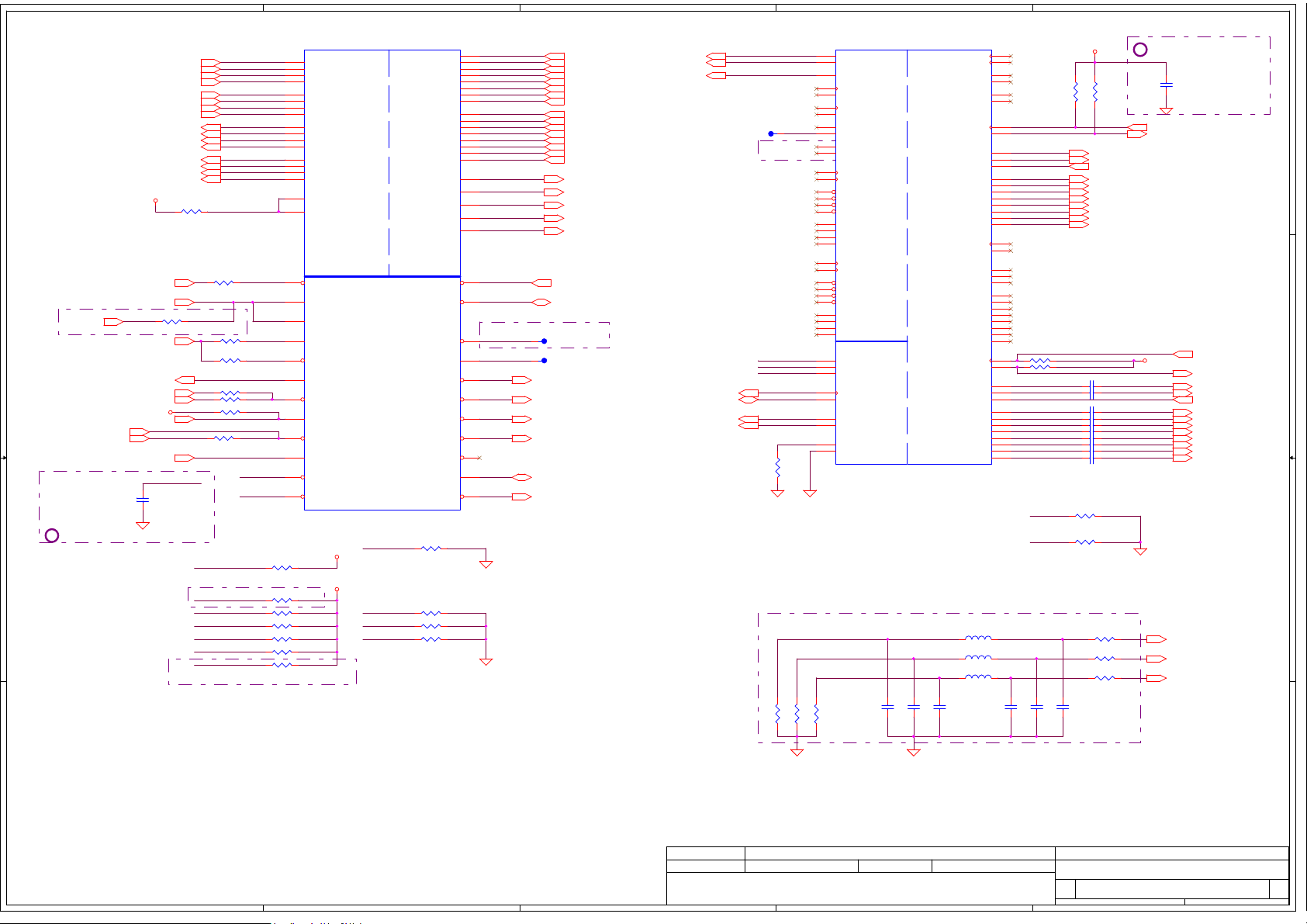

Auburndale(1/5)-Thermal/XDP

LA -5 251 P

H_ CPUR ST#

XDP _DBRES ET#

1 2

R4 6 0_02 01_5%

C2

0.1U _0402 _16V4Z@

+5VS

+3VS

+5VS

+3VS

R3 4

1K_ 0201_5%

1 2

XDP _DBRESE T# 12, 14

PLT_R ST# 12,1 5,21 ,22,2 3,31

FAN _PWM 30

R5 4

10K _0201_5%

1 2

1

1

2

2

3

3

4

4

5

G5

6

G6

ACE S_85 205-04001

CO NN@

5

4 4 7Tues day, Jan uary 05, 2010

JP 2

0. 9

Page 5

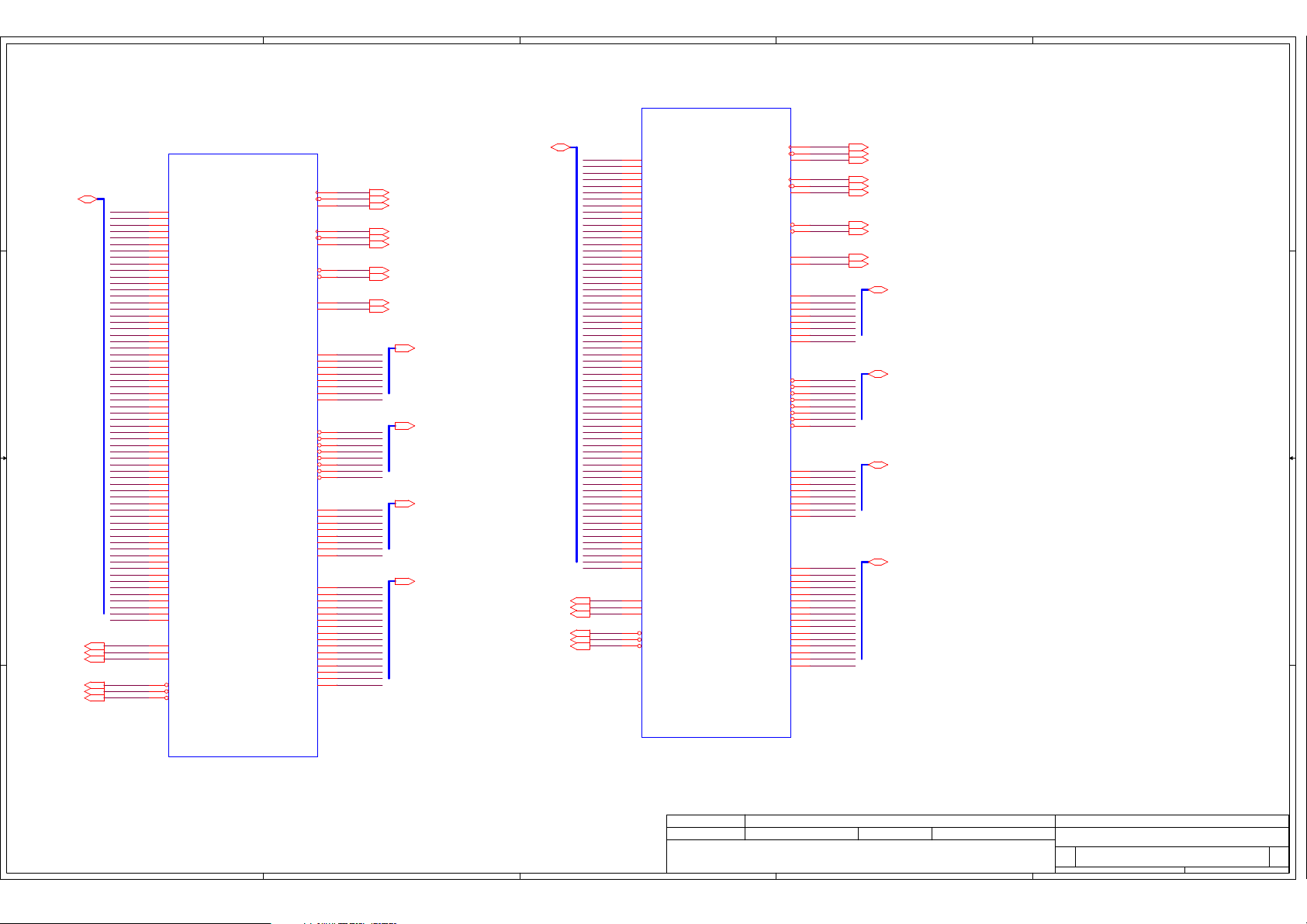

1

2

3

4

5

U1 A

DMI _CRX_PTX _N014

DMI _CRX_PTX _N114

DMI _CRX_PTX _N214

DMI _CRX_PTX _N314

DMI_C RX_PTX_P 014

A A

B B

DMI_C RX_PTX_P 114

DMI_C RX_PTX_P 214

DMI_C RX_PTX_P 314

DMI _CTX_PRX _N014

DMI _CTX_PRX _N114

DMI _CTX_PRX _N214

DMI _CTX_PRX _N314

DMI_C TX_PRX_P 014

DMI_C TX_PRX_P 114

DMI_C TX_PRX_P 214

DMI_C TX_PRX_P 314

FDI _CTX_ PRX_N01 4

FDI _CTX_ PRX_N11 4

FDI _CTX_ PRX_N21 4

FDI _CTX_ PRX_N31 4

FDI _CTX_ PRX_N41 4

FDI _CTX_ PRX_N51 4

FDI _CTX_ PRX_N61 4

FDI _CTX_ PRX_N71 4

FDI _CTX_PRX _P014

FDI _CTX_PRX _P114

FDI _CTX_PRX _P214

FDI _CTX_PRX _P314

FDI _CTX_PRX _P414

FDI _CTX_PRX _P514

FDI _CTX_PRX _P614

FDI _CTX_PRX _P714

FD I_F SYN C014

FD I_F SYN C114

FD I_I NT14

FD I_L SYN C014

FD I_L SYN C114

FDI _CTX_ PRX_N0

FDI _CTX_ PRX_N1

FDI _CTX_ PRX_N2

FDI _CTX_ PRX_N3

FDI _CTX_ PRX_N4

FDI _CTX_ PRX_N5

FDI _CTX_ PRX_N6

FDI _CTX_ PRX_N7

FDI _CTX_PR X_P0

FDI _CTX_PR X_P1

FDI _CTX_PR X_P2

FDI _CTX_PR X_P3

FDI _CTX_PR X_P4

FDI _CTX_PR X_P5

FDI _CTX_PR X_P6

FDI _CTX_PR X_P7

FD I_F SYN C0

FD I_F SYN C1

FD I_I NT

FD I_L SY NC0

FD I_L SY NC1

F7

J8

K8

J4

F9

J6

K9

J2

H17

K15

J13

F10

G17

M15

G13

J11

L2

N7

M4

P1

N10

R7

U7

W8

K1

N5

N2

R2

N9

R8

U6

W10

AC7

AC9

AB5

AA1

AB2

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

FDI_TX#[0]

FDI_TX#[1]

FDI_TX#[2]

FDI_TX#[3]

FDI_TX#[4]

FDI_TX#[5]

FDI_TX#[6]

FDI_TX#[7]

FDI_TX[0]

FDI_TX[1]

FDI_TX[2]

FDI_TX[3]

FDI_TX[4]

FDI_TX[5]

FDI_TX[6]

FDI_TX[7]

FDI_FSYNC[0]

FDI_FSYNC[1]

FDI_INT

FDI_LSYNC[0]

FDI_LSYNC[1]

PEG_RCOMPO

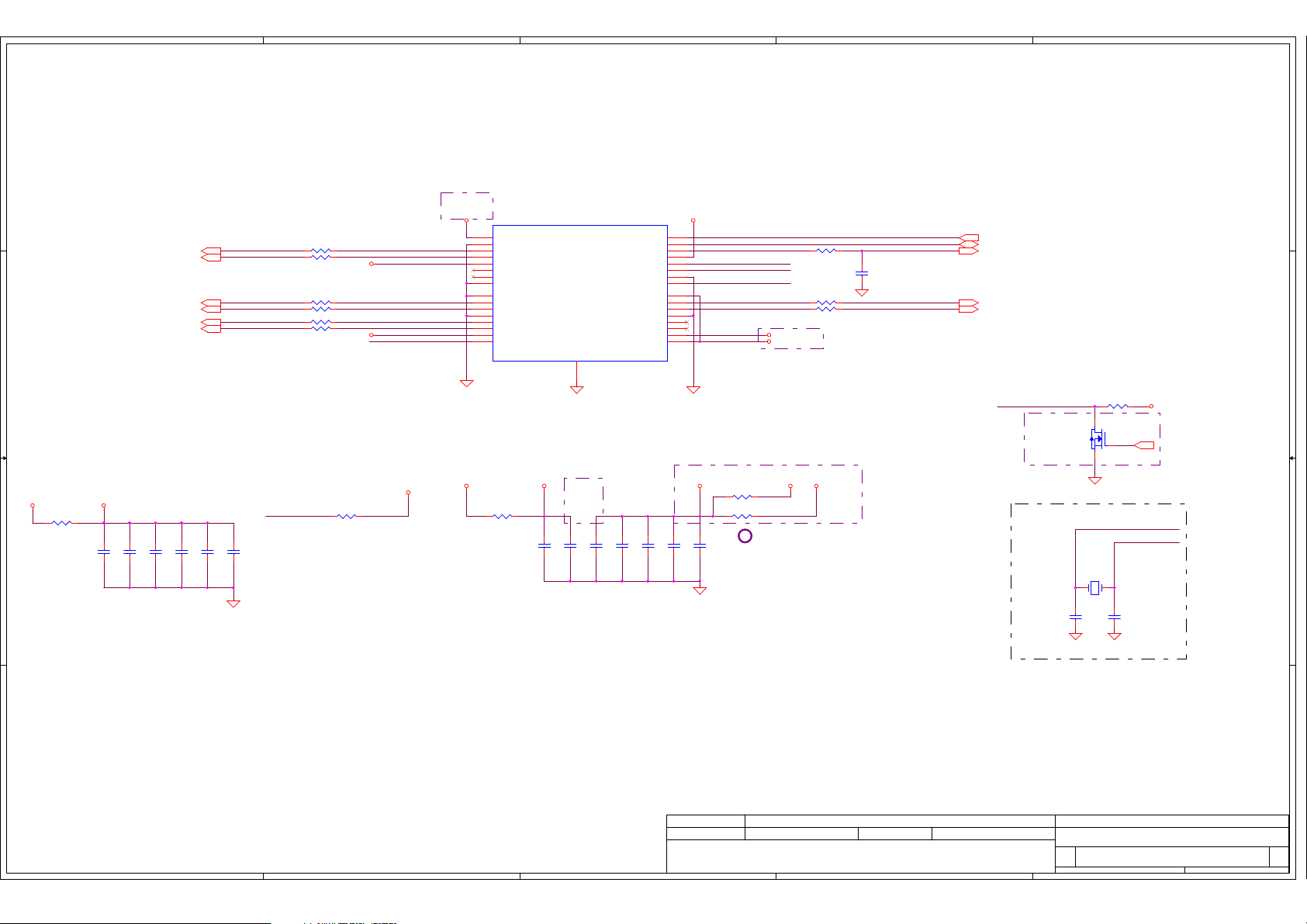

DMI Intel(R) FDI

PCI EXPRESS -- GRAPHICS

C C

INT EL_A UBURN DALE _1288

PEG_ICOMPI

PEG_ICOMPO

PEG_RBIAS

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

B12

A13

D12

B11

G40

G38

H34

P34

G28

H25

H24

D29

B26

D26

B23

D22

A20

D19

A17

B14

F40

J38

G34

M34

J28

G25

K24

B28

A27

B25

A24

B21

B19

MB_ C_DP_A UXP

B18

B16

D15

N40

L38

M32

D40

A38

G32

B33

B35

L30

A31

B32

L28

N26

M24

G21

J20

L40

N38

N32

B39

B37

H32

A34

D36

J30

B30

D33

N28

M25

N24

F21

L20

49.9 _0402_1 %

EXP _ICOMPI

1 2

EXP _RBIAS

1 2

750_ 0402_1%

MB_ C_DP _AUXN

MB_ C_DP _DATA 0_N

0.1U _0402 _16V4Z

MB_ C_DP _DATA0_P

R6 4

R6 5

C9 03

1 2

0.1U _0402 _16V4Z

1 2

C9 04

0.1U _0402 _16V4Z

C9 05

1 2

C8 58

1 2

0.1U _0402 _16V4Z

MB_ DP_AUXN 20

MB_DP _AUXP 20

MB_ DP_DA TA0_N 2 0

MB_ DP_DATA 0_P 20

Q46A

2N70 02DW H 2N SOT3 63-6

+V CCP

12

61

R8 01

7.5K _0402 _1%

2

12

R8 00

100K _040 2_5%~D

MB_ DP_H PD 20

U1 E

CF G0

CF G04

CF G14

CF G24

CF G34

CF G44

CF G54

CF G64

CF G74

CF G84

CF G94

CF G104

CF G114

CF G124

CF G134

CF G144

CF G154

CF G164

CF G174

T50P AD

CF G1

CF G2

CF G3

CF G4

CF G5

CF G6

CF G7

CF G8

CF G9

CF G10

CF G11

CF G12

CF G13

CF G14

CF G15

CF G16

CF G17

AV71

AW70

AY69

BB69

AM2

AK1

AK2

AK4

AG7

AG2

AH1

AC2

AC4

AE2

AD1

AB7

AU1

AL4

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

AJ2

CFG[5]

AT2

CFG[6]

CFG[7]

AF4

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

AF8

CFG[15]

AF6

CFG[16]

CFG[17]

RSVD_TP[0]

T4

RSVD15

T2

RSVD16

U1

RSVD17

V2

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

D8

RSVD23

B7

RSVD24

A10

RSVD26

B9

RSVD27

C5

RSVD_NCTF[7]

A6

RSVD_NCTF[8]

E3

RSVD_NCTF[6]

F1

RSVD_NCTF[5]

INT EL_A UBURN DALE _1288

RESERVED

RSVD_NCTF[3]

RSVD_NCTF[4]

RSVD_NCTF[2]

RSVD_NCTF[1]

DC_TEST_BV71

DC_TEST_BV69

DC_TEST_BV68

DC_TEST_BV5

DC_TEST_BV3

DC_TEST_BV1

DC_TEST_BT71

DC_TEST_BT69

DC_TEST_BT3

DC_TEST_BT1

DC_TEST_BR71

DC_TEST_BR1

DC_TEST_E71

DC_TEST_C71

DC_TEST_C69

DC_TEST_A71

DC_TEST_A69

DC_TEST_A68

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

RSVD53

RSVD54

RSVD55

RSVD56

RSVD57

RSVD58

RSVD_TP[2]

RSVD_TP[1]

RSVD62

RSVD63

RSVD64

RSVD65

DC_TEST_E1

DC_TEST_C3

DC_TEST_A5

W66

W64

AC69

AC71

AA71

AA69

R66

R64

BT5

BR5

BV6

BV8

AV69

AK71

AN69

AP66

AH66

AK66

AR71

AM66

AK69

AU71

AT70

AR69

AU69

AT67

AP2

AN7

AV4

AU2

BE69

BE71

BV71

BV69

BV68

BV5

BV3

BV1

BT71

BT69

BT3

BT1

BR71

BR1

E71

E1

C71

C69

C3

A71

A69

A68

A5

T116 P AD

T117 P AD

04/ 20 IN TEL #4181 25 upda te

T118 P AD

T119 P AD

T120 P AD

T51 PAD

T52 PAD

VSS _NCT F2_R 8

VSS _NCT F6_R 8

VSS _NCT F1_R 8

VSS _NCT F7_R 8

CFG Straps for PROCESSOR

CF G0

R6 8 3.01 K_040 2_1%@

1 2

PCI-Ex press Configuration Select

1: Single PEG

0: Bif urcation enabled

CFG0

Not ap plica ble f or Clarksfield Processor

CF G3

R6 9 3.01 K_040 2_1%@

1 2

CFG3-P CI Ex press Static Lane Reversal

1: Nor mal Operation

0: Lan e Numbers Reversed

CFG3

15 -> 0, 14 ->1, .....

CF G4

R7 0 3.01K _0402_1%

D D

ES1 sa mple n eed ne gative voltage

ES2 sa mple c ontact to GND

1 2

CFG4-D isplay Port Presence

1: Dis abled ; No Physical Display Port

attach ed to Embedded Display Port

CFG4

0: Ena bled; An external Display Port

device is c onnected to the Embedded

Display Port

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

1

2

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2008/09/15 2010/12/31

Compal Secret Data

Deciphered Date

4

Title

Size D ocum ent N umber Re v

Cu stom

Da te: She et o f

Compal Electronics, Inc.

Auburndale(2/5)-DMI/PEG/FDI

LA -5 251 P

5

5 4 7Tues day, Jan uary 05, 2010

0. 9

Page 6

1

2

3

U1D

4

5

A A

DD R_A _D[0 ..63]1 0

B B

C C

DD R_A_B S010

DD R_A_B S110

DD R_A_B S210

DD R_A_ CAS#10

DD R_A_ RAS#10

DD R_A _WE#10

DD R_A _D0

DD R_A _D1

DD R_A _D2

DD R_A _D3

DD R_A _D4

DD R_A _D5

DD R_A _D6

DD R_A _D7

DD R_A _D8

DD R_A _D9

DD R_A _D10

DD R_A _D11

DD R_A _D12

DD R_A _D13

DD R_A _D14

DD R_A _D15

DD R_A _D16

DD R_A _D17

DD R_A _D18

DD R_A _D19

DD R_A _D20

DD R_A _D21

DD R_A _D22

DD R_A _D23

DD R_A _D24

DD R_A _D25

DD R_A _D26

DD R_A _D27

DD R_A _D28

DD R_A _D29

DD R_A _D30

DD R_A _D31

DD R_A _D32

DD R_A _D33

DD R_A _D34

DD R_A _D35

DD R_A _D36

DD R_A _D37

DD R_A _D38

DD R_A _D39

DD R_A _D40

DD R_A _D41

DD R_A _D42

DD R_A _D43

DD R_A _D44

DD R_A _D45

DD R_A _D46

DD R_A _D47

DD R_A _D48

DD R_A _D49

DD R_A _D50

DD R_A _D51

DD R_A _D52

DD R_A _D53

DD R_A _D54

DD R_A _D55

DD R_A _D56

DD R_A _D57

DD R_A _D58

DD R_A _D59

DD R_A _D60

DD R_A _D61

DD R_A _D62

DD R_A _D63

BF11

BE11

BH13

BN11

BG17

BK15

BG15

BH17

BK17

BN20

BN17

BK25

BH25

BJ20

BH21

BG24

BG25

BJ40

BM43

BF47

BF48

BN40

BH43

BN44

BN47

BN48

BN51

BH53

BJ55

BH48

BJ48

BM53

BN55

BF55

BN57

BN65

BJ61

BF57

BJ57

BK64

BK61

BJ63

BF64

BB64

BB66

BJ66

BF65

AY64

BC70

BT38

BH38

BF21

BK43

BL38

BF38

U1C

BM34

SA_CK[0]

BP35

SA_CK#[0]

BF20

AT8

SA_DQ[0]

AT6

SA_DQ[1]

BB5

SA_DQ[2]

BB9

SA_DQ[3]

AV7

SA_DQ[4]

AV6

SA_DQ[5]

BE6

SA_DQ[6]

BE8

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

BK5

SA_DQ[10]

SA_DQ[11]

BF9

SA_DQ[12]

BF6

SA_DQ[13]

BK7

SA_DQ[14]

BN8

SA_DQ[15]

SA_DQ[16]

BN9

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

BK9

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

SA_CKE[0]

BK36

SA_CK[1]

BH36

SA_CK#[1]

BK24

SA_CKE[1]

BH40

SA_CS#[0]

BJ47

SA_CS#[1]

BF43

SA_ODT[0]

BL47

SA_ODT[1]

DD R_A_ DM0

BB10

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

DDR SYSTEM MEMORY A

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

BJ10

BM15

BN24

BG44

BG53

BN62

BH59

AY5

BJ7

BN13

BL21

BH44

BK51

BP58

BE62

AY7

BJ5

BL13

BN21

BK44

BH51

BM60

BE64

BT36

BP33

BV36

BG34

BG32

BN32

BK32

BJ30

BN30

BF28

BH34

BH30

BJ28

BF40

BN28

BN25

DD R_A_ DM1

DD R_A_ DM2

DD R_A_ DM3

DD R_A_ DM4

DD R_A_ DM5

DD R_A_ DM6

DD R_A_ DM7

DD R_A_ DQS# 0

DD R_A_ DQS# 1

DD R_A_ DQS# 2

DD R_A_ DQS# 3

DD R_A_ DQS# 4

DD R_A_ DQS# 5

DD R_A_ DQS# 6

DD R_A_ DQS# 7

DD R_A _DQS 0

DD R_A _DQS 1

DD R_A _DQS 2

DD R_A _DQS 3

DD R_A _DQS 4

DD R_A _DQS 5

DD R_A _DQS 6

DD R_A _DQS 7

DDR_ A_M A0

DDR_ A_M A1

DDR_ A_M A2

DDR_ A_M A3

DDR_ A_M A4

DDR_ A_M A5

DDR_ A_M A6

DDR_ A_M A7

DDR_ A_M A8

DDR_ A_M A9

DDR_ A_MA 10

DDR_ A_MA 11

DDR_ A_MA 12

DDR_ A_MA 13

DDR_ A_MA 14

DDR_ A_MA 15

M_ CLK_D DR0 1 0

M_ CLK_D DR#0 1 0

DDR_ CKE0 _DIM MA 10

M_ CLK_D DR1 1 0

M_ CLK_D DR#1 1 0

DDR_ CKE1 _DIM MA 10

DDR_ CS0_ DIMM A# 10

DDR_ CS1_ DIMM A# 10

M_ODT 0 10

M_ODT 1 10

DD R_A_ DM[0 ..7] 1 0

DD R_A _DQS #[0.. 7] 10

DD R_A _DQS [0..7 ] 10

DDR_ A_MA [0.. 15] 10

DD R_B _D[0 ..63]9

DD R_B_B S09

DD R_B_B S19

DD R_B_B S29

DD R_B_ CAS#9

DD R_B_ RAS#9

DD R_B _WE#9

DD R_B _D0

DD R_B _D1

DD R_B _D2

DD R_B _D3

DD R_B _D4

DD R_B _D5

DD R_B _D6

DD R_B _D7

DD R_B _D8

DD R_B _D9

DD R_B _D10

DD R_B _D11

DD R_B _D12

DD R_B _D13

DD R_B _D14

DD R_B _D15

DD R_B _D16

DD R_B _D17

DD R_B _D18

DD R_B _D19

DD R_B _D20

DD R_B _D21

DD R_B _D22

DD R_B _D23

DD R_B _D24

DD R_B _D25

DD R_B _D26

DD R_B _D27

DD R_B _D28

DD R_B _D29

DD R_B _D30

DD R_B _D31

DD R_B _D32

DD R_B _D33

DD R_B _D34

DD R_B _D35

DD R_B _D36

DD R_B _D37

DD R_B _D38

DD R_B _D39

DD R_B _D40

DD R_B _D41

DD R_B _D42

DD R_B _D43

DD R_B _D44

DD R_B _D45

DD R_B _D46

DD R_B _D47

DD R_B _D48

DD R_B _D49

DD R_B _D50

DD R_B _D51

DD R_B _D52

DD R_B _D53

DD R_B _D54

DD R_B _D55

DD R_B _D56

DD R_B _D57

DD R_B _D58

DD R_B _D59

DD R_B _D60

DD R_B _D61

DD R_B _D62

DD R_B _D63

AW2

BV10

BR10

BT12

BT15

BV15

BV12

BP12

BV17

BU16

BP15

BU19

BV22

BT22

BP19

BV19

BV20

BT20

BT48

BV48

BV50

BP49

BT47

BV52

BV54

BT54

BP53

BU53

BT59

BT57

BP56

BT55

BU60

BV59

BV61

BP60

BR66

BR64

BR62

BT61

BN68

BL69

BJ71

BF70

BG71

BC67

BK70

BK67

BD71

BD69

BV43

BV41

BV24

BU46

BT40

BT41

BA2

SB_DQ[0]

SB_DQ[1]

BD1

SB_DQ[2]

BE4

SB_DQ[3]

AY1

SB_DQ[4]

BC2

SB_DQ[5]

BF2

SB_DQ[6]

BH2

SB_DQ[7]

BG4

SB_DQ[8]

BG1

SB_DQ[9]

BR6

SB_DQ[10]

BR8

SB_DQ[11]

BJ4

SB_DQ[12]

BK2

SB_DQ[13]

BU9

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

DDR SYSTEM MEMORY - B

SB_CK[0]

SB_CK#[0]

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

BU33

BV34

BT26

BV38

BU39

BT24

BP46

BT43

BV45

BU49

BB4

BL4

BT13

BP22

BV47

BV57

BU65

BF67

BE2

BM3

BU12

BT19

BT52

BV55

BU63

BG69

BD4

BN4

BV13

BT17

BT50

BU56

BV62

BJ69

BT34

BP30

BV29

BU30

BV31

BT33

BT31

BP26

BV27

BT27

BU42

BU26

BT29

BT45

BV26

BU23

DD R_B_ DM0

DD R_B_ DM1

DD R_B_ DM2

DD R_B_ DM3

DD R_B_ DM4

DD R_B_ DM5

DD R_B_ DM6

DD R_B_ DM7

DD R_B_ DQS# 0

DD R_B_ DQS# 1

DD R_B_ DQS# 2

DD R_B_ DQS# 3

DD R_B_ DQS# 4

DD R_B_ DQS# 5

DD R_B_ DQS# 6

DD R_B_ DQS# 7

DD R_B _DQS 0

DD R_B _DQS 1

DD R_B _DQS 2

DD R_B _DQS 3

DD R_B _DQS 4

DD R_B _DQS 5

DD R_B _DQS 6

DD R_B _DQS 7

DDR_ B_M A0

DDR_ B_M A1

DDR_ B_M A2

DDR_ B_M A3

DDR_ B_M A4

DDR_ B_M A5

DDR_ B_M A6

DDR_ B_M A7

DDR_ B_M A8

DDR_ B_M A9

DDR_ B_MA 10

DDR_ B_MA 11

DDR_ B_MA 12

DDR_ B_MA 13

DDR_ B_MA 14

DDR_ B_MA 15

M_ CLK_D DR2 9

M_ CLK_D DR#2 9

DDR_ CKE2 _DIM MB 9

M_ CLK_D DR3 9

M_ CLK_D DR#3 9

DDR_ CKE3 _DIM MB 9

DDR_ CS2_ DIMM B# 9

DDR_ CS3_ DIMM B# 9

M_ODT 2 9

M_ODT 3 9

DD R_B_ DM[0 ..7] 9

DD R_B_ DQS# [0..7 ] 9

DD R_B_ DQS[ 0..7] 9

DDR_ B_MA [0.. 15] 9

INT EL_A UBURN DALE _1288

1

INT EL_A UBURN DALE _1288

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

2

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2008/09/15 2010/12/31

Compal Secret Data

Deciphered Date

4

Title

Size D ocum ent N umber R ev

Cu sto m

Da te: She et o f

Compal Electronics, Inc.

Auburndale(3/5)-DDR3

LA -52 51P

5

6 4 7Tues day, Jan uary 05, 2010

0. 9

D D

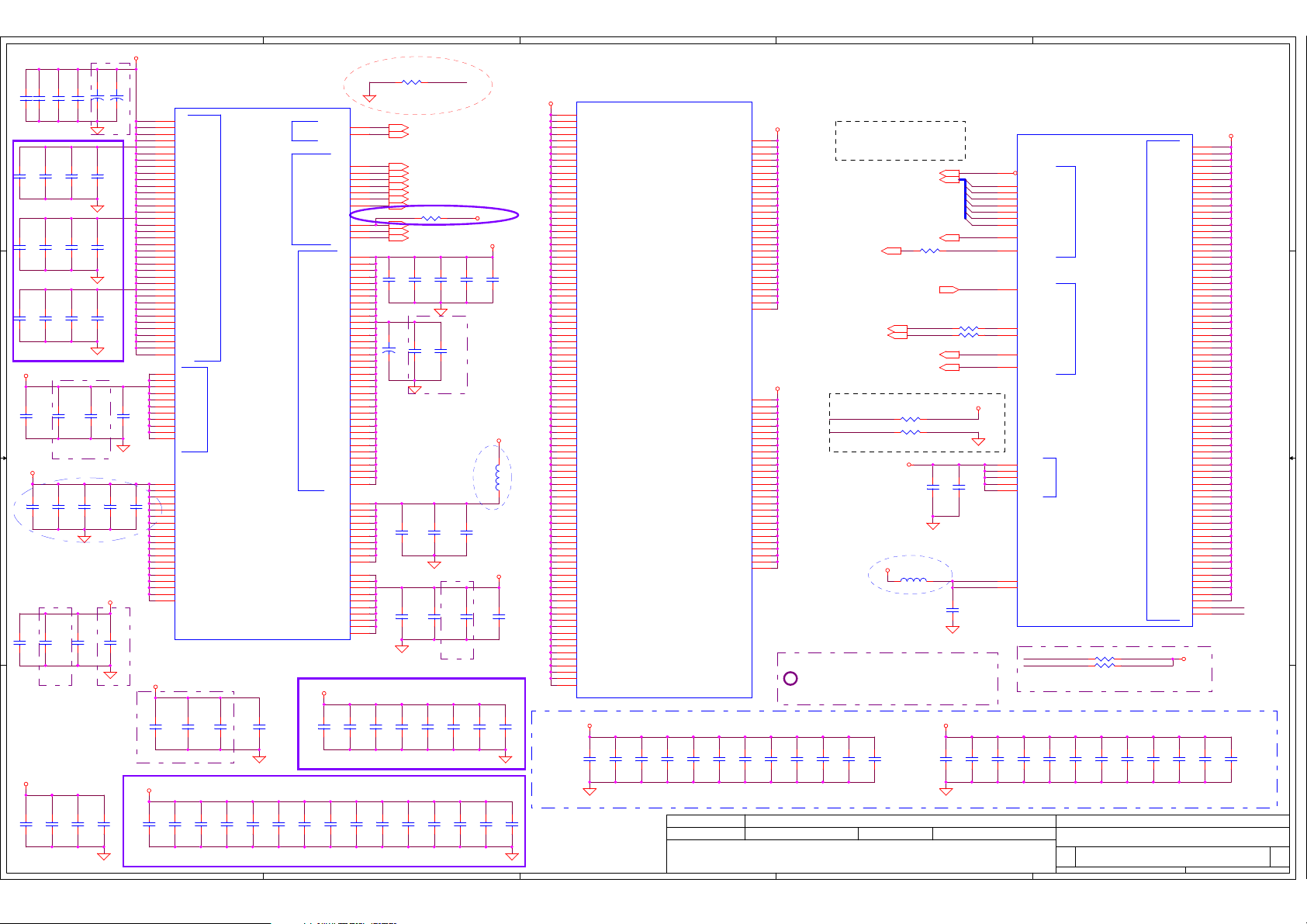

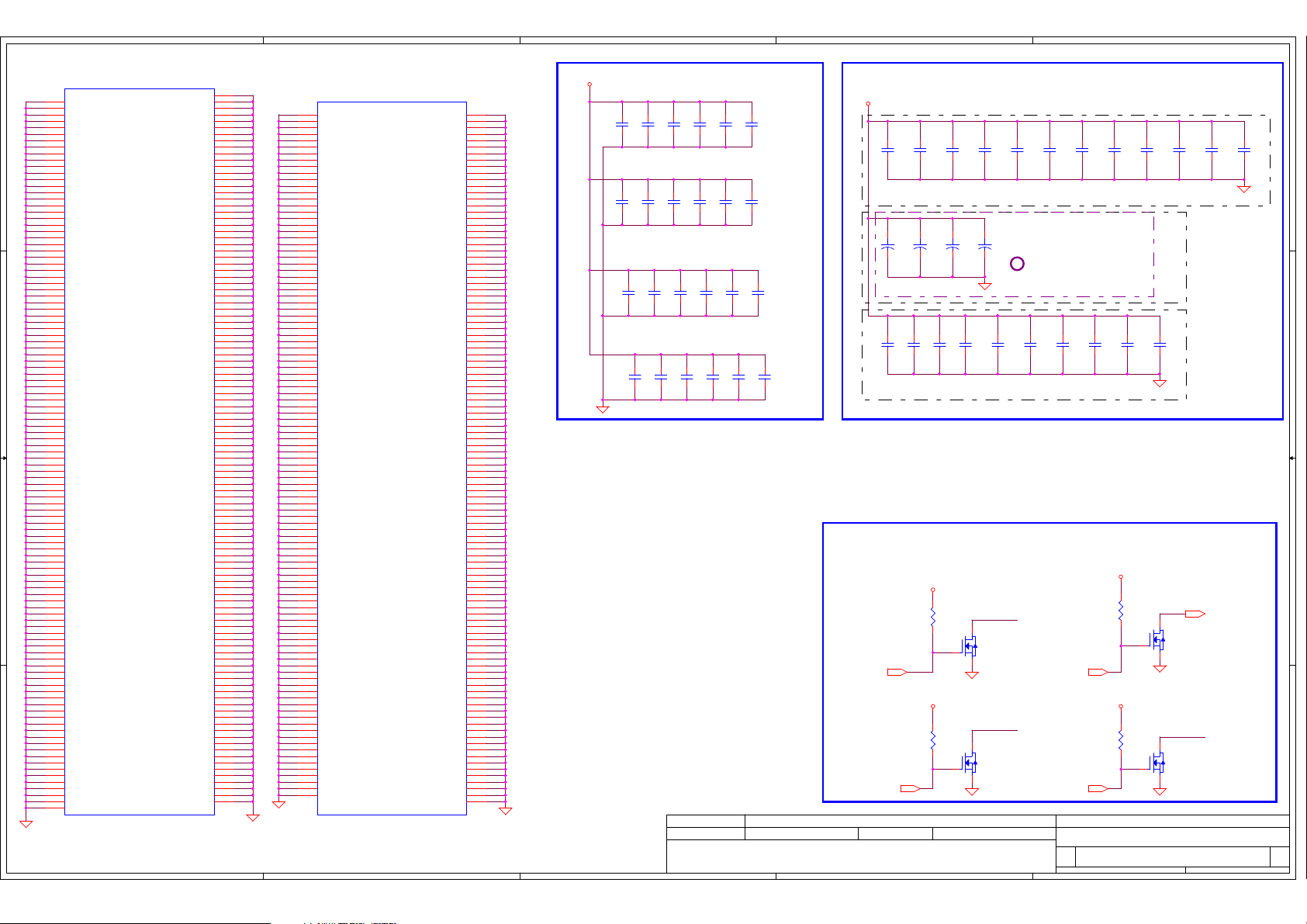

Page 7

C1 9

1U_0 402_6 .3V4Z

1U_0 402_6 .3V4Z

1U_0 402_6 .3V4Z

10U_ 0805_ 6.3V6M

C2 14

C2 18

C3 80

1

2

C3 5

1

2

10U_ 0805_ 6.3V6M

47P _0402_50 V8J

C6 1

1

+

2

1

2

1

2

1

2

10U_ 0805_ 6.3V6M@

1U_0 402_6 .3V4Z

+VC CP

C5 4

@

C9 73

1U_0 402_6 .3V4Z

1U_0 402_6 .3V4Z

1U_0 402_6 .3V4Z

C3 0

1

2

+GF X_CORE

09 /22 u pd ate

1

+

C9 74

2

330U _V_2VM _R6M

C2 13

C2 17

C2 21

1

2

1U_0 402_6 .3V4Z

C3 6

1

2

11 /13 u pd ate

22U_ 0805_ 6.3V6M

C6 2

1

2

47P _0402_50 V8J

U1 G

AN32

330U _V_2VM _R6M

VAXG1

AN30

VAXG2

AN28

VAXG3

AN26

VAXG4

AN24

VAXG5

AN23

VAXG6

AN21

VAXG7

AN19

VAXG8

AL32

VAXG9

AL30

VAXG10

AL28

VAXG11

AL26

VAXG12

AL24

VAXG13

AL23

VAXG14

AL21

VAXG15

AL19

VAXG16

AK14

VAXG17

AK12

VAXG18

AJ10

VAXG19

AH14

VAXG20

AH12

VAXG21

AF28

VAXG22

AF26

VAXG23

AF24

VAXG24

AF23

VAXG25

AF21

VAXG26

AF19

VAXG27

AF17

VAXG28

AF15

VAXG29

AF14

VAXG30

AD28

VAXG31

AD26

VAXG32

AD24

VAXG33

AD23

VAXG34

AD21

VAXG35

AD19

VAXG36

AD17

VAXG37

W21

VTT1_1

W19

VTT1_2

U21

10U_ 0805_ 6.3V6M

VTT1_3

U19

VTT1_4

U17

C3 1

VTT1_5

U15

VTT1_6

U14

VTT1_7

U12

VTT1_8

R21

VTT1_9

R19

VTT1_10

R17

VTT1_11

AK62

VCAP2_1

AK60

VCAP2_2

AK59

1

VCAP2_3

AH60

VCAP2_4

AH59

VCAP2_5

AF60

VCAP2_6

2

AF59

VCAP2_7

AD60

VCAP2_8

AD59

VCAP2_9

AB60

VCAP2_10

AB59

VCAP2_11

AA60

VCAP2_12

AA59

VCAP2_13

W60

VCAP2_14

W59

VCAP2_15

U60

VCAP2_16

U59

VCAP2_17

R60

VCAP2_18

R59

VCAP2_19

INT EL_A UBURN DALE _1288

04/ 29 Ch ang e C55, C56,C5 7 from

@47 P_0 402 to 1UF_ 040 2 by HP.

+C PU_C ORE

1U_0 402_6 .3V6K

1

1

C5 5

C5 6

2

+C PU_C ORE

1U_0 402_6 .3V6K

C6 16

1

2

2

1U_0 402_6 .3V6K

C6 23

1

2

1U_0 402_6 .3V6K

1U_0 402_6 .3V6K

C6 15

1

1

C5 7

2

1U_0 402_6 .3V6K

1U_0 402_6 .3V6K

C6 43

1

1

2

2

GRAPHI CS

PEG & DMI

POWER

47P _0402_50 V8J

C5 8

1

@

2

1U_0 402_6 .3V6K

1U_0 402_6 .3V6K

C6 45

C6 17

1

2

Follow SCH check list

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_DPRSLPVR

GFX_IMON

GRA PHI CS VIDs

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VDDQ19

VDDQ20

VDDQ21

VDDQ22

VDDQ23

DDR3 - 1.5V RAILS

VDDQ24

VDDQ25

VDDQ26

VDDQ27

VDDQ28

VDDQ29

VDDQ30

VDDQ31

VDDQ32

VDDQ33

VDDQ34

VDDQ35

VDDQ36

VTT0_DDR

VTT0_DDR[1]

VTT0_DDR[2]

VTT0_DDR[3]

VTT0_DDR[4]

VTT0_DDR[5]

VTT0_DDR[6]

VTT0_DDR[7]

VTT0_DDR[8]

VTT0_DDR[9]

VTT1_12

VTT1_13

VTT1_14

VTT1_15

VTT1_16

VTT1_17

VTT1_18

VTT1_19

VTT1_20

VTT1_21

+C PU_C ORE

1U_0 402_6 .3V6K

1U_0 402_6 .3V6K

C3 81

C3 82

1

2

1U_0 402_6 .3V6K

1U_0 402_6 .3V6K

C6 46

1

2

C6 47

C6 44

1

1

2

2

C1 7

C1 8

1U_0 402_6 .3V4Z

10U_ 0805_ 6.3V6M

C1 6

1

1

1

1

2

2

2

1U_0 402_6 .3V4Z

C2 12

1

2

1U_0 402_6 .3V4Z

C2 16

1

2

1U_0 402_6 .3V4Z

C2 20

1

2

0116 a dd

10U_ 0805_ 6.3V6M

C2 8

1

2

2

C1 79

1

2

C2 15

1

2

C2 19

1

2

22U_ 0805_ 6.3V6M

C2 9

1U_0 402_6 .3V4Z

1U_0 402_6 .3V4Z

A A

1

2

1U_0 402_6 .3V4Z

1

2

1U_0 402_6 .3V4Z

1

2

B B

+V CCP

1

2

11 /13 u pd ate

+VC AP2

1U_0 402_6 .3V4Z

C3 2

1U_0 402_6 .3V4Z

1U_0 402_6 .3V4Z

C3 4

C3 3

1

1

2

2

0112 c hange size

C C

10U_ 0805_ 6.3V6M

22U_ 0805_ 6.3V6M

C5 9

C6 0

1

1

1

2

2

2

11 /13 u pd ate

D D

+V CCP

47P _0402_50 V8J

47P _0402_50 V8J

C5 1

C5 2

1

@

2

C5 3

1

1

@

@

2

2

1

AF12

AF10

AF71

AG67

AG70

AH71

AN71

AM67

AM70

AH69

AL71

AL69

BU40

BU35

BU28

BN38

BM25

BL30

BJ38

BH32

BH28

BG43

BF16

BF15

BD35

BD33

BD32

BD30

BD28

BD26

BD24

BD23

BD21

BD19

BD17

BD15

BB35

BB33

BB32

BB30

BB28

BB26

BB24

BB23

BB21

BB19

BB17

BB15

AW32

AW30

AW28

AW26

AW24

AW23

AW21

AW19

AW17

AW15

AD15

AD14

AD12

AB12

AA12

W17

W15

W14

W12

R15

C5 33

1

2

0116 a dd

1U_0 402_6 .3V6K

1

2

1U_0 402_6 .3V6K

1U_0 402_6 .3V6K

C6 49

2

GFX VR_E N

1 2

R7 00 4.7K _0201 _5%

VCC _AXG_SE NSE 4 2

VSS_A XG_SENS E 42

GFX VR_V ID_0 42

GFX VR_V ID_1 42

GFX VR_V ID_2 42

GFX VR_V ID_3 42

GFX VR_V ID_4 42

GFX VR_V ID_5 42

GFX VR_V ID_6 42

1 2

GFX VR_EN 4 2

GFX VR_D PRSLPV R 42

GFX VR_IMO N 42

1U_0 402_6 .3V4Z

1U_0 402_6 .3V4Z

C2 1

C2 0

1

1

2

2

330U _B2_ 2.5VM_R15M

22U_ 0805_ 6.3V6M

C2 5

C2 6

1

1

+

@

2

2

11 /27 u pd ate

+VT T_DDR

1U_0 402_6 .3V4Z

1U_0 402_6 .3V4Z

C4 3

C4 2

C4 6

1

1

2

2

10U_ 0805_ 6.3V6M

10U_ 0805_ 6.3V6M

C4 7

1

1

2

2

0116 a dd

1U_0 402_6 .3V6K

1U_0 402_6 .3V6K

C5 34

1

2

1

2

C6 13

C3 83

1

1

2

2

1U_0 402_6 .3V6K

1U_0 402_6 .3V6K

C6 50

C6 48

1

1

2

2

2

R7 054.7 K_020 1_5%@

+1.5 VS_C PU_V DDQ

1U_0 402_6 .3V4Z

1U_0 402_6 .3V4Z

C2 2

1

1

2

2

22U_ 0805_ 6.3V6M

C2 7

1

2

0_06 03_5%

1U_0 402_6 .3V4Z

C4 4

1

2

22U_ 0805_ 6.3V6M

C4 8

1

2

11 /13 u pd ate

1U_0 402_6 .3V6K

1U_0 402_6 .3V6K

C6 14

1

2

1U_0 402_6 .3V6K

1U_0 402_6 .3V6K

C6 52

C6 53

1

2

0116 a dd

+V CCP

1U_0 402_6 .3V4Z

C2 3

1

2

+V CCP

12

L31

+V CCP

10U_ 0805_ 6.3V6M

C4 9

1

2

1U_0 402_6 .3V6K

C6 12

1

2

1U_0 402_6 .3V6K

C6 51

1

2

C2 4

1

2

1

2

+C PU_C ORE

AF57

AF55

AF53

AF51

AF50

AF48

AF46

AF44

AF42

AF41

AD55

AD51

AD48

AD44

AD41

AB55

AB51

AB48

AB44

AB41

AA55

AA51

AA48

AA44

AA41

W55

W51

W48

W44

W41

U55

U51

U48

U44

U41

R55

R51

R48

R44

R41

P60

N55

N51

N48

N44

N42

M60

M51

M44

L55

K60

K51

K44

J55

H60

H51

H44

G60

G55

G51

G44

F55

E60

E57

E53

E50

E46

E42

D59

D57

D55

D54

D52

D50

D48

D47

D45

D43

B60

B56

B53

B49

B46

B42

A57

A54

A50

A47

A43

2.2U _0402 _6.3V4M

3

U1H

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

POWER

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

CPU CO RE SUP PLY

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56

VCC_57

VCC_58

VCC_59

VCC_60

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

VCC_72

VCC_73

VCC_74

VCC_75

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

VCC_81

VCC_82

VCC_83

VCC_84

VCC_85

VCC_86

VCC_87

VCC_88

VCC_89

INT EL_A UBURN DALE _1288

+VCA P0 +VCA P1

2.2U _0402 _6.3V4M

1

C6 8

2

0112 a dd 7pc s Caps to fo llow D esign guide 0112 a dd 7pc s Caps to fo llow D esign guide

2.2U _0402 _6.3V4M

1

1

C6 9

C7 0

2

2

2.2U _0402 _6.3V4M

3

2.2U _0402 _6.3V4M

1

1

C7 1

C7 2

2

2

2.2U _0402 _6.3V4M

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

VCAP0_1

VCAP0_2

VCAP0_3

VCAP0_4

VCAP0_5

VCAP0_6

VCAP0_7

VCAP0_8

VCAP0_9

VCAP0_10

VCAP0_11

VCAP0_12

VCAP0_13

VCAP0_14

VCAP0_15

VCAP0_16

VCAP0_17

VCAP0_18

VCAP0_19

VCAP0_20

VCAP0_21

VCAP0_22

VCAP0_23

VCAP0_24

VCAP0_25

VCAP0_26

VCAP0_27

VCAP1_1

VCAP1_2

VCAP1_3

VCAP1_4

VCAP1_5

VCAP1_6

VCAP1_7

VCAP1_8

VCAP1_9

VCAP1_10

VCAP1_11

VCAP1_12

VCAP1_13

VCAP1_14

VCAP1_15

VCAP1_16

VCAP1_17

VCAP1_18

VCAP1_19

VCAP1_20

VCAP1_21

VCAP1_22

VCAP1_23

VCAP1_24

VCAP1_25

VCAP1_26

VCAP1_27

1

1

C9 3

C1 14

2

2

2.2U _0402 _6.3V4M

BD55

BD51

BD48

BB55

BB51

BB48

AY57

AY53

AY50

AW57

AW53

AW50

AU55

AU51

AU48

AR55

AR51

AR48

AN57

AN53

AN50

AL57

AL53

AL50

AK57

AK53

AK50

BD44

BD41

BD37

BB44

BB41

BB37

AY46

AY42

AY39

AW46

AW42

AW39

AU44

AU41

AU37

AR44

AR41

AR37

AN46

AN42

AN39

AL46

AL42

AL39

AK46

AK42

AK39

+VCA P0

+VCA P1

H_VTTVID1 = Low, 1.1V

H_VTTVID1 = High, 1.05V

PR OC_DP RSLP VR40

VCC SENS E40

VSS SENSE4 0

VCC SENS E

VSS SENSE

10 /01 u pd ate

Ch an ge + VCAP0 /+VCAP 1/ ML CC Cap s fro m

L

1U_ 040 2 t o 2.2 U_0 402 o n S I-2B SV &LV Sku

SM T bu ild.

2.2U _0402 _6.3V4M

2.2U _0402 _6.3V4M

1

1

C1 13

2

2

2.2U _0402 _6.3V4M

2008/09/15 2010/12/31

1

C9 4

2

1

C1 40

C9 2

2

2.2U _0402 _6.3V4M

Compal Secret Data

VTT_S ENSE37

VSS_S ENSE_VT T37

Close to CPU

1 2

R7 5 1 00_04 02_1%

1 2

R7 6 1 00_04 02_1%

+1.8V S

+1.5 VS_C PU_V DDQ

0_06 03_5%

1U_0 402_6 .3V4Z

2.2U _0402 _6.3V4M

1

C1 15

2.2U _0402 _6.3V4M

2

Deciphered Date

4

H_ VID [0..6 ]40

H_V TTVID1

IMV P_IMON40

VCC SENS E

VSS SENSE

L32

4

PSI #40

R7 2

0_02 01_5%

10U_ 0805_ 6.3V6M

1

C3 74.7U _0603 _6.3V6K

2

12

C5 0

C6 3

H_ VID 0

H_ VID 1

H_ VID 2

H_ VID 3

H_ VID 4

H_ VID 5

H_ VID 6

PM_ DPRS LPVR _R

12

0_02 01_5%

R7 3

R7 4

0_02 01_5%

+C PU_C ORE

1

C3 8

2

+V DDQ_ CK

1

2

2.2U _0402 _6.3V4M

1

1

C6 4

2

2

2.2U _0402 _6.3V4M

U1 F

F68

PSI#

A61

VID[0]

D61

VID[1]

D62

VID[2]

A62

VID[3]

B63

VID[4]

D64

VID[5]

D66

VID[6]

AN1

VTT_SELECT[1]

F66

PROC_DPRSLPVR

A41

ISENSE

12

F64

VCC_SENSE

12

F63

VSS_SENSE

N13

VTT_SENSE

R12

VSS_SENSE_VTT

W39

VCCPLL1

W37

VCCPLL2

U37

VCCPLL3

R39

VCCPLL4

R37

VCCPLL5

BB14

VDDQ_CK[1]

BB12

VDDQ_CK[2]

INT EL_A UBURN DALE _1288

04/ 28 Ch ang e P/N fr om SD0340 00080 to

SD0 280 00080

2.2U _0402 _6.3V4M

1

1

C6 5

2

2

1.8V

VTT0_72

R7 7 0_040 2_5%

VTT0_73

C6 6

2.2U _0402 _6.3V4M

1 2

R7 8 0_040 2_5%

1 2

2.2U _0402 _6.3V4M

1

1

C6 7

C8 6

2

2

2.2U _0402 _6.3V4M

Title

Size D ocum ent N umber Re v

Cu stom

LA -5 251 P

Da te: She et o f

5

AW14

VTT0_11

AW12

VTT0_12

AU60

VTT0_13

AU59

VTT0_14

AU12

VTT0_15

AR60

VTT0_16

AR59

VTT0_17

AR12

VTT0_18

AN60

VTT0_19

AN59

VTT0_20

AN35

VTT0_21

AN33

VTT0_22

AN17

VTT0_23

AN15

VTT0_24

AN14

VTT0_25

AN12

VTT0_26

AM10

VTT0_27

AL60

VTT0_28

AL59

VTT0_29

AL17

VTT0_30

AL15

VTT0_31

AL14

VTT0_32

AL12

VTT0_33

AK35

VTT0_34

SENSE LINESCPU VI DS

POWER

2.2U _0402 _6.3V4M

1

C8 9

2

1.1V R AIL PO WER

1

C8 8

2

2.2U _0402 _6.3V4M

VTT0_35

VTT0_36

VTT0_37

VTT0_38

VTT0_39

VTT0_40

VTT0_41

VTT0_42

VTT0_1

VTT0_2

VTT0_3

VTT0_4

VTT0_5

VTT0_6

VTT0_7

VTT0_8

VTT0_9

VTT0_10

VTT0_43

VTT0_44

VTT0_45

VTT0_46

VTT0_47

VTT0_48

VTT0_49

VTT0_50

VTT0_51

VTT0_52

VTT0_53

VTT0_54

VTT0_55

VTT0_56

VTT0_57

VTT0_58

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT0_63

VTT0_64

VTT0_65

VTT0_66

VTT0_67

VTT0_68

VTT0_69

VTT0_70

VTT0_71

VTT0_72

VTT0_73

2.2U _0402 _6.3V4M

1

C8 7

2

AK33

AF39

AF37

AF35

AF33

AF32

AF30

AD39

BF60

BF59

BD60

BD59

BB60

BB59

AY60

AW60

AW35

AW33

AD37

AD35

AD33

AD32

AD30

W35

W33

W32

W30

W28

W26

W24

W23

U35

U33

U32

U30

U28

U26

U24

U23

R35

R33

R32

R30

R28

R26

R24

R23

AY10

AN9

+VC CP

1

1

C8 5

2

2

2.2U _0402 _6.3V4M

Compal Electronics, Inc.

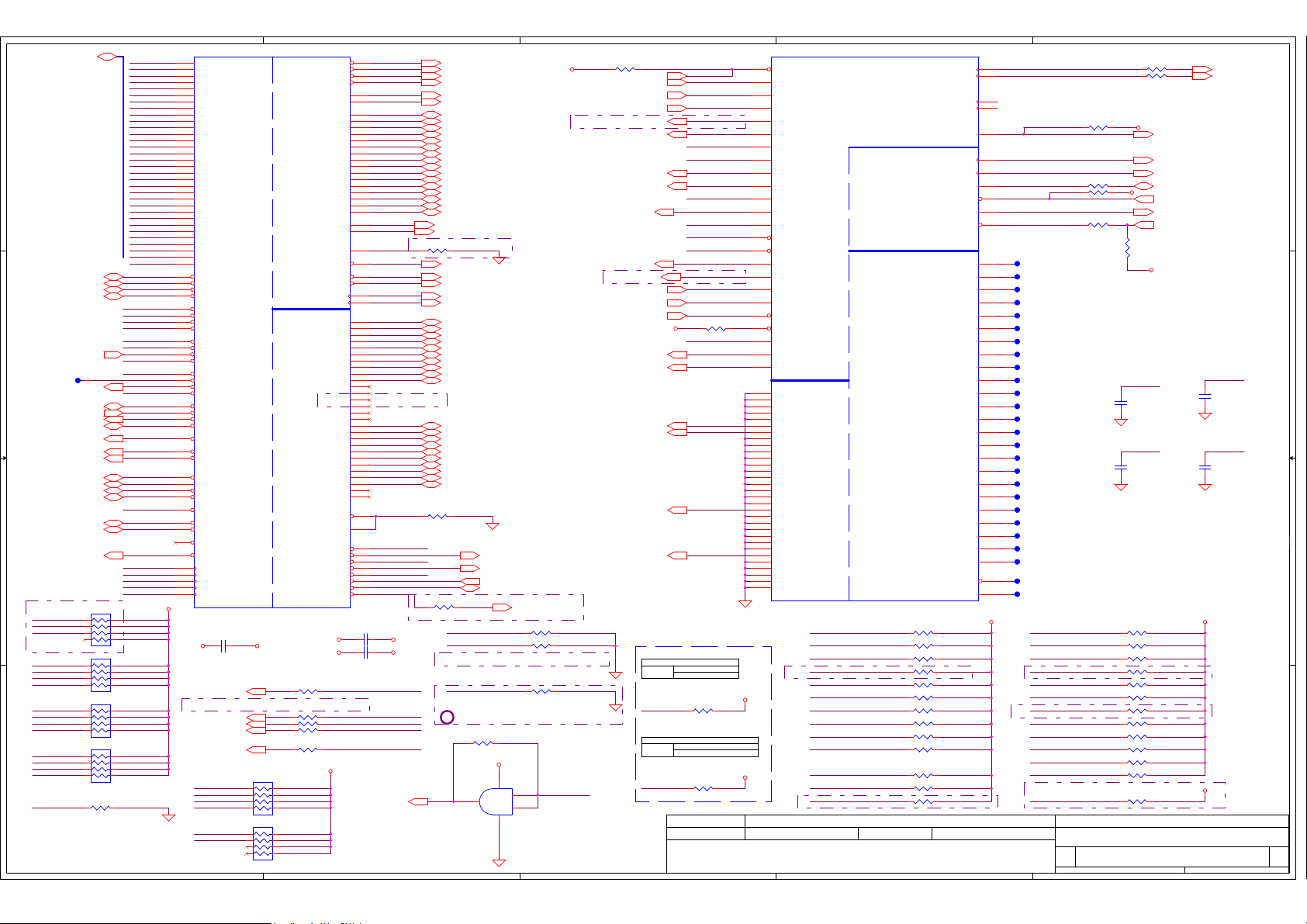

Auburndale(4/5)-PWR

5

+V CCP

VTT0_72

VTT0_73

2.2U _0402 _6.3V4M

1

C9 1

C9 0

2

7 4 7Tues day, Jan uary 05, 2010

0. 9

Page 8

1

2

3

4

5

U1 I

BU62

VSS1

BU58

VSS2

BU55

VSS3

BU51

VSS4

BU48

VSS5

BU44

VSS6

BU37

VSS7

BU32

A A

B B

C C

D D

VSS8

BU25

VSS9

BU21

VSS10

BU18

VSS11

BU14

VSS12

BU11

VSS13

BU7

VSS14

BP42

VSS15

BN64

VSS16

BN6

VSS17

BM70

VSS18

BM51

VSS19

BM44

VSS20

BM32

VSS21

BM24

VSS22

BM17

VSS23

BL57

VSS24

BL55

VSS25

BL48

VSS26

BL40

VSS27

BL28

VSS28

BL20

VSS29

BK63

VSS30

BK60

VSS31

BK53

VSS32

BK34

VSS33

BK10

VSS34

BJ64

VSS35

BJ21

VSS36

BJ9

VSS37

BJ1

VSS38

BH70

VSS39

BH57

VSS40

BH55

VSS41

BH47

VSS42

BH24

VSS43

BH20

VSS44

BH15

VSS45

BG51

VSS46

BG36

VSS47

BF62

VSS48

BF30

VSS49

BF13

VSS50

BF8

VSS51

BE70

VSS52

BE65

VSS53

BE9

VSS54

BE1

VSS55

BD57

VSS56

BD53

VSS57

BD50

VSS58

BD46

VSS59

BD42

VSS60

BD39

VSS61

BD14

VSS62

BB71

VSS63

BB62

VSS64

BB57

VSS65

BB53

VSS66

BB50

VSS67

BB46

VSS68

BB42

VSS69

BB39

VSS70

BB7

VSS71

BB1

VSS72

BA70

VSS73

AY71

VSS74

AY66

VSS75

AY62

VSS76

AY59

VSS77

AY55

VSS78

AY51

VSS79

AY48

VSS80

AR42

VSS140

AR39

VSS141

AR35

VSS142

AR33

VSS143

AR32

VSS144

AR30

VSS145

AR28

VSS146

AR26

VSS147

AR24

VSS148

AR23

VSS149

AR21

VSS150

AR19

VSS151

AR17

VSS152

AR15

VSS153

AR14

VSS154

AR4

VSS155

AR1

VSS156

AP70

VSS157

AP64

VSS158

AN62

VSS159

AN55

VSS160

AY44

VSS81

AY41

VSS82

AY37

VSS83

AY35

VSS84

AY33

VSS85

AY32

VSS86

AY30

VSS87

AY28

VSS88

AY26

VSS89

INT EL_A UBURN DALE _1288

VSS

1

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

AY24

AY23

AY21

AY19

AY17

AY15

AY14

AY12

AY8

AY4

AW67

AW62

AW59

AW55

AW51

AW48

AW44

AW41

AW37

AV9

AV1

AU70

AU62

AU57

AU53

AU50

AU46

AU42

AU39

AU35

AU33

AU32

AU30

AU28

AU26

AU24

AU23

AU21

AU19

AU17

AU15

AU14

AU4

AT64

AT10

AR62

AR57

AR53

AR50

AR46

AN51

AN48

AN44

AN41

AN37

AN5

AN4

AM64

AM8

AL62

AL55

AL51

AL48

AL44

AL41

AL37

AL35

AL33

AL1

AK70

AK64

AK55

AK51

AK48

AK44

AK41

AK37

AK32

AK30

AK28

AK26

AK24

AK23

AK21

AK19

AK17

AK15

AJ70

AH62

AH57

AH55

BV66

BV64

BT68

BR69

BR68

BR3

BN71

BN1

BL71

BL1

R14

H71

F71

E69

E68

A66

A64

E5

C68

U1J

AH53

VSS202

AH51

VSS203

AH50

VSS204

AH48

VSS205

AH46

VSS206

AH44

VSS207

AH42

VSS208

AH41

VSS209

AH39

VSS210

AH37

VSS211

AH35

VSS212

AH33

VSS213

AH32

VSS214

AH30

VSS215

AH28

VSS216

AH26

VSS217

AH24

VSS218

AH23

VSS219

AH21

VSS220

AH19

VSS221

AH17

VSS222

AH15

VSS223

AH4

VSS224

AG64

VSS225

AG9

VSS226

AG6

VSS227

AF69

VSS228

AF62

VSS229

AF1

VSS230

AE70

VSS231

AE64

VSS232

AD62

VSS233

AD57

VSS234

AD53

VSS235

AD50

VSS236

AD46

VSS237

AD42

VSS238

AD4

VSS239

AC67

VSS240

AC64

VSS241

AC10

VSS242

AC5

VSS243

AC1

VSS244

AB70

VSS245

AB62

VSS246

AB57

VSS247

AB53

VSS248

AB50

VSS249

AB46

VSS250

AB42

VSS251

AB39

VSS252

AB37

VSS253

AB35

VSS254

AB33

VSS255

AB32

VSS256

AB30

VSS257

AB28

VSS258

AB26

VSS259

AB24

VSS260

AB23

VSS261

AB21

VSS262

AB19

VSS263

AB17

VSS264

AB15

VSS265

AB14

VSS266

AB9

VSS267

AA66

VSS268

AA64

VSS269

AA62

VSS270

AA57

VSS271

AA53

VSS272

AA50

VSS273

AA46

VSS274

AA42

VSS275

AA39

VSS276

AA37

VSS277

AA35

VSS278

AA33

VSS279

AA32

VSS280

AA30

VSS281

AA28

VSS282

AA26

VSS283

AA24

VSS284

AA23

VSS285

AA21

VSS286

AA19

VSS287

F20

VSS374

F4

VSS375

E37

VSS376

E33

VSS377

E30

VSS378

E16

VSS379

E12

VSS380

D41

VSS381

D38

VSS382

D34

VSS383

D31

VSS384

D27

VSS385

D24

VSS386

D20

VSS387

D17

VSS388

D13

VSS389

D10

VSS390

D6

VSS391

B65

VSS392

B40

VSS415

INT EL_A UBURN DALE _1288

VSS

2

VSS404

VSS405

VSS406

VSS407

VSS408

VSS409

VSS410

VSS411

VSS412

VSS413

VSS393

VSS394

VSS395

VSS396

VSS397

VSS398

VSS399

VSS400

VSS401

VSS402

VSS403

VSS288

VSS289

VSS290

VSS291

VSS292

VSS293

VSS294

VSS295

VSS296

VSS297

VSS298

VSS299

VSS300

VSS301

VSS302

VSS303

VSS304

VSS305

VSS306

VSS307

VSS308

VSS309

VSS310

VSS311

VSS312

VSS313

VSS314

VSS315

VSS316

VSS317

VSS318

VSS319

VSS320

VSS321

VSS322

VSS323

VSS324

VSS325

VSS326

VSS327

VSS328

VSS329

VSS330

VSS331

VSS332

VSS333

VSS334

VSS335

VSS336

VSS337

VSS338

VSS339

VSS340

VSS341

VSS342

VSS343

VSS344

VSS345

VSS346

VSS347

VSS348

VSS349

VSS350

VSS351

VSS352

VSS353

VSS354

VSS355

VSS356

VSS357

VSS358

VSS359

VSS360

VSS361

VSS362

VSS363

VSS364

VSS365

VSS366

VSS367

VSS368

VSS369

VSS370

VSS371

VSS372

VSS373

A40

A36

A33

A29

A26

A22

A19

A15

A12

A8

B62

B58

B55

B51

B48

B44

A59

A55

A52

A48

A45

AA17

AA15

AA14

AA4

W69

W62

W57

W53

W50

W46

W42

W6

W1

V70

U64

U62

U57

U53

U50

U46

U42

U39

U9

U4

T1

R70

R62

R57

R53

R50

R46

R42

R5

P4

N63

N57

N53

N50

N46

N30

N21

N15

M53

M42

M36

M1

L70

L57

L48

L47

L13

K64

K53

K43

K36

K34

K32

K25

K17

K11

K6

K4

J65

J57

J48

J47

J40

J9

H53

H43

H36

H1

G70

G57

G53

G48

G47

G43

G30

G24

G20

G15

F61

F48

F47

F28

+V CCP

1U_0 402_6 .3V6K

0112 Add to fo llow design guide

1U_0 402_6 .3V6K

1

C1 89

2

1

C3 04

2

1U_0 402_6 .3V6K

1

2

1U_0 402_6 .3V6K

1U_0 402_6 .3V6K

1U_0 402_6 .3V6K

1

1

C1 42

C1 91

2

2

1U_0 402_6 .3V6K

1U_0 402_6 .3V6K

1U_0 402_6 .3V6K

C5 10

1

C6 19

2

1U_0 402_6 .3V6K

1

1

C3 03

C3 02

2

2

1U_0 402_6 .3V6K

1

1

C5 09

C5 08

2

2

1U_0 402_6 .3V6K

1U_0 402_6 .3V6K

1

1

C6 18

C5 15

2

2

1U_0 402_6 .3V6K

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

1

1

C1 41

C1 90

2

2

1U_0 402_6 .3V6K

1

1

C3 06

C1 92

2

2

1U_0 402_6 .3V6K

1U_0 402_6 .3V6K

1

1

C3 07

2

2

1U_0 402_6 .3V6K

1U_0 402_6 .3V6K

1

C5 13

2

1U_0 402_6 .3V6K

CPU CORE

1U_0 402_6 .3V6K

1

C2 01

2

1U_0 402_6 .3V6K

1

C3 05

2

1U_0 402_6 .3V6K

1

C5 11

C5 12

2

1U_0 402_6 .3V6K

1

1

C6 28

C6 36

2

2

+C PU_C ORE

22U_ 0805_ 6.3V6MS V@

C7 3

1

2

C9 5

470U _D2_2 VM_R4.5 MSV@

1

+

2

22U_ 0805_6. 3V6M

C1 01

1

2

BGA Ball Cracking Prevention and Detection

100K _0201_5 %

VSS _NCT F1_R5

100K _0201_5 %

VSS _NCT F6_R5 VSS _NCT F7_R5

2008/09/15 2010/12/31

Compal Secret Data

Deciphered Date

22U_ 0805_6. 3V6M

C7 4

1

2

22U_ 0805_6. 3V6M

22U_ 0805_6. 3V6M

C7 6

C7 5

1

1

2

2

22U_ 0805_6. 3V6M

22U_ 0805_6. 3V6M

C7 8

C7 7

1

1

2

2

Inside cavity

470U _D2_2 VM_R4.5 M

C9 7

C9 6

1

1

+

+

2

2

22U_ 0805_6. 3V6M

C1 03

22U_ 0805_ 6.3V6MS V@

C1 02

1

1

2

1

2

2

05 /0 6 upd ate t o c hange

C9 8

C95 ,C9 6,C 97,C98 f rom

1

SGA 000 02X 00( 330 U_7mR) to

+

SGA 000 042 00( 470U_4 .5mR)

2

1- SV BGA 4x 470uF bu lk on C95, C96,C 97,C98

L

2- LV BG A 3 x33 0uF 9mR (SG A20 331 E10 ) bul k on C96,C 97,C98

Under cavity

22U_ 0805_6. 3V6M

C1 05

C1 04

22U_ 0805_ 6.3V6MS V@

1

1

2

2

22U_ 0805_6. 3V6M

C1 06

22U_ 0805_ 6.3V6MS V@

1

2

470U _D2_2 VM_R4.5 M

470U _D2_2 VM_R4.5 M

Under cavity

+3VS

12

R8 0

+3VS +3VS

R8 1

4

12

CRA CK_B GA

3

Q3B

5

2N70 02DW -T/R7 _SOT363-6

4

CRA CK_B GA

61

Q4A

2N70 02DW -T/R7 _SOT363-6

2

VSS _NCT F2_R5

Title

Size D ocum ent N umber Re v

Cu stom

Da te: She et

22U_ 0805_6. 3V6M

C1 08

+3VS

22U_ 0805_6. 3V6M

22U_ 0805_6. 3V6M

C8 0

1

1

2

2

22U_ 0805_6. 3V6M

C1 09

1

2

12

2

12

5

C8 2

C8 1

1

2

22U_ 0805_6. 3V6M

C1 10

1

2

61

Q3A

2N70 02DW -T/R7 _SOT363-6

CRA CK_B GA

3

Q4B

2N70 02DW -T/R7 _SOT363-6

4

22U_ 0805_6. 3V6M

C7 9

1

2

22U_ 0805_ 6.3V6MS V@

C1 07

1

2

R7 9

100K _0201_5 %

R8 2

100K _0201_5 %

Compal Electronics, Inc.

Auburndale(5/5)-GND/Bypass

LA -5 251 P

5

22U_ 0805_6. 3V6M

SV@

22U_ 0805_ 6.3V6M

C8 3

1

1

2

2

CRA CK_B GA 17, 30

o f

8 4 7Tues day, Jan uary 05, 2010

C8 4

0. 9

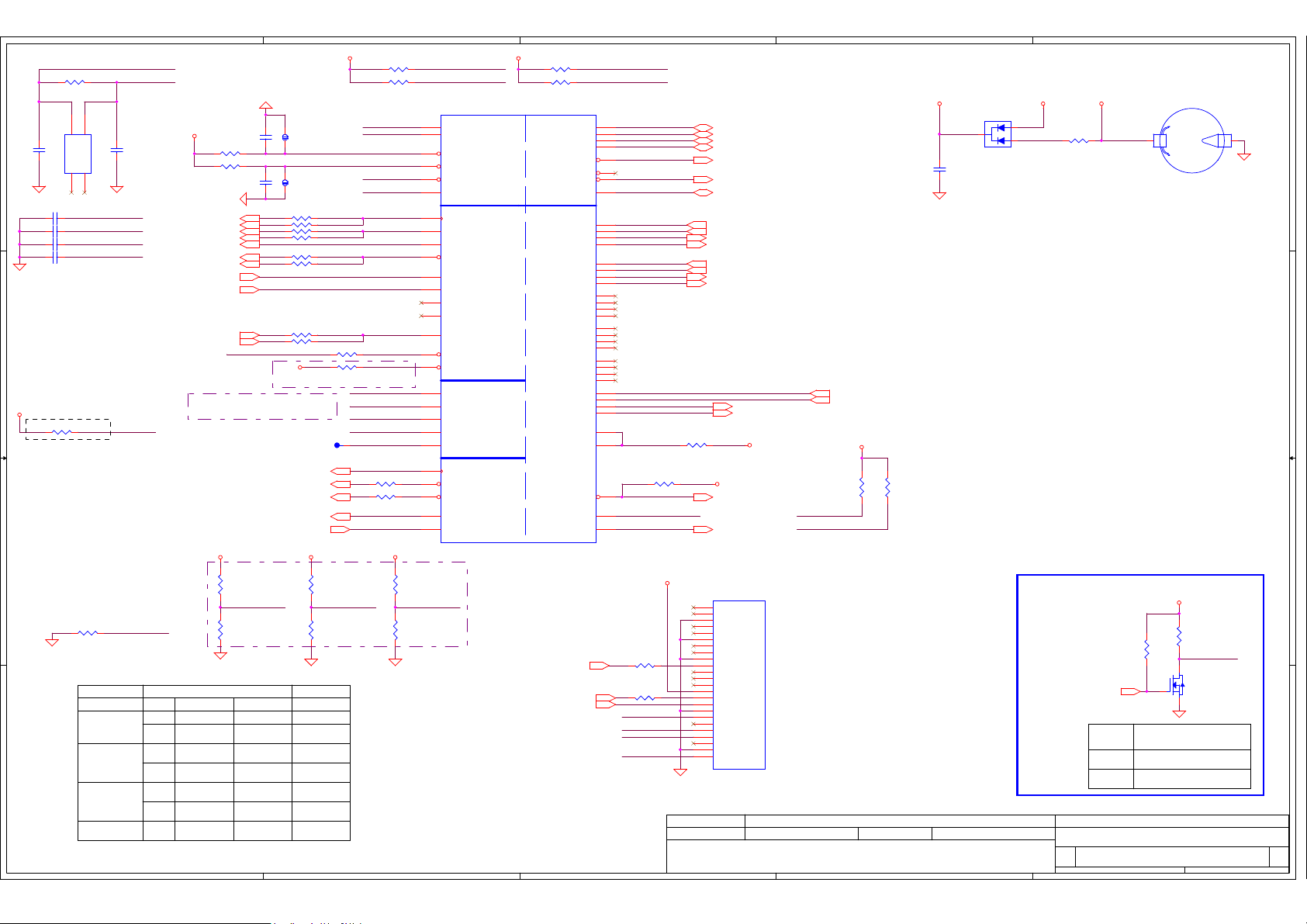

Page 9

1

DDR3 SO-DIMM B

+V _DD R_CP U_REF

0.1U _0402 _16V4Z

2.2U _0805 _16V4Z

C1 11

1

2

A A

B B

C C

D D

C1 12

1

2

DDR_ CKE2 _DIM MB6

DD R_B_B S26

M_ CLK_ DDR26

M_ CLK_D DR#26

DD R_B_B S06

DD R_B _WE#6

DD R_B_ CAS#6

DDR_ CS3_ DIMM B#6

+3VS

DD R_B _D0

DD R_B _D1

DD R_B_ DM0

DD R_B _D2

DD R_B _D3

DD R_B _D8

DD R_B _D9

DD R_B_ DQS# 1

DD R_B _DQS 1

DD R_B _D10

DD R_B _D11

DD R_B _D16

DD R_B _D17

DD R_B_ DQS# 2

DD R_B _DQS 2

DD R_B _D18

DD R_B _D19

DD R_B _D24

DD R_B _D25

DD R_B_ DM3

DD R_B _D26

DD R_B _D27

DDR_ CKE2 _DIM MB

DD R_B_ BS2

DDR_ B_MA 12

DDR_ B_M A9

DDR_B_MA8

DDR_ B_M A5

DDR_ B_M A3

DDR_ B_M A1

M _CLK_ DDR2

M _CLK_ DDR#2

DDR_ B_MA 10

DD R_B_ BS0

DD R_B _WE#

DD R_B_ CAS#

DDR_ B_MA 13

DDR_ CS3_ DIMM B#

DD R_B _D32

DD R_B _D33

DD R_B_ DQS# 4

DD R_B _DQS 4

DD R_B _D34

DD R_B _D35

DD R_B _D40

DD R_B _D41

DD R_B_ DM5

DD R_B _D42

DD R_B _D43

DD R_B _D48

DD R_B _D49

DD R_B_ DQS# 6

DD R_B _DQS 6

DD R_B _D50

DD R_B _D51

DD R_B _D56

DD R_B _D57

DD R_B_ DM7

DD R_B _D58

DD R_B _D59

1 2

10K _0201_5%

2.2U _0402 _6.3V6M

0.1U _0402 _16V4Z

C1 36

C1 37

1

1

2

2

+1.5 V + 1.5V

3A @

3A @ 1. 5 V

3A @3A @

JDI MB1

1

VREF_DQ

3

VSS

5

DQ0

7

DQ1

9

VSS

11

DM0

13

VSS

15

DQ2

17

DQ3

19

VSS

21

DQ8

23

DQ9

25

VSS

27

DQS1#

29

DQS1

31

VSS

33

DQ10

35

DQ11

37

VSS

39

DQ16

41

DQ17

43

VSS

45

DQS2#

47

DQS2

49

VSS

51

DQ18

53

DQ19

55

VSS

57

DQ24

59

DQ25

61

VSS

63

DM3

65

VSS

67

DQ26

69

DQ27

71

VSS

73

CKE0

75

VDD

77

NC

79

BA2

81

VDD

83

A12/BC#

85

A9

87

VDD

89

A8

91

A5

93

VDD

95

A3

97

A1

99

VDD

101

CK0

103

CK0#

105

VDD

107

A10/AP

109

BA0

111

VDD

113

WE#

115

CAS#

117

VDD

119

A13

121

S1#

123

VDD

125

TEST

127

VSS

129

DQ32

131

DQ33

133

VSS

135

DQS4#

137

DQS4

139

VSS

141

DQ34

143

DQ35

145

VSS

147

DQ40

149

DQ41

151

VSS

153

DM5

155

VSS

157

DQ42

159

DQ43