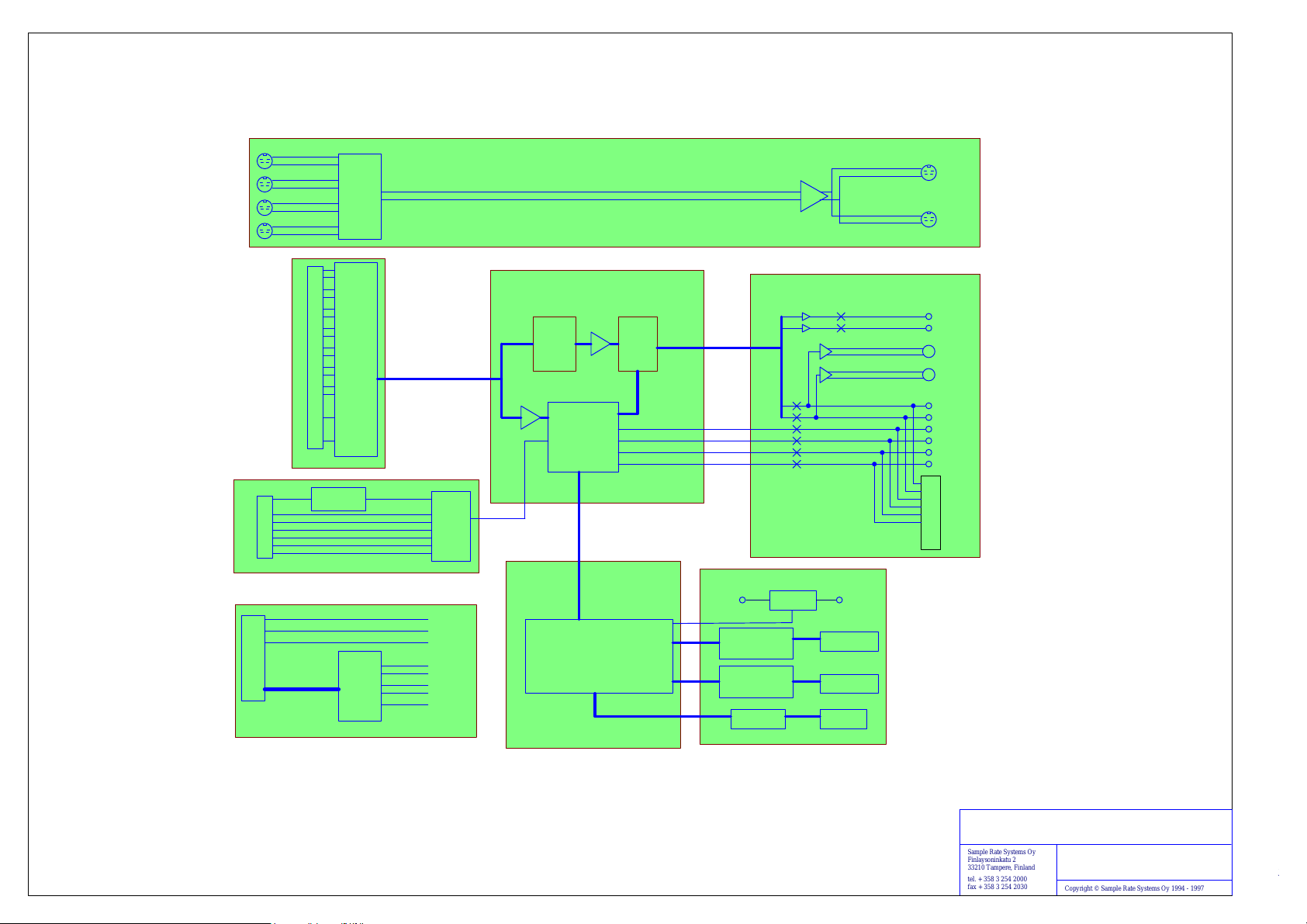

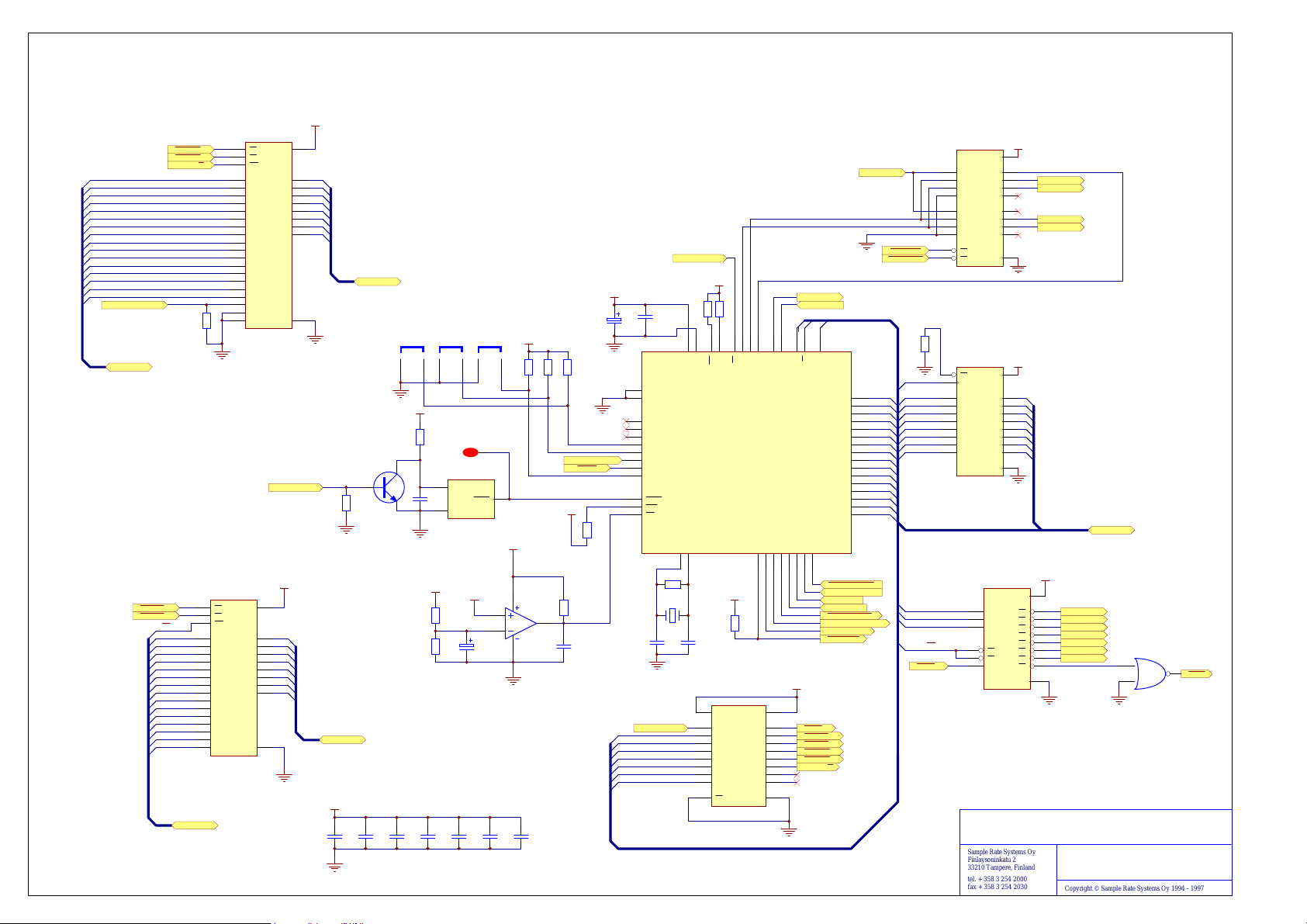

Classe Audio SSP-25 Schematic

D:\CLASSE\HW\VER30\MOTHER~1\DESIGN~1\MOTHER.PRJ

SSP-25 Motherboard

Classe Audio Inc

Classe Audio Inc

SVHS switching

SVHS inputs SVHS

SVHS

Switching

svhs.sch

Audio inputs

Listening

selector

DSP and Bypass

Volume

control

Bypass

relay

Output buffersOutbuf.sch

Buffers

TAPE

output

Balanced

output

digin.sch

Digital inputs

Dig. conn.

Power supply

POWER IN

powers.sch

Analog input connector

inputbuf.sch

RF-demodulator

module

Power

supply

Digital

input

selection

+5D Standby

+5D switched

Digital ground

+15V analog

-15V analog

+5V analog

-5V analog

Analog ground

Microcontroller

micro.sch

DSP MODULE

Analog

audio in

Digital

audio in

DSP SPI

Microcontroller

5.1 ch.

audio out

dsp.sch

Interface

Remote in

interfac.sch

I/O

interface

Bus

interface

BUFFER

BUFFER

Remote out

Frontp.

Display

RS232

R

L

Rs

Ls

C

SUB

D25

5.1ch

output

Title:

SSP-25

Project:

MB block diagram

Sample Rate Systems Oy

Finlaysoninkatu 2

33210 Tampere, Finland

tel. + 358 3 254 2000

fax + 358 3 254 2030

Sheet: 1 of 9 , revision 3.0

2-Dec-1998 Printed:

File:

Copyright © Sample Rate Systems Oy 1994 - 1997

, drawn by Tero

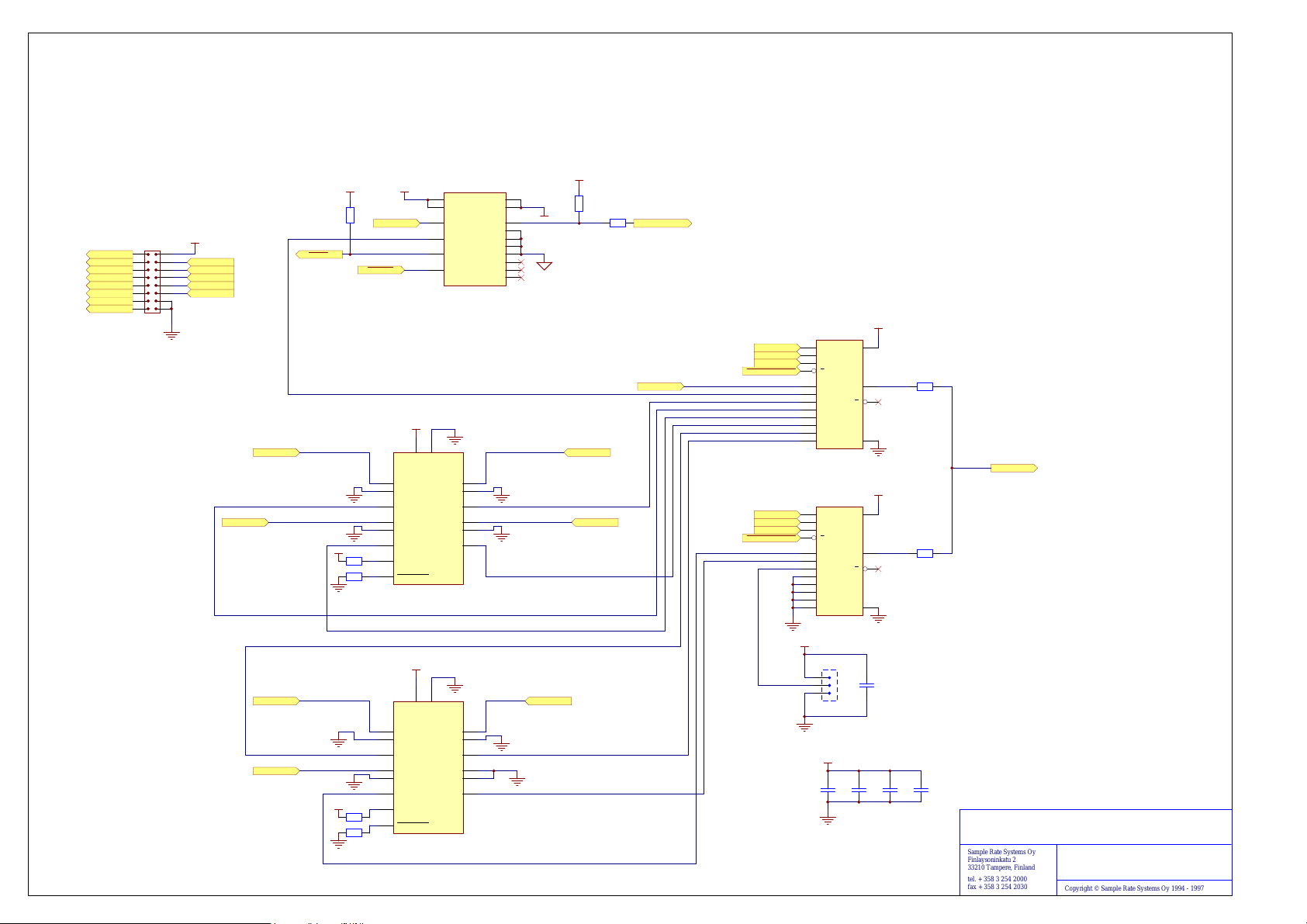

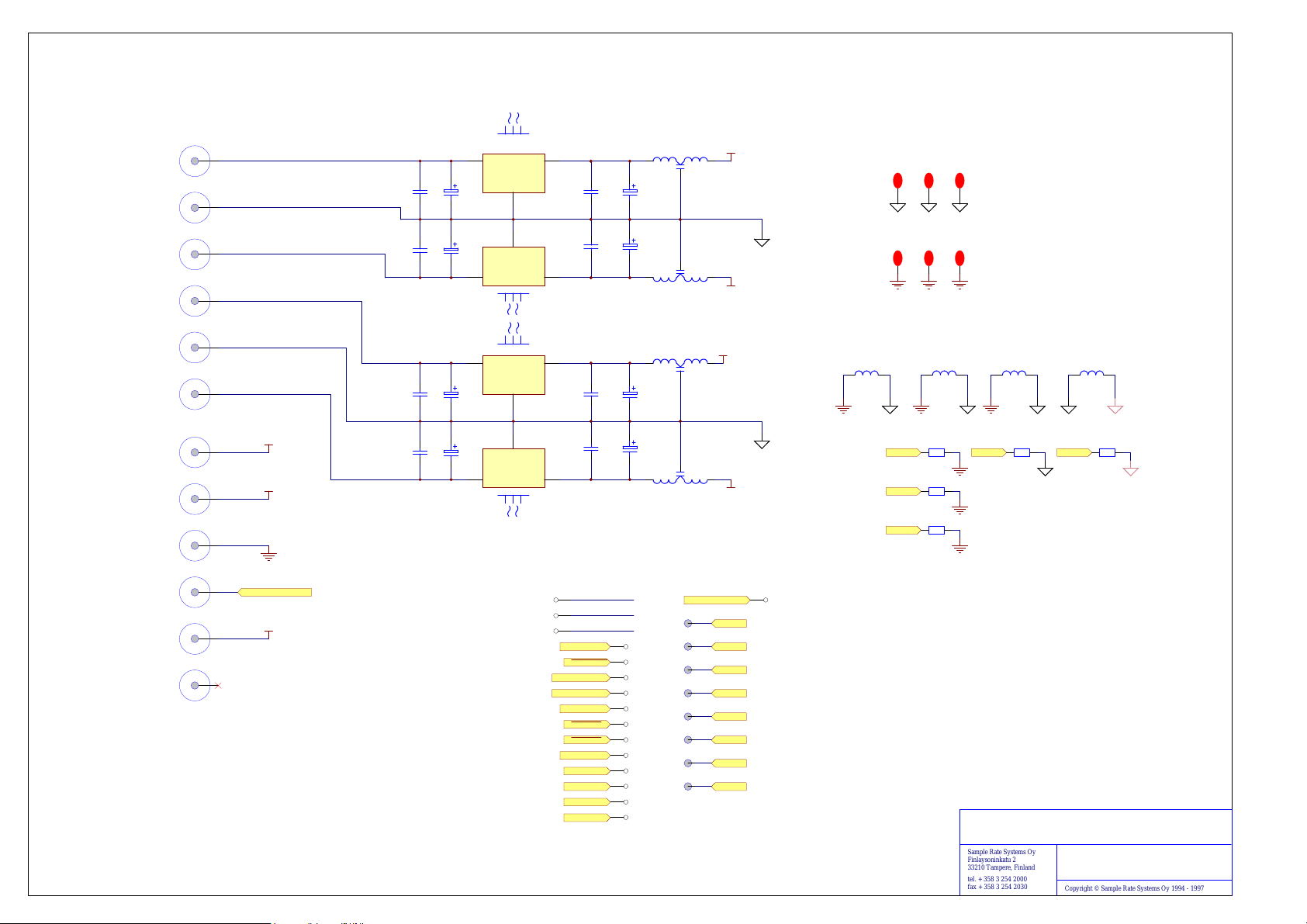

SPDIF RECEIVER & RF DEMODULATOR & SWITCHING

Classe Audio Inc

Classe Audio Inc

DIGITAL CONNECTOR

COX_DIGITAL1

COX_DIGITAL2

COX_DIGITAL3

COX_DIGITAL4

COX_DIGITAL5

COX_DIGITAL6

COX_DIGITAL7

1 2

3 4

5 6

7 8

9 10

11 12

15 16

OPTICAL_IN

X15

16Pin IDC PCB mounting header

+5D

SEL_VIDEO_0

SEL_VIDEO_1

SEL_VIDEO_2

SEL_VIDEO_3

OPTIONAL_RF

1413

COX_DIGITAL3

-5A

COX_DIGITAL6

+5D

R85

10k

COX_DIGITAL4

+5D

R86

10k

OPTIONAL_RF

AC3_OK

COX_DIGITAL1 COX_DIGITAL2

COX_DIGITAL5

COX_DIGITAL7

RF_RESET

2

1

3

6

7

+5D

+5D

5

R70

4

10k

12

R68

IC19

10k

26LS32DIP

2

1

3

6

7

5

4

R69

12

10k

IC18

R67

26LS32DIP

10k

+5A

+5D

16

Input A+

Input A-

Output A

Input C+

Input C-

Output C

3-State Control

3-State Control

+5D

16

Input A+

Input A-

Output A

Input C+

Input C-

Output C

3-State Control

3-State Control

11

12

8

Vcc

8

Vcc

MODULE2

1

+5 V

+5 V

RF in

S/PDIF out

/AC-3 OK

LED+

/reset14S/PDIF-

S/PDIF+

14

15

13

10

9

11

14

15

13

10

9

11

-5 V

-5 V

GND

GND

GND

GND

GND

3

8

RF DEMODULATOR VER. 3.X

GND

Input B+

Input B-

Output B

Input D+

Input D-

Output D

GND

Input B+

Input B-

Output B

Input D+

Input D-

Output D

2

4

5

6

7

9

10

13

15

16

R83

RF_INSTALLED

1k

+5D

16

VCC

R75

5

Z

Z

GND

VCC

Z

Z

GND

100

6

8

SPDIF_IN

+5D

16

R74

5

100

6

8

C62

100nF

OPTICAL_IN

SPDIF_SEL_0

SPDIF_SEL_1

SPDIF_SEL_2

SPDIF_SEL_BANK_0

SPDIF_SEL_0

SPDIF_SEL_1

SPDIF_SEL_2

SPDIF_SEL_BANK_1

IC22

11

S0

10

S1

9

S2

7

E

4

I0

3

I1

2

I2

1

I3

15

I4

14

I5

13

I6

12

I7

74HCT251

IC21

11

S0

10

S1

9

S2

7

E

4

I0

3

I1

2

I2

1

I3

15

I4

14

I5

13

I6

12

I7

74HCT251

+5D

X14

1

2

3

Not installed

+5D

C106

100nF

C100

100nF

C101

100nF

C107

100nF

Title:

SSP-25

Project:

Digital inputs

Sample Rate Systems Oy

Finlaysoninkatu 2

33210 Tampere, Finland

tel. + 358 3 254 2000

fax + 358 3 254 2030

Sheet: 3 of 9 , revision 3.0

2-Dec-1998 Printed:

File: D:\CLASSE\HW\VER30\MOTHER~1\DESIGN~1\DIGIN.SCH

, drawn by Tero

Copyright © Sample Rate Systems Oy 1994 - 1997

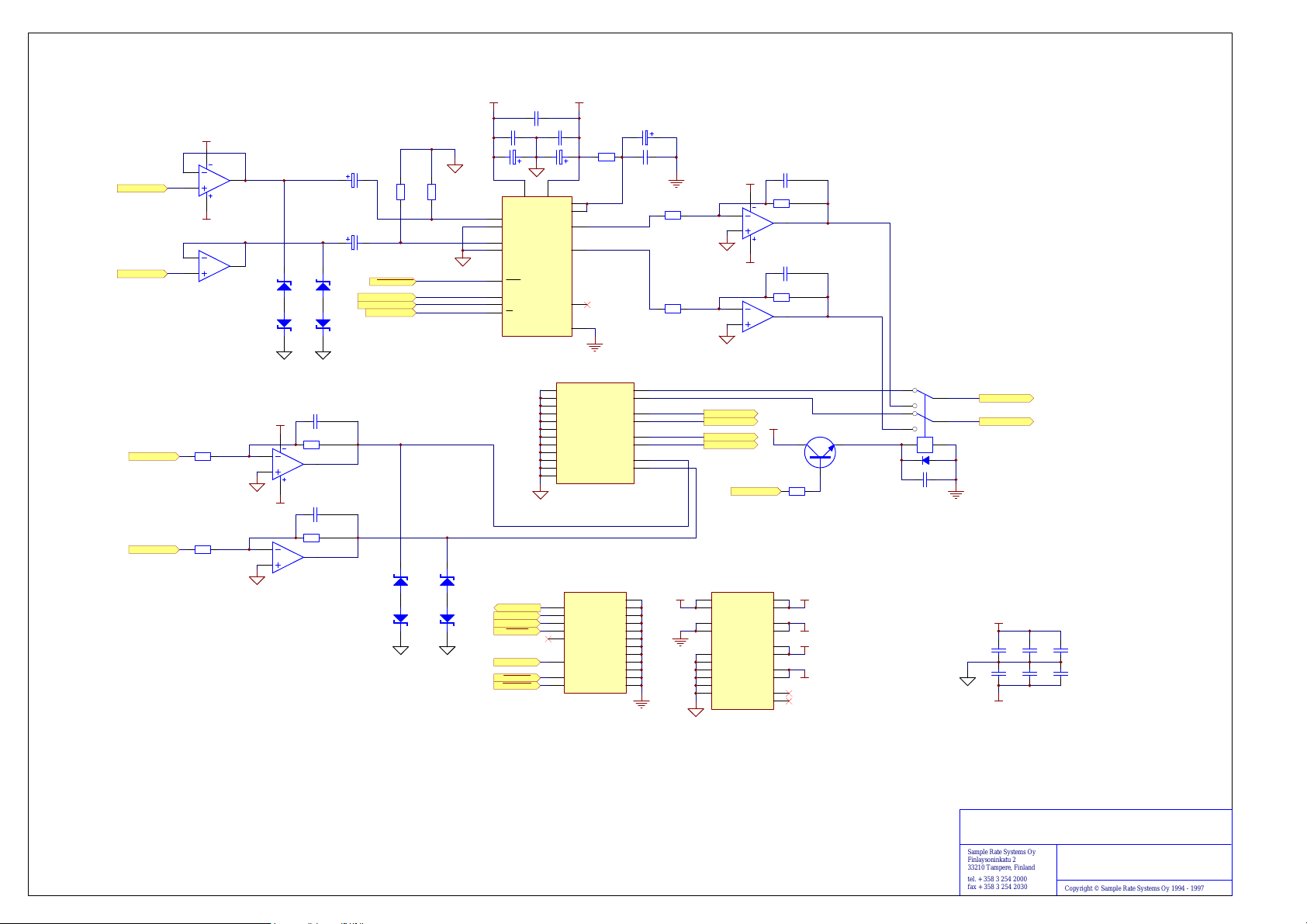

LISTENING_L

Classe Audio Inc

Classe Audio Inc

LISTENING_R

-5A +5A

-15A

D15

4V3

D13

4V3

C60

10uF

C81

10uF

CS3310_MUTE

AUDIO_SPI_SCK

AUDIO_SPI_MOSI

SEL_BP_VOL

R63

100k

R57

100k

16

15

9

10

8

6

2

2

3

6

5

1

IC11A

OPA2134

8 4

+15A

7

IC11B

OPA2134

D6

4V3

D8

4V3

100nF

C68

C70 100nF C69

C79

10uF

13

IC10

VA-

AINL

AGNDL

AINR

AGNDR

MUTE

SCLK

SDATAI3SDATAO

CS

CS3310

12

C78

10uF

VA+

ZCEN

AOUTL

AOUTR

DGND

VD+

100nF

C80

10uF

R56

10

C65

100nF

4

1

14

11

7

5

R53

10k

R64

10k

2

3

6

5

C59

22p

-15A

R55

39K

1

IC9A

OPA2134

8 4

C76

22p

+15A

R61

39K

7

IC9B

OPA2134

LISTENING_L

LISTENING_R

R58

100k

R62

100k

MODULE1B

A2

AGND

A4

C61

10p

-15A

R54

100k

2

3

1

IC12A

OPA2134

8 4

C77

10p

+15A

AGND

A5

AGND

AGNDA6left Surr. Out

AGNDA8Right Surr. Out

A10

AGND

A12

AGND

A14

AGND

A15

AGND

A16

AGND

A18

AGND

A20

AGND

THX THEATER

left Out

Right Out

Center Out

Subwoofer Out

Left In

Right In

A1

DSP_L

A3

DSP_R 13

A7

A9

A11

A13

A17

A19

DSP_SRND_LEFT

DSP_SRND_RIGHT

DSP_CENTER

DSP_SUBWOOFER

SEL_BYPASS

+5D

2 3

1

R60

1k

Q4

BC182LB

11

9

6

8

RE7

MCS2H-S

D11

1N4148

C75

100nF

RELAY_OUT_L

4

116

RELAY_OUT_R

R65

100k

6

5

IC12B

OPA2134

7

D9

4V3

D10

4V3

D14

4V3

DSP_SPI_MISO

DSP_SPI_SCK

D12

DSP_SPI_MOSI

4V3

SEL_DSP

SPDIF_IN

DSP_MUTE

DSP_RESET

MODULE1A

D1

D2

D3

D5

D7

D19

D15

D11

THX THEATER

SPI-Dout

SPI-SCK

SPI-Din

SPI-/Sel

SPI-/HREQ

SPDIF In

/mute

/reset

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

+5STDBY

MODULE1C

P1

P2

P3

P4

P11

P12

P17

P18

P19

P20

THX THEATER

+5 Dig.

+5 Dig.

DGND

DGND

AGND

AGND

AGND

AGND

AGND

AGND

+15 An.

+15 An.

-15 An.

-15 An.

+5 An.

+5 An.

-5 An.

-5 An.

P15

+15A

P16

P13

P14

-15A

P9

+5A

P10

P7

P8

-5A

P6

n.c.

P5

n.c.

+15A

C72

C74

100nF

C66

100nF

C67

100nF

C73

100nF

100nF

C71

100nF

-15A

D4

D6

D8

D9

D10

D12

D13

D14

D16

D17

D18

D20

Title:

SSP-25

Project:

DSP & Bypass

Sample Rate Systems Oy

Finlaysoninkatu 2

33210 Tampere, Finland

tel. + 358 3 254 2000

fax + 358 3 254 2030

Sheet: 3 of 9 , revision 3.0

2-Dec-1998 Printed:

File: D:\CLASSE\HW\VER30\MOTHER~1\DESIGN~1\DSP.SCH

, drawn by Tero

Copyright © Sample Rate Systems Oy 1994 - 1997

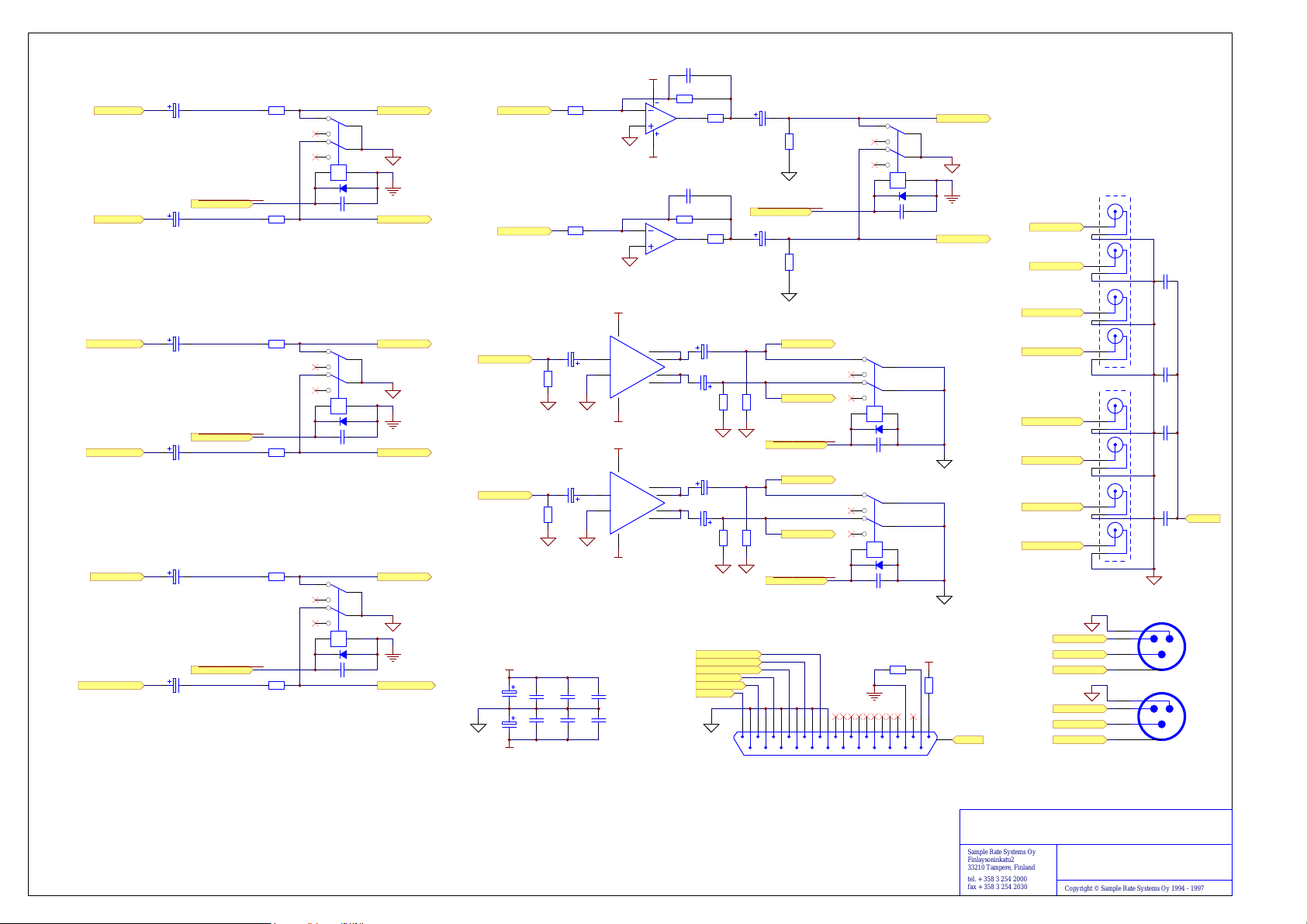

D:\CLASSE\HW\VER30\MOTHER~1\DESIGN~1\OUTBUF.SCH

RELAY_OUT_L

Classe Audio Inc

Classe Audio Inc

RELAY_OUT_R

DSP_SRND_LEFT

DSP_SRND_RIGHT

DSP_CENTER

DSP_SUBWOOFER

C50

100uF

C49

100uF

C36

100uF

C35

100uF

C22

100uF

C21

100uF

MUTE_MAIN_RELAY

MUTE_MAIN_RELAY

MUTE_MAIN_RELAY

C28

68p

-15A

R42

56R

11

9

6

8

LEFT_OUT

13

RE5

MCS2H-S

4

116

LISTENING_L

R40

10k

D5 1N4148

R41

56R

C43 100nF

RIGHT_OUT

LISTENING_R

R45

10k

R39

20k

2

3

8 4

+15A

IC6A

OPA2134

R37

1

56R

C57

68p

R44

20k

6

5

IC6B

OPA2134

R46

7

56R

C63

100uF

MUTE_TAPE_RELAY

C64

100uF

R50

100k

R51

100k

11

9

6

8

D7 1N4148

C58 100nF

TAPE_LEFT_OUT

13

RE6

MCS2H-S

4

116

TAPE_RIGHT_OUT

LEFT_OUT

RIGHT_OUT

X8

Red/White

1

2

3

4

C4

10nF

+15A

IC8

6

R33

56R

11

9

6

8

13

4

116

LSURROUND_OUT

RE4

MCS2H-S

LEFT_OUT

C40

100uF

4

R18

10k

3

D4 1N4148

R32

56R

R16

56R

R15

56R

C32 100nF

11

9

6

8

D1 1N4148

C19 100nF

13

4

116

RSURROUND_OUT

CENTER_OUT

RE1

MCS2H-S

SUBWOOFER_OUT

RIGHT_OUT

Bypass capacitors

+15A

C18

10uF

C17

10uF

-15A

C45

100nF

C44

100nF

C33

100uF

4

C54

not installed

C53

not installed

3

R17

10k

V+

SENSE+

Vin

gnd

SENSE-

V-

5

-15A

+15A

6

V+

SENSE+

Vin

gnd

SENSE-

V-

5

-15A

C39

not installed

C37

not installed

8 Pin socket installed

7

FORCE+

FORCE-

2

IC5

8 Pin socket installed

7

FORCE+

FORCE-

2

C52

8

100uF

C55

1

100uF

R20

10k

C41

8

100uF

C34

1

100uF

R23

10k

R19

10k

R22

10k

BAL_OUT_L_+

BAL_OUT_L_-

MUTE_BAL_RELAY

BAL_OUT_R_+

BAL_OUT_R_-

MUTE_BAL_RELAY

11

9

6

8

D3 1N4148

C24 100nF

11

9

6

8

D2 1N4148

C23 100nF

13

RE2

MCS2H-S

4

116

13

RE3

MCS2H-S

4

116

PREOUT

RSURROUND_OUT

LSURROUND_OUT

SUBWOOFER_OUT

RIGHT_OUT

CENTER_OUT

LEFT_OUT

11421531641751861972082192210231124122513

X11

25 Pin 90deg PCB mount with boardlocks

+5D

R13

0R

R14

100

26

SHIELD

LSURROUND_OUT

RSURROUND_OUT

CENTER_OUT

SUBWOOFER_OUT

TAPE_LEFT_OUT

TAPE_RIGHT_OUT

BAL_OUT_L_+

BAL_OUT_L_-

SHIELD

BAL_OUT_R_+

BAL_OUT_R_-

SHIELD

5

6

7

8

X7

Red/White

1

2

3

4

5

6

7

8

1

2

3

4

1

2

3

4

C2

10nF

C1

10nF

C3

10nF

X9

Neutrik NC3MAH

X10

Neutrik NC3MAH

SHIELD

Title:

SSP-25

Project:

Output buffers

Sample Rate Systems Oy

Finlaysoninkatu2

33210 Tampere, Finland

tel. + 358 3 254 2000

fax + 358 3 254 2030

Sheet: 4 of 9 , revision 3.0

2-Dec-1998 Printed:

File:

, drawn by Tero

Copyright © Sample Rate Systems Oy 1994 - 1997

Classe Audio Inc

Classe Audio Inc

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

FLASH_SEL_STORE

M_BUS

SRAM_CE

SRAM_OE

R/W

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

FLASH_CE

FLASH_OE

FLASH_R/W

IC30

TC55257DPI

M_BUS

20

22

27

10

9

8

7

6

5

4

3

25

24

21

23

2

26

1

IC34

AM29F010 (Installed on socket)

22

CE

VCC

24

OE

31

WE

12

A0

DQ0

11

A1

DQ1

10

A2

DQ2

9

A3

DQ3

8

A4

DQ4

7

A5

DQ5

6

A6

DQ6

5

A7

DQ7

27

A8

26

A9

23

A10

25

A11

4

A12

28

A13

29

A14

3

A15

2

A16

30

A17

R66

1

GND

A18

10k

RESET_MYSELF

+5STDBY

CE

OE

WE

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

28

VCC

AD0

11

DQ0

AD1

12

DQ1

AD2

13

DQ2

AD3

15

DQ3

AD4

16

DQ4

AD5

17

DQ5

AD6

18

DQ6

AD7

19

DQ7

14

GND

+5STDBY

32

13

14

15

17

18

19

20

21

16

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

+5STDBY

M_BUS

R81

10k

C122

100nF

M_BUS

Q5

BC182LB

1

C115

100nF

1

23

C114

100nF

J3

Not installed

2

+5STDBY

R82

330

+5STDBY

C121

10nF

J2

Not installed

J1

1

1

2

TP21

Scopehook (not installed)

IC29

1

VCC

RESET

3

DGND

DS1233

+POWER_GOOD

R78

3k

C113

R77

1uF

2k

C119

C129

100nF

100nF

+5STDBY

2pin 100mil pin strip

R87

2

10k

2

+5STDBY

84

IC26A

LM393

3

2

C117

C110

100nF

100nF

SPI BUFFER

IC25

74HC244

DSP_SPI_MISO

IO_ENABLE

+5STDBY

C116

C118

100uF

100nF

R88

R89

10k

10k

52

Vrh

51

Vrl

50

PE7/AN7

48

PE6/AN6

46

PE5/AN5

44

PE4/AN4

49

PE3/AN3

47

E

R/W

A11

A12

A13

A14

A15

45

43

17

18

19

PE2/AN2

PE1/AN1

PE0/AN0

RESET

XIRQ

IRQ

IO_ENABLE

RF_INSTALLED

AC3_OK

+5STDBY

R79

10k

R76

10k

1

C109

10nF

+5STDBY

R80

R90

10k

10k

1

26

3

2

Vss

Vdd

MODA/LIR

MODB/Vstby

IC32

MC68HC11E0 (Installed on socket)

EXTAL7XTAL

8

R93

1M

XTAL1

+5STDBY

8MHz

C128

C127

22p

22p

IC24

PAL16L8BCN (Installed on socket)

1

CLK/I0

2

I1

3

I2

4

I3

5

I4

6

I5

7

I6

8

I7

9

I8

OE/I911GND

25

24

PD5/SS

R72

10k

23

PD4/SCK

PD3/MOSI

VCC

I/O0

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

21

22

PD2/MISO

PA6/OC2/OC1

PA7/PAI/OC1

29

28

27

PD0/RxD20PD1/TxD

PA4/OC4/OC1

PA5/OC3/OC1

31

30

+5STDBY

20

12

13

14

15

16

17

18

19

10

6

4E5

STRA/AS

STRB/R/W

IO_SEL

SRAM_OE

SRAM_CE

FLASH_OE

FLASH_CE

FLASH_R/W

TxD

RxD

EASR/W

PC0/A0/D0

PC1/A1/D1

PC2/A2/D2

PC3/A3/D3

PC4/A4/D4

PC5/A5/D5

PC6/A6/D6

PC7/A7/D7

PB0/A8

PB1/A9

PB2/A10

PB3/A11

PB4/A12

PB5/A13

PB6/A14

PB7/A15

PA0/IC334PA1/IC233PA2/IC132PA3/OC5/OC1

REMOTE_CONTROL

VOL_ROT_0

VOL_ROT_1

KBD_SCAN

SEL_DATA_LATCH

SWITCHED_POWER_ON

RESET_MYSELF

EN_LATCHES

EN_DSP_SPI

EN_AUDIO_SPI

9

AD0

10

AD1

11

AD2

12

AD3

13

AD4

14

AD5

15

AD6

16

AD7

42

A8

41

A9

40

A10

39

A11

38

A12

37

A13

36

A14

35

A15

1

19

R84

10k

IC31

74HC573

1

11

AS

2

AD0

3

AD1

4

AD2

5

AD3

6

AD4

7

AD5

8

AD6

9

AD7

A0

A1

A2

R/W

IO_SEL

Address decoding

+5STDBY

20

VCC

1A121Y1

1A241Y2

1A361Y3

1A481Y4

2A1172Y1

2A2152Y2

2A3132Y3

2A4112Y4

1G

2G

OE

CLK

1D

2D

3D

4D

5D

6D

7D

8D

18

16

14

12

3

5

7

9

10

GND

+5STDBY

20

VCC

19

1Q

18

2Q

17

3Q

16

4Q

15

5Q

14

6Q

13

7Q

12

8Q

10

GND

IC33

74AC138

1

A0

2

A1

3

A2

4

E1

5

E2

6

E3

Title:

SSP-25

Project:

Microcontroller

Sample Rate Systems Oy

Finlaysoninkatu 2

33210 Tampere, Finland

tel. + 358 3 254 2000

fax + 358 3 254 2030

Vcc

GND

A0

A1

A2

A3

A4

A5

A6

A7

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

DSP_SPI_MOSI

DSP_SPI_SCK

AUDIO_SPI_MOSI

AUDIO_SPI_SCK

M_BUS

+5STDBY

16

15

KBD_LE_0

14

FREE_1

13

LED_LE_0

12

LED_LE_1

11

EN_CTLR0

10

EN_CTLR1

9

EN_CTLR2

7

8

IC35D

11

12

13

LCD_E

74HC02

Sheet: 5 of 9 , revision 3.0

2-Dec-1998 Printed:

File: D:\CLASSE\HW\VER30\MOTHER~1\DESIGN~1\MICRO.SCH

, drawn by Tero

Copyright © Sample Rate Systems Oy 1994 - 1997

D:\CLASSE\HW\VER30\MOTHER~1\DESIGN~1\INTERFAC.SCH

M_BUS

Classe Audio Inc

Classe Audio Inc

SEL_DATA_LATCH

Frontpanel connector

X18

34Pin IDC PCB mounting header

1 2

LD0 LD1

3 4

LD2 LD3

5 6

LD4 LD5

7 8

LD6 LD7

9 10

11 12

1413

15 16

1817

19 20

21

22

23

24

25

26

27 28

29 30

31 32

33 34

+5STDBY

16

C102

1uF

2

C98

6

1uF

14

7

13

8

15

RS232_TxD

RS232_RxD

C105

1uF

LED_LE_1

KBD_LE_0

LCD_E

FREE_1

EN_LATCHES

EN_CTLR0

LD0

LD1

LD2

LD3

LD4

LD5

LD6

LD7

+5DVcc

R48

10k

X12

10Pin IDC PCB mounting header

1 2

3 4

5 6

7 8

9 10

11

1

2

3

4

5

6

7

8

9

IC27

74HC574

OE

CLK

1D

2D

3D

4D

5D

6D

7D

8D

VCC

GND

EN_LATCHES

EN_CTLR2

LD0

LD1

LD2

LD3

LD4

LD5

LD6

LD7

1

11

2

3

4

5

6

7

8

9

IC23

74HC574

OE

CLK

1D

2D

3D

4D

5D

6D

7D

8D

+5STDBY

20

VCC

19

1Q

18

2Q

17

3Q

16

4Q

15

5Q

14

6Q

13

7Q

12

8Q

10

GND

2345678

SEL_LISTENING

CS3310_MUTE

MUTE_MAIN

MUTE_TAPE

SEL_VIDEO_0

SEL_VIDEO_1

SEL_VIDEO_2

SEL_VIDEO_3

9

RP2

10k

1

+5STDBY

20

19

1Q

18

2Q

17

3Q

16

4Q

15

5Q

14

6Q

13

7Q

12

8Q

LD0

LD1

LD2

LD3

LD4

LD5

LD6

LD7

2345678

10

IC20

74HC574

1

OE

VCC

11

CLK

2

1D

1Q

3

2D

2Q

4

3D

3Q

5

4D

4Q

6

5D

5Q

7

6D

6Q

8

7D

7Q

9

8D

8Q

GND

+5STDBY

20

19

18

17

16

15

14

13

12

10

SPDIF_SEL_0

SPDIF_SEL_1

SPDIF_SEL_2

RF_RESET

DSP_RESET

DSP_MUTE

SEL_BYPASS

SEL_BP_VOL

9

RP3

10k

1

2345678

+5STDBY

1

9

RP1

10k

EN_LATCHES

EN_CTLR1

LCD_R/W

LCD_R/S

EN_DSP_SPI

EN_AUDIO_SPI

SEL_DSP

SPDIF_SEL_BANK_0

SPDIF_SEL_BANK_1

FLASH_SEL_STORE

Line filters

C125

IR_RECEIVER

VOL_ROT_0

VOL_ROT_1

KBD_SCAN

1nF

+5STDBY

C120

100nF

C112

100nF

C108

100nF

C103

100nF

C111

100nF

C123

C124

1nF

C126

1nF

1nF

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

1

19

IC28

74HC244

1A121Y1

1A241Y2

1A361Y3

1A481Y4

2A1172Y1

2A2152Y2

2A3132Y3

2A4112Y4

1G

2G

+5STDBY

20

VCC

LD0

18

LD1

16

LD2

14

LD3

12

LD4

3

LD5

5

LD6

7

LD7

9

10

GND

VOL_ROT_0 VOL_ROT_1

KBD_SCAN LED_LE_0

EN_LATCHES

IR_RECEIVER

LCD_R/W

LCD_R/S

+5STDBY

+5D

RS232 buffer

IC17

C104

1uF

1

C1+

3

C1-

4

C2+

5

C2-

C99

1uF

R71

100k

11

10

12

9

T1In

T2In

R1Out

R2Out

MAX232

TxD

RxD

T1Out

T2Out

V+

V-

R1In

R2In

GND

R91

C130

Not installed

10

1

2

IC36

SFH610-A2

+5STDBY

3

4

REMOTE_IN

Remote link

IC35A

74HC02

R92

C131

1k

330nF

IR_RECEIVER

8

9

IC35C

74HC02

10

+5STDBY

14

VCC

2

3

1

7

GND

REMOTE_OUT

REMOTE_CONTROL

IC35B

5

6

7HC402

R47

470

4

MUTE_MAIN

MUTE_MAIN

+5D

+5D

2 3

1

R52

470

2 3

1

R49

Not installed

MUTE_MAIN_RELAY

Q2

BC182LB

MUTE_BAL_RELAY

Q1

Jumper installed, see notes

MUTE_TAPE

+5D

2 3

1

R59

1k

MUTE_TAPE_RELAY

Q3

BC182LB

Title:

SSP-25

Project:

I/O Interface

Sample Rate Systems Oy

Finlaysoninkatu 2

33210 Tampere, Finland

tel. + 358 3 254 2000

fax + 358 3 254 2030

Sheet: 6 of 9 , revision 3.0

2-Dec-1998 Printed:

File:

, drawn by Tero

Copyright © Sample Rate Systems Oy 1994 - 1997

Mute drivers

D:\CLASSE\HW\VER30\MOTHER~1\DESIGN~1\POWERS.SCH

Power connectors

Classe Audio Inc

Classe Audio Inc

X16

6

5

C83

100nF

C82

330uF

IC14

7815

1

Vin

HS1

Thermalloy 6398B

Vout

GND

2

Scope hooks

L6

C93

100nF

Murata DSS306-55F223Z16

C92

2200uF

3

+15A

TP10

Scopehook (not installed)

TP7

Scopehook (not installed)

TP6

Scopehook (not installed)

4

3

2

1

Molex 6Pin PCB header with friction lock

X17

6

5

4

3

2

1

+5STDBY

+5D

SWITCHED_POWER_ON

+POWER_GOOD

Molex 6Pin PCB header with friction lock

C96

100nF

C85

100nF

C94

100nF

C97

330uF

C84

330uF

C95

330uF

2

Vin

IC16

7915

1

Vin

2

Vin

1

GND

-Vout

Thermalloy 6398B

Vout

GND

IC13

2

7805C

IC15

1

79M05

GND

-Vout

HS2

Thermalloy 6398B

3

HS3

HS4

Thermalloy 6398B

3

3

TP19

TP12

TP5

SEL_BYPASS

CS3310_MUTE

AUDIO_SPI_SCK

AUDIO_SPI_MOSI

SEL_BP_VOL

MUTE_MAIN

MUTE_TAPE

SEL_LISTENING

SEL_VIDEO_0

SEL_VIDEO_1

SEL_VIDEO_2

SEL_VIDEO_3

C90

100nF

C86

100nF

C89

100nF

+POWER_GOOD

+5D

DGND

C91

2200uF

L5

Murata DSS306-55F223Z16

L3

Murata DSS306-55F223Z16

C87

2200uF

C88

2200uF

L4

Murata DSS306-55F223Z16

SWITCHED_POWER_ON

MH8

3mm

TP11

TP18

TP15

TP16

TP17

TP8

TP9

TP13

TP1

TP2

TP3

MH6

3mm

MH5

3mm

MH2

3mm

MH7

3mm

MH1

3mm

MH4

3mm

MH3

3mm

TP4

+5A

SHIELD

SHIELD

SHIELD

SHIELD

SHIELD

SHIELD

SHIELD

SHIELD

TP23

Scopehook (not installed)

TP14

Scopehook (not installed)

TP22

Scopehook (not installed)

-15A

Ground connects

L7

Ferrite bead (Not installed)

-5A

SHIELD

SHIELD

SHIELD

L2

Ferrite bead

R95

0R

R73

0R

R94

0R

TP20

L8

Ferrite bead (Not installed)

R21

SHIELD

0R

Title:

SSP-25

Project:

Power supplies

Sample Rate Systems Oy

Finlaysoninkatu 2

33210 Tampere, Finland

tel. + 358 3 254 2000

fax + 358 3 254 2030

L1

Ferrite bead

VGNDAGND

R43

SHIELD

0R

AGND VGND

Sheet: 8 of 9 , revision 3.0

2-Dec-1998 Printed:

File:

Copyright © Sample Rate Systems Oy 1994 - 1997

, drawn by Tero

Loading...

Loading...